# UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Site Selective Laser Processing for Flexible and Wearable Electronics with 2D Materials and 2D-like Random Networks

**Permalink** https://escholarship.org/uc/item/9x96s2pn

Author KWON, HYUKJUN

**Publication Date** 2015

Peer reviewed|Thesis/dissertation

### Site Selective Laser Processing

### for Flexible and Wearable Electronics with 2D Materials and 2D-like Random Networks

by

### Hyuk-Jun Kwon

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Mechanical Engineering

and the Designated Emphasis

in

Nanoscale Science and Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Costas P. Grigoropoulos, Chair Professor Liwei Lin Professor Oscar D. Dubon

Summer 2015

Site Selective Laser Processing

for Flexible and Wearable Electronics with 2D Materials and 2D-like Random Networks

Copyright © 2015

By

Hyuk-Jun Kwon

#### ABSTRACT

#### Site Selective Laser Processing

for Flexible and Wearable Electronics with 2D Materials and 2D-like Random Networks

by

### Hyuk-Jun Kwon

#### Doctor of Philosophy in Engineering - Mechanical Engineering

and the Designated Emphasis in Nanoscale Science and Engineering

University of California, Berkeley

Professor Costas P. Grigoropoulos, Chair

Flexible and wearable electronics are envisioned as a future platform of electronics integrated into a variety of emerging technologies from sensing and monitoring to human-inspired applications. Among many fascinated flexible applications, displays are aggressively developing field of research and they are widely connected with transistor platform. Currently, the needs of people are being particular about for mobile phones, portable devices, and even televisions; they require new and more advanced displays. Therefore, the future displays should have high performances, such as low power consumption, ultra-high resolution, high frame rate and robust flexible platform. High-mobility thin film transistors will be a key enabling technology for achieving such performance by reducing the transistor size in the display's active area. Also, they helps to increase aperture ratio, brightness, and frame rates and to decrease bus-line load power consumption.

In this regard, 2D transition metal dichalcogenides have attracted much interest owing to their finite band gap values, rich excitonic dynamics, and even valley polarization (valleytronics) associated with the broken inversion symmetry. Among these 2D materials, molybdenum disulfide ( $MoS_2$ ) has been considered a channel material for high speed and/or flexible devices and a component material to improve the performance of conventional silicon devices. Furthermore, these layered semiconductors are emerging alternatives to silicon-based electronics. Despite their potentials in electronics and optoelectronics, reliable and stable processing methods are needed for successful transition to practical applications, especially for the flexible/wearable electronics used flexible materials with a low thermal budget (< 200 °C). Typically, used flexible materials cannot be applied conventional high thermal processes, which affect the entire panel including unwanted areas where the high thermal process should be excluded.

For the process having the critical limitations of the flexible/wearable applications, the many features of laser are exactly appropriate; the laser is spatially local selective, air-stable, and widely tunable by varying the duration and intensity of laser irradiation. Moreover, laser process can be digitally controlled by the computer with programmable software. In this dissertation, the proposed approaches (laser annealing, direct laser writing, laser welding, and interference lithography) represent a powerful means to realize high performance flexible devices based 2D materials, especially for MoS<sub>2</sub>.

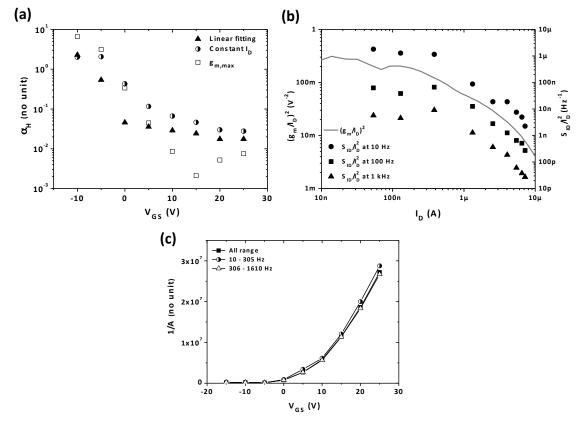

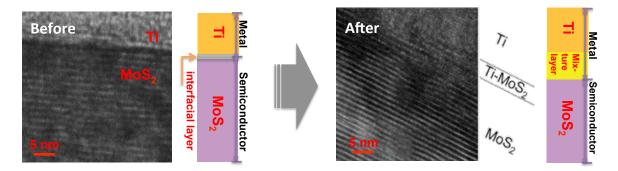

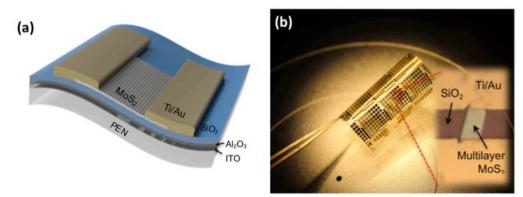

First, I demonstrate that mechanically flexible and optically transparent (more than 81% transmittance in visible wavelength) multilayered MoS<sub>2</sub> thin-film transistors (TFTs) in which the source/drain electrodes are selectively annealed using picosecond laser achieve the enhancement of device performance without plastic deformation, such as boosted mobility, increased output resistance, and decreased subthreshold swing. Numerical thermal simulation for the temperature distribution, transmission electron microscopy (TEM) analysis, current-voltage measurements, and contact-free mobility extracted from the Y-function method (YFM) enable understanding of the compatibility and the effects of pulsed laser annealing process; the enhanced performance originated not only from a decrease in the Schottky barrier effect at the contact, but also an improvement of the channel interface.

Second, through laser direct writing (LDW) method, arbitrary fine patterns are produced for the electrodes as well as defining the channel of TFTs. Also, LDW with ink-jet printing shows the possibility and the potential for the future of flexible/wearable electronics as more versatile process. In addition, interference lithography using phase shift mask allows making periodic nano-scale features, readily.

Furthermore, laser process is also applied to the welding for fabricating mechanically robust and electrically attractive 2D-like random networks. The laser welding is compatible with cost-effective solution process and good for the flexible applications. After the laser welding, the sheet resistance of 2D-like networks created by silver nanowires is significantly improved. Note that the best improvement is around 55 times without any degradation of the electrical performance during cycling bending test.

These various outcomes from the experiments indicate that the site selective laser process can open up opportunities to fabrication of the electrical devices on flexible platforms.

To my parents, my advisor, all committee members, LTL family, my friends, and god

Thank you for all of your love, support, and inspiration. I couldn't have made it without you all.

# **Table of Contents**

# **Chapter 1: Introduction**

| 1.1 Flexible Electronics                   | 1   |

|--------------------------------------------|-----|

| 1.2 Trends of Flexible Displays            | 2   |

| 1.3 Key Component for Displays             | 4   |

| 1.3.1 Flexible substrate                   | 5   |

| 1.3.2 Driving circuitry: TFTs              | 6   |

| 1.3.3 Display module                       | 8   |

| 1.3.1 Supporting films                     | 8   |

| 1.4 Laser Processing for Flexible Displays | 9   |

| 1.5 Scope of Dissertation                  | .10 |

# **Chapter 2: Physical Properties of 2D materials**

| 2.1 2D Transition Metal Dichalcogenides (TMDs)                           |    |

|--------------------------------------------------------------------------|----|

| 2.2 Properties of 2D MoS <sub>2</sub>                                    |    |

| 2.3 Monolayer vs. Multilayer                                             | 14 |

| 2.4 Effects of Temperature and Ambient Conditions: MoS <sub>2</sub> TFTs | 14 |

| 2.4.1 Device preparation                                                 |    |

| 2.4.2 Result and discussion                                              |    |

| 2.5 Analysis of Flicker Noise: MoS <sub>2</sub> TFTs                     | 20 |

| 2.5.1 Device preparation                                                 | 21 |

| 2.5.2 Result and discussion                                              | 23 |

| 2.6 Summary                                                              |    |

|                                                                          |    |

# Chapter 3: Pulsed Laser Annealing for Flexible/Transparent MoS<sub>2</sub> TFTs

| 3.1 Metal-Semiconductor Junctions: Contacts                                        | 27 |

|------------------------------------------------------------------------------------|----|

| 3.2 Pulsed Laser Annealing                                                         |    |

| 3.3 Model of Thermal Analysis for Pulsed Laser Annealing                           |    |

| 3.3.1 Ultra-fast electron dynamics                                                 | 28 |

| 2.3.2 Computation of temperature distribution                                      | 29 |

| 3.4 Effects of Pulsed Laser Annealing I: Flexible Multilayer MoS <sub>2</sub> TFTs | 30 |

| 3.4.1 Device preparation                                                           | 30 |

| 3.4.2 Pulsed laser annealing system                                                | 31 |

| 3.4.3 Temperature distribution                                                     | 32 |

| a. Contact (between metal and semiconductor)                                       |    |

| b. Interface (between semiconductor and dielectric layer)                          |    |

| 3.4.4 Current-voltage measurement (2-terminal): contact resistance                     | 35 |

|----------------------------------------------------------------------------------------|----|

| 3.4.5 Electrical performance                                                           |    |

| 3.4.6 TEM analysis at the contacts: Schottky barrier                                   |    |

| 3.4.7 Y-function method: intrinsic mobility                                            |    |

| 3.5 Effects of Pulsed Laser Annealing II: Transparent Multilayer MoS <sub>2</sub> TFTs |    |

| 3.5.1 Device preparation                                                               | 43 |

| 3.5.2 Results and discussion                                                           |    |

| 3.6 Summary                                                                            | 47 |

# Chapter 4: Non-vacuum and Maskless Laser Direct Writing Process and Sol-gel ZrO<sub>2</sub> for MoS<sub>2</sub> Transistor with Highly Boosted Mobility

| 4.1 Laser Direct Writing (LDW)                                                | 48 |

|-------------------------------------------------------------------------------|----|

| 4.2 High-k Dielectric Materials                                               | 49 |

| 4.3 Sol-gel ZrO <sub>2</sub> of MoS <sub>2</sub> Transistor Fabricated by LDW | 49 |

| 4.3.1 Device preparation                                                      | 49 |

| 4.3.3 LDW lithography and behavior                                            |    |

| 4.3.3 Electrical performance                                                  | 54 |

| 4.4 Summary                                                                   | 57 |

|                                                                               |    |

# Chapter 5: Laser-Induced Fine Patterns and Ink-Jet Printing Process for MoS<sub>2</sub> Transistors

| 5.1 Fine Patterns through Laser                             | 58 |

|-------------------------------------------------------------|----|

| 5.1.1 Line-by-line laser scanning                           | 59 |

| 5.1.2 Interference lithography                              | 61 |

| 5.2 Ink-Jet Printing Process                                | 65 |

| 5.2.1 Capilary with positively laser patterned geometry     | 65 |

| 5.2.2 Self-align through negativly laser patterned geometry | 69 |

| 5.3 MoS <sub>2</sub> Transistors                            | 70 |

| 5.3.1 Device preparation                                    | 70 |

| 5.3.2 Electrical performance                                | 71 |

| 5.4 Summary                                                 |    |

# Chapter 6: Laser Welded 2D-like Random Networks for Robust Flexible MoS<sub>2</sub> Transistors

| 6.1 2D-like Random Networks of AgNWs         | 75 |

|----------------------------------------------|----|

| 6.2 Laser Welding on 2D-like Random Networks | 76 |

| 6.3 Robust Flexible MoS <sub>2</sub> Transistors on the Solution Based PI Substrate with Laser |    |

|------------------------------------------------------------------------------------------------|----|

| Welded 2D-like Random Network Electrodes                                                       | 77 |

| 6.3.1 Device preparation                                                                       | 78 |

| 6.3.2 Electrical performance                                                                   | 79 |

| 6.3.3 Mechanical flexibility                                                                   | 81 |

| a. Numerical simulation (hyperelastic nonlinear analysis)                                      |    |

| b. Mechanical bending tolerance test                                                           |    |

| 6.4 Summary                                                                                    | 84 |

# **Chapter 7: Conclusions**

| <ul><li>7.1 Concluding Remarks</li><li>7.2 Future Works</li></ul> |  |

|-------------------------------------------------------------------|--|

| References                                                        |  |

# **LIST OF FIGURES**

### <Chapter 1>

- **Figure 1.1** New paradigm and platform of flexible/wearable electronics and their various applications including flexible displays, human-inspired electronics, sensors, and energy/power devices. (images from Google search)

- **Figure 1.2** Big evolution of display platform and paradigm away from CRT to FPD and to the odd-shaped future flexible display. (images from Google search)

- **Figure 1.3** Total market value of flexible/conformal electronics versus non-flexible/rigid electronics 2013-2023. (from IDTechEx forecast report)

- **Figure 1.4** Total market value of only flexible/conformal electronics 2013-2023. (from IDTechEx forecast report)

- **Figure 1.5** Schematic cross-sectional display structure briefly separated by four parts: (1) substrate, (2) driving circuitry, (3) display module, and (4) supporting films. (image from S. Kim and H.–J. Kwon *et al.* Adv. Mat. 2011)

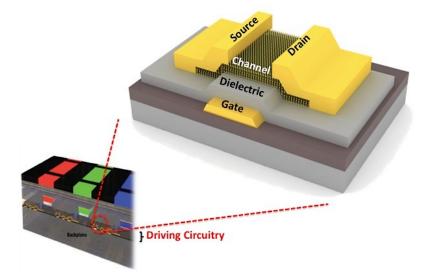

- Figure 1.6 Schematic cross-sectional TFT structure with three electrodes: gate, source, and drain.

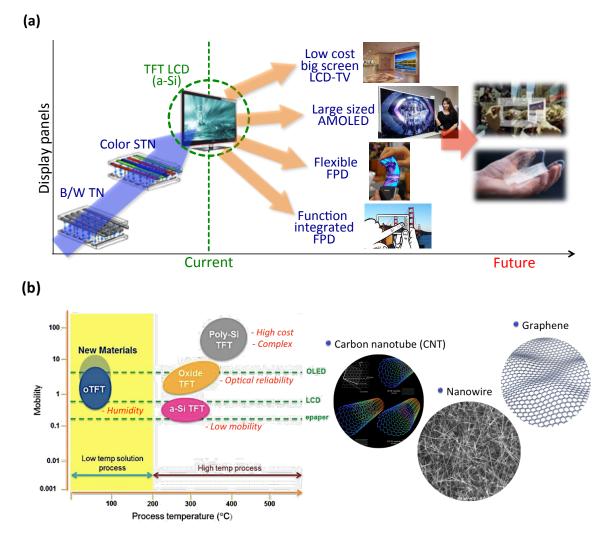

- Figure 1.7 (a) Trends of technology of commercialized display panels. Currently, the promise of OLED technology has been to deliver displays that are more visually compelling and power efficient. Furthermore, the resolution and size of displays keeps going up caused by customers' needs. (b) TFT technologies and candidates of channel materials by the mobility and process temperature for the next generation flexible displays. (graph from plastic logic company and images from Google search)

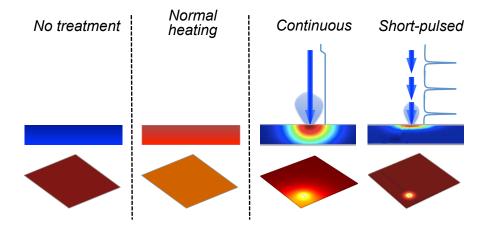

- **Figure 1.8** The spatial temperature distributions plotted along the surface for conventional thermal annealing as well as continuous laser and pulsed lasers heating.

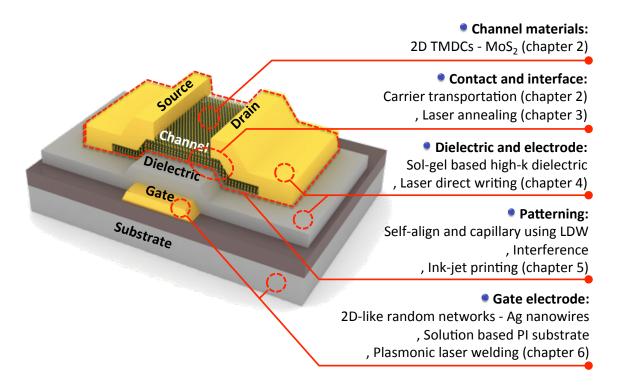

- **Figure 1.9** Organized schematics for the structure of this research and dissertation, showing the five technical focus areas on the TFTs: (1) 2D channel materials, (2) contact and interface, (3) dielectric and defining electrodes using LDW, (4) maskless small patterning (LDW and interference) with ink-jet printing, (5) 2D-like random networks using Ag nanowires and plasmonic laser welding process for the gate electrode.

### <Chapter 2>

- **Figure 2.1** Combinations and structures for 2D materials with the formula MX<sub>2</sub>, where M is a transition metal element from group IV, V or VI and X is chalcogen. (images from Google search)

- **Figure 2.2** Calculated band structures of MoS<sub>2</sub>: (a) bulk, (b) quadrilayer, (c) bilayer, and (c) monolayer. The top of valence band (blue) and bottom of conduction band (red) are highlighted. (image from A. Splendiani *et al.* Nano Lett. 2010)

- Figure 2.3 Multilayer MoS<sub>2</sub> TFT structure: (a) the cross-sectional schematic structure of a multilayer MoS<sub>2</sub> TFT with a 300-nm-thick SiO<sub>2</sub> gate dielectric. (b) The top view of a 3D confocal laser microscope image of a multilayer MoS<sub>2</sub> transistor after fabrication.

- **Figure 2.4** Representative electrical characteristics of multilayer  $MoS_2$  TFT at room temperature: (a) the plot of  $I_D$ - $V_D$ . (b) Plots of  $I_D$ - $V_G$  (left axis) and  $I_D^{0.5}$ - $V_G$  (right axis).

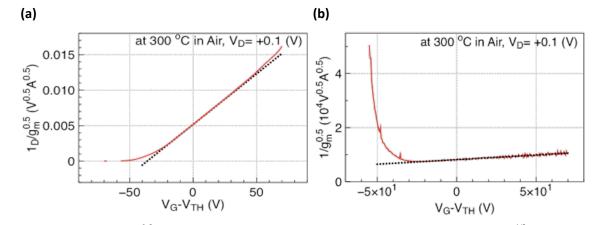

- **Figure 2.5** (a) The  $I_d/g_m^{0.5}$  plot with linear fitting in ambient condition. (b) The plot of  $1/g_m^{1/2}$  with respect to gate voltage with linear fitting for evaluation of mobility attenuation factor,  $\theta$ .

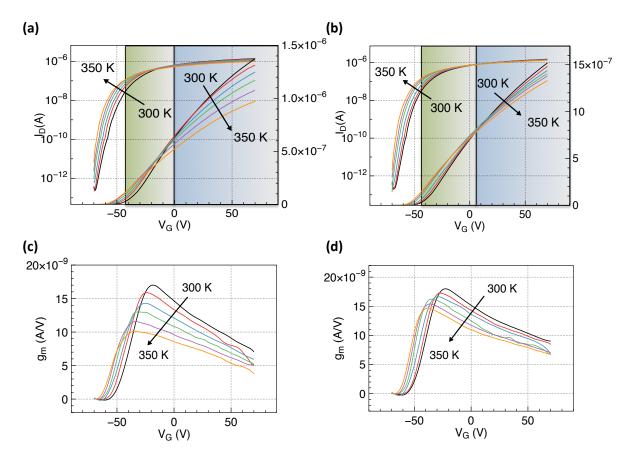

- Figure 2.6 The typical  $I_D$ - $V_G$  transfer characteristics of the fabricated multilayer MoS<sub>2</sub> transistor at  $V_{DS}$  of 0.1 V (a) in air and (b) in a vacuum at different operating temperatures (T = 300, 310, 320, 330, 340, and 350 K) in both log and linear scales. Transconductance versus  $V_G$  curves (c) in air and (d) in a vacuum at different operating temperatures.

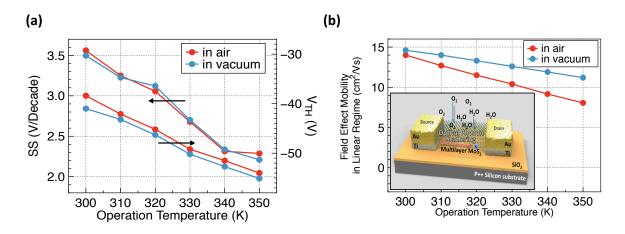

- **Figure 2.7** The operating temperature dependence of the sub-threshold slope (SS), threshold voltage ( $V_{TH}$ ), and field effect mobility in the linear regime ( $\mu_{eff\_lin}$ ) and intrinsic mobility ( $\mu_0$  at  $V_{DS}$  of 0.1 V) (a) in air and (b) in a vacuum at different operating temperatures.

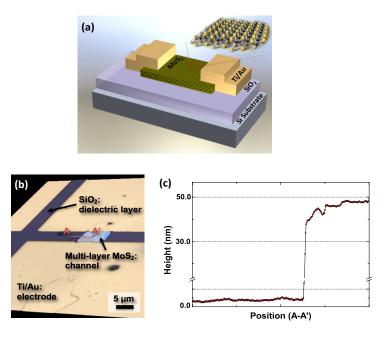

- **Figure 2.8** Structure of the multilayer  $MoS_2$  FET: (a) Cross-sectional schematic of a multilayer  $MoS_2$  FET with a 300-nm-thick  $SiO_2$  gate dielectric. (b) Top-view 3D confocal laser micrograph of a fabricated multilayer  $MoS_2$  transistor ( $L_{ch} = 5 \ \mu m$ ,  $W = 6.9 \ \mu m$ ). (c) AFM height profile of a mechanically exfoliated multilayer  $MoS_2$  flake (shown in (b) as the A'-A region, marked by an arrow).

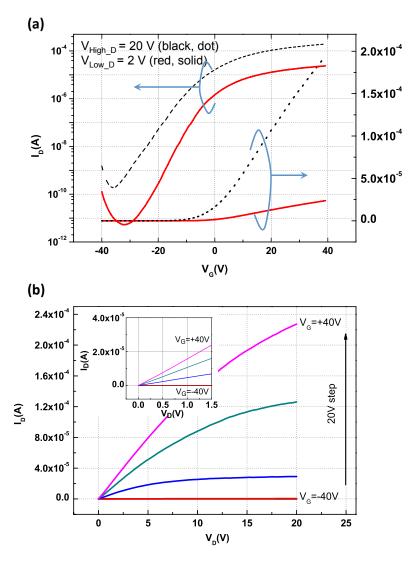

- **Figure 2.9** Representative characteristics of the multilayer MoS<sub>2</sub> FETs for various drain and gate voltages: (a) Transfer characteristics and (b) output characteristics; the inset shows the output characteristics in the linear region.

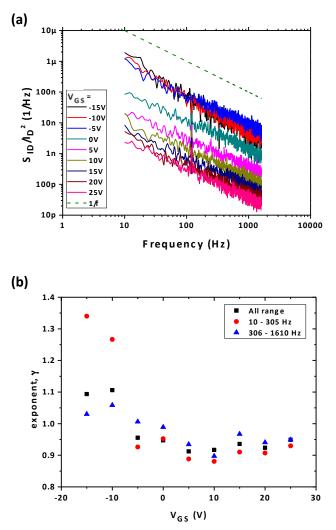

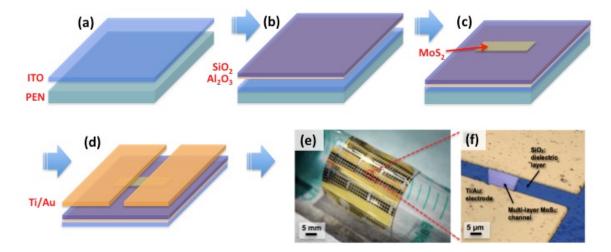

- **Figure 2.10 (a)** Normalized drain-current PSD of multilayer MoS<sub>2</sub> TFTs at various gate biases and a constant drain bias of 2 V, measured from 10 to 1610 Hz in 1 Hz increments. **(b)** Values of the  $\gamma$  exponent from  $1/f^{r}$ , extracted from the PSD results in (a).

- **Figure 2.11 (a)** The  $\alpha_{\rm H}$  as a function of gate bias. (b)  $(g_{\rm m}/I_{\rm D})^2$  and normalized drain-current PSD  $(S_{\rm ID}/I_{\rm D}^2)$  as functions of  $I_{\rm D}$  at various frequencies. (c) The 1/A parameter as a function of gate bias.

<Chapter 3>

- Figure 3.1 (a-d) Schematic fabrication process for bottom-gated multilayer MoS<sub>2</sub> TFTs on flexible PEN substrate. (e) Photograph of flexible multilayer MoS<sub>2</sub> transistors on a plastic substrate showing mechanical flexibility. (f) The 3D confocal laser microscope image of multilayer MoS<sub>2</sub> transistors with ALD Al<sub>2</sub>O<sub>3</sub> / SiO<sub>2</sub> gate dielectric on the flexible PEN substrate.

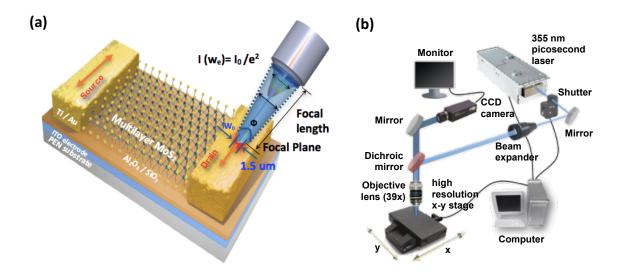

- **Figure 3.2** (a) Gaussian beam intensity distribution and its shape near the focal plane.  $2W_0$  is the beam waist,  $\Phi$  is the beam divergence angle, and 1.5 µm beam diameter based on the  $1/e^2$  intensity. The picosecond laser irradiation with a Gaussian beam profile is focused and scanned along the edge of the source and drain electrodes. (b) The schematic view of the optical setup for picosecond laser annealing.

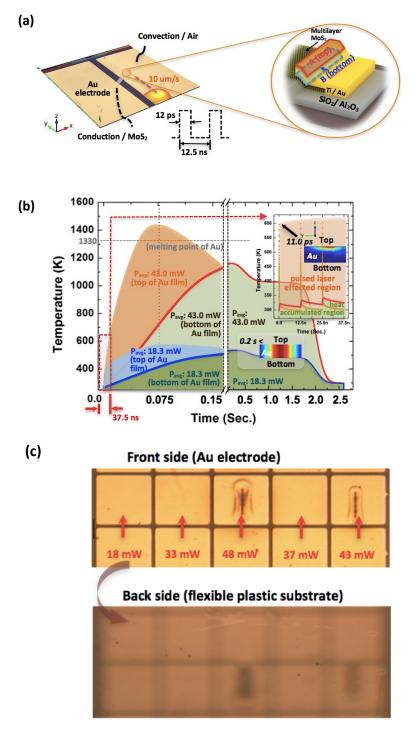

- Figure 3.3 Numerical results calculated by finite-difference methods (FDM) for the temperature distribution under picosecond-pulsed laser source. (a) The spatial temperature distribution along the surface when picosecond pulsed laser is applied onto the Au electrode surface in contact with air and ALD  $Al_2O_3 / SiO_2$  dielectric layer. (b) The temperature of Au electrode versus exposure time at the specific points "A" (the top of Au film) and "B" (the interface of the Au electrode and the MoS<sub>2</sub> channel) in (a) irradiated by the center of the laser beam. The 37.5 ns window (not on scale in the horizontal time axis) is depicted in the insert. (c) The optical images of the front and backside of laser-irradiated Au contacts on a flexible plastic substrate. Au contacts irradiated with laser power > 40 mW show severe damage.

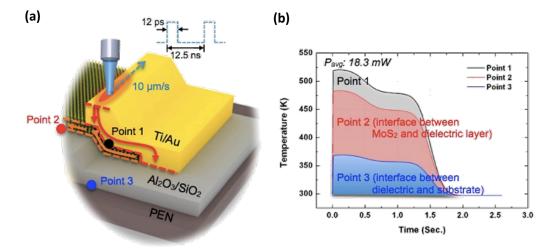

- Figure 3.4 (a) Spatial schematic images of laser irradiated Au contacts at a speed of 10 μm/s on a flexible PEN substrate and three points of interest: point 1 (the interface between the contact and MoS<sub>2</sub>), point 2 (the interface between MoS<sub>2</sub> and the dielectric layer), and point 3 (the interface between the dielectric layer and the substrate). (b) Numerical thermal analysis of temperature distribution versus exposure time at the three specific points when a picosecond pulsed laser was applied and scanned onto the top surface (Au) at ambient conditions.

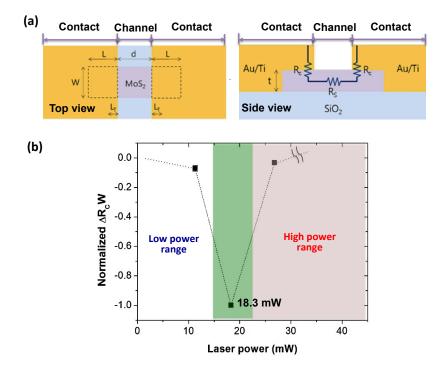

- **Figure 3.5** Effects of laser annealing on the  $R_c$  of multilayer MoS<sub>2</sub> transistors fabricated on Si wafers. (a) Schematic device configuration with an equivalent circuit model. (b) The reduction of  $R_c$  per width after laser annealing normalized with respect to that of 18.8 mW ( $\Delta R_c W = (R_c W)_{After} (R_c W)_{Before}$ ).  $V_{ds} = 1$  V and scan speed = 10 µm s<sup>-1</sup>.

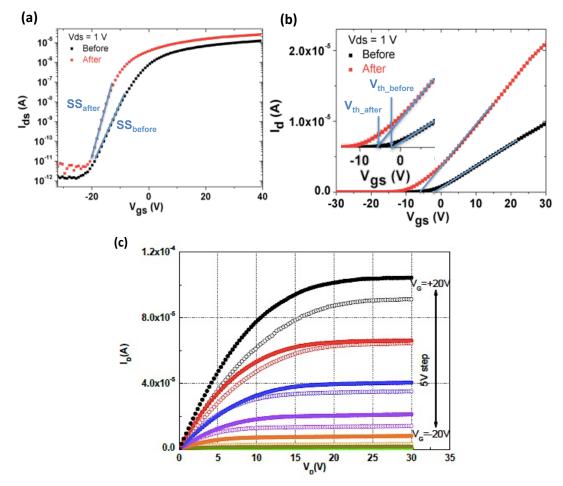

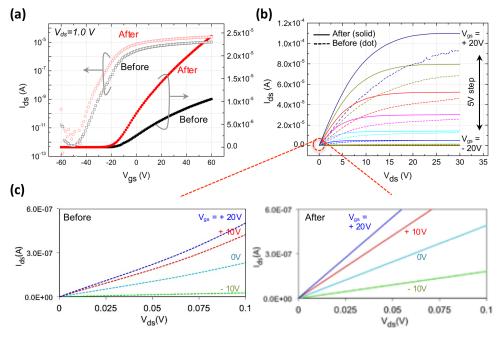

- **Figure 3.6** The enhanced performance of a representative flexible MoS<sub>2</sub> transistor by the selective laser annealing of contacts. (a) The log-scale  $I_D$ -V<sub>G</sub> characteristics for a MoS<sub>2</sub> transistor (L = 7 µm) before and after laser annealing at V<sub>D</sub> = 1 V. (b) the I<sub>D</sub>-V<sub>G</sub> in linear-scale. (c) The I<sub>D</sub>-V<sub>G</sub> characteristics of the MoS<sub>2</sub> transistor before (open circle) and after (solid circle) laser annealing. V<sub>G</sub> ranges from -10 to 15 V in 5 V steps.

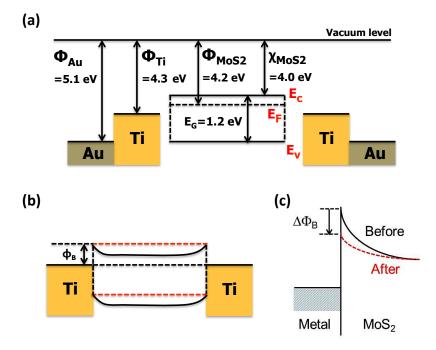

- Figure 3.7 (a) Schematic energy-band diagrams of multilayer  $MoS_2$  transistors with a Schottky barrier at the isolation and (b) at equilibrium. Note that  $\Phi$  is work function of metal;  $\Phi_B$  is Schottky barrier;  $\chi$  is electron affinity. (c) Schematic band diagram of the metal-MoS<sub>2</sub> junction illustrating the reduction of the Schottky barrier width after laser annealing.

- **Figure 3.8** Cross-sectional TEM images showing the mixture layer at the interface after laser annealing.

- Figure 3.9 (a) Cross-sectional schematic structure of multilayer MoS<sub>2</sub> FETs with a 300-nm-thick SiO<sub>2</sub> gate dielectric. Picosecond laser irradiation with a Gaussian beam profile is focused and scanned along the edge of the source and drain electrodes. (b) Topview of the optical microscope image for multilayer MoS<sub>2</sub> FETs after fabricating completely.

- Figure 3.10 (a) Transfer characteristics  $(I_D-V_G)$  for the flexible MoS<sub>2</sub> transistor in log-scale (left) and linear-scale (right) before and after laser annealing at  $V_D = 1$  V. (b) Output characteristics  $(I_D-V_D)$  before (dot) and after (solid) laser process. (c) Magnifications (before and after) for the low  $V_D$  range from 0 to 0.1 V.

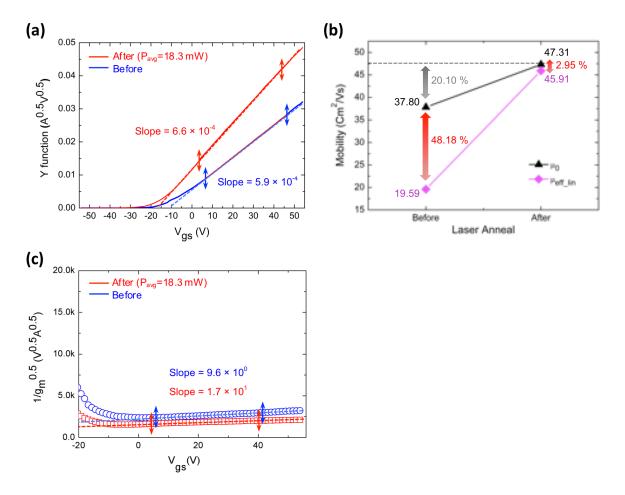

- Figure 3.11 Y-function and evaluation of electrical parameters before and after the laser process. (a) Plots of Y-function with respect to  $V_G$  and the linear fitting in the strong accumulation region for obtaining the slope. (b) Comparison of the  $\mu_0$  and  $\mu_{eff\_lin}$  before and after the laser process. (c) Plots of  $1/g_m^{0.5}$  with respect to the  $V_G$  and their slopes in the straight line fitting for extraction of the mobility attenuation factor ( $\theta$ ).

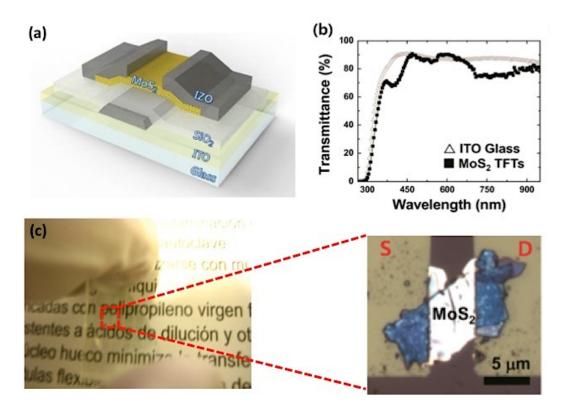

- Figure 3.12 (a) 3D cross-sectional schematic view of the transparent multilayered MoS<sub>2</sub> TFT. The dashed red line indicates atomic arrangements and a layered structure in multilayer MoS<sub>2</sub>. (b) Transmission spectra of the ITO glass (Δ) and the transparent MoS<sub>2</sub> TFTs (**■**) in the visible wavelength range. (c) Optical microscope image of the transparent MoS<sub>2</sub> TFTs on the printed texts and magnified optical microscope image of a single TFT consisting of a MoS<sub>2</sub> flake between the IZO source and drain electrodes.

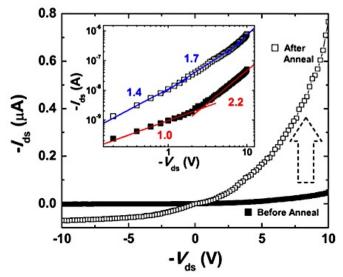

- **Figure 3.13** Comparison of the  $I_D-V_D$  characteristic curves of transparent MoS<sub>2</sub> TFT at  $V_G = 0$ V before (**■**) and after ( $\Box$ ) laser annealing. Inset:  $I_D-V_D$  characteristic curves of transparent MoS<sub>2</sub> TFT ( $V_G = 0$  V) using the logarithmic scale.

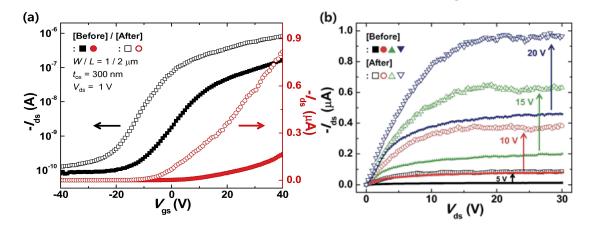

- **Figure 3.14 (a)** Transfer characteristic  $(V_G-I_D)$  of the transparent MoS<sub>2</sub> TFT as  $V_D = 1$  V before (solid) and after (open symbols) laser annealing. The L and W were equal to 2 and 1  $\mu$ m, respectively. (b) Output characteristic  $(V_D-I_D)$  curves of the transparent MoS<sub>2</sub> TFT with different gate biases ( $V_G = 5$ , 10, 15, and 20 V) before (solid) and after (open symbols) laser annealing.

### <Chapter 4>

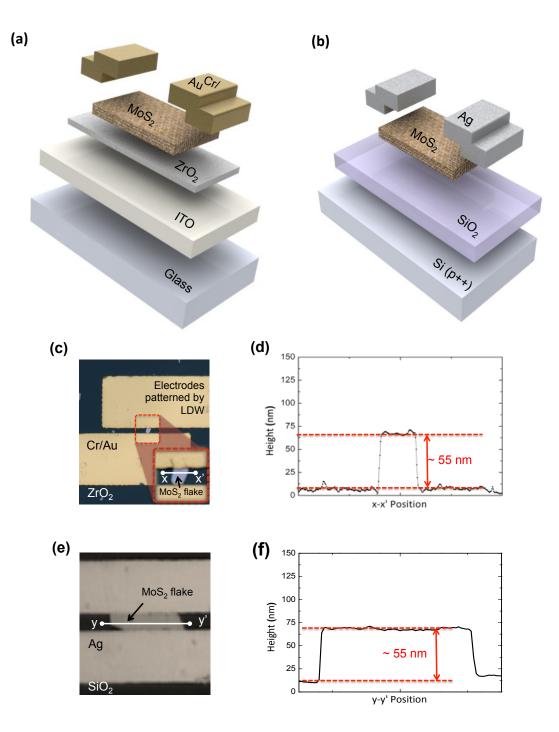

- **Figure 4.1** Multilayered MoS<sub>2</sub> FETs structures. The cross-sectional schematic structure of fabricated multilayered MoS<sub>2</sub> FETs (a) with solution based sol-gel high-k ZrO<sub>2</sub> gate dielectric on the ITO electrode and (b) with a 300 nm thick SiO<sub>2</sub> gate dielectric on the silicon substrate. (c) The top-view of the confocal laser microscope image for fabricated MoS<sub>2</sub> FETs with the sol-gel ZrO<sub>2</sub> and Cr/Au electrodes drawn by LDW. Note that a channel width and length are 2  $\mu$ m and 2  $\mu$ m, respectively. (d) Surface profile for x-x' position of MoS<sub>2</sub> channel on the sol-gel ZrO<sub>2</sub> with the thickness of ~ 55 nm measured by AFM. (e) The top-view of the optical microscope image for fabricated MoS<sub>2</sub> FETs with SiO<sub>2</sub> and Ag electrodes drawn by LDW. Note that the reference device has a channel length of 2  $\mu$ m and a width of 7  $\mu$ m. (f) 2D AFM topography of MoS<sub>2</sub> flake placed on SiO<sub>2</sub> with ~ 55 nm thick.

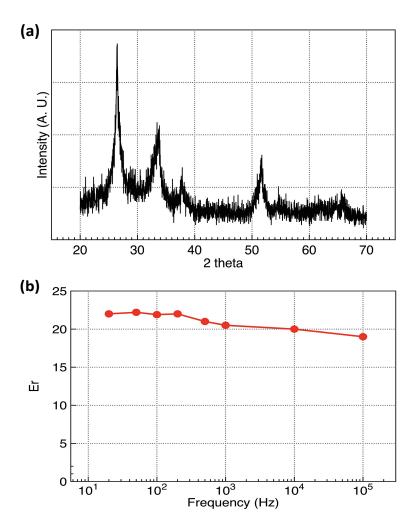

- Figure 4.2 The XRD spectra of the sol gel processed ZrO<sub>2</sub> layer, processed at 500°C for 1 hour in O<sub>2</sub>. (b) The dielectric constant of sol gel processed ZrO<sub>2</sub>, corresponding to frequency.

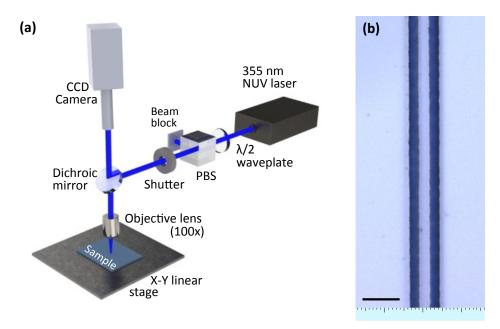

- **Figure 4.3** LDW lithography system. (a) Schematic diagram of the experimental optical setup for LDW process. (b) The top-view of a confocal laser microscope image of line patterns of positive photoresist (i-line) through moving the linear stage with the speed of 20  $\mu$ m/s after the process of LDW and development. The patterned line width is 2.2  $\mu$ m and scale bar is 10  $\mu$ m.

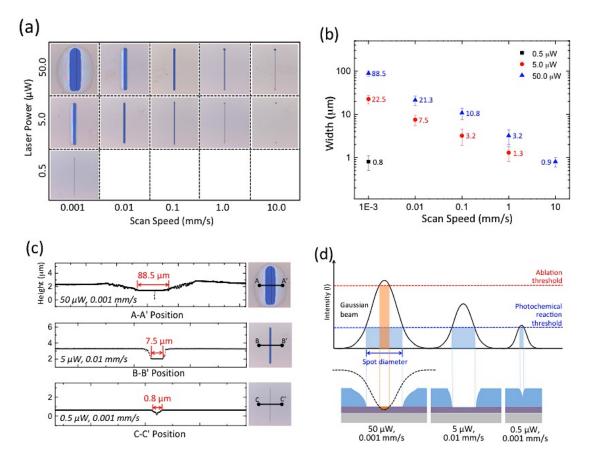

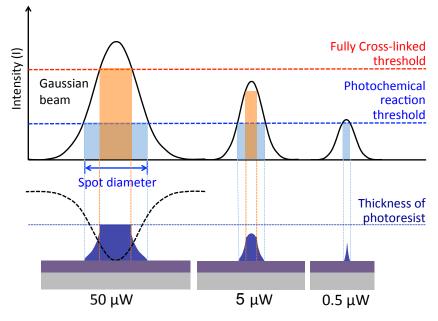

- Figure 4.4 Various LDW lithography behaviors. (a) Comparison of the positively patterned geometry for different laser power and scan speed on the Si/SiO<sub>2</sub> substrate and (b) their quantitative measurements of the line width with the linear trend. (c) Cross sectional profiles of the representative three patterns (d) with different intensities of the laser: superfluous, moderate, and insufficient exposure conditions.

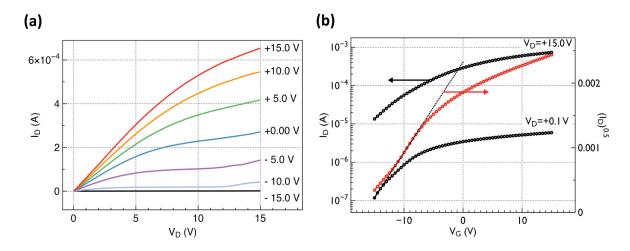

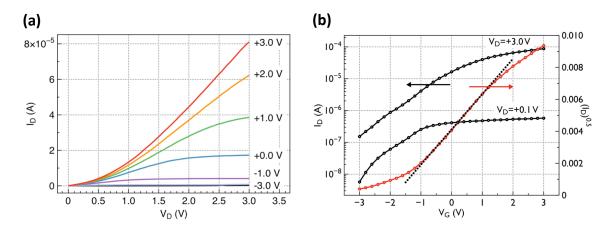

- **Figure 4.5** The representative electrical characteristics of fabricated MoS<sub>2</sub> TFT on SiO<sub>2</sub> at room temperature: (a) the plot of  $I_D$ -V<sub>D</sub>; and (b) plots of  $I_D$ -V<sub>G</sub> (left axis) and  $I_D^{0.5}$ -V<sub>G</sub> (right axis) at V<sub>D</sub> = +15.0 V and +0.1 V, respectively.

- **Figure 4.6** The representative electrical characteristics of fabricated MoS<sub>2</sub> TFT on sol-gel processed ZrO<sub>2</sub> at room temperature: (a) the plot of  $I_D$ -V<sub>D</sub>; and (b) plots of  $I_D$ -V<sub>G</sub> (left axis) and  $I_D^{0.5}$ -V<sub>G</sub> (right axis) at V<sub>D</sub> = +3.0 V and +0.1 V, respectively.

### <Chapter 5>

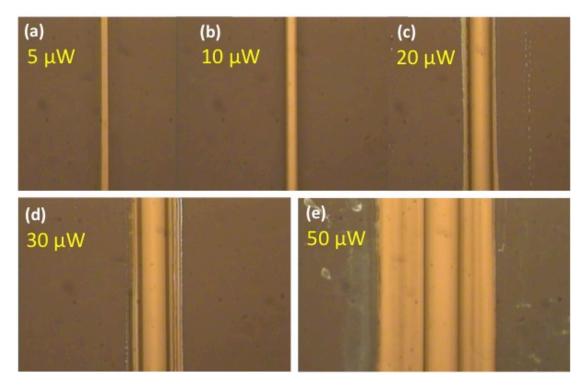

- Figure 5.1 Optical microscope images of SU-8 photoresist after the LDW lithography and development. Different laser powers ((a) 5.0, (b) 10.0, (c) 20.0, (d) 30.0, and (e) 50.0  $\mu$ W) are irradiated with 0.005 mm/s of the fixed scan speed, 355 nm of wavelength through 20 X of objective lens.

- **Figure 5.2** LDW lithography behaviors for the negative photoresist, SU-8. The representative three different cases with respect to the intensities of the laser: superfluous, moderate, and insufficient exposure conditions.

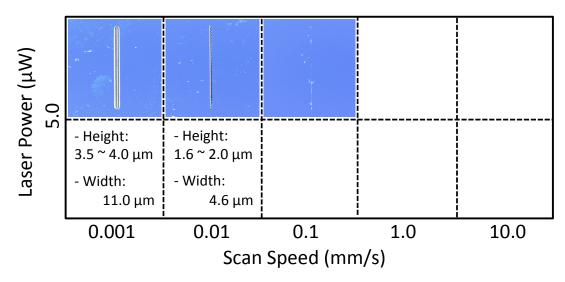

- **Figure 5.3** Comparison of the negatively patterned geometry for the different scan speed (fixed laser power:  $5.0 \mu$ W) on the Si/SiO<sub>2</sub> substrate. Note that spin-coated (at 5000 rpm) photoresist is SU-8 2005 with 4.0 µm of the thickness.

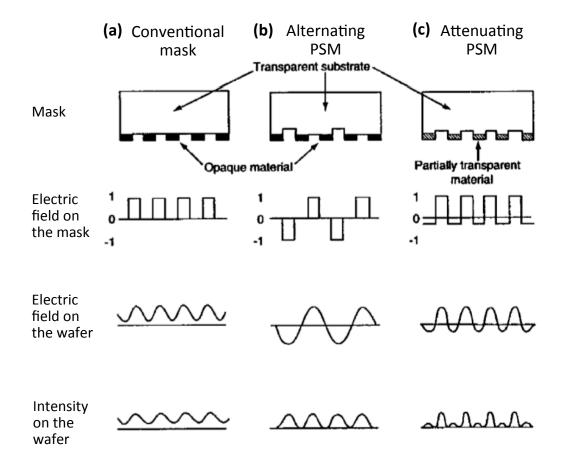

- Figure 5.4 Comparison of various types of PSMs: (a) conventional, (b) alternating, and (c) attenuating PSMs. (image from C. Pierrat *et al.* Appl. Opt. 1995)

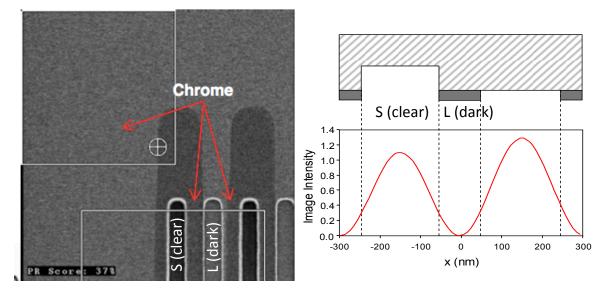

- **Figure 5.5** Top-View of SEM image for AltPSM with 350 nm of the width (for clear area, S) and 300 nm of the width (for dark area, L). Note that schematic cross-sectional image (right) is not a real scale; it is the example for understanding easily.

- **Figure 5.6** Optical photo image of diffracted beams with several orders after the light incidents at normal angle and passes through the AltPSM.

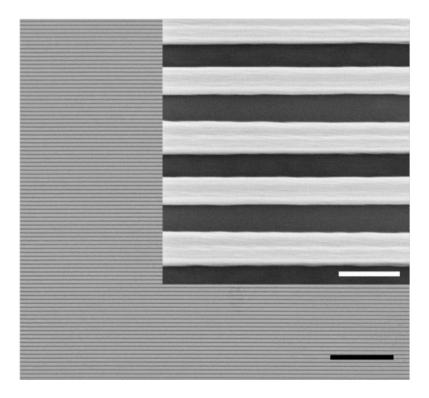

- **Figure 5.7** SEM images of the line-space patterns created by interference lithography using AltPSM. Note that the scale bars are 20 µm and 500 nm (inset).

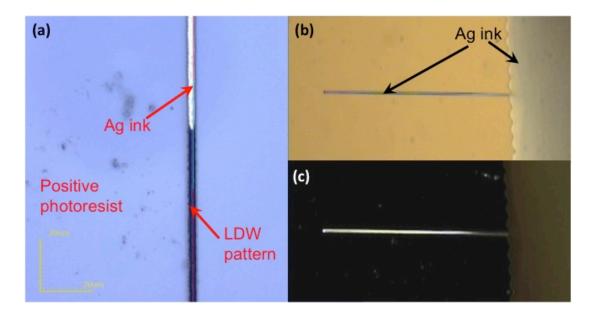

- Figure 5.8 (a) The top-view of a confocal laser microscope image of line patterns of positive photoresist and partially filled Ag ink after the process of LDW and ink-jet printing of Ag ink. (b) Optical microscope image of completely filled Ag ink under the bright field (BF) and (c) the dark field (DF).

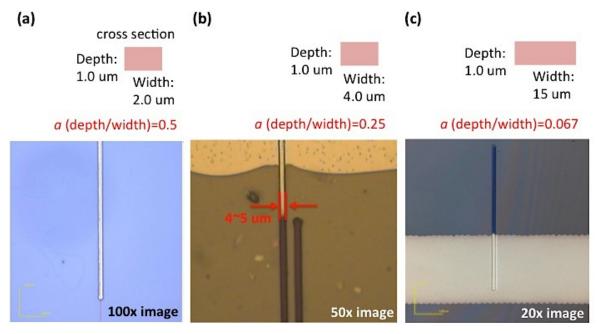

- **Figure 5.9** The top-view images of line patterns with varying width of the channel using positive photoresist and filled Ag ink after the process of LDW and ink-jet printing. The thicknesses of spin-coated photoresist are the same ( $\sim 1.0 \ \mu\text{m}$ ), however, the widths are different: (a) 2.0  $\mu\text{m}$ , (a = 0.5), (b) 4.0  $\mu\text{m}$ , (a = 0.25), (c) 15.0  $\mu\text{m}$ , (a = 0.067).

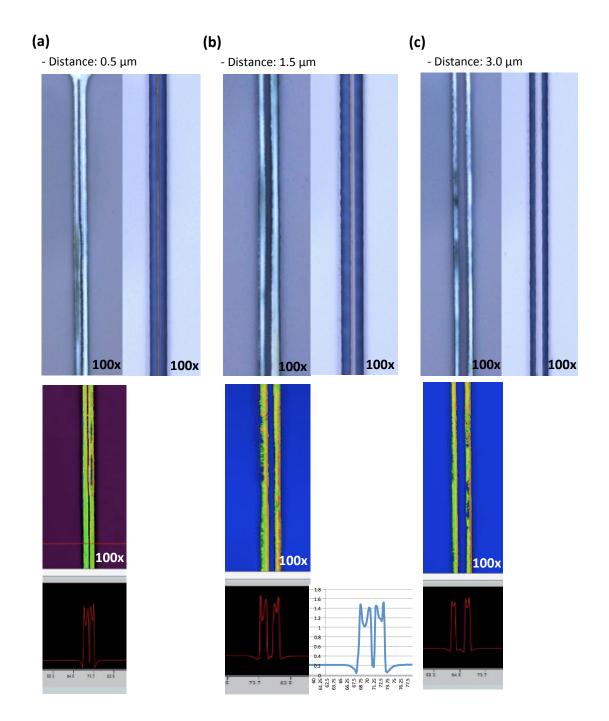

- Figure 5.10 The top-view images and cross-sectional profile measured by 3D confocal laser microscope for filled line patterns (various distances of the channel: (a) 0.5  $\mu$ m, (b) 1.5  $\mu$ m, (c) 3.0  $\mu$ m) with Ag ink after the process of LDW and ink-jet printing. Note that the thicknesses of spin-coated photoresist are ~ 1.0  $\mu$ m.

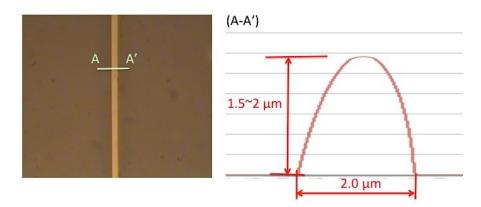

- Figure 5.11 The top-view images and cross-sectional profile measured by 3D confocal laser microscope for the negatively patterned wall.

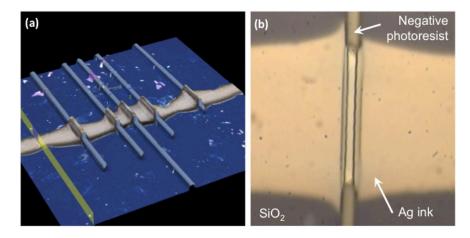

- Figure 5.12 (a) 3D confocal laser microscope image and (b) magnified top-view image for the negatively patterned wall and printed Ag ink over the walls after the process of LDW and ink-jet printing of Ag ink.

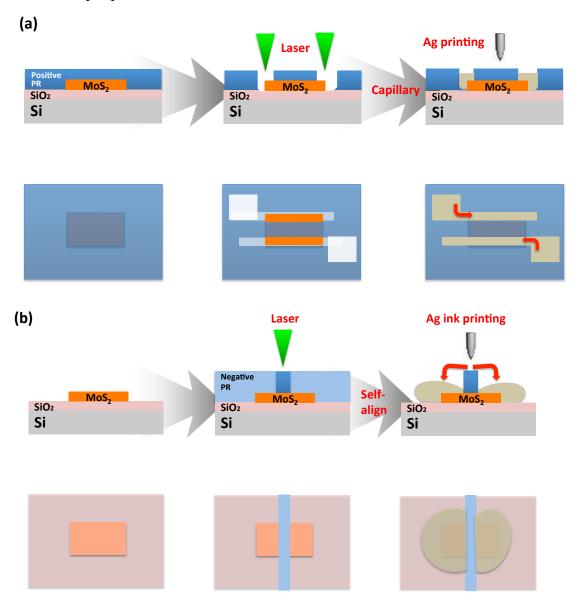

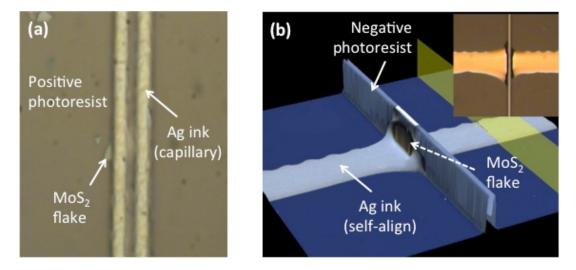

- Figure 5.13 Schematic fabrication process for MoS<sub>2</sub> TFTs (a) using the positive photoresist and capillary and (b) using the negative photoresist and self-alignment with ink-jet printed Ag ink.

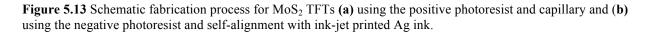

- **Figure 5.14** The optical images of fabricated  $MoS_2$  TFTs (a) using the positive photoresist and capillary (Note that the representative device has a channel length of 2 µm and a width of 4 µm) and (b) using the negative photoresist and self-alignment with inkjet printed Ag ink (Note that a channel length and a width are 2 µm and a width of 2 µm).

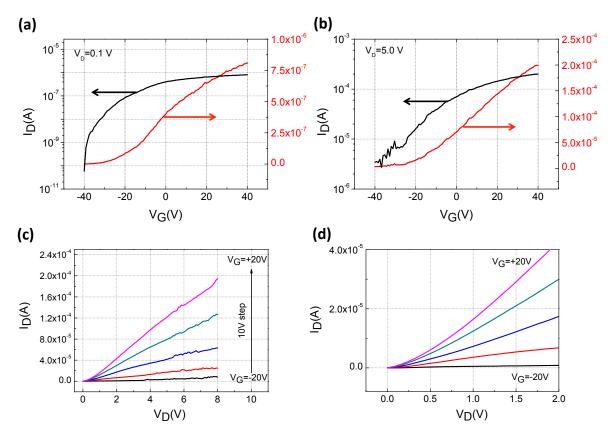

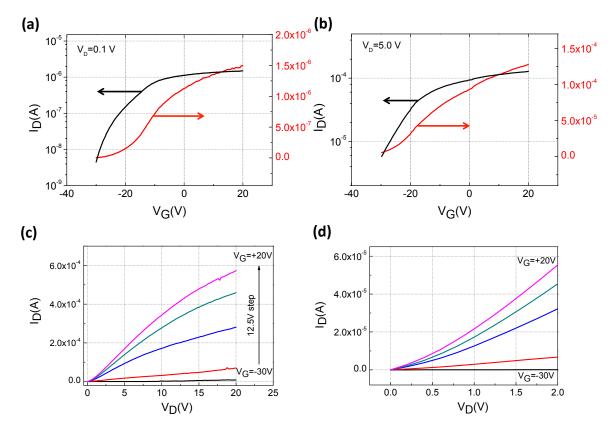

- Figure 5.15 Device performance of MoS<sub>2</sub> TFTs with the Ag electrodes formed by capillary and positively patterned channels. (a) Transfer characteristics  $(I_D-V_G)$  for the representative MoS<sub>2</sub> transistor in log-scale (left) and linear-scale (right) at  $V_D = 0.1$  V and (b) at  $V_D = 5.0$  V. (c) Output characteristics  $(I_D-V_D)$  in the range of  $V_D$  from 0 V to 8 V with 10 V step of  $V_G$  (from -20 V to 20 V). (d) Magnifications for the low  $V_D$  range from 0 to 2.0 V.

- Figure 5.16 Device performance of  $MoS_2$  TFTs with the Ag electrodes formed by selfalignment and negatively patterned walls. (a) Transfer characteristics (I<sub>D</sub>-V<sub>G</sub>) for the representative  $MoS_2$  transistor in log-scale (left) and linear-scale (right) at  $V_D =$ 0.1 V and (b) at  $V_D = 5.0$  V. (c) Output characteristics (I<sub>D</sub>-V<sub>D</sub>) in the range of  $V_D$ from 0 V to 20 V with 12.5 V step of  $V_G$  (from -30 V to 20 V). (d) Magnifications for the low  $V_D$  range from 0 to 2.0 V.

### <Chapter 6>

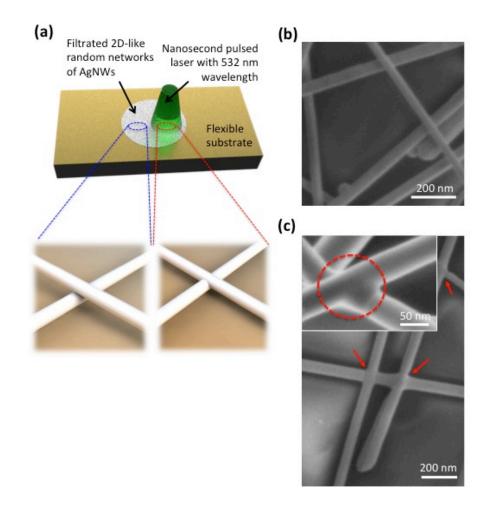

- Figure 6.1 (a) The schematic concept of laser welding process for metal AgNW network on the PI substrate formed by filtration method. (b) SEM image of as-prepared AgNW random networks before the laser welding process and (c) after the laser treatment (red arrows indicate the laser welded junctions). Note that at magnified image (inset), laser welded part is observed in evidence.

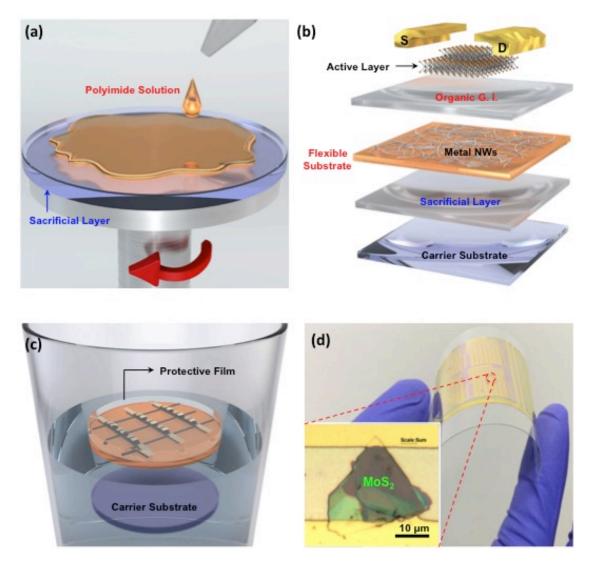

- Figure 6.2 Flexible multilayer MoS<sub>2</sub> TFTs. (a) Schematic illustration of fabricating flexible substrate from PI solution. (b) Flow chart of the fabrication procedure including sacrificial layer, flexible substrate, and organic gate insulator. (c) Schematic illustration of detaching flexible TFTs from carrier substrate. (d) Photograph of bent flexible MoS<sub>2</sub> TFTs array. PET protective film was laminated under the PI flexible substrate. (Inset) Optical microscope image of multilayer MoS<sub>2</sub> active channel in single TFT.

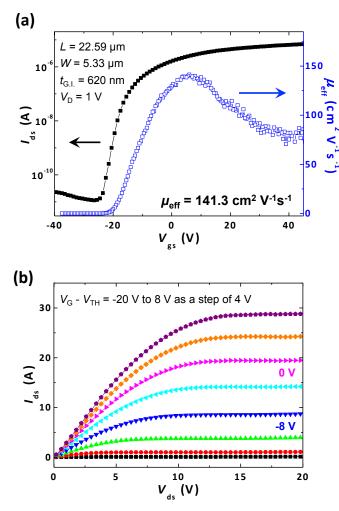

- **Figure 6.3** Electrical properties of flexible MoS<sub>2</sub> TFT at initial flat condition. (a)  $I_D-V_G$  curve and  $\mu_{eff}$  of the flexible MoS<sub>2</sub> TFT at  $V_D = 1$  V. (b)  $I_D-V_D$  curve of the same TFT under different gate biases ( $V_G V_{TH} = -20$  V to 10 V as a step of 4 V).

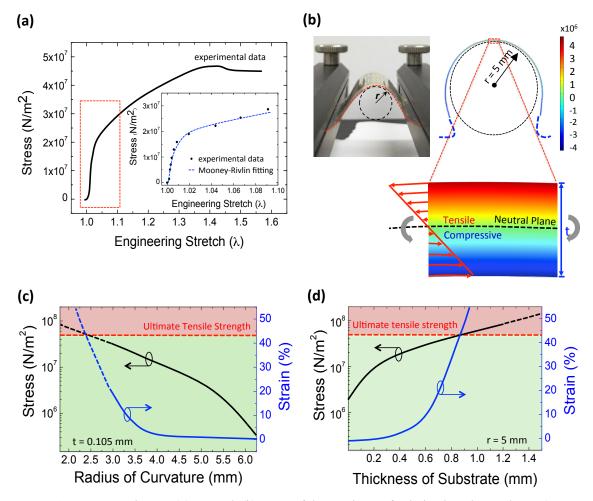

- **Figure 6.4** (a) Measured stress ( $\sigma$ ) stretch ( $\lambda$ ) curve of the specimen of solution based PI and PET (t= 0.105 mm) and (inset) fitting Mooney-Rivlin model with experimental data. (b) The numerical result on hyperelastic nonlinear stress analysis based on the parameters extracted by the real experimental data when the bending radius was 5 mm. (c) Through fitted Mooney-Rivlin model, expected mechanically stable range (green region) of the structure with resect to the radius of curvature of the substrate and (d) to thickness of the substrate.

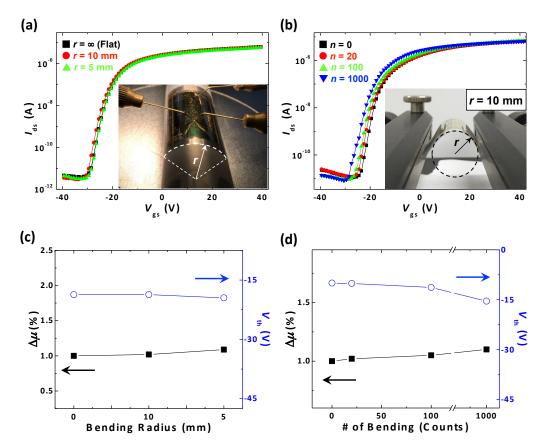

- **Figure 6.5** Variation of TFT performances of the flexible MoS<sub>2</sub> TFTs under various mechanical stresses. (a) Comparison of the transfer characteristics of the flexible MoS<sub>2</sub> TFTs under static bending environments with three different bending radii (flat, r = 10 mm, and 5 mm). (Inset) Photograph of the bent MoS<sub>2</sub> TFTs attached on rigid cylinder with pre-defined radius, which was depicted as white dashed arc and arrow. (b) Comparison of the transfer characteristics of the flexible MoS<sub>2</sub> TFTs under cyclic bending environments with respect to number of bending (n = 0, 20, 100, and 1000). (Inset) Photograph of the flexible MoS<sub>2</sub> TFTs loaded on multimodal bending tester. Bending radius (r = 10 mm) was depicted as black dashed circle and arrow. Variations of  $\mu_{eff}$  and  $V_{TH}$  of the flexible MoS<sub>2</sub> TFTs as a function of (c) static bending radii and (d) number of cyclic bending.

# **LIST OF TABLES**

**Table 1.1**Representative candidates of flexible substrates for flexible applications: metal foil,<br/>glass, PET, PEN, PC, PES, and PI. (values in this table are taken from the<br/>reference)

# Chapter 1 Introduction

# **1.1 Flexible Electronics**

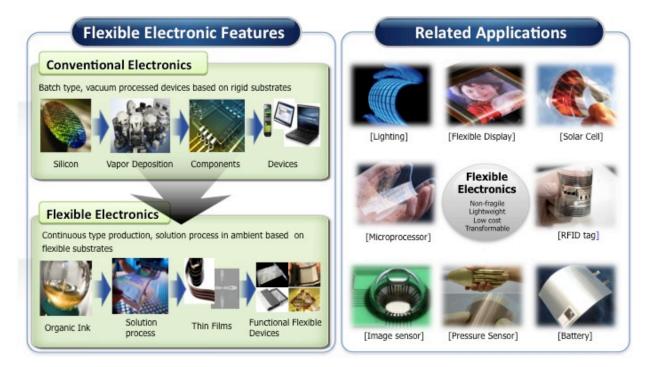

Flexible has various meanings and many qualities: bendable, wearable, elastic, lightweight, rollable, non-fragile, low cost, and others. In this aspect, we can define that flexible electronics encompasses electronic devices with mutifunctional (e.g. electrical, sensing, photonic, etc.) features using flexible materials (e.g. soft, light, rugged). Nowadays, the boundary of flexible/wearable electronics is wide-open and the field has rapidly developed and moved with pioneering applications for light-weight, portable, and comformable producs such as flexible OLED displays,<sup>[1]</sup> solar cells and batteries,<sup>[2]</sup> wearable health patches for personal health-monitoring/therapeutics,<sup>[3]</sup> and implantable medical devices<sup>[4]</sup> as shown in **Figure 1.1**.

Figure 1.1 New paradigm and platform of flexible/wearable electronics and their various applications including flexible displays, human-inspired electronics, sensors, and energy/power devices. (images from Google search)

In order to produce aforementioned functional applications, an important segment of flexible/wearable electronics is widely connected with thin-film transistor (TFT) platform. Furthermore, among the various applications based on TFT platform, flexible displays are aggressively developing field of research.

# **1.2 Trends of Flexible Displays**

Science fiction (SF) movies and fantasy novels have inspired flexible displays for many years. For example, in the Harry Potter movies, flexible display, daily prophet, appears to be a wizard's fantasy aiming at reading video newspaper. Also, we usually imagine the roll-up display inside a pen or a phone as a future flexible display. In addition, there are a plethora of candidate applications for the next generation displays. Nowadays, the size of the display is getting larger and larger. Therefore, we easily expect the wall can be a display. Moreover, Google already commercially released wearable goggle display named Google glass. Also, display can deliver two-way communication through mirror display or can obtain some information while looking over the transparent display.

However, just a few decades ago when we used bulkly and heavy cathod ray tube (CRT) display (early 1900s), these flexible displays were a dream and imagination in our mind. After that (mid 1900s), invented TFTs shifted the paradigm of the display; flat panel display (FPD) with unparalled featrues (e.g. very thin, lightweight, low-power consumption) created a great sensation. Then, now, many companies and researchers have tried to make a future display platform and to change a picture of our life which does not exist today (see **Figure 1.2**).

Figure 1.2 Big evolution of display platform and paradigm away from CRT to FPD and to the odd-shaped future flexible display. (images from Google search)

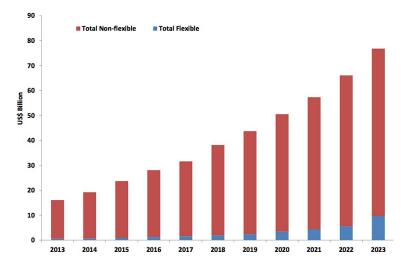

IDTechEx, a knowledge-based consultancy company, offered a more positive forecast for the flexible electronics and displays. **Figure 1.3** shows the market value of flexible electronics versus non-flexible electronics.<sup>[5]</sup> According to the report, \$1 billion (US) of the electronics (7%) was conformal or flexible in 2015 (93% of non-flexible).<sup>[5]</sup>

**Figure 1.3** Total market value of flexible/conformal electronics versus non-flexible/rigid electronics 2013-2023. (from IDTechEx forecast report)<sup>[5]</sup>

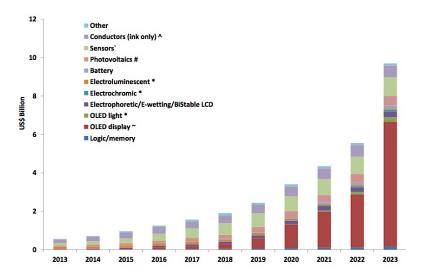

In 2023, however, the market value of conformal/flexible will raise to \$10 billion of the total value (15%, 85% of non-flexible).<sup>[5]</sup> Moreover, through the following graph (**Figure 1.4**), we can expect that flexible display based on the organic light-emitting-diode (OLED) panel will be \$ 6.5 billion (70 %) of the market value and be placed the first among other flexible applications in 2023; the difference will be more evident (the  $2^{nd}$  place: 9% of sensors).<sup>[5]</sup>

Figure 1.4 Total market value of only flexible/conformal electronics 2013-2023. (from IDTechEx forecast report)<sup>[5]</sup>

Note that the OLEDs, a special class of LEDs, is manufactured by placing a series of thin layers of organic compounds between two conductors and is primarily based on the principle of electro-phosphorescence, where certain organic molecules are observed to emit light upon application of electric voltage. The OLED is key to many 'Flexible Electronics' applications as it offers many advantages. First of all, it can realize any shape, providing versatility in terms of design. In addition, its structure does not present any cell gap, so that it can achieve the wide viewing angle. The aspect of manufacturing, the OLED process is in good compatibility with flexible substrate which means that it has wide variety of manufacturing options such as roll-to-roll process and printing method.

### **1.3 Key Component for Displays**

For operating displays, numerous components and technologies should be required and supported; displays are a complex system of linked many components. Furthermore, as today the consumers are becoming increasingly specific in their demands such as large size, high resolution, high operating speed, generating vivid colors, low price, and low power consumption, the displays are getting complex and specialized.

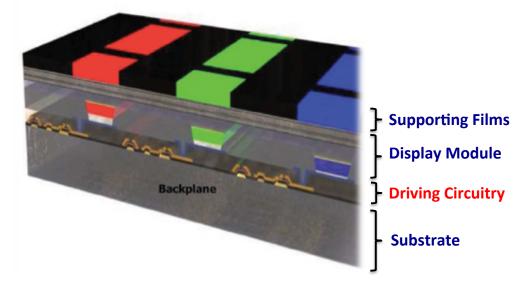

Even though the display panels come in various formats (e.g. liquid crystal display (LCD), plasma display panel (PDP), OLED) depending on their intended applications, they can be simply divided into four main parts to function efficiently as illustrated in **Figure 1.5**: (1) a substrate, (2) driving circuit, (3) display module, and (4) supporting films. A detailed explanation will be given in the following section.

**Figure 1.5** Schematic cross-sectional display structure briefly separated by four parts: (1) substrate, (2) driving circuitry, (3) display module, and (4) supporting films. (image from S. Kim and H.–J. Kwon *et al.* Adv. Mat. 2011)<sup>[1]</sup>

### 1.3.1 Flexible substrates

The substrate is the starting component for all displays and other components. In an architectural analogy, it is like the land where a house is built. Therefore, it is very important to select the suitable flexible substrates for making the devices in the beginning. Also, depending on which substrates choose to use, it can make the limitations of process temperature and the challenges in terms of compatibility with the other components that need to be integrated onto them.

**Table 1.1** summarizes the properties of the general candidates of flexible substrates for flexible applications.<sup>[6]</sup> The values of the properties come from the commercially available products: polyethylene terephthalate (PET) – Melenix® from DuPont Teijin Films, polyethylene naphthalate (PEN) – Teonex® Q65 from DuPont Teijin Films, poly carbonate (PC) – Lexan® from GE, polyethersulfone (PES) – Sumilite® from Sumitomo Bakellite, and polyimide (PI) – Kapton® from DuPont).

Based on these various candidates of the substrates, PEN substrates are being widely used for the flexible TFT backplanes and OLED display because of the properties, availability, long-term potential, and reasonable cost.<sup>[7-9]</sup> Although, metal foil has relatively high thermal stability, roughness and electrical isolation are issues. Glass with high transmittance and thermal stability could be a good candidate, however, it has weak flexibility. Note that Corning company now releases flexible Willow® glass, still in progress. Also, PET is very cheap material compared to PI, however, low thermal resistance is a hurdle as the substrate.

|                                                   | Metal Foil<br>(Stainless<br>Steel) | Glass | Polyethylene<br>terephthalate<br>(PET) | Polyethylene<br>naphthalate<br>(PEN) | Poly<br>carbonate<br>(PC) | Poly<br>ethersulfone<br>(PES) | Polyimide<br>(Pl) |

|---------------------------------------------------|------------------------------------|-------|----------------------------------------|--------------------------------------|---------------------------|-------------------------------|-------------------|

| Transmission<br>(400-700 nm)<br>(%)               | 0                                  | 92    | 89                                     | 87                                   | 90                        | 90                            | < 70<br>(Yellow)  |

| CTE<br>(-55 to 85 °C)<br>(ppm/°C)                 | 10                                 | 5     | ~ 15                                   | ~ 13                                 | 60 ~ 70                   | ~ 54                          | 30 ~ 60           |

| T <sub>g</sub><br>(°C)                            | ~ 1000                             | ~ 600 | ~ 78                                   | ~ 120                                | ~ 150                     | ~ 220                         | ~ 410             |

| Permeability<br>for oxygen<br>and moisture<br>(%) | 0                                  | ~ 0   | 0.14                                   | 0.14                                 | 0.4                       | 1.4                           | 1.8               |

| Young's<br>modulus<br>(Gpa)                       | ~ 200                              | ~ 70  | ~ 5.3                                  | ~ 6.1                                | ~ 1.7                     | ~ 2.2                         | ~ 2.5             |

**Table 1.1** Representative candidates of flexible substrates for flexible applications: metal foil, glass, PET, PEN, PC, PES, and PI. (values in this table are taken from the reference<sup>[6]</sup>)

### 1.3.2 Driving circuitry: TFTs

For switching and controlling the current like mechanical faucet, the driving circuitry, especially for TFTs, is as important as the aforementioned substrate. As described in **Figure 1.6**, TFT has three electrodes (gate, source, and drain) and two types (*n*-type and *p*-type). For the operating case of *n*-type, a positive gate voltage ( $V_{GS} > V_{TH}$ , threshold voltage) induces the accumulation of electrons near the dielectric–semiconductor interface, which flows from source to drain via a semiconducting channel material under a positive drain bias ( $V_{DS} > 0$ ) and vice versa (for *p*-type). During the current flow, moving electrons, the gate plays an important function of either blocking or admitting electrons. The design of the TFTs is the most critical factor in determining the quality for attaining high performance of the displays.

**Figure 1.6** Schematic cross-sectional TFT structure with three electrodes: gate, source, and drain. (image from S. Kim and H.–J. Kwon *et al.* Adv. Mat. 2011)<sup>[1]</sup>

To this day, we are widely using TFTs based on amorphous silicon (a-Si) with low temperature process (<200°C, conventional process: ~300°C) as a channel material for switching devices such as LCD, imagers, and sensors due to the economic cost.<sup>[10,11]</sup> However, the technology and trend are moving toward the large-area, transparent, multifunctional and flexible type of displays since OLED panel switched by low-temperature poly-silicon (LTPS) TFTs (process temperature: ~450°C) has been commercialized as shown in **Figure 1.7(a)**. Because poly-silicon has very high mobility compared to a-Si, it is suitable for high current driving device like active matrix OLED display.<sup>[12-14]</sup> However, the cost is high and fabrication process is quite complex and requires high temperature. Even though the two materials (a-Si, poly-Si) have these issues, they are being considered for flexible display applications because of the well-established knowledge and technologies. On top of that, many scientists and researchers have endeavored to find alternate and more compatible materials for the next generation of channel designs. Therefore, new TFT technologies with other materials (e.g. oxide, organic, carbon nanotube (CNT), nanowire (NW), graphene, etc.) are emerging for the flexible displays.

**Figure 1.7 (a)** Trends of technology of commercialized display panels. Currently, the promise of OLED technology has been to deliver displays that are more visually compelling and power efficient. Furthermore, the resolution and size of displays keeps going up caused by customers' needs. (b) TFT technologies and candidates of channel materials by the mobility and process temperature for the next generation flexible displays. (graph from plastic logic company and images from Google search)

Nowadays, oxide TFTs are on the verge of mass production due to their high mobility and low cost. Also, oxide materials such as  $ZnO_{2}^{[15]} In_{2}O_{3}^{[16]}$  and  $SnO_{2}^{[17]}$  have a widebandgap which allow to make transparent displays. Through In-Ga-Zn-O (IGZO), compound oxide material, the first flexible transparent TFT on PET was made in 2004.<sup>[18]</sup> However, the electron mobility of the material is still low (~ 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and weak optical reliability is an issue. Organic TFT (OTFT) is also attracting attention for flexible display because organic materials are soluble and low temperature process (~ room temperature). However, because hole mobility is higher than the electron mobility (i.e. OTFTs are *p*-type transistors) in most organic materials. Note that the mass of hole is larger than the mass of electron; electron mobility is usually faster than hole mobility. Therefore, the performance of OTFTs was not impressive before the introduction of new organic materials and improved fabrication.<sup>[19-22]</sup> However, still there is much to be resolved such as stability for humidity. **Figure 1.7(b)** summarizes these technologies and materials for TFTs by their mobilities and process temperatures with key issues.

Aside from this, carbon nanotube, nanowire, and graphene are investigated in spite of the many capabilities of the TFTs based on a-Si, LTPS, organic semiconductors, and oxide semiconductors. For 20 years, nano-electronics have been widely studied for switching devices and optoelectronics. Especially, one-dimension (1D) carbon nanotubes<sup>[23-25]</sup> and nanowires<sup>[26]</sup> are attractive for thin-film transistor with high mobility. But there are limitations for integrated circuit. One reason is the deviation of device because of the distribution of diameter and chirality in growth. Another reason is the difficulty of aligning in a specific area. For these reasons, in order to overcome these limitations, nano-researchers turn their gaze on 2D graphene because 2D film is easily patterned and aligned with uniform characteristics.<sup>[27]</sup> After all, 2D graphene opens the door to 2D layer electronics, but has zero-bandgap, it is hard to apply to switching device. In the following, the recent potential candidates with ultra-thin and high mobility will be discussed for flexible and transparent display.

### 1.3.3 Display module

Display module has a special role in image delivery to the human eye by controlling the light. Today, three main display modules are considered in use: LCD, OLED, and electrophoretic display (EPD). LC has a rod-like molecular structure. Aligned LC molecules modulate the transmission of the light by modifying the angle between the direction of the incident light and LC molecules. Note that TFTs allow switching the orientation of the molecules. And OLED is the self-emissive electroluminescent module depending on an applied electric current of TFTs. Therefore, OLED module does not need backlight source and color filters and the nature of organic is suitable for the flexible display. Lastly, EPD is a reflective bistable module like paper. Because of using ambient light, the module is very comfortable to read, even in direct sunlight with low-power consumption. However, it is hard to support images in motion because the response time is still very low (~100 ms) and the reproducibility of desired colors is not good.

### 1.3.4 Supporting films

Depending on the types of modules, required supporting films are varied due to their features. In the case of LCD, color filters are necessary because the module cannot generate colors. Because OLEDs have the most sensitivity to moisture and oxygen, they should need barrier layer in order to protect the display panel and degradation. Touch, protecting, polarizing, brightness enhanced films are sometimes integrated onto the panel to improve functions.

# **1.4 Laser Processing for Flexible Displays**

Laser processing has been developed steadily and is widely applied in various parts of flexible display now because of its irreplaceable advantages.

Typically used flexible materials, e.g. PEN, PET, and PI, as substrates pose significant manufacturing challenges, since their fabrication sequence must have a low thermal budget (< 200 °C). Therefore, conventional high temperature thermal processes cannot be applied as they affect the entire panel, including unwanted areas where the process should be excluded. **Figure 1.8** shows comparison of the spatial temperature distributions for thermal process and between pulsed and continuous wave (CW) laser source. As is evident in the Figure, the heat-affected zone (HAZ) expands in all directions through heat conduction. However, the HAZ extent is different, depending on whether the laser source is pulsed or CW laser. Consequently, the pulsed laser momentarily induces high temperature, imparting a smaller HAZ. Furthermore, high repetition rate of the irradiated pulses, the temperatures do not drop to the ambient temperature before the next pulse arrives. This leads to heat accumulation.<sup>[28]</sup> In this respect, the laser processing is a promising technology because it can induce thermal effect at very locally confined small area that needs high temperature without incurring extreme thermal damage to surrounding regions.<sup>[29, 30]</sup>

Figure 1.8 The spatial temperature distributions plotted along the surface for conventional thermal annealing as well as continuous laser and pulsed lasers heating.

In the commercially successful flexible AMOLED displays (e.g. Samsung's Galaxy Note Edge, LG Display's G Flex), laser is an indispensable process for their products even though the related processes are costly. Moreover, laser share of total process is on an increasing trend. For example, (1) plastic-based AMOLED displays are operated by excimer-laser-annealed TFTs (ELA-TFTs) on PI substrates. A large area excimer laser beam allows improving crystallinity and properties without thermal damage of the underlying substrate. (2) Secondly, to avoid difficulties presented by the plastic materials for the direct fabrication, the process of the flexible AMOLED displays is performed on the carrier glass. Therefore, at the last step, the structure should be released from the rigid carrier. This lift-off process relies on a laser-irradiation that is

favored for the high throughput. When the laser with the specific wavelength irradiates a special layer that reacts upon exposure, hydrogen gas is generated, and the gas is the driving force to separate the structure with the ELA-TFTs from the original carrier substrate. (3) Thirdly, today many product companies adopt a sapphire glass and even metal case having the great hardness as a protection layer from external factors. However, the strong hardness presents difficulty of direct and clear cutting. The laser solves this issue and achieves high quality of cutting surfaces and lines. (4) Moreover, the laser can be used for panel chamfering or trimming, which is removing unnecessary areas of the panel that has no patterns. Corner chamfering/trimming process by the laser can prevent cracks near the chamfering/trimming lines and can realize a very narrow bezel design of the panel before applying the laser process. (5) Lastly, the laser provides new solutions by allowing the machining and tooling to be micro scale. Because the mobile devices are getting thinner and thinner as the day goes on, the devices should be built to very high standard with close tolerance. Therefore, we need a more precise system and laser is a good candidate in this respect; perhaps it may be a promising way forward.

Likewise, the laser technology discussed earlier and later in this dissertation can enable emerging flexible devices and will pave the way for new fields of flexible electronics not yet imagined.

### **1.5 Scope of Dissertation**

Laser is an essential factor for the flexible display. With regard to further challenges in flexible displays, several other laser technologies, especially for TFTs (driving part, see Section 1.3.2), are focused and investigated in the following chapters as summarized in Figure 1.9.

Chapter 2 focuses on the 2D semiconductor materials with the formula of  $MX_2$  (M = Mo, W; X = S, Se, Te) composed of vertically stacked layers held together by van der Waals interactions as channel materials and their unique optical and electrical properties. The electrical characteristics of molybdenum disulfide (MoS<sub>2</sub>) TFTs are observed and carrier transport mechanism is predicted through variable temperature measurement (from room temperature up to 350 K) and different operating ambient (in air and in a vacuum, ~10<sup>-5</sup> Torr). Moreover, low-frequency noise measurement supports the immunity of MoS<sub>2</sub> for the effect of chemisorption.

In chapter 3, the irradiation of a pulsed laser with high energy density and short wavelength onto the metal electrodes leads to localized and confined thermal annealing effect without inflicting thermal damage to adjacent structures. This laser annealing effect on the electrical performances of flexible and transparent  $MoS_2$  TFTs is explored through current-voltage measurements and Y-function method (YFM). I also seek to understand in depth the effect of the laser processing on the interface structure and composition by performing cross-sectional high-resolution transmission electron microscopy (HRTEM).

Chapter 4 describes highly enhanced field effect mobility ( $\mu_{eff}$ ) of MoS<sub>2</sub> TFTs through sol-gel processed high-k ZrO<sub>2</sub> insulator, compared to general MoS<sub>2</sub>/SiO<sub>2</sub>/Si structures.

Furthermore, to avoid costly conventional mask-based photolithography, laser direct writing (LDW) process is employed using a simple set-up for defining the patterns of electrodes.

All non-vacuum and maskless processes for fabricating  $MoS_2$  TFTs are achieved through LDW and ink-jet printing (silver ink) in chapter 5. Self-alignment by difference of surface energy and capillary force allows unshaped ink-jet printed silver (Ag) ink to make well-defined electrode structures. The chapter also describes the use of interference lithography through a phase shift mask (PSM) for producing periodic nano scale patterns.

A large number of groups have struggled to find alternative conductive films as new flexible electrodes superior to indium tin oxide (ITO) that has brittle ceramic properties and is deposited through an expensive vacuum process limiting its further progress. 2D-like random networks of Ag nanowires (NWs) are attracting a lot of attention because of compatibility for cost-effective solution processible mass production and their good electrical conductivity. In chapter 6, as a gate electrode, 2D-like random networks of AgNWs are uniformly formed onto the solution based PI substrate. Then, plasmonic laser welding is employed to enhance interconnection each other like a net or mesh.

Chapter 7 summarizes the key findings and results in this dissertation and research and suggests the direction of future works for the flexible/wearable electronics.

**Figure 1.9** Organized schematics for the structure of this research and dissertation, showing the five technical focus areas on the TFTs: (1) 2D channel materials, (2) contact and interface, (3) dielectric and defining electrodes using LDW, (4) maskless small patterning (LDW and interference) with ink-jet printing, (5) 2D-like random networks using Ag nanowires and plasmonic laser welding process for the gate electrode.

# Chapter 2

# **Physical Properties of 2D materials**

### 2.1 2D Transition Metal Dichalcogenides (TMDs)

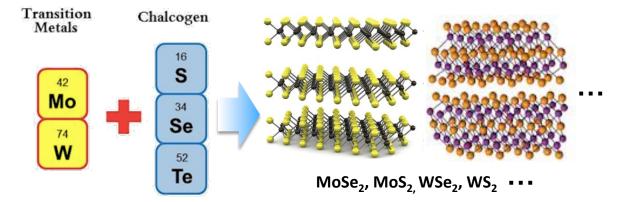

2D materials are a class of materials with the formula of  $MX_2$  (M (transition metal) = Mo, W; X (Chalcogenide) = S, Se, Te) composed of vertically stacked layers held together by van der Waals interactions like graphene (**Figure 2.1**). The general symmetry structure of TMDs is hexagonal or rhombohedral, and the metal atoms have octahedral or trigonal prismatic coordination.<sup>[31]</sup>

Graphene, one of the 2D materials has been studied and attracted the most attention culminated in the award of the 2010 Nobel Prize in physics because of its outstanding mechanical, optical, and electrical properties, as well as its processability.<sup>[32-34]</sup> Despite these excellent properties, graphene's major drawback is its gapless band structure, which makes it difficult to use in electrical switching devices such as transistors. Furthermore, a great amount of effort to achieve a sufficient bandgap has created other issues, increasing fabrication complexity and reducing mobility.<sup>[35, 36]</sup> However, owing to the advent and the exploration of graphene, 2D atomic layers from other materials can be easily exploited in a extremely short period of time. Therefore, there are a substantial number of reports that demonstrate novel devices for a wide variety of applications and explore their novel properties range from insulating (e.g. hexagonal boron nitride, h-BN) to semiconducting (e.g. MoS<sub>2</sub>, molybdenum diselenide MoSe<sub>2</sub>, tungsten diselenide, WSe<sub>2</sub>).<sup>[31]</sup> The extraordinary properties will be explored more detail in the **Section 2.2**.

**Figure 2.1** Combinations and structures for 2D materials with the formula  $MX_2$ , where M is a transition metal element from group IV, V or VI and X is chalcogen. (images from Google search)

### 2.2 Properties of 2D MoS<sub>2</sub>

Among atomic layered 2D TMDs materials,  $MoS_2$  has been widely used in numerous areas and has drawn attention as a promising alternative channel material due to the exotic electrical, optical, and mechanical properties. The electronic and optoelectronic applications of  $MoS_2$  are highly dependent on the electronic properties (e.g. band structure, density of states).

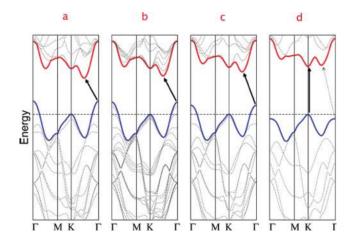

2D MoS<sub>2</sub> has *n*-type semiconducting characteristics with a relatively large bandgap (direct (1.8 eV) or indirect bandgap (1.2 eV) depending on the exact number of atomic layers) compared to zero-gap graphene.<sup>[37-40]</sup> Note that the band structure of bulk MoS<sub>2</sub> has the top of valence band situated at  $\Gamma$  of the Brillouin zone and the bottom of conduction band halfway between  $\Gamma$  and K (indirect).<sup>[38-40]</sup> On the other hand, the band structure of single monolayer MoS<sub>2</sub> is situated at K point (direct) as shown in **Figure 2.2**.<sup>[38-40]</sup> Moreover, the band structure of monolayer MoS<sub>2</sub> is changed by the mechanical strains when 10% of the homogeneous biaxial tensile strain is applied; the bandgap is reduced and manipulated from a direct to indirect and from a semiconductor to metal.<sup>[41]</sup>

**Figure 2.2** Calculated band structures of  $MoS_2$ : (a) bulk, (b) quadrilayer, (c) bilayer, and (c) monolayer. The top of valence band (blue) and bottom of conduction band (red) are highlighted. (image from A. Splendiani *et al.* Nano Lett. 2010)<sup>[40]</sup>

Besides interesting band structure, 2D MoS<sub>2</sub> shows attractive characteristics for the switching devices: high carrier mobility (~200 cm<sup>2</sup>/Vs range at high-k hafnium oxide (HfO<sub>2</sub>) and room temperature),<sup>[37,42]</sup> high on/off current ratio (I<sub>on</sub>/I<sub>off</sub>, ~10<sup>6</sup>),<sup>[37,43]</sup> low subthreshold swing (SS, ~70mV per decade),<sup>[37,43]</sup> and absence of dangling bonds.<sup>[37]</sup> Also, because of 2D nature, MoS<sub>2</sub> with very thin atomic thickness (6.5 Å) can be easy to fabricate complex structure and has good mechanical flexibility. In addition, other distinctive properties are reported: spin Hall effect for valleytronics and spintronics,<sup>[44-46]</sup> lattice dynamics through two different structures (e.g. 1H-MoS<sub>2</sub>, 2H-MoS<sub>2</sub>),<sup>[47,48]</sup> magnetism.<sup>[49,50]</sup> However, these properties lie beyond the scope of this research and dissertation; I won't go into all properties of MoS<sub>2</sub>.

The aforementioned exciting properties of MoS<sub>2</sub> lead to good switching behavior, can be fabricated into transistors using standard top-down nano/micro-fabrication process, and enable strong control of its carrier density by gate bias. Therefore, 2D semiconducting MoS<sub>2</sub> now creates various applications with performance far superior to devices made from current flexible semiconductors (e.g. organic semiconductors, solution-processed inorganic semiconductors): TFTs,<sup>[37,43]</sup> integrated circuits,<sup>[51]</sup> and sensors.<sup>[52-55]</sup>

### 2.3 Monolayer vs. Multilayer

The monolayer MoS<sub>2</sub> has direct band structure at K point of the Brillouin zone and has direct bandgap in the visible range. Therefore, very strong photoluminescence (PL) and large exciton binding energy are only present in a monolayer; these facts are promising for optoelectronic applications. Several different types of optoelectronic devices have been demonstrated including photodetectors, solar cells, and light emitting devices.<sup>[56]</sup> Moreover, because of high sensitivity to the strain force and gases (more specifically hydrogen, H<sub>2</sub>), there are many sensor applications as well.<sup>[52-55]</sup>

However, high sensitivity to external surroundings sometimes has negative effects on flexible TFTs for the displays or circuits, which are fabricated and designed strongly and solidly against the external impacts. Except for multilayer  $MoS_2$ , it is well known that absorbed molecules on surfaces result in the degradation of the performances of single- or bi-layer  $MoS_2$  transistors.<sup>[57,58]</sup> In this respect, multilayer  $MoS_2$  appears to be apt for these applications. In addition, a few early reports suggest that multilayer  $MoS_2$  can surpass single-layer  $MoS_2$  in the TFT-based applications because it has a larger density of states and helps to create a larger channel carrier density (i.e. presenting multiple conducting channel), which boosts the current drive of field effect transistors (FETs) made using this system.<sup>[43]</sup> Also, multilayer is more well suited for practical fabrication process. For example, currently 8 generation (2160 × 2400 mm) or 10 generation (2880 × 3130 mm) glass is applied in the industrial field of the displays; using one 8 generation glass, we can make 6 number of 55 inch display. Monolayer with 1 nm thickness is very hard to make thin film onto such a large glass panel, by the way.

# 2.4 Effects of Temperature and Ambient Conditions: MoS<sub>2</sub> TFTs

For use in electronics of these multilayer MoS<sub>2</sub> TFTs, unfortunately, the carrier transport mechanism and molecule absorption effects, critically related to transistor performances, has not yet been intensively explored at realistic operating temperatures (the working temperatures of commercial displays rise to +50 °C, and the extended temperatures increase to +85 °C). Even though a few reports have studied on temperature-dependent characteristics, such as the effective Schottky barrier height, these papers only focused on the single- or bi-layer MoS<sub>2</sub> TFTs below room temperature.<sup>[59-61]</sup> Therefore, I report observed preliminary evidence of the dominant scattering mechanism and the temperature dependent performance of multilayer MoS<sub>2</sub> TFTs.<sup>[62]</sup>

From the measurements of the temperature-dependent conduction at practical working temperatures (from room temperature up to 350 °K), extracted drop-off rates of the mobility are helpful knowledge to use as the active channel materials of the thermistors. Also, to show the effect of operating ambient on the devices, the electrical characteristics in the linear regime (at low drain voltage,  $V_D$ ) as a function of operating temperatures in air and in a vacuum (~10<sup>-5</sup> Torr) are specifically investigated. It exhibits that the multilayer MoS<sub>2</sub> transistors are more stable and less sensitive to ambient, comparing to the very thin monolayer MoS<sub>2</sub> transistors.

### 2.4.1 Device preparation

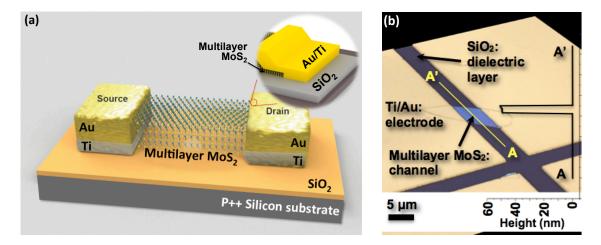

Figure 2.3(a) shows a schematic architectural diagram for a fabricated multilayer  $MoS_2$  TFT. A silicon dioxide (SiO<sub>2</sub>) dielectric layer with a thickness of 300 nm was deposited by chemical vapor deposition (CVD) on a heavily doped *p*-type Si wafer (resistivity  $< 5 \times 10^{-3}$  $\Omega$ cm). Multilayer MoS<sub>2</sub> flakes (~50 nm) were mechanically exfoliated from bulk MoS<sub>2</sub> crystals (SPI Supplies, USA), and transferred onto the deposited SiO<sub>2</sub> layer. For the source and drain electrodes, titanium (Ti, 10 nm) and gold (Au, 300 nm) were deposited by electronbeam evaporation and were patterned by conventional ultraviolet (UV) photolithography and lift-off techniques. Ti (~4.3 eV) was selected among the low work function materials because it has been suggested as a good contact for injection into the conduction band of MoS<sub>2</sub>.<sup>[39]</sup> Furthermore, Ti has been suggested since it is a transition metal with d orbitals that blend constructively with Mo4d states. Therefore, this favorable interface geometry is expected to facilitate good bonding and allow maximized injection at the contacts by increasing the overlap between the states at the interface.<sup>[39]</sup> Lastly, for reducing the contact resistance and residue, fabricated devices were treated by thermal anneal process at 200 °C in a vacuum furnace for two hours with 100 sccm argon (Ar) and 10 sccm H<sub>2</sub>. Figure 2.3(b) shows a 3D confocal laser microscope (LEXT OLS4000, Olympus) image of a fabricated multilayer MoS<sub>2</sub> TFT with the bottom gate structure. Measurements using an atomic force microscope (AFM) showed that the thickness of the MoS<sub>2</sub> channel was around 50 nm among the measured devices (inside Figure 2.3(b)).

**Figure 2.3** Multilayer  $MoS_2$  TFT structure: (a) the cross-sectional schematic structure of a multilayer  $MoS_2$  TFT with a 300-nm-thick  $SiO_2$  gate dielectric. (b) The top view of a 3D confocal laser microscope image of a multilayer  $MoS_2$  transistor after fabrication.

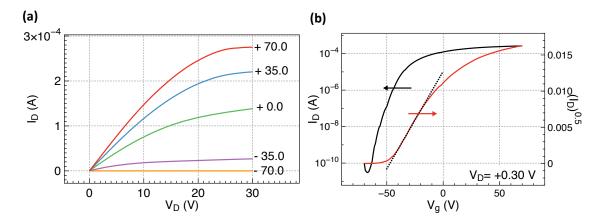

**Figure 2.4(a)** shows the drain current (I<sub>D</sub>) versus drain voltage (V<sub>D</sub>) curves for representative multilayer MoS<sub>2</sub> TFTs with a channel length of 4 µm and width of 5 µm, as a function of V<sub>D</sub> in a range from 0 to 30 V with the selected gate voltage (V<sub>G</sub>) ranging from -70 to +70 V in steps of 35 V. The fabricated multilayer MoS<sub>2</sub> TFTs exhibited conventional *n*-type behavior with negative threshold voltages (V<sub>TH</sub>). An on/min current ratio (I<sub>on</sub>/I<sub>min</sub>) of ~10<sup>7</sup> and SS of 3.4 V/decade were obtained and the µ<sub>eff</sub> in the saturation regime (µ<sub>eff\_sat</sub>  $\approx$  10.9 cm<sup>2</sup>/Vs extracted at V<sub>G</sub> = -25 V, V<sub>G</sub>-V<sub>TH</sub> < V<sub>D</sub>) was evaluated from a linear fitting of the curve of I<sub>D</sub><sup>0.5</sup> versus V<sub>G</sub> at a fixed high drain voltage (V<sub>D</sub> = 30.0 V) as shown in **Figure 2.4(b**). Initially, our device exhibited the square-law behavior at low V<sub>G</sub> (-40 V to +15 V), well. However, the device shown saturated I<sub>D</sub> for V<sub>G</sub> above -15V, even though V<sub>D</sub> did not reach V<sub>G</sub>-V<sub>TH</sub>. This notes that other authors have proposed that this strong saturation in output characteristics can partially be explained by the self-heating effect (corresponding to the intermediate regime) before reaching the negative I<sub>D</sub>-V<sub>D</sub> slope regime (where the self-heating effect is dominant).<sup>[63]</sup>

**Figure 2.4** Representative electrical characteristics of multilayer  $MoS_2$  TFT at room temperature: (a) the plot of  $I_D$ - $V_D$ . (b) Plots of  $I_D$ - $V_G$  (left axis) and  $I_D$ <sup>0.5</sup>- $V_G$  (right axis).

#### 2.4.2 Results and discussion

To further understanding the carrier transport mechanisms in multilayer MoS<sub>2</sub> TFTs, I investigated the effect of the ambient conditions (in air and in a vacuum) in combination with the variable operating temperature measurements. The transfer curves,  $I_D$ -V<sub>G</sub>, were obtained in the linear regime (at a low V<sub>D</sub> of 0.1V) to create a uniform charge density in the accumulation layer and the field effect mobility in the linear regime ( $\mu_{eff_lin} \approx 14.0 \text{ cm}^2/\text{Vs}$ ) was calculated at room temperature by the MOSFET square-law model:

$$\mu_{eff} = \frac{dI_D}{dV_G} C_i \times \frac{1}{V_D}$$

(2.1)

where  $C_i$  is the insulator capacitance per unit area. Note that Das and others suggested that the maximum potential of back-gated multilayer MoS<sub>2</sub> TFTs with the thickness in the range of 30  $\sim 60$  nm and Scandium (Sc) contacts would be limited around 50 cm<sup>2</sup>/Vs due to involving

interlayer coupling resistances.<sup>[64]</sup> Therefore, the extracted  $\mu_{eff}$  both in saturation and linear regimes are lower than that of reported results, but nevertheless we can boost the  $\mu_{eff}$  through incorporating metals with lower work function (like Sc (3.5 eV)) than Ti (4.3 eV) / Au (5.1 eV) for reducing the Schottky barrier and through a high-k dielectric layer for minimizing the effect on Coulomb electron scattering. The contact resistance factor should be well separated from measured extrinsic characteristics to exploit the transport mechanism inside the MoS<sub>2</sub> semiconductor channel. Here, the Y function method (YFM) was hired to extract the intrinsic low field mobility ( $\mu_{0}$ , the maximum available mobility in this system) and contact resistance (R<sub>c</sub>):<sup>[65-67]</sup>

$$Y = \frac{I_D}{\sqrt{G_m}} = \sqrt{\frac{W}{L} C_i \mu_0 V_D} \times (V_G - V_{TH})$$

(2.2)

where  $C_i$  is the insulator capacitance per unit area. The  $\mu_0$  can be extracted from the slope of Y-function (discussion later in detail). Note that the slope of the plot is  $1.42 \times 10^{-4}$  as shown in **Figure 2.5(a)** and the extracted  $\mu_0$  at a low  $V_{DS}$  of 0.1 V is 14.6 cm<sup>2</sup>/Vs. If the contact effect is dominant, the extracted  $\mu_{eff\_lin}$  should be significantly lower than  $\mu_0$  and the non-linear I<sub>D</sub>-V<sub>D</sub> curves should be presented at low  $V_D$  as well. However,  $\mu_0$  (14.6 cm<sup>2</sup>/Vs) was only 3% more than the extrinsic  $\mu_{eff\_lin}$  (14.0 cm<sup>2</sup>/Vs) at the same  $V_D$ . Furthermore, the linear I<sub>D</sub>-V<sub>D</sub> curves were presented clearly at low  $V_D$ . Another interesting aspect is that the extracted  $\mu_{eff\_lin}$  (14.0 cm<sup>2</sup>/Vs) is higher than  $\mu_{eff\_sat}$  (10.9 cm<sup>2</sup>/Vs). First, this may originate from the fringing effect and/or the scattering effect. The fringing currents depend on  $V_D$ , the 1:1 aspect ratio of the channel would overestimate the calculated  $\mu_{eff}$ , particularly when the MoS<sub>2</sub> flakes exceed the contacted channel width. Second, it is well known that the  $\mu_{eff\_sat}$  is commonly less affected by the R<sub>c</sub> than  $\mu_{eff\_lin}$ . Therefore, the  $\mu_{eff\_lin}$  should be lower than  $\mu_{eff\_sat}$  in contact resistant dominant system. To investigate this phenomenon more specific, the R<sub>c\\_max</sub> (23.4 kΩ) was estimated from the mobility attenuation factor ( $\theta = \mu_0 C_i R_c W/L$ ).<sup>[66,67]</sup>  $\theta$  can be extracted by following equation:<sup>[65,66]</sup>

$$g_m = \frac{\partial I_D}{\partial V_G}, (V_D = const) = \frac{W}{L} C_i \frac{\mu_0}{[1 + \theta (V_G - V_{TH})]^2} \times V_D$$

(2.3)

From Equation (2.3), we can know that the  $\theta$  can be calculated from the slope of the plot  $(1/g_m^{1/2} \text{ versus } V_G)$  and the linear fitted slope is 33.16 as shown in Figure 2.5(b). Also, to calculate the channel resistance  $(R_{ch})$  and to compare with  $R_{c_max}$ , the total resistance  $(R_{total}=R_c+R_{ch})$  was calculated from  $I_D-V_D$  curves at low  $V_D$  and the obtained  $R_{total}$  and  $R_{ch}$  were 333.4 k $\Omega$  and 310 k $\Omega$ , respectively. For double-checking the value of  $R_{ch}$ , we directly calculated from induced charge carriers,  $R_{ch}=L/(\mu_0WC_i(V_G-V_{TH}))$  once again. Note that the reconfirmed  $R_{ch}$  was ~250 k $\Omega$  and both values of  $R_{ch}$  are larger than  $R_c$  in this system. Therefore, it can be possible that the effect of scattering is more significant than the effect of  $R_c$ .<sup>[68]</sup> I address these features in more depth later with the transconductance ( $G_m$ ) and the  $\mu \sim T'$  law, specifically.

**Figure 2.5 (a)** The  $I_d/g_m^{0.5}$  plot with linear fitting in ambient condition. (b) The plot of  $1/g_m^{1/2}$  with respect to gate voltage with linear fitting for evaluation of mobility attenuation factor,  $\theta$ .

To describe the electrical characteristics for the variable operating temperatures, two regimes (green and blue regions) based on the zero temperature coefficient (ZTC) point in the on-state were defined in **Figure 2.6(a)** and **2.6(b)**. At the ZTC gate voltage, the devices exhibit constant DC performance with operating temperature. However, the fabricated TFTs did not show a clear ZTC point. Thus, the minimum point of dI/dT was set as a cut-off point to divide the two regimes. Qiu and others reported that a  $\Phi_B$  was formed between the Ti/Au metal contact and the MoS<sub>2</sub> semiconductor in their research; the structure investigated was the same as our structure.<sup>[59]</sup> The Schottky barrier height was ~65 meV, which exceeded the thermal emission energy at room temperature.<sup>[59,69]</sup> Therefore, at low V<sub>G</sub> (below V<sub>TH</sub>), these barriers partially hindered the flow of carriers. However, when the operating temperature increased, the carriers easily overcame these barriers by thermionic emission.<sup>[70]</sup> This caused I<sub>min</sub> to rise.