# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Heteroepitaxial Thick GaN Layers and Vertical High-Power Devices by Selective Area MOCVD Growth

Permalink https://escholarship.org/uc/item/9wz8j1kd

**Author** Tanaka, Atsunori

**Publication Date** 2019

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SAN DIEGO

Heteroepitaxial Thick GaN Layers and Vertical High-Power Devices by Selective Area MOCVD

Growth

A dissertation submitted in partial satisfaction of

the requirements for the degree Doctor of Philosophy

in

Materials Science and Engineering

by

#### Atsunori Tanaka

Committee in charge:

Professor Shadi A. Dayeh, Chair Professor Peter M. Asbeck Professor Prabhakar R. Bandaru Professor William Trogler Professor Charles Tu Professor Paul K. Yu

Copyright

Atsunori Tanaka, 2019

All right reserved.

The Dissertation of Atsunori Tanaka is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2019

# DEDICATION

To my parents

# TABLE OF CONTENTS

| Signature   | Pageiii                                                                |

|-------------|------------------------------------------------------------------------|

| Dedicatior  | ıiv                                                                    |

| Table of C  | ontentsv                                                               |

| List of Fig | uresviii                                                               |

| List of Tal | blesxiii                                                               |

| Acknowle    | dgementxiv                                                             |

| Vita        | xviii                                                                  |

| Publicatio  | nsxviii                                                                |

| Conferenc   | es xx                                                                  |

| Field of st | udyxxi                                                                 |

| Abstract o  | f the Dissertationxxii                                                 |

| Chapter 1   | Motivation and Challenges for Vertical GaN High Power Devices on Si1   |

| 1.1 I       | ntroduction1                                                           |

| 1.2 E       | Background of Wide Bandgap Power Device2                               |

| 1.2.1       | Advantages of GaN Over Si-Based Power Device                           |

| 1.2.2       | Pros and Cons of Lateral and Vertical Power Devices                    |

| 1.2.3       | Requirement for Vertical Power Device                                  |

| 1.3 (       | Challenges for GaN Vertical Power Device on Si10                       |

| 1.3.1       | Thickness limitation due to Thermal Mismatch Between GaN and Si11      |

| 1.3.2       | Unintentional Doping of GaN in MOCVD and Selective Area Growth (SAG)16 |

| 1    | .4    | Overview of the Dissertation                                              | 17  |

|------|-------|---------------------------------------------------------------------------|-----|

| 1    | .5    | References                                                                | 18  |

| Ch   | apter | 2 A Comprehensive Analysis of GaN Selective Area Growth: Size Effects and |     |

| Inf  | luenc | e on Light Extraction from GaN Light Emitting Diodes                      | .21 |

| 2    | .1    | Introduction                                                              | 21  |

| 2    | 2     | Experimental Details                                                      | 23  |

| 2    | .3    | Generic Geometric Effects in SAG GaN on c-Sapphire                        | 24  |

|      | 2.3.1 | Gallium Adatom Diffusion Length on GaN Surface                            | 29  |

|      | 2.3.2 | 2 Diameter Dependent Vertical Growth Rate                                 | 31  |

|      | 2.3.3 | 3 Spacing Dependent Vertical Growth Rate                                  | 33  |

|      | 2.3.4 | 4 Spacing Dependent Lateral Growth Rate, Facet Length and Facet Evolution | 35  |

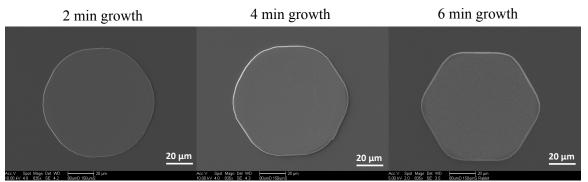

|      | 2.3.5 | 5 Time Dependent Facet Evolution                                          | 37  |

| 2    | .4    | Enhancement of LED Light Extraction by Tailoring Array Pattern Structure  | 38  |

| 2    | 5     | Conclusion                                                                | 46  |

| 2    | 6     | Acknowledgements                                                          | 46  |

| 2    | .7    | References                                                                | 47  |

| Ch   | apter | 3 Si Complies with GaN to Overcome Thermal Mismatches for the Heteroepita | ıxy |

| of ] | Гhick | GaN on Si                                                                 | .51 |

| 3    | .1    | Introduction                                                              | 51  |

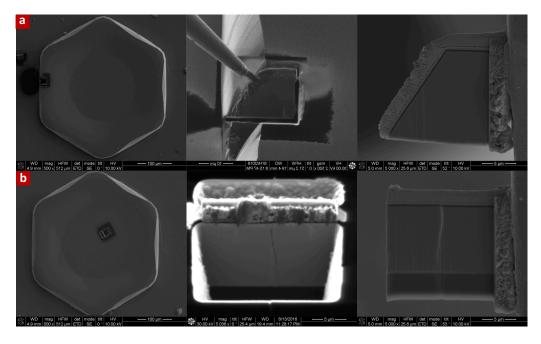

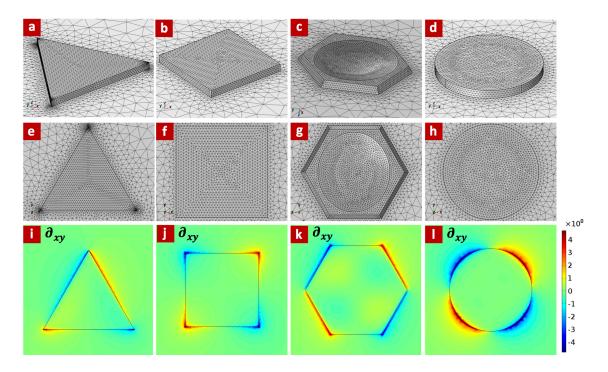

| 3    | .2    | Optimization of SAG Mask Design for Thick GaN Growth                      | 52  |

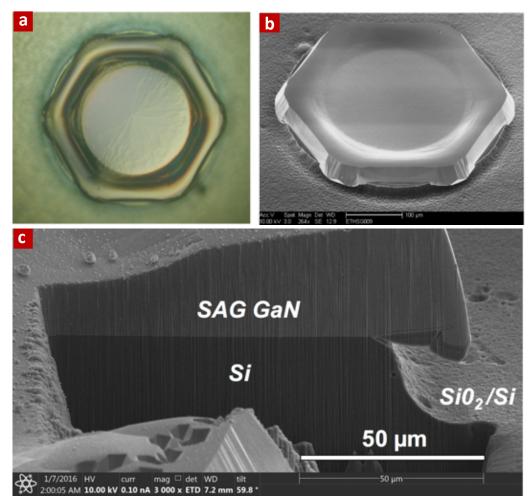

| 3    | .3    | Cracking Mechanism of SAG GaN-on-Si                                       | 55  |

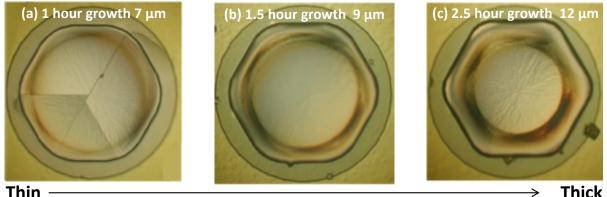

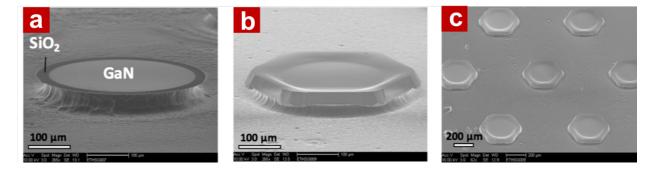

|      | 3.3.1 | Time Dependent Growth of SAG GaN on Si                                    | 55  |

|      | 3.3.2 | 2 Stress Relaxation by Facet Evolution                                    | 56  |

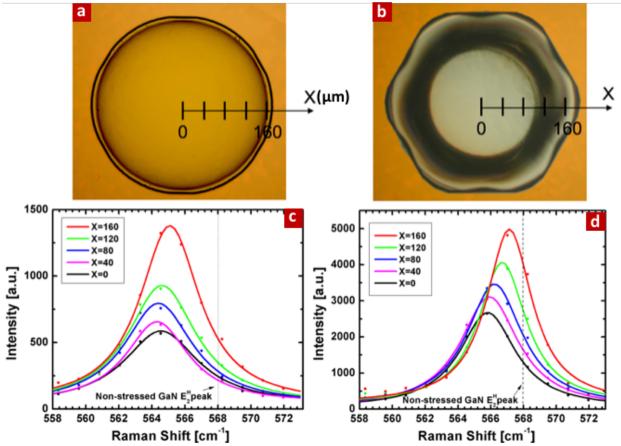

|      | 3.3.3 | 3 Stress Measurement by Micro Raman Spectroscopy                          | 60  |

| 3    | .4    | Tangential Stress in GaN/Si Interface and Cracking in Si substrate        | 63  |

| 2     | 3.4.1  | Observation of Cracking in Si substrate                                       | 63         |

|-------|--------|-------------------------------------------------------------------------------|------------|

| ŝ     | 3.4.2  | Substrate Engineering to Accommodate the Tangential Stress                    | 68         |

| 3.5   |        | Material Quality Improvement by Thick GaN Growth                              | 71         |

| 3.6   |        | Demonstration of Vertical GaN MISFET on Si                                    | 73         |

| 3.5   |        | Conclusion                                                                    | 77         |

| 3.6   |        | Acknowledgements                                                              | 77         |

| 3.7   |        | References                                                                    | 78         |

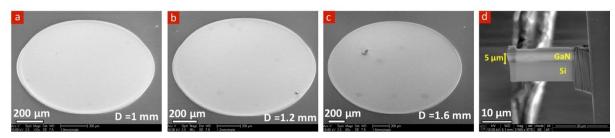

| Chap  | oter 4 | 4 Structural and electrical characterization of thick GaN layers on Si, Ga    | aN, and    |

| engin | neere  | ed substrates                                                                 |            |

| 4.1   |        | Introduction                                                                  | 80         |

| 4.2   |        | Experimental Detail                                                           | 82         |

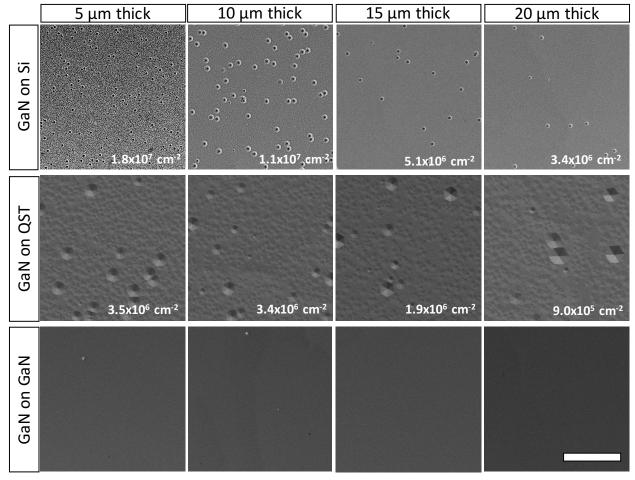

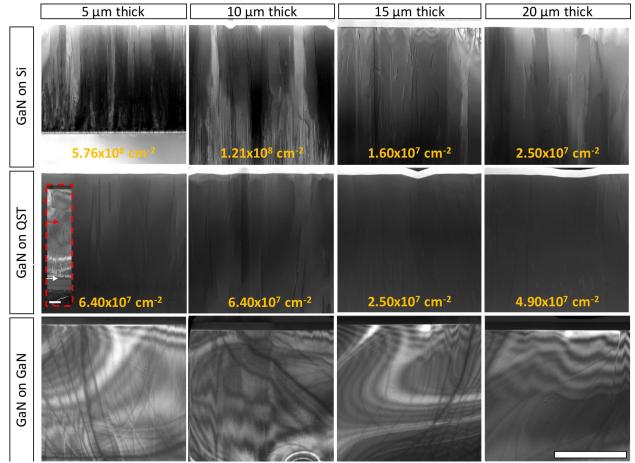

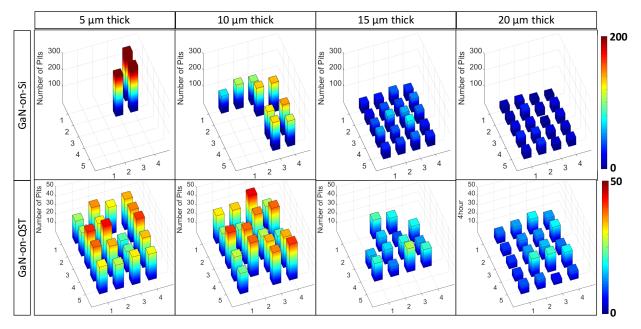

| 4.3   |        | Evaluation of Defect Densities as a Function of Thickness for Each Substrates | 84         |

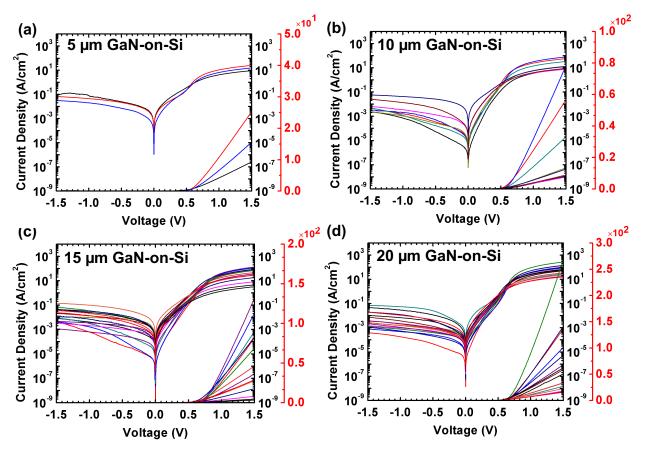

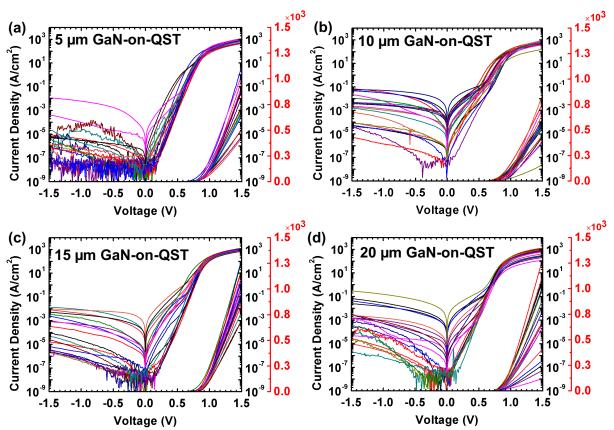

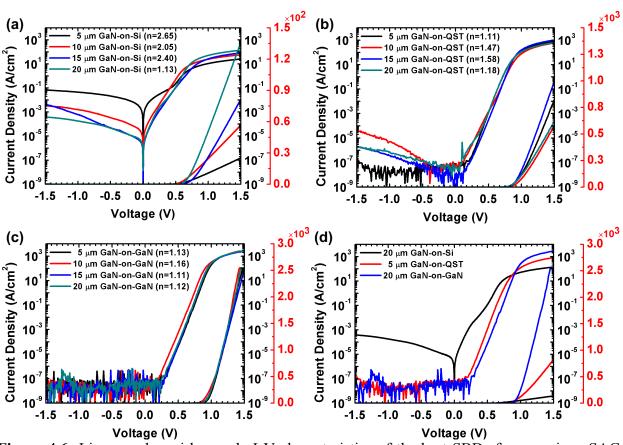

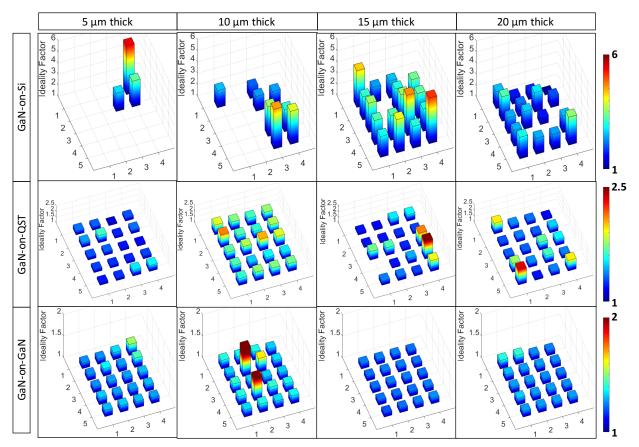

| 4.4   |        | Evaluation of SAG Electronic Properties by Schottky Barrier Diode Character   | ization90  |

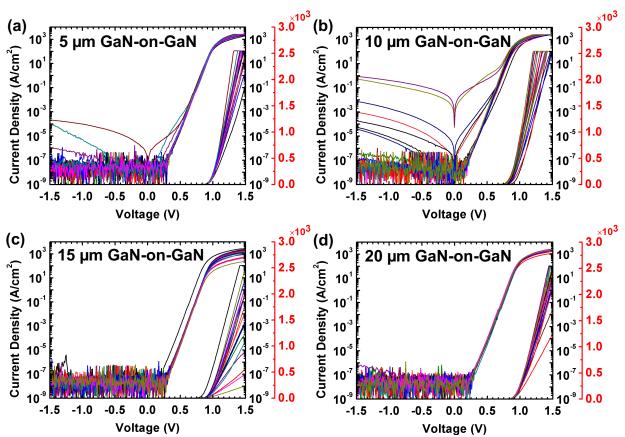

| 2     | 4.4.1  | Current, Capacitance -Voltage Characteristics of SBDs on Each Substrates      | 90         |

| 2     | 4.4.2  | Geometrical Effect of Dislocation Densities and Ideality Factors              | 99         |

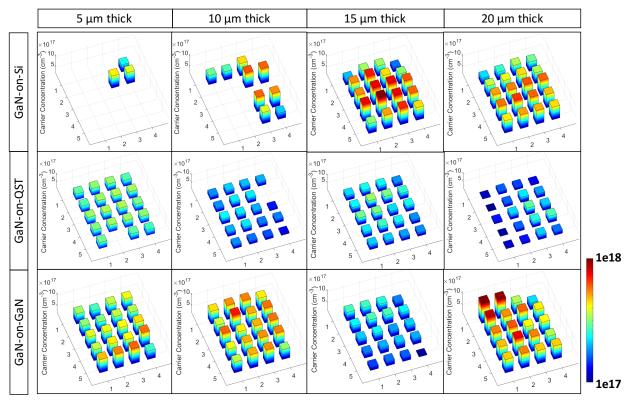

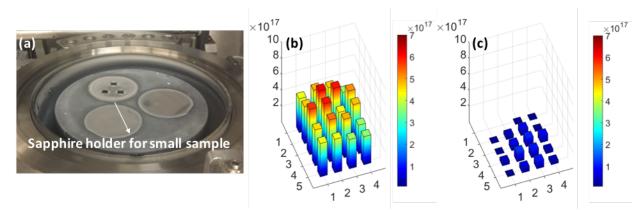

| 2     | 4.4.3  | Effect of Geometrical FCarrier Concentration and Sample Holder on t           | he Carrier |

| (     | Conc   | entrations                                                                    |            |

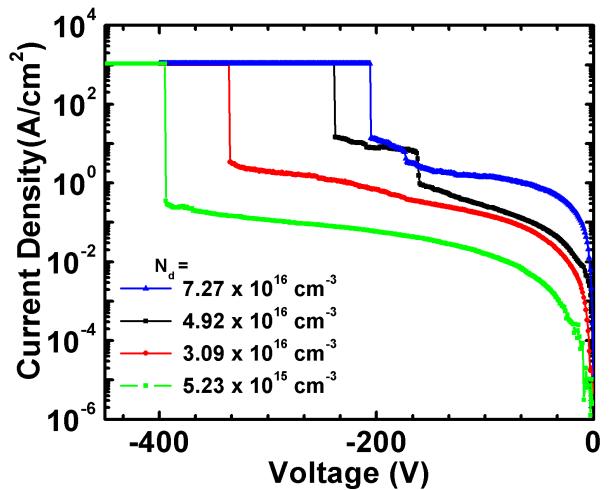

| 2     | 4.4.3  | Breakdown Characteristics of GaN SBDs on QST substrate                        |            |

| 4.5   |        | Conclusion                                                                    | 107        |

| 4.6   |        | Acknowledgements                                                              | 107        |

| 4.7   |        | References                                                                    |            |

# LIST OF FIGURES

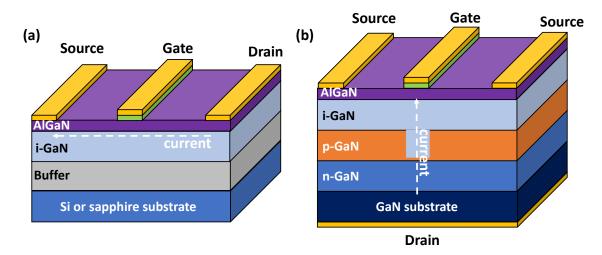

| <b>Figure 1.1</b> Schematic illustration of (a) lateral AlGaN/GaN HEMT and (b) GaN current-aparture-vertical-electron-transistor(CAVET)                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

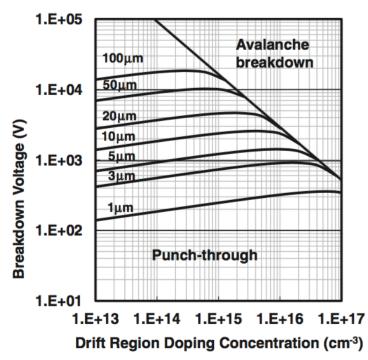

| <b>Figure 1.2</b> Breakdown voltage vs drift region doping concentration for each drift layer thickness from 1 to 100 μm. <sup>11</sup>                                                                                                                                                                                                             |

| <b>Figure 1.3 (a)</b> Stress in GaN film as a fuction of the thickness. The AlGaN buffer layer thickness decrease the increment of tensile stress generation. <b>(b)</b> Critical thickness of GaN for cracking as a function of buffer layer thickness. <sup>18</sup>                                                                              |

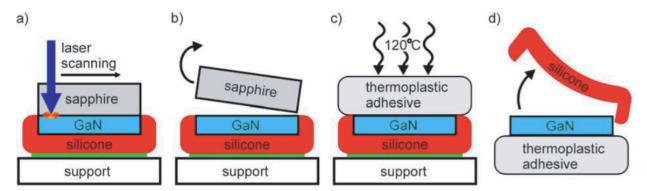

| <ul> <li>Figure 1.4 Process sequence for the laser lift -off of 2" GaN membranes. (a) Laser lift-ff of the GaN film from sapphire; (b) sapphire removal; (c) deposition of a ~3mm thick layer of thermoplastic adhesive at 120 °C; (d) peel-off of the silicone elastomer.<sup>19</sup>13</li> </ul>                                                |

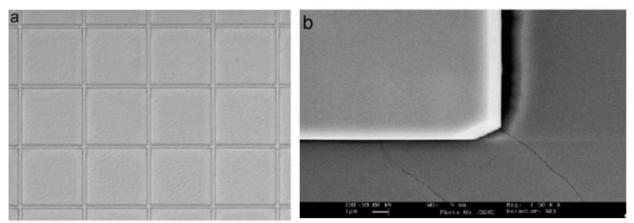

| Figure 1.5 (a) Microscope image of as-grown LEDs layer on patterned Si substrate. (b) Top-view SEM image of GaN on patterned Si substrate. <sup>20</sup>                                                                                                                                                                                            |

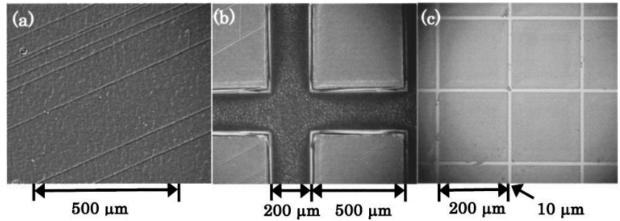

| Figure 1.6 Microscope image of SAG GaN/AlN/Si. (a) GaN film grown without grid mask. (b) GaN grown on 500 μm wide square windows with 200 μm wide masks. (c) GaN grown on 200 μm square windows with 10 μm wide masks. <sup>21</sup>                                                                                                                |

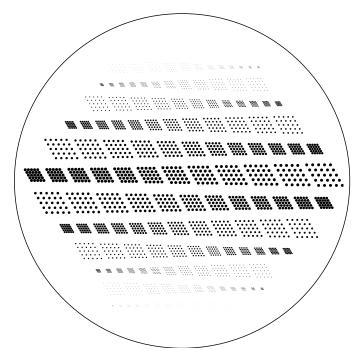

| Figure 2.1 Photomask design for SAG GaN on 2 inch wafer                                                                                                                                                                                                                                                                                             |

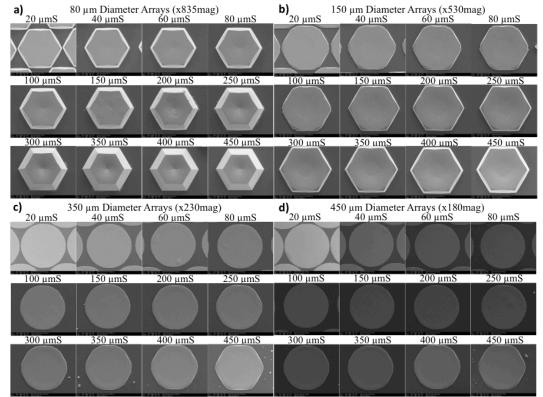

| <b>Figure 2.2</b> Top view SEM images of the SAG GaN structures for different mask openings (a) 80 μm, (b) 150 μm, (c) 350 μm, and (d) 450 μm for edge-to-edge spacings in the range of 20 μm to 450 μm                                                                                                                                             |

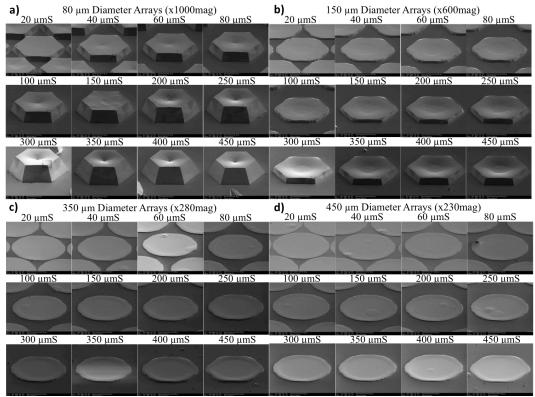

| <b>Figure 2.3</b> 45°-angled SEM images of the SAG GaN structures for different mask openings (a) 80 μm, (b) 150 μm, (c) 350 μm, and (d) 450 μm for edge-to-edge spacings in the range of 20 μm to 450 μm. Strong vertical growth rate enhancement was observed for all diameters and spacings.                                                     |

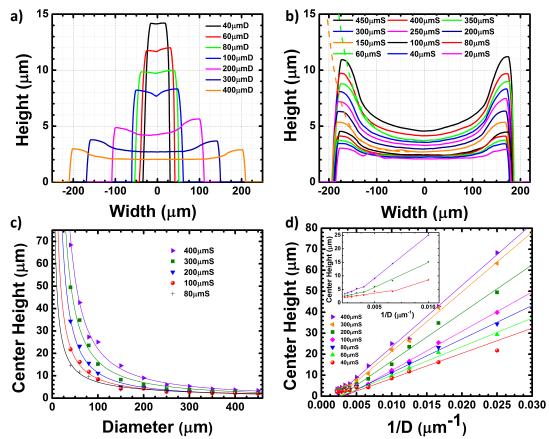

| <b>Figure 2.4</b> Surface profilometry on the grown structure with (a) fixed spacing at 20 $\mu$ m and (b) fixed diameter at 350 $\mu$ m. (c) The heights of the grown structures as a function of the mask diameters and (d) the inverse of the mask diameters; the inset highlights the large diameter region of the plots                        |

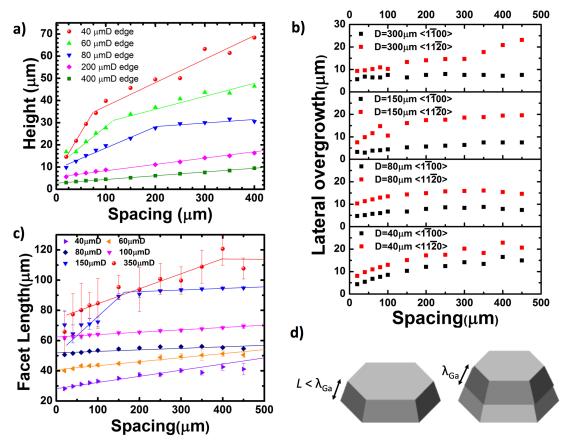

| <b>Figure 2.5</b> (a) Edge heights for the grown structures. (b) The lateral overgrowth lengths and (c) the facet lengths as a function of the mask spacings. The facet lengths are defined as the average length of the six sides of the grown hexagon base. (d) Schematic illustration of the collection area contributing to the vertical growth |

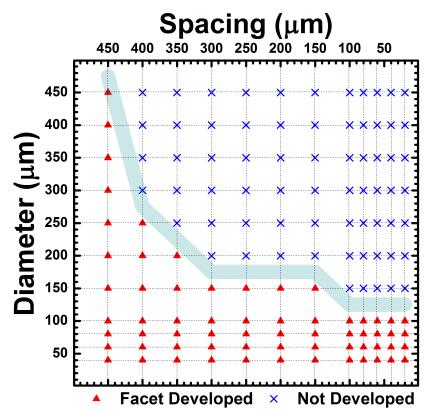

| <b>Figure 2.6</b> Facet evolution with the mask geometry as was observed by SEM. The triangles represent the grown structure with six complete well-developed facets and the crosses represent the grown structure with at least one rough sidewall                                                                                                 |

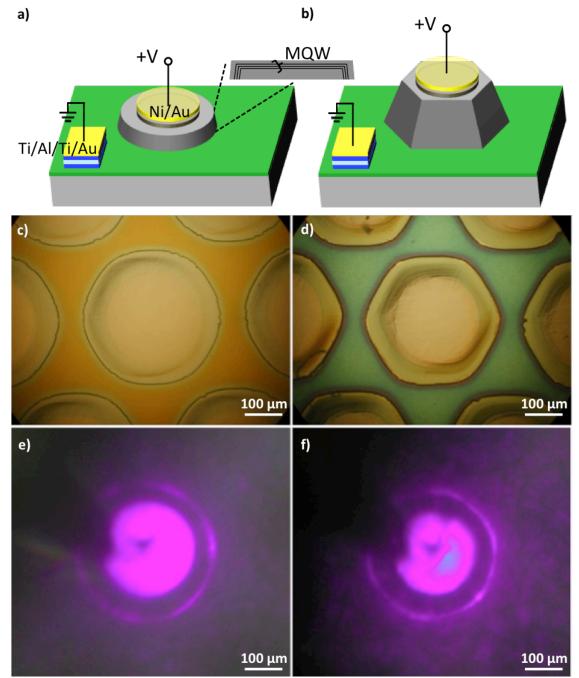

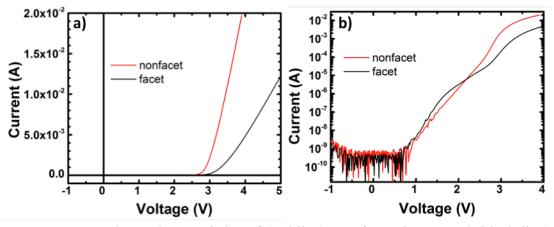

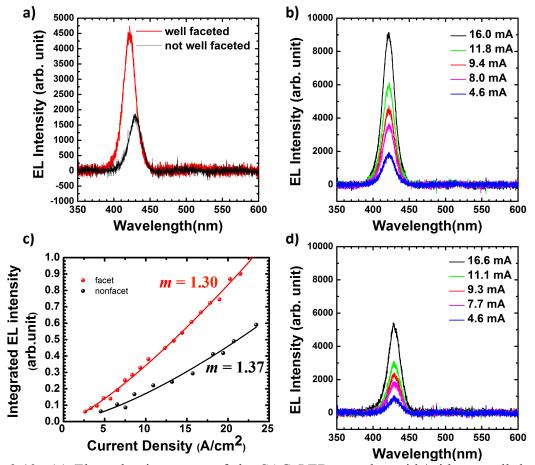

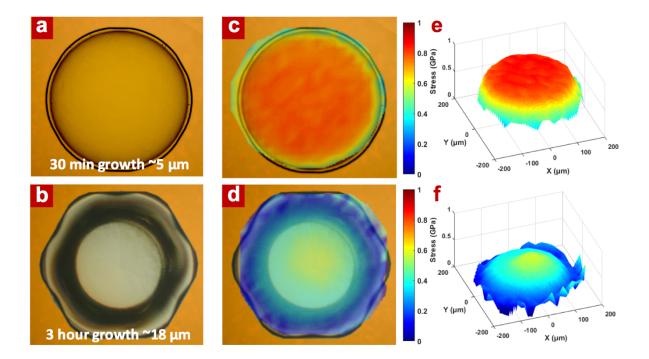

- **Figure 2.8** Schematic illustration of the device structure for (a) non-faceted SAG LED and (b) well-faceted SAG LED. Optical microscope images of (c) non-faceted and (d) well-faceted and their emitting images in (e) and (f) respectively. The mask geometries are the same, 350 µmD and 80 µmS for each structure.

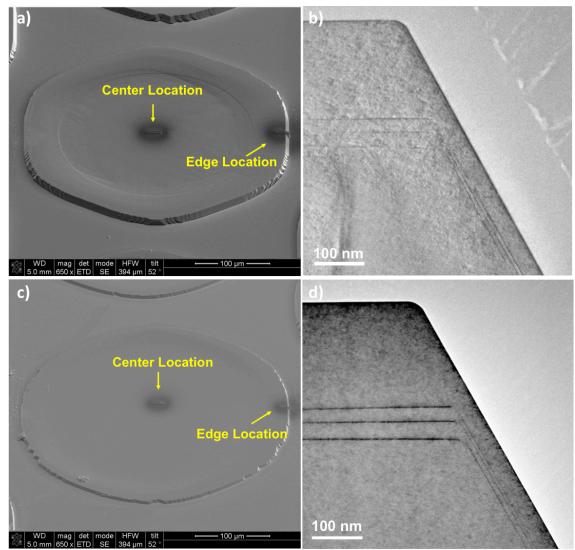

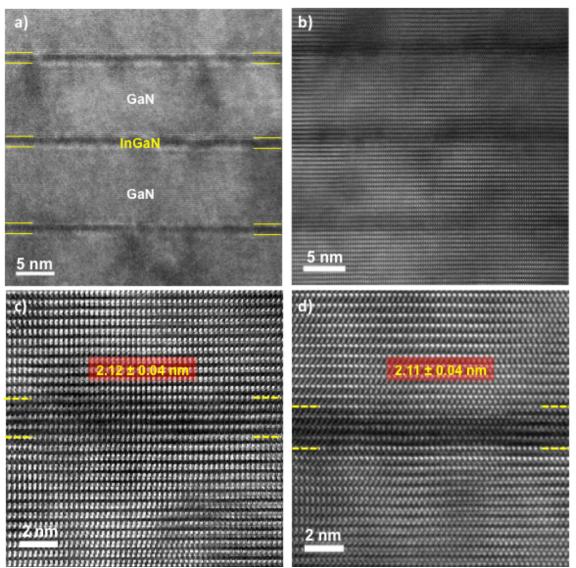

- **Figure 2.12** Cross-sectional TEM images of (a),(c) well-faceted and (b), (d) non-faceted MQW structures near the center of the structures. (a) and (b) show the uniform growth of three cycles of InGaN MQWs. (c) and (d) are zoomed-in images of (a) and (b), respectively......44

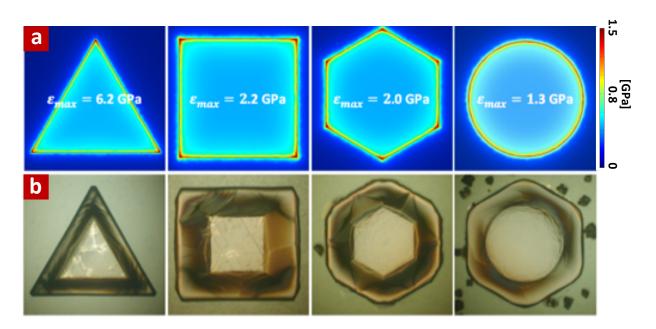

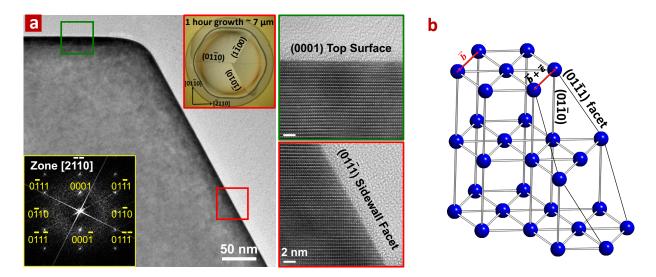

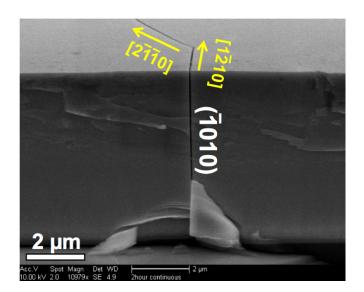

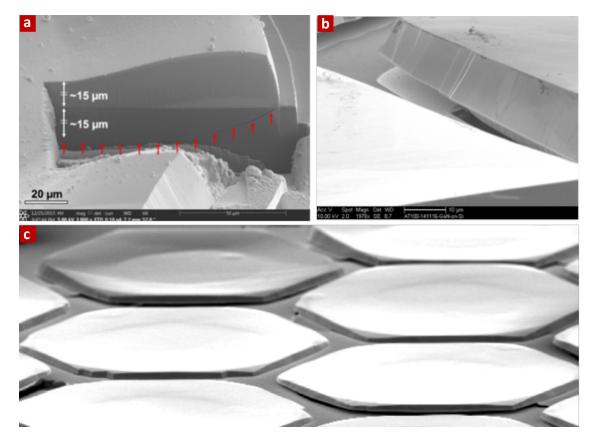

- **Figure 3.4 Major crack plane determination by SEM.** Angled view SEM image of diced GaN disk in <1010> direction. The crack propagates straight down to the substrate and ~60° intersections, indicating the crack plane is in (1010) and propagate in the <2110> directions.

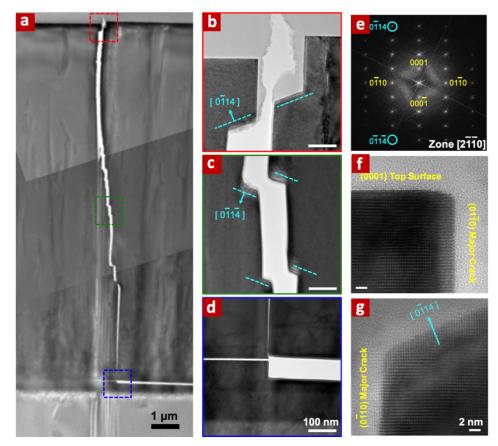

| Figure 3.6 Crack plane determination by TEM. | 59 |

|----------------------------------------------|----|

|----------------------------------------------|----|

#### Figure 3.8 Stress relaxation mechanism in crack-free GaN-on-Si by facet formation.......62

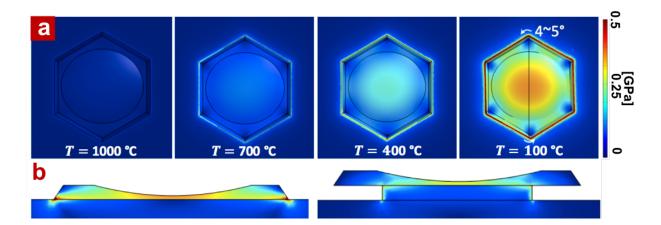

- **Figure 3.9 (a)** Evolution of thermal stress during cooling down from 1050 to 100 °C. The solid black lines are the original GaN disk location at the growth temperature. **(b)** Cross-sectional view of thermal stress simulation of SAG GaN with/without Si base etched. The stress peaks at the interface of hexagonal vertices were eliminated by removing Si under the SAG GaN.

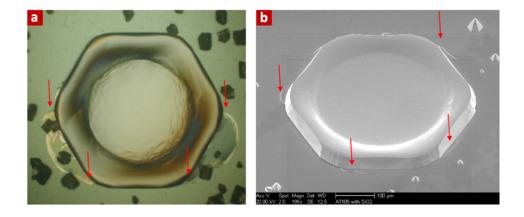

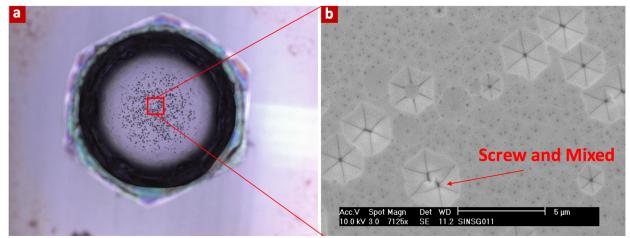

- Figure 3.17 Dislocation selective etching. (a) Top view microscope image after etching (b) Top view SEM image near the center of the disk where most dislocations were found......72

Figure 4.8 3D color map of ideality factors of each dot in the SAG arrays for the GaN-on-Si, GaN-on-QST and GaN-on-GaN. 101

**Figure 4.11** Breakdown characteristics of GaN-on-QST SBDs fabricated on 20 μm thick drift layers with different carreir concentrations. All the SBDs have no edge termination.......106

# LIST OF TABLES

| Table 1.1 Material properties of wide bandgap semiconductors in comparison with those of Silicon <sup>4,6,7</sup>                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 1.2</b> Implications of the usual substrate materials for the GaN-epitaxy (data relative to the GaN properties. <sup>6</sup>                                                                                                                          |

| Table 2.1 Diffusion lengths for selected different mask geometries    30                                                                                                                                                                                       |

| <b>Table 2.2</b> MQW thicknesses of the well-faceted and non-faceted LED at different points of the<br>structures; center, edge and sidewall of the structure. These thicknesses were measured from<br>TEM images and averaged over 10 lines for each point.45 |

| Table 4.1. Substrate and buffer layer details and properties.    83                                                                                                                                                                                            |

| Table 4.2 GaN-on-Si SBD characteristics.    93                                                                                                                                                                                                                 |

| Table 4.3 GaN-on-QST SBD characteristics.    95                                                                                                                                                                                                                |

| Table 4.4 GaN-on-GaN SBD characteristics    96                                                                                                                                                                                                                 |

| Table 4.5       SBD breakdown characteristics for GaN-on-QST substrates with different carrier concentrations.         106                                                                                                                                     |

#### ACKNOWLEDGEMENT

First of all, I would like to express my greatest gratitude to my advisor prof. Shadi A. Dayeh for his warm guidance, financial support, hard work and continual encouragement over the course of my 6 years Ph.D researches. He has been a tremendous mentor for me. I still remember we spent 6 hours from 10 pm to 3 am to discuss the selective growth result in his office. The first 2 years was very tough and challenging for me but his work ethic and thinking approaches to unknown problems have taken root in my brain. I am sure it will help my future work and life. I am very happy to have him my Ph.D advisor and I am very appreciate he accepted me as a member of IEBL.

I am also highly grateful to the members of my thesis committee, prof. Peter M. Asbeck, prof. Prabhakar R. Bandaru. prof. William Trogler, prof. Charles Tu and prof. Paul K.L. Yu. Prof. Asbeck always provided me crucial feedback on both of GaN growth and device results as he is one of the pioneer of GaN devices. Prof. Paul Yu kindly allowed me to operate his Nitride MOCVD system and put me as a superuser of the system even I was not his lab member. Also, he gave us many valuable feedback on GaN growth and MOCVD system maintenance. Prof. Tu and his former students helped me bring up Arsenide/Phosphide MBE system in my first year. I also thank prof. Bandaru and prof. Trogler for their advices during my qualifying exam and final defense, and their great support over the past six years.

I would also like to express my great gratitude to prof. S. S. Lau for many valuable inputs and discussions during my Ph.D. researches. His sharp questions in our group meeting always let me rethink about purpose of the projects, fundamental physics and problems. Late Dr. Phil Mages trained me for operation and maintenance of MOCVD system. Through the process of bringing up one of the MOCVD system, I was able to fully understand each components of the system. The time I spent with him was very precious. Thank you.

I am also very happy to work with brilliant labmates in IEBL. Dr. Renjie Chen, YunGoo Ro and I were first three Ph.D students in IEBL and we spent very tough and challenging first year. I spent almost all the time with YunGoo in the lab as well as outside of the lab. One of the biggest treasure by doing PhD was having them as my friends. I also very appreciate help and collaboration with Woojin Choi. All of the good results were obtained after he joined and provided me great feedback about device fabrication. Without him, I would not publish any papers with functional device results. Moreover, other group members, Ren Liu, SangHeon Lee, Dr. Mehran Ganji, Lorraine Hossain, Andrew Bourhis, Po Chun Chen, Jihwan Lee, Samantha Russman, Ritwik Vastyayan, Keundong Lee, Dr. Hongseok Oh and Dr. Younbin Tchoe have given me great supports both in experiments and in daily life. They are much more brilliant and hardworking than I used to be at their ages. I am very sure that IEBL group will have another successful era after I leave.

I would like to also thank UCSD EH&S, Doug Harvey, Anju Melkani and Michael Cerdinio, and ECE Department staffs, Cheryle Wills and Julie Mortiz. Without their assistance, I would not be able to conduct our research safely since we have used some toxic materials and high temperature furnaces at EBU1. All of our fabrication was carried out in Nano3 facility. Nano3 staffs maintained the cleanroom very well and they are also very flexible upon our request. I would like to thank Dr. Bernd Fruhberger and Dr. Maribel Montero and all other staff members in nano3.

Outside the lab, I have received many help from Keio university alumni group (Mita-kai). I would like to express my greatest gratitude to them, especially late Yoko Onaka, Jun Onaka, Kaori Hashimoto, Yuko Wilde, Hiroyuki Hakozaki. Masao Nishikawa, Shumon Koga and prof. Kanetaka Maki.

I have survived in Ph.D program with many friends at UCSD. I sometimes shared difficulties with them and they kindly helped in many aspects. I would like to thank all of my friends especially, Ahmed Youuset, Weichuan Yao, Dr. Lujian Yan, Iftikar A. Niaz and Dr. Namseok Park.

I would like also to acknowledge financial support from the Material Science and Engineering Program especially first year and last two quarter for the fellowships and National Science Foundation for the research grant.

Last but not the least, I would like to express my deep appreciation and thankfulness to my parents, Michiharu Tanaka and Ritsuko Tanaka, my sister Yuko Yasue and to my grandparents, Etsuko Tanaka, late Tomeichi Tanaka, late Katsumi Miura and late Shizue Miura. I have lost three grandparents after I came to US and I am very sorry that I could not attend their funerals. However, I am sure they keep watching me from heaven now and in the future. All of their support and continual encouragement have made me persevere in some difficult situations through my Ph.D.

The list does not mean to be exhaustive and I would like to thank all other people who have helped me but are not mentioned above.

xvi

Most of chapter 2 was published in Scientific Reports 2015. A. Tanaka, R. Chen, K. L.

Jungjohann and S. A. Dayeh. The dissertation author is the first author of this paper.

Most of chapter 3 was published in Advanced Material 2017. A. Tanaka, W. Choi, R. Chen

and S. A. Dayeh,. The dissertation author is the first author of this paper.

Most of chapter 4 was published in *Journal of Applied Physics* 2019. A. Tanaka, W. Choi, R. Chen, R. Liu, W. M. Mook, K. L. Jungjohann, P. K. L. Yu and S. A. Dayeh. The dissertation author is the first author of this paper.

## VITA

| 2013      | Bachelor of Science, Applied Physics and Physico-Informatics |  |  |  |

|-----------|--------------------------------------------------------------|--|--|--|

|           | Keio University, Japan                                       |  |  |  |

| 2013-2019 | Research Assistant, University of California San Diego       |  |  |  |

| 2015      | Master of Science, Materials Science and Engineering         |  |  |  |

|           | University of California San Diego                           |  |  |  |

| 2019      | Doctor of Philosophy, Materials Science and Engineering      |  |  |  |

|           | University of California San Diego                           |  |  |  |

# PUBLICATIONS

## Journal papers (3 first-authored, 9 co-authored)

- 1. <u>A. Tanaka,</u> W. Choi, R. Chen, R. Liu, W. M. Mook, K. L. Jungjohann, P. K. L. Yu and S. A. Dayeh, "Structural and Electrical Characterization of Thick GaN layers on Si, GaN, and Engineered Substrates", **Journal of Applied Physics** 125, 082517 (2019).

- <u>A. Tanaka</u>, W. Choi, R. Chen and S. A. Dayeh, "Si Complies with GaN to Overcome Thermal Mismatches for the Heteroepitaxy of Thick GaN on Si", Advanced Materials 29, 1702557 (2017).

- 3. <u>A. Tanaka,</u> R. Chen, K. L. Jungjohann and S. A. Dayeh, "Strong geometrical effects in submillimeter selective area growth and light extraction of GaN light emitting diodes on sapphire", **Scientific Reports** 5, 17314 (2015).

- 4. M. Ganji, L. Hossain, A. Tanaka, M. Thunemann, E. Halgren, V. Gilja, A. Devor, S. A. Dayeh, Advanced Healthcare Materials 7 (22), 1800923 (2018).

- 5. L. Ferrari, J. ST Smalley, H. Qian, <u>A. Tanaka</u>, D. Lu, S. A. Dayeh and Y. Fainman, Z. Liu, ACS Photonics 5, 3557 (2018)

- M. Ganji, E. Kaestner, J. Hermiz, N. Rogers, <u>A.Tanaka</u>, D. Cleary, S. Lee, J. Snider, M. Halgren, G. Cosgrove, B. S. Carter, D. Barba, I. Uguz, G. G. Malliaras, S. S. Cash, V. Gilja, E. Halgren and S. A Dayeh, Advanced Functional Materials 28, 1700232 (2018).

- M. Ganji, <u>A. Tanaka</u>, V. Gilja, E. Halgren and S. A. Dayeh, Advanced Functional Materials 27, 1703019 (2017).

- R. Liu, R. Chen, A. T. Elthakeb, S. H. Lee, S. Hinckley, M. L. Khraiche, J. Scott, D. Pre, Y. Hwang, <u>A. Tanaka</u>, Y. G. Ro, A. K. Matsushita, X. Dai, C. Soci, S. Biesmans, A. James, J. Nogan, K. L. Jungjohann, D. V. Pete, D. B. Webb, Y. Zou, A. G. Bang and S. A. Dayeh, Nano Letters 17, 2757 (2017).

- 9. M. Ganji, A. T. Elthakeb, <u>A. Tanaka</u>, V. Gilja, E. Halgren and S. A. Dayeh, Advanced Functional Materials 27, 1703018 (2017).

- M. Ganji, E. Kaestner, J. Hermiz, N. Rogers, <u>A. Tanaka</u>, D. Cleary, S. H. Lee, J. Snider, M. Halgren, G. R. Cosgrove, B. S. Carter, D. Barba, I. Uguz, G. G. Malliaras, S. S. Cash, V. Gilja, E. Halgren and S. A. DayehAdvanced Functional Materials, 1700232 (2017).

- I. Uguz, M. Ganji, A. Hama, <u>A. Tanaka</u>, S. Inal, A. Youssef, R. M. Owens, P. P. Quilichini, A. Ghestem, C. Bernard, S. A. Dayeh and G. G. Malliaras, Advanced Healthcare Materials 5 (24), 3094 (2016).

- S. Dayeh, <u>A. Tanaka</u>, W. Choi and R. Chen, "Strain Engineered Crack-Free GaN on Si for Integrated Vertical High Power GaN Devices with Si CMOS", ECS Transactions 75, 711 (2016).

#### Patents(2 co-authored)

- S. A. Dayeh, R. Chen, S. Lee, R. Liu, Y. Ro, <u>A. Tanaka</u>, Y. Hwang, "ADDRESSABLE VERTICAL NANOWIRE PROBE ARRAYS AND FABRICATION METHODS", US Patent App. 16/069,783 (2019).

- S. A. Dayeh, Y. Ro, N. Park, <u>A. Tanaka</u>, S. Vishniakou, A. Youssef, J. Buckwalter and C. Levy, "MONOLITHIC THIN FILM ELEMENTS AND PERFORMANCE ELECTRONICS, SOLAR POWERED SYSTEMS AND FABRICATION", US Patent App. 15/556,542 (2018).

# CONFERENCES

## **Oral Presentations**

- 1. MRS Fall Meeting & Exhibit "Heteroepitaxy of Thick GaN layers on Si and Improvement of electrical/Material Characteristics by Defect Annihilation", November 2018 (<u>MRS graduate</u> <u>student silver award</u>)

- 2. 60th Electronic Materials Conferences "Structural and Electrical Characterization of Defect Annihilation in Thick GaN layers on Si, GaN, and CTE Matched Substrates", **June 2018**

- Compound Semiconductor Week 2018 "Si Complies with GaN to Overcome Thermal Mismatches for the Heteroepitaxy of Thick GaN on Si", May 2018 (<u>Best student paper</u> <u>award</u>)

- 4. 59th Electronic Materials Conferences "Selective Area Growth and Characterization of over 15um thick Vertical GaN Diodes on Si", **June 2017**

- 15th International Conference on Advanced Materials "When GaN and Si Tango, Thermal Mismatches are Overcome for Thick GaN- on-Si Vertical Power Devices", August 2017 (Award for Encouragement of Research)

- **6.** 58th Electronic Materials Conferences "Strain Engineering for over 10 μm Thick Crack-Free GaN Growth on Si for High Power Applications", **June 2016**

- Lawrence Symposium on Epitaxy "Beyond 10 μm Thick Crack-Free GaN Growth on Si for High Power Device Application", February 2016

- 8. 43rd Conference on the Physics & Chemistry of Surfaces & Interfaces "Beyond 10 μm Thick Crack-Free GaN Growth on Si for High Power Device Application", January 2016

- 9. 47th International Conference of Solid State Devices and Materials "Beyond 10 μm Thick Crack-Free GaN Growth on Si for High Power Device Application", **September 2015**

- **10.** Two presentation: 57th Electronic Materials Conferences "Beyond 10 μm Thick Crack-Free GaN Growth on Si for High Power Device Application" and "Size Effects on the Selective Area Growth of GaN on Sapphire", **June 2015**

## **Poster Presentations**

- 1. Research Expo at UCSD "Structural and Electrial Characterization of Defect Annihilation in Thick GaN layer on Si, GaN and CTE Matched Substrates", **April 2018**

- 2. 4<sup>th</sup> C-DEN workshop "Growth and Integration Aspects of GaN on GaN, Si, and Ceramic Substrates and their structural and Electrical Characteristics", **May 2018**

- 3. UCSD-NSYSU Bilateral Symposium "When GaN Tangoes with Si, Thermal Mismatches are Overcome for Thick GaN-on-Si Vertical Power Device", **November 2017**

- 4. Research Expo at UCSD "Beyond 10 μm Thick Crack-Free GaN Growth on Si for High Power Device Application", **April 2015**

# FIELD OF STUDY

Major Field: Materials Science and Engineering

Professor Shadi A. Dayeh

#### **ABSTRUCT OF THE DISSERTATION**

Heteroepitaxial Thick GaN Layers and Vertical High-Power Devices by Selective Area MOCVD

Growth

by

Atsunori Tanaka

Doctor of Philosophy in Materials Science and Engineering University of California San Diego, 2019 Professor Shadi A. Dayeh, Chair

Gallium nitride (GaN) is now widely used in commercial white Light Emitting Diodes (LEDs) thanks to the emergence of high-brightness GaN blue LEDs in 1990s. In addition to its application in solid-state lighting, GaN has been also vowed as a strong contender for next-generation high power and frequency devices due to its high critical electric field (3.3 MV/cm) and high mobility of the 2-dimensional electron gas (2DEG) at the aluminum gallium nitride

(AlGaN)/GaN interface. Lateral AlGaN/GaN high-electron-mobility-transistors (HEMTs) have been available as commercial off-the-shelf devices since 2005. However, with the demand for even higher power at reduced chip area and cost and with better thermal management at high currents, vertical device architectures have emerged as the chosen structure to meet these demands.

But vertical devices that can hold high power require thick and high quality GaN layers. Recent developments of bulk GaN substrate growth technologies allowed vertical GaN device with thick drift layer to be more feasible. However, GaN substrate technology is challenged with cost, reliability and uniformity issues even at the currently commercially available 2" (diameter) substrates. Therefore, GaN vertical power devices on cheap substrates without compromising the GaN material quality remains to be of great interest. Si substrates with their fab-scale integrated circuit technology can propel the development of commercial vertical high power GaN devices. The biggest challenge for realizing thick GaN layers on Si to hold high voltage in the vertical direction is the large thermal and lattice mismatch between GaN and Si that leads to cracking of the GaN layers beyond only a few micrometers.

In major part of this dissertation, we will focus on the epitaxy techniques of thick crackfree GaN layers on Si by selective area growth (SAG) and the fabrication of vertical GaN switches. The epitaxy technique developed in this work resulted in crack-free thick GaN layers on Si that are of high quality with low dislocation densities and low background doping in order to sustain high breakdown voltages. The developed processes hold the potential to significantly advance the fundamental electronic materials research in power devices and their efficient system level integration.

xxiii

# Chapter 1

# Motivation and Challenges for Vertical GaN High Power Devices on Si

## **1.1 Introduction**

Modern human life and our societies are currently dependent on energy, more specifically electricity even at the personal level. Much effort has been made to implement green energies as electrical power generation for realizing a sustainable society. The energy production using renewable energies led mainly by solar cells has been attracting attention from various fields for decades. Concurrent with this development, energy losses in power conversion process by present Si-based power devices is known to be 10-20 % due to limitation in the physical properties of the Si material itself.<sup>1</sup> The energy loss in inefficient power electronic devices almost equated with the US renewable energy consumption in 2018.<sup>2</sup> Therefore, the pursuit of effective power conversion systems in parallel with renewable energy generation is equally important for enabling an energy saving society. To make drastic improvement in power conversion, it is inevitable to substitute Si with other higher performing materials and to pursue innovations at all levels of device

development and packaging of power electronics as well as at the circuit and magnetics levels of power conversion modules.

## **1.2 Background of Wide Bandgap Power Device**

#### 1.2.1 Advantages of GaN Over Si-Based Power Device

For high power and high frequency operation, the power device should have short carrier transit time  $\tau$  between the source to drain spacing *l* in switching field-effect transistor (FET) devices. On the contrary, applicable voltage becomes lowered since the electric field is inversely proportional to the spacing, which results in lowering the breakdown voltage. The breakdown voltage for impact ionization can be expressed using critical electric field,  $E_c$ ,<sup>3,4</sup>

$$B_V = E_c \cdot l \tag{1-1}$$

The cutoff frequency, which is the frequency at which the enegy (Gain) of the system begins to reduce, is described using carrier saturation velocity,  $v_{sat}$ ,

$$f_T = \frac{1}{2\pi\tau} = \frac{v_{sat}}{2\pi l} \tag{1-2}$$

Therefore, we can define the trade-off relationship between the breakdown voltage and the cutoff frequency,  $f_T$  as:

$$B_V \cdot f_T = \frac{E_c \cdot v_{sat}}{2\pi} \tag{1-3}$$

The eq. (1-3) is independent of the device spacing and defined only by materials properties. Therefore, this index is often used as one of the FOM (figure of merit) of the materials for high frequency devices, which is called Johnson's FOM(JFOM).<sup>5</sup>

| 2                             |                     |                     |                       |                     |

|-------------------------------|---------------------|---------------------|-----------------------|---------------------|

| Parameter                     | Silicon             | 4H-SiC              | GaN                   | Diamond             |

| $E_g$ , eV                    | 1.12                | 3.26                | 3.39                  | 5.47                |

| $E_c$ , MV/cm                 | 0.23                | 2.2                 | 3.3                   | 5.6                 |

| $\mu_n$ , cm <sup>2</sup> /Vs | 1400                | 950                 | 800/1700 <sup>a</sup> | 1800                |

| $v_{sat}$ , cm/s              | 1.0×10 <sup>7</sup> | 2.0×10 <sup>7</sup> | 2.7×10 <sup>7</sup>   | 2.0×10 <sup>7</sup> |

| $\varepsilon_r$               | 11.8                | 9.7                 | 9                     | 5.7                 |

| JFOM                          | 1                   | 20                  | 40                    | 50                  |

| BFOM                          | 1                   | 500                 | 1300/2700ª            | 9000                |

Table 1.1 Material properties of wide bandgap semiconductors in comparison with those of

Silicon<sup>4,6,7</sup>

<sup>a</sup> Significant difference between the bulk/the 2DEG

As shown in **Table 1.1**, the critical electric field,  $E_c$  is typically larger for wide band gap materials since impact ionization would not take place till the hot carriers gain the energy exceeding that of the bandgap to generate electron-hole pairs. This is why wide bandgap semiconductors are suitable for high-frequency and high-power device applications. Among these wide bandgap semiconductors, silicon carbide (SiC)-based power metal-oxide FETs (MOSFETs) have been already commercialized and started to replace some Si-based power modules in electric vehicles thanks to earlier development of SiC wafer technology. However, SiC also suffers from low effective channel mobility, which limits the FOM. GaN similarly possesses higher bandgap and therefore higher critical electric field, but what is distinctive about GaN is that it also has the highest saturation velocity of GaN materials is estimated to be higher than other wide bandgap semiconductor materials due to the relatively large energy separation of electrons between the conduction band  $\Gamma$  and L minima that reduces intervalley scattering and sustains the high electron velocity and mobility at high electric fields. Therefore, GaN is more suitable for high-frequency and high-power applications. As a reference, the normalized JFOM of Si, SiC, GaN and diamond materials are approximately 1, 20, 40 and 50 calculated from material properties in **Table 1.1** using eq. (1-3).

For vertical high voltage device, another expression for trade-off relationship between onresistance,  $R_{on}$  and  $B_V$  is suggested depending on the doping in the drift layer. The trade-off relationship can be expressed using drift region doping concentration,, in drift region and the depletion width under the critical electric field,

$$E_C = \frac{qN_d}{\varepsilon_r} W_d \tag{1-4}$$

The blocking voltage under the critical electric field is simply written as follows.

$$B_V = \frac{1}{2} E_c W_d \tag{1-5}$$

Since the resistance of the epitaxial drift layer,  $R_{on}$  is obtained using eq. (1-4) and eq. (1-5),

$$R_{on} = \frac{W_d}{q\mu_n N_d} = \frac{4B_V^2}{\mu_n \varepsilon_r E_c^3}$$

(1-6)

The denominator of the eq. (1-6),  $\mu_n \varepsilon_r E_c^3$ , is independent of device dimension and is also used as another index of power device FOM, Baliga's FOM(BFOM) of the material, which is a measure for the material dependence of the on-resistance of unipolar devices.<sup>8</sup> The normalized BFOMs of Si, SiC, GaN and diamond materials are approximately 1, 500, 1300 and 9000 calculated from **Table 1.1.**  Thus, GaN-based devices have desirable properties for the high-power amplification in microwave and millimeter-wave frequency range as well as vertical high-voltage devices that significantly outperform Si-based power devices. According to calculated JFOM and BFOM, diamond seems to possess superior material properties to GaN but the epitaxy of diamond is still developing, and the control of the conductivity in diamond remains to a fundamental issue.<sup>9</sup> Therefore, GaN is today the front contender for next generation high power electronics.

#### 1.2.2 Pros and Cons of Lateral and Vertical Power Devices

Similar to the material selection for high power devices, device architecture is also important to bring out full potential of materials. **Figure 1.1** shows the two typical device architectures for high power device applications. Today, lateral AlGaN/GaN HEMT devices are already in market and used for RF device applications. The main advantage of the lateral devices is that they can be easily integrated onto Si substrate by epitaxial growth since the GaN thickness does not have to be too thick to increase the breakdown voltage and is traditionally accomplished by increasing the lateral gate-to-drain separation. However, increasing the gate-to-drain distance impairs transit time, as shown in eq. (1-2) and also chip size increases with breakdown voltage in lateral devices. Thus, the lateral architecture is suitable for high frequency devices but for very high breakdown voltage, the device structure needs to be modified.

**Figure 1.1** Schematic illustration of (a) lateral AlGaN/GaN HEMT and (b) GaN current-aparture-vertical-electron-transistor(CAVET).

**Figure 1.1 (b)** shows GaN vertical power device structure, where the current flows vertically from the source and is extracted by the drain contact at the bottom of wafer. With this device architecture, the voltage is held across the film and the breakdown voltage can be increased simply by increasing the thickness of the drift layer without compromising the chip area. Also the vertical current conduction alleviates the current collapse which remains a challenge in GaN HEMT devices due to current conduction near the interface of AlGaN/GaN.<sup>10</sup> Therefore, the vertical architecture is more suitable for high voltage and high current application. The challenge, however, is that the growth of sufficiently thick epitaxial GaN film on Si is extremely difficult, as will be discussed in section 1.3.1.

#### **1.2.3** Requirement for Vertical Power Device

In vertical devices, to simultaneously enable a low on-resistance, fast switching, and high breakdown voltage, the drift layer n-type doping has to be low at a level around  $1 \times 10^{16}$  cm<sup>-3</sup> or lower and has to be sufficiently thick. **Figure 1.2** shows relationship between doping concentration and breakdown voltage as a function of drift layer thickness.<sup>11</sup> It can be noted that the breakdown voltage cannot be larger than 120 V if the carrier concentration is higher than  $1 \times 10^{17}$  cm<sup>-3</sup> regardless of the thicknesses of the drift layer. This is because the strong electric field needs to be held across the thickness and the depletion region thickness decreases with impurity concentrations.

**Figure 1.2** Breakdown voltage vs drift region doping concentration for each drift layer thickness from 1 to 100 µm.<sup>11</sup>

The breakdown voltage is typically chosen to be as twice as high than maximum voltage of the high voltage module. For example, electric vehicles (EVs) use many power modules such as DC-DC boost converter to drive the main motor at maximum voltage of 650V which requires the breakdown voltage to be higher than 1.25 kV. A compressor in the air conditioner is driven by an inverter with the battery voltage of 200–300V which requires 400-600 V of breakdown voltages. Therefore, if the GaN power modules are used in EVs, doping concentrations that are less than cm<sup>-3</sup> are required. In addition, for breakdown voltage devices higher than higher than 1kV, the thickness has to be more than 10  $\mu$ m. Both of these requirements are very challenging for heteroepitaxial GaN and are the main focus of this dissertation.

#### **1.3** Challenges for GaN Vertical Power Device on Si

As discussed in section 1.2.3, GaN high power vertical devices require (i) thicknesses greater than at least 10  $\mu$ m to hold 1kV and (ii) carrier concentration lower than 1×10<sup>16</sup> cm<sup>-3</sup> to provide sufficient depletion layer thickness to hold the voltage. Recent trend for GaN high power devices are the use of bulk GaN substrate thanks to the development of many wafer growth techniques.<sup>12–14</sup> The dislocation density of the GaN wafer is now becoming lower than 10<sup>6</sup> cm<sup>-2</sup> and the subsequent growth of GaN drift layers by MOCVD enabled very thick and low carrier concentration GaN for vertical power devices.<sup>15,16</sup> However, as shown in **Table 1.2**, the cost of bulk GaN is still 1000 times higher than Si which is still very expensive for GaN to be employed in utility tools. Therefore, integration of GaN to cheap substrates is the long-cherished goal for the power device community.

In this section, we will discuss the fundamental issues of GaN-on-Si hetero-integration for meeting the vertical power device requirements.

| Gurv properties.         |          |                  |          |                  |

|--------------------------|----------|------------------|----------|------------------|

| Substrate                | Bulk GaN | 4H-SiC           | Sapphire | Silicon          |

| Lattice mismatch         | none     | +3.5%            | -16%     | -17%             |

| Thermal mismatch         | none     | +33%             | -25%     | +116%            |

| Electrical resistance    | low      | low <sup>a</sup> | $\infty$ | low <sup>a</sup> |

| Thermal resistance       | same     | 0.3 <sup>a</sup> | 3        | 0.9              |

| Available wafer size     | 2"(3")   | 4"(6")           | Up to 8" | any              |

| Cost, \$/cm <sup>2</sup> | 100      | 10               | 1        | 0.1              |

Table 1.2 Implications of the usual substrate materials for the GaN-epitaxy (data relative to the GaN properties <sup>6</sup>

<sup>a</sup> Only non-conductive interface for successful heteroepitaxy of GaN

#### 1.3.1 Thickness limitation due to Thermal Mismatch Between GaN and Si

Si is the most technically developed wafer and is also available with cheap price in market. Therefore, the ultimate goal is always to integrate newly materials on the Si substrate. The MOCVD growth of GaN on Si has been extensively studied and many issues were solved such as melt backing, which is caused by strong reaction between Ga and Si at high temperature, and lattice mismatches.<sup>17</sup> However, as shown in **Table 1.2**, a huge difference in coefficient of thermal expansion(CTE) between GaN and Si (+116% relative to the GaN) results in severe cracking in the film if the thickness exceeds 5 µm on top of Si<sup>17</sup> which is not thick enough for high voltage device applications.

The typical approach to overcome the mismatch is using well optimized AlGaN/AlN buffer layer to intentionally induce compressive stress to the film at the growth temperature. Once the growth is finished at tempeatures exceeding 1000 °C, as the whole GaN-on-Si system cools down, the GaN film experiences tensile stress due to the CTE mismatch. As a result, the residual stress at the room temperature can be close to initial values due to the intentionally introduced and stress-compensating layers. Raghavan and Redwing summarized the relationship between stress and thickness under different buffer layer conditions. (**Figure 1.3**).<sup>18</sup> They achieved crack-free 1  $\mu$ m thick GaN on Si with using a graded 1  $\mu$ m thick AlGaN buffer. However, achieving a thickness greater than 10  $\mu$ m is very challenging with this technique.

**Figure 1.3 (a)** Stress in GaN film as a fuction of the thickness. The AlGaN buffer layer thickness decrease the increment of tensile stress generation. **(b)** Critical thickness of GaN for cracking as a function of buffer layer thickness.<sup>18</sup>

Another alternative to integrate GaN on Si is to grow the thick GaN film on a different substrate (donor) and to perform wafer bonding to a host Si substrate. Misky et al demonstrated a successful lift-off of GaN film from sapphire substrate using laser excitation.<sup>19</sup> The GaN and sapphire were separated due to the thermal decomposition of GaN at the laser focal point (typically the GaN/sapphire interface) and the GaN film is transferred to silicone elastomer. This process can also be used for producing a free standing GaN wafer and they succeeded in lift-off of 300 µm GaN from the sapphire substrate. However, since this is a physical lift off from the sapphire wafer, it impairs surface condition of GaN which will be extremely important for high power applications.

**Figure 1.4** Process sequence for the laser lift off of 2" GaN membranes. (a) Laser lift-ff of the GaN film from sapphire; (b) sapphire removal; (c) deposition of a  $\sim$ 3mm thick layer of thermoplastic adhesive at 120 °C; (d) peel-off of the silicone elastomer.<sup>19</sup>

Selective area growth(SAG) technique has also been used for GaN device application especially for LEDs. SAG is carried out typically by depositing a dielectric layer followed by making openings in the region where GaN is to be grown. Because the area of GaN is smaller and continuous over the whole wafer, wafer bowing effect due to thermal mismatch can be minimized in SAG GaN. Kei-Mei Lau et al have demonstrated using SAG a 2 µm thick crack free GaN blue LED in an area of 300  $\mu$ m  $\times$  300  $\mu$ m on Si.<sup>20</sup> Honda et al. reported 1.5  $\mu$ m thick crack free SAG GaN on Si with 200  $\mu$ m × 200  $\mu$ m.<sup>21</sup> They observed cracking in 500  $\mu$ m × 500  $\mu$ m window for the same thickness of GaN, which indicates that the critical thickness of crack free GaN is dependent on the SAG GaN area. However, again these thicknesses are still much smaller than that required for vertical power devices. Despite these advances, it was still very difficult to integrate over 10 µm GaN on Si without introducing damage on the surface. However, among these techniques, SAG has not been extensively studied especially for device applications beyond those for LEDs. One interesting observation that we noticed through these literature reviews is that the crack formation of SAG GaN film generally nucleated at the corner of square widows which have been extensively used in SAG GaN growth in previous work (Figure 1.5 and 1.6). This observation motivated us to revisit the SAG mask shapes which are optimal for minimizing stress at the SAG interface (Chapter 3). Therefore, in this dissertation, we focus on SAG GaN to achieve thick and crack free GaN on Si to meet the high-power device requirements.

**Figure 1.5 (a)** Microscope image of as-grown LEDs layer on patterned Si substrate. **(b)** Top-view SEM image of GaN on patterned Si substrate.<sup>20</sup>

**Figure 1.6** Microscope image of SAG GaN/AlN/Si. (a) GaN film grown without grid mask. (b) GaN grown on 500  $\mu$ m wide square windows with 200  $\mu$ m wide masks. (c) GaN grown on 200  $\mu$ m square windows with 10  $\mu$ m wide masks.<sup>21</sup>

#### **1.3.2** Unintentional Doping of GaN in MOCVD and Selective Area Growth (SAG)

Similar to the thickness, the carrier concentration in power device applications is extremely important because it affects both of device on- and off-characteristics. For GaN growth, unintentional doping (UID) of GaN is a very well-known issue and the origin still has been under investigation. Because of the UID of GaN, MOCVD grown GaN is always n-type doped at a range between  $1 \times 10^{15}$  cm<sup>-3</sup> to  $1 \times 10^{18}$  cm<sup>-3</sup> depending on the growth conditions and substrates. In 1960s, it was believed that n-type doping was associated with nitrogen vacancies in GaN because of the vapor pressures of nitrogen required to stabilize GaN at high temperatures.<sup>22</sup> By early 1980s, Seifert et al. showed that the carrier concentration is dependent on oxygen impurities in nitrogen sites in GaN, O<sub>N</sub>, and it could be reduced by improving the purity of the NH<sub>3</sub> source material.<sup>23</sup> Later, Neugebauer and Van de Walle argued using first-principles calculations that the nitrogen vacancies in GaN cannot explain the carrier concentration present in unintentionally doped GaN film that was higher than 10<sup>18</sup> cm<sup>-3</sup>.<sup>24</sup> They concluded that the source of high carrier concentration is from Si and O impurities incorporated during GaN growth. Today, the origin of the unintentional doping is believed to be associated with Si and O impurities either from the chamber, source gases or substrate materials. For even decreasing the carrier concentration lower than  $1 \times 10^{16}$  cm<sup>-3</sup>, codoping technique is used to compensate the donor type impurities with acceptor type impurities such as carbon or iron.<sup>25,26</sup> However, one needs to be careful of the concentration of the carbon impurities since it also increases the leakage current.<sup>27</sup>

UID in SAG GaN is more severe and complicated because  $SiO_2$  and  $SiN_x$  is typically used as growth masks and decomposed at high growth temperature. In selective area growth, the source of impurities is typically attributed to (i) impurities incorporated from the regrowth interface after opening  $SiO_2$  window<sup>28</sup>, (ii) diffusion of Si and O atoms from the SAG mask or substrate.<sup>29–34</sup> If only these two are the source of impurities in SAG GaN, increasing GaN thickness should result in low carrier concentration at the surface of GaN since both of the sources are confined near the regrowth interfaces.

Thus, we can assume that increasing thickness of GaN-on-Si would also benefit lowering carrier concentration of the GaN which are desirable for vertical power devices.

#### **1.4** Overview of the Dissertation

The ultimate goal of the work conducted for the preparation of this dissertation is to fabricate GaN vertical power devices on Si with the drift layer thickness exceeding 10  $\mu$ m, which may also result in low carrier concentration of the film due to reduction of impurity incorporations.

In chapter 2, we discuss systematic mechanistic studies of SAG GaN. The growth mask with different spacings and diameters enabled us to study geometrical effects on SAG GaN growth thickness, facet evolution and lateral growth rate. The chapter is concluded with the application of SAG GaN technique to enhance light extraction of GaN-based LEDs.

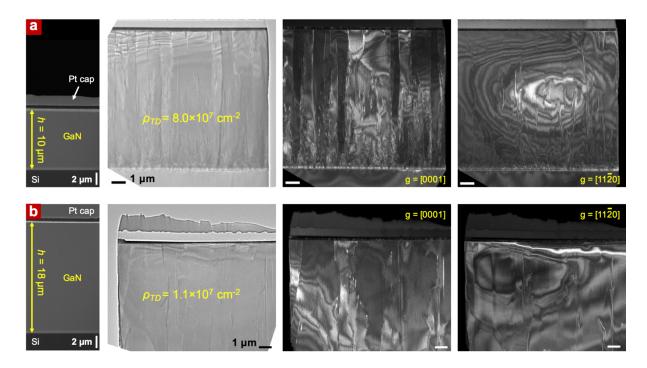

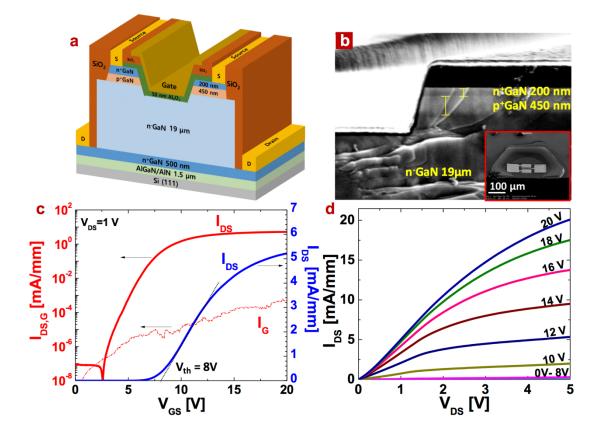

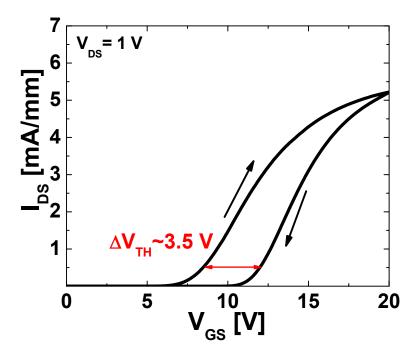

Chapter 3 documents the main results of this dissertation in which we discuss approaches to achieve thick GaN on Si using the knowledge acquired from the chapter 2. We associated the cracking mechanism in SAG GaN-on-Si to hexagonal growth facet evolution and strain-sharing with crack-planes and successfully grew 19 µm thick GaN-on-Si. The thick growth of GaN also helped annihilate threading dislocations and enabled GaN vertical metal-semiconductor-insulator-FET (MISFET) for the first time on a Si substrate.

In chapter 4, we performed additional systematic experiments to study phenomenon of dislocation annihilation as a function of GaN thickness on different substrates, namely GaN, Si

and QST. The systematic experiments revealed that the number of dislocations reduced with thicknesses. We fabricated vertical Schottky diodes on all substrate types and we achieved 400 V breakdown voltage on the QST substrate. We found that the background carrier concentration was not dependent on the thickness and was influenced by the placement location in the SAG pattern. At the time of writing of this dissertation, the control over the background concentration in SAG remains to be a challenge and further studies need to be conducted to understand the origin of impurities in SAG GaN.

This dissertation covers critical aspects of the GaN research from development of material growth to the fabrication and characterization of test device structures and to the fabrication and analysis of fundamental device properties in GaN devices.

#### 1.5 References

- <sup>1</sup> E. Gurpinar and A. Castellazzi, IEEE Trans. Power Electron. 1 (2015).

- <sup>2</sup> U.S. Energy Information Administration (EIA), (2019).

<sup>3</sup> M. Meneghini, G. Meneghesso, and E. Zanoni, editors , *Power GaN Devices* (Springer International Publishing, Cham, 2017).

<sup>4</sup> Nando Kaminski, in 2009 13th Eur. Conf. Power Electron. Appl. ([IEEE], 2009).

<sup>5</sup> E. Johnson, in *IRE Int. Conv. Rec.* (Institute of Electrical and Electronics Engineers, n.d.), pp. 27–34.

<sup>6</sup> N. Kaminski and O. Hilt, IET Circuits, Devices Syst. 8, 227 (2014).

<sup>7</sup> C.J.H. Wort and R.S. Balmer, Mater. Today 11, 22 (2008).

<sup>8</sup> B.J. Baliga, IEEE Electron Device Lett. **10**, 455 (1989).

<sup>9</sup> S. Yamasaki, T. Makino, D. Takeuchi, M. Ogura, H. Kato, T. Matsumoto, T. Iwasaki, M. Hatano,

M. Suzuki, S. Koizumi, H. Ohashi, and H. Okushi, in 2013 25th Int. Symp. Power Semicond. Devices IC's (IEEE, 2013), pp. 307–310.

<sup>10</sup> A.S.A. Fletcher and D. Nirmal, Superlattices Microstruct. **109**, 519 (2017).

<sup>11</sup> T. Kachi, Jpn. J. Appl. Phys. 53, 100210 (2014).

<sup>12</sup> K. Fujito, S. Kubo, H. Nagaoka, T. Mochizuki, H. Namita, and S. Nagao, J. Cryst. Growth **311**, 3011 (2009).

<sup>13</sup> D. Ehrentraut, R.T. Pakalapati, D.S. Kamber, W. Jiang, D.W. Pocius, B.C. Downey, M. McLaurin, and M.P. D'Evelyn, Jpn. J. Appl. Phys. **52**, 08JA01 (2013).

<sup>14</sup> T. Iwahashi, F. Kawamura, M. Morishita, Y. Kai, M. Yoshimura, Y. Mori, and T. Sasaki, J. Cryst. Growth **253**, 1 (2003).

<sup>15</sup> R. Li, Y. Cao, M. Chen, and R. Chu, IEEE Electron Device Lett. 37, 1466 (2016).

<sup>16</sup> T. Oka, T. Ina, Y. Ueno, and J. Nishii, in 2016 28th Int. Symp. Power Semicond. Devices ICs (IEEE, 2016), pp. 459–462.

<sup>17</sup> A. Dadgar, T. Hempel, J. Bläsing, O. Schulz, S. Fritze, J. Christen, and A. Krost, Phys. Status Solidi **8**, 1503 (2011).

<sup>18</sup> S. Raghavan and J. Redwing, J. Appl. Phys. **98**, 023515 (2005).

<sup>19</sup> C.R. Miskys, M.K. Kelly, O. Ambacher, and M. Stutzmann, Phys. Status Solidi 1627 (2003).

<sup>20</sup> B. Zhang, H. Liang, Y. Wang, Z. Feng, K.W. Ng, and K.M. Lau, J. Cryst. Growth **298**, 725 (2007).

<sup>21</sup> Y. Honda, Y. Kuroiwa, M. Yamaguchi, and N. Sawaki, Appl. Phys. Lett. 80, 222 (2002).

<sup>22</sup> T. Zhu and R.A. Oliver, Phys. Chem. Chem. Phys. 14, 9558 (2012).

<sup>23</sup> W. Seifert, R. Franzheld, E. Butter, H. Sobotta, and V. Riede, Cryst. Res. Technol. 18, 383 (1983).

<sup>24</sup> J. Neugebauer and C.G. Van De Walle, Adv. Solid State Phys. **35**, 25 (1996).

<sup>25</sup> S. Heikman, S. Keller, S.P. DenBaars, and U.K. Mishra, Appl. Phys. Lett. 81, 439 (2002).

<sup>26</sup> D.. Koleske, A.. Wickenden, R.. Henry, and M.. Twigg, J. Cryst. Growth 242, 55 (2002).

<sup>27</sup> Y. Cao, R. Chu, R. Li, M. Chen, R. Chang, and B. Hughes, Appl. Phys. Lett. 108, 062103 (2016).

<sup>28</sup> F. Yang, Y. Yao, Z. He, G. Zhou, Y. Zheng, L. He, J. Zhang, Y. Ni, D. Zhou, Z. Shen, J. Zhong, Z. Wu, B. Zhang, and Y. Liu, J. Mater. Sci. Mater. Electron. **26**, 9753 (2015).

<sup>29</sup> M. Holtz, M. Seon, T. Prokofyeva, H. Temkin, R. Singh, F.P. Dabkowski, and T.D. Moustakas, Appl. Phys. Lett. **75**, 1757 (1999).

<sup>30</sup> A. Kaschner, A. Hoffmann, C. Thomsen, F. Bertram, T. Riemann, J. Christen, K. Hiramatsu, T. Shibata, and N. Sawaki, Appl. Phys. Lett. **74**, 3320 (1999).

<sup>31</sup> M. Seon, T. Prokofyeva, M. Holtz, S.A. Nikishin, N.N. Faleev, and H. Temkin, Appl. Phys. Lett. **76**, 1842 (2000).

<sup>32</sup> J.A. Freitas, O.-H. Nam, R.F. Davis, G. V. Saparin, and S.K. Obyden, Appl. Phys. Lett. **72**, 2990 (1998).

<sup>33</sup> S. Heikman, S. Keller, S.P. DenBaars, and U.K. Mishra, Appl. Phys. Lett. 78, 2876 (2001).

<sup>34</sup> J. Sumner, R.A. Oliver, M.J. Kappers, and C.J. Humphreys, J. Appl. Phys. **106**, 104503 (2009).

### **Chapter 2**

# A Comprehensive Analysis of GaN Selective Area Growth: Size Effects and Influence on Light Extraction from GaN Light Emitting Diodes

#### 2.1 Introduction

The selective area growth (SAG) of III-V compound semiconductor materials has been studied for decades because of its numerous advantages in controlling the growth structure and morphology.<sup>1–6</sup> Most notably, SAG allows the reduction of threading dislocations at the grown surface by trapping and bending with lateral overgrowth<sup>5,7–12</sup> and it allows accommodation of thermal stresses during heteroepitaxial growth.<sup>13,14</sup> The SAG of arsenide and phosphide III-V materials has been analyzed quite extensively but less studies were reported for nitride materials except for nano-scale mask openings and spacings.<sup>6,7,9,15–21</sup> The interest in submillimeter scale heteroepitaxy and SAG have witnessed recently increased interest for large scale integration of light emitting diodes (LEDs)<sup>22–24</sup> and the development of high power devices.<sup>25–31</sup> It is therefore timely to conduct detailed and systematic studies of the SAG of GaN in submillimeter scale mask

openings. The deep understanding of geometric effects for SAG is necessary for the application to versatile devices, particularly when device scaling and their array density become relevant.

In this work, we conducted SAG GaN in oxide masks in previously unexplored geometries of circular openings with 20  $\mu$ m to 450  $\mu$ m diameters and edge-to-edge spacings on a 2" c-plane sapphire wafer (**Figure 2.1**). With systematic observation by scanning electron microscopy (SEM) and thickness profilometry, we characterized the SAG GaN on sapphire both qualitatively and quantitatively using mass-transport limited growth models. To exploit the morphological control attained here at different opening diameter and spacing, we fabricated GaN/InGaN quantum well LEDs and demonstrated 2.5 times enhanced light extraction with carefully engineered structures.

**Figure 2.1** Photomask design for SAG GaN on 2 inch wafer. These arrays of circular patterns consist of 12 different edge-to-edge spacings for each of 12 different diameter dots, resulting in 144 different array patterns in total. The patterns on the photomask can fit in a single 2 inch wafer, which provides a side-by-side comparison for all investigated parameters and allows us to minimize experimental sampling errors.

#### **2.2** Experimental Details

For the growth of SAG GaN films, we utilized a 3 x 2" Thomas Swan/Axitron closecoupled showerhead (CCS) metal-organic chemical vapor deposition (MOCVD) system with trimethylgallium (TMGa) and ammonia precursors, and H<sub>2</sub> carrier gas. To circumvent surface preparation effects on nucleation in different size/spacing patterns, we first grew a 1 µm thick GaN buffer layer on a single 2-inch  $c-Al_2O_3$  (sapphire) wafer. A 200 nm thick SiO<sub>2</sub> layer was then deposited on the wafer surface by plasma enhanced chemical vapor deposition (PECVD) at 350 °C and conventional photolithography then followed in order to pattern 144 different hexagonal arrays of circular openings, which consist of combinations of 12 different mask openings and edge-toedge spacings (Figure 2.1). The mask openings and spacings in SiO<sub>2</sub> were varied from 20 µm to 450  $\mu$ m, and were etched by a diluted buffered oxide etch (BOE) with a 6:1 volume ratio of 40 % NH4OH in water to 49% HF in water. The exposed GaN surface was treated with hydrochloric acid (HCl) solution (36 - 38 %) at 60 °C for 3 min in order to remove native gallium oxides (Ga<sub>x</sub>O<sub>y</sub>).<sup>32</sup> We carried out the SAG on these wafers at a temperature of 1050 °C which was calibrated at the susceptor surface, and a chamber pressure of 100 mbar for 1 hour. A V/III ratio of 2250 was employed for the SAG, which corresponds to a planar growth rate of 1 µm/hour on 2-inch c-Al<sub>2</sub>O<sub>3</sub> (sapphire) wafer. This mask pattern allowed us to eliminate sample-to-sample fluctuations of the growth and consider only geometrical effects on GaN SAG. The morphologies of the grown structures were characterized by scanning electron microscope (SEM) and Dektak surface profilometer. In addition, the growth for different times with fixed growth conditions was conducted to observe facet evolution with time.

Post growth rate, dopant, and metal-contact optimization, and to demonstrate the engineering aspects of our geometric SAG studies, we tailored the growth structure to control the

morphologies of InGaN/GaN multiple quantum well (MQW) blue LEDs that exhibited greater light extraction effects. Their electroluminescence(EL) characteristics were determined using a DU420A-OE Andor charge coupled device (CCD) camera mounted on an Oriel instrument cornerstone 260 motorized 1/4m monochromator and using a National Instruments interface control board with Labview automated measurements. The high-resolution transmission electron microscopy (HRTEM) characterization was performed in an FEI Tecnai F30 300 kV microscope for the well-faceted and non-faceted samples for investigating the MQW structures.

#### 2.3 Generic Geometric Effects in SAG GaN on c-Sapphire

We first systematically characterized the SAG GaN with different mask openings and spacings by top-view(**Figure 2.2**) and glanced angle(**Figure 2.3**). The 45° angled-view SEM images showed strong size and spacing dependence of the vertical growth rate manifesting clear geometrical effects in the SAG GaN on sapphire at such submillimeter scales. For a given opening diameter, the overall height of the GaN structure was increased with increasing mask spacing accompanied by a significant increase in the dot edge height. A concave shaped surface morphology evolved as the mask spacing was increased. The dot edges always exhibited larger heights than the center indicating more adatom arrival and incorporation at the mask edges. Similarly, for a given spacing, the heights of the SAG GaN structure decreased with increasing the mask diameter.

**Figure 2.2** Top view SEM images of the SAG GaN structures for different mask openings (a) 80  $\mu$ m, (b) 150  $\mu$ m, (c) 350  $\mu$ m, and (d) 450  $\mu$ m for edge-to-edge spacings in the range of 20  $\mu$ m to 450  $\mu$ m.

**Figure 2.3** 45°-angled SEM images of the SAG GaN structures for different mask openings (a) 80  $\mu$ m, (b) 150  $\mu$ m, (c) 350  $\mu$ m, and (d) 450  $\mu$ m for edge-to-edge spacings in the range of 20  $\mu$ m to 450  $\mu$ m. Strong vertical growth rate enhancement was observed for all diameters and spacings.

For quantitative comparison, the heights of the grown structures were measured by surface profilometry and plotted with respect to mask dot diameters and spacings in Figure 2.4. To eliminate pattern array edge effects, we chose for our analysis the center dot from each of the 5x5 hexagonal array patterns and measured the dot height profile along with  $<1\overline{1}00>$  direction. From the fixed spacing data (Figure 2.4 (a)) we observed a remarkable growth rate difference for different dot diameters. The center height of the 40 µm diameter (referenced thereafter as µmD) dot was found to be 4 times taller than that of the 400 µmD at 20 µm spacing (referenced thereof as µmS). Edge effects are defined as growth processes that lead to strong growth rate and morphological anomalies compared to that of thin film. For example, concave-shaped surface morphology becomes prominent at larger dot diameters and larger spacings as discussed later. From Figure 2.4 (a), the edge height for the 400 µmD is twice as high as its center. For sufficiently small diameters (<80 µm), the concave-shaped surface morphologies are generally minimal and become visible for larger spacing as can be observed in Figure 2.3 (a). For dot diameters larger than 60 µm, concave-shaped surface morphology was observed as shown for the 150 µmD in Figure 2.3 (b). The flatness of the surface was improved for larger diameter dots as shown in Figure 2.3 (c) and Figure 2.3 (d).

**Figure 2.4** Surface profilometry on the grown structure with (a) fixed spacing at 20  $\mu$ m and (b) fixed diameter at 350  $\mu$ m. The solid lines represent the measured thickness profile and dashed lines are fitted lines for 350  $\mu$ mS and 150  $\mu$ mS dots to extract the Ga adatom diffusion length. (c) The heights of the grown structures as a function of the mask diameters and (d) the inverse of the mask diameters; the inset highlights the large diameter region of the plots.

#### 2.3.1 Gallium Adatom Diffusion Length on GaN Surface

The above observations can be explained by the relative scales of pattern radii and the Ga adatom surface diffusion length on the c-plane GaN dot surface. If the Ga diffusion length is larger than the dot radius, the Ga adatom adsorbing/arriving at the edge of the dot can reach the center of the dot leading to a nearly flat dot surface. In contrast, if the Ga diffusion length is smaller than the radius of the dot, Ga adatoms impinged at the dot edge cannot make it to the dot center, resulting in nonuniformity of the dot height across its diameter. If the dot radius is much larger than the Ga adatom diffusion length, the height gradient will be limited to the edges of the dot that extend over a distance that is comparable to the Ga adatom diffusion length on the c-plane GaN surface, and the center region will be nearly flat. To extract the Ga adatom surface diffusion length, we utilize the formulation developed by Rozhavskaya et al. who considered the edge effects on the growth rate of GaN stripes and extracted Ga adatom diffusion length to be in the range of 5 μm to 24 μm.<sup>33</sup> In the 1D approximation along the diameter of a GaN dot, the solutions for the diffusion equation accounting for impinging flux and desorption of Ga adatoms from the GaN surface together with the two boundary conditions of a constant Ga adatom density at the dot center and zero density at the dot edge yield:<sup>33</sup>

$$\frac{H(x)}{H_{max}} = \frac{\sinh(R/\lambda) + (\lambda_0/\lambda)\cos[(R-x)/\lambda]}{\sinh(R/\lambda) + (\lambda_0/\lambda)\cos[R/\lambda]}$$

(2-1)

Here, *R* is the original mask dot radius,  $\lambda = \sqrt{D\tau}$  is the incorporation-limited diffusion length of Ga adatoms on the GaN surface and  $\lambda_0$  is the diffusion length on the dot side facets. For simplicity in the extraction of the diffusion lengths, we assume that the usually different diffusion length on different planes to be identical on our GaN dot top surface and sidewalls ( $\lambda = \lambda_0$ ). The measured plots with fitting curves using equation (2-1) are shown in **Figure 2.4 (b)** with corresponding extracted values listed in **Table 2.1** to be 29 µm - 35 µm. The extracted diffusion length has implications on the synergetic effects during the GaN SAG. For the same spacings and different diameters, the smaller diameter dot has a higher diffusion length. For the same diameters, the diffusion length increases with spacing. In our experiment, the growth conditions are the same such that the input molar fraction of precursors is identical. Thus, the difference in the diffusion length results from the mask geometry itself rather than the growth conditions as observed by Rozhavskaya et al. .<sup>33</sup> By changing the mask geometry, the local V/III ratio at the mask edge can change. For larger spacings, the larger collection area of Ga adatoms on the SiO<sub>2</sub> mask leads to more Ga diffusion to the growth interface and the effective V/III ratio at the mask edge decreases. Similarly, for smaller diameters, the relative ratio of the dot area to the collection area on SiO<sub>2</sub> is smaller resulting in enhanced Ga concentration at the edge and lower effective V/III ratio. Naturally, it is more likely for Ga adatoms to react with NH<sub>3</sub> when the V/III ratio is higher, which decreases the Ga adatom diffusion length. These trends agree well with those previously observed in the SAG of InGaAs.<sup>34</sup>

| Mask geometry   | Extracted diffusion<br>length (µm) |  |

|-----------------|------------------------------------|--|

| 350 µmD 150 µmS | 29                                 |  |

| 350 µmD 350 µmS | 33                                 |  |

| 80 µmD 350 µmS  | 35                                 |  |

Table 2.1 Diffusion lengths for selected different mask geometries

The surface nonuniformity became significant when the diameter of the openings were equivalent to or larger than the diffusion length of Ga on GaN surface. Therefore, this edge enhanced growth effect is specific to SAG in wide patterns. The thickness variation throughout the structure will affect the material thickness in critical regions of devices, such as in quantum wells, which can be detrimental to their performance and should be suppressed. Based on these observations, wider mask openings and tight edge-to-edge spacings would be the best-suited SAG geometries that can be utilized for attaining uniform device morphologies.

#### 2.3.2 Diameter Dependent Vertical Growth Rate

To quantitatively analyze the size-dependent vertical growth rates in SAG GaN on sapphire, we need to fully account for reactant direct impingement as well as their mass transport on both the SiO<sub>2</sub> and the GaN surfaces to the growth interface. This is customary for whisker<sup>35</sup> and nanowire<sup>36,37</sup> growth and has been employed recently in the GaN SAG.<sup>38</sup> The reactant impingements on the top surface of the opened GaN surface,  $J_{top}$ , surface diffusion length of the reactants on SiO<sub>2</sub>,  $\lambda_{sub}$ , surface diffusion of the reactants on GaN sidewall,  $\lambda_{sw}$ , and gas phase diffusion flux from the substrate and impingement on the sidewall surface,  $J_{sw}$ , all contribute to SAG GaN growth rate.<sup>38</sup> It is also important to note that the SAG occurs simultaneously normal to and parallel to the substrate surface, typically referred to as vertical growth and lateral overgrowth, respectively. For same diameter areas, the increase of lateral overgrowth is relatively small and can therefore be ignored. The lateral overgrowth rate as a function of diameter and spacing is discussed in section 2.3.4. With these considerations, the growth rate in SAG can be written as:<sup>38</sup>

$$\frac{dV}{dt} = \frac{\pi}{4} D^2 \frac{dH}{dt} = \gamma_{top} D^2 + \gamma_{sw}(t) D + \gamma_{sub}(t)$$

(2-2)

Where V is the volume of the GaN dot, H is the height, D is the diameter,  $\gamma_{top}$  is a time independent constant related to top surface impingement, and  $\gamma_{sw}$  and  $\gamma_{sub}$  are time dependent impingement and adsorption parameters and are constant in our case due to the fixed growth time of 1 hour.  $\gamma_{sw}$  in our experiment is however dependent on facet development which varies with size and spacing as deduced from **Figure 2.2** and **Figure 2.3**. Therefore, the vertical growth rate dependency should be characterized with the following equation:

$$\frac{dH}{dt} \propto \gamma_{top} + \frac{\gamma_{sw}(t)}{D} + \frac{\gamma_{sub}(t)}{D^2}$$

(2-3)

In **Figure 2.4 (c)** and **Figure 2.4 (d)**, we plotted the SAG GaN dot center height as a function of mask opening diameter and inverse diameter, respectively. The fitted lines in **Figure 2.4 (c)** are proportional to  $1/D^{\beta}$  where  $1 \le \beta \le 2$ . **Figure 2.4 (d)** shows further details of the diameter dependence and its inset highlights the large diameter region where we see a transition from  $\beta = 1$  for small diameters to  $\beta = 2$  for large diameters. From equation (2-3), we can deduce that the sidewall diffusion coefficient  $\gamma_{sw}$  dependence dominates the SAG dot growth height. The larger spacing dots had heights with larger slopes ( $\beta = 1$ ) as a function of inverse diameter because the diffusion of Ga is more favorable as shown in **Table 2.1**. The systematic SEM images in **Figure 2.2** and **Figure 2.3** demonstrated that the growth facets for larger dot diameters were not well developed whereas the growth facets for smaller dot diameters were well developed for all spacings. The non-flat and not well-developed facets impede Ga adatom diffusion on the sidewall and slow down the increase in the vertical height with inverse diameter.

#### 2.3.3 Spacing Dependent Vertical Growth Rate

In addition to the strong size effects, the array edge-to-edge spacing was found to have significant influence on the vertical growth rate of SAG GaN as illustrated in Figure 2.5 (a). The smaller diameter dots exhibited two different slopes with spacing whereas the height for the larger diameter dots showed weaker yet a fixed linear increase with spacing. This can also be explained by the relative difference between the Ga diffusion length which we extracted to be  $\sim 30 \,\mu\text{m}$  on the GaN surface and the GaN dot height. When the thickness is less than 30 µm, the collection area of SAG GaN structure increased with spacings because most of the impinging Ga adatoms on the GaN dot sidewall can diffuse on the sidewall and reach the growth interface at the top GaN surface. However, when the thickness becomes larger than 30 µm, the collection area of SAG GaN structure remains fixed within 30 µm from the top surface. The fixed collection area leads to an overall reduction of the rate of increase of the height with spacing than for thinner dots. This also corroborates with our earlier discussions that for smaller dot diameters, the Ga adatom surface diffusion lengths are high due to a lower effective V/III ratio at the dot edges. This size enhanced growth rate for smaller diameters diminishes when the collection area becomes constant (Figure **2.5 (d)** leading to a transition from sharp increase of growth height with spacing to slower increase at larger spacings when the dot height exceeded  $25-30 \,\mu\text{m}$ .

**Figure 2.5** (a) Edge heights for the grown structures. (b) The lateral overgrowth lengths and (c) the facet lengths as a function of the mask spacings. The facet lengths are defined as the average length of the six sides of the grown hexagon base. (d) Schematic illustration of the collection area contributing to the vertical growth when the sidewall length is less than or equivalent to Ga diffusion length on GaN (left) and when it is larger than the diffusion length (right).

#### 2.3.4 Spacing Dependent Lateral Growth Rate, Facet Length and Facet Evolution