## **UC Santa Barbara**

#### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Discovery and Remediation of Vulnerabilities in Monolithic IoT Firmware

#### **Permalink**

https://escholarship.org/uc/item/9t6805zc

#### **Author**

Gustafson, Eric David

#### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

#### University of California Santa Barbara

## Discovery and Remediation of Vulnerabilities in Monolithic IoT Firmware

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Computer Science

by

Eric D. Gustafson

#### Committee in charge:

Professor Giovanni Vigna, Co-Chair Professor Christopher Kruegel, Co-Chair Professor Chandra Krintz

September 2020

| The Dissertation of Eric D. Gustafson is approved. |  |  |  |  |  |  |

|----------------------------------------------------|--|--|--|--|--|--|

|                                                    |  |  |  |  |  |  |

|                                                    |  |  |  |  |  |  |

| Professor Chandra Krintz                           |  |  |  |  |  |  |

|                                                    |  |  |  |  |  |  |

| Professor Christopher Kruegel Committee Co Chair   |  |  |  |  |  |  |

| Professor Christopher Kruegel, Committee Co-Chair  |  |  |  |  |  |  |

|                                                    |  |  |  |  |  |  |

| Professor Giovanni Vigna, Committee Co-Chair       |  |  |  |  |  |  |

Discovery and Remediation of Vulnerabilities in Monolithic IoT Firmware

Copyright © 2020

by

Eric D. Gustafson

#### Acknowledgements

The content of Chapter 3 is based upon work supported by the National Science Foundation under Award No. CNS-1704253, and by the Office of Naval Research under Award # N00014-17-1-2011. Additionally, this work was in part funded by a research contract with Siemens AG.

The content of Chapter 4 is based upon work supported by ONR under Award No. N00014-17-1-2011 and N00014-17-1-2513, by NSF under award numbers CNS-1718637, CNS-1704253 and CNS-1801601, by AFRL and DARPA under agreement number FA8750-19-C-0003, by the US Department of Homeland Security under agreement number FA8750-19-2-0005, and by the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement No. 850868).

Portions of this work were supported by Sandia National Laboratories, a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the U.S. Department of Energy, Sandia National Laboratories, Department of Homeland Security, Office of Naval Research, AFRL, DARPA, the U.S. Government, or the European Research Council.

#### Curriculum Vitæ

#### Eric D. Gustafson

#### Education

| 2020 | Ph.D. in Computer Science (Expected), University of California,    |

|------|--------------------------------------------------------------------|

|      | Santa Barbara.                                                     |

| 2014 | M.S. in Computer Science, University of California, Davis.         |

| 2011 | B.S. in Computer Science, California Polytechnic State University, |

|      | San Luis Obispo.                                                   |

#### **Publications**

- 1. **Abraham Clements and Eric Gustafson**, Tobias Scharnowski, Paul Grossen, David Fritz, Christopher Kruegel, Giovanni Vigna, Saurabh Bagchi, Mathias Payer. *HALucinator: Firmware Re-hosting Through Abstraction Layer Emulation*. Proceedings of the 29th USENIX Security Symposium (USENIX '20).

- 2. Eric Gustafson, Marius Muench, Chad Spensky, Nilo Redini, Aravind Machiry, Yanick Fratantonio, Aurelien Francillon, Davide Balzarotti, Yung Ryn Choe, Christopher Kruegel, Giovanni Vigna. Toward the Analysis of Embedded Firmware through Automated Re-hosting. Proceedings of the 22nd International Symposeum on Research in Attacks, Intrusions, and Defenses (RAID '19).

- 3. Shirin Nilizadeh, Hojjat Aghakhani, **Eric Gustafson**, Christopher Kruegel, and Giovanni Vigna. *Think Outside the Dataset: Finding Fraudulent Reviews using Cross-Dataset Analysis*. Proceedings of the 2019 World Wide Web Conference (WWW '19)

- 4. Machiry, Aravind, Nilo Redini, **Eric Gustafson**, Hojjat Aghakhani, Christopher Kruegel, and Giovanni Vigna. *Towards Automatically Generating a Sound and Complete Dataset for Evaluating Static Analysis Tools*. Proceedings of the NDSS Workshop of Binary Analysis Research (BAR '19).

- 5. Machiry Aravind, Nilo Redini, **Eric Gustafson**, Yanick Fratantonio, Yung Ryn Choe, Christopher Kruegel, and Giovanni Vigna. *Using Loops For Malware Classification Resilient to Feature-unaware Perturbations*. Proceedings of the Annual Computer Security Applications Conference (ACSAC '18).

- 6. Antonio Bianchi, **Eric Gustafson**, Yanick Fratantonio, Christopher Kruegel, Giovanni Vigna. *Exploitation and Mitigation of Authentication Schemes Based on Device-Public Information*. Proceedings of the Annual Computer Security Applications Conference (ACSAC '2017).

- 7. Erik Trickel, Francesco Disperati, **Eric Gustafson**, Faezeh Kalantari, Mike Mabey, Naveen Tiwari, Yeganeh Safaei, Adam Doupé, Giovanni Vigna. *Shell We Play A Game? CTF-as-a-service for Security Education*. Proceedings of the 2017 USENIX Workshop on Advances in Security Education (ASE '17)

- 8. Nilo Redini, Aravind Machiry, Dipanjan Das, Yanick Fratantonio, Antonio Bianchi, **Eric Gustafson**, Yan Shoshitaishvili, Christopher Kruegel, and Giovanni Vigna. *BootStomp: On the Security of Bootloaders in Mobile Devices*. Proceedings of the 26th USENIX Security Symposium (USENIX Security '17).

- 9. Aravind Machiry, **Eric Gustafson**, Chad Spensky, Chris Salls, Nick Stephens, Ruoyu Wang, Antonio Bianchi, Yung Ryn Choe, Christopher Kruegel, Giovanni Vigna. *BOOMERANG: Exploiting the Semantic Gap in Trusted Execution Environments*. Proceedings of the Network and Distributed System Security Symposium (NDSS '17).

#### Abstract

Discovery and Remediation of Vulnerabilities in Monolithic IoT Firmware

by

#### Eric D. Gustafson

Many recent advances in the scale, cost, and connectivity of hardware have brought about the era of the Internet of Things (IoT), in which numerous objects in our every-day lives now contain networked computing capabilities. Most notably, this has brought with it an astonishing array of new device market sectors, form factors, and use cases, which purport to make our lives easier, simpler, and safer. However, these new network-connected devices have opened a massive new attack surface for attackers to exploit, and a challenging landscape for defenders, which could undermine these benefits.

Unfortunately for analysts, the code of these new ubiquitous, low-power embedded systems increasingly utilize monolithic firmware images, in which code, libraries, and data are intermixed, without a conventional operating system or metadata needed by third-party analyses. This combines with the extreme hardware-software coupling found in firmware to create a complex software environment, that is extremely difficult to model for the purposes of conventional program analyses. This has created two significant gaps in the vulnerability discovery lifecycle: modeling of the execution environment, and patching of vulnerabilities, even without a manufacturer's help. As a result, devices with monolithic firmware have been largely ignored by academia and industry thus far.

In this dissertation, we will showcase novel techniques to help bridge the gaps in analysis capabilities between traditional programs and the monolithic firmware of deeply-embedded systems. To overcome the environment modeling problem, we will focus on re-hosting, the act of transferring a program from one execution environment to another,

typically from a hardware environment to an emulated one. Re-hosting an important prerequisite to fuzzing or symbolic execution used for vulnerability discovery, as it allows execution environments to be freely copied and scaled. we will propose two techniques: an automated approach based on observing and modeling the original device's hardware, and a semi-automatic approach based on abstracting away and modeling parts of the firmware itself. we will show how these techniques can allow us to re-host many firmware images, and can be directly used for security analyses to find both synthetic and previouslyundiscovered real-world vulnerabilities.

Finally, we will address the issue of patching monolithic firmware. While numerous steps are required for an analyst to produce a final patched firmware image, we focus on automating three critical steps: finding sources of attacker-controlled input, finding a safe location to insert a payload, and locating self-checks intended to thwart modification. We combined these techniques into a system able to produce modified firmware, and used it to correct serious safety-critical issues in three products from the medical, industrial automation, and engineering sectors.

Through both re-hosting and patching, this work completes the vulnerability lifecycle for embedded devices, and helps make our connected world safer.

# Contents

| Cı           | urric                                                            | ulum Vitae                   | V   |  |  |  |

|--------------|------------------------------------------------------------------|------------------------------|-----|--|--|--|

| $\mathbf{A}$ | bstra                                                            | ct                           | vii |  |  |  |

| 1            | Intr                                                             | roduction                    | 1   |  |  |  |

|              | 1.1                                                              | Permissions and Attributions | 9   |  |  |  |

| <b>2</b>     | Background and Related Work                                      |                              |     |  |  |  |

|              | 2.1                                                              | The Vulnerability Lifecycle  | 10  |  |  |  |

|              | 2.2                                                              | The Re-hosting Problem       | 13  |  |  |  |

|              | 2.3                                                              | Library Matching             | 20  |  |  |  |

|              | 2.4                                                              | Binary Patching              | 21  |  |  |  |

| 3            | Toward Firmware Analysis through Automated Re-Hosting            |                              |     |  |  |  |

|              | 3.1                                                              | Methodology                  | 27  |  |  |  |

|              | 3.2                                                              | Evaluation                   | 44  |  |  |  |

|              | 3.3                                                              | Discussion                   | 52  |  |  |  |

|              | 3.4                                                              | Conclusion                   | 55  |  |  |  |

| 4            | Firmware Re-Hosting through Hardware Abstraction Layer Emulation |                              |     |  |  |  |

|              | 4.1                                                              | Motivation                   | 60  |  |  |  |

|              | 4.2                                                              | Design                       | 64  |  |  |  |

|              | 4.3                                                              | Implementation               | 74  |  |  |  |

|              | 4.4                                                              | Evaluation                   | 76  |  |  |  |

|              | 4.5                                                              | Limitations and Discussion   | 91  |  |  |  |

|              | 4.6                                                              | Conclusion                   | 92  |  |  |  |

| 5            | Security Retrofitting for Monolithic Embedded Firmware           |                              |     |  |  |  |

|              | 5.1                                                              | Challenges & Goals           | 97  |  |  |  |

|              | 5.2                                                              | Methodology                  | 100 |  |  |  |

|              | 5.3                                                              | Implementation               | 111 |  |  |  |

|              | 5.4                                                              | Evaluation                   | 113 |  |  |  |

|    |       | Conclusion |     |

|----|-------|------------|-----|

| 6  | Con   | nclusion   | 126 |

| Bi | bliog | graphy     | 130 |

# Chapter 1

## Introduction

Over the last twenty years, advances in wireless networking technology and in the design of embedded systems have led to a shift in the way technology integrates with our daily lives. This movement, known as the Internet of Things (IoT), represents the elimination of the barrier between networked, interactive devices, and more mundane objects, tools, and appliances.

In the last five years, this phenomenon has become tangible to consumers, with the mass-market availability of connected devices for homes and businesses, including thermostats, lighting, physical security, and a variety of sensors. The promise of these products is to enable unprecedented convenience and utility, without the usual complexity and cost of sensing and automation. This increased functionality has been a hit with consumers, with an estimated 5.5 million IoT devices being connected every day in 2016 [1], and over 20 billion in use in 2020.

While these numbers may seem rather high, IoT does not merely describe one class of devices with the same functional or security needs, nor can the user typically achieve any benefit with only one component alone. These devices and services compose an *ecosystem*, combining the means to collect data, make decisions based on this data, and act on it, potentially in a physical manner. One device alone may provide the functionality to close a water valve through an app, and another may be able to detect when water

passes a sensor and notify the user, but only through the combination of those two with communications and logic infrastructure can the user mitigate flood damage in their home. Because the value of an IoT ecosystem is dependent on its ability to incorporate a wide array of devices, the value of a single device is also determined by which, and how many, devices and services it will integrate with. This puts the unusual burden on manufacturers to inter-operate, even without the presence of dominant IoT standards for protocols and design.

This emphasis on heterogeneity and high interconnectedness of devices has resulted in additional implications for the security and privacy of users. Instead of converging on standards, the market has continued to support a collection of protocols, frameworks, and Application Program Interfaces (APIs) as diverse as the devices themselves. Each of these brings with it its own security models, assumptions, and trade-offs, as well as a broadened networked attack surface. This close relationship with the physical world also brings deployment complications (e.g., physical location, intended use), which violate various traditional security assumptions (e.g., physical attacks, observability).

This enticing set of targets has not gone unnoticed by attackers. Security vulnerabilities located in relatively small set of devices allowed for the creation of botnets responsible for some of the largest Distributed Denial of Service (DDoS) attacks to date, targeting journalist Brian Krebs [2], DNS infrastructure used by many websites [3], and the country of Liberia [4]. This botnet leverages weak authentication and poor deployment of certain IoT devices (i.e., Internet-connected cameras) to compromise them, and direct traffic toward a target. The Common Vulnerabilities and Exposures (CVE) group, which catalogs security vulnerabilities, has blamed the rise in IoT-related vulnerabilities for a massive backlog in their workflow [5]. The European Union is even working on a law that would require IoT devices to be accompanied by a security rating [6].

Looked at from a different angle, the result of this IoT trend is that newly-commercialized

embedded systems are now in the hands of consumers, and being used in an increasing number of security and safety-critical applications. Unfortunately, in stark contrast to the desktop and mobile ecosystems, market forces have not created any de facto standard for components, protocols, or software, hampering existing program analysis approaches, and making the understanding of each new device an independent, mostly manual, time-consuming effort. At the software level, each new device comes with its unique firmware, which is purpose-built for its specific function, and may not include a conventional operating system. At the hardware level, each device includes its own unique selection of hardware, both on the board (sensors, actuators, etc.) and on the chip (bus controllers, timers, and other I/O peripherals), which combine to form the unique execution environment of the firmware.

Even with rapidly-improving software environments, developers create and test firmware almost entirely on physical testbeds, typically consisting of development versions of the target devices. However, modern software-engineering practices that benefit from scale, such as test-driven development, continuous integration, or fuzzing, are challenging or impractical due to this hardware dependency. In addition, embedded hardware provides limited introspection capabilities, including extremely limited numbers of breakpoints and watchpoints, significantly restricting the ability to perform dynamic analysis on firmware.

The situation for third-party auditors and analysts is even more complex. Manufacturing best-practices dictate stripping out or disabling debugging ports (e.g., JTAG) [7, 8], meaning that many off-the-shelf devices remain entirely opaque. Even if the firmware can be obtained through other means, dynamic analysis remains challenging due to the complex environmental dependencies of the code.

One factor that massively complicates this hardware-software dependency is the format of the firmware itself. Many devices use *monolithic binary firmware*, also know as

"blobs", which pack application code, library code, and data into one binary image, with no discernible metadata or formatting. Therefore, it is difficult for the analyst to distinguish code and data separation, function boundaries, library vs. application code, and the memory map of the execution environment, which are typical prerequisites for common program analyses.

These numerous complexities have caused significant changes in the usual lifecycle of discovering and remediating vulnerabilities found in traditional desktop and mobile software. All aspects of obtaining, analyzing, and eventually patching code have become more difficult as a result of the way hardware and firmware interact. However, the lack of standardization of execution environments (in the case of monolithic firmware, just the device's hardware) has necessitated an additional step: creating a model of this environment to enable tractable, accurate, analyses.

Firmware re-hosting—the process of enabling code to run in a different environment from which it was designed—is the primary means by which this gap can be overcome. By re-hosting the firmware into a fully-virtualized, emulated, environment, we can execute firmware at scale through the use of commodity computers, and provide more insight into the execution than is possible on a physical device [9]. Yet, heterogeneity in embedded hardware poses a significant barrier to the useful re-hosting of firmware. The rise of intellectual-property-based, highly-integrated chip designs (e.g., ARM based Systems on Chip—SoC) has resulted in an explosion of available embedded CPUs, whose various on-chip peripherals and memory layouts must be supported in a specialized manner by emulators. However, the popular open-source QEMU emulator supports fewer than 30 ARM devices. Intel's SIMICS [10] supports many CPUs and peripherals, but requires the analyst to manually construct a full model of the system at the hardware level. Worse yet, most embedded systems have other components on their circuit boards that must exist for the firmware to operate, such as sensors, storage devices, or networking components.

Emulation support for these peripherals is virtually nonexistent. Therefore, it is nearly impossible to take an embedded firmware sample and emulate it without significant engineering effort.

Current solutions allowing for the re-hosting of diverse hardware rely on a real specimen of the device, where the emulator forwards interactions with unsupported peripherals to the hardware [11, 12, 13]. Such a "hardware-in-the-loop" approach limits the ability to scale testing to the availability of the original hardware, and offers restricted instrumentation and analysis possibilities compared to what is possible in software. Other techniques [14, 15] focus on recording and subsequently replaying data from hardware, which allows these executions to be scaled and shared, but necessarily requires trace recording from within the device itself, limiting faithful execution in the emulator to just the recorded paths in the program.

Even when bugs are found, and reported, that does not guarantee that a fix will be available. A worrying trend in IoT devices is that devices are being abandoned by vendors [16, 17], or otherwise excluded from support by the vendor [18], and do not receive patches for security issues when they are found. Since embedded systems based on monolithic firmware cannot be simply updated by updating an operating system or libraries, vulnerabilities in these systems may have a much longer patch latency, due to the extra work involved in creating and verifying them. The recent Urgent/11 [19] vulnerabilities affect such a wide variety of real-time operating systems and libraries [20], that it is unclear exactly what the patching situation will be for many of these systems. Unfortunately, the increasingly safety and security critical nature of many of these devices means that users may have no choice but to patch or replace the device. In some cases, replacing the device may not be physically possible or financially practical, and users must take matters into their own hands.

Current solutions tackling binary rewriting work primarily on ELF files [21, 22, 23]. They leverage the metadata found in the files to re-arrange code, fixing code offsets and pointers. Of course, with blob firmware, this metadata is not present, and we are left with only Detours-style patching [24], in which code is inserted into an otherwise-unused space, and the instructions of the program are altered to use it. Worse yet, without metadata, and without an operating system, there is no standard source of input data to the program for a patch to make security-related decisions with. Finding the place to put code in the first place is also difficult, with no guarantees of space to insert code into, minimal onboard storage, and no easy way to determine existing content that's expendable. Finally, in order to make these systems robust, firmware will typically check their content to ensure that it is not intentionally or accidentally modified; this must be overcome before any kind of binary patching can take place. In summary, no technique exists which allows a third-party user or analyst to create patches for a monolithic firmware image without intensive, manual, firmware-specific reverse-engineering.

In this work, we will address the unique challenges preventing the security analysis and remediation of monolithic firmware images, through the use of novel re-hosting and automated program analysis techniques.

We propose to tackle the gap in environment modeling capabilities through the use of novel re-hosting techniques, allowing the virtualization of the firmware with a minimum of analyst effort. In order to help frame these approaches, we identified four aspects of an ideal re-hosting solution, which could allow it to tackle today's diverse embedded systems: A re-hosting scheme must be *virtual* to allow for scale and reduce costs; should also be *interactive*, to allow the firmware to process new input and actually withstand program analysis; should be *abstraction-less* (i.e., it should not rely on high-level concepts, such as operating systems and hardware abstraction layers) to allow the system to handle the

widest possible variety of firmware. Finally, re-hosting should be *automated*, so that the system can overcome the extreme diversity that is impractical for humans to handle. Although previous approaches to the problem are numerous, all are missing at least one of these aspects.

Automated Re-Hosting. The first approach we will present is the first to strive for this kind of idealized automated re-hosting. The technique works by observing the behavior of the original device, then modeling this behavior, creating a set of models which can be plugged into an emulator. We use the system to emulate three hardware devices, with six firmware images, and were able to successfully emulate and automatically test the firmware, and discover synthetic vulnerabilities.

While this approach has the advantage of being mostly hands-off for the analyst, there are a few challenges remaining to be solved when it comes to tackling real-world commercial devices. Aspects of these systems, such as high-frequency interrupts, Direct Memory Access (DMA), and highly-complex peripherals will confound this and similar approaches.

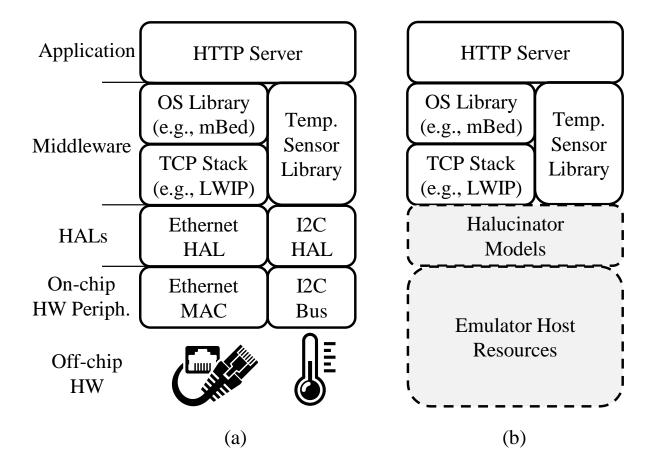

These same challenges complicate both the development and testing of firmware by device manufacturers as well. To mitigate some of these issues, and make their platforms more attractive under tight time-to-market constraints, chip vendors and various third parties provide Hardware Abstraction Layers (HALs). HALs are software libraries that provide high-level hardware operations to the programmer, while hiding details of the particular chip or system on which the firmware executes. This makes porting code between the many similar models from a given vendor, or even between chip vendors, much simpler. Application code written with HALs is therefore, by design, less tightly coupled to the hardware, even when distributed as a monolithic firmware image.

Re-hosting with High Level Emulation. To leverage this observation, the second

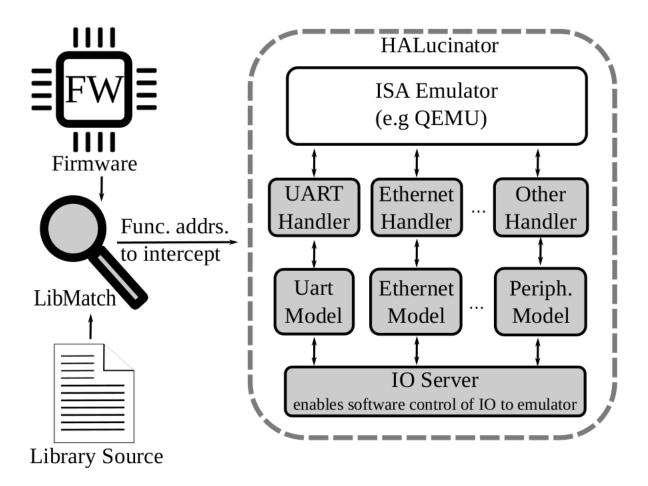

re-hosting approach applies re-hosting based on High Level Emulation (HLE), in which these hardware-facing functions are replaced with analyst-created, high-level equivalents. When working with a monolithic firmware image, the first step is to locate the libraries within the firmware using binary analysis. With the function names identified, high level handlers (e.g., written a scripting language such as Python) can be quickly created, and re-used for any firmware sample using the same libraries. While this process is neither fully automatic nor abstraction-less, we will show that this trade-off allows our prototype system, HALUCINATOR, to re-host dramatically more complex firmware than other techniques, and keeping the burden on the analyst low. Furthermore, we will show how this technique can be used to fuzz realistic firmware samples, and discover previously-unknown vulnerabilities in firmware and libraries.

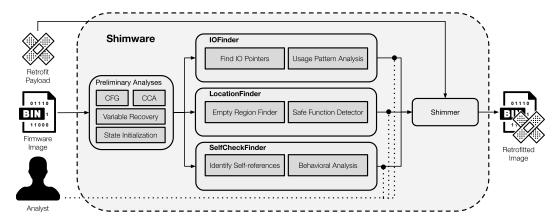

Security Retrofitting for Monolithic Firmware. In this final chapter, we explore the challenges of retrofitting monolithic firmware images with new security measures. First, we outline the steps any analyst must take to retrofit firmware, and show that previous work is missing crucial aspects of the process, which are required for a practical solution. We then automate three of these aspects—locating attacker-controlled input, a safe retrofit injection location, and self-checks preventing modification—through the use of novel automated program analysis techniques. We assemble these analyses into a system, Shimware, that is able to guide the analyst in creating a working retrofitted firmware image with a minimal amount of effort and prior knowledge of the device.

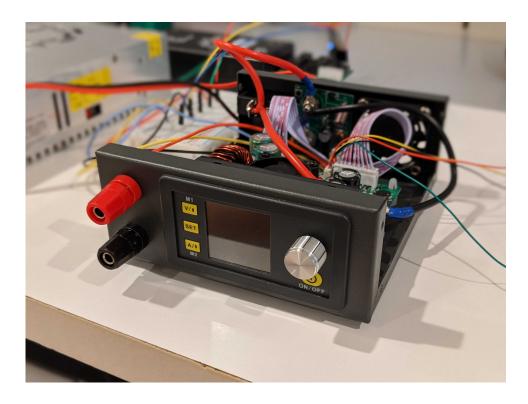

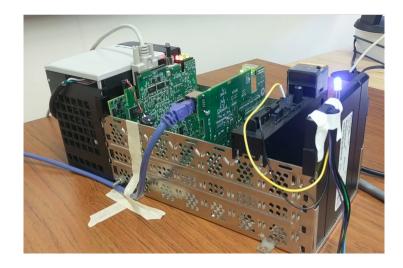

To evaluate our system, we employ both a synthetic evaluation and actual retrofitting of three case study devices: a networked bench power supply, a Bluetooth-enabled cardiac implant monitor, and a high-end programmable logic controller (PLC). Not only was our system able to identify the correct sources of input, injection locations, and self-checks, but it injected payloads to correct serious safety and security-critical vulnerabilities in these devices.

### 1.1 Permissions and Attributions

1. The content of chapter 2 is the result of a collaboration with Marius Muench, Chad Spensky, Nilo Redini, Machiry Aravind, Yanick Fratantonio, Aurelien Francillon, Davide Balzarotti, Yung Ryn Choe, Christopher Kruegel, and Giovanni Vigna, and has previously appeared in the 2019 edition of the Symposium on Research in Attacks, Instrusions and Defenses (RAID 2019).

- 2. The content of chapter 3 is the result of a collaboration with Abraham Clements, Tobias Scharnowski, Paul Grosen, David Fritz, Christopher Kruegel, Giovanni Vigna, Saurabh Bagchi, and Mathias Payer, and will appear in the 2020 edition of the USENIX Security Symposium.

- 3. The content of chapter 4 is the result of a collaboration with Paul Grosen, Ruoyu Wang, Nilo Redini, Saagar Jha, Sara Rampazzi, Kevin Fu, Christopher Kruegel, and Giovanni Vigna.

## Chapter 2

# Background and Related Work

## 2.1 The Vulnerability Lifecycle

In this section, we will frame the concepts presented in this work in the context of how vulnerabilities in software are found and fixed by analysts today. In particular we will discuss how this process differs on embedded systems, and the gaps in our analysis capabilities this creates.

Vulnerability discovery and detection efforts have become a major part of the security efforts of both device and software vendors, and third-party analysts alike. Their combined efforts can help reduce the number of severe bugs available to hostile adversaries, assuming the discovered issues are ethically reported to, and fixed by, the vendors. For third-party analysts, however, discovering new vulnerabilities is also now a lucrative business, with numerous bug bounty programs, contests, and other entities willing to provide significant financial compensation for their efforts.

Regardless of their identities or motives, the overall process used to find and fix vulnerabilities in programs can be broken down into a few key steps: obtaining the code-under-test, performing an analysis to locate potential bugs, confirming these bugs, and creating a patch. In the case of an embedded system, particularly one running a monolithic firmware image, the steps are similar, but with a dramatically higher level of

complexity and difficulty:

- 1. Obtaining Code. The analyst needs to first obtain the code-under-test. Depending on the scenario, this could be source code, or a compiled binary. For common desktop or mobile software, this step is trivial; the program to be analyzed can be simply downloaded or installed via the Internet, an app store, or some other distribution mechanism. However, the firmware of an embedded device was developed for that device only; the manufacturer may only provide the firmware through a specialized update mechanism (e.g., on the device itself, or through a companion app or software package), or in some cases, not at all. Therefore, third-party analysts have the additional tedious step of obtaining this firmware through potentially invasive means, such as attacking the device's storage chips, or interfering with the firmware update mechanism.

- 2. Environment Modeling. In order to perform a meaningful analysis, the analyst must understand or recreate the environment in which the code-under-test is run. When analyzing mobile or desktop applications, this step is generally inherent in the previous step of obtaining the code. An application designed for Android, for example, runs within Android's well-specified environment. Tools are built with the assumptions of this environment in mind, and allow any app built on top of this OS's abstraction to be quickly analyzed in a similar fashion. This is true of all program analyses; dynamic analyses need to be able to execute the program, and static analyses need to know enough about the environment to make meaningful inferences.

With embedded systems, this step is profoundly more difficult, particularly for devices based on monolithic firmware. The environment that needs to be modeled instead consists of the device's hardware, both within the CPU executing the code, and elsewhere. We explore this issue in depth in Section 2.2.

- 3. Analysis. With the environment modeled, the analyst can now examine the program for bugs. For third-party analysts, this will typically involve binary program analyses, such as fuzzing, static or dynamic taint tracking, and dynamic symbolic execution-based approaches. While these same kinds of analyses are used on embedded systems, they contain numerous new caveats. Firmware does not follow a typical pattern of taking input from or interacting with the user. Many analyses will also need to reason about interrupt events and timing, features typically handled by the operating system in normal programs.

- 4. Patching. With newly-discovered bugs in hand, the focus now turns to preventing them from being abused in the future. This typically involves the vendor re-compiling the software to create a patched version. Of course, this is similar for firmware, but the primary difference is that the device vendor completely controls the update process. Even if the vulnerability is in a library component not written by the vendor, their complicity is typically required to create updated firmware versions.

In summary, when searching for vulnerabilities in a device with a monolithic firmware, there are two major gaps in the typical lifecycle that prevent analysts from readily exploring them. Complexities in modeling the execution environment prevent execution of the code without either the original device or significant manual effort. Patching currently requires the vendor's help, given that source code and correct build environments are typically unavailable. As a result, analysts today often do not analyze monolithic firmware images, due to the immense challenges involved.

In the remainder of this chapter, we will discuss these two issues in more depth. The

following chapters will present novel approaches to both re-hosting and patching to help close these gaps.

## 2.2 The Re-hosting Problem

To deal with the plethora of software applications that need to be analyzed on desktop and mobile platforms, the security community has developed many techniques for enabling the scalable analysis of programs to find bugs and detect malice. In this section, we examine what makes embedded systems different and much less tractable to these techniques, as well as propose qualities that a system capable of analyzing arbitrary firmware must have.

Today's state-of-the-art program analysis techniques, including dynamic analysis tools such as AFL [25] or symbolic execution engines such as angr [26] or S2E [27], rely on some form of abstraction to be tractable. Dynamic approaches typically rely on virtualization to enable parallel, scalable analyses, while symbolic approaches rely on function summarization of the underlying operating system to minimize the code that they need to execute. In order to use any of these tools, the analyst must take the program out of its original execution environment, and provide a suitable analysis environment able to execute it. This is a process referred to as re-hosting.

For desktop and mobile programs, the standardization of the execution environments (e.g., commodity hardware, which consists of a relatively small number of OSes and architectures) has made this re-hosting process simpler. However, with embedded firmware, many well-established assumptions fail. For example, there may not be a general-purpose operating system designed to run arbitrary code on the device, leaving the analyst to deal with the hardware directly. This is especially true for low-power Internet of Things (IoT) devices, which are typically based on microcontroller-class CPUs that lack the ability to

run such OSes. Firmware for these devices is typically obtained in the form of a binary blob, an opaque code object containing no metadata about its contents. How this blob is handled is entirely dependent on the CPU hardware, and will vary widely from chip to chip. This also makes distinguishing between library code and device-specific code challenging. With no visible abstractions to use, the execution environment for embedded firmware is the hardware itself. We can break this hardware down into three distinct categories:

- **CPU Core.** The CPU core itself must, of course, be emulated. This includes the instruction set, but also any function able to directly alter code execution, such as the chip's primary interrupt controller.

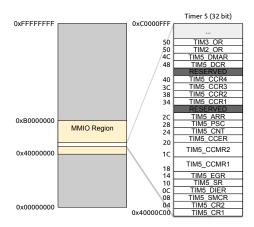

- On-Chip Peripherals. These peripherals include timers, bus controllers, serial ports, General Purpose Input and Output (GPIO), and other features typically included on the die of the CPU itself. Most CPUs expose these peripherals to the program as Memory-Mapped Input/Output (MMIO), where they are organized as a group of contiguous memory locations, that do not behave like normal memory. Each group may contain multiple locations, used for configuring, checking the status of, and exchanging data with the peripheral. An example of a typical MMIO peripheral mapping is shown in Figure 2.1. On-chip peripherals are also responsible for issuing interrupts, events that trigger asynchronous changes in control flow in response to a hardware event. More precisely, a peripheral is associated with one or more numbered interrupt "channels" or "lines"; when an interrupt occurs, the code in the firmware associated with that interrupt (known as an Interrupt Service Routine, or ISR) is executed. When, how, and why a peripheral issue interrupts are all properties of the peripheral's hardware on a particular chip, but typically includes the arrival of data, the expiration of timers, and error conditions.

Table 2.1: Excerpt of tools tackling the re-hosting problem

| Tool              | Virtual | Interactive | Abstraction-less | Automatic |

|-------------------|---------|-------------|------------------|-----------|

| Simics [10]       | ✓       | ✓           | ✓                | -         |

| FIE [28]          | ✓       | ✓           | ✓                | -         |

| Avatar [29]       | -       | ✓           | ✓                | -         |

| PROSPECT [30, 31] | -       | ✓           | -                | ✓         |

| Surrogates [32]   | -       | ✓           | ✓                | -         |

| Firmadyne [33]    | ✓       | ✓           | -                | ✓         |

| $Avatar^2$ [34]   | ✓       | ✓           | ✓                | -         |

| P2IM [35]         | ✓       | ✓           | ✓                | ✓         |

| Pretender         | ✓       | ✓           | ✓                | ✓         |

| HALucinator       | ✓       | ✓           | ✓                | -         |

• External Peripherals. These peripherals are the sensors, actuators, and other circuitry on the device's circuit board(s). They are exposed to the program only through one of the on-chip peripherals, including GPIO, or a bus such as Inter-Integrated Circuit (I2C) or Serial Peripheral Interface (SPI). While from the programmer's perspective, communicating with these peripherals is as easy as sending and receiving messages thanks to software libraries, the resulting compiled firmware does so through a complex series of accesses to the MMIO regions of on-chip peripherals, making the direct flow of data in and out of each peripheral difficult to observe. This is also the source of the most variety in embedded systems, as these devices typically contain entirely-custom circuit boards, with whatever array of components the designers felt were necessary.

## 2.2.1 Aspects of Ideal Re-Hosting

Many solutions have been proposed to enable firmware re-hosting, each with their own qualities and drawbacks. To showcase their differences, we identify four salient properties that an ideal analysis system, capable of handling arbitrary firmware, should possess. Table 2.1 shows prevalent tools that tackled the re-hosting problem in the past, and classifies them according to the aspects, which are described as follows.

Abstraction-less. An ideal re-hosting solution should not rely on a software abstraction that greatly limits the kinds of firmware on which it can be used. Recently, advances have been made in re-hosting firmware based on the abstractions provided by the Linux OS [33, 36]. Using such an abstraction, when it exists, is advantageous, but it naturally limits the scope of firmware to those that do not have a significant coupling between their primary function and the underlying hardware. Relying on an OS precludes the analysis of, for example, the *blob* firmware we explore in this work. However, as we explore in Chapter 4, even blob firmware samples are often built with an abstraction in mind, although it must be located in the binary in order to be used as such. We therefore show how we can trade the goal of idealized rehosting, which should indeed not rely on an abstraction, for the ability to rehost more complex firmware.

Firmware relying on an abstraction can also be *simulated* without full emulation, if source code is available. Simulators for Contiki [37], mBed [38] and RIOT-OS [39] allow the developer to compile their firmware code into a binary that can run on the host system. In contrast, HALUCINATOR allows for a similar kind of re-hosting to be performed, but on the final firmware binary, and without the availability of source code.

HALUCINATOR draws some inspiration from the work done in game console emulation [40, 41], which pioneered the idea of High Level Emulation, albeit applied to specific hardware environments and software stacks. HALUCINATOR represents a generalization of this idea, and presents the first known application to embedded firmware for security. Virtual. A re-hosting solution should not depend on the presence of hardware during analysis. Many proposed approaches to firmware analysis [29, 32, 30, 42] require hardware-in-the-loop execution. However, such approaches inherently limit the scale of

the analyses. In a dynamic context, only one thread of execution is possible per-device, and re-starting execution, which happens very often in modern fuzzers, can incur a significant time penalty [43]. One way to allow those optimizations, however, is presented by Kammerstetter, et al. [31], who proposed a means of caching requests and responses between a program and the high-level device objects exposed by its Linux-based firmware. While this approach also concerns approximating state, and has a similar goal, it is distinct from the State Approximation approach we present here, as it attempts to understand the state of the program as a proxy for the state of the peripheral, and not the state of the peripheral directly.

Another way to move from a hardware-in-the-loop approach to a fully emulated environment is proposed by Zaddach [44]. Hereby, peripheral fingerprints are first generated by recording MMIO traces in a manner similar to PRETENDER. Afterwards, those fingerprints are used to match peripherals which are already *known* to a given emulator. While this allows accurate emulation of peripherals if successful, a single *unknown* peripheral would spoil hardware-less emulation.

Symbolic execution is even more impacted by such approaches; analyses using hardware-in-the-loop must be careful to only execute portions of code that do not contain hardware interactions, to avoid corrupting the hardware's state visible by all parallel code paths being explored. Cost also becomes a factor, as each analyst wishing to explore a set of devices must purchase and instrument the devices, which raises the barrier to entry for firmware analysis. While hardware-in-the-loop techniques do allow for interactive, relatively low-effort analyses, they are by no means adequate for thorough program analyses of arbitrary firmware.

A recent system proposed by Talebi, et al. [45] employs a hybrid of Linux-based rehosting and hardware-in-the-loop to enable the fuzzing of device drivers. While moving the bulk of the execution to an already-rehosted system presents speed improvements over

on-device fuzzing, it inherits the limitations of both approaches: dependence on the Linux abstraction, scalability limitations due to the need for a device, and incompatibilities with DMA.

Interactive. A re-hosting solution should be responsive to new program input. While defining the notion of input on an embedded firmware is itself a nuanced problem, the remaining hardware (not used as the source of input) should react accordingly. Trace replay-based solutions, such as PANDA [46], while quite flexible and useful for certain analyses, are not interactive and cannot be used to implement fuzzing or symbolic execution, which rely on this primitive.

**Automatic.** An ideal re-hosting solution should not require a significant effort perdevice to use. The diversity in on-chip and external peripherals is so severe, that it is highly unlikely that any firmware can be emulated out-of-the-box with a commercial or open-source emulation package.

While some commercial systems provide the ability to rehost completely custom hard-ware architectures (e.g., Simics [10]), these systems still require the hardware models to be programmed manually. This is made worse by customizable CPU cores, and the diverse array of electronics components that the electronics industry continues to support. Even static and symbolic analysis tools [47, 28, 48] heavily rely on the manual specification of hardware behavior, particularly around IO and interrupts.

While there is little useful data able to quantify embedded CPU diversity, and documentation from vendors is not in a comparable form, we managed to locate a dataset of 555 CMSIS System View Description (SVD) files [49], which are XML files describing chipsets based on Cortex-M microcontrollers. They detail the on-chip peripheral locations and layouts of 463 distinct chips across 13 different chip vendors. This collection is by no means complete (it does not even include all of the chips used in our experiments

in Chapter 3 Section 3.2), but it shows the complexity and the scale of this problem. In this dataset alone, we could identify 1592 unique implementations of peripherals demonstrating the immense variety of peripheral and chip designs.

This complexity increases even more when considering external peripherals connected to the chip via on-chip buses and interrupt controllers. Hence, emulators such as QEMU [50] have to include carefully and—up to now—manually crafted implementations of peripherals and align them at the right location. In fact, the upstream version of QEMU only exposes implementations for three different Cortex-M chips, none of them present in the above dataset.

As a result, analysts end up creating their own peripheral and board implementations and maintaining them in separate forks of the project, such as *QEMU STM32* [51] or *GNU MCU Eclipse* [52]. A different approach is taken by *LuaQEMU* [53] and avatar<sup>2</sup> [34], which provide an interface for the analyst to define the peripheral layout. While these may be preferable to languages such as C used by QEMU itself, the analyst is still required to obtain and understand the full documentation for the particular CPU model used, and this effort may not transfer entirely to other similar CPUs, even from the same vendor. Therefore, it is very clear that an automated solution is needed to be able to make firmware analysis tractable.

In Chapter 3, we will present the first system aiming at ideal rehosting. Subsequent to this work's publication, other attempts have been made, such as P2IM [35]. Naturally, no system presented here or elsewhere claims to have completely achieved ideal re-hosting; we discuss the limitations of this in Section 3.3

Figure 2.1: The memory layout for a simple 32 bit memory-mapped timer on the STM32 embedded processor.

## 2.3 Library Matching

HALUCINATOR'S LibMatch component builds upon related work in binary library matching and naming.

Previous work has explored various aspects of "function identification". As this term has many over-loaded uses, it is important to distinguish the problem LibMatch solves (labeling specific binary function names in firmware samples) from others. *BinDiff* [54, 55], and its open source counterpart *Diaphora* [56] use graph-matching techniques to effectively and efficiently compare two programs. While these tools can be effectively used to label functions, by matching a target binary to each library object, the tool does not account for collisions.

ByteWeight [57] identifies the locations (e.g., start and end) of functions by computing a prefix-tree of likely sequences based on a database of known libraries but does not attach labels to located functions. LibMatch must also perform this analysis to eventually label function names in firmware, but ByteWeight itself does not attach any label to the functions it locates. The angr platform underlying LibMatch incorporates the results of

ByteWeight in its CFG recovery algorithm.

Multiple previous works have explored the problem of function labeling, using various combinations of features extracted from functions, and matching methods, to associate one set of code from another. Feature extraction techniques include function preamble-based signatures [58], backward slices from system calls [59], and traces from symbolic execution [60, 61]. Matching the extracted features has been performed through Bayesian networks [62], neural networks [63], and locality-sensitive hashing [64]. Unfortunately, none of these systems are suited for labeling functions in firmware due to several challenges: the inability to analyze or execute ARM Cortex-M code, the lack of information available to machine learning approaches due to small size and close similarity of functions in HALs, and the inability of some approaches to deal with collisions in an efficient way. This lack of existing approaches leads us to develop our function matching approach that is tailored to embedded firmware.

## 2.4 Binary Patching

Many previous works have explored the area of patching binary programs. Each has various pros, cons, limitations, and assumptions, which must be compared to understand the current state of the field.

Wenzl, et al. [65] dissect this area of research, and define four common steps to binary rewriting: *Parsing*, *Analysis*, *Transformation*, and *Code Generation*. The work in this area varies in terms of how they handle each of these steps.

The largest class of this work concerns reassemblable disassembly [66, 22, 21], the notion of disassembling a binary completely into standard assembly code for the architecture in question, adjusting the code, and then simply assembling it again into the finished binary. This is a preferable technique for the analyst, as it makes the Trans-

formation and Code Generation step easy; assembly can be easily patched manually or automatically via the human-readable assembly code, and turned into a binary again with standard tools.

However, this work presents problems when it comes to tackling the rewriting of firmware. First, reassembly assumes that the firmware can be disassembled completely during the Parsing phase. This includes the inter-related problems of distinguishing code and data, finding function boundaries, distinguishing pointers from integers, and the resolution of indirect jumps. Unless we can re-host the firmware into an emulated environment, we are left with performing those tasks entirely statically. We also are dealing with monolithic firmware images, and therefore do not have an explicit memory map, symbols, or other metadata that can make these steps easier. Therefore, we cannot guarantee the completeness of the disassembly, control-flow recovery, or function identification. As an indicator of this challenge, the samples in Chapter 5 Section 5.4 have an average of 401 unresolved indirect jumps after angr's resolution mechanisms (based on [67], with our real-world firmware samples having an order of magnitude more than vendor sample code. Since monolithic firmware is not position independent by nature, if we cannot locate every pointer, including those used to access code and data, and adjust them during reassembly, the firmware will not execute correctly.

On top of this, many aspects of these approaches are architecture-specific, with the majority of works focusing only on Intel x86 binaries [66, 22, 68, 69], or requiring x86 hardware extensions [70]. Some caveats related to ARM instruction set features that inhibit the Parsing and Analysis phases were addressed by Kim, et al. [23], but the approach still inherits the aforementioned severe limitations of reassembly.

Another emerging class of work revolves around transferring patches from one program to another. OSSPatch [71] works by leveraging source code of open-source projects used in the unpatched target binary to retrofit patches from their upstream sources. A

similar work [72] aims to transfer the patched portions of compiled binaries, without the source code. In our scenario, the patch has simply not been developed, and will not be developed by the manufacturer, therefore we cannot leverage either of these approaches.

Finally, while the above work has explored the Parsing, Analysis, and Transformation aspects of binary rewriting, little thought has thus far been given to the Code Generation portion. Unfortunately, this is where the unique challenges of embedded systems, and particularly safety-hardened systems, begin to restrict our ability to patch. First, all of the above work assumes that, when a patched binary is created, the system will simply execute this binary instead of the original. As we discuss in Chapter 5 Section 5.1, most commercial embedded systems contain self-checks to guard against accidental modification or corruption of the firmware (e.g., CRCs and checksums), or intentional manipulation by an attacker or user (e.g., digital signatures) which must be located, and bypassed, for a patch to work. On top of this, it is also assumed by reassembly-based approaches that we have the toolchain needed to create a functioning binary image. In the case of a monolithic firmware image, we do not know what format, if any, is present in the firmware, or what tools may have been used to create it.

Additionally, we need to find space for our added code, either within the image, or by appending it to the end. Since we often obtain monolithic firmware in the form of full flash images (e.g., we cannot simply append data to the end), we must decide what in this image can be removed, or what apparently-empty space is indeed available. This relates to the problem of binary de-bloating, the known-undecidable problem of removing unnecessary content from a program. Recent work has proposed solutions for debloating Dockerized applications [73], during program compilation [74], or using shared library files [75]. Naturally, these kinds of approaches involve extensive knowledge of the program, in the form of source code, object code, or simply do not apply to the firmware domain.

Razor [76] uses a series of test-cases, along with the collection of execution traces and heuristics to determine removable portions of code. Unfortunately, as we mention in Chapter 5 Section 5.1, this kind of trace collection is not possible in the embedded systems domain, without a successful re-hosting solution. Redini, et al. [67] propose BinTrimmer, which aims to remove unnecessary code, without using any of the above assumptions. It does so through improvements to indirect jump resolution, which are used as the basis for angr's own indirect jump resolver, although, as mentioned above, this too is not complete enough to be useful in this context.

In summary, these numerous issues combine to rule out any *Dynamic* or *Full Translation* approaches (as defined by Wenzl, et al. [65]), and we must resort to the more simplistic *Direct* or *Minimal Invasive* techniques when dealing with monolithic firmware images. Even these (such as Detours [24]) require us to solve at least the problems of code insertion, self-checks, and sources of security-relevant data, which we focus on in this work.

# Chapter 3

# Toward Firmware Analysis through Automated Re-Hosting

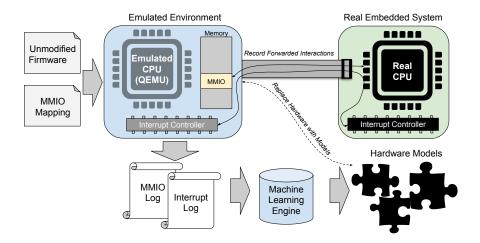

In this chapter, we propose an approach, aiming to achieve ideal re-hosting (as defined in Chapter 2, and propose a proof-of-concept system, called PRETENDER, which is able to observe hardware-firmware interactions and create models of hardware peripherals automatically. Our system first creates a recording of real interactions between the firmware and its hardware, and uses machine learning and pattern recognition techniques to create models for each peripheral on the CPU. The generated models can then be leveraged by popular full-system emulators (e.g., QEMU [50]) or program analysis engines (e.g., angr [26]) to enable precise, scalable, interactive analyses of the accompanying firmware.

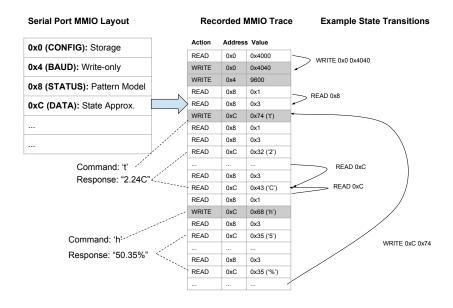

While automated re-hosting may seem conceptually straightforward, the challenges in modeling even simple hardware-firmware interactions are numerous. We may think of a peripheral, such as a serial port, as a simple object that sends and receives data, but the firmware's view of this hardware is much more complex, consisting of dozens of individual configuration, status, or data registers, which, from the point-of-view of the firmware, appear as only opaque memory accesses, without any indication of their layout or behavior. Two peripherals performing the same function on two different CPUs,

even from the same vendor, vary wildly in terms of memory layout and implementation details. On top of this, accesses to these peripherals occur within the CPU itself, and obtaining these interactions for modeling is its own challenge. Interrupts are also a common feature of embedded peripherals, and must occur exactly as expected, or the hardware or firmware may fail.

To evaluate our approach, we demonstrate our recording and modeling techniques on a set of six unique "blob" firmware samples, each on three different hardware platforms, with associated external peripheral devices. Our experiments show that PRETENDER is able to successfully extract the peripheral models and execute the firmware in a fully emulated environment. The models offer enough interactivity to allow for the exploration of parts of the program not seen during recording or training. We further show the potential for direct applications to dynamic analysis, by using these modeled environments to trigger synthetic security vulnerabilities in the firmware samples. The hardware modeled in these experiments represents CPUs and other components common to low-power IoT and embedded devices. However, many challenges remain before typical commercial devices can be modeled in full. We nevertheless believe that the goal of automated firmware re-hosting is both achievable and necessary. Therefore, we conclude with a discussion of limitations, open problems, and next steps toward tackling the complexity of commercial devices.

In summary, our contributions in this chapter are as follows:

- We explore the problem of *firmware re-hosting*, and show that virtual, interactive, automatic, and abstraction-less approaches are needed to handle today's diverse firmware.

- We present Pretender, a proof-of-concept system able to automatically build hardware models, through a mix of novel hardware and interrupt recording tech-

Figure 3.1: Overview of the functionality of PRETENDER

niques, machine learning, and peripheral state approximation.<sup>1</sup>.

We apply Pretender to multiple firmware samples across multiple hardware platforms and show that the generated peripheral models are accurate, automatic, and interactive enough to enable program analysis and vulnerability discovery.

### 3.1 Methodology

In this section, we present PRETENDER, a step toward automating the modeling of MMIO and interrupt-driven hardware peripherals to enable re-hosting. The goal is to gather data on, and build models of, these peripherals, such that the firmware under analysis can later be independently executed in a CPU emulator. We present our solution in the context of its use to support dynamic analysis of firmware, although the generated models have other possible uses, which we will discuss in more detail in Section 3.3.

The success metric we adopt to evaluate the completeness of the extracted models is what we call *survivable execution*, which we define as the ability for the firmware to

$<sup>^1\</sup>mathrm{To}$  allow the reproducibility of this work, the source code to this work is available at https://github.com/ucsb-seclab/pretender

execute the same regions of code as it would if the original hardware were present, without faulting, stalling, or otherwise impeding this process. We include in this definition the need for our program to be interactive, as this is a requirement for many analyses. That is, the firmware and our hardware models need to be able to operate on inputs and execute code paths that were not observed during the recording and model-generation phase.

**Assumptions and Prerequisites.** We make a few basic assumptions in the implementation of PRETENDER.

- We assume that a CPU emulator is available for the target device, and that this emulator supports all CPU features that can impact control flow, including the interrupt controller.

- We assume the analyst has the ability to observe memory accesses and the occurrence of interrupts in the device in real-time. We will present a method for accomplishing this on any device with a basic debugging interface, lowering the requirement to the ability to read and write the device's memory.

- We assume that the basic memory layout of the target device is known, particularly the location of code and data in the memory space. More generally, we need to know where these areas are *not* located, as we can assume that the remaining areas are interesting locations we wish to model, including the MMIO regions.

- We assume that a human or automated process is able to interact with the hardware and that it achieves sufficient code coverage during the recording phase to reveal enough hardware interactions to generate a model. The more complete the code coverage is, the more detailed the extracted model will be.

A discussion of these assumptions can be found in Section 3.3.

PRETENDER works in the following phases:

- 1. **Recording.** We instrument the device to obtain a trace of accesses to the MMIO regions, and any interrupt that occurs during the execution.

- 2. **Peripheral Clustering.** We locate the boundaries of each distinct peripheral within the device's memory space, and divide the recording into sub-recordings for each peripheral.

- 3. **Interrupt Inference.** Based on the interleaving of interrupts with MMIO, we assign each numbered interrupt event to a peripheral group. We then infer which bits in which memory location in the peripheral control interrupts, and create timing patterns to be used during emulation.

- 4. **Memory Model Training.** In this step, we attempt to select and train known models for each memory location within the identified peripheral regions. Any unidentified memory locations will be modeled using State Approximation.

- 5. **Test Harness Creation.** Finally, the analyst must decide how input should be introduced into the system, through the creation of a simple test harness. This is the only manual step in the process, as the decision depends on the analyst's needs.

A complete overview of PRETENDER and the interplay between its different parts can be seen in Figure 3.1. In the remainder of this section, we will discuss the individual phases of the system in detail.

#### 3.1.1 Recording MMIO

The natural first step in building models of hardware is recording a trace of the IO activity that occurred during execution. As we outline in Section 2.2, the firmware depends on both internal "on-chip" peripherals, and external "off-chip" peripherals, both of which are needed for the firmware to operate as expected. However, the firmware only

communicates with off-chip peripherals through its interactions with on-chip peripherals, so in order to have a complete recording, we must capture all memory accesses that constitute MMIO.

Rationale. Peripherals are considered "memory-mapped" because they are attached to, and addressed via, one of the CPU's internal memory buses. Unlike external buses, which can be physically probed and monitored, these interactions only occur within the CPU's die, and cannot be directly monitored. While some debugging facilities used in the development of new chips offer a data trace of the memory bus, such as ARM's ETM/HTM Data Trace, these features are seldom available on production chips, and are entirely absent in the low-cost, low-pin-count chips of commercial embedded devices. Typical CPUs found in the wild include, at best, a debugger capable of simple execution control, and memory/register access.

On top of this, MMIO behaves differently from a normal region of memory; instead of just storing data, these locations instead control or represent aspects of on-chip peripherals. Their value or function may change based on external factors, without any interaction with the firmware.

One possible alternative approach to MMIO recording would be to instrument the firmware to record IO interactions. This requires us to understand, from the binary firmware itself, where this IO takes place. This could be done on architectures where explicit in and out instructions are used for peripherals. On ARM, however, this is not a straightforward operation, as peripherals are accessed via normal memory handling instructions (LDR/STR), and it is often difficult to tell statically whether an instruction is addressing a peripheral or normal memory. Inserting this instrumentation code non-destructively, and collecting the cumbersome volumes of data it generates, are both hard problems, and may even be impossible if the code is present on a Read-Only Memory (ROM).

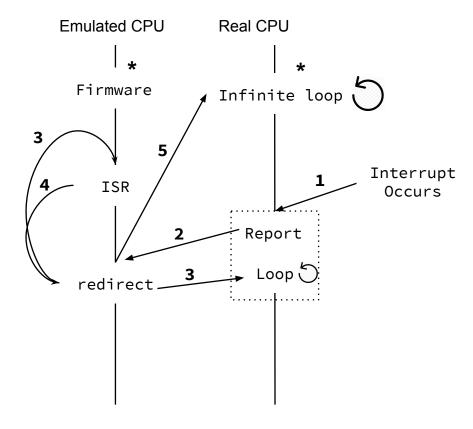

Figure 3.2: State diagram of interrupt recording in Pretender. \* indicates the initial state.

Recording Implementation. As a result of these complications, our recording approach leverages a hardware-in-the-loop execution approach, where the firmware is deployed in an emulator, and the MMIO requests are forwarded to the original hardware, which allows recording in-transit. We built upon the  $avatar^2$  framework [34], which allows for the simultaneous control and orchestration of emulators and hardware.  $Avatar^2$  supports an event-based callback infrastructure, which allowed us to implement the recording of memory events.

#### 3.1.2 Recording Interrupts

In order to fully model on-chip hardware peripherals, we must observe the interrupts that they generate, in the context of the MMIO activity of the firmware.

Rationale. Interrupts play an important role in most peripherals, and are a particularly difficult aspect to record and model correctly. Interrupts are triggered by some event, whether it is an explicit MMIO operation, or an event in the physical world, and cause the execution of Interrupt Service Routines (ISRs) as a result. These ISRs typically contain MMIO operations associated with the peripheral that triggered the interrupt (e.g., reading data that arrives at a serial port or counting the number of times a counter overflows). Without the peripherals' ISRs executing at the correct times, the peripherals may not function, or the system may crash. This behavior is a property of the hardware itself; the internal logic of the peripheral decides when and how often to trigger its associated interrupts. Many peripherals allow this behavior to be adjusted at runtime, through their configuration registers. For example, many peripherals have a single bit in their configuration register controlling whether interrupt events are generated at all.

Hardware features exist on many chips for providing a log of the interrupts, such as ARM's Instrumentation Trace Macrocell (ITM), but these features are not universal, and are difficult to coordinate with simultaneous peripheral recording or even basic hardware-in-the-loop emulation. Hence, previous solutions, such as the first version of the Avatar framework [29] or SURROGATES [32] tried to tackle interrupt forwarding with custom stubs injected onto the device under analysis. However, both of these solutions forward interrupts in a "fire-and-forget" manner. This results in inconsistencies between hardware and emulated firmware, as incoming interrupts on the hardware could easily be missed when the emulator serves a previous interrupt. Although those inconsistencies are a negligible problem for manual analysis, they dramatically complicate automated modeling,

and must be avoided. A more recent approach, presented by Corteggiani et al. [42], uses a custom tailored protocol to keep hardware and emulator *synchronized* during interrupt forwarding. Unfortunately, this method requires custom debugging hardware that would greatly reduce the generality of PRETENDER.

Hence, we heavily extended avatar<sup>2</sup> to support the notion of forwarding and recording interrupts, while carefully keeping the two systems synchronized without the need of specialized debugging hardware. The current published version of avatar<sup>2</sup> retains the hardware in a "debug-halt" state while forwarding memory accesses, in order to avoid side-effects from the resident code. Unfortunately, this debug-halt state inhibits all interrupts, and thus cannot be used as-is. However, we cannot simply keep the CPU running and forward all of the generated interrupts into the emulator; if too many un-handled interrupts arrive, or spurious, unwanted interrupts occur, the hardware or emulator can experience an unrecoverable fault. The current version of avatar<sup>2</sup> also does not support writing to memory while the CPU is running. To make matters worse, halting the CPU during interrupt routines is problematic, as we noticed that some peripherals, particularly those that control future interrupts, will not work properly in this halted state because they are bound to the CPU's instruction pipeline. As a final complication, we must ensure that we return from these interrupts properly, both in the emulator and on the hardware to ensure that the hardware continues to function, even though it is not executing any code.

Interrupt Recording Implementation. Figure 3.2 shows how interrupts are recorded in PRETENDER. As interrupts are generated on the real device, we should have the Real CPU running. Hence, we always have the Real CPU execute an infinite loop. Furthermore, we replace the ISR of all the interrupts with a recording stub (shown in dotted box in the Figure 3.2).

When an interrupt occurs (Step 1), the recording stub is triggered, which immediately

reports the interrupt number to PRETENDER (i.e., the Emulated CPU), and halts the Real CPU (Step 2). The emulated CPU then starts executing the actual ISR for the corresponding interrupt, and directs the real CPU to run a loop in the interrupt's context to mimic the execution of the interrupt (Step 3). Once the ISR completes execution on the emulated CPU (Step 4), PRETENDER redirects the execution of the Real CPU to the default infinite loop, and the Emulated CPU to continue executing the firmware (Step 5). This ensures that both the hardware and emulated interrupt controllers are synchronized.

#### 3.1.3 Peripheral Clustering

With the combined MMIO and interrupt recording collected, we can now proceed to reason about and model the peripherals themselves. In the end, we need to construct a model, such that each MMIO location that the firmware accesses returns a reasonable value. However, these locations are not independent; multiple locations represent one logical device in the silicon of the chip, which has its own concept of state, control interrupts, and so on. For example, writing a byte to the data register of a serial port may cause the "transfer in progress" or "busy" flag to become active in the same peripheral's status register. Therefore, a major prerequisite to the future modeling steps is to group all memory accesses by their associated peripherals.

To do this, we rely on the intuition that each MMIO peripheral is typically associated with a block of contiguous memory addresses (e.g., 0xC00-0xCFF in Figure 2.1). While we cannot be sure exactly what the boundaries between the peripherals are, we assume there is some fixed alignment for—and the minimal gap between—them, likely due to the underlying details of the peripheral buses that serve MMIO peripherals. These details are supported by the SVD data explored in Section 2.2, as well as the manuals for all of the devices explored in Section 3.2. We can, therefore, find our peripheral boundaries through

clustering techniques. For this work, we take the set of accessed addresses and employ the Density-based Spatial Clustering of Applications with Noise (DBSCAN) algorithm [77] to recover the peripheral groupings.

The intuition behind this choice is that each peripheral will appear as a small cluster of accesses in a relatively sparse memory space. For example, in Figure 2.1, while an entire page of memory (0x1000) is allocated to the timer, only a small portion (0x00-0x50) of that memory space is actually used, meaning that subsequent peripherals in memory will likely have large gaps between their relative clusters. DBSCAN is able to quickly discern these clusters, providing us with the capability to efficiently group the various accesses. In our work, we set our maximum gap between any of the addresses in a cluster (i.e., epsilon) to be 0x100 and the minimum cluster size to be one. Almost any reasonable value for epsilon (e.g., 0x8-0x100) would likely produce identical and useful clusters, and our minimum cluster size of one ensures that we will not exclude simple or infrequently-used peripherals from our models.

#### 3.1.4 Interrupt Inference

In order to model interrupts correctly, we need to establish a reasonable approximation for when to fire each interrupt and which MMIO event triggered it. First, we find the association between the interrupt number and the peripheral firing the interrupt, which is a property of the hardware that varies widely between chip models. Then, we discern which MMIO register is used to enable and disable each interrupt, so that we do not fire it too soon or too late in the execution. Finally, we determine how often to fire interrupts when they are eventually enabled.

To associate an interrupt with a peripheral, we examine the interleaved interrupt and MMIO traces and locate all of the MMIO operations that occur during an Interrupt Service Routine (ISR) (e.g., between an interrupt event and the emulator returning from the ISR). We leverage the intuition that the purpose of most interrupts is to trigger the firmware to communicate with the interrupting peripheral, by executing the code in the ISR. Therefore, we associate an interrupt number with a peripheral if that peripheral's MMIO addresses were accessed the most during the ISR's execution.

We then locate the memory location containing the interrupt's trigger, which is a location in the peripheral which, when a certain bit pattern is written, causes interrupts to be enabled. The location can be determined by finding the very first interrupt for a given interrupt number, and seeking backward in the MMIO/interrupt trace until a write to the associated peripheral is found. This is intuitively the configuration, or interruptenable register, as it is best practice to enable interrupts as the final step during peripheral configuration, as, after this point, any operation could be interrupted. However, this memory location may be shared with other functions, and many bit patterns may be written to it during an execution which have no effect on interrupts. The next step is therefore to refine the bit pattern which can enable interrupts in the model, based on which writes appear to control interrupt behavior in the hardware. We start with the assumption that all bits in the trigger location control the interrupts. For each write to the detected trigger location, if a bit is set to 0 when interrupts occur, it is unlikely to be the interrupt trigger bit, and is removed from consideration. The remaining bits are considered the final interrupt trigger; during emulation, when these bits are set in the trigger location, interrupt events will be fired by the model.