### **UC Santa Cruz**

### **UC Santa Cruz Electronic Theses and Dissertations**

### **Title**

Pyrope: A Latency-Insensitive Digital Architecture Toolchain

### **Permalink**

https://escholarship.org/uc/item/9md197hg

#### **Author**

Skinner, Haven Blake

### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SANTA CRUZ

# PYROPE: A LATENCY-INSENSITIVE DIGITAL ARCHITECTURE TOOLCHAIN

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

**COMPUTER ENGINEERING**

by

**Haven Blake Skinner**

December 2018

|              | Haven Blake Skinner is approved: |

|--------------|----------------------------------|

|              | Professor Jose Renau, Chair      |

|              | Professor Martine Schlag         |

|              | Professor Heiner Litz            |

| Lori Kletzer |                                  |

Vice Provost and Dean of Graduate Studies

The Dissertation of

Copyright © by

Haven Blake Skinner

2018

## **Table of Contents**

| Li | st of I | igures                                                      | vi |

|----|---------|-------------------------------------------------------------|----|

| Li | st of T | ables                                                       | ix |

| Al | bstrac  |                                                             | X  |

| A  | cknow   | edgments                                                    | xi |

| 1  | Intr    | duction                                                     | 1  |

| 2  | Bacl    | ground                                                      | 6  |

|    | 2.1     | Fluid Pipelines and the Pyrope Project                      | 7  |

|    |         | 2.1.1 Fluid Pipelines                                       | 7  |

|    |         | 2.1.2 Clock Synchronous vs. Fluid Pipeline Architectures    | 9  |

|    |         | 2.1.3 Fluid Pipelines vs. Other Latency Insensitive Systems | 13 |

|    |         | 2.1.4 Motivations for the Pyrope Project                    | 17 |

|    | 2.2     | Languages                                                   | 18 |

|    |         | 2.2.1 Hardware Description Languages                        | 19 |

|    |         | 2.2.2 The Actor Model                                       | 21 |

|    |         | 2.2.3 Other Programming Languages                           | 22 |

|    | 2.3     | Fluid Pipelines and Hardware Simulation                     | 22 |

| 3  | The     | Liam Programming Paradigm                                   | 26 |

|    | 3.1     | Describing Fluid Behavior with Liam                         | 26 |

|    |         | 3.1.1 Overview                                              | 26 |

|    |         | 3.1.2 Liam within a Pyrope Architecture                     | 27 |

|    |         | 3.1.3 Inferring Fluid Behavior                              | 28 |

|    |         | 3.1.4 Liam-Specific Operators                               | 30 |

|    |         | 3.1.5 Catching the Abort with "Try" Blocks                  | 34 |

|    |         | Compiling Liam                                              | 36 |

|    |         | 3.2.1 Stages and State                                      | 37 |

|    |         | 3.2.2 Deriving Logic for External State                     | 39 |

|    |         |                                                             |    |

|   |      | 3.2.3 D      | eriving Logic for Internal State          | 42 |

|---|------|--------------|-------------------------------------------|----|

|   | 3.3  | Arrays an    | d Liam                                    | 42 |

|   |      | 3.3.1 Se     | oftware Arrays and Hardware Memory Blocks | 43 |

|   |      | 3.3.2 P      | rope Internal Array Representation        | 45 |

|   |      | 3.3.3 an     | vr Optimizations                          | 46 |

|   | 3.4  | Conclusio    | n                                         | 49 |

| 4 | Pipe | line Trans   | formations                                | 52 |

|   | 4.1  |              |                                           | 54 |

|   | 4.2  | Implemen     | tation                                    | 56 |

|   | 4.3  | Evaluation   | 1 Setup                                   | 57 |

|   | 4.4  | Synthesis    |                                           | 59 |

|   | 4.5  | Simulatio    | n                                         | 63 |

|   | 4.6  | Verification | on                                        | 68 |

|   |      | 4.6.1 A      | Note on Fluid Induced Bugs                | 69 |

| 5 | Live | Programi     | ning                                      | 71 |

|   | 5.1  | _            | 9                                         | 77 |

|   |      | 5.1.1 L      | ve Programming and Hot Reloading          | 77 |

|   |      | 5.1.2 C      | heckpointing and Parallel Replay          | 78 |

|   | 5.2  |              |                                           | 79 |

|   | 5.3  |              |                                           | 81 |

|   | 5.4  | LiveSim      |                                           | 83 |

|   |      |              |                                           | 84 |

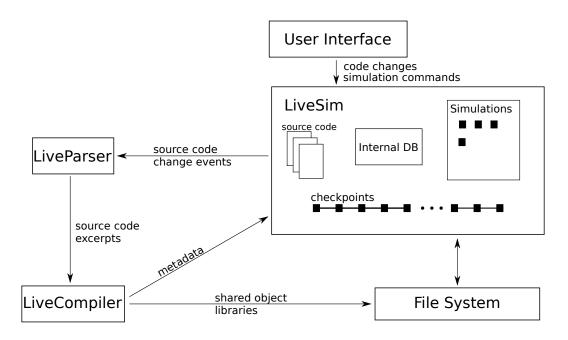

|   |      | 5.4.2 T      | ne LiveSim Architecture                   | 85 |

|   |      | 5.4.3 L      | veParser and LiveCompiler                 | 92 |

|   |      | 5.4.4 Fa     | ast Reloading                             | 93 |

|   |      | 5.4.5 R      | eloading Rules                            | 94 |

|   |      | 5.4.6 C      | heckpoints and Memory Usage               | 96 |

|   |      | 5.4.7 C      | heckpoint Consistency Verification        | 96 |

|   | 5.5  | Setup .      |                                           | 97 |

|   |      |              | 8                                         | 98 |

|   |      | 5.5.2 A      | Note on Compiler Configuration            | 99 |

|   | 5.6  | Evaluation   | 1                                         | 99 |

|   |      | 5.6.1 H      | ot Reloading                              | 00 |

|   |      | 5.6.2 Si     | mulation Efficiency                       | 02 |

|   |      | 5.6.3 C      | heckpointing                              | 06 |

|   | 5.7  | Conclusio    | n                                         | 06 |

| 6 | Con  | clusion an   | d Future Work                             | 08 |

|   | 6.1  | The Pyrop    | pe Language                               | 09 |

|   | 6.2  | The Pyro     | be Compiler and Toolchain                 | 10 |

|   | 63   | Pineline T   | ransformations 1                          | 11 |

| 6.4     | Final Thoughts | <br> | <br> | 111 |

|---------|----------------|------|------|-----|

| Bibliog | raphy          |      |      | 113 |

# **List of Figures**

| 2.1 | A fluid pipeline replaces synchronous registers with fluid registers, which use <i>valid</i> and <i>stop</i> signals to execute a simple handshake protocol to update its in-                                                         |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | ternal state                                                                                                                                                                                                                          | 8  |

| 2.2 | Fluid Registers are used in place of traditional clock-synchronous registers in Fluid Pipelines. They contain enough internal buffering to allow back pressure                                                                        |    |

| 2.3 | to propagate without dropping data. (Picture credit: R. Possignolo [65]) The clock-synchronous pipeline is the standard model for developing modern digital architecture. A side effect of doing so is that the system's behavior be- | 8  |

| 2.4 | comes closely tied to its timing                                                                                                                                                                                                      | 9  |

|     | tains hidden assumptions about the latency between different sections of the pipeline, which makes the system harder to manipulate in general                                                                                         | 11 |

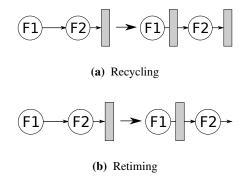

| 2.5 | Latency insensitive pipeline transformations allow for adding or removing register blocks (Recycling) or moving logic between register blocks (Retiming),                                                                             |    |

|     | without changing behavior. (Picture credit: R. Possignolo [64])                                                                                                                                                                       | 12 |

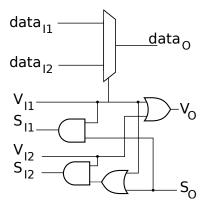

| 2.6 | The "merge" or "fluid mux" operator selects an input based on which is valid. This can break sequence-invariance. (Picture credit: R. Possignolo [64])                                                                                | 16 |

| 3.1 | The first step to adding fluid behavior to a Pyrope block is to add flags indicating when an input or output port has been read or written. This figure shows the                                                                     |    |

|     | flags added to Listing 3.1                                                                                                                                                                                                            | 39 |

| 3.2 | The dataflow graph generated by Listing 3.1                                                                                                                                                                                           | 40 |

| 3.3 | If the try block does not abort, the state update comes from that block, otherwise                                                                                                                                                    |    |

|     | it comes from the else block                                                                                                                                                                                                          | 41 |

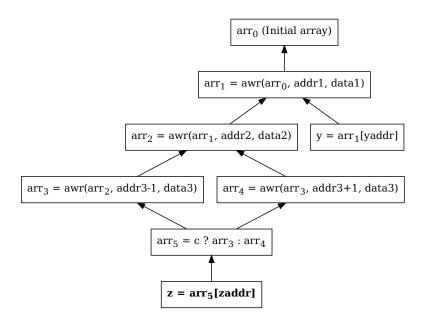

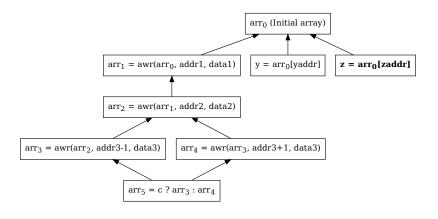

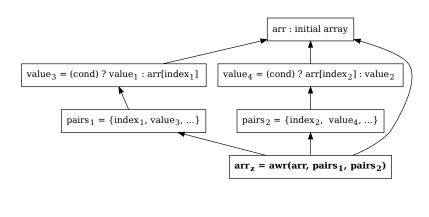

| 3.4 | Arrays in Pyrope are either <i>inline</i> if they are updated immediately after being written, or <i>deferred</i> if they are updated at the end of the cycle. The distinc-                                                           |    |

|     | tion is reflected in their respective dataflow graphs; for inline arrays, reads are dependent on the latest version of the array, while deferred reads are always                                                                     |    |

|     | dependent on the version present at the beginning of the cycle                                                                                                                                                                        | 47 |

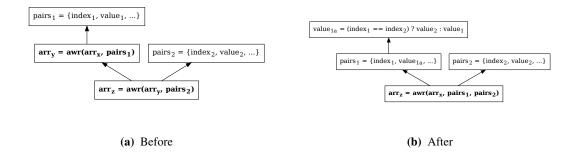

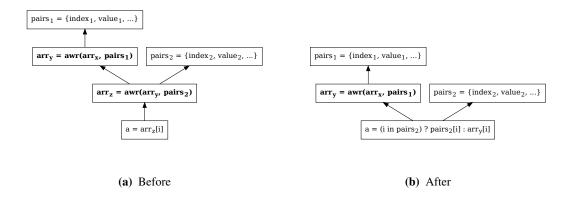

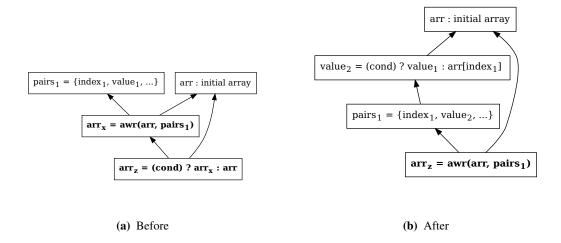

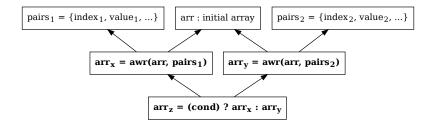

| 3.5 | A chain of array_writes requires that all indexes not written be copied unmod-                                                                                                                                                        |    |

|     | ified. This can be collapsed to a single <i>array_write</i>                                                                                                                                                                           | 48 |

| 3.6        | When a read is dependent on an <i>array_write</i> , that dependency can be moved to an earlier version of the array as long as the logic to forward an updated value is implemented.                                                                                                                                                 | 48                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.7        | is implemented                                                                                                                                                                                                                                                                                                                       | 40                              |

| 3.8        | around the values being updated, eliminating unnecessary copying This corresponds to the case of an array being written to on one branch of an $if-else$ block. The result is similar to Figure 3.7                                                                                                                                  | 49<br>50                        |

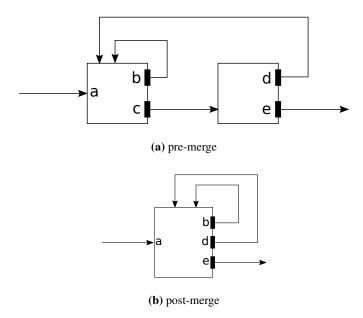

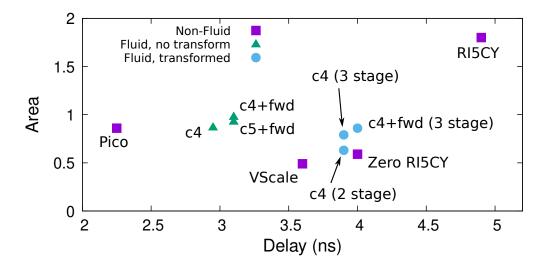

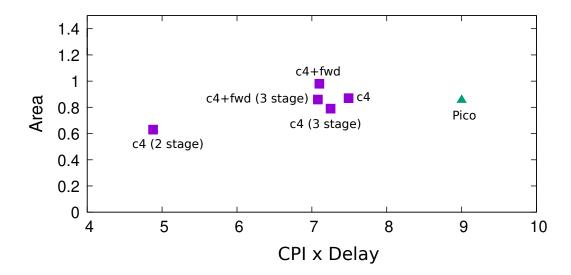

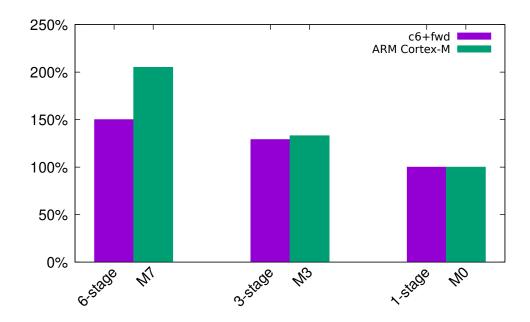

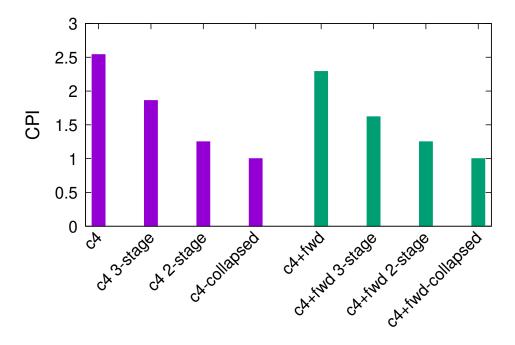

| 4.1<br>4.2 | Merging two stages together results in the "forward" connections between them going away while the "back" connections between them are maintained Fluid cores are competitive against manually generated Non-Fluid RISC-V cores.                                                                                                     | 55                              |

| 4.3        | The Pico CPU has a CPI of 4, giving it a lower overall performance than the Cliffs, despite its favorable area/delay stats. This figure also shows that the                                                                                                                                                                          | 60                              |

| 4.4        | performance fluctuations from merging stages is not constant                                                                                                                                                                                                                                                                         | 61                              |

| 4.5        | automatically transformed cores can be similar to well-tuned cores implemented manually                                                                                                                                                                                                                                              | 63                              |

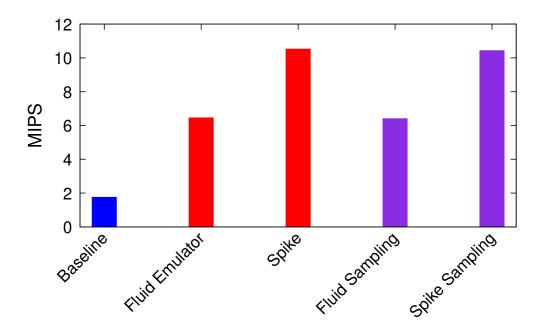

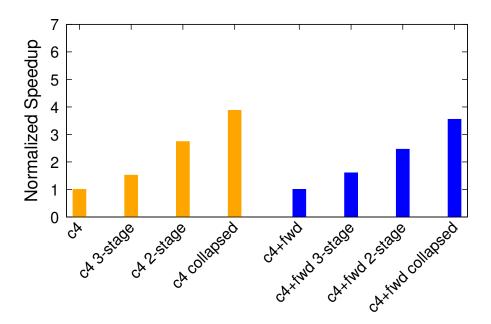

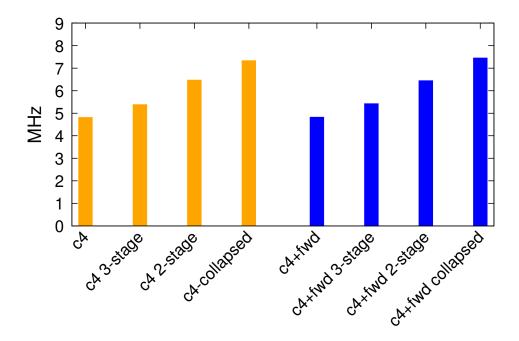

| 4.6        | baseline simulation. It is also less than $50\%$ slower than Spike, a C emulator Collapsing stages together improves the overall simulation speed, with com-                                                                                                                                                                         | 64                              |

| 4.7        | pounding benefits as more transformations are done                                                                                                                                                                                                                                                                                   | <ul><li>66</li><li>70</li></ul> |

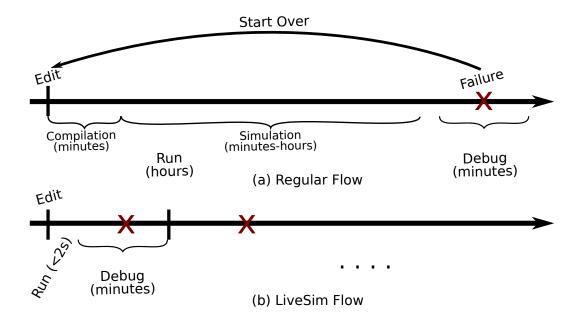

| 5.1        | The proposed workflow for LiveSim is to allow iterations within a few seconds. This contrasts with the traditional flow where after a change, there is a lot of latency in each iteration. With the much faster ERD loop, enabled by LiveSim, productivity is expected to improve. (Picture credit: R. Possignolo <i>publication</i> |                                 |

| 5.2        | pending                                                                                                                                                                                                                                                                                                                              | 75                              |

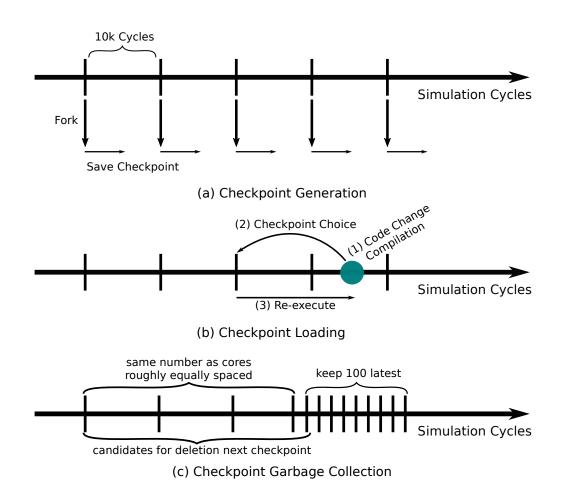

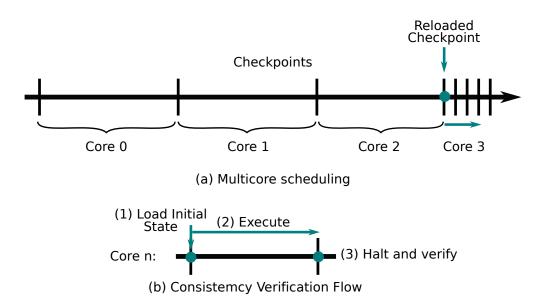

| 5.3<br>5.4 | Possignolo <i>publication pending</i> )                                                                                                                                                                                                                                                                                              | 84<br>86                        |

|            | cores. (Picture credit: R. Possignolo <i>publication pending</i> )                                                                                                                                                                                                                                                                   | 98                              |

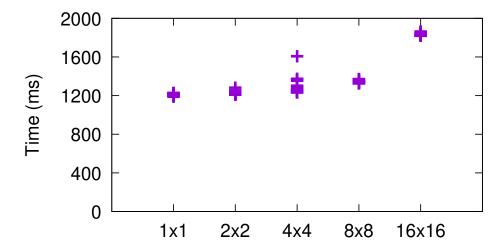

| 5.5 | LiveSim can not reload in less than 2 seconds from small PGAS with 1 node          |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | to large mesh with 256 PGAS multicore ( $16 \times 16$ ). Even in the case where a |     |

|     | stage was duplicated hunderds of times in the design, the latency required to      |     |

|     | update the code for all instances of that stage is dominated by the parsing and    |     |

|     | compilation costs, which remain constant                                           | 100 |

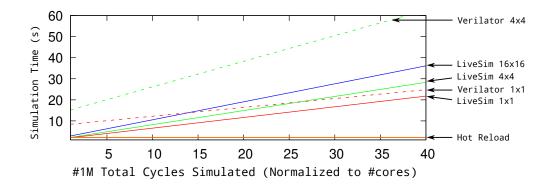

| 5.6 | Even without checkpoints LiveSim has a faster starting (ERD) and a faster for      |     |

|     | large PGAS                                                                         | 103 |

## **List of Tables**

| 3.1  | Liam adds some new constructs which helps the programmer manage elastic behavior abstractly                                                                | 31  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1  | Cores used in the evaluation                                                                                                                               | 58  |

| 5.1  | Pyrope's data structure is designed to minimize the amount of information needed to represent the architecture                                             | 81  |

| 5.2  | LiveSim commands. (Stage/tb)-handle variables refer to the handle column on Table 5.3. Stage-name variables refer to the corresponding columns in Ta-      |     |

|      | bles 5.4 and 5.5                                                                                                                                           | 89  |

| 5.3  | The Object Library Table contains a listing of all the objects LiveSim could find in the shared object libraries on its path                               | 89  |

| 5.4  | The Pipeline table. Contains a name to pointer reference for each pipeline object active in the session.                                                   | 89  |

| 5.5  | The Stage table. Contains a pointer reference for each stage of each pipeline                                                                              | 90  |

| 5.6  | <b>Update metadata:</b> when LiveCompiler recompiles a pipeline, stage, or test-                                                                           |     |

|      | bench object it sends a metadata update to LiveSim, shown below                                                                                            | 91  |

| 5.7  | If the register names do not completely match from version to version, transformation rules are applied to provide a deterministic way to load checkpoints |     |

|      | from the old version to the new one                                                                                                                        | 94  |

| 5.8  | The Register Transform History Table lists the changes to an architecture's reg-                                                                           |     |

|      | ister topology require to translate the system's state from one version to the                                                                             |     |

|      | next. It is structured to allow for branching                                                                                                              | 95  |

| 5.9  | Compilation time for LiveSim and Verilator. Hot Reload can swap a module in                                                                                |     |

|      | under 2 seconds. Even full compilation with LiveSim is faster than with Verilator.                                                                         | 102 |

| 5.10 |                                                                                                                                                            |     |

|      | nificantly                                                                                                                                                 | 104 |

#### **Abstract**

Pyrope: A Latency-Insensitive Digital Architecture Toolchain

by

#### Haven Blake Skinner

This paper proposes a new toolchain for digital architecture development which is designed to leverage Fluid Pipelines, a variant of latency-insensitive (LI) systems developed at the UCSC Micro-Architecture (MASC) Lab. Prior work on Fluid Pipelines and other LI systems has shown that they have promising properties which can be leveraged in various ways to aid in digital architecture design, especially when developing and manipulating large digital architectures, but that there are also challenges when working with this type of system. This paper presents Pyrope, a toolchain designed for developing Fluid Pipelined digital architectures. The toolchain includes a custom hardware description language and optimizations for simulation, synthesis, and verification which leverage Fluid Pipelines. The final section of this document presents LiveSim, a live development environment built on top of Pyrope, which uses incremental compilation and hot binary reloading to update simulation results based on code changes in seconds, even for large architectures.

### Acknowledgments

I would like to thank my parents, who put me on this path by raising me to value learning, the sciences, and academic research. Without their love and continuous support this PhD would not have been possible. I would also like to thank Lourdes, my girlfriend, was also a rock of support through the most difficult times in my grad school career.

My deepest gratitude also goes out to my advisor, Jose Renau, who provided the initial vision vision for Pyrope I had the privilege of developing, and who continued to support the project, and me, even when things were difficult. The same goes for the rest of the students of the MASC lab, especially Rafael Possignolo who was a close collaborator, and lead researcher for much of the early work on Fluid Pipelines.

I would finally like to thank the other friends, colleges, teachers, and many others who've influenced and inspired me over the years.

## **Chapter 1**

### Introduction

Be careful starting something you may regret.

Publilius Syrius, Maxims

Over the last several decades we have seen digital architectures scale from a few thousand logic units, to billions. Being able to develop systems of this size and complexity has required the continued improvement of tools which enable engineers to reason about, implement, and verify these systems.

Despite all the prior progress, however, the digital architecture design process still has significant problems, and these problems are becoming more acute as architectures continue to scale in size and complexity. Hardware design is notorious for using programming languages such as Verilog and VHDL which have limited abstraction capabilities, for example.

More importantly, the vast majority of modern architectures are designed around a paradigm called the *clock-synchronous pipeline* (further discussed in Chapter 2.1.2), which has

the side effect of closely integrating the behavior of the system with its timing attributes (maximum clock frequency). This forces hardware developers to lock down design decisions such as the target clock frequency and/or the number of stages early in the design process, making it difficult to change later.

Another significant source of inefficiency in the hardware design process, which particularly affects debugging and verification, is the long latency between when a developer makes a change to the code, and when they can see the result of that change. This is due to both the time required to recompile the updated architecture, and the fact that bugs often occur after tens of thousands, hundreds of thousands, or even millions of cycles or more, and thus the simulation must be rerun to that point to access the results of that change. Sometimes developers test their systems on FPGAs rather than software simulations since those can run cycles faster, however FPGAs require more time to recompile since they require additional steps (place-and-route, uploading bit file). This paper refers to the time required between making an edit, and seeing the results, as the *edit-run-debug* (ERD) latency, that for modern digital architectures can easily be a half hour or more. Prior research has shown that long time intervals between input and feedback hinders productivity [31,41,57], a fact that is intuitively true to developers as well.

This paper proposes a new digital architecture design flow to address these issues, based on a variant of Latency Insensitive (LI) systems developed at the UCSC MASC lab: Fluid Pipelines. Fluid Pipelines, like all latency insensitive systems, are distinct from the traditional clock-synchronous pipeline commonly used in hardware design in that their behavior is independent of the latency between any two blocks. At the MASC lab, we have come to believe

that this type of design paradigm holds a lot of promise for managing the ever increasing size and complexity of digital architectures.

In the subsequent chapters I will describe a new toolchain for developing Fluid Pipeline-based architectures. It is built around the Pyrope programming language, which is designed for implementing latency insensitive systems, and its compiler, which is designed to leverage them in a variety of ways. The language and compiler were designed to address various shortcomings with the current digital architecture design flows.

The specific contributions of the Pyrope project are summarized below.

A major motivation for the Pyrope project was to design a toolchain which could (1) leverage LI pipeline transformations. Chapter 4 shows how this can leveraged to aid the simulation, synthesis, and verification process. These optimizations depend on fundamental differences between Fluid Pipelines and traditional clock-synchronous circuits.

A major challenge with this project is that the Fluid Pipeline paradigm is fundamentally different from the developer perspective as well, as the system must be designed to behave consistently regardless of the latency between any two sections of the architecture. For the hardware developer, this means implementing LI behavior using simple handshake protocols and/or message passing queues, which is difficult, error prone, and not very portable. We in the MASC lab believe that the difficulty in working with these types of systems at the synthesis level is a major hindrance to their adoption.

To address this, a core part of the Pyrope toolchain is the Pyrope hardware description language, which is built on top of (2) the Liam programming paradigm to implement

latency-insensitive behavior implicitly (Chapter 3). Liam, which is an acronym for Latency-Insensitive Actor-Model is a custom programming paradigm which allows the programmer to describe LI behavior using the control flow structure of the source code. Though internal use by myself and other researchers, we found that this made RTL code easier to reason about in general, vastly decreased the amount of code which had to be written, without sacrificing control or tunability. Pyrope also provides a stronger type system than traditional HDLs to decrease the occurrence of overflow and other sorts of common bugs.

The Pyrope compiler is also designed for speed, to address another problem with digital architecture development discussed above. In Chapter 5, this thesis shows that for large architectures, the Pyrope compiler (3) supports incremental compilation and hot reloading of a simulation binary. I am not aware of any other hardware design flow that supports this. Incremental compilation and hot reloading allow Pyrope to significantly outperform Verilator (Chapter 5.6) in both compilation and simulation speed.

Chapter 5 also shows how the Pyrope compiler, along with incremental compilation, simulation binary hot reloading, and what is referred to as *checkpoint transformations* (Chapter 5.4.4), can be used to implement a **(4) digital architecture live development environment.**This requires implementing the Pyrope compiler into a Software-as-a-Service (SaaS) tool. As this paper demonstrates, Pyrope's live development environment is not just for toy designs, but can scale to even large architectures, such as as mesh of 256 RISC-V processors.

The remainder of this document is organized as follows: Chapter 2 discusses prior work on latency insensitive systems, fluid pipelines, and the Pyrope programming language. Chapter 3 focuses on Liam, demonstrating how Pyrope uses it to implement fluid behavior,

followed by a detailed discussion of its implementation. Chapter 4 discusses pipeline transformations, how they are integrated into the compilation flow, and how they can be leveraged to aid in various parts of the digital architecture design process. Chapter 5 discusses the internal design of the Pyrope compiler and the LiveSim live development environment. That chapter also evaluates the viability of LiveSim to provide the response times necessary to deliver a live development experience, even with large architectures, and also compares the performance of the Pyrope compiler to Verilator [18], an open-source Verilog compiler widely used in industry and academia. Finally, Chapter 6 offers some concluding remarks.

## Chapter 2

## **Background**

The wrath of the gods may be great, but it certainly is slow.

Decimus Iunius Iuvenalis, Satirae

Since the Pyrope project is an intersection of several research topics, I divide the background into the following sections: Section 2.1 discusses Fluid Pipelines, a variation of Latency Insensitive systems on top of which the Pyrope toolchain is built. Section 2.2 discusses other programming and hardware description languages which influenced Pyrope. Finally, Section 2.3 discusses hardware simulation, beginning with some background information on the challenges in that area, and on how Fluid Pipelines can be used to address them, both in prior work and in work presented in this paper.

### 2.1 Fluid Pipelines and the Pyrope Project

The goal of the Pyrope project is the build a digital architecture development toolchain based around Fluid Pipelines, a variation of Latency Insensitive (LI) systems. The project was inspired by some inherent challenges to developing large system with the traditional model for digital architecture design: *the clock-synchronous pipeline*. An in-depth discussion of this can be found in Section 2.1.2. Prior work on LI systems [36] [51] [45] have suggested that this model could be a good solution to manage some of those issues. Furthermore, some foundational work conducted at UCSC [63] [64], to which I had the privilege to contribute, shows that Fluid Pipelines could make better use of pipeline transformations than previous hardware based LI implementations, adding further value to this model.

The rest of this section is organized as follows: Section 2.1.1 provides an overview of the Fluid Pipelines model, and shows how it is implemented in synthesis. Section 2.1.2 compares Fluid Pipelines to the standard model for digital architecture design, the clock-synchronous pipeline. Section 2.1.3 differentiates Fluid Pipelines from other Latency Insensitive systems. Finally, Section 2.1.4 draws on all this to discuss the motivations for the Pyrope project.

### 2.1.1 Fluid Pipelines

Fluid Pipelines are a variation of Latency Insensitive systems developed in the MASC lab at UCSC [63] [64]. They are designed to address many of the challenges in work with clock-synchronous pipelines, the dominant model for developing digital architecture, discussed in Section 2.1.2. Fluid Pipelines differ from the clock-synchronous paradigm in that their func-

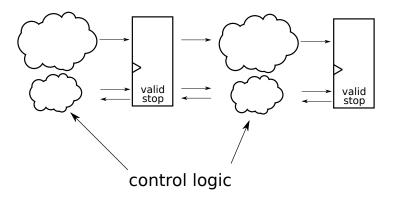

**Figure 2.1:** A fluid pipeline replaces synchronous registers with fluid registers, which use *valid* and *stop* signals to execute a simple handshake protocol to update its internal state.

tional behavior is not sensitive to changes in latency between any two points in the pipeline.

This is further discussed in Section 2.1.2.

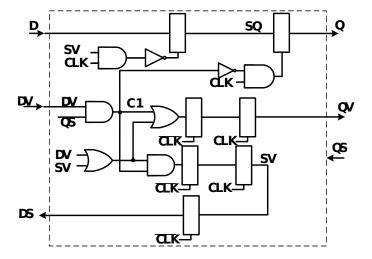

**Figure 2.2:** Fluid Registers are used in place of traditional clock-synchronous registers in Fluid Pipelines. They contain enough internal buffering to allow back pressure to propagate without dropping data. (Picture credit: R. Possignolo [65])

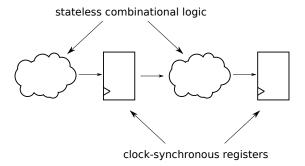

**Figure 2.3:** The clock-synchronous pipeline is the standard model for developing modern digital architecture. A side effect of doing so is that the system's behavior becomes closely tied to its timing.

Figure 2.1 shows a Fluid Pipeline. It is made up of combinational logic blocks divided by *fluid registers*, which have *valid* and *stop* control signals to flag valid data and handle back pressure. These control signals add LI behavior (waiting for valid data, handling back pressure without dropping packets) to the architecture.

The internal design of a fluid register is shown in Figure 2.2. Fluid registers are made using clock-synchronous registers and other control logic, implementing the equivalent of a two entry buffer. This provides exactly enough space for the *stop* signal to propagate backwards without having to drop data.

#### 2.1.2 Clock Synchronous vs. Fluid Pipeline Architectures

The traditional model for developing digital architecture is the synchronous pipeline, shown in Figure 2.3. In a synchronous pipeline, behavior is modeled as blocks of stateless combinational logic divided between clock-synchronous register blocks. This section discusses

some fundamental problems the synchronous pipeline design paradigm presents, and how the Pyrope Project hopes to address those issues with Fluid Pipelines.

One major implication of modeling a digital architecture as a clock-synchronous pipeline is that the maximum frequency at which the system can be clocked is a function of the longest propagation delay between any two registers, also referred to as the *critical path*. Creating an architecture with a fast clock speed means minimizing the critical path by carefully dividing the combinational logic between registers.

This adds many difficulties to the development process. First, it is difficult to precisely know the maximum clock speed of a circuit until after it has been implemented and the code can be analyzed by a synthesis tool. If the circuit is too slow, the only way to increase the maximum clock speed is to manually divide and/or redistribute application logic between registers. Not only is this known to be an open-ended and difficult problem [50, 70], but also makes it hard to share code between projects with different timing goals, since for systems that can run at a slower speed, removing registers saves on energy usage.

This type of tuning is critical for implementing modern digital architectures and is one of the reasons why specialized hardware description languages, which allow developers to work on the register-transistor level (RTL), are used for this purpose. Although circuits can be synthesized from more traditional programming languages, a technique referred to as *high-level synthesis*, this is rarely used in modern hardware design because the levels of abstraction make it more difficult to control what is synthesized.

Another issue with clock-synchronous pipelines is that often the clock cycle latency is what is keeping the system in sync, which makes the entire pipeline more difficult to manip-

**Figure 2.4:** Situations which require the data path to branch often result in code that contains hidden assumptions about the latency between different sections of the pipeline, which makes the system harder to manipulate in general.

ulate. In Figure 2.4, adding or removing any block on either of the branches requires adding or removing and equivalent amount on the other branch or it could risk creating a timing error. Such architectures often have additional forward or back paths between stages in the pipeline, which often contain additional hidden assumptions about the clock latency between them. This is another factor which makes synchronous pipelines harder to work with.

Unlike clock-synchronous pipelines, Fluid Pipelines can more easily manipulated at a high level as there is no risk of creating timing errors. There is also no issue with stages being in different timing domains so long as the setup and hold conditions for the hardware components are not violated. This advantage was a motivation for early work on LI systems which proposed them as a means for more robust on-chip communication in the face of long wire lengths and arbitrary variations in latency at interconnects [36].

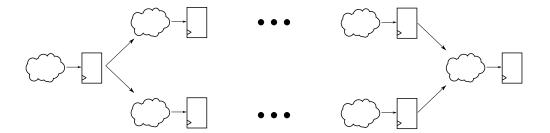

Another important advantage that Fluid Pipelines have over pipelines designed under the clock-synchronous paradigm is that Fluid Pipelines can be transformed more aggressively, as shown in Figure 2.5. This figure shows that fluid registers can be added, removed, or moved between blocks of combinational logic without regard to the underlying behavior of the system.

**Figure 2.5:** Latency insensitive pipeline transformations allow for adding or removing register blocks (Recycling) or moving logic between register blocks (Retiming), without changing behavior. (Picture credit: R. Possignolo [64])

This is possible because Fluid Pipeline transformations can leverage the fact that since behavior is independent of the latency between stages, dropping that latency to zero, or in other words merging two stages, can safely be done without breaking functionality. Likewise, increasing the latency of a region, by adding more registers, can also be done safely. Cortadella, et. al. refer to such transformations as "behavior preserving" and "correct-by-construction", where they were first proposed [45].

Leveraging transformations on Fluid Pipelines is a major motivation behind the Pyrope project. Section 2.1.3 shows that Fluid Pipelines differ from other LI systems in a way that allows developers to make better use of transformations, and Chapter 4 shows how transformations are integrated into the Pyrope compilation flow.

#### 2.1.3 Fluid Pipelines vs. Other Latency Insensitive Systems

Fluid Pipelines are a type of LI system in that their behavior is not sensitive to changes in latency inside or outside of the architecture. There are a variety of types of LI systems including hardware implementations [36] [48] [51] [43], and distributed networks such as those built around TCP/IP. This section makes a distinction between prior hardware LI systems, fluid pipelines, and distributed networks in that prior hardware implementations provide not just a LI guarantee, but an even stronger guarantee which this thesis refers to as *sequence-invariance*. The fact that Fluid Pipelines provide latency insensitivity but not sequence-invariance allows it to avoid the performance degradation that other hardware LI systems experience with pipeline transformations.

Sequence-invariance means that not only is the system latency insensitive, but that the order of packets through any given point is also invariant with regards to latency. This is a stronger guarantee than is given by latency-insensitive systems such as TCP/IP networks, since the latency between routers can affect the path that a packet takes to its destination. The contents of the packet, however, are generally unaffected.

Early work on LI systems proposed them as a means of providing more robust on-chip communication [36]. In 2010 Cortadella et al proposed adding *elastic buffers*, their version of fluid registers, to clock-synchronous circuits as a means of transforming them while preserving their behavior [45]. For these applications, guaranteeing sequence-invariance is an implicit requirement. To accomplish this, in cases where the pipeline branches, each path must remain balanced by adding elastic buffers on the shorter paths. Furthermore, when dealing with se-

quential loops in the pipeline (a loop in the pipeline's data path, not to be confused by software program loops) design tools are unable to insert stages in those regions [46]. Combined, these issues have been shown to degrade overall throughput [34, 37, 51].

Sequence-invariance can also be a useful tool for verification, since if a system can be shown to have this property, the verification procedure can safely make that assumption. The Kahn Process Networks (KPN) [52] is the seminal work which formalizes sequence-invariance. It does this by modeling the nodes of the network as reading from unbounded FIFOs, with only blocking reads and non-block writes. Programmers are expressly forbidden from executing any sort of non-blocking read, or in other words, is not allowed to check if data is available on a port and make a decision based on that. Another way of thinking about this restriction is that programmers are forbidden from writing code which takes the current network conditions, i.e. the presence or absence of a packet in the input buffer, into account on any sort of decision it makes. In doing so, a KPN's behavior is guaranteed to be independent of those factors. KPNs have been applied to modeling real time systems [6], high-speed graphics processing [40], and even circuit design [43].

In the foundational work on Fluid Pipelines we argue for a more lax latency insensitive guarantee, however, as this allows the system to better leverage pipeline transformations. In "Fluid Pipelines: Elastic Circuitry Meets Out of Order Execution" [63], a paper to which I was a contributing author but not the primary one, we show that overall throughput can be improved if the system is allowed to relax the ordering guarantee. In practical terms, this means that architectures implemented with fluid pipelines must be designed to function properly even if the arrival order of some packets is changed due to pipeline transformations. Architectures

designed on top of a KPN based paradigm can safely assume that the arrival order of packets will not change. We justify this in another paper to which I contributed: "Fluid Pipelines: Elastic Circuitry without Throughput Penalty" [64], where we show that removing the ordering guarantee completely eliminates the throughput degradation observed in earlier work on latency insensitive pipeline transformations.

This means the Fluid Pipelines implicitly cannot be KPNs, since their ability to fully leverage pipeline transformations is dependent on allowing packets to reorder themselves.

The distinction between Fluid Pipelines and KPNs is expressed in practical terms by the Pyrope language, discussed in detail in Chapter 3. Pyrope provides an operator ("?"), which if applied to an input port will return *true* if that port is valid (or in other words, that a packet is present), *false* otherwise. Used with an "if-then-else" block, this gives the developer the ability to check if that port is valid and act differently depending on the outcome. This is expressly forbidden in a KPN. An equivalent operator exists for outputs to indicate back pressure ("!"), which is likewise forbidden.

The distinction between Fluid Pipelines and KPNs is expressed in terms of synthesis blocks as well. Figure 2.6 shows the *merge* operator from "Fluid Pipelines: Elastic Circuitry Meets Out-Of-Order Execution" [63]. This is a combinational logic block with ports for two data inputs:  $data_{i1}$  and  $data_{i2}$ , and one data output:  $data_o$ . Each port has corresponding valid and stop control signals. The stop signal is always in the opposite polarity of its corresponding data port.

This circuit merges the inputs  $data_{i1}$  and  $data_{i2}$  into output  $data_o$ , giving preference to  $data_{i1}$ , and holding either or both input with the stop signals ( $S_{i1}$  and  $S_{i2}$ ) until they are used.

**Figure 2.6:** The "merge" or "fluid mux" operator selects an input based on which is valid. This can break sequence-invariance. (Picture credit: R. Possignolo [64])

More specifically,  $data_o$  is connected to  $data_{i1}$  if  $V_{i1}$  is true,  $data_{i2}$  otherwise.  $V_o$  is true if either  $V_{i1}$  or  $V_{i2}$  is true.  $S_{i1}$  is asserted if  $data_{i1}$  is valid  $(V_{i1})$  and if the stop input,  $S_o$  is asserted (back pressure).  $S_{i2}$  if  $data_{i2}$  is valid and back pressure is present  $(S_o)$ , or is  $V_{i1}$  is true, since  $data_{i1}$  is given priority.

Despite the complexity added by the fluid control signals, the behavior of this circuit is rather straight-forward. This circuit violates the KPN protocol nonetheless because it decides which input to select based on what is valid. This means that its behavior could be affected by the relative latencies of the input control signals.

Relaxing the ordering guarantee would certainly increase the complexity of the verification process. Chapter 4.6 proposes a verification technique that leverages Fluid Pipeline transformations, which could be helpful in alleviating some of the added complexity. In addition, speaking from anecdotal experience in making Fluid Pipelined processors, I can say that

the verification complexity can also be reduced with better architecture design. Fully addressing the challenge of Fluid Pipeline verification is outside the scope of this paper, however.

Although we are not aware of any other projects strictly targetting hardware synthesis which are based on non-delay-invariant LI systems, Gorilla++ [58] is a programming language and toolchain designed for creating custom accelerators targeting streaming input processing which does have some similarities. The general flow of Gorilla++ is to compile the application into a dataflow representation, then leverage a flow similar to HLS to optimize the dataflow based on available accelerators. Most nodes in Gorilla++ are compatible with the KPN paradigm, but it also allows for nodes that can reorder packets, but may not change them, allowing it to violate the KPN paradigm for operations such as opportunistic merge. That feature was added because, as the author notes, many stream processing applications have relaxed ordering guarantees. Although the application is rather different, there are some interesting parallels.

#### 2.1.4 Motivations for the Pyrope Project

As digital architectures continue to scale in size and complexity, so too will the difficulties associated with managing such systems under the clock-synchronous pipeline model. Latency Insensitive systems have many properties that can be helpful in managing large systems, and Fluid Pipelines expand on that model to implement architectures as a fully distributed system. The benefits of developing an architecture this way are shown in the foundational work on Fluid Pipelines [63] [64], demonstrating unrestricted use of pipeline transformations at no cost to throughput.

The early work on Fluid Pipelines also showed challenges in employing this paradigm. There can be no latency-related assumptions in the application logic, as is common when developing with clock-synchronous pipelines. More significantly, the *valid* and *stop* control signals must be implemented properly, both as inputs and outputs, for every port. When implementing Fluid Pipelines with Verilog or traditional programming languages such as C, this results in control logic being mixed in with application logic, in a manner that is difficult to separate with traditional programming abstraction constructs. Making a mistake in such control logic can result in unpredictable and difficult to find errors, such as deadlocks and invalid data being interpreted as valid data.

The goal of the Pyrope project is to bring the advantages of working with Fluid Pipelines to developers, and help manage the challenges. It employs an Actor-Model based programming paradigm designed to implement fluid behavior implicitly, allowing the developer to manipulate the behavior of the system within the bounds of the Fluid Pipeline paradigm, while sparing them from implementing the logic directly and the bugs associated with it. This is discussed in Chapter 3. The Pyrope toolchain also provides an interface to specify pipeline transformations as part of the compilation flow, discussed in Chapter 4.

### 2.2 Languages

The name "Pyrope" comes from the pyrope stone, which is similar in appearance to ruby. Pyrope was originally envisioned as bridging the gap between low-level HDLs and scripting languages using fluid pipelines.

Before developing the *abort-based* paradigm described in Chapter 3 we experimented with a variety of solutions to the problem of managing LI behavior from Pyrope, some which were little more than syntax sugar on top of Verilog macros, and others that were inspired by functional languages, before settling on a paradigm similar to the *Actor Model*. In addressing this problem, we had to balance the goal of simplifying the fluid pipeline development process with the need to still provide full control to the user.

This section discusses other programming and hardware description languages which are similar to, and/or have influenced Pyrope. I first discuss other HDLs in Section 2.2.1, I then present a little background on the Actor Model in Section 2.2.2, and finally some other programming languages we looked to for inspiration in Section 2.2.3.

### 2.2.1 Hardware Description Languages

By far, the dominant HDL in academia and industry for developing synthesizable digital architectures is Verilog. It can be thought of as the "assembly of hardware" as it provides developers with low level control to develop systems at the *register-transistor level* (RTL).

There have been a variety of projects to create better HDLs. Bluespec [61] could be considered a functional language. Circuits are inferred based on any number of "rules", one or more of which could evaluate depending on the inputs to the module. Bluespec's paradigm is perhaps most similar to Pyrope's out of all the HDLs listed here. Pyrope, however, is designed for creating Fluid Pipelines, this both restricts the programmer and provides fundamental guarantees (further discussed in Chapter 3), while Bluespec is a general purpose HDL. Another key

difference is that clock-barriers in Pyrope are implicit, since they can change based on pipeline transformations, while clock-barriers in Bluespec are explicit.

Chisel [29] is an HDL developed at UC Berkeley and built on top of Scala, providing a stronger type system better abstraction capabilities than Verilog. PyMTL [59] and PyRTL [39] are built on top of Python.

Writing RTL code for synthesis is distinct from other types of programming in that the developer cannot use constructs such as loops and "malloc"-ing from main memory which cannot be translated directly into combinational logic (transistors) and finite sized storage units (registers).

Attempts to synthesize circuits from code with more traditional programming constructs is generally referred to as "high-level synthesis" (HLS). There are a variety of projects aimed at doing this [16, 35, 71]. A major limiting factor in these projects' applicability is the importance or carefully balancing logic between register blocks in order to achieve a high clock frequency. This is more difficult when having the tool synthesize something like a loop, which will require it to infer a state machine to implement that behavior, including multiple registers and feedback paths.

Although there are similarities between Pyrope and many HLS flows, the key distinguishing feature is that HLS includes some sort of automated algorithm to optimize the resulting system for features such as frequency and area. In contrast, with Pyrope the architecture would be developed at the RTL level, enabling for high-level, but manual transformation, tuning, and optimization by leveraging latency insensitivity.

Chapter 3 discusses how Pyrope implements LI behavior, which involves inferring logic. We distinguish this from HLS flows because using Pyrope's operators, the developer has low-level control over the inferred logic network. Pyrope does not support high-level constructs such as open-ended loops.

#### 2.2.2 The Actor Model

Pyrope's LI paradigm is based on the *Actor Model*, which is a programming paradigm first proposed in 1973 [49] as an artificial intelligence computational model. It proposed viewing the system as an interaction between *actors*, which are atomic units that communicate via message passing. Specifically, actors have the ability to: send a message, update its internal state, or create new actors.

The Actor Model has served as a concurrency model [1,11,24] and a general platform for parallel and distributed system programming [8]. It has been used in the backends of various design and simulation tools [12,21,33] and there are Actor Model libraries available for a variety of programming languages [1,11]. The Cal Actor Language [3], is a programming language built directly on top of the actor model.

We are not aware of any HDL Actor Model libraries, however, or any HDLs which use the it as part of their design philosophy. We were attracted to it as we saw parallels between fluid pipelines and heterogeneous concurrent systems where the Actor Model is well suited to simulate. It also adapts well to an imperative programming style, that we also found appealing.

#### 2.2.3 Other Programming Languages

There were other languages we looked at that tackled similar problems, but from which we ultimately did not draw inspiration on for Pyrope.

Synchronous programming languages like Esterel [6] and Lustre [62] are languages designed for implementing *reactive systems*, which are systems that must react to their environments within specific time constraints. Esterel, for example, defines modules in terms of input and output signals which are either "present" or "absent" at any given time, and provides constructs to do things like wait for signals and emit signals.

These types of languages are more commonly used to implement robust, time-critical systems such as flight-guidance systems, however we did see an analogy between a language based around objects with react to signals, and a fluid pipeline of stages that process packets when they arrive. There has also been prior work on synthesizing hardware with Esterel [42]. We ultimately went with a paradigm that was more similar to widely used general purpose programming languages such as C and Python.

### 2.3 Fluid Pipelines and Hardware Simulation

Hardware simulation is the process of implementing a digital architecture, or some part of a digital architecture, in software. Simulation is an essential tool in digital architecture design, and also often forms a bottleneck in many parts of the development process. This section provides some background on hardware simulations and why we in the MASC lab saw the potential for leveraging Fluid Pipelines to address some of the challenges in this area.

Architecture simulation can be broadly divided into two categories: cycle accurate and non-cycle accurate. Cycle-accurate means that the implementation can reproduce the architecture's behavior cycle by cycle. This is not generally possible without being able to represent the architecture's entire state, thus a cycle-accurate representation is required to *synthesize*, or generate a physical implementation of the system, and likewise an implementation which can be used for synthesis can be simulated cycle-accurately.

Cycle-accurate implementations of modern architectures are often done at the register-transistor level (RTL), and the system is generally implemented as a clock-synchronous pipeline. The exception to this is high-level synthesis (HLS), though this is generally used for fast prototyping, as HLS underperforms RTL implementations.

Non-cycle-accurate representations, cannot reproduce the architecture's behavior cycle by cycle. Examples include ESESC [28] and Gem5 [32], which simulate some part of the architecture's behavior, such as the performance of its branch predictor or estimated power usage. These types of simulations are better for early design-space exploration, such as studying the trade-offs of design decisions like the architecture's cache size, since they can be implemented more quickly than a cycle accurate simulation, and can cover ground more quickly in long testbenches.

These simulation options present a trade-off that hardware architects are forced to contend with. Cycle-accurate implementations are required for synthesis, but require more effort to implement and are slow to simulate. Non-cycle-accurate implementations cannot be used for synthesis since they do not contain complete information about the system. Likewise, there is no easy way to extract a non-cycle-accurate simulation from an RTL implementation

without significant planning and infrastructure since clock-synchronous RTL implementations closely tie timing and behavior.

We in the MASC lab felt that Fluid Pipelines could be leveraged to address this tradeoff. As with all LI systems, Fluid Pipelines can be more easily manipulated at a high-level

since their behavior is independent of timing. This would make it easier to isolate different

parts of the architecture and test them in different contexts. Conceptually simple optimizations,

such as replacing a floating point unit with a software floating point operation, is simple in a LI

architecture, but near-impossible in a clock-synchronous pipeline.

Fluid pipelines' ability to be transformed, changing their timing without changing their behavior, could be further leveraged to blend cycle-accurate and non-cycle-accurate simulation. Chapter 4 shows how 4 and 5-stage RISC-V CPUs can be transformed into single-stage CPUs. Compiled to C, these implementations are functionally similar to software emulators; that chapter also compares their performance against the official RISC-V reference emulator, which is written in C.

Chapter 4 also shows how transformations cause some architectural optimizations, such as branch predictors and forwarding paths, redundant, providing a speed up by simplifying the system as well, analogous to a non-cycle-accurate simulation.

These optimizations directly allow developers to trade speed for cycle-accuracy, but using the same code-base, rather than having to implement the system multiple times.

Prior work has also proposed other types of hybrid simulations for which Fluid Pipelines could also be helpful.

SMARTS [74] sampling framework combines a slow, cycle-accurate simulation and a fast, non-cycle accurate simulation, to provide faster measurements of power-usage and CPI (cycles-per-instruction) over a long testbench. With Fluid Pipeline Transformations, SMARTS could be implemented with one code base.

Another project [68] addresses the problem that not only is cycle-accurate simulation slow, but providing cycle by cycle values of every variable in the simulation is even slower, even though this is generally needed for effective debugging. The authors propose using a fast simulation which contains a minimal state representation of the system, taking checkpoints, then using the checkpoints to do a detailed simulation in parallel. This system could also be implemented with one code base with Fluid Pipelines.

# Chapter 3

# The Liam Programming Paradigm

You wonder why travel did not improve you? You had yourself as a companion.

Seneca the Younger, Epistulae Morales

This chapter discusses the Latency-Insensitive Actor-Model (Liam) paradigm, that is central to how Pyrope is used to create Fluid Pipelines. First, Section 3.1 discusses how Liam works, and shows how it can be used with code examples. Next, Section 3.2 shows how Liam is implemented by the Pyrope compiler.

## 3.1 Describing Fluid Behavior with Liam

#### 3.1.1 Overview

The motivation behind Liam, and what it adds to Pyrope, is shown in Figure 2.1. We can see that the added difficulty in working with fluid pipelines, or any type of latency

insensitive system, is the additional work of implementing logic for the control network to drive the *valid* and *stop* signals (or the equivalent). If one were implementing a fluid pipeline architecture in Verilog, one would have to implement all of that logic manually. Instead, Liam provides a paradigm designed to infer that network based on the structure of the code.

The way we manage this is by leveraging the Actor Model, as discussed in Section 2.2.2. In the abstract, the Actor Model defines the system in terms of actors who can affect the state of the system by either updating its internal state or sending messages to each other (external state). To be clear, this does not refer to a finite, countable, number of states as in a finite state machine, but an uncountable number of states described by the value of each actor's internal memory and the packets in its message passing queue. Liam provides a mechanism to manage these state transitions in the abstract, and guarantee that they happen atomically. As an example, if the developer's intention is that a stage will send a packet and update an internal counter to reflect that, Pyrope code can be structured to guarantee that either both of those things will happen, or neither of them will.

The Pyrope compiler compiles Liam behavior into logic networks to drive the *valid* and *stop* control signals of Fluid Registers. Liam is not specific to HDLs however, and could be adapted by other languages and toolchains.

### 3.1.2 Liam within a Pyrope Architecture

Pyrope architectures are divided between any number of *pipes* and *stages*. Stages contain logic and have an internal state characterized by their internal registers and their IO

ports. Pipes instantiate stages, and can connect the IO ports of stage instances to each other, and to the pipe's own IO ports. They have no logic or internal state of their own.

Liam is designed to manage how data-path logic interacts with the control paths and ultimately the state of the overall system. Thus, it only applies to blocks with logic and state, referred to as *stages*, and not with *pipes*, which have neither.

As of now, all stages in Pyrope are implicitly fluid (although that will change in future versions). This means that each IO port is actually a fluid port with *valid* and *stop* control signals, and that logic to implement Liam behavior will be inferred for each of them by the compiler.

#### 3.1.3 Inferring Fluid Behavior

**Listing 3.1:** A Pyrope implementation of a simple multiplexer, with two data inputs: a,b, one data output: o and one select input: s If instantiated as a stage, fluid pipeline control logic will be inferred for its input and output ports.

Listing 3.1 shows an implementation of a simple multiplexer in Pyrope, which routes the data from one of its input ports to its output port based on a selector input. If this block is instantiated as a stage in another block, all of its inputs and outputs will be considered fluid inputs and outputs, which will each implicitly have their own *valid* and *stop* control signals.

To describe fluid behavior for this stage, Liam creates the concept of the stage's *state*, which includes the values of the block's internal registers, the values on its output ports (and whether or not that output port is valid), and the state of each input port (whether or not the block is asserting back pressure on that port). The Pyrope paradigm provides rules, or Axioms, 1 (Atomicity), 2 (Abortion), 3 (Consumption), and 4 (Isolation), to describe when and how a stage's state is updated.

**Axiom 1** (**Atomicity**) A stage is a block of code that evaluates from the top down. If it completes without aborting, it updates its state. All outputs written to are valid in the new state. All registers written to are updated. All inputs read from are consumed.

**Axiom 2 (Abortion)** A stage aborts when an invalid input is read, or an output with back-pressure is written.

**Axiom 3 (Consumption)** All valid inputs are held (back pressure) until they are consumed.

**Axiom 4 (Isolation)** An aborted stage does not consume any input, generate any valid output, or make any other changes to its state.

Liam adds the concept of stage aborting as a means of managing state. When an abort happens in a cycle, no inputs are consumed or outputs are produced. This concept only exists

within the programming language, and is based on the control flow structure of the stage. When synthesized, this behavior is implemented as combinational logic to drive a fluid register's *valid* and *stop* signals. Implementing Liam in synthesis is further discussed in Section 3.2.

Considering the axioms, if s is valid and equal to 1, the control flow will lead to line 7, otherwise it will lead to line 9. If s is valid and equal to 1, and a is valid, than both those inputs will be consumed and o will equal a; likewise if s is valid and equal to 0 with regards to input b.

The mux in Listing 3.1 actually acts more like a switch, as it will it will only consume one of the data inputs, a and b, each time it produces output. The data input which is not selected, or "consumed" will be held with the stop signal.

### 3.1.4 Liam-Specific Operators

The Liam paradigm includes operators designed to allow the programmer to check the state of an IO port, and make a decision based on that. The Pyrope version of these operators is shown in Table 3.1. The "Valid Check" and "Stop Check" allow the developer to check if an input is valid or if an output has back pressure without triggering an abort.

As stated in the Consumption Axiom 3 (Consumption), an input is consumed if it is read and the stage does not abort that cycle. The "Keep Statement" allows the user to prevent that, keeping the input on the next cycle as well. Finally the "Consume Statement" does the opposite, marking an input as read, and triggers an abort if the input is not valid. This is syntax sugar since the same could be accomplished by just reading the variable and not using the value, but it improves readability.

**Table 3.1:** Liam adds some new constructs which helps the programmer manage elastic behavior abstractly.

| Name              | Code form     | Description                            |

|-------------------|---------------|----------------------------------------|

| Valid Check       | var?          | Checks if an input or output is valid  |

| Stop Check        | var!          | Checks if an input or output stop flag |

|                   |               | is asserted.                           |

| Keep Statement    | keep input    | Prevents an input from being con-      |

|                   |               | sumed.                                 |

| Consume Statement | consume input | Explicitly consume an input.           |

Consider that for some application we may want this to act as a "fluid mux", and not a "fluid switch", meaning it should wait for both input ports to have valid values, then output one and drop the other. A stage with that behavior is shown in Listing 3.2. Pyrope has the syntax sugar *read*, that marks a port as having been read on that path. In a non-stage block this line has no effect. In a stage, however, the two *read* commands will force an abort unless the unselected input is also valid, and will cause that port to also be consumed when the state is updated.

By default, variables in Pyrope do not maintain their values across cycles. Those that do are marked with @. Placing the increment above the "if-else" block implements the desired behavior because if the stage fails to send a packet it will abort, preventing the increment of @sent\_ctr from going through. Placing the increment at the bottom of the block may be more intuitive, however.

As another example, it may be the case for some application that we would want a "fluid mux" which would consume the input on the unselected port if it is valid, but ignore that port otherwise. Listing 3.3 introduces the ? operator which checks if an input port is valid, without triggering an abort. An equivalent operator exists for output ports: !, which checks for the presence of back pressure.

```

1 mux :: {

s as input logical

a,b as input bits:32

o as output bits:32

@sent_ctr as bits:32

@ s e n t_c t r ++

if s {

o = a

10

read b

11

} else {

12

o = b

13

read a

14

15

```

**Listing 3.2:** This version of the mux will only produce output once both input ports have a valid value. The other port is read and discarded. It also maintains an internal count of how many packets it sent.

```

mux :: {

s as input logical

a,b as input bits:32

o as output bits:32

if s {

o = a

if b? { read b }

} else {

o = b

if a? { read a }

}

```

**Listing 3.3:** This version will only consume the input on the unselected port if it is valid, and will ignore that port otherwise.

The three examples 3.1 3.2 3.3 show the general idea behind Pyrope's abort-based paradigm. This paradigm allows the developer to manage the fluid aspects of the system, in other words the presence of valid and invalid data and back pressure, using the control flow structure of the stage. We found that it came naturally to reason about a stage's behavior in sequential terms, such as: "the stage gets to this line and aborts", or: "it checks for back pressure here, then continues", even though we knew that the logic that drives the control signals is actually evaluated in parallel in the synthesized system.

This also prevents some types of bugs we encountered when manually implementing fluid pipelines, such as invalid data accidentally being interpreted as valid data or data with back pressure being overwritten due to small typos in the control logic. Pyrope will not generate a control network which would act that way, that in our experience made fluid pipelines much more predictable to work with.

These examples also show why a tool which automatically converts a synchronous circuit like a mux attached into a clock-synchronous register to a latency insensitive system will never be ideal. The LI system contains additional vectors of control: the concept of valid/invalid data and of back pressure/consumption. Those vectors of control must be available to the developer or their ability to optimize and tune the system will be limited.

#### 3.1.5 Catching the Abort with "Try" Blocks

**Listing 3.4:** This stage will route a valid input from "inp" to the first available output port.

Liam models a stage's abort as an exception. If it is uncaught, the stage will abort, however the abort can be avoided if it is triggered inside a "try" block. Listing 3.4 shows a simple stage that will send its input to the first available output. It does this by first attempting to read from input inp and write that result to output o1. If that fails either because inp is not valid or o1 has back pressure, the abort will be caught and the stage will attempt to write inp to o2.

Listing 3.5 shows how the try block can be used to implement a register file with two read ports and one write port. Note that the decision to put the reads into two separate "try" blocks, rather than the same one, may require some architectural level consideration. If both inputs r1addr and r2addr arrive on the same cycle but there's back pressure on only one output port, then it's possible for the results of the reads to appear on very different cycles. Putting them both in the same "try" block guarantees their read values will be produced on the same cycle by regfile, if that behavior is desired.

```

regfile :: {

rladdr as bits:WORD input

waddr as bits: WORD input

r1 as bits:WORD output

@data as bits:WORD count:32 register

r1 = @data[r1addr]

try {

11

r2 = @data[r2addr]

12

14

try {

15

@data[waddr] = wdata

16

17

```

**Listing 3.5:** The try block allows operations to be isolated, so that their abortion does not affect the rest of the stage.

Removing the "try" blocks would mean that a read could not happen unless a write was requested, and vice versa. This is likely not desirable, in fact, there's a good chance it

could cause a deadlock in many processor implementations. No programming language can prevent the developer from making a mistake, though in my opinion, Pyrope's paradigm makes that sort of error easier to recognize and reason about, as opposed to having the control logic implemented manually in the same design space as the data logic. This is something I was not able to test experimentally, unfortunately.

The "try" block does not technically add any new functionality, as its behavior could be implemented with the ? and ! operators. It is useful because it frees the programmer from having to manually reason about what needs to be checked in a given sub-block to prevent the entire stage from aborting. This can make it easier to describe behavior such as the regfile in Listing 3.5, where the desired behavior is for each statement to be *tried* separately.

## 3.2 Compiling Liam

Pyrope's paradigm is designed to describe fluid behavior implicitly based on where registers and IO ports are read and written to in the control flow structure of the stage. This behavior can be compiled into control logic that drives the *valid* and *stop* signals of fluid registers. As stated in Section 3.1.2, this only applies to *stages*, that have logic and internal state. *Pipes* do not have this implicit logic compiled in.

This section is divided into several parts. The first, Section 3.2.1, discusses how Liam manages state in more detail. Then, Section 3.2.2, discusses deriving logic for the stage's external state, in other words its IO ports. Section 3.2.3 discusses deriving logic for a stage's internal state, meaning its registers.

The final section of this chapter, Section 3.3, discusses some of the challenges Liam presents when implementing large, internal memory blocks. Conceptually, Liam treats large and small registers the same. Due to practical challenges of implementing large memory blocks in synthesized hardware, and Liam's ability to abort a state change, however, the Pyrope compiler treats scalar and arrays registers differently, implementing special optimizations for the latter.

#### 3.2.1 Stages and State

A stage's state is defined as the values of its internal registers (if it has any), along with the state of each of its IO ports (whether they have valid data and/or are asserting back pressure). The data at each IO port is also part of the stage's state if that data is valid. Invalid data is considered "don't care".

For descriptive purposes, this thesis refers to a stage's registers as its *internal state*, and a stage's IO ports as its *external state*, as these require different considerations to manage, as discussed in Section 3.2.2 and 3.2.3, and Section 3.3.

To provide access to the state Liam supports several types of variables, each of which could exist as scalar values or arrays:

**Public:** Visible outside the stage, in other words IO ports. Reading and writing to these means accessing fluid ports which could trigger an abort.

**Register:** These variables retain their values across cycles, making them implicitly part of the stage's internal state.

**Private:** These variables don't retain their values between cycles. They correspond to combinational logic in synthesized hardware.

Within the *register* variable type, Liam supports two kinds: *inline registers* and *deferred registers*. The difference is illustrated by Listings 3.6 and 3.7. It is important to note that inline versus deferred refers to how registers behave during a cycle. Inline registers act like software variables, updating after being assigned to in the control flow, while deferred registers act like hardware registers, updating on the next cycle. This is discussed in detail in Section 3.3.1. Both register types behave the same across cycles, in that they both will only commit their changes if the stage does not abort.

```

@reg1 as inline

2 @reg1 = 5

3 x = @reg1 # x = 5

```

**Listing 3.6:** The value of an inline register is updated after it is written, but that value will not persist to the next cycle if the stage aborts.

```

@reg1 as deferred

2 @reg1 = 5

3 x = @reg1 # x = previous value>

```

**Listing 3.7:** Deferred registers are updated at the end of the cycle, assuming the stage doesn't abort.