# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

# Title

In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET)

## Permalink

https://escholarship.org/uc/item/9dw8r0t3

## **Author** Gupta, Chirag

Publication Date

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA

Santa Barbara

## In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET)

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in Electrical and Computer Engineering

by

Chirag Gupta

Committee in charge: Professor Umesh Mishra, Chair Professor Steven DenBaars Professor Robert York Dr. Stacia Keller Dr. Yifeng Wu

June 2018

The dissertation of Chirag Gupta is approved.

Professor Steven DenBaars

Professor Robert York

Dr. Stacia Keller

Dr. Yifeng Wu

Professor Umesh Mishra, Committee Chair

June 2018

In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET)

Copyright © 2018

by

Chirag Gupta

## DEDICATION

This dissertation is dedicated to my grandparents, Srinath Gupta, Sukhi Devi, Kishanlal Ji

Mor and Bansi Devi

#### ACKNOWLEDGEMENTS

My academic and non-academic experience at UCSB would not have been possible without the support and help from a lot of people. I would like to take this opportunity to express my gratitude towards them.

First and foremost, I would like to express my thanks and gratitude to my advisor Prof. Umesh K. Mishra for accepting me as a graduate student in his research group. Umesh is an ideal advisor for a graduate student. He allows his students to work on challenging and technologically relevant problems while providing a great deal of guidance and support. I especially admire his optimism, pragmatism, dedication and faith in his students.

I would like to thank rest of my committee. Stacia Keller was practically a second advisor to me. Her expertise in MOCVD growth helped tremendously in developing MOCVD regrowth for the OG-FET. I am extremely grateful to her for taking time and patiently answering my questions and explaining growth processes. I owe all my understanding pertaining to materials to her. Also, her contribution and encouragement in publishing scientific results has been of great help. I would also like to thank Prof. Steven DenBaars, Prof. Bob York and Dr. Yifeng Wu for their critical feedback and guidance. Especially, Prof. Denbaars for providing constructive and useful comments during SSLEEC practice talks and annual reviews.

Apart from my committee members, I would like to thank our collaborators on ARPA-E SWITCHES program, Prof. Srabanti Chowdhury and her research group. The shared enthusiasm for vertical GaN devices and close collaboration resulted in numerous insightful, interesting and fun conversations. I thank the funding agencies for this project, ARPA-E SWITCHES program monitored by Dr. Timothy Heidel and Dr. Isik Kizilyalli, SSLEEC and UC Solar. The ARPA-E quarterly reviews helped me in checking my progress and are to some extent responsible for timely completion of my dissertation work.

Next, I would like to thank my colleagues in Mishra group with direct contribution towards this dissertation work. Anchal and Silvia, for growing a ton of material for vertical devices. It was fun developing OG-FETs with your support and learning a little bit about growth as well. Thank you Silvia for such a cool device name. Matt L., Cory, Haoran, Niru, Ryo, and Yuuki for providing the support with growths. Dong, for fabricating large area OG-FETs and pushing OG-FET further. Onur, for all the help with FIBs. Yuuki and Yusuke, for introducing and involving me into projects outside my thesis work. It has been a great learning experience. Geetak, thank you for training me in the cleanroom and all the help with understanding device physics. Matt Guidry, Davide and Jeffery Haller (Transphorm) for helping me out with measurements and Brian Romanczyk for all the help regarding process development. My interns Anna, Eugene, Jq and Will for performing a ton of measurements.

I would like to thank the remaining Mishra group members (Aditya, Athith, Christian, Elaheh, Jeong, Jing, Karine, Matt L., Maher, Pawana, Ramya, Shalini, Steven, Takuro, Trey, Shubhra, Weiyi, Xiang, Xun) for providing a great support system and a lively workplace. I would especially like to thank Steven for attending my wedding in India and all the fun conversations over the years. I thank all the past members of the Mishra group for creating a huge knowledge base which has enabled this work.

I thank the UCSB Nanofab staff for providing an excellent, up and running cleanroom facility. I would like to thank Val and Yukina for all the paperwork related to ECE and SSLEEC respectively.

Outside Mishra group, my friends (Abhishek, Akhilesh, Anusha, Anchal S., Arjun, Ekta, Guru, Tanya, Tanmoy, Sagar, Udbhav and many more) and my room-mates (Geetak, Advait, Anant, Anirudha, Prashansa, Hsin-Ying) provided great company and helped me through the grind of grad school.

I thank my parents (Shivraj Guptra and Usha Gupta) and sister (Paridhi Gupta) for all the support and inspiration.

Finally, I would like to thank my wife Shubhra for all the unconditional love, encouragement and support. I consider myself extremely fortunate to have you as a colleague, friend and life partner. I love you.

### CURRICULUM VITAE OF CHIRAG GUPTA

June 2018

# **EDUCATION**

| Ph.D., Electrical and Computer Engineering                                         | GPA 3.88/4.0               | 2018 |  |

|------------------------------------------------------------------------------------|----------------------------|------|--|

| Dept. of Electrical & Computer Engineering, Universit                              | y of California Santa Barb | para |  |

| M.S., Electrical and Computer Engineering                                          | GPA 3.88/4.0               | 2016 |  |

| Dept. of Electrical & Computer Engineering, University of California Santa Barbara |                            |      |  |

| B.Tech., Electrical Engineering                                                    | GPA 8.8/10.0               | 2013 |  |

| Dept. of Electrical Engineering, Indian Institute of Tec.                          | hnology Kanpur             |      |  |

|                                                                                    |                            |      |  |

# **RESEARCH EXPERIENCE**

## **Graduate Student Researcher**

Sept. 2013- Present

Dept. of Electrical & Computer Engineering, University of California, Santa Barbara

- Design, fabrication, and characterization of III-N trench MOSFETs for high voltage/high power switching applications.

- Part of multiple research projects including III-N based light emitting diodes (LEDs), III-N Power Electronic devices and MOCVD dielectrics for III-N.

## Major Highlights:

- Innovated novel GaN trench MOSFET device design namely *OG-FET* and demonstrated high DC performance

- Demonstrated first GaN field effect transistor with aluminium silicon oxide (AlSiO) as the gate-dielectric

# **HONORS & AWARDS**

- Outstanding Graduate Student Researcher 2017 Solid state lighting and energy efficiency center (SSLEEC), UC Santa Barbara

| - | Outstanding Graduate Student Researcher                                                               | 2016 |

|---|-------------------------------------------------------------------------------------------------------|------|

|   | Solid state lighting and energy efficiency center (SSLEEC)                                            |      |

| - | Outstanding Graduate Student Researcher<br>Solid state lighting and energy efficiency center (SSLEEC) | 2015 |

| - | Academic Excellence Award<br>Indian Institute of Technology Kanpur                                    | 2013 |

|   | παιαπ πειιίαιε οι τεςποιοχή καπρα                                                                     |      |

# **JOURNAL PUBLICATIONS**

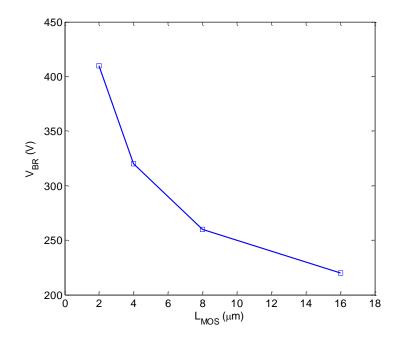

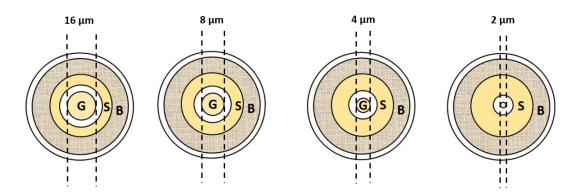

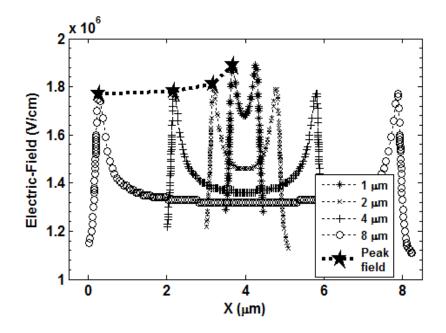

- <u>C. Gupta</u>, D. Ji, S. H. Chan, A. Agarwal, W. Leach, S. Keller, S. Chowdhury, and U. K. Mishra, "Impact of trench dimensions on device performance in GaN trench MOSFETs", under review at *IEEE Electron Device Letters*. (2017)

- <u>C. Gupta</u>, S. H. Chan, A. Agarwal, N. Hatui, S. Keller, and U. K. Mishra, "First demonstration of AlSiO as gate-dielectric in GaN FETs; applied to high performance OG-FET", under review at *IEEE Electron Device Letters*. (2017)

- <u>C. Gupta</u>, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U.K. Mishra, "In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG -FET) on bulk GaN substrates", *IEEE Electron Device Letters.*, vol. 38, no. 3, pp. 353 -356. (2017)

- <u>C. Gupta</u>, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller and U. K. Mishra, "OG -FET: An in-situ Oxide, GaN interlayer based vertical trench MOSFET", *IEEE Electron Device Letters*, vol. 37, no. 12, pp.1601-1604. (2016).

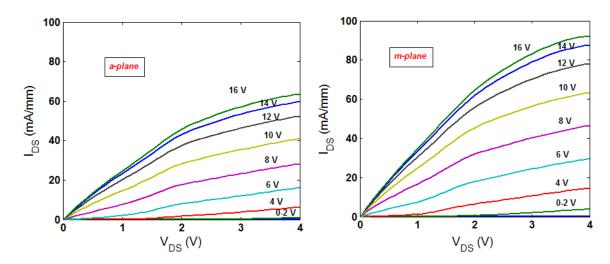

- <u>C. Gupta</u>, S. H. Chan, C. Lund, A. Agarwal, O. Koksaldi, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "Comparing electrical performance of GaN trench -gate MOSFETs with a -plane (1120) and m -plane (1100) sidewall channels," *Appl. Phys. Exp.*, vol. 9, no. 12, pp. 121001 1 121001 -3. (2016).

- <u>C. Gupta</u>, Y. Enatsu, G. Gupta, S. Keller and U. K. Mishra, "High breakdown voltage p-n diodes on GaN on sapphire by MOCVD", *Phys. Status Solidi A*, 213: 878–882. (2016)

- D. Ji, <u>C. Gupta</u>, A. Agarwal, S. H. Chan, C. Lund, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Large Area Normally-Off In -Situ Oxide, GaN Interlayer Based Vertical Trench MOSFET (OG -FET) With 1A Output Current", under review at *IEEE Electron Device Letters*. (2017)

- A. Agarwal, <u>C. Gupta</u>, A. Alhasaan, T. Mates, S. Keller, and U. K. Mishra, "Abrupt GaN/p-GaN:Mg junctions grown via metalorganic chemical vapor deposition", under review at *Applied Physics Express* (2017)

- Y. Enatsu, <u>C. Gupta</u>, S. Keller, S. Nakamura and U. K. Mishra, "P-n junction diodes with polarization induced p-type graded In<sub>x</sub>Ga<sub>1- x</sub>N layer", under review at *Semiconductor. Science and Technology* (2017)

- Y. Enatsu, <u>C. Gupta</u>, M. Laurent, S. Keller, S. Nakamura and U. K. Mishra, "Polarization induced three-dimensional hole gas in compositionally graded In<sub>x</sub>Ga<sub>1- x</sub>N layer", *Appl. Phys. Express* **9** 075502. (**2016**)

- A. Agarwal, <u>C. Gupta</u>, Y. Enatsu, S. Keller, and U. K. Mishra, "Controlled low Si doping and high breakdown voltages in GaN on sapphire grown by MOCVD", *Semiconductor Science and Technology*, vol. 31, no. 12, 125018 pp. 1-4. (**2016**)

- A. Agarwal, O. Koksaldi, <u>C. Gupta</u>, S. Keller, and U. K. Mishra, "Blanket regrowth of GaN for trenched devices by MOCVD", under review at *Applied Physics Letters* (2017)

- S. Chan, S. Keller, O. Koksaldi, <u>C. Gupta</u>, S. P. Denbaars and U. K. Mishra, "Exploring metalorganic chemical vapor deposition of Si-alloyed Al<sub>2</sub>O<sub>3</sub> dielectrics using disilane", *Journal of Crystal Growth*, 464, pp. 54-58 (**2017**)

- S. Chan, M. Tahhan, X. Liu, D.Bisi, S. Keller, <u>C. Gupta</u>, O. Koksaldi, S. Keller, S.

P. Denbaars and U. K. Mishra, "Metalorganic chemical vapor deposition and characterization of (Al,Si)O dielectrics for GaN-based devices", *Japanese Journal of Applied Physics* 55 (2), 021501. (2016)

- V. K. Arora, M. L. P. Tan and <u>C. Gupta</u>, "High-field transport in a graphene nanolayer", *Journal of Applied Physics* 112 (11), 114330. (2012)

# **CONFERENCE PRESENTATIONS**

- D. Ji, <u>C. Gupta</u>, S. H. Chan, A. Agarwal, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of large-area devices", under review at *International Electron Device Meeting*. (2017)

- M. Tahhan, A. Agarwal, B. Romanczyk, S. H. Chan, <u>C. Gupta</u>, S. Keller and U. K. Mishra, "Self-aligned source-first process for vertical conduction GaN fin MOSFETs", *12<sup>th</sup> International Conference on Nitride Semiconductors*, July 2017, Strasbourg, France.

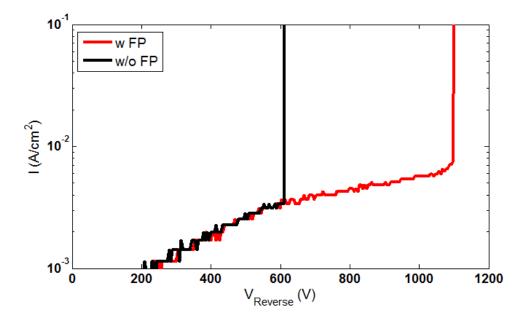

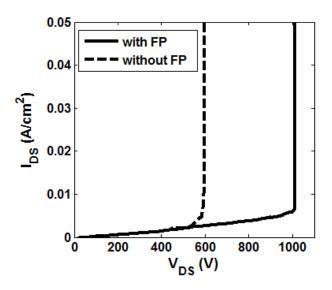

- <u>C. Gupta</u>, A. Agarwal, S. H. Chan, S. Keller and U. K. Mishra, "1 kV field plated insitu oxide, GaN interlayer based vertical trench MOSFET (OG-FET)", 75<sup>th</sup> Device Research Conference, June 2017, South Bend, IN, USA.

- D. Ji, <u>C. Gupta</u>, A. Agarwal, S. H. Chan, C. Lund, W. Li, M. A. Laurent, S. Keller, U. K. Mishra, and S. Chowdhury, "First report of scaling a normally-off in-situ oxide, GaN interlayer based vertical trench MOSFET (OG-FET)", 75<sup>th</sup> Device Research Conference, June 2017, South Bend, IN, USA.

- A. Agarwal, <u>C. Gupta</u>, C. Lund, A. Alhassan, T. Mates, S. Keller, and U. K. Mishra,

"Blanket regrowth of GaN for trenched devices by MOCVD", 59<sup>th</sup> Electronic Materials Conference, June 2017, South Bend, IN, USA.

- <u>C. Gupta</u>, S. H. Chan, A. Agarwal, W. Leach, S. Keller, and U. K. Mishra, "Impact of threading dislocations on the device performance of GaN trench MOSFETs and potential yield of large area devices", 44<sup>th</sup> International Symposium on Compound Semiconductors, May 2017, Berlin, Germany.

- S. H. Chan, H. Li, <u>C. Gupta</u>, N. Hatui, S. Keller, and U. K. Mishra, "Towards normally-off GaN power devices: Impact of GaN polarity and (Al,Si)O gate dielectrics on the MOS Flat-band voltage", 44<sup>th</sup> International Symposium on Compound Semiconductors, May 2017, Berlin, Germany.

- A. Agarwal, O. Koksaldi, <u>C. Gupta</u>, S. Keller, and U. K. Mishra, "Trench regrowth studies by MOCVD for GaN based power devices", *44*<sup>th</sup> International Symposium on Compound Semiconductors, May 2017, Berlin, Germany.

- <u>C. Gupta</u>, Y. Enatsu, S. H. Chan, A. Agarwal, D. Bisi, S. Keller and U. K. Mishra, "Regrown Mg doped GaN interlayer to enhance the breakdown voltage in GaN trench MOSFETs", *11<sup>th</sup> International Workshop of Nitride Semiconductors*, Oct. 2016, Orlando, FL, USA.

- <u>C. Gupta</u>, S. Keller, S. H. Chan, Y. Enatsu, A. Agarwal, W. Leach, and U. K. Mishra, "Comparison between GaN trench MOSFETs with *a*-plane and *m*-plane sidewalls", *Lester Eastman Conference*, Aug. 2016, Allentown, PA, USA.

- <u>C. Gupta</u>, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller, and U. K. Mishra, "A novel device design to lower the on-resistance in GaN trench MOSFETs", 74<sup>th</sup> Device Research Conference, June 2016, Newark, DE, USA.

- A. Agarwal, <u>C. Gupta</u>, Y. Enatsu, S. Keller, and U. K. Mishra, "Controlled low Si doping and high breakdown voltages in GaN on sapphire grown by MOCVD", *58*<sup>th</sup> *Electronic Materials Conference*, June 2016, Newark, DE, USA.

- S. H. Chan, D. Bisi, O. Koksaldi, <u>C. Gupta</u>, A. Agarwal, S. Keller, S. Keller and U. K. Mishra, "MOCVD Based Amorphous (Al,Si)O Dielectrics for GaN MOS Capacitors: A Route to Improved Interface and Bulk Properties", *58<sup>th</sup> Electronic Materials Conference*, June 2016, Newark, DE, USA.

- <u>**C. Gupta**</u>, Y. Enatsu, G. Gupta, S. Keller and U. K. Mishra, "High breakdown voltage p-n diodes on GaN on sapphire",  $42^{nd}$  International Symposium on Compound Semiconductors, June 2015, Santa Barbara, CA, USA.

- <u>C. Gupta</u> and V. K. Arora, "Equilibrium to non-equilibrium carrier statistics for a nano-layer", 2<sup>nd</sup> International Conference on Emerging Electronics, Dec. 2012, Mumbai, India.

- <u>C. Gupta</u> and D. Biswas, "Pedestrian tracking algorithm in NLOS environments", *IEEE International Conference on Advanced Networks and Telecommunications Systems*, Dec. 2012, Bangalore, India.

- <u>**C. Gupta</u>**, K. Singh and D. Sanghi, "Unity Metric Based highly Adaptive Scheduler for Smartphones (UMBASS)", *IEEE International Conference on Advanced Networks and Telecommunications Systems*, Dec. 2012, Bangalore, India.</u>

#### ABSTRACT

#### In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET)

by

#### Chirag Gupta

The surge in world-wide energy consumption places a growing need for highly efficient power electronics for generation, transportation, and utilization of electricity. With the advent of new markets such as electric vehicles, PV solar inverters, the market for these power electronics components is predicted to reach \$15 billion by 2020. Silicon-based devices are most commonly used in traditional power electronics applications, however, wide bandgap semiconductors such as gallium nitride (GaN) are more efficient and thus, useful for future energy applications.

Consequently, Gallium Nitride (GaN) based power devices have gained increased attention in recent years. For 600 V class power devices, lateral GaN high electron mobility transistors are available today. However, it is generally considered that for high voltage/high current applications (>900V/100 A), vertical device structures might be more suitable owing to their capability of achieving lower specific on-resistance and high breakdown voltage simultaneously.

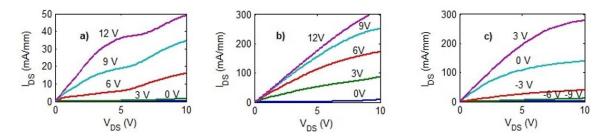

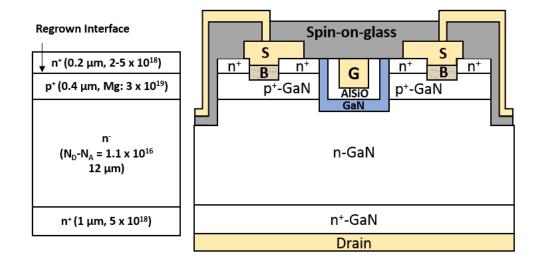

Amongst numerous vertical device structures, the trench MOSFET is an attractive device structure to reduce on-resistance due to the capability of high cell density and the absence of a JFET region. However, high channel resistance in trench MOSFETs due to poor electron mobility in the channel creates reliability issues as a higher gate bias needs to be applied to reduce the channel resistance. In this dissertation work, we developed a novel device design (called OG-FET) to enhance the channel mobility and therefore, lower the channel-resistance for the trench MOSFET structure while maintaining normally-off operation and the same breakdown voltage. In OG-FET, a GaN interlayer is regrown followed by *in-situ* dielectric deposition via MOCVD on the n-p-n trenched structure to enhance the channel mobility. In addition, the *in-situ* gate-dielectric growth onto the GaN interlayer allows this device to achieve lower interface trap density compared to devices with *ex-situ* dielectrics deposited onto the trenched structure.

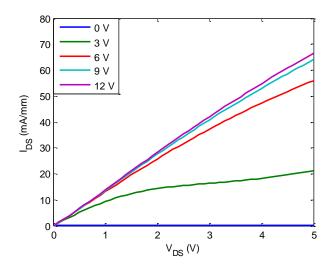

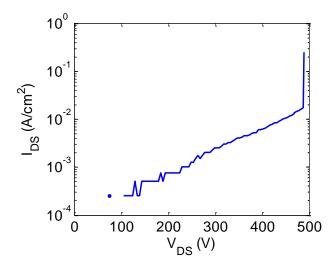

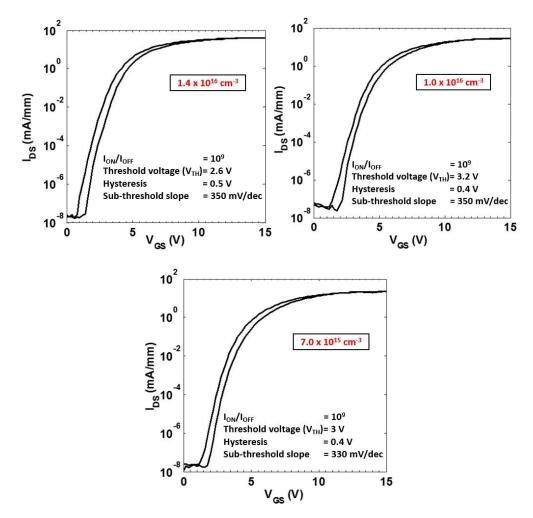

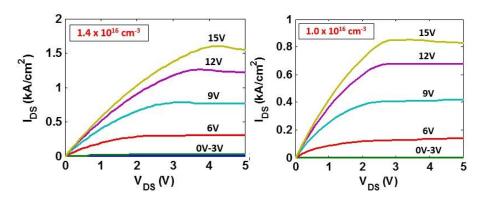

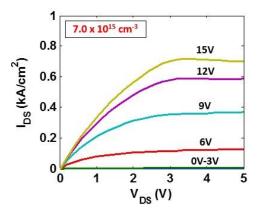

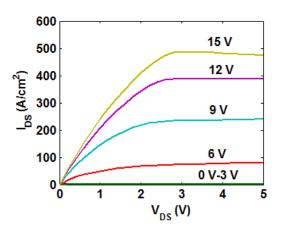

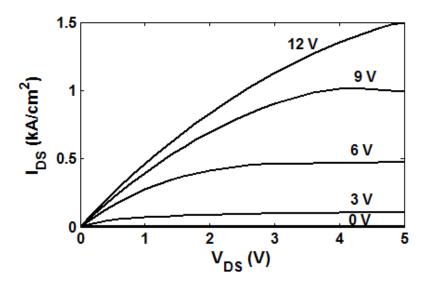

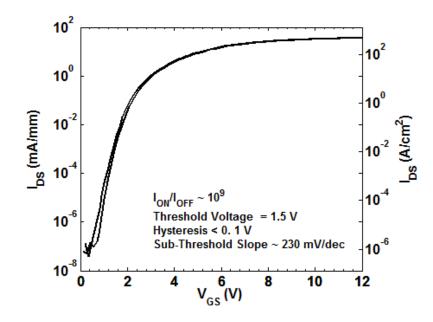

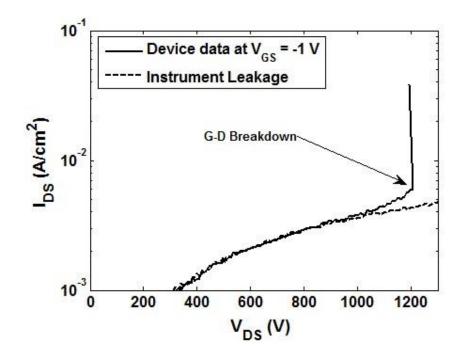

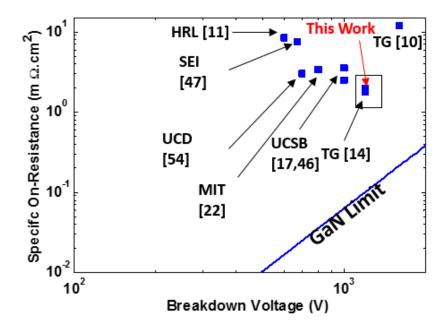

This thesis discusses the OG-FET device design, growth and fabrication process alongside device results and analysis. With sustained efforts, OG-FETs with high DC performance were achieved. The OG-FETs demonstrated threshold voltage between 1-4 V, breakdown voltage beyond 1 kV with a low on-resistance between 1.5-3 m $\Omega$ .cm<sup>2</sup>. The on-resistance values were achieved at a relatively low gate bias (~12 V-15 V) and low gate-dielectric field (~2-3 MV/cm) compared to conventional GaN trench MOSFETs.

These results are promising for the future application of OG-FETs for high voltage and high-power electronics.

## TABLE OF CONTENTS

| Chapter 1 : Introduction       |                                             |

|--------------------------------|---------------------------------------------|

| 1.1 Vertical GaN Device        | es 4                                        |

| 1.1.1 CAVET Device             | e Design                                    |

| 1.1.2 Trench MOSFE             | T Device Design                             |

| 1.2 Thesis Overview            |                                             |

| Chapter 2 : Epitaxial requirem | ent for vertical GaN devices13              |

| 2.1 Substrate                  |                                             |

| 2.2 Threading dislocatio       | ns in GaN14                                 |

| 2.2.1 GaN MOSCAP               | s: SiN vs Al <sub>2</sub> O <sub>3</sub> 15 |

| 2.2.2 GaN MOSCAP               | s: Bulk GaN vs Sapphire20                   |

| 2.3 Role of Carbon on d        | evice performance                           |

| Chapter 3 : The OG-FET inno    | vation; device design and fabrication       |

| 3.1 OG-FET vs Trench           | MOSFET                                      |

| 3.2 Epitaxial structure d      | esign and device fabrication                |

| 3.2.1 Epitaxial Desig          | n                                           |

| 3.2.2 Device Fabricat          | ion Process                                 |

| 3.3 Important Fabricatio       | n Modules                                   |

| 3.3.1 Etch                     |                                             |

| 3.3.2 MOCVD Chan               | nel Regrowth Process                        |

| 3.3.3 Edge terminatio          | on                                          |

| 3.3.4 Sidewall chann           | el plane orientation 63                     |

| 3.4 S       | ummary                                              | . 69 |

|-------------|-----------------------------------------------------|------|

| Chapter 4 : | High voltage OG-FETs                                | . 70 |

| 4.1 G       | aN on sapphire OG-FETs                              | . 70 |

| 4.1.        | 1 Basic growth and fabrication                      | . 70 |

| 4.1.2       | 2 Device details                                    | . 72 |

| 4.1.3       | 3 Device results and analysis                       | . 74 |

| 4.2 B       | ulk GaN OG-FETs without edge termination            | . 76 |

| 4.2.        | 1 Basic growth and fabrication                      | . 76 |

| 4.2.2       | 2 Device details                                    | . 78 |

| 4.2.3       | 3 Device results and analysis                       | . 79 |

| 4.3 Fi      | ield-plated bulk GaN OG-FETs                        | . 85 |

| 4.3.        | 1 Basic growth and fabrication                      | . 85 |

| 4.3.2       | 2 Device results and discussion                     | . 86 |

| 4.3.        | 3 OG-FETs with angled isolation etch                | . 89 |

| 4.4 B       | ulk GaN OG-FETs with Aluminum Silicon Oxide (AlSiO) | . 89 |

| 4.4.        | 1 Basic growth and fabrication                      | . 90 |

| 4.4.2       | 2 Device results and analysis: OG-FETs with AlSiO   | 92   |

| 4.5 O       | n-state analysis                                    | . 95 |

| 4.5.        | 1 Source resistance                                 | . 96 |

| 4.5.2       | 2 Channel resistance                                | . 97 |

| 4.5.3       | 3 Drift and substrate resistance                    | . 98 |

| 4.5.4       | 4 Sub-threshold slope and hysteresis                | . 99 |

| 4.6 O       | ff-state analysis                                   | 99   |

| 4.6.1 Impact of material quality on device breakdown                           |

|--------------------------------------------------------------------------------|

| 4.7 Dynamic performance of unit-cell OG-FETs 103                               |

| 4.8 Large area OG-FETs103                                                      |

| Chapter 5 : Summary, conclusion, and future work 109                           |

| 5.1 Summary                                                                    |

| 5.1.1 Material Quality109                                                      |

| 5.1.2 Fabrication process                                                      |

| 5.1.3 Device results and comparison with state-of-the art unit cell GaN trench |

| MOSFETs 112                                                                    |

| 5.2 Conclusion                                                                 |

| 5.3 Future Work                                                                |

| 5.3.1 On-state characteristics                                                 |

| 5.3.2 Off-state characteristics                                                |

| 5.3.3 Switching and stress testing                                             |

| Appendix A : Process Traveler 110                                              |

| References                                                                     |

# **Chapter 1: Introduction**

Electricity is fast becoming a necessity of human life. The pervasive utilization of electricity brings a large strain on non-renewable sources of energy which are the major source of electricity generation (as of now). Consequently, in the past decade, rapid advances have been made towards generation of electricity from renewable sources of energy. However, such technologies are still far from wide deployment. Therefore, efficient generation, transmission and utilization of electricity is of paramount importance.

Power generated at the base stations is not utilized as it is by the consumer. It needs to be converted multiple times from one form to another before it is finally consumed. These power conversion processes are not 100 % efficient and thus, incur losses. With increased system complexity, number of power conversion processes increases and total efficiency decreases. According to recent studies, approximately 10 % of the total generated electricity gets wasted due to these inefficient power conversion processes [1]. This inefficiency drives the need towards developing efficient power conversion processes.

At the heart of every power conversion process is a semiconductor switch/transistor. The performance of power semiconductor transistor drives the overall system design, cost and efficiency. Therefore, a power semiconductor device can be considered as the most basic and critical building block of a power system.

The most basic requirements of a power device are high breakdown voltage ( $V_{BR}$ ) and low on-state resistance ( $R_{ON}$ ) [2]. Together these characteristics allow for a highly efficient switch/transistor. There are few figures of merit (FOM) that are commonly used to benchmark power device performance [2]. One of the simplest FOM is  $V_{BR}^2/R_{ON}$ . The  $V_{BR}$  and  $R_{ON}$  of a device are strongly related to the material properties of the semiconductor [2] used by the following relation known as Baliga's FOM,

$$\frac{V_{BR}^2}{4R_{ON}} = \mu_{bulk} \varepsilon_S E_C^3$$

1.1

here,  $\mu_{\text{bulk}}$  is the bulk electron mobility,  $\epsilon_{\text{S}}$  is the dielectric constant, and  $E_{\text{C}}$  is the critical electric field for breakdown. This result defines the one-dimensional material limit line on the transistor performance. However, using advanced device designs such as cool MOS or superjunction MOSFET, device performance can be pushed beyond this one-dimensional material limit [3].

Silicon (Si) has long been the preferred material choice for power semiconductor devices. However, akin to logic devices, Si power semiconductor devices are now rapidly approaching fundamental limits [4]. This has driven the need for alternative materials to satisfy ever growing demand for efficient power electronics. Consequently, in the past two decades, wide band gap (WBG) semiconductors have been actively pursued [4]. With superior material properties such as high breakdown field, high bulk mobility, high thermal conductivity etc., WBG semiconductors have the potential to improve the size, weight, efficiency, power density, current density, and high temperature reliability for the power conversion system. Such improvements could revolutionize the entire power system design. Table 1 shows the material properties of various WBG semiconductors and silicon [5]. Amongst WBG semiconductors, silicon carbide (SiC) and gallium nitride (GaN) have emerged as suitable candidates for next generation power electronics beyond Si. In addition, gallium oxide and diamond are being explored for future enhancements.

GaN and SiC based power devices are commercially available today [6]. Their performance is approximately 2-5 times higher than that of fundamental limit of Si. However,

| Material                         | Breakdown field,       | Bulk Mobility            | Dielectric Constant | BFOM  |

|----------------------------------|------------------------|--------------------------|---------------------|-------|

|                                  | E <sub>C</sub> (MV/cm) | μ (cm <sup>2</sup> /V-s) | $(\varepsilon_S)$   |       |

| Silicon                          | 0.3                    | 1400                     | 11.8                | 1     |

| 4H-SiC                           | 2.5                    | 1000                     | 9.7                 | 340   |

| GaN                              | 3.3                    | 1200                     | 9                   | 870   |

| β-Ga <sub>2</sub> O <sub>3</sub> | 8                      | 300                      | 10                  | 3444  |

| Diamond                          | 10                     | 2000                     | 5.5                 | 24664 |

Table 1.1 Material parameters of different semiconductors and BFOM

these material systems are relatively immature compared to Si and their performance is not yet close to one-dimensional material limit, therefore, with technological advances much higher performance can be expected in next few years.

Power devices can be fabricated using both lateral and vertical device structures. SiC based power devices were extensively explored using vertical device structures such as MOSFETs and JFETs. MOSFET device design is more suitable than JFET because (ideally) the MOSFET can be applied in a similar way as Si MOSFETs and IGBTs and is potentially more reliable than JFET. However, in SiC MOS devices, high MOS channel resistance was observed due to low inversion channel mobilities [6]. This limits the application of SiC MOS devices in low and medium power applications as channel resistance dominates the total on-resistance of the device. Although, for high voltage applications ( $\geq 1200$  V), drift resistance is either comparable or sufficiently larger than the channel resistance. Thus, allowing fundamental onedimensional material limits to be approached in high voltage (> 1200 V) applications.

Unlike SiC, majority of GaN power device development was targeted towards lateral structures. AlGaN/GaN hetero-structure based high electron mobility transistors (HEMTs) becomes a natural choice because an AlGaN/GaN interface easily forms a highly conductive two-dimensional electron gas (2DEG) and offers very low sheet resistances. Consequently, lateral GaN HEMTs on Si are commercially available today for medium range power

conversion applications [7]. However, it is considered that for high voltage, high current applications (1200 V/100A), vertical structures might be more suitable [8], [9], [10], [11]. There are multiple reasons for the same. First, in a vertical device, the die area is weakly dependent on the breakdown voltage. Second, vertical devices hold the strong electric fields in the bulk rather than along the surface, resulting in lower trapping. Third, avalanche breakdown can be achieved in these devices. Fourth, relatively easier current extraction/wiring is possible due to the placement of the source and drain on vertically opposite sides and better thermal management.

Even in the presence of SiC vertical commercial devices, GaN vertical devices are worth exploring as the material properties of GaN are superior to that of SiC. The reason for slow progress of vertical GaN compared to SiC was lack of high quality native GaN substrates. In the past few years, research on p-n diodes have shown that the GaN substrate quality has significantly improved and these substrates can be applied for the fabrication of high voltage devices [12], [13]. Consequently, GaN power devices have been demonstrated with blocking voltages between 1-2 kV with low specific on-resistance and normally-off operation [10], [14], [15], [16], [17], [18]. Even though, these results are encouraging, however, to fully realize the potential of GaN vertical devices, significant research on multiple fronts still needs to be done.

# **1.1 Vertical GaN Devices**

Numerous vertical GaN power transistors have been demonstrated in the past few years. Predominantly, vertical device structures can be divided into two broad device designs. The first type is a current aperture vertical electron transistor (CAVET) [9], [15], [16], [19]. The second type is a trench MOSFET device with a sidewall gate [10], [11], [14], [17], [18], [20], [21], [22].

## **1.1.1 CAVET Device Design**

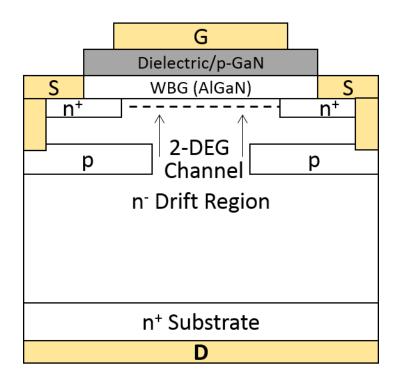

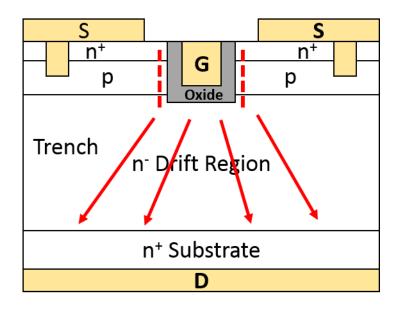

The CAVET device was first reported in 2000 by Yaacov *et al* [23]. However, the first report on CAVETs was targeted towards RF power applications for dispersion free device performance. Later, CAVET device design was explored for power switching applications by Chowdhury *et al* [9]. The CAVET device design to some extent is analogous to D-MOSFET which has been explored in Si and SiC. CAVET is a merged lateral-vertical device. Figure 1.1 shows the CAVET cross sectional schematic.

Figure 1.1 CAVET cross sectional schematic.

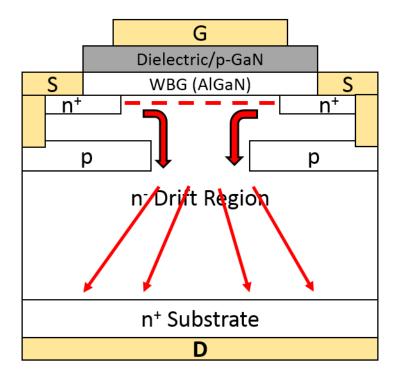

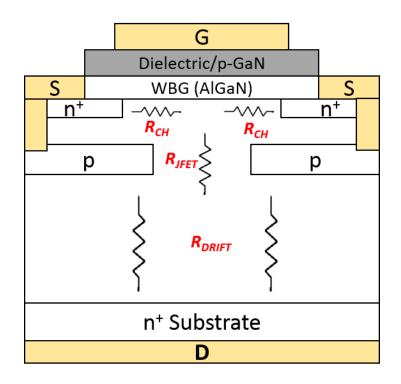

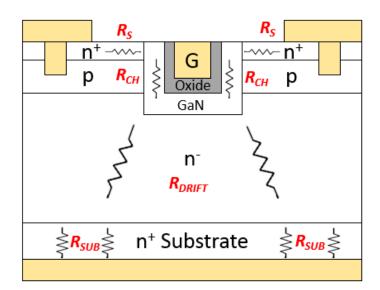

In CAVET, in the on-state, the flow of electrons is in lateral direction from the source through the channel which is modulated by planar gate. Then, electrons flow vertically through an aperture or JFET region into the drift region and are collected by the drain contact. This is illustrated in Figure 1.2. The design of conductance of the JFET or aperture region has a considerable impact on device performance [24]. The total on-state resistance components are shown in the following equation,

$$R = R_S + R_{CH} + R_{IFET} + R_{DRIFT} + R_D$$

1.2

Here, *R* is the total resistance of the device extracted in the linear region.  $R_S$ ,  $R_{CH}$ ,  $R_{JFET}$ ,  $R_{DRIFT}$ ,  $R_D$  are the source, channel, JFET region or aperture, drift and drain resistances respectively. These resistance components are illustrated in Figure 1.3.

Figure 1.2 Flow of electrons in CAVET.

In high voltage vertical devices,  $R_S$  and  $R_D$  contribution to the total on-resistance is negligible. Also, due to the presence of highly conductive 2-DEG in CAVETs, the  $R_{CH}$  is also negligible compared to other resistances. Therefore, the major resistance components are  $R_{JFET}$ and  $R_{DRIFT}$ . The equation 1.2 can be approximated as,

$$R \sim R_{IFET} + R_{DRIFT}$$

1.3

Figure 1.3 Major resistance contributions in a high voltage CAVET.

The drift resistance depends on the doping, mobility, and thickness of the drift region. Doping and thickness of the drift region determines the expected blocking voltage from the device. The conductivity of the JFET region determines the total on-resistance of the device. A resistive aperture can result in poor saturation of drain current with increasing drain voltage and can increase the on-resistance of the device. A conductive aperture can result in improved saturation behavior and device pitch can be reduced. However, higher doping in the aperture region would reduce the breakdown voltage of the device. Therefore, optimization of aperture or JFET region conductivity is of paramount importance in CAVETs.

Apart from aperture conductivity design, there are other challenges with the device design. One such aspect is the design of the current blocking layer (CBL). The CBL prevents the flow of electrons from source to drain both in the off-state and in the on-state. Ion implantation of Al and Mg have been used for the CBL [9], [25]. Ion implantation allows the planarity of the region to be maintained for subsequent re-growths. However, in GaN, p-type ion implantation does not work as efficiently as it does in Si and SiC. Recent reports are showing improvement in p-type ion implantation, but its performance is still far from as grown p-type layers [26], [27]. As grown p-type layer on top of the drift region can also be used as CBL as demonstrated in first CAVET report. In this type of CBL device design, the aperture is formed by etching through the CBL followed by regrowth of the aperture. The re-growth within the trenched structure has proved to be challenging [24], [28]. However, recently, good device performance has been demonstrated by Nie *et al.* with regrown aperture [16].

Another challenge of CAVET device design is to achieve enhancement mode operation with MOS or MIS gate structure in Ga-Polar orientation (with AlGaN/GaN heterojunction). Since, the gate structure of CAVET is similar to lateral HEMT structure, achieving reliable normally-off operation in CAVET is almost equally challenging as AlGaN/GaN HEMTs. With use of a junction gate (p-GaN), normally-off devices can be achieved [16]. As mentioned in the previous section, like in SiC devices, MOSFET type gated structure will always be preferred over JFET gate. Therefore, achieving normally-off operation with a MOS/MIS gate is another big challenge of this device design.

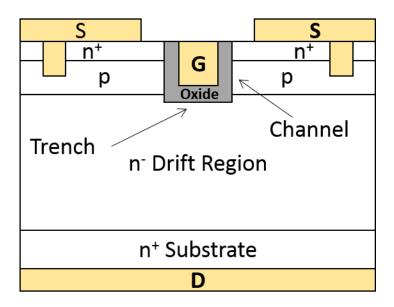

#### **1.1.2 Trench MOSFET Device Design**

The trench MOSFET basic device design dates to early 1990s [29]. In Si, the trench MOSFET has grown into a 3-billion-dollar annual market [29]. Trench MOSFET device design has also been extensively explored in SiC. SiC trench MOSFETs are also commercially available today. The success of trench MOSFET device design in Si and SiC indicates that reliable MOSFET could be manufactured on a vertically etched sidewall. Trench MOSFET has also been explored in GaN alongside CAVET. The first GaN trench MOSFET was reported

in 2007 by Otake *et al* [30]. Thereafter, there have been multiple reports on trench MOSFETs. In 2015. Oka *et al.* demonstrated high DC performance trench MOSFET with 1.2 kV breakdown voltage and an on-resistance of 1.8 m $\Omega$ .cm<sup>2</sup> [14].

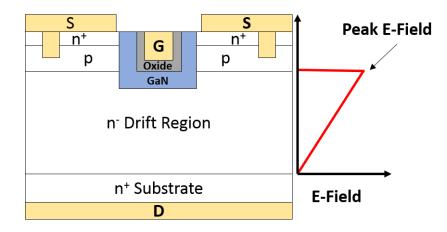

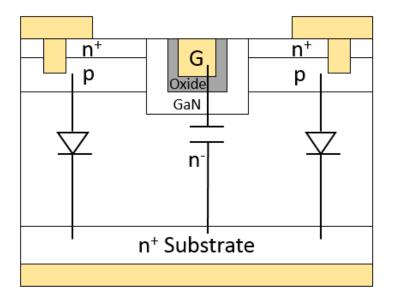

A cross-sectional schematic of a trench MOSFET is shown in Figure 1.4. The functioning of a trench MOSFET is in principle similar to a conventional Si MOSFET. Akin to the Si MOSFET, when a gate bias more than the threshold voltage is applied, the channel forms via inversion in the p-GaN layer at the p-GaN/dielectric interface on the sidewall. Subsequently, the electrons flow vertically from the source via the sidewall channel and spreads out into the drift region and are finally collected by the drain contact. The electron flow in a trench MOSFET is illustrated in Figure 1.5.

Figure 1.4 Trench MOSFET cross sectional schematic.

Trench MOSFETs have some basic advantages over the CAVET type device design. First, normally-off or enhancement mode operation can be achieved with relative ease in trench MOSFETs with MOS gate in trench MOSFETs. Second, the absence of regrowth makes fabrication process relatively shorter and less challenging. In CAVETs, as discussed earlier, regrowth of channel region is challenging and becomes even more challenging due to the need for conformal growth in the trenched structure. Third, the absence of a JFET or aperture region in these devices. This allows high cell density which results in lower specific on-resistance of the device. Unlike the CAVET, the trench MOSFET is a fully vertical device. Since, the device is fully vertical, the pitch of the device can be significantly reduced in comparison with the CAVET.

Figure 1.5 Electron flow in a trench MOSFET.

Such advantages of the trench MOSFET makes it an attractive device design for vertical devices. However, one of the biggest challenges of a trench MOSFET is the channel resistance in these devices [29], [31]. The formation of a channel on the etched sidewall results in poor electron channel mobility which increases the channel resistance. Low electron mobility can potentially create reliability issues as a higher gate bias needs to be applied to reduce the channel resistance by inducing high inversion charge. Similar issues were encountered in Si

and SiC trench MOSFETs as well. In both Si and SiC, etch damage caused on the sidewall was removed by depositing a "sacrificial oxide". The oxide is grown on the trench sidewall and completely removed by wet etch. After this sacrificial oxidation process, the gate dielectric is grown. This process step has proved to a major breakthrough in developing reliable and highperformance trench MOSFETs in Si and SiC [29].

Unfortunately, application of such "sacrificial oxide" technique to improve the semiconductor/dielectric interface in GaN is difficult. The oxidation of GaN at high temperatures is not well behaved and makes the application of the above technique difficult or almost impossible. Therefore, to improve the channel properties, an alternate technique is needed for GaN trench MOSFETs.

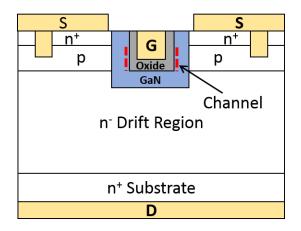

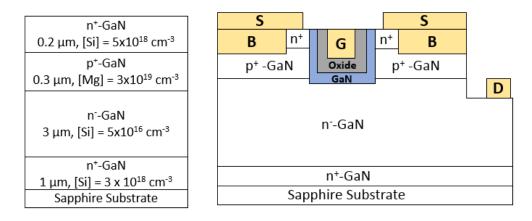

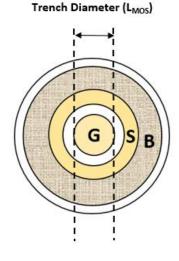

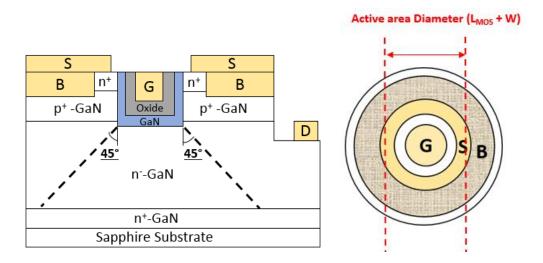

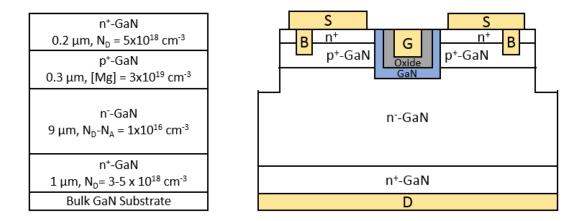

In this work, a solution to the aforementioned problem was proposed by introducing a novel device modification in trench MOSFETs. In this device design, a GaN interlayer is regrown followed by *in-situ* dielectric deposition on the trenched structure to enhance the channel electron mobility. As per the functionality, the device was named in-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET) and illustrated in Figure 1.6.

Figure 1.6 OG-FET cross sectional schematic.

# 1.2 Thesis Overview

This dissertation focuses on the development of the OG-FET for high power switching applications. The basic or bare minimum requirements of high power transistor are high breakdown voltage, low on-resistance, and normally-off operation. Since, the OG-FET device design had never been previously reported, majority of this work was focused on obtaining state of the art DC performance.

Chapter 2 describes the material requirement for high voltage vertical devices. Experiments pertaining to substrate choice and threading dislocation density performance on vertical devices are described. Also, the role of impurity incorporation in epitaxial layers affecting device performance is also discussed.

Chapter 3 describes the conceptualization and fabrication process of the OG-FET. The advantages of the OG-FET device design over a trench MOSFET are described. Important fabrication modules critical to the device performance are also discussed in detail.

Chapter 4 discusses the high voltage OG-FETs. Device results, experiments and analysis are described in detail.

Chapter 5 summarizes this dissertation work and provides research ideas to further the OG-FET performance.

# Chapter 2: Epitaxial requirement for vertical GaN devices

Vertical GaN devices require the highest material quality for prolonged safe operation. The development of vertical GaN devices compared to SiC devices have been slower primarily due to the limited availability of bulk GaN substrates [32]. Threading dislocations in GaN are another big concern for the development of failsafe high voltage vertical GaN power electronics. GaN has been traditionally grown on heterogeneous substrates such as Si, SiC, and sapphire, for use in lateral devices. This material has a high threading dislocation density of  $10^{8}$ - $10^{10}$  cm<sup>-2</sup>. These dislocations arise from the lattice mismatch between GaN and the substrate. Bulk GaN substrates have lower dislocation density ( $10^{6}$  cm<sup>-2</sup>) and are more suited for vertical GaN devices. However, current bulk GaN substrates suffer from uniformity issues and are significantly more expensive than heterogeneous substrates [33].

Another important aspect of GaN epitaxial growth is the unintentional impurity incorporation in GaN layers. Impurities such as carbon in GaN layers result in donor compensation. This limits the lower bound of free carrier concentration that can achieved and could lead to various issues in epitaxial growth and subsequent device behavior.

In subsequent sections, the role of substrate, threading dislocations and impurity incorporation are discussed.

## 2.1 Substrate

The starting substrate for the epitaxial growth of GaN plays an important role in determining the device performance. Initial vertical GaN development was done on heterogeneous substrates due to the absence of high quality bulk GaN substrates [23]. GaN

grown on heterogeneous substrates such as Si, SiC, sapphire etc. result in high threading dislocation density due to lattice mismatch between GaN and the substrate. The dislocation density on heterogeneous substrates vary from 10<sup>8</sup>-10<sup>10</sup> cm<sup>-2</sup>. Threading dislocations have been shown to affect off-state performance in GaN p-n diodes [13], [32]. Due to threading dislocations, increased off-state leakage was observed in p-n diodes. Furthermore, the development of vertical GaN on heterogeneous substrates is challenging due to the limitations in the thickness of the layers grown on substrates due to the thermal mismatch. Vertical devices targeted towards achieving breakdown voltage of 1200 V and above requires the nominal drift region to be thicker than at least 10 µm [34]. Therefore, due to threading dislocations and limitations in the drift region thickness, realization of high performing vertical GaN devices on heterogeneous substrates is difficult. However, when bulk GaN substrates are used, low dislocation density epitaxial GaN ( $\sim 10^6$  cm<sup>-2</sup>) layers can be obtained. High performance p-n diodes and FETs were demonstrated on bulk GaN substrates. Numerous reports demonstrating avalanche breakdown in p-n diodes demonstrate the improved quality of bulk GaN substrates [12], [13], [35]. However, the uniformity of substrate quality from wafer to wafer or within different areas of a wafer is still a concern and needs to be improved [33].

# 2.2 Threading dislocations in GaN

Numerous researchers have studied the impact of threading dislocations on the performance of p-n diodes. Researchers observed that with the increased density of threading dislocations, higher off-state leakage was observed in p-n diodes [32]. Higher off-state leakage in p-n diodes due to threading dislocation could be attributed to two reasons. First, due to the presence of threading dislocation, local lowering of the p-n junction barrier height. Second, a threading dislocation could act as an electron-hole pair generation center. Under reverse bias,

the electron-hole pair generated in the depletion region will move towards cathode and anode respectively under the influence of electric field, thus, contributing to increased off-state leakage.

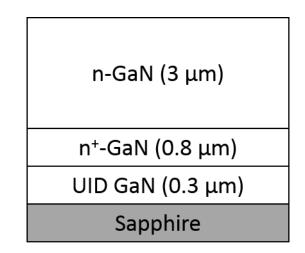

MOSCAPs and p-n diodes are an integral part of GaN power devices. Even though understanding both MOSCAP and p-n diode off-state behavior is important, MOSCAP reverse bias studies are non-existent. Therefore, the impact of threading dislocations on GaN vertical power devices was studied for the first time by fabricating metal-oxide-semiconductor capacitors (MOSCAPs). MOSCAPs were fabricated on both sapphire and bulk GaN substrates. In the next sub-sections, the experiments and results are discussed.

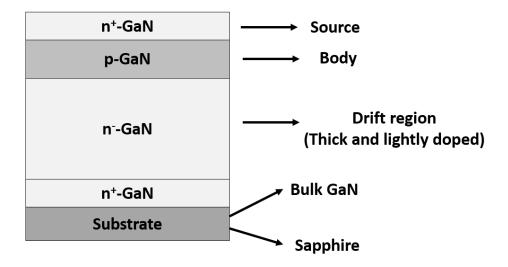

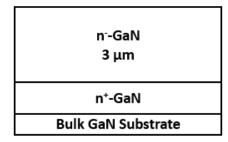

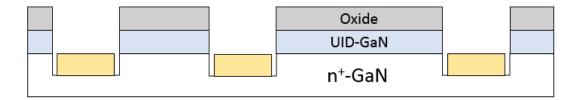

Figure 2.1: GaN layers grown by MOCVD for MOSCAPs.

#### 2.2.1 GaN MOSCAPs: SiN vs Al<sub>2</sub>O<sub>3</sub>

In this study, the dielectrics were chosen to study the impact of dislocations on different gate-dielectrics. The dielectrics (SiN and Al<sub>2</sub>O<sub>3</sub>) in this experiment were deposited by MOCVD. First, a lightly doped GaN epi was grown by MOCVD shown in fig 2.1. Prior to dielectric depositions, the samples underwent UV ozone and 48 % hydrofluoric acid (HF) treatment to remove residual silicon (Si) at the dielectric/semiconductor interface [31]. The

presence of Si at the regrowth interface can cause high electric field in the gate-dielectric under reverse bias and can cause early breakdown of the gate-dielectric. Therefore, it is important to remove and/or reduce Si at the interface. Immediately after UV ozone and HF cleaning, the samples were loaded in the MOCVD reactor and dielectric growths were performed. The thicknesses of the gate dielectrics were 50 nm. Ti/Au (300 nm/2000 nm) was used as both the gate and the ohmic contact. The MOSCAP cross sectional schematic is shown in fig. 2.2.

Figure 2.2: MOSCAP cross sectional schematic.

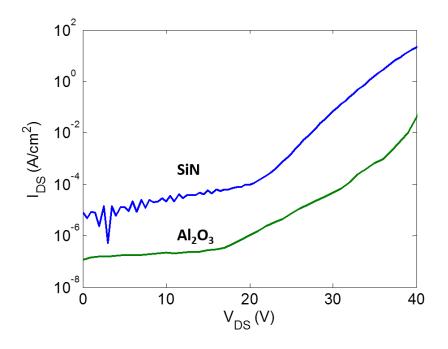

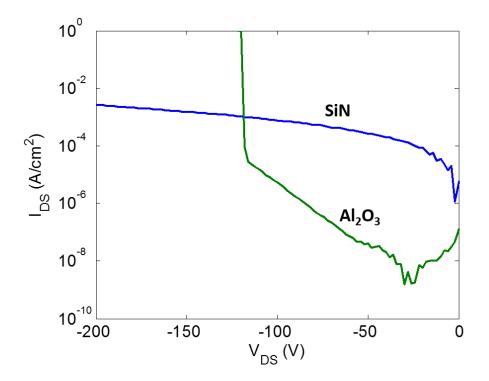

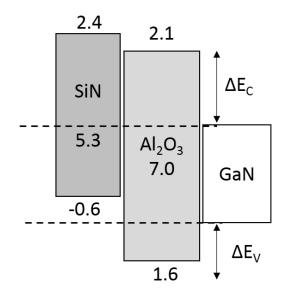

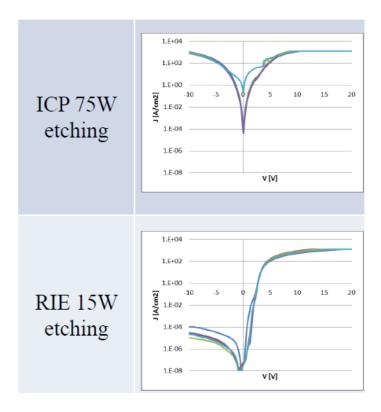

Forward and reverse current-voltage characteristics of both MOSCAPs are shown in fig 2.3 and fig. 2.4 respectively. Both lower forward and reverse leakage current was observed with Al<sub>2</sub>O<sub>3</sub> compared with SiN. High forward leakage current is a characteristic of SiN on GaN and has been observed by numerous researchers. Al<sub>2</sub>O<sub>3</sub> demonstrated catastrophic breakdown at 120 V. However, no catastrophic breakdown was observed with SiN up to the measurement limit of 200 V. Under reverse bias, higher leakage was observed with SiN compared with Al<sub>2</sub>O<sub>3</sub>. The major difference between these two dielectrics is their band lineup with GaN as shown in fig. 2.5. SiN has negative valence band offset with GaN while Al<sub>2</sub>O<sub>3</sub> has positive valence band offset with GaN.

Figure 2.3: Forward I-V characteristics of both MOSCAPs.

Figure 2.4: Reverse I-V characteristics of both MOSCAPs.

Figure 2.5 Conduction and valence band line up of SiN and Al<sub>2</sub>O<sub>3</sub> with GaN.

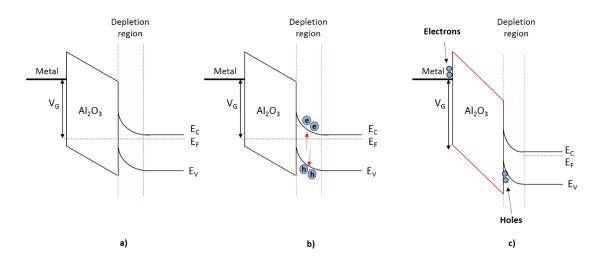

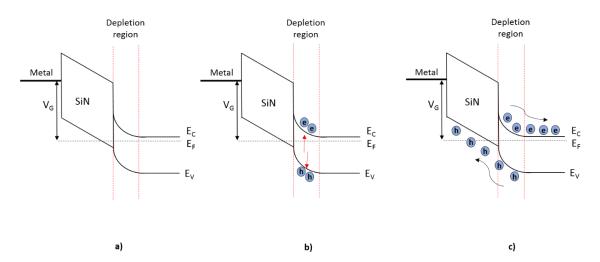

The reverse bias behavior of two dielectrics could be explained by considering threading dislocations to be the generation centers for electron-hole pairs. Fig. 2.6 a) shows the band diagram of MOSCAP (assuming gate dielectric has positive valence band offset with respect to GaN) under reverse bias with a gate voltage  $V_G$  (here, it is assumed that  $V_G$  is more negative than the flat-band voltage of the MOSCAP). Electron-hole pairs generated in the depletion region under the influence of electric field will move towards ohmic and gate contact respectively. However, in Al<sub>2</sub>O<sub>3</sub>, due to the presence of positive valence band offset between semiconductor and the gate electrode. Due to this barrier, holes start piling up at the semiconductor-dielectric interface and electrons flowing through the external circuit pile up at the gate electrode to maintain system charge neutrality. The piling up of holes and electrons across the gate-dielectric increases the electric field in the gate-dielectric. This can potentially result in early breakdown of the gate-dielectric.

Figure 2.6: a) shows the depletion region of n-type GaN under the application of reverse bias (with a gate voltage  $V_G$ ). The electron-hole pair generation in the depletion region by threading dislocations acting as generation centers (b). The presence of an electric field in the depletion region moves electrons and holes in the opposite direction. The positive valence band offset between Al<sub>2</sub>O<sub>3</sub> and GaN results in holes (generated by threading dislocations in the depletion region) piling up at the semiconductor-dielectric interface as shown in c). The piling up of holes and electrons results in an increased electric field in the gate-dielectric.

Figure 2.7: a) shows the depletion region of n-type GaN under the application of reverse bias (with a gate voltage  $V_G$ ). The electron-hole pair generation in the depletion region by threading dislocations acting as generation centers (b). The presence of electric field in the depletion region moves electrons

and holes in the opposite direction. The absence of barrier for holes (unlike Al<sub>2</sub>O<sub>3</sub>) with SiN results in free movement of holes towards gate electrode (c). Similarly, electrons move towards ohmic electrode resulting in increased reverse leakage current (c).

Similar effect was not observed in SiN due to the presence of negative valence band offset between SiN and GaN [36]. Therefore, the absence of a hole barrier allows the generated holes to be collected by the gate electrode and electrons to be collected by ohmic electrode [37]. This results in an increased reverse leakage current in SiN MOSCAPs compared with Al<sub>2</sub>O<sub>3</sub>.

This experiment shows how threading dislocations affect power devices. Apart from increasing reverse or off-state leakage current, it could result in early catastrophic breakdown of the device. In the next sub-section, MOSCAPs were fabricated on both bulk GaN and sapphire to study this phenomenon in more detail.

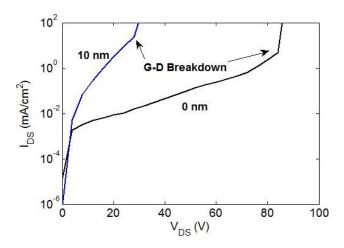

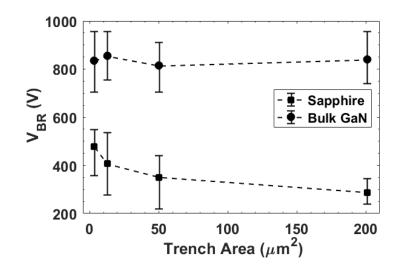

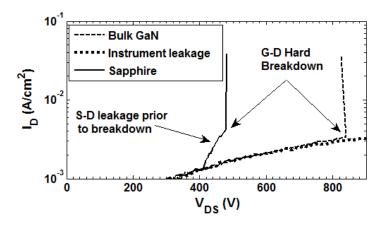

#### 2.2.2 GaN MOSCAPs: Bulk GaN vs Sapphire

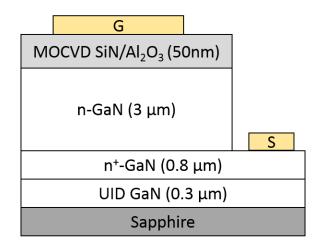

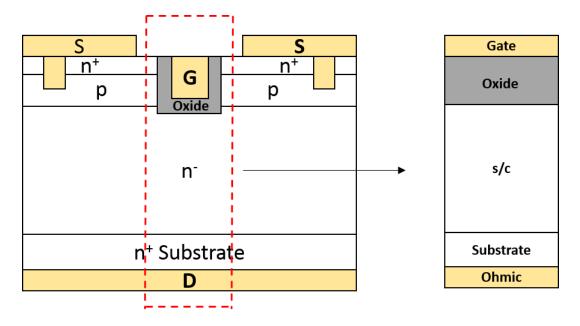

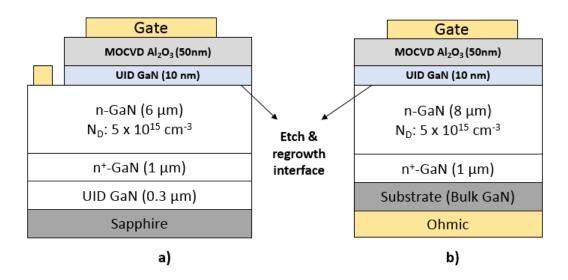

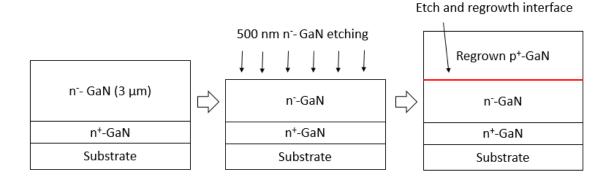

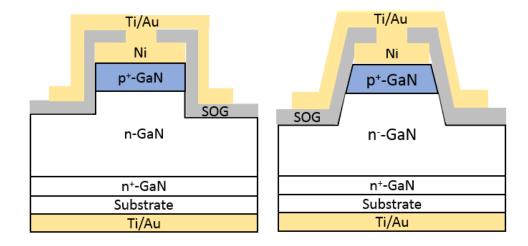

Motivated by the experiment in the above section which showed that dislocations could result in the early breakdown of the gate-dielectric (with positive valence band offset to GaN), the next step was to investigate MOS capacitor off-state performance on bulk GaN with low threading dislocation density. Since, our final goal was to fabricate trench MOSFETs, etched MOSCAPs were fabricated to mimic the trench MOSFET gate-drain structure as shown in the figure. In a trench MOSFET as shown in figure 2.8, the gate-drain region is like a MOSCAP structure. In the trench MOSFET, the trench-etch ends on n-type semiconductor region, therefore, the semiconductor-dielectric interface is ex-situ and is not ideal [10]. Therefore, studying etched MOSCAPs behavior is important.

Figure 2.8: Gate-drain region of a trench MOSFET structure (shown in dashed lines) mimics a MOS capacitor structure.

In this study, the planar MOSCAPs were fabricated on both sapphire and bulk GaN to study the impact of dislocations on the gate-dielectric. To mirror the trench MOSFET fabrication process, first, a trench MOSFET epitaxial structure was grown on both bulk and sapphire. Thereafter, the top n<sup>+</sup>-GaN and p<sup>+</sup>-GaN layers were etched like a typical trench MOSFET fabrication process [10]. Since, the trench-etch was not selective between n- and p-type GaN, n-type GaN underneath p-type GaN was etched to ensure the complete etching of p-GaN layer. To improve the interface quality between etched semiconductor and the gate-dielectric, a thin GaN interlayer was added by MOCVD. Prior to MOCVD regrowth process, the samples underwent UV ozone and 48 % hydrofluoric acid (HF) treatment to remove residual silicon (Si) at the dielectric/semiconductor interface as described in the previous section. The MOCVD regrowth process was performed in two steps. First, the samples were annealed in N<sub>2</sub>/NH<sub>3</sub> for 30 min. at 930 °C to recover etch damage [38]. Following annealing, UID-GaN interlayer was grown on the sample. The GaN interlayer regrowth was followed by the in-situ deposition of the gate-dielectric (Al<sub>2</sub>O<sub>3</sub>) [39]. The thickness of the MOCVD Al<sub>2</sub>O<sub>3</sub> was 50 nm. Ti/Au (300 nm/2000 nm) was used as both gate and ohmic contact. For sapphire, due to thick drift region, a large pad (3mm x 3mm) was deposited which was used as the ohmic contact [31]. For bulk GaN, metal was deposited on the backside.

Figure 2.9: a) GaN MOSCAP on sapphire substrate. The ohmic contact was made far from the gate contact. On a separate die, the gate dielectric was etched off entirely and ohmic metal was deposited on the entire die area (3 mm x 3 mm). This was used as ohmic contact for the MOSCAP. b) GaN MOSCAP on bulk GaN substrate. In both MOSCAPs, GaN interlayer was added to obtain improved semiconductor/dielectric interface.

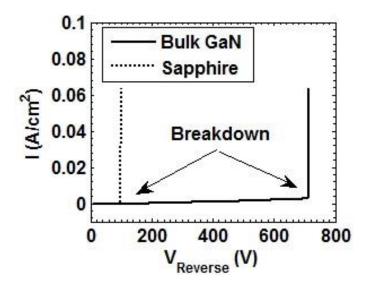

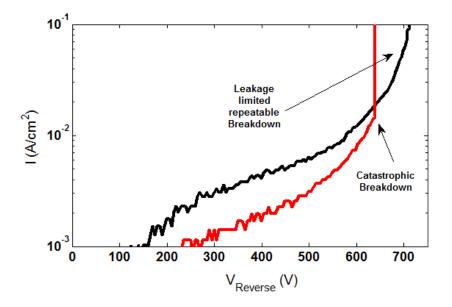

Similar forward bias behavior was observed for both MOSCAPs (on bulk GaN and sapphire). However, a stark difference in reverse bias behavior of both MOSCAPs was observed. The MOSCAP fabricated on sapphire demonstrated a significantly low breakdown of 90 V compared to 700 V for MOSCAP fabricated on bulk GaN.

Figure 2.10: The MOSCAP reverse bias characteristics. The reverse leakage current for both MOSCAPs was in the noise and they both broke down catastrophically.

The associated breakdown fields in GaN at which the gate-dielectric breaks down for sapphire and bulk GaN MOSCAPs were estimated to be ~0.3 MV/cm and ~1.4 MV/cm respectively. For GaN on sapphire MOSCAP, at such low breakdown field of ~0.3 MV/cm, the breakdown of GaN layers is not expected and cannot be explained. However, considering dislocations as generation centers, these results can be understood. We hypothesize that with sapphire substrate, due to high dislocation density, the holes piling up at the semiconductor/dielectric interface would be higher compared to bulk GaN substrate. This would result in an increased electric field in the gate-dielectric and would cause an early breakdown in sapphire devices as observed.

## 2.3 Role of Carbon on device performance

Vertical GaN devices are attractive for high voltage, high power switching applications. To service these applications, a lightly n-type doped GaN layer that is tens of micrometers thick is required; furthermore, the free carrier concentration must be 10<sup>16</sup> cm<sup>-3</sup> or lower to provide a breakdown voltage of several kilovolts [34]. Reliably achieving free carrier concentration of 10<sup>16</sup> cm<sup>-3</sup> in the thick drift layer is a big challenge, as the interplay between unintentional acceptors or other point defects and donors must be well controlled [40]. Numerous researchers have demonstrated good linearity between Si dopant and free carrier concentrations above 10<sup>16</sup> cm<sup>-3</sup>. However, due to the presence of residual impurity concentration such as carbon (C), it is difficult to control free carrier concentration lower than 10<sup>16</sup> cm<sup>-3</sup>. Nitrogen-site carbon incorporation in GaN has been reported to act as an acceptor and compensate donors. This results in a non-linear behavior of Si dopant and free carrier concentration [34]. This lack of controlled doping can inadvertently result in low free carrier concentrations or insulating layers and can significantly increase the resistance of the GaN layers.

Carbon incorporation in MOCVD grown GaN films occurs due to the methyl groups present in the Ga precursor, trimethylgallium (TMGa). High temperature, high V-III ratio, and high growth pressure are effective to reduce carbon incorporation in GaN films [40]. Therefore, growth conditions need to be optimized to obtain GaN layers with free carrier concentration of  $10^{16}$  cm<sup>-3</sup> or lower.

The incorporation of carbon in n-type GaN layers affect unipolar and bipolar transport differently. In compensated layers, where, incorporated carbon  $(N_T)$  is greater than the targeted doping  $(N_D)$ , the fermi level lies at the trap (carbon) level. For unipolar transport, for example, a schottky diode fabricated on compensated layers will exhibit a high turn-on voltage and high on-resistance. The electrons injected in the semiconductor instead of being mobile will fill the empty trap states. The voltage applied  $(V_{AP})$  will be governed by the following equation,

$$V_{AP} = \frac{qN_T W^2}{2\varepsilon_{O\varepsilon_T}}$$

2.1

where,  $N_T$  is the incorporated carbon density and W is the thickness of the drift layer with carbon. Only after entirely filing the trap states, the injected electrons will flow as mobile electrons i.e. current. Therefore, the amount of voltage needed is significantly high as for power devices, the drift regions are relatively thick. For example, an incorporation of  $10^{16}$  cm<sup>-3</sup> carbon in 1µm thick drift region would give an approximate turn-on voltage of 10 V.

However, in bipolar transport, for example, a p-n junction, the injection of holes and electrons under forward bias neutralizes the trap and low on-resistance is observed compared to schottky diode. Since, power devices are unipolar in nature, to avoid high resistances, it is of paramount importance to control impurity incorporation in GaN layers.

# Chapter 3: The OG-FET innovation; device design and fabrication

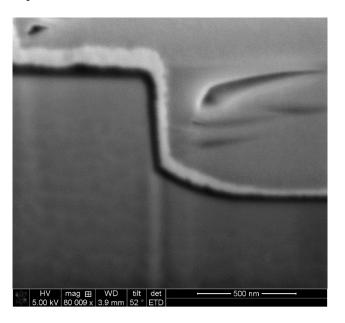

In trench MOSFETs, the channel forms on the tapered/vertical etched sidewall. Roughness of the etched sidewall along with impurity incorporation prior to the dielectric deposition results in poor channel properties, especially poor channel mobility [10]. Poor channel properties can potentially cause reliability issues and limit the realization of full potential of this device design [29]. As discussed in the introduction chapter, in Si and SiC trench MOSFETs, the sidewall etch damage was reduced by using a "sacrificial oxide" technique [29]. In this method, a thick gate oxide (SiO<sub>2</sub>) was formed on the trenched structure by oxidation and was completely removed by wet chemistry. This method removes sidewall roughness and improves interface quality. Following the sacrificial oxidation process, the gate dielectric is deposited. This technique played a significant role on producing reliable and highperformance trench MOSFETs in Si.

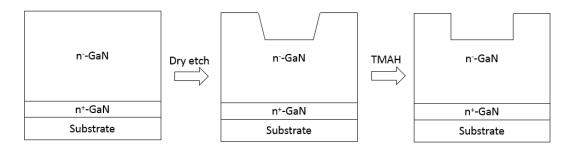

However, the absence of native oxide and lack of oxidation of GaN even at high temperatures makes the adoption of "sacrificial oxide" technique for GaN difficult. In GaN, using tetramethylammonium hydroxide (TMAH) sidewall roughness can be reduced. TMAH selectively etches sidewall plane and stops on the non-polar planes while c-plane (0001) remains unaffected [11], [21], [41] as shown in figure 3.1. However, the roughness on the c-plane remains unaffected and the damage caused underneath the sidewall surface is difficult to recover. Therefore, to improve channel properties, alternate technique is needed for GaN trench MOSFETs.

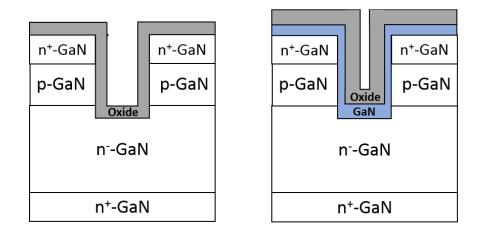

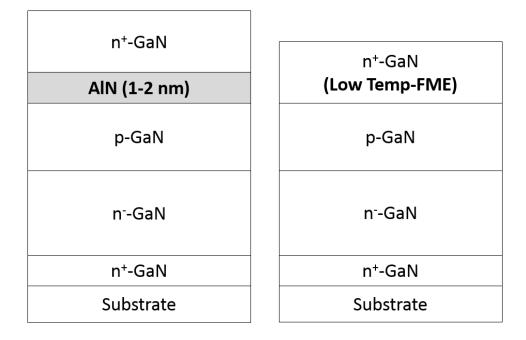

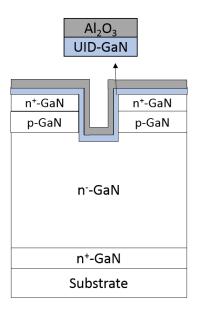

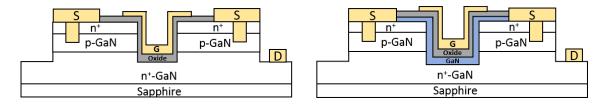

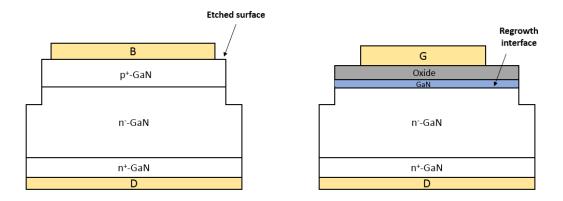

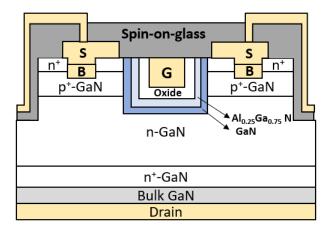

The OG-FET device design was targeted towards improving channel properties in GaN trench MOSFETs. In the OG-FET, a GaN interlayer is regrown followed by *in-situ* dielectric deposition on the trenched structure to enhance the channel (electron) mobility (Fig 3.2). As per the construction, the device was named in-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET) [31], [42]. In the next section, the OG-FET device design is discussed and compared with conventional trench MOSFET device design.

Figure 3.1: TMAH selectively etches GaN sidewall planes and helps in achieving true vertical sidewalls.

Figure 3.2: A conventional trench MOSFET structure where gate-dielectric is deposited after gate trench-etch (Left). An OG-FET device design, where after gate trench etch, a GaN interlayer is regrown followed by the gate-dielectric deposition (Right).

In the remaining part of this chapter, the OG-FET epitaxial design and fabrication process is described. In addition, important fabrication process modules are also discussed.

## **3.1 OG-FET vs Trench MOSFET**

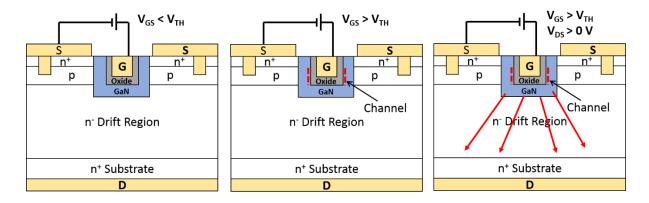

The functioning of the OG-FET is akin to a conventional trench MOSFET as shown in fig. 3.3. When a gate bias more than the threshold voltage is applied, the channel forms at the UID-GaN interlayer/*in-situ* gate-dielectric interface and the electrons flow from the source into the drift region through this sidewall channel modulated by the sidewall gate.

Figure 3.3: With gate-voltage lower than the threshold voltage, the OG-FET remains in the offstate (Left). When a gate voltage greater than the threshold voltage is applied, the channel forms (Middle) and with a positive drain source voltage, the electrons flow from source to drain via the channel and the drift region (Right).

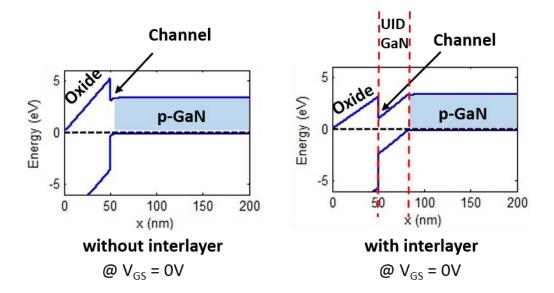

The OG-FET device design builds up on the advantages offered by the conventional trench MOSFET device design. The improvement in channel properties is expected with the OG-FET due to primarily two reasons. First, because of the separation of the channel and the p-GaN layer introduced by the UID-GaN interlayer results in reduced ionized impurity scattering (Fig 3.4). Second, is the *in-situ* channel interface. The growth of in-situ dielectric after the growth of GaN without breaking vacuum offers an improved channel interface compared to

conventional trench MOSFET. In addition, the *in-situ* dielectric growth onto the GaN interlayer allows this device to achieve lower interface trap density ( $D_{IT}$ ) compared to devices with ex-situ dielectrics deposited onto the trenched structure which is of paramount importance for gate-stack reliability [43], [44]. Third, addition of GaN interlayer lowers the sub-threshold slope in this device design compared to trench MOSFET without GaN interlayer.

Figure 3.4: Sidewall band diagram (Gate/Oxide/UID-GaN/p-GaN) comparison of OG-FETs with and without interlayer at zero gate-bias. The figure clearly shows with increasing UID-GaN interlayer thickness the channel is further spaced from p-GaN, thereby, reducing ionized impurity scattering.

Compared to the conventional trench MOSFET, the OG-FET requires an additional regrowth step [31]. However, the regrowth involved in OG-FET is blanket and mask-less as shown in fig. 3.2. Unlike the CAVET, planarity of the surface after regrowth is not preferred with the conformal nature of regrowth being desirable which is easily attainable. Also, with the III-N growth followed by the gate-dielectric without breaking vacuum in MOCVD reduces additional step of growing GaN interlayer separately.

Enhancement mode operation is a key requirement in power devices to facilitate reliable and failsafe operation. Reliable normally-off GaN HEMTs are achieved by using Si MOSFETs in cascode configuration with GaN HEMT [45]. With the trench MOSFET, obtaining normally-off behavior in intrinsic device is relatively easier. Compared to the conventional trench MOSFET, the OG-FET is expected to have a lower threshold voltage. This is a negative consequence of the addition of the GaN interlayer in the gate stack. With GaN interlayer, the conduction band in OG-FET is closer to the fermi level compared to the trench MOSFET at zero gate bias as shown in fig. 3.4. However, as shown in the figure, the conduction band in the OG-FET is still above the fermi level at zero gate bias, therefore, normally-off device can be achieved. The threshold voltage of an OG-FET can be controlled by GaN interlayer thickness design and p-GaN doping. Using both these parameters, good normally-off behavior with threshold voltage > 2 V can be achieved [31], [46].

Regrown channel in a GaN trench MOSFET has been reported by Okada *et al.* in 2010 [47]. However, they employed AlGaN/GaN regrown channel on a shallow (75° from vertical) sidewall with a schottky gate. With the regrown AlGaN/GaN interlayer, normally-off operation was achieved with a low threshold voltage of 0.3 V. For high voltage power devices, a threshold voltage above 2-5 V is preferred to facilitate failsafe reliable operation [48]. The results obtained by Okada *et al* indicates that with regrown AlGaN/GaN channel, it is difficult to achieve normally-off operation above 2 V and hence an alternate approach deserves investigation.

With the mentioned on-state advantages, similar off-state, and normally-off behavior, OG-FET device design is very interesting and was explored in this thesis. State-of-the art DC performance was demonstrated in this work [17], [18], [46].

### **3.2** Epitaxial structure design and device fabrication

In this work, the OG-FETs were fabricated on both sapphire and bulk GaN substrates. Initial OG-FET development and optimization of the fabrication process was done on sapphire substrates. This was due to the high cost of bulk GaN substrates. The device epitaxial structure and fabrication process were similar on both substrates except for few details.

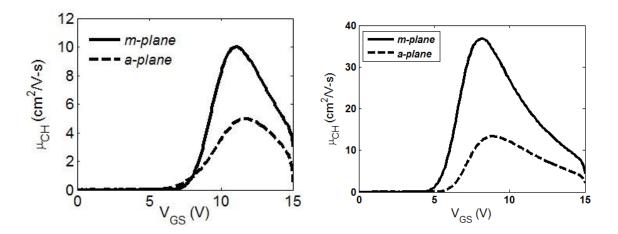

Figure 3.5: OG-FET epitaxial structure.

#### **3.2.1** Epitaxial Design

The OG-FET epitaxial structure consists of n<sup>+</sup>-GaN/p-GaN/n<sup>--</sup>GaN/n<sup>+</sup>-GaN layered stack as shown in fig. 3.5. The OG-FETs in this dissertation were grown in an MOCVD reactor using trimethyl gallium (TMGa), silane, bis-cyclopentadienyl magnesium (Cp<sub>2</sub>Mg), and NH<sub>3</sub> as precursors. The bottom n<sup>+</sup>-GaN serves as the drain in GaN on sapphire, while, on Bulk substrates in serve as conducting buffer layer. It has been shown that a buffer layer on bulk GaN substrates results in improved off-state performance [49]. The targeted thickness and the doping of the bottom n<sup>+</sup>-GaN layer was 1µm and 2-5 x 10<sup>18</sup> cm<sup>-3</sup> in this work on both sapphire and bulk substrates. Following the drain layer, the drift region was grown. The drift region thickness (W) and doping concentration ( $N_D$ ) is related to the breakdown voltage ( $V_{BR}$ ) and specific drift-resistance ( $R_{DRIFT}A$ ) by following equations,

$$V_{BR} = \frac{qN_D W^2}{2\varepsilon_S}$$

3.1

$$R_{DRIFT}A = \frac{W}{q_{N_D\mu}}$$

3.2

Where, q is the charge,  $\mu$  is the mobility of the drift region,  $\varepsilon_S$  is the permittivity of GaN. It should be noted that these abovementioned equations assume ideal device design. Also, the ideal device design is also related to critical field of GaN as,

$$E_C = \frac{qN_DW}{2\varepsilon_S}$$

3.3

Therefore, in an ideal power device design, the device breaks down when the drift region is fully depleted, and the breakdown voltage corresponds to critical field of the material (Figure 3.6). This ideal device design allows the realization of one dimensional material limit. It can be seen from above equations, that there is an inherent trade-off between the drift resistance and the breakdown voltage. High drift region mobility is advantageous as it reduces onresistance without affecting the breakdown voltage. The drift region thickness and doping concentration were varied in this dissertation to achieve the desired device characteristics.

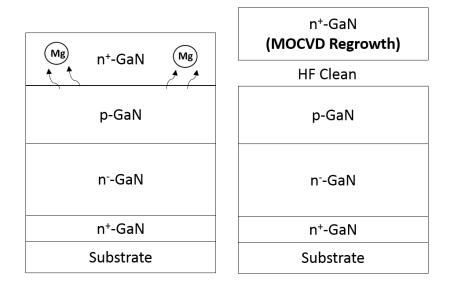

After the drift region, the p-GaN body region was grown. Here, the p-GaN thickness is the nominal gate-length of the device. In this dissertation work, the targeted p-GaN (Mg) doping was 3 x  $10^{19}$  cm<sup>-3</sup>. Such high concentration was chosen to avoid short channel effects, to avoid punch-through and achieve threshold voltage > 2V. After p-GaN growth, the sample was taken out of the MOCVD reactor and a 5 minute, (48%) HF dip was used to remove excess Mg from the surface and the sample was again loaded into the MOCVD reactor for the source growth

[50]. This was done to prevent the surface riding of magnesium into subsequent layers (Figure 3.7). This is an important step as incorporation of Mg into source layer could potentially increase source resistance and therefore, the total on-resistance of the device.

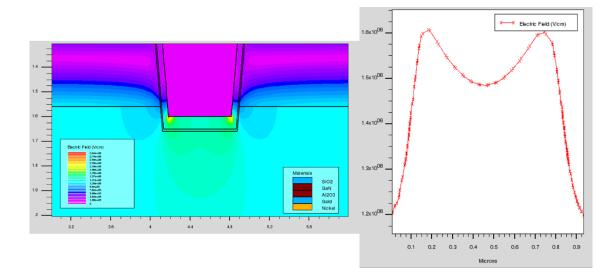

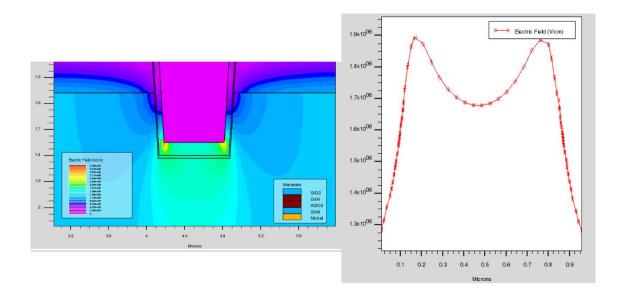

Figure 3.6: Desired electric field profile along the drift region is shown at the breakdown voltage. The peak electric field, therefore, should occur at the p-n junction and the electric field goes down to zero at the end of the drift region resulting in this triangular electric field profile.

Finally, 0.2  $\mu$ m thick heavily doped n<sup>+</sup>-GaN was grown for the source. High doping of the source layer reduces both contact and sheet resistance resulting in reduction of the source resistance. However, with higher doping, good surface morphology is imperative. Therefore, in this dissertation the source layer doping was kept between 2-5 x 10<sup>18</sup> cm<sup>-3</sup> as higher doping could result in the degradation of surface morphology.

In the future, to avoid MOCVD regrowth and simultaneously address surface riding of magnesium into subsequent layers a couple of techniques can be utilized. First, employing an AlN blocking layer following p-GaN growth as shown in fig 3.8. It has been shown that AlN is effective in reducing Mg incorporation in subsequent layers [51]. Second, using low temperature flow modulation epitaxy (LT-FME). With LT-FME, Mg incorporation in subsequent layers can be controlled remarkably [52]. However, high source layer doping (>2-

5 x  $10^{18}$  cm<sup>-3</sup>) with good surface morphology has proved to be challenging to obtain with flow modulation epitaxy.

Figure 3.7: Surface riding of magnesium (Mg) in subsequent layers (Left). Surface riding can be reduced by removing excess Mg from the surface by introducing a HF clean (Right).

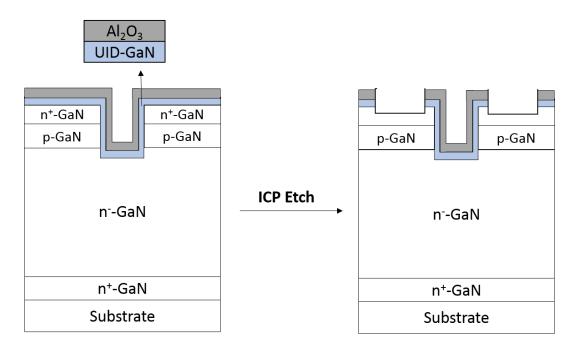

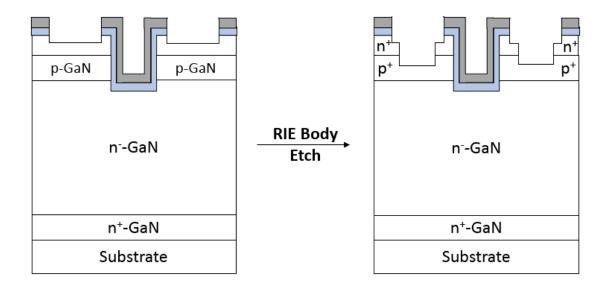

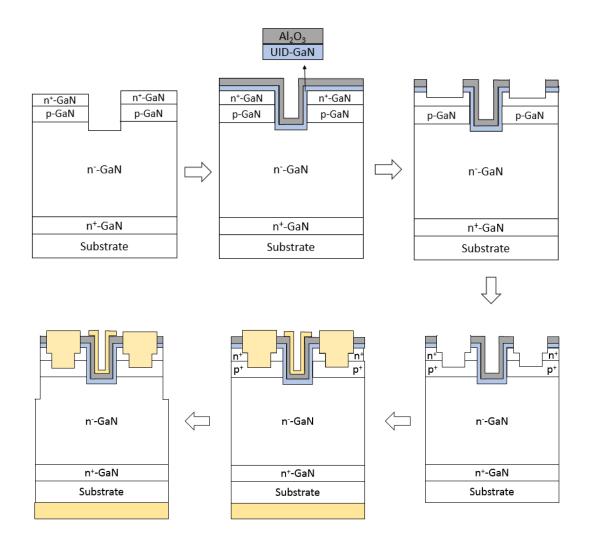

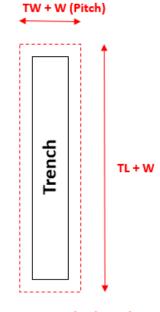

#### **3.2.2 Device Fabrication Process**

The OG-FET fabrication process starts with the formation of nearly vertical trench structures by dry etching. Tapered sidewalls provide longer channel length and thus result in an increased channel resistance of the device. However, it is difficult to obtain low damage perfect vertical sidewalls with only a dry etch. A combination of dry and wet etch can be used to obtain true vertical sidewalls. TMAH selectively etches sidewall planes such as *a*- and *m*-plane without affecting the c-plane (0001). Following dry etch, TMAH treatment can result in perfect vertical sidewalls [53]. However, in this dissertation, TMAH based wet etch can be readily incorporated. The dry etches used in this dissertation work resulted in trench angle of less than

or equal to 15° from vertical. Further details regarding etch and etch chemistry are provided in next section.

Figure 3.8: Alternative techniques to suppress Mg incorporation in subsequent layers without taking the sample out of reactor. By using a thin AlN interlayer (Left) and by growing n<sup>+</sup>-GaN layer by low temperature flow modulation epitaxy (Right).

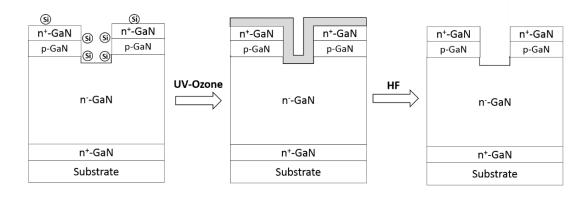

Following the trench-gate etch process, a cleaning procedure was developed prior to the MOCVD regrowth (Figure 3.9). The samples underwent UV-Ozone and HF treatment to remove residual Si, which is commonly observed at regrowth interfaces [51]. The UV-ozone and HF treatment were always performed immediately before MOCVD regrowth process. It involves 3 cycles of 15 minutes of UV ozone treatment followed by 1 minute 48 % hydrofluoric acid dip followed by a deionized water rinse. The presence of Si can result in negative threshold shift and early breakdown of devices [54]. Therefore, it is imperative to perform cleaning prior to MOCVD regrowth process.

Figure 3.9: UV-ozone and HF treatment. First, the elemental silicon present at the interface is oxidized to  $SiO_2$  by performing UV-ozone treatment. HF dip removes the  $SiO_2$ , thereby reducing Si at the interface.

Figure 3.10: Sample after MOCVD regrowth process. On the etched surface shown in fig 3.9, UID-GaN interlayer followed by Al<sub>2</sub>O<sub>3</sub> were regrown.

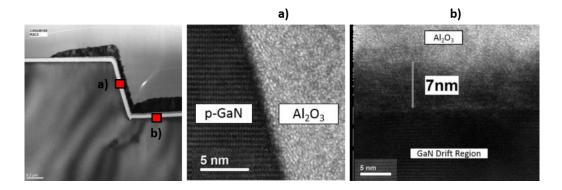

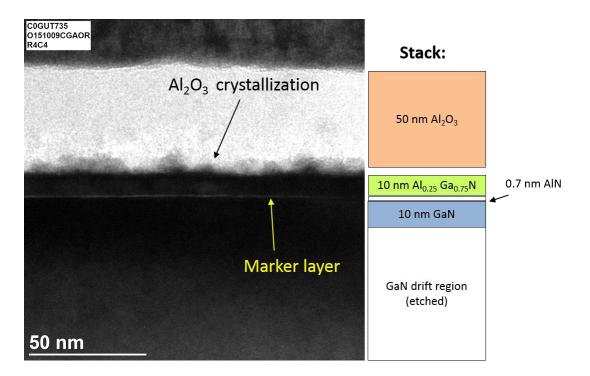

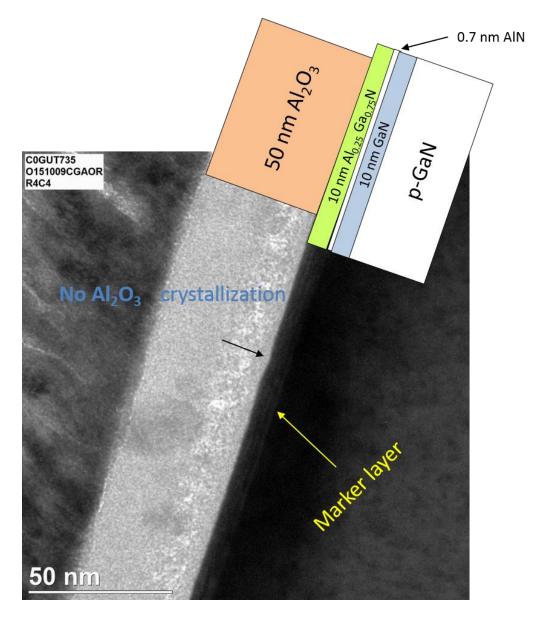

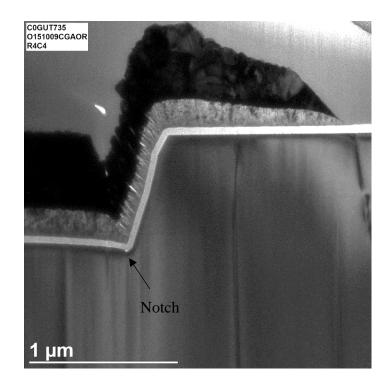

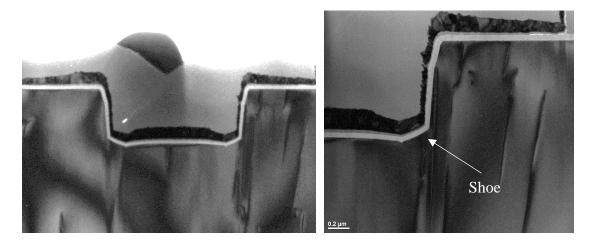

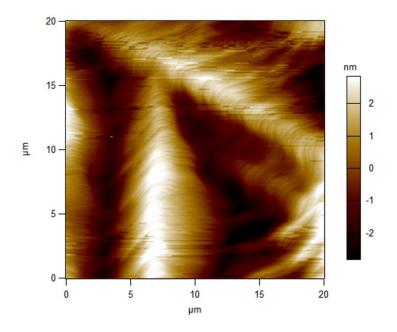

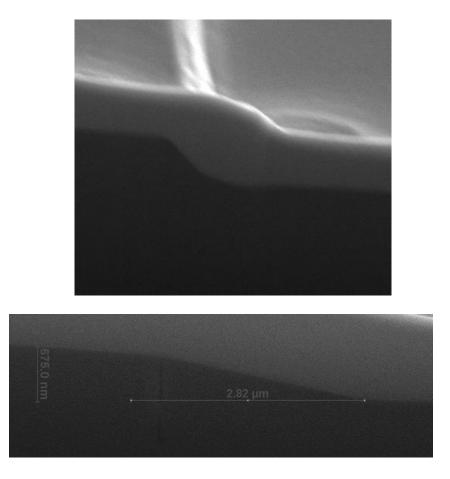

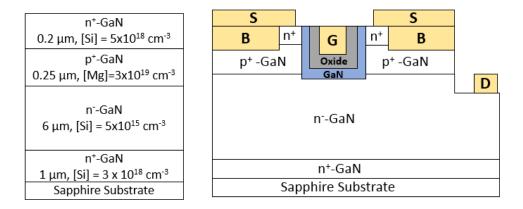

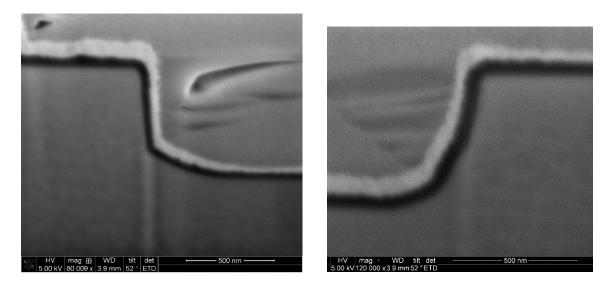

Thereafter, the sample goes through MOCVD trench channel regrowth process as shown in fig. 3.10. The MOCVD regrowth process consisted of two steps. First, the samples were annealed in  $N_2/NH_3$  for 30 min. at 930 °C to recover trench-gate etch damage [38]. Even though this recovery anneal was performed, the extent to which this helps in healing etch damage is not known and studies need to be performed to characterize the impact of recovery anneal on the device performance. Following annealing, the UID-GaN interlayer (of desired thickness) was grown on the sample at 950 °C. At this temperature, no mass reflow was observed. Conformal regrowth of GaN interlayer was desired and achieved. GaN exhibits varied growth rates on different growth planes. The trench offers one such situation. The bottom part of the trench was c-plane GaN and sidewalls were oriented towards either a- or m-plane. It was observed that the sidewall growth rate was slower (approximately half) than the c-plane growth rate. This was estimated by performing transmission electron microscopy (TEM) studies. Multiple samples with gate trenches were prepared. On the first sample, the GaN interlayer was regrown followed by MOCVD oxide and gate metal deposition (Figure 3.11). On the second sample, GaN interlayer regrowth was followed AlGaN interlayer and MOCVD oxide regrowth and gate metal deposition. For the first sample, the GaN interlayer was not clearly visible as GaN on GaN was difficult to differentiate (Figure 3.11 a)). The oxide was visibly crystallizing at the GaN/oxide interface on the c-plane as shown in fig. 3.11 a). However, no such crystallization was observed at the sidewall GaN/oxide interface (Figure 3.11 b)). Therefore, it can be inferred that the oxide was amorphous on the sidewall. For the second sample, since AlGaN was used, regrown AlGaN layer was identified and characterized. Additionally, an AlN marker layer was also added as shown in fig. 3.12 and fig. 3.13 to identify the regrown GaN/AlGaN interface. The thickness observed on the c-plane was as targeted (~10 nm). However, on the sidewall, a thinner interlayer was observed (~5nm). Similar results were obtained for both *a*- and *m*-plane sidewalls. More details regarding regrowth conditions are described in the later sections.

Figure 3.11: TEM images of GaN interlayer sample. No Al<sub>2</sub>O<sub>3</sub> crystallization occurs on the sidewall as can be seen from a). However, on the etched c-plane Al<sub>2</sub>O<sub>3</sub> crystallizes (b). It can be seen from the left figure that Al<sub>2</sub>O<sub>3</sub> thickness on sidewall and c-plane was almost similar. (Copyright © 2016, IEEE)

Figure 3.12: The c-plane cross-section TEM image of the second sample. Here, a thin AlN interlayer was grown to identify the GaN/AlGaN interface. Here, it can be clearly observed that AlGaN regrows followed by Al<sub>2</sub>O<sub>3</sub> growth. Non-uniform crystallization of Al<sub>2</sub>O<sub>3</sub> can be observed as well.

Figure 3.13: The c-plane cross-section TEM image of the second sample. The AlGaN layers and marker layer are clearly visible. The amorphous nature of the oxide was again observed on the sidewall. It should be noted that the lower AlGaN thickness (~5nm) was observed on the sidewall compared to c-plane regrown AlGaN (~10 nm).

The GaN interlayer regrowth was followed by the in-situ deposition of the gate-dielectric. This is very important as an *in-situ* deposition of the gate-dielectric improves semiconductor/dielectric interface and channel properties compared to an *ex-situ* dielectric deposition. MOCVD grown aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) deposited at 700° C was predominately used as the gate-dielectric in this dissertation [39]. This dielectric was extensively studied through c-plane GaN planar *in-situ* MOSCAPs. In the later stages of this dissertation, Si alloyed aluminum oxide (AlSiO) was used due to improved gate-dielectric characteristics. The thickness of MOCVD Al<sub>2</sub>O<sub>3</sub> and AlSiO were kept 50 nm and 60 nm throughout this dissertation.

Figure 3.14: Cross-sectional schematic after source etch.

After the MOCVD regrowth, the gate-dielectric (Al<sub>2</sub>O<sub>3</sub>) and UID-GaN interlayer were etched in an inductive coupled plasma (ICP) system using CF<sub>4</sub>/O<sub>2</sub> (Recipe #134) gas mixture (Figure 3.14). The non-selective nature of dielectric and GaN interlayer etch results in source region etch as well. In this dissertation, this etch was timed such that 20-40 nm of source region was etched. This was done to ensure n<sup>+</sup>-GaN region exposure to form good ohmic (source) contact.

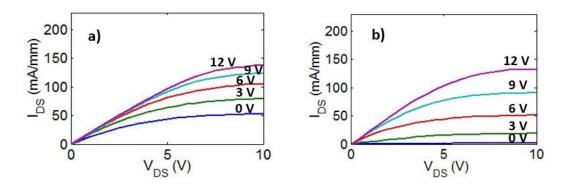

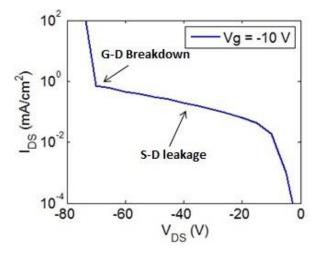

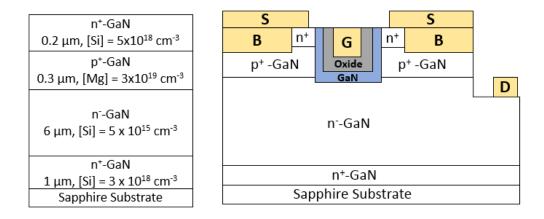

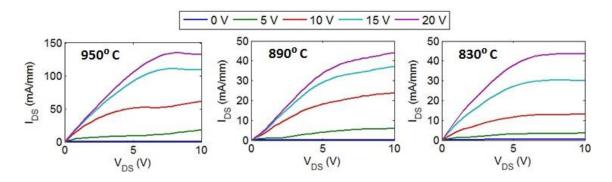

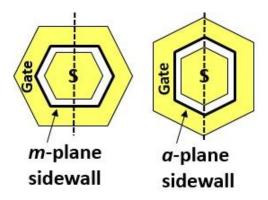

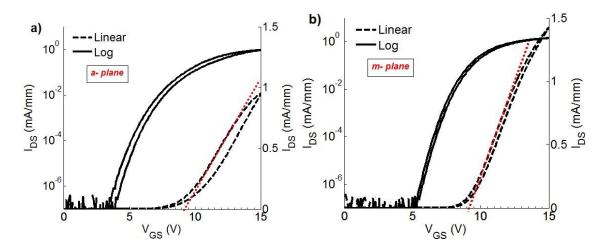

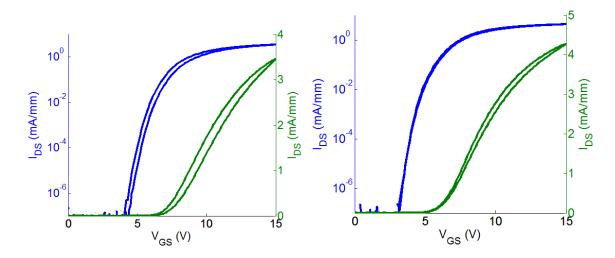

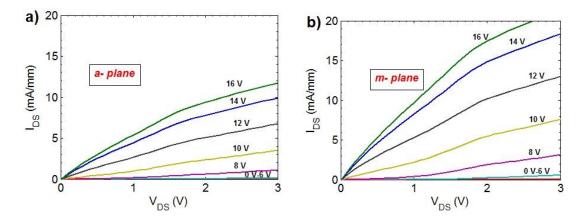

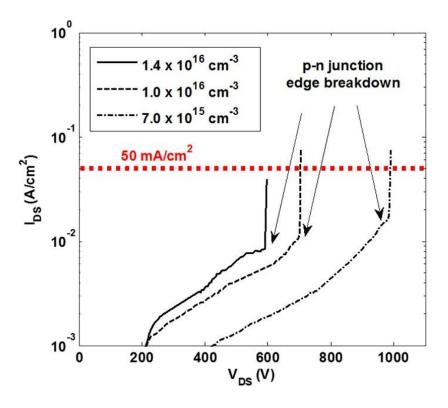

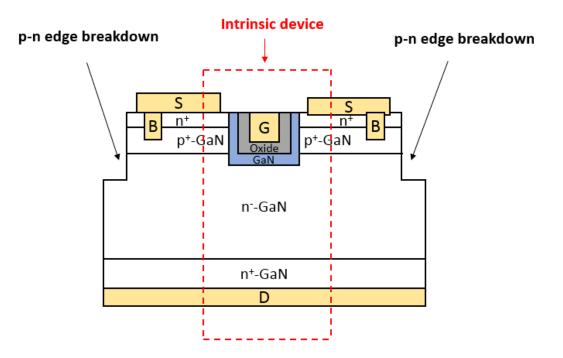

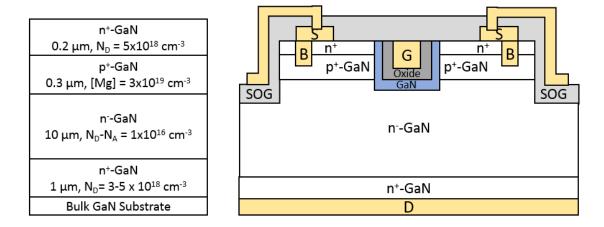

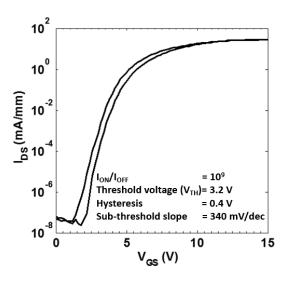

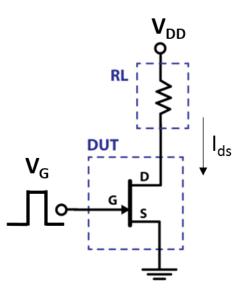

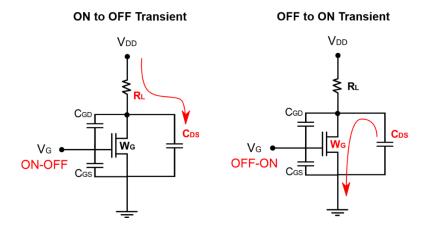

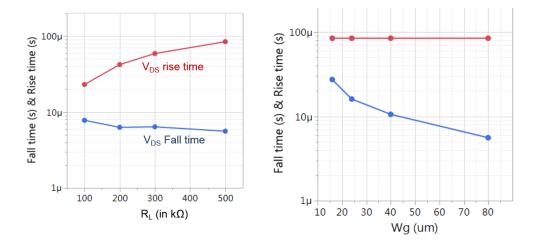

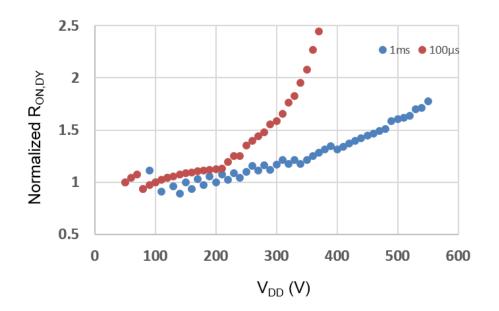

Figure 3.15: Cross-sectional schematic after body etch.