## **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Highly Scaled InP/InGaAs DHBTs Beyond 1 THz Bandwidth

#### **Permalink**

https://escholarship.org/uc/item/9db0g2gd

#### **Author**

Rode, Johann Christian

## **Publication Date**

2015

Peer reviewed|Thesis/dissertation

## UNIVERSITY of CALIFORNIA Santa Barbara

# Highly Scaled InP/InGaAs DHBTs Beyond 1 THz Bandwidth

A Dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Johann Christian Rode

### Committee in Charge:

Professor Mark J. W. Rodwell, Chair Professor Umesh K. Mishra Professor Christopher Palmstrøm Professor Robert York Doctor Miguel Urteaga

| The Dissertation of Johann Christian Rode is approved |

|-------------------------------------------------------|

|                                                       |

| Professor Umesh K. Mishra                             |

| Professor Christopher Palmstrøm                       |

| Professor Robert York                                 |

| Doctor Miguel Urteaga                                 |

| Doctor Miguer Offeaga                                 |

### Curriculum Vitæ Johann Christian Rode

#### Personal

Aug. 1982 Born in Paderborn, Germany.

#### Education

2014 Ph.D. in Electrical and Computer Engineering, University of Cali-

fornia, Santa Barbara.

2009 Diplom in Electrical Engineering (with distinction), Universität Karl-

sruhe, Germany.

#### **Publications**

- [1] J. C. Rode, H.-W. Chiang, P. Choudhary, V. Jain, B.J. Thibeault; W.J. Mitchell; M.J.W. Rodwell, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J.M. Fastenau, A.W.K. Liu, "Indium Phosphide Heterobipolar Transistor Technology Beyond 1 THz Bandwidth," in preparation.

- [2] **J. C. Rode**, H.-W. Chiang, P. Choudhary, V. Jain, B.J. Thibeault; W.J. Mitchell; M.J.W. Rodwell, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J.M. Fastenau, A.W.K. Liu, "An InGaAs/InP DHBT With Simultaneous  $f_{\tau}/f_{\text{max}}$  404/901 GHz and 4.3 V Breakdown Voltage," Electron Devices Society, IEEE Journal of the , vol.3, no.1, pp.54,57, Jan. 2015.

- [3] H. W. Chiang, J. C. Rode, P. Choudhary, and M. J. W. Rodwell, "Interfacial transport and current gain in InGaAs/InP DHBTs for THz applications," 72nd IEEE Device Research Conference, 2014.

- [4] H. W. Chiang, **J. C. Rode**, P. Choudhary, and M. J. W. Rodwell, "Lateral Carrier Diffusion and Current Gain in THz InGaAs/InP DHBTs," J. Appl. Phys., vol. 115, no. 3, pp. 034513, 2014.

- [5] S. Daneshgar, H.-C. Park, **J. C. Rode**, Z. Griffith, M. Urteaga, B.-S. Kim, M.J.W. Rodwell, "High efficiency W-band power amplifiers using ring-shaped sub-quarter-wavelength power combining technique," Microwave Symposium (IMS), 2014 IEEE MTT-S International, vol., no., pp.1,4, 1-6 June 2014.

- [6] H.-C. Park, S. Daneshgar, **J. C. Rode**, Z. Griffith, M. Urteaga, B.-S. Kim, M. Rodwell, "An 81 GHz, 470 mW, 1.1 mm<sup>2</sup> InP HBT power amplifier with 41 series power combining using sub-quarter-wavelength baluns," Microwave Symposium (IMS), 2014 IEEE MTT-S International, vol., no., pp.1,4, 1-6 June 2014.

- [7] H.-C. Park, S. Daneshgar, J. C. Rode, Z. Griffith, M. Urteaga, B.-S. Kim, M. Rodwell, "30% PAE W-Band InP Power Amplifiers Using Sub-Quarter-Wavelength Baluns for Series-Connected Power-Combining," Compound Semi-conductor Integrated Circuit Symposium (CSICS), 2013 IEEE, vol., no., pp.1,4, 13-16 Oct. 2013.

- [8] M. J. W. Rodwell, M. Seo, J. Hacker, A. Young, Z. Griffith, R. Pierson, M. Urteaga, J. C. Rode, H. W. Chiang, V. Jain, E. Lobisser, T. Reed, A. Baraskar, J. J. M. Law, A. D. Carter, S. Lee, D. C. Elias, B. J. Thibeault, W. J. Mitchell, S. Stemmer, A. C. Gossard, S. Mehotra, M. Povolotskyi, G. Klimeck, "Transistor and IC design for Sub-mm-wave and THz ICs," 2012 European Microwave IC Conference, 2012.

- [9] M. J. W. Rodwell, J. C. Rode, H. W. Chiang, P. Choudhary, T. Reed, E. Bloch, S. Danesgar, H-C Park, A. C. Gossard, B. J. Thibeault, W. J. Mitchell, M. Urteaga, Z. Griffith, J. Hacker, M. Seo, B. Brar, "THz Indium Phosphide Bipolar Transistor Technology," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium, 2012.

- [10] E. Lobisser, J. C. Rode, V. Jain, H. W. Chiang, A. Baraskar, W. J. Mitchell, B. J. Thibeault, Mark J. W. Rodwell, "InGaAs/InP DHBTs with Emitter and Base Defined through Electron-Beam Lithography for Reduced Ccb and Increased RF Cut-off Frequency," 39th International Symposium on Compound Semiconductors, 2012.

- [11] V. Jain, J. C. Rode, H. W. Chiang, A. Baraskar, E. Lobisser, B. J. Thibeault, M. J. W. Rodwell, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J. M. Fastenau, W. K. Liu, "1.0 THz f<sub>max</sub> InP DHBTs in a refractory emitter and self-aligned base process for reduced base access resistance," 69th IEEE Device Research Conference, 2011.

- [12] M.H. Beringer, S. Illy, J. Jin, S. Kern, **J. C. Rode**, M. Thumm, "Further design steps towards a 4 MW 170 GHz coaxial-cavity gyrotron," Infrared, Millimeter, and Terahertz Waves, 2009. IRMMW-THz 2009. 34th International Conference on , vol., no., pp.1,2, 21-25 Sept. 2009.

- [13] J. C. Rode, M.H. Beringer; S. Illy, S. Kern, B. Piosczyk, M. Thumm, "Design study of magnetron injection guns for a 4 MW 170 GHz coaxial gyrotron," Vacuum Electronics Conference, 2009. IVEC '09. IEEE International, vol., no., pp.96,97, 28-30 April 2009.

- [14] R. Bonk, R. Brenot, C. Meuer, T. Vallaitis, A. Tussupov, **J. C. Rode**, et al., "1.3/1.5 m QD-SOAs for WDM/TDM GPON with extended reach and large upstream/downstream dynamic range. In Optical Fiber Communication Conference (p. OWQ1)", Optical Society of America, 2009.

#### Abstract

# Highly Scaled InP/InGaAs DHBTs

Beyond 1 THz Bandwidth

by

#### Johann Christian Rode

This work examines the efforts pursued to extend the bandwidth of InP-based DHBTs above 1 THz. Aggressive lithographic and epitaxial scaling of key device dimensions and simultaneous reduction of contact resistivities have enabled increased RF bandwidths by reduction of device RC and transit delays. A fabrication process for forming base electrodes and base/collector mesas of highly scaled transistors has been developed that exploits superior resolution (10 nm) and alignment (sub-30 nm) of electron beam lithography. Ultra-low resistance, thermally stable base contacts are critical for extended  $f_{\text{max}}$  bandwidth: a novel dual-deposition base metalization technique is presented that removes contaminating lithographic processes from the formation of the base contact, thereby enabling low resistivity contacts  $(4 \Omega \,\mu\text{m}^2)$  to ultra-thin base layers (20 nm). The composite base metal stack exploits an ultra-thin layer of platinum that controllably reacts with base, yielding low contact resistivity, as well as a thick refractory diffusion barrier which permits stable operation at high current densities and elevated temperatures. Reduction in emitter-base surface leakage and subsequent increase of current gain was achieved by passivating emitter-base semiconductor surfaces with conformally grown ALD  $Al_2O_3$ . RF bandwidth limiting parasitics associated to the perimeter of highly scaled transistors have been identified and significantly reduced, among which are high sheet resistance of base electrodes, excess undercut of emitter stripes and improperly scaled base posts. At 100 nm collector thickness, the breakdown voltage of the transistor  $BV_{CEO}$  has been increased to more than 4.1 V by passivating base/collector surfaces.

With the technology improvements discussed, transistors with  $f_{\tau}$  of 480 GHz and  $f_{\text{max}}$  in excess of 1 THz have been demonstrated at 200 nm emitter width and 80 nm single-sided base contact width. Transistors at the same emitter width, but 30 nm base contact width exhibit  $f_{\tau}$  of 550 GHz and  $f_{\text{max}}$  of 850 GHz. Estimations from a finite element model predict higher bandwidth on smaller footprint transistors. However, inadequacies of RF calibration structures prevent  $f_{\text{max}}$  extraction on these devices.

# Contents

| $\mathbf{C}$  | urric | ulum '                                                         | Vitæ                                 | <b>iii</b><br>iii |

|---------------|-------|----------------------------------------------------------------|--------------------------------------|-------------------|

| $\mathbf{A}$  | bstra | ${f ct}$                                                       |                                      | v                 |

| $\mathbf{Li}$ | st of | Figure                                                         | es                                   | xi                |

| $\mathbf{Li}$ | st of | Table                                                          | $\mathbf{s}$                         | xvi               |

| 1             |       | $egin{array}{c} \mathbf{oduct} \\ \mathbf{rences} \end{array}$ | ion<br>                              | <b>1</b><br>5     |

| 2             | InP   | Bipol                                                          | ar Transistor Design                 | 6                 |

|               | 2.1   | Princi                                                         | ple of Operation                     | 6                 |

|               | 2.2   |                                                                | e Topology                           | 8                 |

|               |       | 2.2.1                                                          | Emitter Design                       | 10                |

|               |       | 2.2.2                                                          | Base Design                          | 14                |

|               |       | 2.2.3                                                          | Collector Design                     | 15                |

|               | 2.3   | TLM                                                            | Structures                           | 17                |

|               | 2.4   | Equiva                                                         | alent Circuit Model                  | 22                |

|               |       | 2.4.1                                                          | Emitter Access Resistance $R_{ex}$   | 22                |

|               |       | 2.4.2                                                          | Base Access Resistance $R_{bb}$      | 25                |

|               |       | 2.4.3                                                          | Collector Access Resistance $R_{cc}$ | 30                |

|               |       | 2.4.4                                                          | Base-Collector Capacitance $C_{cb}$  | 33                |

|               |       | 2.4.5                                                          | Base-Emitter Resistance $R_{be}$     | 34                |

|               |       | 2.4.6                                                          | Base-Collector Resistance $R_{cb}$   | 35                |

|               |       | 2.4.7                                                          | Base-Emitter Capacitance $C_{be}$    | 35                |

|               | 2.5   | Figure                                                         | es of Merit                          | 35                |

|               | 2.6   |                                                                | buted Circuit Model                  | 41                |

|               | 2.7   | Scalin                                                         | g Laws                               | 43                |

| InF                    | P HBT Fabrication Technology                                            |

|------------------------|-------------------------------------------------------------------------|

| 3.1                    | Process Overview                                                        |

| 3.2                    | Emitter Process Improvements                                            |

|                        | 3.2.1 Emitter Shape                                                     |

|                        | 3.2.2 Chrome Hard Mask Removal                                          |

|                        | 3.2.3 Surface Preparation for Emitter Wet Etch                          |

|                        | 3.2.4 Emitter End Undercut                                              |

| 3.3                    | Base Process Improvements                                               |

|                        | 3.3.1 Electron Beam Lithography Strategies                              |

|                        | 3.3.2 Base Metal Formation by Electron Beam Lithography                 |

|                        | 3.3.3 Base Mesa Formation by Electron Beam Lithography                  |

|                        | 3.3.4 Dual-Deposition Base Metal Process                                |

|                        | 3.3.5 Base Post Scaling                                                 |

| 3.4                    | Collector Process Improvements                                          |

| 3.5                    | Backend Improvements                                                    |

|                        | 3.5.1 Device Passivation                                                |

|                        | 3.5.2 Low Temperature Nitride                                           |

|                        | 3.5.3 Tapered Base Feed Line                                            |

| 3.6                    | Scaled TLM Process                                                      |

| Ref                    | erences                                                                 |

| $\mathbf{E}\mathbf{x}$ | perimental Results                                                      |

| 4.1                    |                                                                         |

|                        | 4.1.1 DC Characteristics                                                |

|                        | 4.1.2 Small-signal Microwave Characteristics                            |

| 4.2                    | HBT 56                                                                  |

|                        | 4.2.1 Epitaxial Design                                                  |

|                        | 4.2.2 Fabrication                                                       |

|                        | 4.2.3 DC Characteristics                                                |

|                        | 4.2.4 Microwave Characteristics                                         |

|                        | 4.2.5 TEM Analysis                                                      |

|                        | 4.2.6 Discussion                                                        |

| 4.3                    | Scaled TLM Results                                                      |

|                        | 4.3.1 Sample 121217E                                                    |

|                        | 4.3.2 Scaled TLM Samples with Emitter Processing                        |

|                        | 4.3.3 Discussion                                                        |

|                        |                                                                         |

|                        | 4.3.4 Scaled TLM Sample with Emitter and Dual-Deposited Base            |

|                        | 4.3.4 Scaled TLM Sample with Emitter and Dual-Deposited Base Processing |

| 4.4                    |                                                                         |

|              |      | 4.4.2    | Fabrication                               |

|--------------|------|----------|-------------------------------------------|

|              |      | 4.4.3    | DC Characteristics                        |

|              |      | 4.4.4    | Microwave Characteristics                 |

|              |      | 4.4.5    | TEM Analysis                              |

|              |      | 4.4.6    | Discussion                                |

|              | Refe | rences . |                                           |

| 5            | Con  | clusion  | $12^{4}$                                  |

|              | 5.1  | Accom    | plishments                                |

|              | 5.2  | Future   | Work                                      |

|              | Refe | rences . |                                           |

| $\mathbf{A}$ | Tera | ahertz   | HBT Process Flow 13:                      |

|              | A.1  |          | e Preparation                             |

|              | A.2  |          | r Formation                               |

|              |      | A.2.1    | Emitter Surface Preparation               |

|              |      | A.2.2    | Emitter Mo Evaporation                    |

|              |      | A.2.3    | Emitter W/TiW Calibration and Deposition  |

|              |      | A.2.4    | Sacrificial $SiO_2/SiN_x$ Deposition      |

|              |      | A.2.5    | Chrome Hardmask Deposition                |

|              |      | A.2.6    | Emitter Lithography                       |

|              |      | A.2.7    | Emitter Hardmask Etch                     |

|              |      | A.2.8    | Emitter Contact Dry Etch                  |

|              |      | A.2.9    | Etch Hardmask Removal                     |

|              |      | A.2.10   | First Sidewall Formation                  |

|              |      | A.2.11   | Emitter InGaAs Wet Etch                   |

|              |      | A.2.12   | Second Sidewall Formation                 |

|              | A.3  | Base F   | ormation                                  |

|              |      | A.3.1    | Emitter InP Etch / Base Contact Formation |

|              |      | A.3.2    | Base $Al_2O_3$ Passivation                |

|              |      | A.3.3    | Base Sidewall Formation                   |

|              |      | A.3.4    | Base Electrode Lithography                |

|              |      | A.3.5    | Base Electrode Liftoff                    |

|              |      | A.3.6    | Base Post Lithography                     |

|              |      | A.3.7    | Base Post Liftoff                         |

|              |      | A.3.8    | Base Mesa Lithography                     |

|              |      | A.3.9    | Base Mesa Etch                            |

|              | A.4  | Collect  | or Formation                              |

|              |      | A.4.1    | Collector Electrode Lithography           |

|              |      | A.4.2    | Collector Electrode Liftoff               |

|              |      | A.4.3    | Device Isolation Lithography              |

|              |      | Δ 1 1    | Davies Isolation Etch                     |

|     | A.4.5  | Collector Post Formation                  | 149 |

|-----|--------|-------------------------------------------|-----|

| A.5 | Back-I | End Fabrication                           | 149 |

|     | A.5.1  | $SiN_x$ Passivation and BCB Planarization | 149 |

|     | A.5.2  | BCB Ashing                                | 150 |

|     | A.5.3  | Contact Via Deposition                    | 151 |

|     | A.5.4  | Contact Via Lithography                   | 151 |

|     | A.5.5  | Contact Via Etch                          | 151 |

|     | A.5.6  | Post Cleanup Sputter                      | 152 |

|     | A.5.7  | Metal 1 Formation                         | 153 |

|     | A.5.8  | Metal 1 Cleanup Sputter                   | 153 |

# List of Figures

| 2.1  | Band diagram of heterobipolar transistor under bias with valence band                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (VB) and conduction band (CB), showing bands with no (black) and                                                                                        |    |

|      | Kirk (blue) current density in the collector                                                                                                            | 7  |

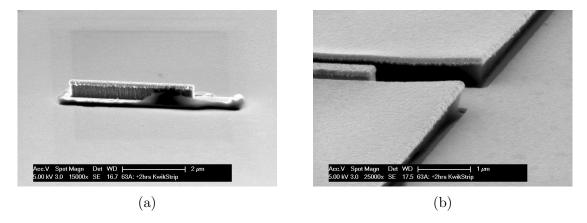

| 2.2  | Angled scanning electron micrograph (SEM) of a fabricated hetero-                                                                                       |    |

|      | junction bipolar transistor prior to BCB planarization                                                                                                  | 8  |

| 2.3  | Cross-sectional schematic of a triple-mesa HBT with metal (yellow),<br>low bandgap semiconductor (red) and wide bandgap semiconductor                   |    |

|      | (blue). Key dimensions labeled                                                                                                                          | 9  |

| 2.4  | · / · · ·                                                                                                                                               | Э  |

| 2.4  | Conduction band profile at the abrupt emitter base junction for increasing $J_e(V_{be})$ . As $J_e$ is increased, a barrier for the electrons is formed |    |

|      | in emitter that does not coincide with the metallurgical heterointerface                                                                                |    |

|      | anymore                                                                                                                                                 | 11 |

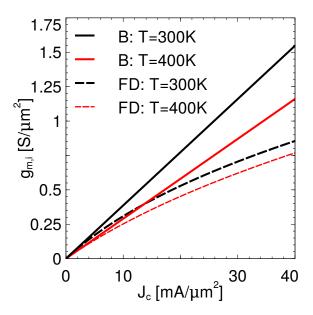

| 2.5  | Transconductance calculated with Boltzmann (B) and Fermi-Dirac (FD)                                                                                     |    |

|      | statistics at temperatures $T=300\mathrm{K}$ and $400\mathrm{K}$                                                                                        | 13 |

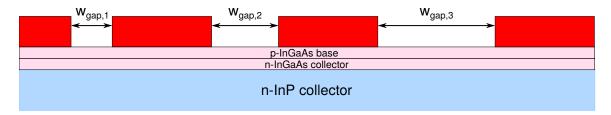

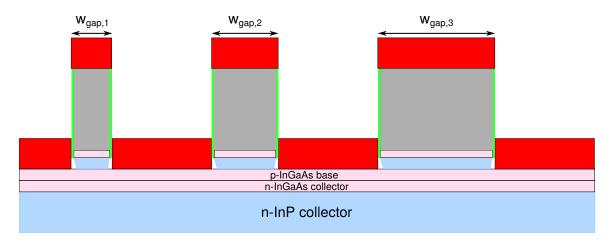

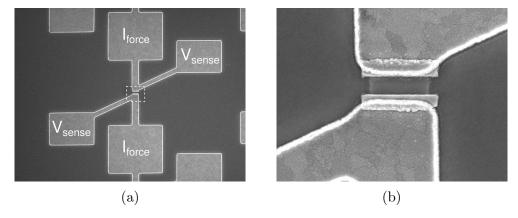

| 2.6  | Non-pinched TLM structure with exposed base semiconductor surface.                                                                                      | 20 |

| 2.7  | Pinched TLM structure with gaps defined by emitter metal                                                                                                | 20 |

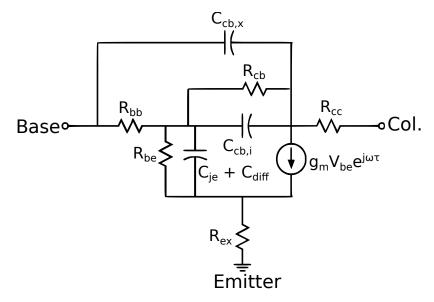

| 2.8  | Hybrid- $\pi$ model of a bipolar transistor                                                                                                             | 23 |

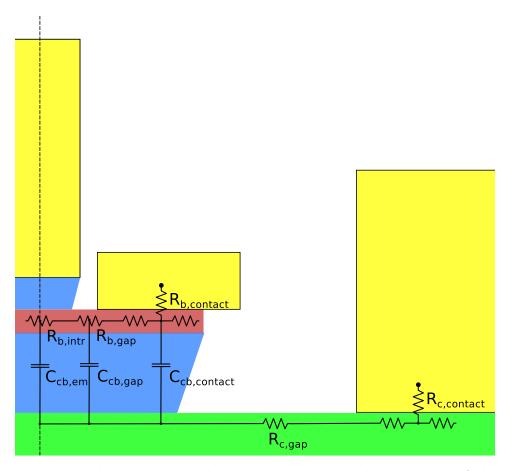

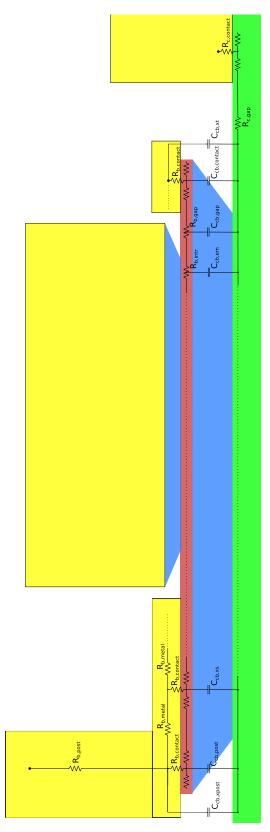

| 2.9  | Equivalent circuit overlaid to a cross-sectional illustration of the active                                                                             |    |

|      | transistor across the emitter                                                                                                                           | 25 |

| 2.10 | 1                                                                                                                                                       |    |

|      | along the emitter                                                                                                                                       | 26 |

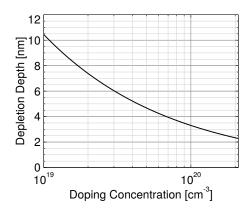

| 2.11 | Depletion depth of p-InGaAs as a function of doping concentration                                                                                       |    |

|      | assuming Fermi level pinning $0.2\mathrm{eV}$ below the conduction band                                                                                 | 29 |

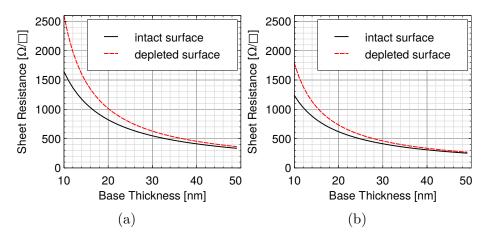

| 2.12 | Sheet resistance of p-InGaAs semiconductor doped from (a) $9 \times 10^{19}/\text{cm}^3$                                                                |    |

|      | to $4 \times 10^{19} / \text{cm}^3$ and (b) $12 \times 10^{19} / \text{cm}^3$ to $8 \times 10^{19} / \text{cm}^3$ as a function                         |    |

|      | of layer thickness. Solid: no surface depletion. Dotted: surface depleted.                                                                              | 30 |

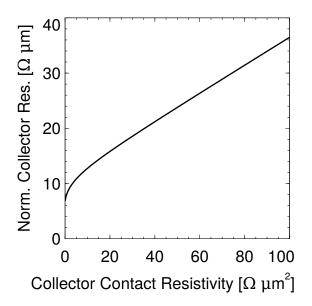

| 2.13 | Normalized collector resistance $R'_{cc} = R_{cc} L_e$ as a function of spe-                                                                            |    |

|      | cific contact resistance $\rho_{c,\text{contact}}$ assuming $R_{sh} = 16 \Omega/\Box$ , $w_{cc} = 2 \mu\text{m}$ ,                                      |    |

|      | $w_{c,gap} = 750 \text{nm},  w_{mesa} = 260 \text{nm}.  \dots \dots \dots \dots \dots \dots$                                                            | 32 |

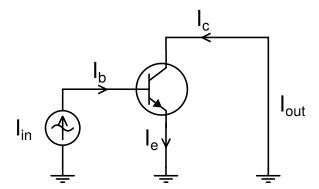

| 2.14 | Bipolar transistor with short-circuited output biased with base current source.                                                            | 36  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

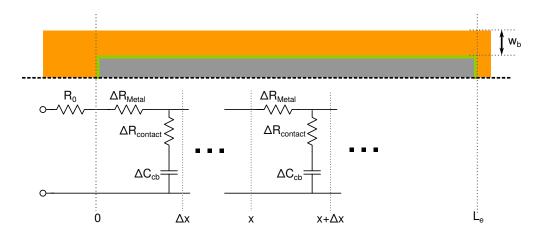

| 2.15 | Circuit schematics for estimating charging time constant $\tau_{cb}$ due to                                                                | 50  |

| 2.10 | voltage drops along the emitter stripe                                                                                                     | 38  |

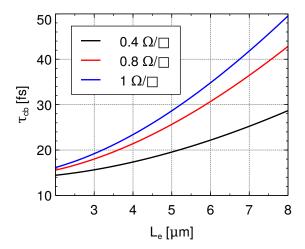

| 2.16 | Numerical calculations of charging delay $\tau_{cb}$ as a function of emitter                                                              | 00  |

|      | length $L_e$ for different base metal sheet resistance $R_{sh}$ . A finite element                                                         |     |

|      | model has been used that has been matched to a fabricated transistor.                                                                      | 40  |

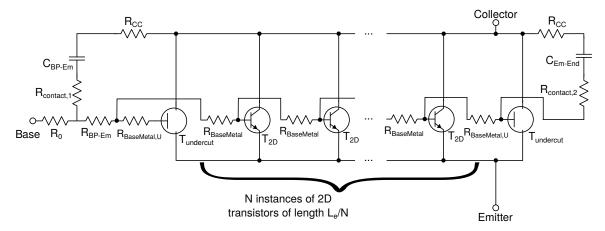

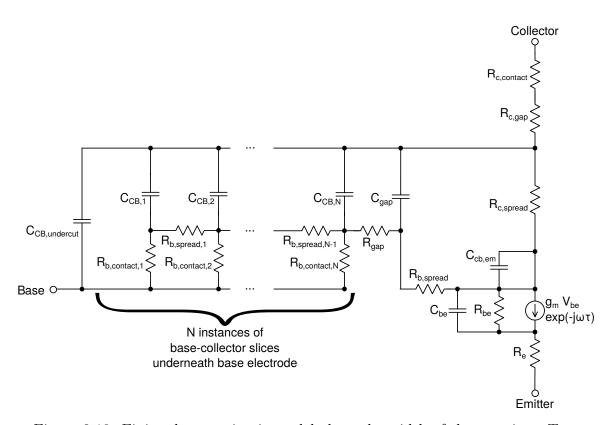

| 2.17 | Finite element circuit model along the length of the transistor                                                                            | 42  |

|      | Finite element circuit model along the width of the transistor $T_{2D}$                                                                    | 42  |

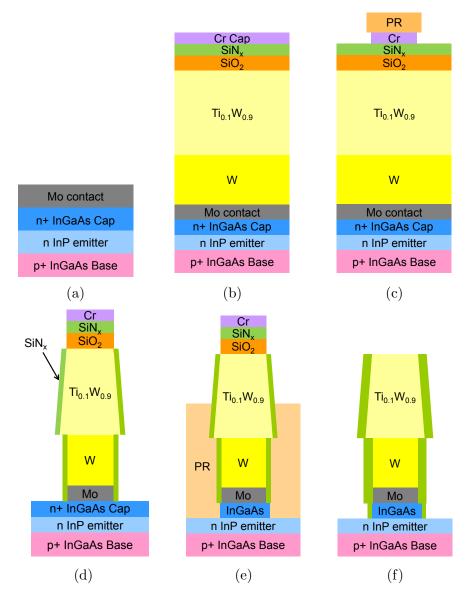

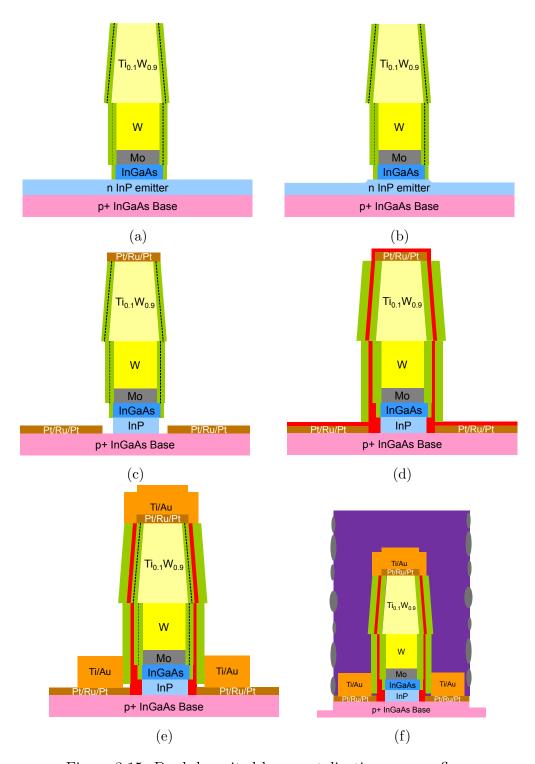

| 3.1  | HBT Process: Emitter metal and sidewall formation                                                                                          | 51  |

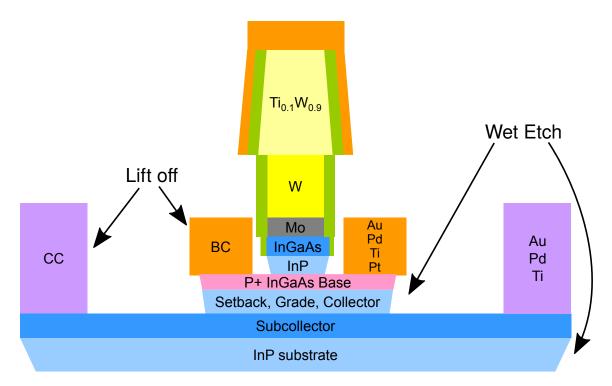

| 3.2  | HBT Process: Base and collector electrode formation                                                                                        | 53  |

| 3.3  | Transferred emitter pattern into chrome hard mask without (a) and                                                                          |     |

|      | with (b) rounding the edges of emitter stripes                                                                                             | 55  |

| 3.4  | Failure modes of the chrome hard mask removal process: (a) chrome                                                                          |     |

|      | hard mask has collapsed onto emitter, (b) chrome hard mask has fallen                                                                      |     |

|      | onto the semiconductor, and damaged photoresist has contaminated                                                                           |     |

| 2.5  | the semiconductor surface                                                                                                                  | 55  |

| 3.5  | Discoloration of surface around emitters after stripping of the pla-                                                                       | 56  |

| 3.6  | narization resist in the chrome hard mask removal process                                                                                  | 30  |

| 5.0  | as a result of diluted NH <sub>4</sub> OH surface treatment (a) immediately after                                                          |     |

|      | the wet etch and (b) after a solvent clean (rinse in acetone, isopropyl                                                                    |     |

|      | alcohol, deionized water)                                                                                                                  | 58  |

| 3.7  | Emitter after oxidation/oxide removal cycles and InP wet etch showing                                                                      |     |

|      | uniform base surface without any signs of contamination                                                                                    | 59  |

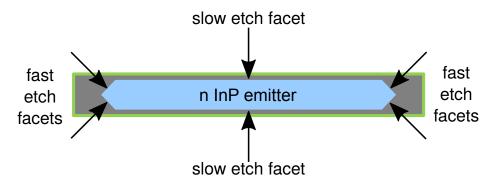

| 3.8  | Bottom-up view of the emitter with slow and fast etch facets                                                                               | 60  |

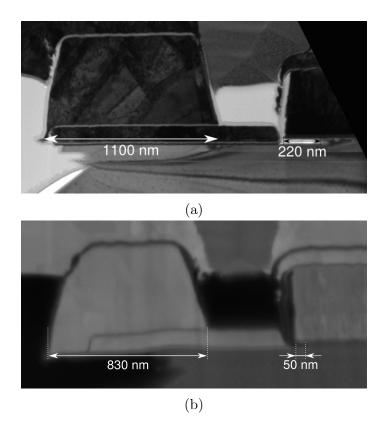

| 3.9  | Emitter end and base post undercut/scaling between (a) regular (a)                                                                         |     |

|      | and (b) improved process                                                                                                                   | 60  |

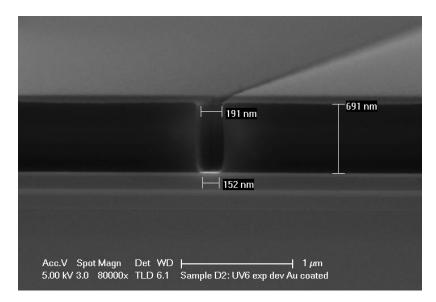

| 3.10 | Cross-sectional SEM of exposed and developed UV6 resist coated with                                                                        |     |

|      | a thin layer of Au for enhanced contrast                                                                                                   | 64  |

| 3.11 | UV6 resist damaged by electron and x-ray radiation during electron                                                                         |     |

|      | beam evaporation. (a) Residues around lifted-off base electrode, (b)                                                                       |     |

|      | lift-off failure due to damaged resist sidewalls that failed to be removed                                                                 | C.F |

| 2 10 | in photoresist stripper                                                                                                                    | 65  |

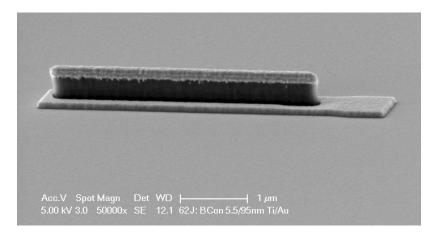

|      | Emitter with base electrode lifted off using PMGI/ZEP                                                                                      | 65  |

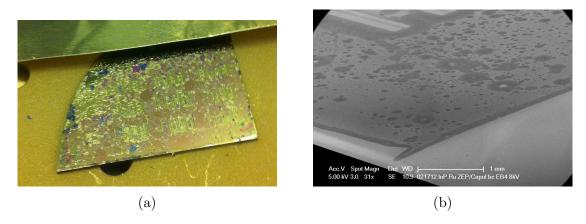

| 3.13 | ZEP resist damaged by electron and x-ray radiation during electron<br>beam evaporation. (a) photograph of a sample immediately after evap- |     |

|      | oration showing resist blistering, (b) low magnification SEM of a sam-                                                                     |     |

|      | ple after stripping blistered resist                                                                                                       | 66  |

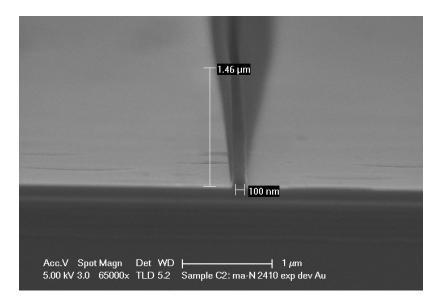

| 3.14 | Cross-sectional SEM of a 100 nm wide line in maN2410                                                                                       | 68  |

|      | Dual deposited base metalization process flow                                                                                              | 69  |

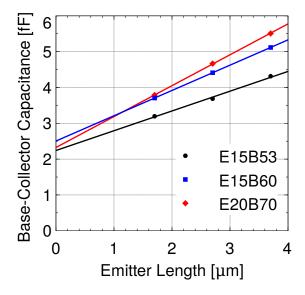

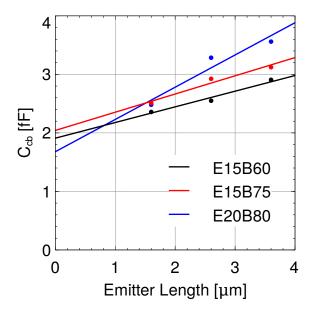

| 3.16 | Base-collector capacitance at Kirk current density of a set of devices with identical widths as a function of emitter length. The intercept                                                                          |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

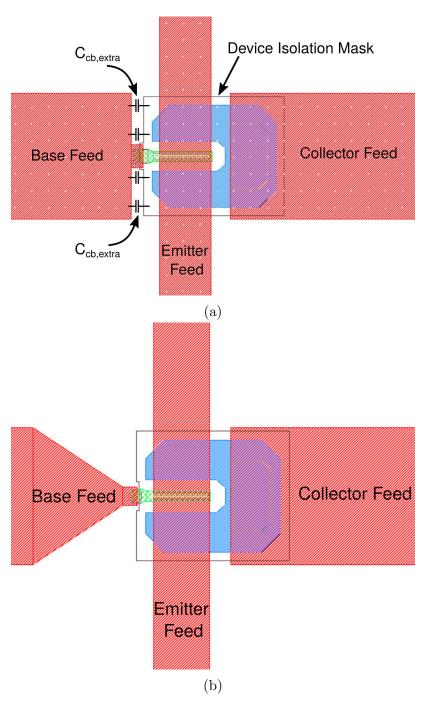

| 3 17 | gives an estimate for the capacitance of the base post $C_{cb,post} \approx 2.2 \text{fF}$ .<br>Metal 1 mask layout adjustments to reduce overlap capacitance be-                                                    | 72       |

|      | tween base feed line and subcollector: (a) before adjustment, (b) after.                                                                                                                                             | 76       |

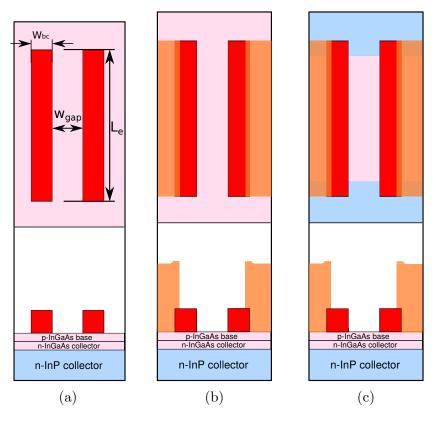

| 3.10 | Top-down and cross-sectional view of scaled TLM process for unpinched TLMs. Gap spacing $w_{gap} \approx w_e$ , contact pad width $\approx w_{bc}$ , pad dimensions a second scale of $v_{bc}$ .                     | 70       |

| 3.19 | sions perpendicular to gap $L_e$                                                                                                                                                                                     | 78<br>78 |

| 3.20 |                                                                                                                                                                                                                      | 79       |

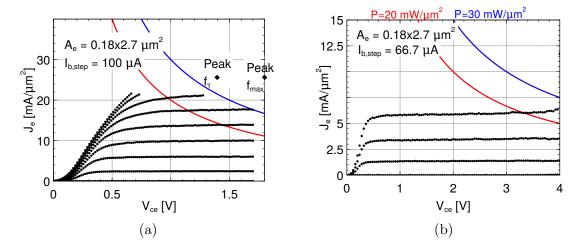

| 4.1  | Numerically calculated band structure of HBT56 for $J_e$ =0 mA/ $\mu$ m <sup>2</sup> (black) and $J_e$ =24 mA/ $\mu$ m <sup>2</sup> (blue), $V_{cb}$ =1 V, $V_{be}$ =1 V, $V_{cb}$ =0.7 V. A                         |          |

| 4.2  | current spreading factor of $J_e/J_c \approx 2$ was assumed                                                                                                                                                          | 89       |

| 4.3  | operation                                                                                                                                                                                                            | 90       |

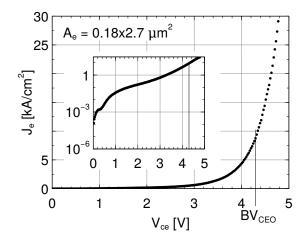

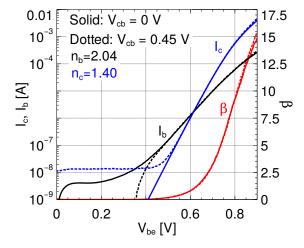

| 4.4  | tracted when the emitter current density is $10\mathrm{kA/cm^2}$ Gummel characteristics for an HBT with $180\mathrm{nm} \times 2.7\mu\mathrm{m}$ emitter junc-                                                       | 91       |

| 4.5  | tion area                                                                                                                                                                                                            | 91<br>92 |

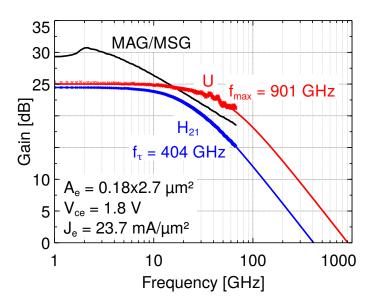

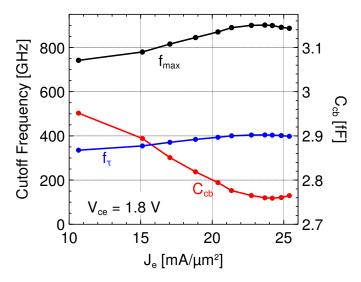

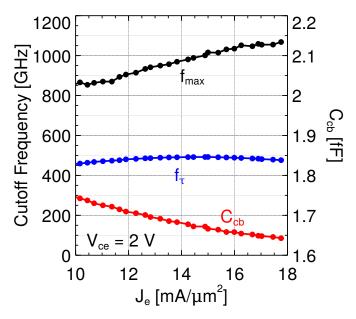

| 4.6  | Variation of $f_{\tau}$ , $f_{max}$ and $C_{cb}$ with $J_e$ at $V_{ce} = 1.8 \mathrm{V}$ for an HBT with $180 \mathrm{nm} \times 2.7 \mathrm{\mu m}$ emitter junction area and $310 \mathrm{nm}$ base-collector mesa | 0.0      |

| 4.7  | width                                                                                                                                                                                                                | 93       |

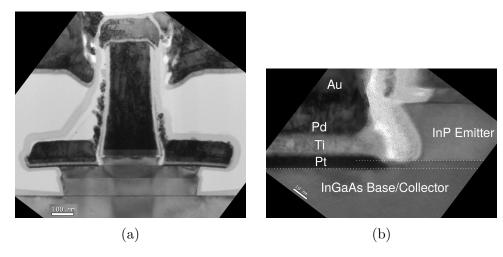

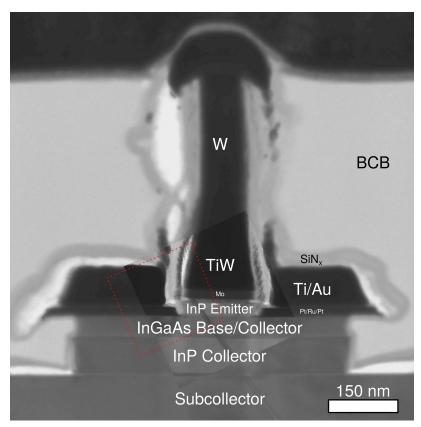

| 4.8  | 4.5 and (x) simulated S-parameters from 0.5 to 67 GHz Cross-sectional TEMs of (a) the entire device, (b) magnified at the emitter-base region. Emitter junction width $w_e = 240 \mathrm{nm}$ , single-              | 94       |

|      | sided base metal width $w_{bm}=220\mathrm{nm},$ single-sided base mesa undercut                                                                                                                                      | 05       |

| 4.9  | $w_{bmu} = 125 \mathrm{nm}$ , emitter-base contact spacing $w_{Gap} \approx 12 \mathrm{nm}$ Variation of base-collector capacitance $C_{cb}$ versus emitter length $L_e$ for                                         | 95       |

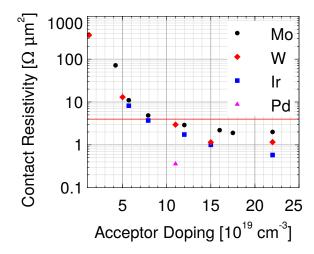

| 4.10 | different device geometries. Intersect $C_{cb,\text{excess}} \approx 2 \text{ fF}$ Variation of contact resistivity $\rho_c$ to p-InGaAs at different doping levels                                                  | 96       |

|      | for metals Mo, W, Ir and Pd [9]. The red line indicates the upper limit for 100 nm collector thickness HBT node $\rho_c = 4 \Omega  \mu \text{m}^2 \dots \dots$                                                      | 98       |

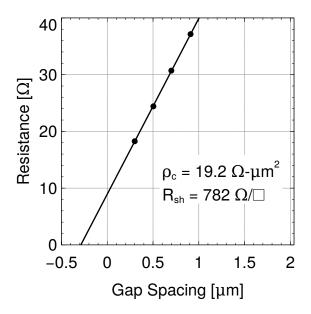

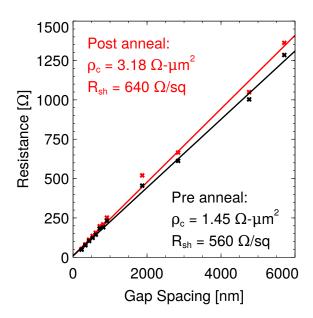

| 4.11 | Measured base TLM resistance as a function of gap spacing on sample HBT65D: 15 nm Ru contact to 18 nm p-InGaAs base with a doping |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|      | grade from $14-9 \times 10^{19} / \text{cm}^3$                                                                                    | 98  |

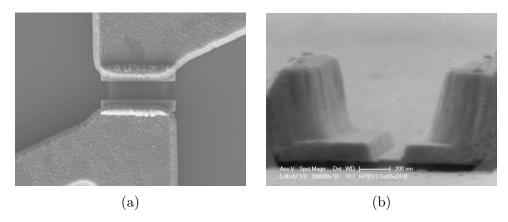

| 4.12 | (a) Top-down and (b) $85^{\circ}$ SEMs of a scaled TLM on sample $121217E$                                                        |     |

|      | fabricated without emitter processing                                                                                             | 99  |

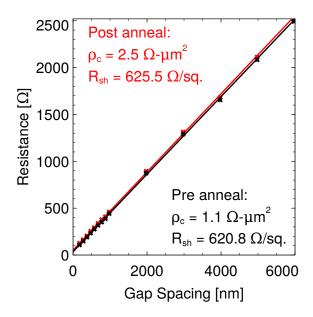

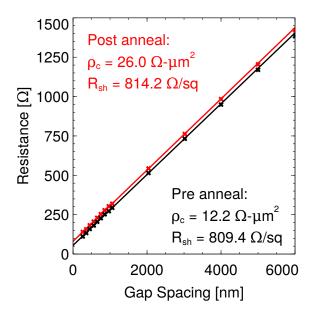

| 4.13 | Measured TLM resistance as a function of pad spacing for the sample                                                               |     |

|      | 121217E                                                                                                                           | 100 |

| 4.14 | SEM of pinched TLM structure on TLMv3D after deposition of TLM electrodes                                                         | 101 |

| 4.15 | Measured TLM resistance as a function of pad spacing for the sample                                                               |     |

|      | TLMv3D                                                                                                                            | 102 |

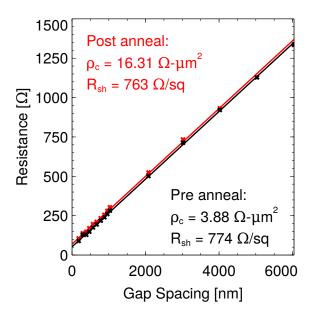

| 4.16 | Measured TLM resistance as a function of pad spacing for the sample                                                               |     |

|      | TLMv3C                                                                                                                            | 103 |

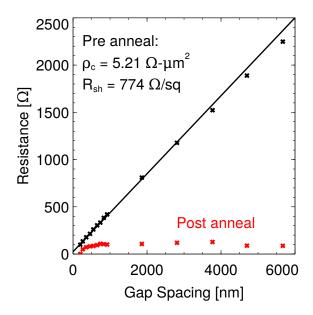

| 4.17 | Measured TLM resistance as a function of pad spacing for the sample                                                               |     |

|      | TLMv3O                                                                                                                            | 104 |

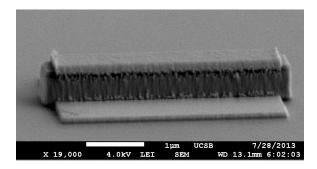

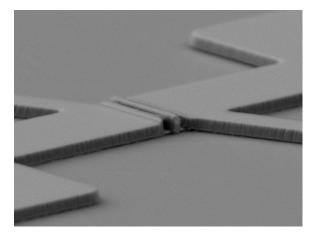

| 4.18 | SEM of pinched TLM structure on TLMv3B at 80° after fabrication.                                                                  | 106 |

|      | Measured TLM resistance as a function of pad spacing for the sample                                                               |     |

|      | TLMv3B                                                                                                                            | 106 |

| 4.20 | Numerically calculated band structure of HBT64 for $J_e=0\mathrm{mA/\mu m^2}$                                                     |     |

|      | (black) and $J_e=18 \mathrm{mA/\mu m^2}$ (blue), $V_{cb}=1 \mathrm{V}, V_{be}=1 \mathrm{V}, V_{cb}=0.7 \mathrm{V}$ . A            |     |

|      | current spreading factor of $J_e/J_c \approx 1.5$ was assumed                                                                     | 108 |

| 4.21 | · · · · · · · · · · · · · · · · · · ·                                                                                             |     |

|      | planarization indicating rough surface in the field                                                                               | 109 |

| 4.22 | Accidental emitter-to-base shorts on metal 1 interconnect layer (a)                                                               |     |

|      | before and (b) after dry etch                                                                                                     | 109 |

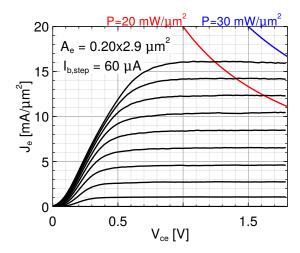

| 4.23 | Common-emitter characteristics of a transistor with junction area 200 nm                                                          |     |

|      | х 2.9 µm                                                                                                                          | 111 |

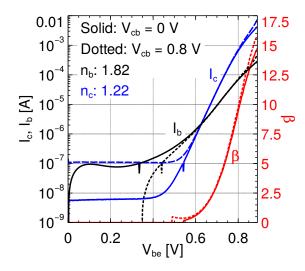

| 4.24 | Gummel characteristics for an HBT with 200 nm x 2.9 µm emitter junc-                                                              |     |

|      | tion area.                                                                                                                        | 112 |

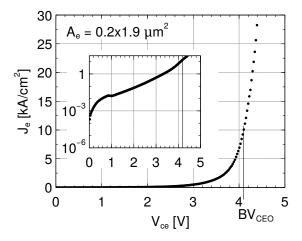

| 4.25 | Common-emitter breakdown measurement with floating base of a tran-                                                                |     |

|      | sistor with junction area 200 nm x 1.9 µm. $BV_{ceo} = 4.1 \mathrm{V}$ has been                                                   |     |

|      | extracted when the emitter current density is $10 \mathrm{kA/cm^2}$                                                               | 112 |

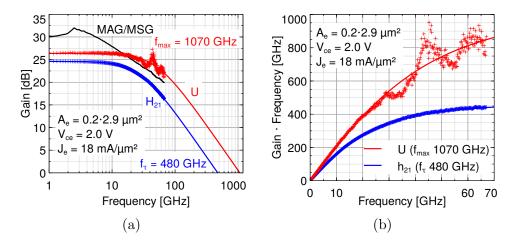

| 4.26 | Microwave gains for an HBT with 200 nm x 2.9 μm emitter junction                                                                  |     |

|      | area. (a) Double logarithmic plot, (b) linear plot of gain-frequency vs                                                           |     |

|      | frequency. Single pole fit yields $f_{\tau}$ 470 GHz, $f_{\text{max}}$ 1070 GHz                                                   | 113 |

| 4.27 | Variation of $f_{\tau}$ , $f_{max}$ and $C_{cb}$ with $J_e$ at $V_{ce} = 2.0 \mathrm{V}$ for an HBT with                          |     |

|      | $200\mathrm{nm}$ x $2.9\mu\mathrm{m}$ emitter junction area and $390\mathrm{nm}$ base-collector mesa                              |     |

|      | width                                                                                                                             | 113 |

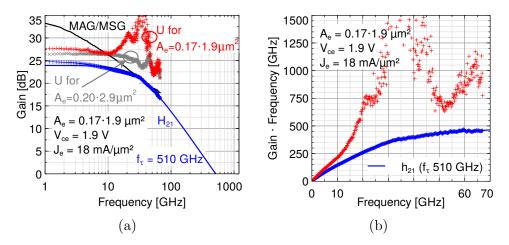

| 4.28 | Microwave gains for an HBT with $170\mathrm{nm}$ x $1.9\mu\mathrm{m}$ emitter junction                                            |     |

|      | area. (a) Double logarithmic plot with unilateral gain of device in                                                               |     |

|      | figure 4.26 drawn for comparison, (b) linear plot of gain-frequency vs                                                            |     |

|      | frequency. Single pole fit yields $f_{\tau}$ 510 GHz                                                                              | 115 |

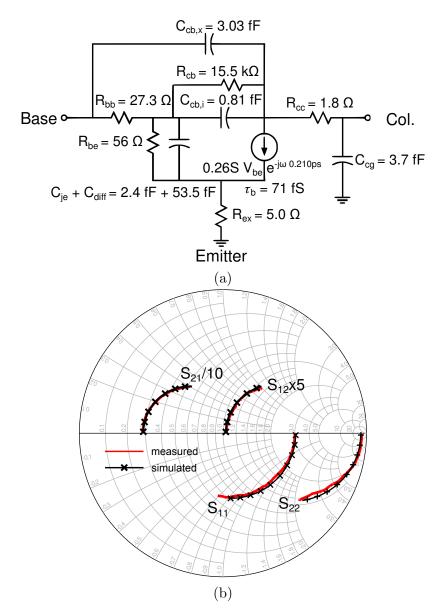

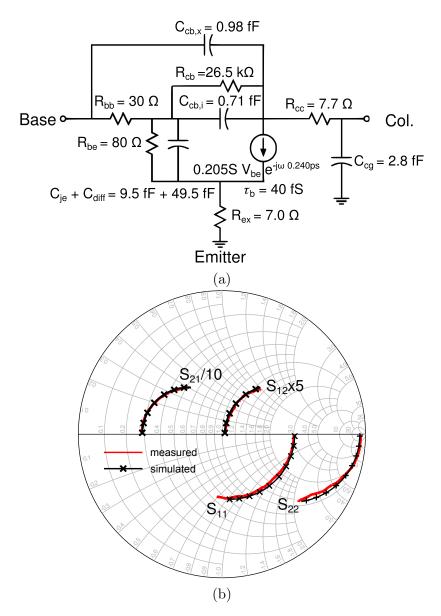

| 4.29 | (a) A hybrid- $\pi$ equivalent circuit for the HBT at peak $f_{\text{max}}$ perfor-     |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | mance. (b) Comparison of (solid line) measured S-parameters of Figure                   |     |

|      | 4.26 and (x) simulated S-parameters from 0.5 to 67 GHz                                  | 116 |

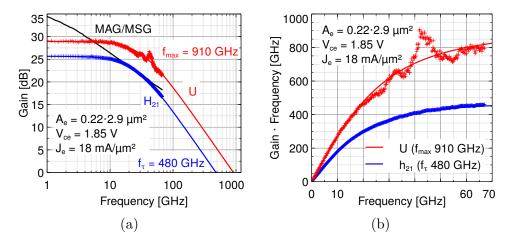

| 4.30 | Microwave gains for an HBT with $220\mathrm{nm}$ x $2.9\mu\mathrm{m}$ emitter junction  |     |

|      | area. (a) Double logarithmic plot, (b) linear plot of gain-frequency vs                 |     |

|      | frequency. Single pole fit yields $f_{\tau}$ 480 GHz, $f_{\text{max}}$ 910 GHz          | 117 |

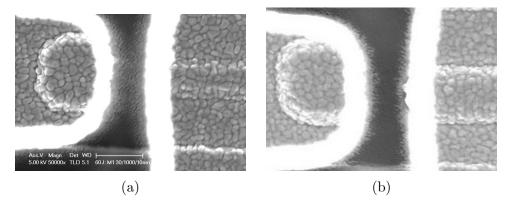

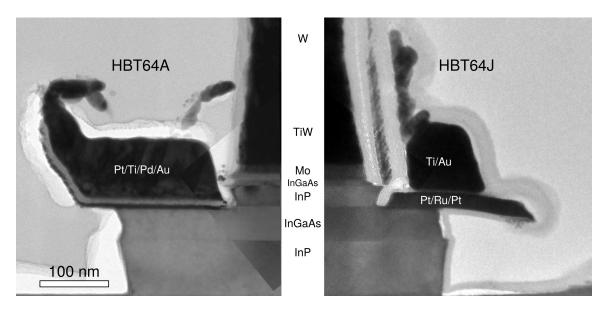

| 4.31 | Composite TEMs of sample with base fabricated using lifted-off base                     |     |

|      | contact technology (left, HBT64A) and dual-deposited base contact                       |     |

|      | technology (right, HBT64J)                                                              | 117 |

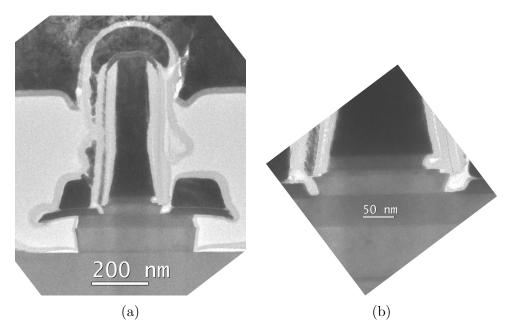

| 4.32 | Cross-sectional TEM of (a) the complete HBT with $200\mathrm{nm}$ x $2.9\mathrm{\mu m}$ |     |

|      | emitter junction area and (b) the emitter-base region of the same device                |     |

|      | on sample 64J                                                                           | 118 |

| 4.33 | Cross-sectional TEM of (a) the complete HBT with $150\mathrm{nm}$ x $2.9\mathrm{\mu m}$ |     |

|      | emitter junction area and (b) higher-magnification cutaway of the                       |     |

|      | emitter-base region marked with red dotted rectangle in (a) on sample                   |     |

|      | 64C                                                                                     | 119 |

# List of Tables

| 2.1 | Approximate HBT scaling laws        | 44  |

|-----|-------------------------------------|-----|

| 4.1 | Epitaxial Structure Design of HBT56 | 88  |

| 4.2 | Epitaxial Structure Design of HBT64 | 108 |

# Chapter 1

# Introduction

The demand for submm-wave radio systems [1,2], high data rate communication systems [3] and high performance signal processing systems [4,5] drives the development of high bandwidth transistors [6]. Despite the cost advantage of highly integrated RF CMOS circuits in the matured Si technology, heterojunction bipolar transistors in Si/SiGe and InGaP/GaAs material systems remain the prime choice for commercial RF designs that require both high linearity, power-added efficiency and breakdown simultaneously while delivering high output power.

Heterojunction bipolar transistors in the InGaAs/InP material system exhibit highest RF bandwidth at a given lithographic feature size: the low effective carrier mass in InGaAs enables fast diffusive transport through the base (InGaAs:  $0.045 m_0$ , GaAs:  $0.067 m_0$ , SiGe:  $0.12 m_0$ ). Electrons are swept through the InP collector in excess of their Fermi velocity. The advantageous band alignment between the InP

Introduction Chapter 1

emitter and InGaAs base allows for high base doping  $>1 \times 10^{20}/\text{cm}^3$  for low base contact resistance while retaining high emitter injection efficiency. The dielectric strength of the InP collector enables high breakdown voltage.

In this work, InP HBTs with triple-mesa structure are discussed: fabrication begins with epitaxial growth of collector, base and emitter semiconductor by a commercial vendor. Tall emitter contacts are deposited and electrically isolated in a  $SiN_x$  sidewall process. The emitter semiconductor mesa is isolated with selective wet etches. Base electrodes are deposited around the emitters in a self-aligned process, minimizing the gap between electrodes and active device region. The base/collector semiconductor mesa is patterned with selective wet etches, and the collector terminal is fabricated by metalizing the subcollector. Finally, posts are deposited, the devices are isolated and planarized in a low- $\varepsilon$  dielectric. Coplanar-like wiring structures are fabricated that enable RF characterization of HBT devices.

The RF performance of mesa HBTs is increased by means of scaling [7]: transit delays are lowered by thinning epitaxial base and collector layers,  $(2\pi f_{\tau})^{-1} \approx \tau_c + \tau_b + RC$ . Concurrently, RC charging delays are reduced by lithographically narrowing emitter and base/collector widths while maintaining constant parasitic resistances  $R_{ex}$ ,  $R_{bb}$ , device current  $I_c$  and transconductance  $g_m$ . Successful scaling requires lithographic resolution for both emitter and base to be less than a quarter of the smallest emitter width, while base-to-emitter alignment must be better than a third of an emitter width in order to simultaneously obtain low base access resistance

Introduction Chapter 1

$R_{bb}$  and base-collector capacitance  $C_{cb}$  for optimum RF performance. Major scaling challenges arise from fabricating ohmic contacts with lowest contact resistitivies to both emitter and base. The emitter and base metalization must also sustain high device current densities  $J_e > 30 \,\mathrm{mA/\mu m^2}$  at elevated junction temperatures  $\sim 400 \,\mathrm{K}$  without degradation by either electromigration or thermal decomposition processes.

Chapter 2 briefly introduces basic design considerations, figures of merit and scaling laws for triple-mesa RF HBTs. With shrinking base contact resistivity, high sheet resistivity of base electrodes  $R_{sh,\mathrm{base}}$  causes voltage drops along the length of the emitter, degrading  $f_{\text{max}}$  bandwidth with increasing emitter length  $L_e$ : a simple calculation is presented that estimates this effect as a function of  $R_{sh,\mathrm{base}}$  and  $L_e$ . A simple finite-element circuit is introduced that has been used to verify this effect as well as to quantify the deterioration of RF bandwidths due to various fabrication issues. In chapter 3, the fabrication process and improvements that have enhanced device performance and yield are discussed. The process for forming base electrodes and base/collector mesas has been transitioned from i-line projection to electron beam lithography, yielding better than 30 nm base-to-emitter alignment at 10 nm resolution. In an effort to improve base contact resistivity, a dual-deposition base metalization process is presented that has lithographic processes removed from the formation of base contacts in order to retain pristine semiconductor surfaces. The metal composition of the base electrodes has been modified to simultaneously yield thermally stable low resistivity contacts while reducing the sheet resistivity of the Introduction Chapter 1

base electrodes for increased  $f_{\text{max}}$  bandwidth. As part of the dual-deposition process, base/emitter semiconductor surfaces are passivated with Al<sub>2</sub>O<sub>3</sub> for increased current gain and reduced base access resistance. In identifying further limitations to the fabrication process of highly-scaled devices, additional key improvements have been made to increase device performance, among which are scaled base posts, reduced emitter end undercut and base/collector passivation with SiN<sub>x</sub>. A process for fabricating scaled TLM structures is introduced as means to quickly evaluate the effects of thermal anneals, process contaminants and modifications to base metal composition on base contact resistivity. Unlike non-scaled TLM structures, the scaled TLM fabrication resembles HBTs in both fabrication processes and dimensions. Chapter 4 discusses results of HBT fabrication campaigns and scaled TLMs. Simultaneous  $f_{\tau}$  and  $f_{\rm max}$  of 0.48 THz and 1.07 THz have been achieved on a sample that has been fabricated with discussed process improvements: smaller footprint devices with higher RF bandwidth  $f_{\tau}$  0.51 THz have been fabricated, but inadequacies in the calibration methods and structures prevent accurate extraction of  $f_{\text{max}}$  bandwidth.

## References

- [1] J. Hacker, M. Urteaga, M. Seo, A. Skalare, and R. Lin, "InP HBT amplifier MMICs operating to 0.67 THz," in *Microwave Symposium Digest (IMS)*, 2013 *IEEE MTT-S International*, pp. 1–3, IEEE, 2013.

- [2] M. Seo, M. Urteaga, J. Hacker, A. Young, A. Skalare, R. Lin, and M. Rodwell, "A 600 GHz InP HBT amplifier using cross-coupled feedback stabilization and dual-differential power combining," in *Microwave Symposium Digest (IMS)*, 2013 *IEEE MTT-S International*, pp. 1–3, June 2013.

- [3] E. Bloch, H.-c. Park, Z. Griffith, M. Urteaga, D. Ritter, and M. J. Rodwell, "A 107 GHz 55 dB-Ohm InP broadband transimpedance amplifier ic for high-speed optical communication links," in *Compound Semiconductor Integrated Circuit Symposium (CSICS)*, 2013 IEEE, pp. 1–4, IEEE, 2013.

- [4] B. Oyama, D. Ching, K. Thai, A. Gutierrez-Aitken, and V. Patel, "InP HBT/Si CMOS-based 13-b 1.33-Gsps digital-to-analog converter with >70-dB SFDR," Solid-State Circuits, IEEE Journal of, vol. 48, pp. 2265–2272, Oct 2013.

- [5] Z. Xu, J. McArdle-Moore, T. Oh, S. Kim, S. Chen, Y. Royter, M. Lau, I. Valles, D. Hitko, and J. Li, "A 0.8/2.4 GHz tunable active band pass filter in InP/Si BiC-MOS technology," *Microwave and Wireless Components Letters*, *IEEE*, vol. 24, pp. 47–49, Jan 2014.

- [6] M. Urteaga, M. Seo, J. Hacker, Z. Griffith, A. Young, R. Pierson, P. Rowell, A. Skalare, V. Jain, E. Lobisser, and M. Rodwell, "InP HBTs for THz frequency integrated circuits," in *Compound Semiconductor Week (CSW/IPRM)*, 2011 and 23rd International Conference on Indium Phosphide and Related Materials, pp. 1– 4, May 2011.

- [7] M. J. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. Smith, et al., "Submicron scaling of HBTs," Electron Devices, IEEE Transactions on, vol. 48, no. 11, pp. 2606–2624, 2001.

# Chapter 2

# InP Bipolar Transistor Design

In this chapter, the principle of operation of triple-mesa RF HBTs, essential device parameters and trade-offs between different design goals are presented.

# 2.1 Principle of Operation

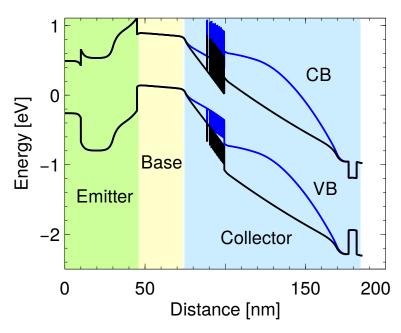

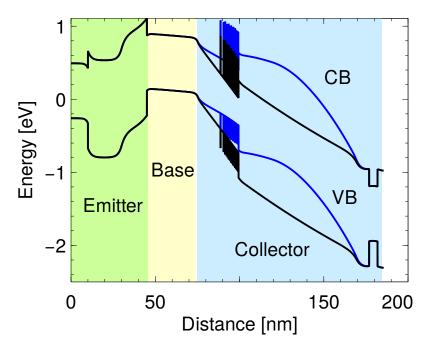

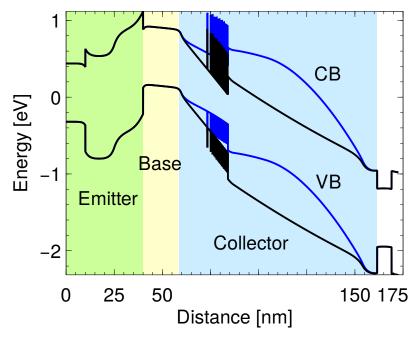

An npn heterobipolar transistor structure is fabricated by epitaxially growing a wide bandgap n- collector, a narrow bandgap p+++ base and a wide bandgap n+ emitter in sequence. Ohmic contacts to emitter, base, and collector are formed. A band diagram of such structure under bias is shown in figure 2.1.

In forward-active operation mode, the base-collector diode is reverse-biased while the base-emitter diode is forward-biased. Electrons are swept vertically from the emitter into the base which is thinner than their diffusion length. Most electrons diffuse through the base with only a small fraction recombining with holes. The

Figure 2.1: Band diagram of heterobipolar transistor under bias with valence band (VB) and conduction band (CB), showing bands with no (black) and Kirk (blue) current density in the collector.

electrons are then swept across the collector by the electric field of the reverse-biased junction. The electron concentration at the metallurgical base-emitter interface and subsequently the collector current can be modified by changing the (input) potential across the base-emitter diode: the collector current is approximately independent to changes of the base-collector potential (output), achieving transistor behavior.

Holes are confined to the base by the heterointerfaces: potential barriers in the valence band and differences in effective mass restrict holes from flowing to either emitter or collector, thereby suppressing parasitic hole currents.

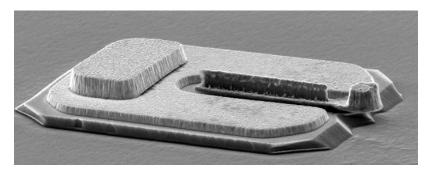

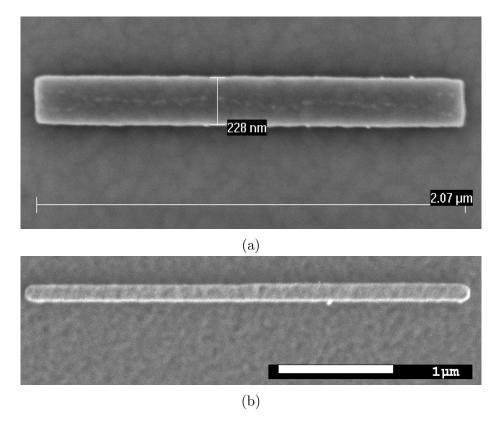

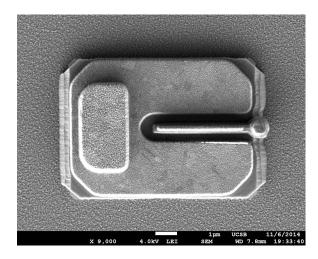

Figure 2.2: Angled scanning electron micrograph (SEM) of a fabricated heterojunction bipolar transistor prior to BCB planarization.

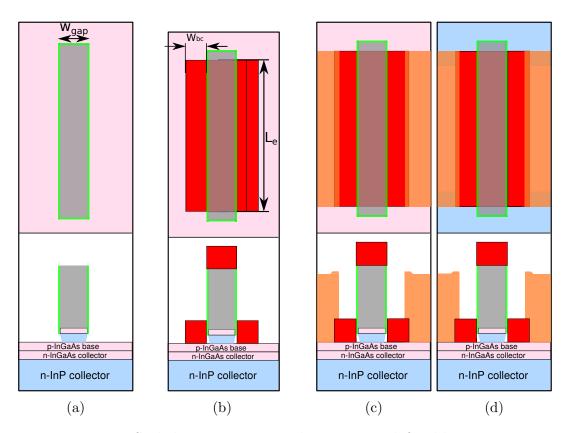

## 2.2 Device Topology

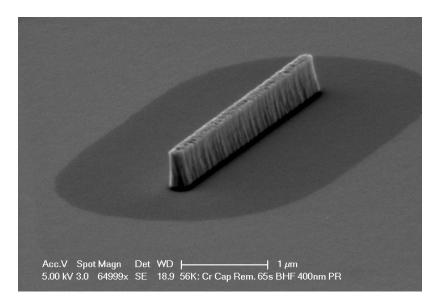

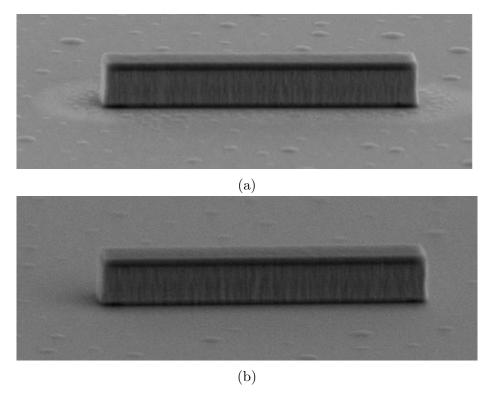

At UCSB, triple-mesa HBTs in the InP/InGaAs material system are researched. Emitter contacts are formed on a highly doped, low bandgap emitter cap InGaAs layer. The emitter is isolated, and base electrodes are deposited around the emitter in a self-aligned process: close spacing of base electrodes to active regions of the device  $\approx 15\,\mathrm{nm}$  reduces gap resistance terms, thereby minimizing critical base access resistance. Base/collector mesas are formed in selective wet etches. The collector is contacted with a highly doped, thick and thus conductive subcollector. Although the subcollector has similar gap resistance terms associated to it, the conductivity of this layer is high enough to be mostly irrelevant for RF performance. A large area, non-self-aligned horseshoe-shaped contact to the subcollector is therefore formed. Devices are isolated in the third mesa etch. Figure 2.2 shows a scanning electron micrograph of a fabricated triple mesa HBT prior to planarization in a low- $\varepsilon$  dielectric benzocyclobutene (BCB).

While current flowing across emitter contacts is swept vertically into the device,

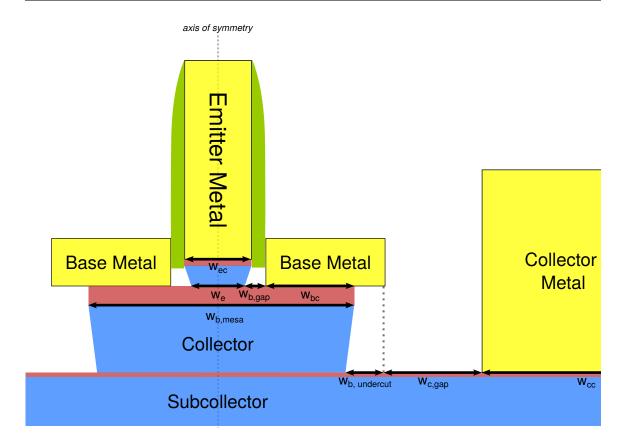

Figure 2.3: Cross-sectional schematic of a triple-mesa HBT with metal (yellow), low bandgap semiconductor (red) and wide bandgap semiconductor (blue). Key dimensions labeled.

current through planar base and subcollector contacts changes direction from vertical flow at the metal-semiconductor interface to horizontal flow into the device, imposing limitations on minimum access resistance that can be attained by enlarging metal contacts [1]. Key device dimensions are illustrated in figure 2.3: the emitter contact width  $w_{ec}$ , the emitter junction width  $w_e$ , the overlap of the base metal with the base semiconductor  $w_{bc}$ , the gap between base metal and active device  $w_{b,gap}$ , the total width of the base/collector mesa  $w_{b,mesa}$ , and the single-sided undercut of the base

mesa  $w_{b,\text{undercut}}$ , the gap between base-collector mesa and collector contact  $w_{b,\text{undercut}} + w_{c,\text{gap}}$ , and the extent of the collector metal  $w_{cc}$ .

## 2.2.1 Emitter Design

Crucial for high  $f_{\tau}$  bandwidth is low emitter access resistivity. The emitter is therefore capped with a highly doped layer of low bandgap material to enable low resistivity ohmic contacts [2]. The InP emitter layers below contain a thin n+ region which clamps the extent of the space charge region, followed the n- space charge region itself.

Among processing considerations, the extent of the depletion zone  $t_e$  should be chosen to find the optimum between low emitter-base junction capacitance  $C_{je} \lesssim 1/t_e$  as well as low space charge zone resistance that adds to emitter access resistance:

$$\rho_{sc} = \frac{1}{q} \int_{t_e} \frac{1}{\mu_n(z) \, n(z)} \, dz \tag{2.1}$$

with the elementary charge q, the electron mobility  $\mu_n$  and local charge density n(z).

The doping of the space charge region  $n_{de}$  should be high enough to support operation at and above Kirk current density  $J_{e,Kirk} \approx 2J_{c,Kirk}$  at which optimum transport is achieved in the collector. If the doping of the depletion zone has been chosen too low, injected carriers can screen the electric field in the space charge region so the injection point for the emitter-to-base electron current is moved away from the heterointerface: for any additional change in  $\partial V_{be}$ , the change in base current  $\partial I_b$

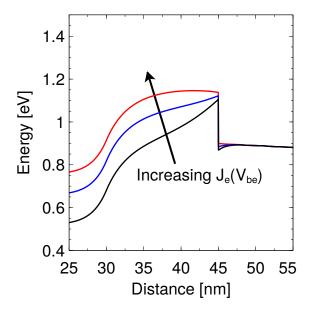

Figure 2.4: Conduction band profile at the abrupt emitter base junction for increasing  $J_e(V_{be})$ . As  $J_e$  is increased, a barrier for the electrons is formed in emitter that does not coincide with the metallurgical heterointerface anymore.

and subsequently collector current  $\partial I_c$  is no longer determined by energy difference  $E_F - E_c$  at the heterointerface, but by maximum height of the barrier (see Figure 2.4). Transconductance  $g_m = \partial I_c/\partial V_{be}$  and subsequently RF bandwidth is compromised in this operating regime.

At high current densities, Boltzmann carrier statistics remain no longer valid: degenerate Fermi-Dirac carrier statistics must be used to calculate current transport. Assuming specular conduction across the heterointerface (no reflection, unidirectional flow), it can be shown that the current density is [3]

$$J_{e,\text{Fermi-Dirac}} = \frac{q \, m^*}{2\pi^2 \hbar^3} (k_B T)^2 \int_0^\infty \frac{x}{1 + \exp(x - \eta_f)} \, dx, \tag{2.2}$$

with the effective electron mass  $m^*$ , the reduced Planck constant  $\hbar = h/2\pi$ , the Boltzmann constant  $k_B$ , the junction temperature T, and normalized Fermi energy  $\eta_f = E_f/k_BT$ .

In the regime where Boltzmann statistics are valid, the emitter current density is

$$J_{e,\text{Boltzmann}} = \frac{q \, m^*}{2\pi^2 \hbar^3} (k_B T)^2 \exp(\eta_f) \tag{2.3}$$

.

A closed-form approximation for the transconductance normalized to emitter area as a function of relative Fermi level can be found [4]:

$$g_m = \frac{\partial I_c/A_e}{\partial V_{be}} \approx \frac{\partial J_e}{\partial V_{be}} = \frac{q \, m^*}{2\pi^2 \hbar^3} (k_B T) \ln \left[ 1 + \exp\left(\frac{E_f - E_c}{k_B T}\right) \right]$$

(2.4)

with the collector current  $I_c$ .

Figure 2.5 shows a plot of the transconductance as a function of emitter current density calculated from Boltzmann and Fermi-Dirac statistics at different junction temperatures. Transconductance can be improved at a given current density by using a material with higher effective density of states / higher effective mass  $m^*$ .

The transconductance of abrupt heterointerfaces is deteriorated by tunneling: a significant portion of electrons in the space charge region can tunnel through the triangular potential barrier and contribute to a parastic collector current. This is reflected by high collector ideality  $\eta_c > 1$  in Gummel characteristics and reduced

Figure 2.5: Transconductance calculated with Boltzmann (B) and Fermi-Dirac (FD) statistics at temperatures  $T=300\,\mathrm{K}$  and  $400\,\mathrm{K}$ .

charging time  $(C_{je} + C_{cb})/g_m$ .

Quantum reflection of carriers at the heterojunction, barrier modulation effects and quasi-Fermi level drops diminish transconductance further at high current densities [5].

Elevated operating temperatures and high current densities necessitate thermally stable metal contacts that are impervious to electromigration. In the UCSB fabrication technology, an emitter metalization process for a composite refractory Mo/W/TiW metal stack has been established that is stable to current densities up to  $60\,\mathrm{mA/\mu m^2}$  and can deliver a total access resistance to the emitter of less than  $3\,\Omega\,\mu\mathrm{m^2}$ .

## 2.2.2 Base Design

The power gain cutoff frequency  $f_{max}$  is very sensitive to the resistivity of the ohmic contact between base electrode and semiconductor. Previous experiments on test samples have indicated that high base doping  $n_a$  is crucial for producing a low ohmic contact [6,7]. High doping, however, decreases current gain  $\beta = \tau_n/\tau_b$  (electron/hole carrier lifetime  $\tau_n/\tau_b$ ) mainly due to Auger recombination  $\tau_n \propto n_{a,\text{effective}}^{-2}$ . Simultaneous reduction of base thickness  $t_b$  is therefore required to maintain current gain when base doping is increased.

The base transit time and, by extension, current gain bandwidth  $f_{\tau}$  can be enhanced by a quasi-electric field: the slope of the semiconductor energy bands is adjusted to improve electron transport by either grading the doping concentration or by varying the composition of the base semiconductor alloy throughout the base. While compositional grading decouples the quasi-electric field from the doping concentration, it introduces additional challenge of lattice-matching base semiconductor layers and has been therefore not used in this work.

The enhanced base transit time can be written as [8]

$$\tau_b = \frac{t_b^2}{D_n} \frac{k_B T}{\Delta E_C} \left[ 1 - \frac{k_B T}{\Delta E_C} (1 - \exp(-\frac{\Delta E_C}{kT})) \right] + \frac{t_b}{v_{\text{exit}}} \frac{k_B T}{\Delta E_C} (1 - \exp(\frac{\Delta E_C}{kT})), \quad (2.5)$$

with the conduction band slope  $\Delta E_C$ , electron diffusivity  $D_n$  and exit velocity of minority carriers into the collector  $v_{\text{exit}}$ .

High doping concentrations in the base cause contraction of the bandgap [9] and subsequently modifications to the the conduction band slope. For accurate prediction of the base transit time, it must be therefore taken into account. High doping concentration also changes the lattice constant slightly: the In:Ga ratio is therefore adjusted during growth to ensure lattice match to InP.

In addition to improving base transit time, the quasi-electric field also drives electrons away from the base surface, thereby reducing base-emitter surface leakage and increasing current gain.

### 2.2.3 Collector Design

Low collector transit time is essential for attaining high  $f_{\tau}$ : careful considerations must be therefore taken for designing the collector.

In epitaxial design of wafers presented in this work, the collector is comprised of a setback region, a superlattice grade, a pulse doping and a drift collector region. The superlattice chirped between InGaAs and InAlAs provides a smooth grading to the bands from the InGaAs base to the InP drift collector. The setback layer provides carriers with sufficient energy to traverse the grade. The pulse doping layer forms a dipole to restore fields across the graded region.

Optimum transport is attained at Kirk threshold current density: the charges comprising the collector current screen out the collector doping such that the electric field at the base side of the collector is zero. This current can be written as

$$J_{c,\text{Kirk}} = \frac{2\varepsilon\varepsilon_0 v_{\text{eff}}}{t_c^2} (\varphi_{bi} + V_{cb}) + q n_c v_{\text{eff}}, \qquad (2.6)$$

with the effective carrier velocity in the collector  $v_{\rm eff}$ , the collector thickness  $t_c$ , the built-in potential  $\varphi_{bi}$  and the collector doping concentration  $n_c$ .

The collector should be fully depleted when no base-collector voltage is applied,  $V_{cb} = 0$ : this limits the maximum doping concentration to

$$n_{c,\text{max}} = \frac{2\varepsilon\varepsilon_0\varphi_{bi}}{q\,t_c^2} \tag{2.7}$$

. For  $n_c = n_{c,\text{max}}$ , equation 2.6 can be rewritten as

$$J_{c,\text{Kirk}} = \frac{4\varepsilon\varepsilon_0 v_{\text{eff}}}{t_c^2} (\varphi_{bi} + V_{cb})$$

(2.8)

Further limitation on the maximum doping concentration and subsequently the Kirk current density arises from the pulse doping layer [10].

In the Kirk regime, electrons sweep through the the first part of the collector in near flatband conditions without scattering. The effective carrier velocity as defined by the charge control model

$$\tau_c \equiv \frac{t_c}{2 \, v_{eff}} \tag{2.9}$$

can exceed  $3 \times 10^7 \,\mathrm{cm/s}$  in  $100 \,\mathrm{nm}$  thick InGaAs/InP collectors.

However, transport is severely degraded if only a small portion of electrons accumulates enough energy to scatter from low effective mass  $\Gamma$  into high effective mass L valleys ( $\approx 0.6\,\mathrm{eV}$   $\Gamma$ -L separation for InP) [11].

The subcollector has a thin layer of n++ InGaAs to yield low resistivity ohmic contacts to the collector electrodes. A certain thickness of this layer is desirable to reduce sensitivity to contaminants that have accumulated on the sample surface from prior processing and overetching of the base/collector mesa. However, the heat conductivity of InGaAs is an order of magnitude worse than InP: a layer too thick would therefore thermally isolate the ambient substrate from the collector in which most of the heat is generated during device operation, causing degradation of carrier transport and early device failure.

## 2.3 TLM Structures

Transfer length method (TLM) structures enable the extraction of the contact resistivity between metal electrodes and semiconductor [1]. A set of metal pads with varying spacing {  $w_{\text{gap},1}$ ,  $w_{\text{gap},2}$ , ... } is deposited onto the semiconductor surface. After fabrication, the resistance between each pair of adjacent pads  $R(w_{\text{gap}})$  is measured using four-terminal sensing at current densities which HBTs are operated at. From the set of measured resistances, the contact resistivity of the metal-semiconductor interface and the sheet resistance of the semiconductor in the gap can be extracted.

The resistance R of metal-semiconductor-metal structures as a function of gap spacing  $w_{\rm gap}$  is:

$$R(w_{\rm gap}) = 2R_c + R_{sh} \frac{w_{\rm gap}}{L_{\rm pad}},\tag{2.10}$$

with the contact resistance  $R_c$ , the dimension of the pad  $L_{\text{pad}}$  transversal to the current flow and the sheet resistance of the semiconductor between the pads  $R_{sh}$ .

A 2D model has been developed that describes the potential distribution underneath the metal contacts and subsequently the total contact resistance  $R_c$  [12]. The similarity of the partial differential equations to those of transmission lines gave rise to the term  $transmission\ line\ model$ , also abbreviated as TLM. The contact resistance can be written as

$$R_c = \frac{\sqrt{R_{sh} \rho_c}}{2 L_{pad}} \coth\left(\frac{w_{pad}}{L_t}\right)$$

(2.11)

with the sheet resistance of the semiconductor underneath the contact  $R_{sh}$ , the specific contact resistance  $\rho_c$ , the dimension of the pad transverse to the gap  $L_{pad}$  and the contact width  $w_{pad}$ . Within a transfer length

$$L_t = \sqrt{\rho_c/R_{sh}},\tag{2.12}$$

the voltage has dropped to  $1/e \ (\approx 36.7\%)$ , and most of the current is passed through this section.

Three special cases are of interest:

•  $w_{\text{pad}} > 3 L_t$ . The contact width is much larger than the transfer length. Equation 2.11 reduces to  $(\lim_{x\to+\infty} \coth(x) = 1)$

$$R_c = \frac{\sqrt{R_{sh}\,\rho_c}}{L_{\text{pad}}} = \frac{\rho_c}{L_t\,L_{\text{pad}}} \tag{2.13}$$

The contact resistance is independent of contact pad width  $w_{\text{gap}}$ : a increase of contact pad width  $w_{\text{gap}}$  will therefore not reduce the contact resistance.

•  $w_{bc} \ll L_t$ . The contact width is much smaller than the transfer length. The contact resistance becomes area-limited, similar to metal-semiconductor contacts with current flow perpendicular to the interface. Equation 2.11 reduces to  $(\coth(x) \approx 1/x)$  for |x| < 0.5

$$R_c = \frac{\rho_c}{L_{\text{pad}} w_{\text{pad}}} \tag{2.14}$$

•  $w_{bc} \approx L_t$ . The contact resistance can be approximated with the first two terms of the Laurent series:  $\coth(x) \approx 1/x + x/3$  for  $|x| \approx 1$ . The values of two equivalent resistors  $R_{c1} + R_{c2} = R_c$  are thus

$$R_{c1} = \frac{\rho_c}{L_{\text{pad}} w_{\text{pad}}}, \quad R_{c2} = \frac{R_{sh} w_{\text{pad}}}{3 L_{\text{pad}}}$$

(2.15)

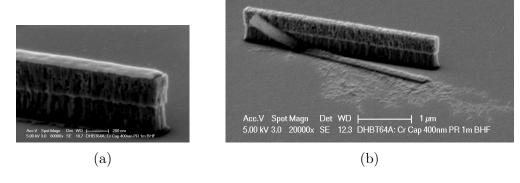

In the HBT process, two types of TLM structures are fabricated alongside transistors to monitor base contact resistivity: non-pinched (Figure 2.6) and pinched

Figure 2.6: Non-pinched TLM structure with exposed base semiconductor surface.

Figure 2.7: Pinched TLM structure with gaps defined by emitter metal.

(Figure 2.7). Non-pinched TLM structures have gaps defined in resist with the semiconductor surface in the gap exposed: the surface is therefore depleted and can suffer from process damage (e.g. oxidation in thermal processes) that can create surface states. The sheet resistance  $R_{sh,non-pinched}$  extracted from measurements of nonpinched TLM structures is therefore higher than the sheet resistance underneath the metal pads:

$$R_{\text{non-pinched}}(w_{\text{gap}}) = 2R_c + R_{sh,\text{non-pinched}} \frac{w_{\text{gap}}}{L_{\text{pad}}},$$

(2.16)

The gap of pinched TLMs is defined by emitter stripes with the TLM pads de-

posited around the emitter gap in a self-aligned process: the base semiconductor remains encapsulated and has a sheet resistance  $R_{sh, \rm pinched}$  similar to the sheet resistance underneath the metal contacts. The measured resistance is

$$R_{\text{pinched}}(w_{\text{gap}}) = 2(R_c + R_{b,\text{undercut}}) + R_{sh,\text{pinched}} \frac{w_{\text{gap}}}{L_{\text{pad}}}.$$

(2.17)

The additional resistance  $R_{b,\text{undercut}} = R_{sh,\text{non-pinched}} w_{\text{undercut}} / L_{\text{pad}}$  arises due to the gap between TLM electrodes and emitter semiconductor that results from the emitter semiconductor undercut and sidewall thickness.

With the contact width  $w_{\text{gap}}$  much larger than the transfer length, the contact resistance becomes (cf. equation 2.13)

$$R_c = \frac{\rho_c}{L_t L_{\text{pad}}} = \frac{\sqrt{R_{sh,\text{pinched}} \rho_{c,base}}}{L_{\text{pad}}}$$

(2.18)

The contact resistivity  $\rho_c$  can be therefore extracted with slope of equation 2.17 and the intersect of equation 2.16:

$$\rho_c = \frac{R_c^2 L_{\text{pad}}^2}{R_{sh,\text{pinched}}} \tag{2.19}$$

The measurements assume uniform contact resistivity across the area onto which the TLM pads are deposited. Further errors arise from uncertainty in the determination of gap spacing by SEM, non-uniform pad edges as a result of a lift-off process and parasitic currents at pad corners that have been inadvertently rounded in lithographic processes.

## 2.4 Equivalent Circuit Model

An equivalent hybrid- $\pi$  model of a bipolar transistor is shown in figure 2.8. This model is a first order approximation of the equivalent Tee circuit and has been simplified by lumping RC networks corresponding to distributed capacitances and resistances spread across the device, but it accurately represents the physical device in the small signal regime and can be used to quantify essential device parameters. At its core, a voltage controlled current source models the current gain of the transistor. The remaining parameters account for various physical effects and will be described in detail.

#### 2.4.1 Emitter Access Resistance $R_{ex}$

The emitter access resistance represents the resistance that an electron encounters while traversing from the top of the emitter metalization up to the metallurgical emitter-base junction. It includes the emitter metal resistance

$$R_{em,\text{metal}} \approx \rho_{s,em,\text{metal}} \cdot \frac{T_{em,\text{metal}}}{A_{ec}},$$

(2.20)

Figure 2.8: Hybrid- $\pi$  model of a bipolar transistor.

with the specific resistivity of the emitter metal  $\rho_{s,em,metal}$ , the emitter contact area  $A_{ec} = L_e w_{ec}$ , the emitter length  $L_e$ , and the emitter metal thickness  $T_{em,metal}$ . An additional constituent is the emitter contact resistance

$$R_{con,em} = \frac{\rho_{em}}{A_{ec}} \tag{2.21}$$

with  $\rho_{em}$  the specific contact resistance between emitter metalization and semiconductor. The resistance of emitter space charge region of thickness  $t_{dep}$  adds a term [13]

$$R_{sc,em} = \frac{1}{q} \cdot \frac{\partial \Delta E_{fn}}{\partial I_e},\tag{2.22}$$

with the emitter current  $I_e$  and the drop of the electron quasi-Fermi level

$$\Delta E_{fn} = \int_{t_{dep}} \frac{J_e}{\mu_n(z) n(z)} dz, \qquad (2.23)$$

with the emitter current density  $J_e = I_e/A_e$ , the emitter area  $A_e = L_e w_e$ . The total emitter access resistance is the sum

$$R_{ex} = R_{em,\text{metal}} + R_{con,em} + R_{sc,em}. \tag{2.24}$$

Normalizing the emitter access resistance to the device area gives a device-independent figure that allows quantitative comparison of emitter access technologies:

$$\rho_{ex.xs} = R_{ex} \cdot A_{ec} \tag{2.25}$$

A typical value for the upper limit of the sheet resistance of the composite emitter metal stack in the UCSB process is  $0.8\,\Omega/\Box$ . For a transistor with  $T_{em,\text{metal}} = 500\,\text{nm}$ , the contribution from the normalized finite resistance of the emitter metal ranges below  $0.3\,\Omega\,\mu\text{m}^2$ . For a well designed emitter, the normalized resistance of the emitter space charge region is below  $0.1\,\Omega\,\mu\text{m}^2$  [13]. The bulk of the emitter access resistance can therefore be attributed to the contact resistance which is  $\approx 4\,\Omega\,\mu\text{m}^2$  or less for the transistors discussed in this work.

Figure 2.9: Equivalent circuit overlaid to a cross-sectional illustration of the active transistor across the emitter.

#### 2.4.2 Base Access Resistance $R_{bb}$

Current from the base metal that surrounds both sides of the emitter enters the semiconductor vertically and then traverses horizontally to the active part of the device, encountering the sheet resistance of the metal, the specific contact resistance between metal and semiconductor and the sheet resistance of the semiconductor. The base access resistance consists thus out of multiple contributions (see Figure 2.9):

Figure 2.10: Equivalent circuit overlaid to a cross-sectional illustration of the device along the emitter.

Base Contact Resistance. The base contact resistance can be expressed as

$$R_{b,\text{contact}} = \frac{R_{sh,\text{base}} \rho_{b,\text{contact}}}{2L_e} \coth\left(\frac{w_{bc}}{L_t}\right), \qquad (2.26)$$

with the single-sided overlap of base electrode and semiconductor  $w_{bc}$ , the contact resistivity  $\rho_{b,\text{contact}}$ , the sheet resistance underneath the contact  $R_{sh,\text{base}}$ , the transfer length  $L_t$  and emitter length  $L_e$ .

For the devices presented in this work, a typical value for the sheet resistance of the base semiconductor layer is  $750 \,\Omega/\Box$ , while the contact resistance is  $4 \,\Omega \,\mu\text{m}^2$ . The transfer length is hence 70 nm.

Base Gap Resistance. The gap resistance reflects the sheet resistance of the exposed semiconductor between base metalization and the active device area underneath the emitter:

$$R_{b,\text{gap}} = R_{sh,\text{gap}} \frac{w_{b,\text{gap}}}{2L_e}, \tag{2.27}$$

with the sheet resistance of the exposed base semiconductor  $R_{sh,\text{gap}} \approx R_{sh,\text{unpinched}}$  (equation 2.16).

Intrinsic Base Resistance. The resistance of the base semiconductor underneath the emitter can be expressed as [14]

$$R_{b,\text{intr}} = R_{sh} \frac{w_e}{12 L_e}.$$

(2.28)

Base Metal Resistance. The resistance of the base metal contributes as

$$R_{b,\text{met}} = R_{sh,\text{bmet}} \frac{w_{bc}}{6L_e},\tag{2.29}$$

with the sheet resistance of base metal  $R_{sh,\text{bmet}}$ .

The total base access resistance includes all contributions:

$$R_{bb} = R_{b,\text{contact}} + R_{b,\text{gap}} + R_{b,\text{intr}} + R_{b,\text{met}}$$

(2.30)

The sheet resistance of the base semiconductor can be obtained from TLM measurements (section 2.3) and verified numerically:

$$R_{sh} = \left( q \int_{0}^{t_{\text{base}}} \mu_{p}(p) \, p(x) dx \right)^{-1} \tag{2.31}$$

Fitting parameters for the doping dependent hole mobility  $\mu_p(p)$  of p-InGaAs with carbon doping concentration  $n_a$  have been obtained from hall measurements of previous growths:

$$\mu_p(p) = 5448 \frac{\text{cm}^2}{\text{V s}} - 107.3 \frac{\text{cm}^2}{\text{V s}} \cdot \ln \left( n_a \cdot \text{cm}^3 \right)$$

(2.32)

The depletion depth of the exposed p-InGaAs base semiconductor can be calculated under the assumption that the Fermi level is pinned  $\Delta E_c \approx 0.2\,\mathrm{eV}$  below the

Figure 2.11: Depletion depth of p-InGaAs as a function of doping concentration assuming Fermi level pinning 0.2 eV below the conduction band.

conduction band edge [15]. The depletion potential is

$$\varphi_{\text{dep}} = \frac{1}{q} \left[ \left( E_v - E_F \right) + E_g - \Delta E_c \right], \qquad (2.33)$$

with Fermi level offset to the valence band  $E_v - E_F$ , and the semiconductor band gap  $E_g$ .

Assuming Schottky boundary conditions, the depletion depth is

$$t_{\rm dep} = \sqrt{\frac{2\,\varepsilon_0\varepsilon_{\rm InGaAs}\,\varphi_{\rm dep}}{p}},$$

(2.34)