## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

An Energy-Efficient Triple-Channel UWB-based Cognitive Radio

#### Permalink

https://escholarship.org/uc/item/7tp81586

#### Author Kim, Nam-Seog

# **Publication Date** 2014

Peer reviewed|Thesis/dissertation

### An Energy-Efficient Triple-Channel UWB-based Cognitive Radio

By

Nam-Seog Kim

A dissertation submitted in partial satisfaction of the Requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

#### UNIVERSITY of CALIFORNIA, BERKELEY

Committee in charge: Professor Jan Rabaey, Chair Professor Ali M. Niknejad Professor Paul K. Wright

Spring 2014

## An Energy-Efficient Triple-Channel UWB-based Cognitive Radio

Copyright 2014 by Nam-Seog Kim

#### An Energy-Efficient Triple-Channel UWB-based Cognitive Radio

by

#### Nam-Seog Kim

Doctor of Philosophy in Electrical Engineering and Computer Science University of California, Berkeley Professor Jan M. Rabaey, Chair

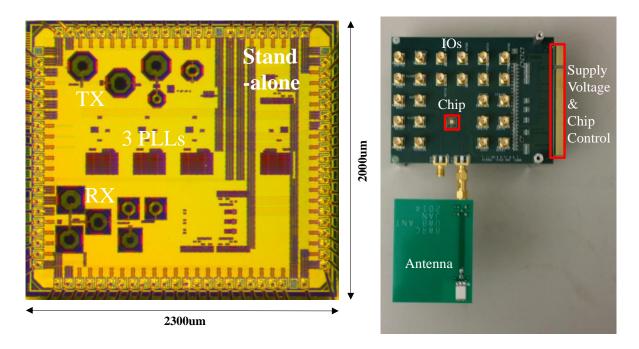

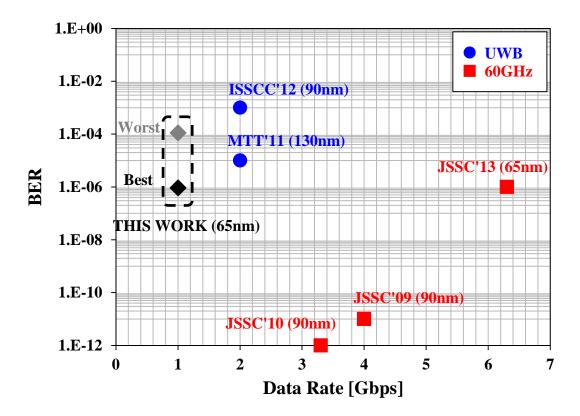

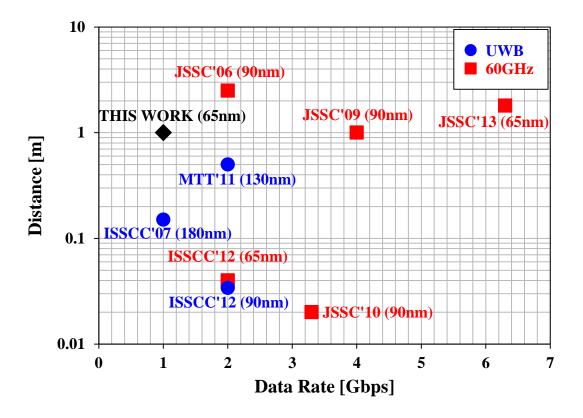

The proposed triple-channel UWB-based cognitive radio exploits spectral crowding and coexistence of other wireless devices as the number of sensors and wearable computing devices increases in 3.1GHz to 10.6GHz ISM band to achieve energy efficient 1Gb/s shortrange wireless communication. A dual-resolution analog wavelet-based spectrum performs bandwidth-and frequency-agile band pass filter (BPF) to detect narrowband and wideband interferers with low power consumption. A charge-pump-based triangular waveform generators and a source follower type low pass filter (LPF) generates basis function for the spectrum sensing with 132MHz sensing resolution. A Low power integer-N QPLL with reduced reference spur by digital calibration on mismatch of the charge pump current supports the tuning frequencies with a linear tuned wide range two stage ring-VCO and a low power programmable true-single-phase-clock (TSPC) divider. The proposed Triplechannel UWB-based cognitive radio was fabricated in 1V 65nm CMOS GP process. The test chip size is  $2.3 \times 2 \text{ mm}^2$ , and the active area is  $2.1 \text{ mm}^2$ . The data rate by using triangular shaped BPSK data is 1Gb/s at 1m communication. The lowest FoM of the energy/bit is 61pJ/bit, and the highest FoM is 102pJ/bit. It achieves BER from  $9.2 \times 10^{-7}$  to  $1.1 \times 10^{-4}$ according to frequency allocation of the triple-channels. The triple-channel UWB-based cognitive radio can provide energy efficient high-data rate wireless communication even with over 20% channel occupation.

Dedicated to my Family...

## Contents

## List of Figures v

| List of Tables ix                                                          |

|----------------------------------------------------------------------------|

| <b>1 Introduction</b> 1                                                    |

| 1.1 High-Data-Rate and Short-Range-Radio 1                                 |

| 1.2 Comparison between UWB Radio and 60GHz Radio                           |

| 1.3 Interferers in UWB band 6                                              |

| 1.4 UWB-based Cognitive Radios 8                                           |

| 1.5 Dissertation Outline                                                   |

| <b>2 Multi-Channel High-Data-Rate UWB-based Cognitive Radio</b> 11         |

| 2.1 Modulation Schemes of the UWB Radio 11                                 |

| 2.2 Pulse Shaping of the UWB Radio 11                                      |

| 2.3 Single-Channel UWB-based Cognitive Radio 13                            |

| 2.4 Multi-Channel UWB-based Cognitive Radio                                |

| 2.5 Adaptive BW Multi-Channel UWB-based Cognitive Radio 20                 |

| 2.6 Link Budget for Triple Channel UWB-based Cognitive Radio 22            |

| 2.7 Group Delay of Multi-Channel UWB-based Cognitive Radio 26              |

| <b>3 Dual-Resolution Analog Wavelet-based Wideband Spectrum Sensing</b> 27 |

| 3.1 Spectrum Sensing in UWB band 27                                        |

| 3.2 Wideband Spectrum Sensing 28                                           |

| 3.3 An Analog Wavelet-based Wideband Spectrum Sensing                      |

| 3.4 Spectrum Sensing Resolution for a UWB-based Cognitive Radios           |

| 3.5 Triangular waveform generation with Source Follower LPF for Side-lobe<br>Reduction | 38   |

|----------------------------------------------------------------------------------------|------|

| 3.5.1 Triangular waveform generation with Source Follower LPF for Side-<br>Reduction   |      |

| 3.5.2 A Low power Triangular Waveform Generator                                        | . 39 |

| 3.5.3 Side-lobe Reduction of Triangular Waveform                                       | . 42 |

| 3.5.4 Modified Source-Follower-based Butterworth LPF                                   | . 43 |

| 3.5.5 Proposed Composite Triangular Waveform Generator with LPF                        | 45   |

| 3.6 Dual-Resolution Spectrum Sensing                                                   | 46   |

| 3.7 Measurement Results                                                                | 49   |

| 3.8 Conclusion                                                                         | 52   |

| 4 A 3-11GHz Low-Power Integer-N QPLL                                                   | 53   |

| 4.1 Wideband QPLL for UWB-based Cognitive Radio                                        | . 53 |

| 4.2 Two-stage Linear Tuning Differential QVCO                                          | . 54 |

| 4.3 Digital Calibration for Charge Pump Mismatch                                       | . 57 |

| 4.4 A Wideband Low-Power TSPC Frequency Divider                                        | . 61 |

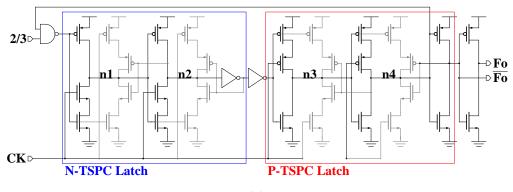

| 4.4.1 Truly Modular Programmable Divider                                               | . 63 |

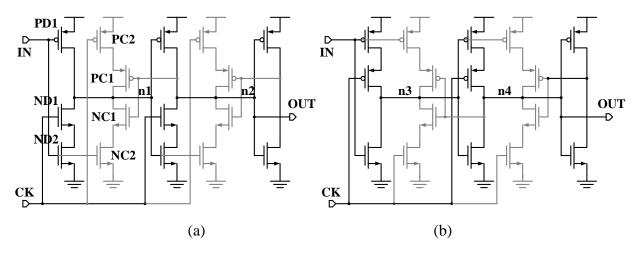

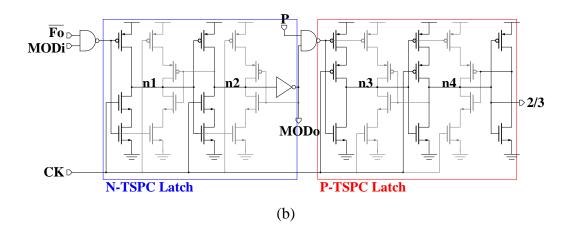

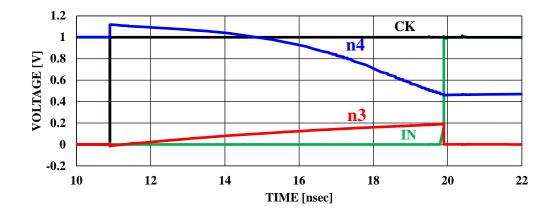

| 4.4.2 N/P-TSPC Latches with Gated Inverting Keeper                                     | . 63 |

| 4.5 Measurement Results                                                                | . 68 |

| 4.5.1 A 3-11GHz Low-Power Integer-N QPLL with Spur Reduction<br>Technique              | . 68 |

| 4.5.2 A 0.02-6.5GHz Low-Power TSPC Programmable Frequency<br>Divider                   | 71   |

| 4.6 Conclusion                                                                         | . 75 |

| 5 Triple Channel UWB-based Cognitive IR-UWB                                            | 76   |

| 5.1 A Carrier-based UWB Radio                                                          | 76   |

| 5.2 A Triple-Channel UWB-based Cognitive Radio                  |

|-----------------------------------------------------------------|

| 5.3 Transmitter of the triple-channel UWB-based Cognitive Radio |

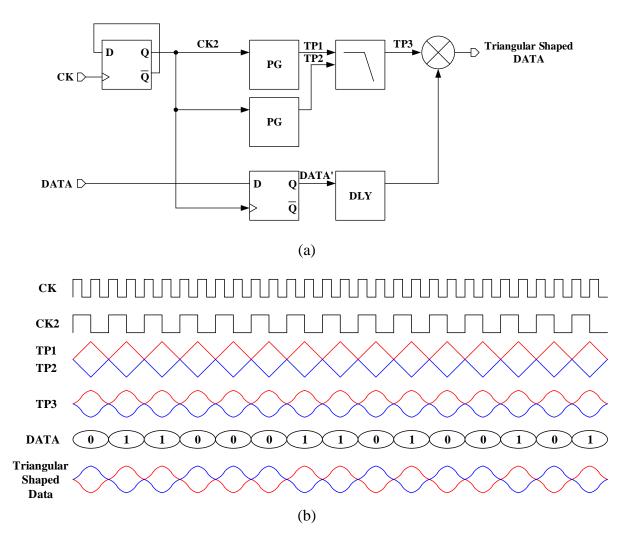

| 5.3.1 Triangular-shaped BPSK modulation                         |

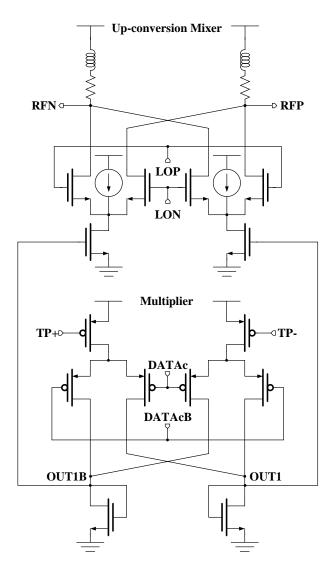

| 5.3.2 Up-Conversion Mixer and Modulation Multiplier             |

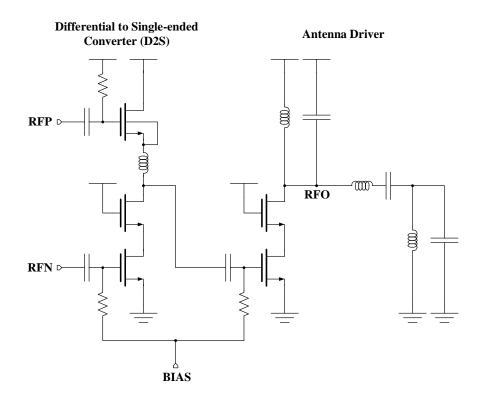

| 5.3.3 Differential to Single-ended convertor and Antenna Driver |

| 5.4 Receiver of the triple-channel UWB-based Cognitive Radio    |

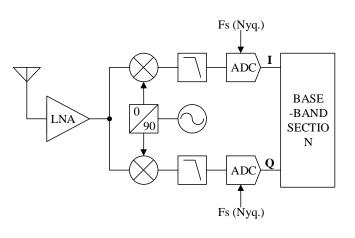

| 5.4.1 Quadrature Analog Correlation Receiver                    |

| 5.4.2 Wideband Low Noise Amplifier                              |

| 5.4.3 Down-Conversion Mixer                                     |

| 5.4.4 Analog Correlation Circuit 89                             |

| 5.4.5 Variable Gain Amplifier with DCOC                         |

| 5.5 UWB Chip Antenna 3.1 -10.3 GHz 94                           |

| 5.6 Measurement Results                                         |

| 5.7 Conclusion                                                  |

### **6** Conclusion

| 6.1 Summary      | 107 |

|------------------|-----|

| 6.2 Contribution | 109 |

| 6.3 Future Work  | 111 |

107

## Bibliography

# List of Figures

| 1.1 Ubiquitous wireless systems                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 UWB spectrum mask as defined by FCC and various type of UWB radios                                                                                                                                                                                                                                              |

| 1.3 Worldwide spectrum availability at the 60 GHz band and Atmospheric propagation attenuation versus frequency                                                                                                                                                                                                     |

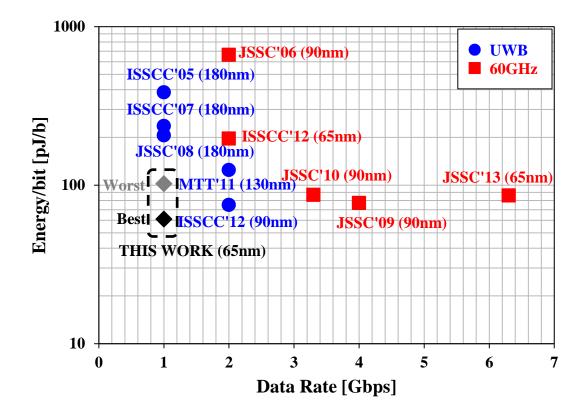

| 1.4 UWB and 60GHz transceivers FoM (Energy/bit) relative to data rate and process 5                                                                                                                                                                                                                                 |

| 1.5 Required data rate with the resolution of the screen for uncompressed wireless data communication                                                                                                                                                                                                               |

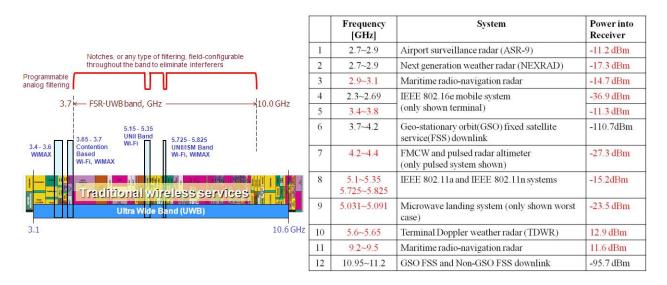

| 1.6 Services licensed to operate in the UWB band                                                                                                                                                                                                                                                                    |

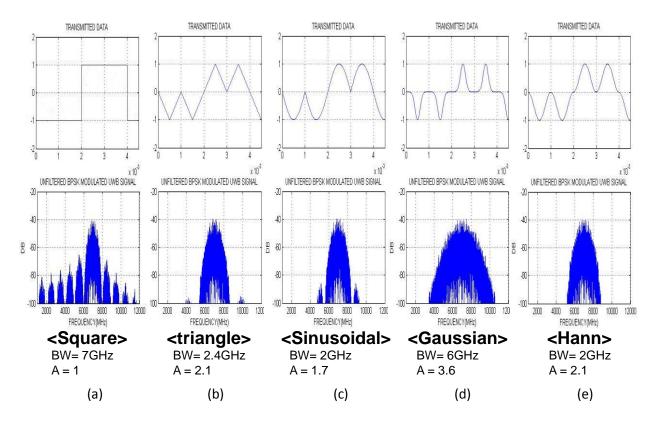

| 2.1 Time domain pulse shapes modulated with 1000 random bit sequence and power spectral density of the (a) square, (b) triangle, (c) cosine, (d) Gaussian, and (d) Hann for 1Gb/s data rate. The null-to-null bandwidth (BW) for 1Gb/s and the carrier amplitude (A) to ge -41dBM/MHz spectral density are included |

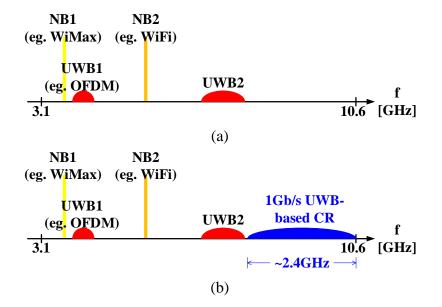

| <ul> <li>2.2 (a) An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) and (b) a single-channel 1Gb/s UWB-based CR with triangular BPSK pulses</li></ul>                                          |

| <ul> <li>2.3 (a) An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) and (b) a single-channel 1Gb/s UWB-based CR with triangular BPSK pulses</li></ul>                                          |

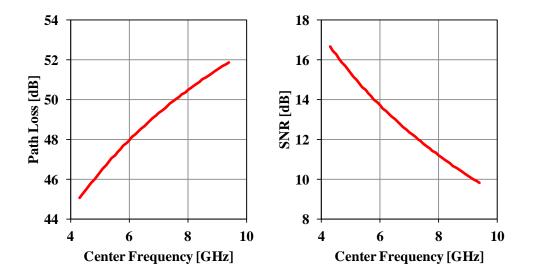

| 2.4 (a) Free path loss and (b) the SNR at the receiver with center frequency 10                                                                                                                                                                                                                                     |

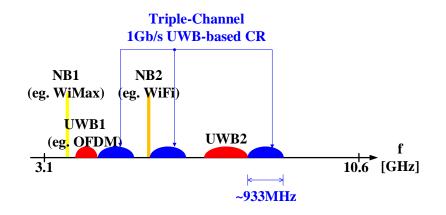

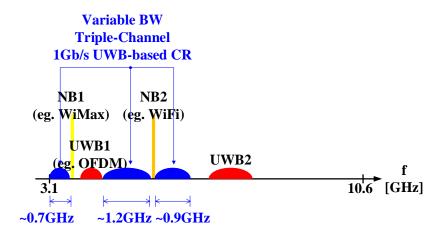

| 2.5 An example of the interferers with 30% channel occupation in MATLAB simulation (Th carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) and with a triple-channel 1Gb/s UWB-based CR with triangular BPSK pulses                                                                 |

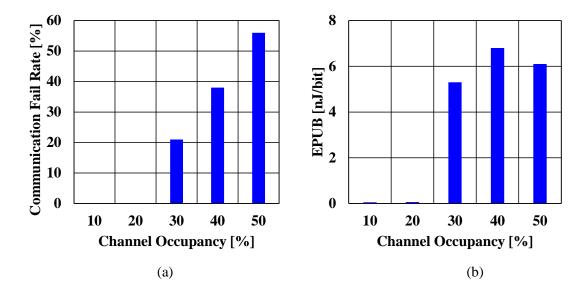

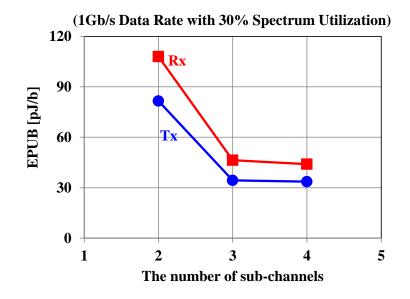

| 2.6 EPUB with the number of sub-channels in multi-channel UWB-based CR for 1Gb/s data rate with 30% spectrum utilization environment                                                                                                                                                                                |

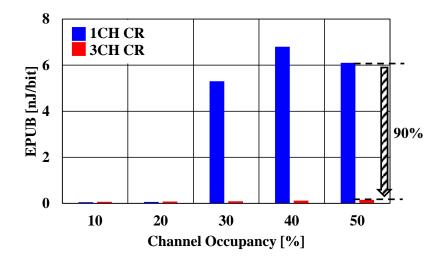

| 2.7 Performance comparison between a single-channel and a triple-channel UWB-based CRs<br>in terms of EPUB except communication fail cases of the single-channel CR along with<br>channel occupancy rate                                                                                                            |

| 2.8 An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) with a triple-channel 1Gb/s UWB-based CR with triangular BPSK pulses and adaptive BW for respective sub-channels                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

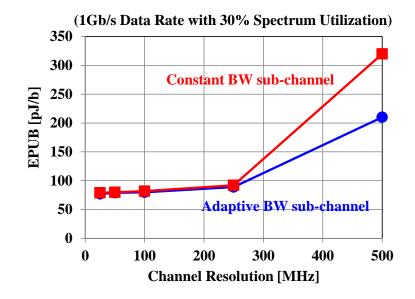

| 2.9 Comparison between constant BW and adaptive BW of the triple-channel CR in terms of EPUB with channel resolution 21                                                                                                                                                                                          |

| 2.10 (a) Receiver sensitivity and (b) required noise factor of the receiver chain of the single-<br>channel UWB-based CR with different carrier frequency and communication distance. 25                                                                                                                         |

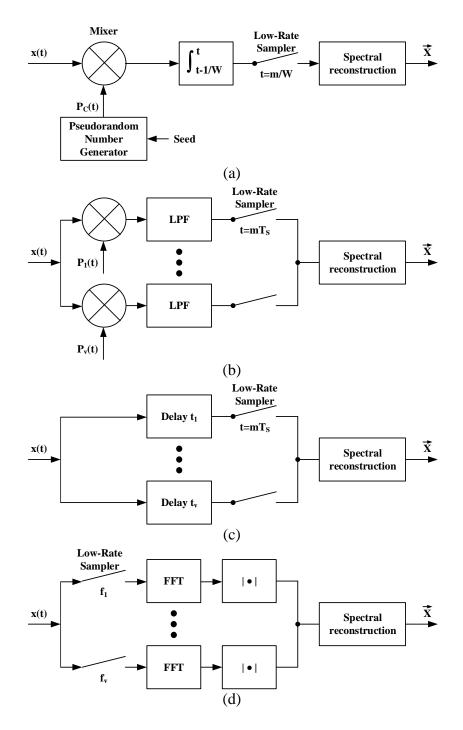

| <ul><li>3.1 Block diagrams for Nyquist wideband sensing algorithms of (a) multiband joint detection,</li><li>(b) wavelet detection, (c) sweep-tune detection, and (d) filter-band detection 30</li></ul>                                                                                                         |

| 3.2 Block diagrams for sub-Nyquist wideband sensing algorithms of (a) analog-to-<br>information converter based wideband sensing, (b) modulated wideband converter-based<br>wideband sensing, (c) multi-coset sampling-based wideband sensing, and (d) multi-rate<br>sub-Nyquist sampling-based wideband sensing |

| 3.3 Functional block diagram of the analog wavelet-based spectrum sensing 35                                                                                                                                                                                                                                     |

| 3.4 (a) Statistical Analysis in terms of the spectrum utilization efficiency and the sensing time, and (b) the quantized spectrum sensing resolution and maximum and minimum carrier frequency of the PLL                                                                                                        |

| 3.5 Functional block diagram of the modified analog wavelet-based spectrum sensing 38                                                                                                                                                                                                                            |

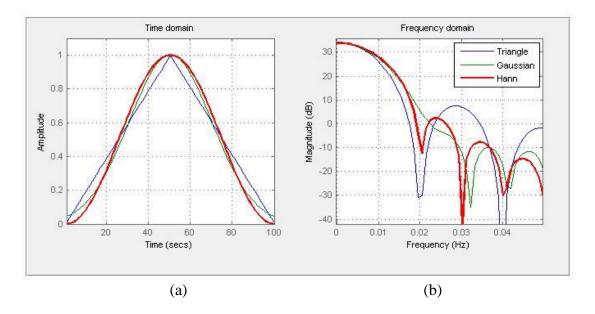

| 3.6 (a) Time domain plot and (b) power spectral densities of triangular, Gaussian, and Hann waveforms                                                                                                                                                                                                            |

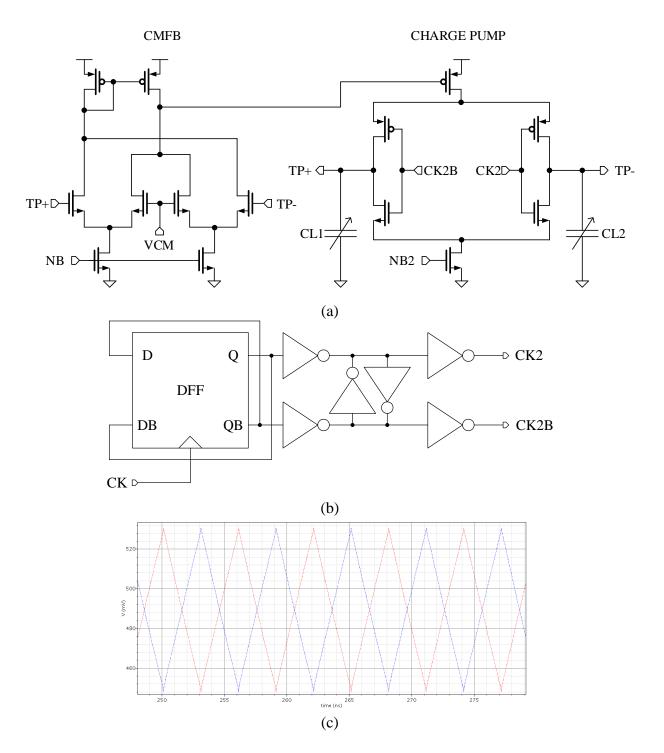

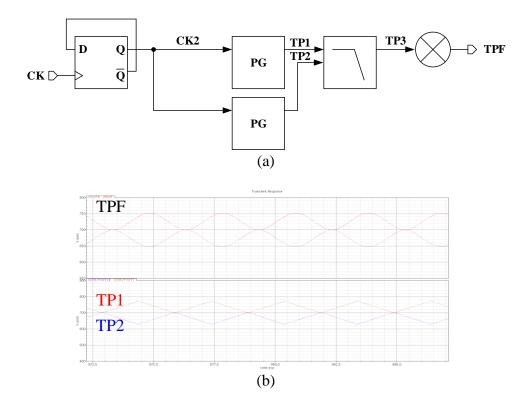

| <ul> <li>3.7 (a) Proposed fully differential Charge pump based triangular waveform generator, (b) a 50% duty cycle correction circuit, and (c) simulated output waveforms of the triangular waveform generator</li></ul>                                                                                         |

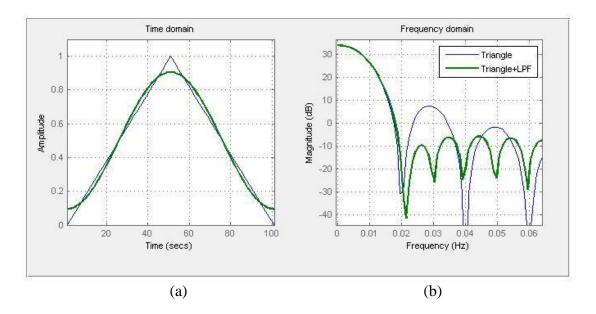

| 3.8 (a) Time domain plot and (b) power spectral densities of the triangular waveform without LPF and with 4th order Butterworth LPF                                                                                                                                                                              |

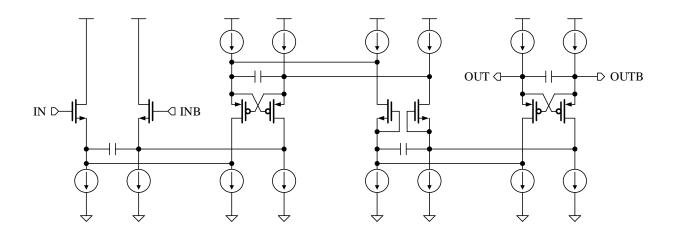

| 3.9 Modified source-follower-based 4th order Butterworth LPF                                                                                                                                                                                                                                                     |

| 3.10 Proposed composite triangular waveform generator with LPF and (b) its output waveforms                                                                                                                                                                                                                      |

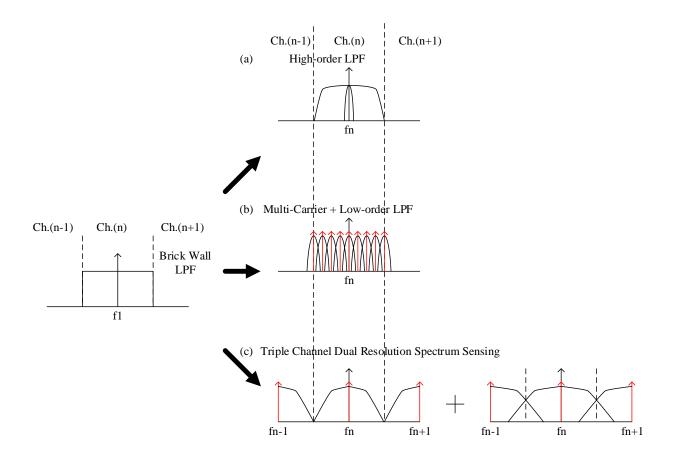

| 3.11 Methods to make brick wall BPF with (a) one carrier with a high-order LPF, (b) multi-<br>carriers with a low-order narrow-BW LPF, and (c) Triple carrier with a tunable dual<br>resolution LPF                                                                                                              |

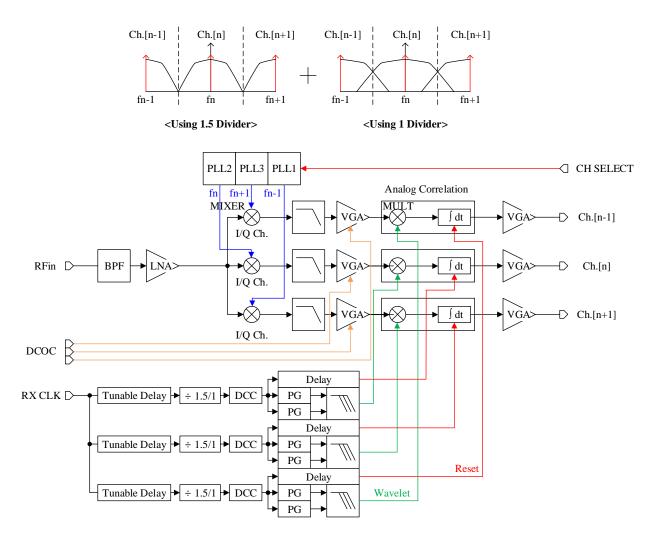

| 3.12 Proposed dual-resolution analog wavelet-based spectrum sensing                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

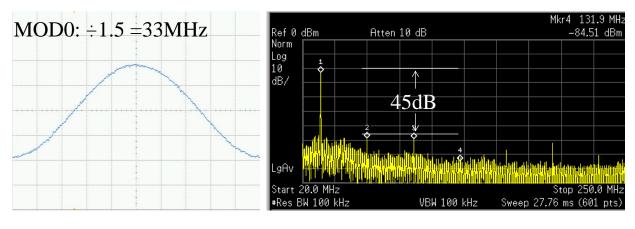

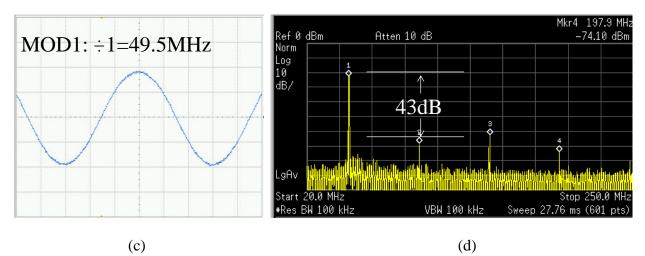

| 3.13 (a) time-domain wavelet and (b) spectrogram for MOD0 and (c) time-domain wavelet<br>and (d) spectrogram for MOD1 of the proposed triangular waveform generator with<br>LPF                                                                |

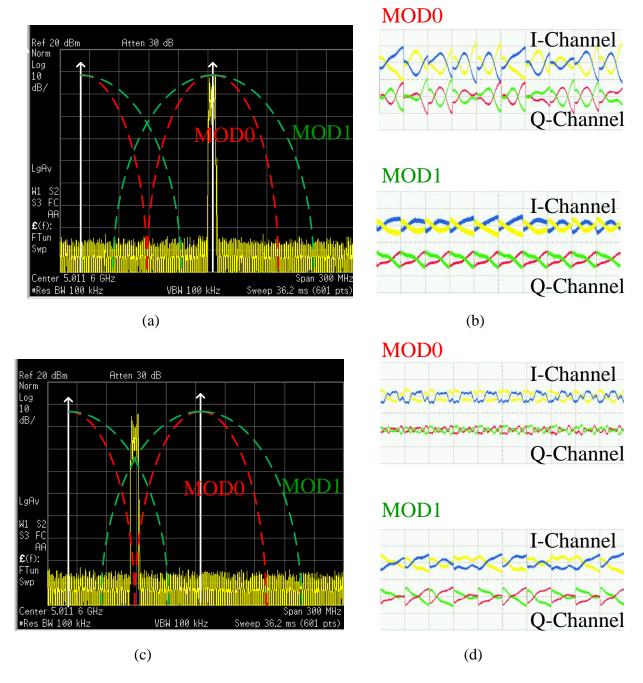

| 3.14 Dual-resolution analog wavelet-based spectrum sensing for narrow band interferer (a, b) at the center of the channel and (c, d) at the boundary of the channel                                                                            |

| 3.15 Dual-resolution analog wavelet-based spectrum sensing for wideband interferer 52                                                                                                                                                          |

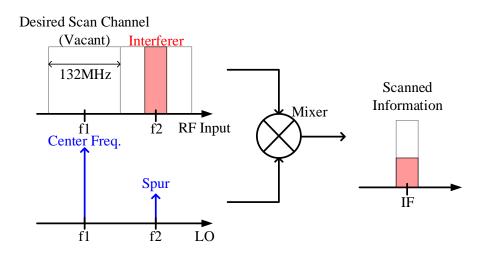

| 4.1 Reference spur issue in wavelet-based spectrum sensing 53                                                                                                                                                                                  |

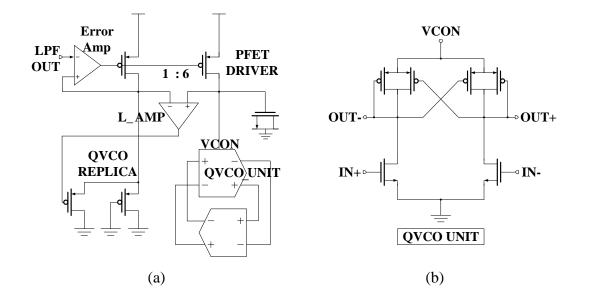

| 4.2 (a) The proposed supply regulated two stage differential QVCO, and (b) the QVCO unit cell                                                                                                                                                  |

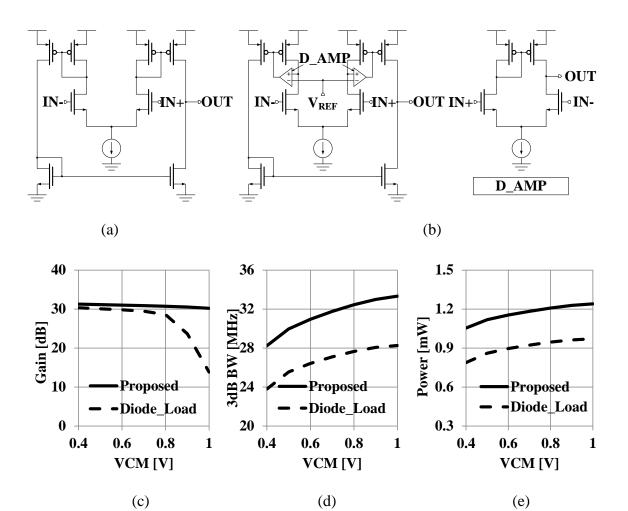

| 4.3 (a) The conventional dioded connected PMOS load error amplifier, (b) the proposed error amplifier with enhanced gm technique, and comparion in terms of (c) gain, (d) 3dB BW, and (e) power consumption with input common mode level (VCM) |

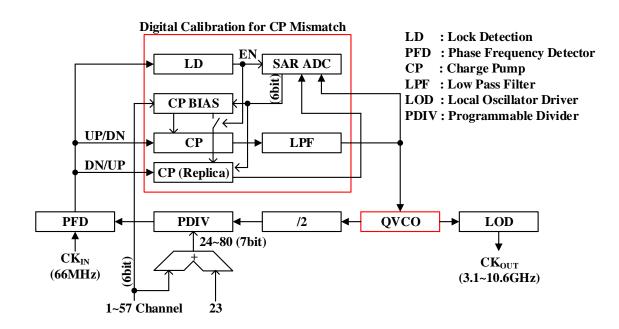

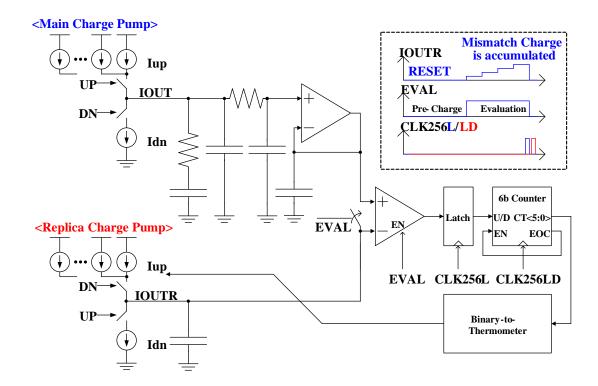

| 4.4 The proposed QPLL Architecture with digital calibration for CP                                                                                                                                                                             |

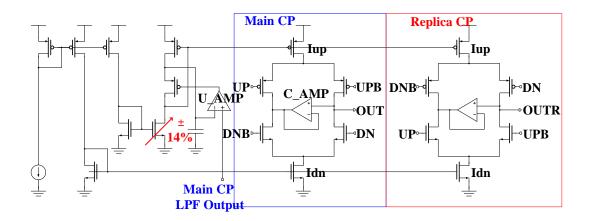

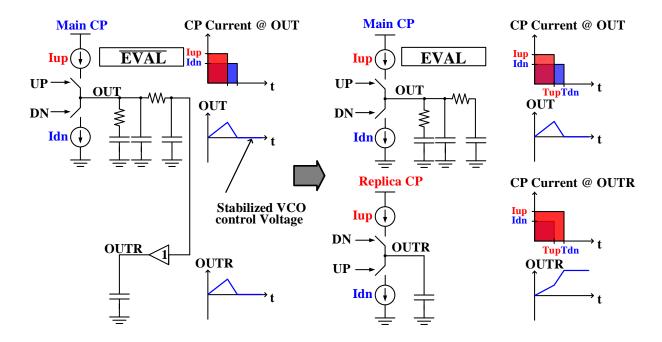

| 4.5 The proposed charge pump with the replica                                                                                                                                                                                                  |

| 4.5 The proposed charge pump with the replica                                                                                                                                                                                                  |

| 4.6 The proposed digital calibration for the CP current mismatch                                                                                                                                                                               |

| 4.7 Principal operation of the digital cariblation for Iup > Idn case                                                                                                                                                                          |

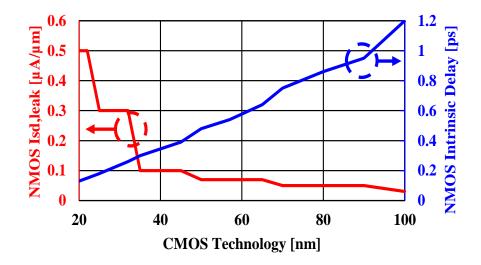

| <ul><li>4.8 Intrinsic delay and sub-threshold source drain leakage current of the NMOS with technology scaling (ITRS2003)</li></ul>                                                                                                            |

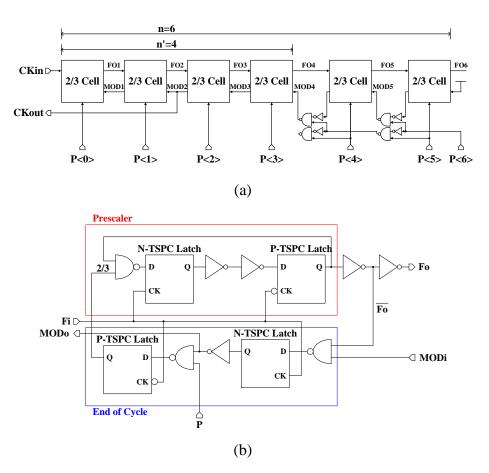

| 4.9 (a) Fully modular PDIV with extended division range architecture and (b) modified 2/3-<br>divider cell for TSPC latches                                                                                                                    |

| 4.10 (a) N-TSPC and (b) P-TSPC latches with the gated inverter for leakage compensation at dynamic nodes                                                                                                                                       |

| 4.11 (a) Prescaler logic and (b) end-of-cycle logic with N/P-TSPC latches of the modified 2/3-divider                                                                                                                                          |

| 4.12 Simulated leakage effect on the dynamic nodes of the prescaler P-TSPC latch without compensation technique                                                                                                                                |

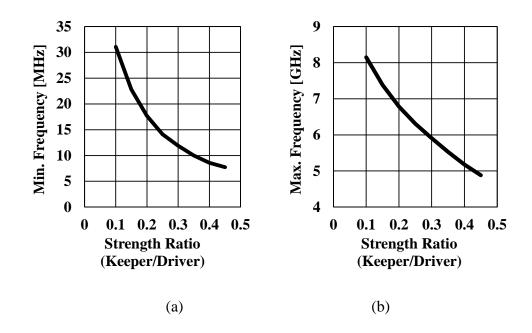

| 4.13 Simulated (a) minimum and (b) maximum operating frequencies with the strength ratio of the keeper to the driver                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

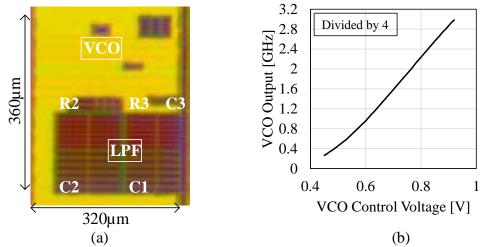

| 4.14 (a) Chip photo of the proposed QPLL and (b) Measured VCO output tuning range with an 8 divider                                                                                                |

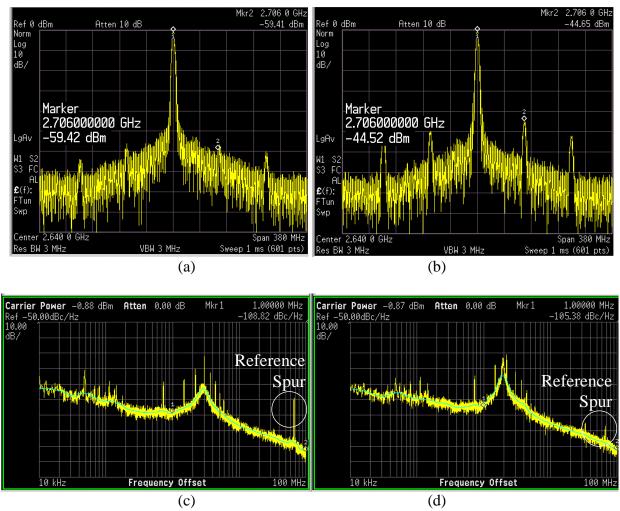

| 4.15 Comparison of the measured QPLL output spectrum and phase noise (a,c) without and (b,d) with the digital calibration technique                                                                |

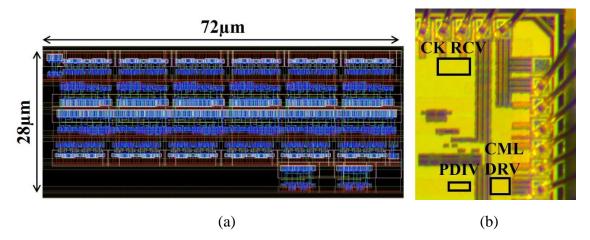

| 4.16 (a) Layout of the proposed TSPC PDIV with the gated inverting keeper and (b) chip photo of the test chip                                                                                      |

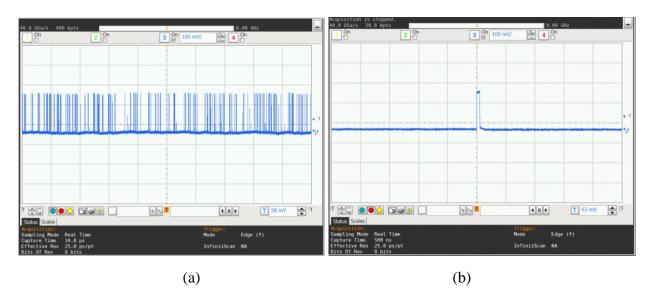

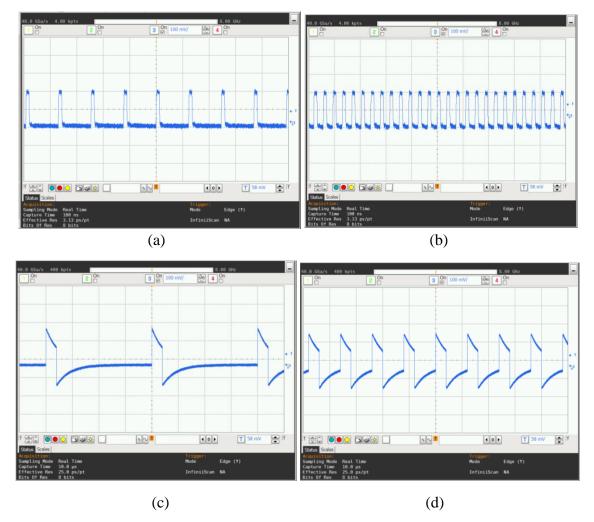

| <ul><li>4.17 TSPC PDIV output of the non-gate inverting keeper with (a) 80-division (20MHz) and</li><li>(b) 24-division ratio (20MHz)</li></ul>                                                    |

| <ul> <li>4.18 TSPC PDIV output of the gate inverting keeper with (a) 80-division (6.5GHz), (b) 24-division (6.5GHz), (c) 80-division (20MHz), and (d) 24-division ratio</li> <li>(20MHz)</li></ul> |

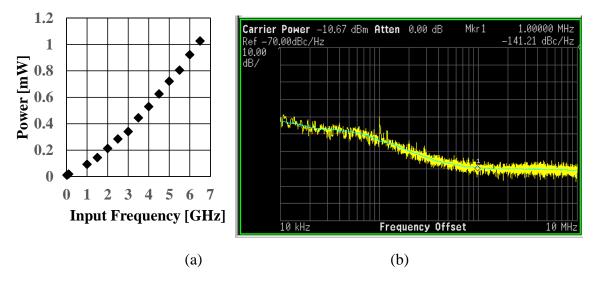

| 4.19 (a) Power consumption of the PDIV and (b) phase noise with 6.5GHz input frequency                                                                                                             |

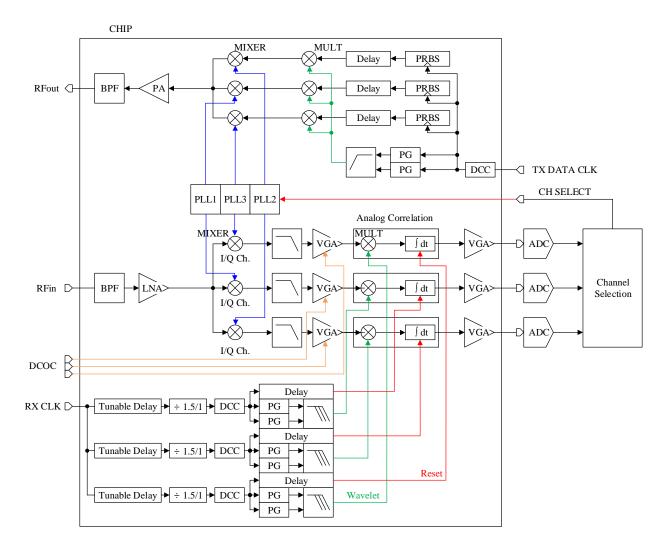

| 5.1 Architecture of Triple Channel UWB-based Cognitive IR-UWB                                                                                                                                      |

| 5.2 (a) Block diagram and (b) waveforms of the triangular-shaped BPSK modulation 80                                                                                                                |

| 5.3 Up-conversion mixer and modulation multiplier for the triangular-shaped BPSK modulated signals                                                                                                 |

| 5.4 Differential to single-ended converter and antenna driver with BPF                                                                                                                             |

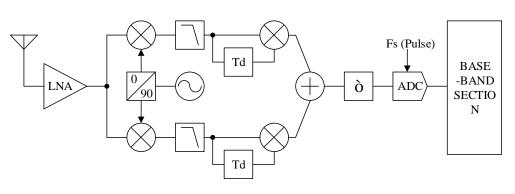

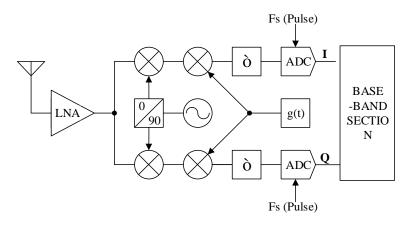

| 5.5 (a) Direct conversion (DC), (b) transmitted reference (TR), and (c) quadrature analog correlation (QAC) receivers                                                                              |

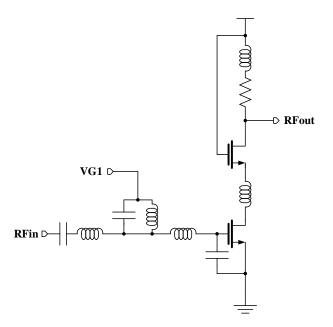

| 5.6 An ultra-wideband amplifier using Chebyshev active filter                                                                                                                                      |

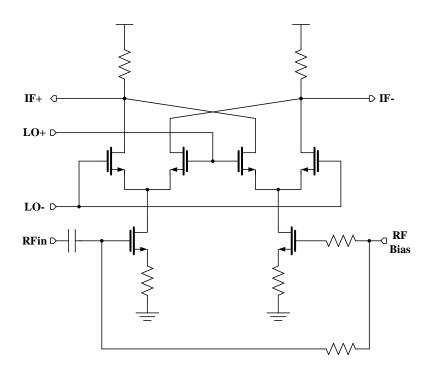

| 5.7 Gilbert-type double balanced active mixer with resistive source degeneration                                                                                                                   |

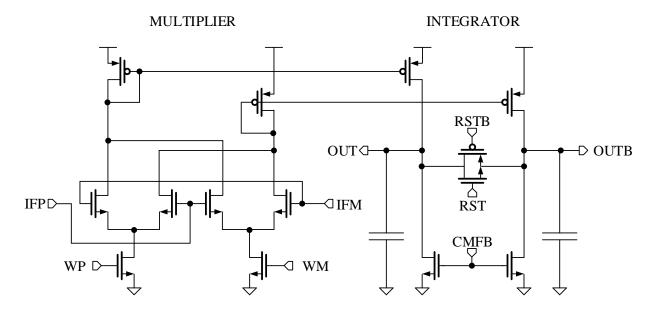

| 5.8 Gilbert-type Analog correlation circuit with a multiplier and integrator                                                                                                                       |

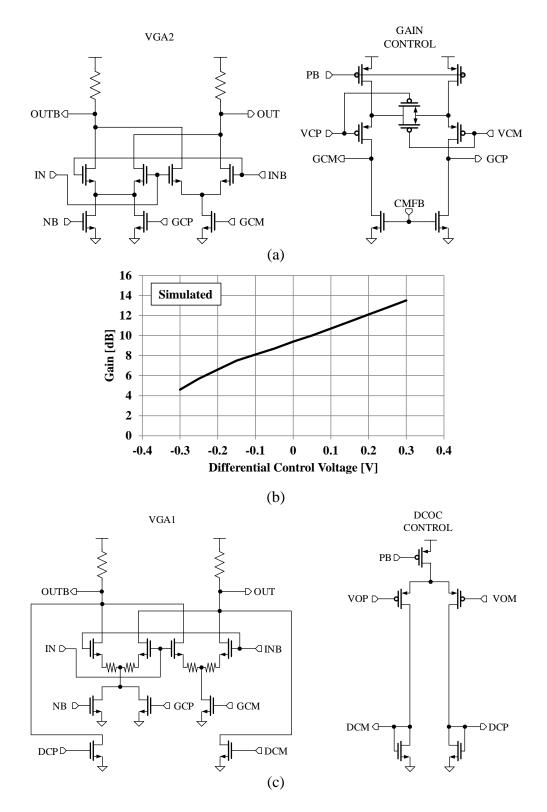

| 5.9 (a) Variable gain amplifier (VGA), (b) simulated gain curve with differential control voltage, and (c) VGA with DC offset cancellation and the control                                         |

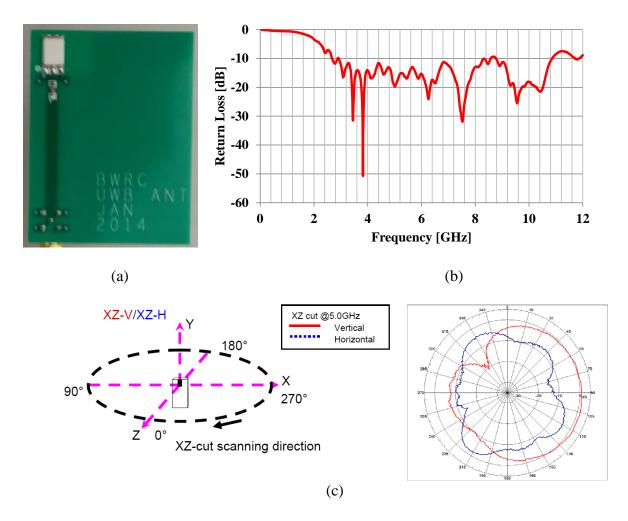

| 5.10 (a) Antenna board with UWB chip antenna, (b) antenna return loss and isolation, and (c) antenna radiation pattern                                                                             |

| <ul><li>5.11 (a) Die microphotograph of the test chip and (b) PCB with chip-on-board packing for test chip and a UWB antenna board</li></ul>                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

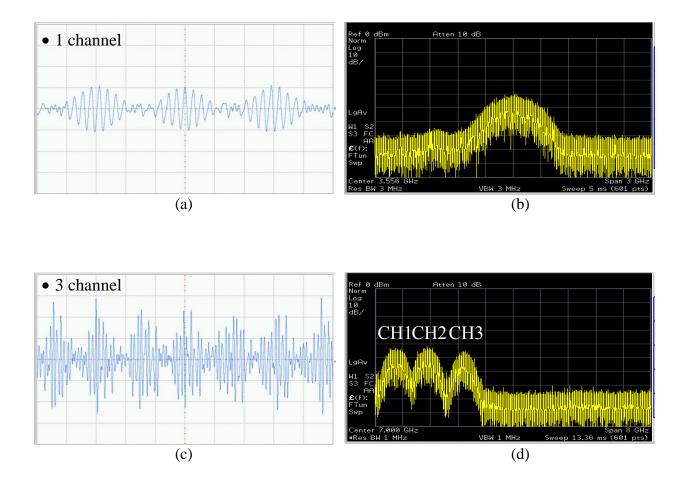

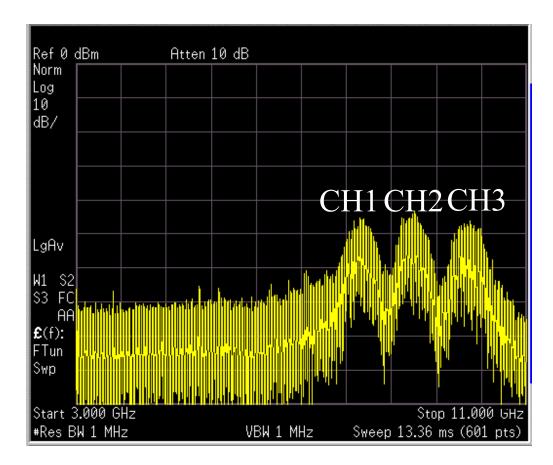

| <ul> <li>5.12 (a) Measured BPSK triangular-shaped pulse with a center frequency of 3.564GHz and</li> <li>(b) its power spectral density, and (c) measured BPSK triangular-shaped pules with three center frequencies of 3.564GHz, 4.488GHz, and 5.412GHz and (d) their power spectral densities</li></ul> |

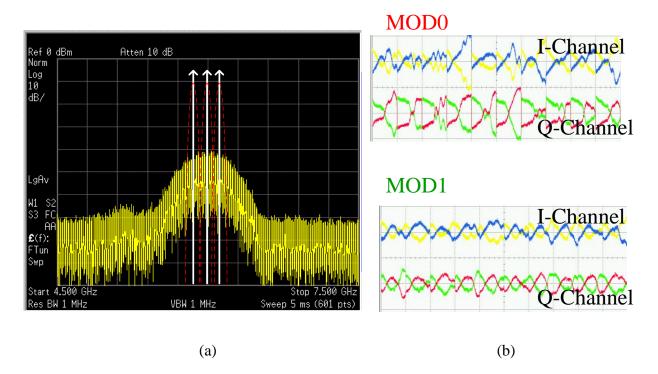

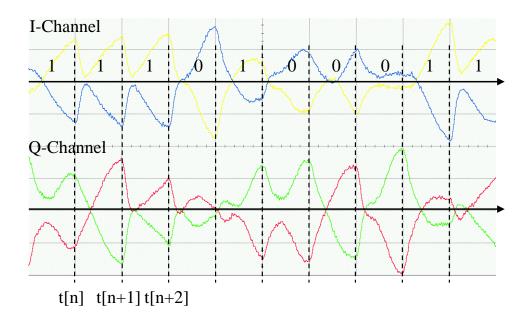

| 5.13 I- and Q- channel analog correlation output waveforms for QAC receiver mode 98                                                                                                                                                                                                                       |

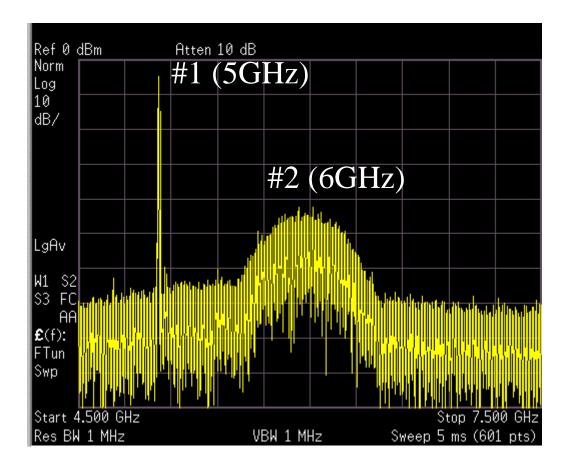

| <ul> <li>5.14 Measured narrowband interferer with a center frequency at 5GHz (about 30MHz of 3dB BW) and wideband interferer with a center frequency at 5.94GHz (about 900MHz of 3dB BW)</li></ul>                                                                                                        |

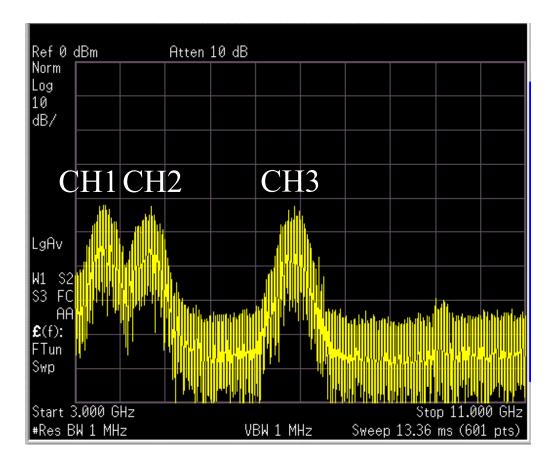

| 5.15 Measured power spectral density of the BPSK triangular-shaped pules with three center frequencies of 3.564GHz, 4.488GHz, and 6.864GHz                                                                                                                                                                |

| 5.16 Measured power spectral density of the BPSK triangular-shaped pules with three center frequencies of 8.184GHz, 9.108GHz, and 10.032GHz101                                                                                                                                                            |

| 5.17 FoM (Energy/bit) comparison with data rate and process                                                                                                                                                                                                                                               |

| 5.18 BER comparison with data rate and process                                                                                                                                                                                                                                                            |

| 5.19 Communication distance comparison with data rate and process                                                                                                                                                                                                                                         |

## List of Tables

| 2.1 Link budget of the single-channel UWB-based CR for 1Gb/s data rate | 24  |

|------------------------------------------------------------------------|-----|

| 4.2 Performance summary and comparison of the proposed QPLL            | .70 |

| 4.2 Performance summary and comparison of the proposed PDIV            | .74 |

| 5.1 Chip performance summary                                           | 105 |

### Acknowledgments

Working and studying with brilliant people in the superb environment at UC Berkeley was one of the most fortunate and honorable opportunities in my whole life. Most of all my gratitude to my research advisor, Prof. Jan M. Rabaey is so sincere and deep that I can't even find proper words to express it. Without the dedication, insight, and tolerance he showed me during my stay, I could not have reached this point, much less conducted proper research. I also would like to convey my deepest thanks to Prof. Ali M. Ninejad for the discussion and his devotion to the field of research. It was also my honor to have Prof. Paul K. Wright as my qualification committee.

The Berkeley Wireless Research Center (BWRC) was the ideal place to study, discuss, and make chips. I've been proud of being a member of this great facility from the first day. I still vividly remember my hard feeling of pride when I first got my cubicle at BWRC. In the center, Brian helped me how to do tape out, and Fred had done his all effort for my chip testing. Other BWRC staff gave me a lot of support that I can focus on my research work.

I appreciate the support and help from Jan's group: Tsung-Te Liu, Michael Mark, David Chen, Simone Gambini, Louis Alarcon, Wenting Zhou, Rikky Muller, Jesse Richmond, Wen Li, Arash Parsa, Christopher Sutardja, Dan Yeager, Wiliam Biederman, and Nathan Narevsky. I would like to special thank Shinwon Kang, Yue Lu, Jun Chau Chien, and Steven Callendar. I have gotten a lot of support and feedback from them to do my Ph.D. research. Jiashu Chen and Lingkai Kong also gave me lots of comments and guidance when I faced with issues that I couldn't get exact solution. I want to express my gratitude to Stanley Chen for co-working on first tape-out in BWRC and on teaching assistance of EE141. Ping-chen Huang was always trying her best to help me in my research and coursework. Ji-Hoon Park has encouraged me to win through difficulties during my Ph.D. program in UC Berkeley. It was my great my pleasure to do my coursework with Kyoohyun Noh. I would also thank Changhwan shin, Kanghoon Jeon, Eungsuk Park and Jaewon Jang for their continuous support both on school and on social lives. I'm also proud of Kwangmo Jung, Jaewha Kwak, Jaeduk Han, and Seobin Jung, the Korean circuit students who overcame the difficulties of Ph.D program of UC Berkeley. I am also grateful to Kenichi Agawa for being great sources of inspiration. I cannot forget assistance from other previous students whom I have spent previous time with: Changho Suh, Zhengya Zhang,

Pulkit Grover, Amin Arbabian, Richard Su, Chintan Thakkar, Stan Baek, Jiwoong Lee, Jaeseok Jeon, Sung-Hwan Kim, Hanh-Phuc Le, Wookhyun Kwon, Omar Bakr, Hongki Kang, Yida Duan, Kangwook Lee, and Jaeyeon Baek.

I would like to thank my friends Koohong Chung and Yongbae Lee in my Berkeley life. For the past six years, they enriched my life in many different ways. I cannot imagine my life in Berkeley without them. They are definitely the best friends in my life. Moreover, Koohong gave me another chance to do different perspective research that enriched my academia life. I want to say my gratitude to Byunggon Chun, Jemin Park, and Jungkyu Kim for their continuous advice for my daily life and religious life. I also appreciate continuous friendship from Tony Taehyoung Kim. Albany Korean Tennis club that I have enjoyed as a hobby helped me to relive my stress from studying and research and to provide me with chances to meet many good people who also enrich my Berkeley life.

Last but not least, my greatest gratitude goes to my family who has been my endless source of encouragement and self-confidence even though they were thousands miles away. My wife has supported and encouraged me to struggle on my Ph.D. program. My daughter also enriches my life by getting happiness and encouragement from her even if I could not be with her for long time. I deeply appreciate my Mom dedication on my life. She always prays for me. Without her emotional support, I wouldn't have made it through the desperate, dark moments and many sleepless nights. I also appreciate Dad's constant concern and encouragement. I also appreciate my brother's dedication to my family. In all, this work would have been impossible without the support of my family. I dedicate this humble work to my wife, daughter, brother, Dad, and Mom.

## Chapter 1. Introduction

## 1.1 High-Data-Rate and Short-Range Radio

With the rapid evolution of wireless technologies, ubiquitous and always-on wireless system in homes and enterprises are expected to emerge in the near future as shown in Fig. 1.1. A wide range of heterogeneous systems, including wireless personal area networks (WPAN), wireless local area networks (WLAN), cellular, WiMAX, and satellite systems will be present together to meet consumer demand for wireless data capacity [1].

Figure 1.1: Ubiquitous wireless systems

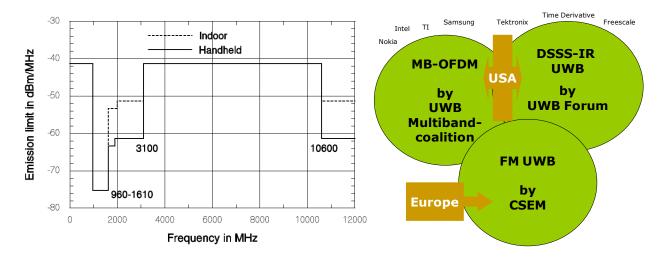

Figure 1.2: UWB spectrum mask as defined by FCC and various type of UWB radios

The ultra-wideband (UWB) and 60 GHz millimeter-wave based radios are expected to play a vital role in emerging WPAN for high-data-rate wireless applications. UWB technology, proposed for high-speed short-range applications, is one of the more active areas of focus in academia, industry, and regulatory circles. UWB technology affects the basic policy of spectrum regulation by using both the occupied and the unoccupied spectrum across the 3.1–10.6 GHz band as shown in Fig. 1.2. The -10dB bandwidth (BW) is greater than 500MHz and the transmitted power density is limited to be less than -41.3dBm/MHz in the UWB band. After allowance of commercialized UWB radio in United States from FCC [2], IEEE802.15.3a was an attempt to provide high rate UWB PHY based on multiband orthogonal frequency domain multiplexing (MB-OFDM) and direct sequence spread spectrum (DSSS) by industry mainly. However, the members of the task group were not able to come to an agreement choosing between two technology proposals.

In the meantime, Impulse radio systems have received much attention as a possible architecture for UWB transceivers from academia and research institute due to the large data bandwidth, low spectral interference with nearby channels, and simplicity of UWB transmitter/receiver architectures with mostly digital implementations. Because of the low emitted power spectral density of -41.3dBm MHz mandated by the FCC, impulse radio is especially well suited for low-cost, low power, and short-range wireless communications [3].

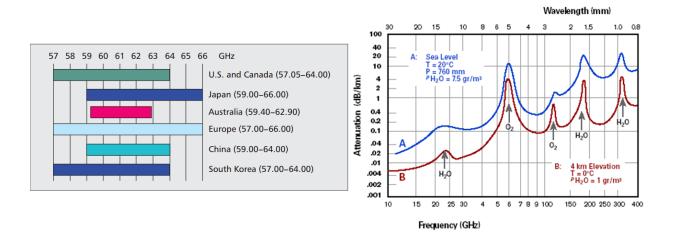

Figure 1.3: Worldwide spectrum availability at the 60 GHz band and Atmospheric propagation attenuation versus frequency.

There is also an ongoing effort to migrate indoor WLAN and WPAN networks toward less congested higher frequency unlicensed spectrum bands of 60 GHz (Fig. 1.3) to provide high data rates of up to several gigabits per second for indoor applications. Their interest in this frequency band stems from a phenomenon of nature: the oxygen molecule (O2) absorbs electromagnetic energy at 60GHz. Several standardization bodies have been working on the 60-GHz PHY and MAC protocols approaching 10Gb/s service rate. These include the IEEE 802.11ad and Wireless Gigabit Alliance (WiGig) for WLAN, and IEEE 802.15.3c, and Wireless HD for short-range PANs. The IEEE 802.15.3c standard defines a central controlled network topology and TDMA-based MAC protocol for 60-GHz wireless PANs [4]. The IEEE 802.11ad draft standard introduces a new

network architecture named Personal Basic Service (PBSS) without an access point in which each station can serve the role of a central coordination point which supports a combination of random access CSMA access and scheduled TDMA access modes. There are still a number of open research issues related to 60-GHz networks such as MAC-layer support for beam switching, diversity techniques to overcome propagation impairments, cooperative relaying [5]. Overall, 60-GHz technology is expected to mature during the next three to five years and will provide an important option for high-speed indoor connectivity associated with applications such as device docking and HD video.

### 1.2 Comparison between UWB Radio and 60GHz Radio

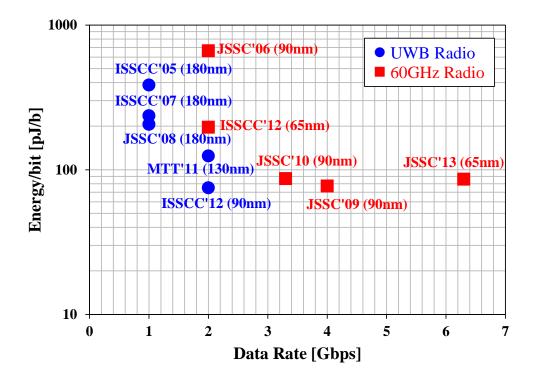

The plot in Fig. 1.4 compares the energy/bit of recently published UWB and 60GHz transceivers [6-15]. Energy/bit is a popular figure-of-merit (FoM) for wireless transceivers because it directly relates to the energy required to transmit and receive a single bit of data, or the efficiency of the radio. All results are measurements from fabricated custom integrated circuits. The highest data rate of the UWB radio and 60GHz radio goes up to 2Gb/s and 6.5Gb/s respectively. UWB radio output power (-41dBm/MHz) is much lesser than that of 60GHz radio. Thus, there is limitation to get the data rate of larger than 2Gb/s.

On the other hand, the lowest data rate of the 60GHz radio is 1 or 2Gb/s since average power consumption of the 60GHz radio is higher than that of the UWB radio mainly due to the difference of the carrier frequency. Two radio technology has the same dependence on the data rate as the FoM generally decreases with increasing data rate. Comparison on 2Gb/s data rate shows that UWB radio is more efficient than 60GHz radio in terms of energy consumption. This two

observations verify that UWB radio is more efficient less than 2Gb/s data rate wireless communication than 60 GHz transceivers.

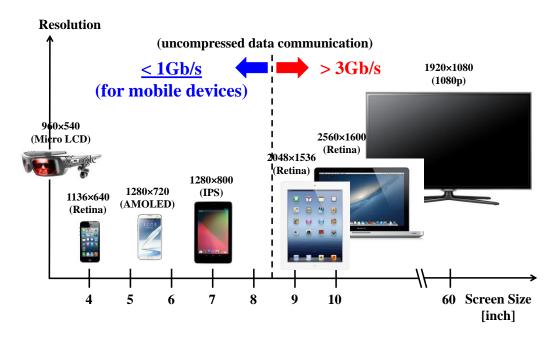

Fig 1. 5 shows the required data rate with the resolution of the screen for uncompressed wireless data communication that is one of the example of high data rate short range wireless communication. In case of mobile devices like 4~5 inch smart phones and head-mount displays, around 1Gbps data rate is enough to provide the uncompressed data application.

Figure 1.4: UWB and 60GHz transceivers FoM (Energy/bit) relative to data rate and process

Figure 1.5: Required data rate with the resolution of the screen for uncompressed wireless data communication.

## 1.3 Interferers in UWB band

Potentially a large number of UWB devices may operate in close proximity of an indoor wireless application such as Wireless Local Area Network (WLAN). The UWB signal is a very low power signal and therefore the power of any single UWB device can be compared to that of a noise floor. But when a number of such devices operate simultaneously then the interference level could rise significantly above the level of the noise floor [16]. In addition to UWB interferers, Fig. 1.6 shows the narrow band licensed interferes like IEEE 802.11a and WiMax that operate in the UWB band also increases noise level of the desired UWB signals [17, 18].

Figure 1.6: Services licensed to operate in the UWB band.

The traditional regulatory mechanism to handle interference is to separate contenders in space or in frequency. Thus regulators would impose artificial limits on transmissions to minimize interference. This approach precludes dynamic spatial/temporal reuse of the spectrum. Furthermore, with all frequency bands being allocated multiple times over, new spectrum is not readily available for such allocation.

UWB regulations in Japan, Europe, Korea and China has introduced Detect and Avoid (DAA) Schemes, in which UWB systems will first check whether there are NB systems existing in the environment and if it exists, NB avoidance techniques can be applied [19]. Thus, by declaring that all new users of the spectrum are secondary users and requiring that they must detect and avoid (DAA) the primary user, the regulators are opening up spectrum for opportunistic use. In the absence of DAA functionality, UWB devices would have to forfeit the band designated as 'DAA required' which would greatly reduce the spectrum available for communication.

## 1.4 UWB-based Cognitive Radios

The general idea behind Cognitive Radio is that performance can be improved by reducing interference if wireless systems were aware of other RF signals in the band. While communication engineers have historically thought of channel capacity and Shannon's Law simply in terms of bandwidth, Cognitive Radio considers an expanded view of the wireless channel by managing various dimensions of time, frequency, space, power, and coding [20].

Since UWB faces severe interference from narrowband system nearby, it will surely benefit more from utilizing Cognitive radio techniques implementing the collaborative coexistence process than will the non-UWB systems [21]. UWB is highly competent in satisfying many basic requirements of cognitive radio. Therefore, employing UWB in cognitive radio networks could be very instrumental for the successful penetration of cognitive radio into the wireless world. Nevertheless, since today's spectrum regulations prohibit employing UWB systems in the overlay mode, UWB based implementation of cognitive radio might not become a reality in the near future. However, besides being a strong candidate for practical cognitive radio implementation, UWB can be considered as a supplement to cognitive radio systems that are realized by means of other wireless technologies. Therefore, it can be concluded that this way or the other, UWB will be an inseparable part of cognitive radio applications. UWB can offer various kinds of support to cognitive radio network. These include sharing the spectrum sensing information via UWB, locating the cognitive nodes in a cognitive network by means of IR-UWB, and sensing the physical environment channel with IR-Spectrum Sensing.

## 1.5 Dissertation Outline

Chapter 2 discusses architecture level design for short-range high-data rate radio. UWB radio and 60GHz millimeter wave radio are compared in terms of energy efficiency with their data rate. Interference issue in UWB band is addressed with cognitive radio technique. Statistical analysis helps to define UWB-based cognitive radio architecture like modulation method and pulse shaping. Another investigation is done with a multi-channel UWB-based cognitive radio and a single-channel one. The analysis also gives high energy efficiency of the triple-channel UWB-based cognitive radio in over 20% channel occupancy cases.

Low power spectrum sensing algorithms are discussed with architecture level and circuit level approach in Chapter 3. Several algorithms are investigated to find out proper spectrum sensing solution for energy efficient, short-range, and high data rate UWB-based cognitive radios. Moreover, dual-resolution analog wavelet-based spectrum sensing is introduced to detect narrowband and wideband interferers together with low power consumption. This chapter also deals with the implementation of the proposed spectrum sensing, and the test chip results verify the efficiency.

In Chapter 4, the wide lock range and low power QPLL is introduced to utilize whole bandwidth of the UWB band and to accommodate higher capacity and data rates. Low power and wide lock range can be achieved with the proposed two stage ring oscillator having highly linear tuning characteristics over whole UWB frequency range. Digitally spur reduction technique on the charge pump mismatch is also introduced to reduce spur level, which causes malfunction in spectrum sensing operation. This chapter also deals with the implementation of the proposed QPLL with the spur reduction technique, and the test chip results verify the efficiency. Low power programmable divider is addressed with true-single-phase-clock logic in chapter 4. Gated inverter technique is adopted for wide frequency range operation. Proper frequency range can be defined by the maximum cycle with timing analysis and the minimum cycle with subthreshold leakage current analysis. This chapter also deals with the implementation of the proposed QPLL with the spur reduction technique, and the test chip results verify the efficiency.

Chapter 5 describes circuit details and demonstrates functionality of the proposed triple-channel UWB-based cognitive radio with the test chip. This approach can be shown to be optimal to avoid unknown narrowband and wideband interferers. The best and the worst cases of the channel allocation in the proposed radio according to channel occupancies are described, and the measurement results show the energy efficiency of the radio. Finally, this chapter summarizes performance of the chip and compares it with other recently published high data rate UWB and 60GHz radios.

Conclusions and contributions are given in Chapter 6.

## Chapter 2. Multi-Channel High-Data-Rate UWB-based Cognitive Radio

## 2.1 Modulation Schemes of the UWB Radio

In UWB radio, simple modulation schemes are used such as pulse amplitude modulation (PAM) [22], on-off keying (OOK) [23], pulse position modulation (PPM) [24], binary frequency shift keying (BFSK) [25], binary phase shift keying (BPSK) [26], and transmitted reference [27]. BPSK outperforms PAM and PPM due to an inherent 3dB increase in separation between constellation points. The high data rate transmitters use BPSK modulation with a coherent receiver. BPSK can minimize losses in the link budget and can obtain the maximum distance with more than hundreds Mb/s.

## 2.2 Pulse Shaping of the UWB Radio

The time domain pulse shapes considered are the square, triangle, cosine, Gaussian, and Hann. These pulses are BPSK modulated with 1000 random bit sequence in time domain, and corresponding power spectral densities are shown in Figure 2.1 with MATLAB simulation. The carrier frequency is 7GHz. First, the null-to-null bandwidth (BW) for 1Gb/s data rate is examined. Hann and cosine require the minimum null-to-null BW of 2GHz, and Gaussian pulse has the maximum null-to-null BW of 6GHz. Second, each pulse requires different carrier amplitude to get -41dBm/MHz spectral density. The magnitude is normalized to the amplitude of the square pulse case, which is defined as A in the figure. The parameter A is strongly related with power consumption of the transmitter. Gaussian pulse needs high power consumption since it has the largest BW. Third, side-lobe leakage is examined. Small side lobe leakage is desirable to get high spectral efficiency. Hann and Gaussian pulses have the lowest side-lobe leakage, and square pulse has the highest one. Finally, implementation complexity should be considered since the complexity is highly proportional to circuit power consumption. It is hard to generate Gaussian and Hann pulses in CMOS technology.

Figure 2.1: Time domain pulse shapes modulated with 1000 random bit sequence and power spectral density of the (a) square, (b) triangle, (c) cosine, (d) Gaussian, and (d) Hann for 1Gb/s data rate. The null-to-null bandwidth (BW) for 1Gb/s and the carrier amplitude (A) to get -41dBm/MHz spectral density are included.

Triangular pulses do not show the best results in terms of BW, A, and side-lobe leakage. However, if all design parameters including BW, A, side-lobe leakage, and complexity, are considered, triangular pulses can provides optimal performance among the five candidates. Triangular pulse shaping requires 2.8GHz null-to-null BW, 2.1 relative carrier frequency amplitude to square pulse, and about -54dBc/MHz side-lobe magnitude to main-lobe magnitude. Moreover, design complexity can be simplified even with CMOS technology, which leads to low power consumption.

## 2.3 Single-Channel UWB-based Cognitive Radio

Statistical analysis is done with the help of MATLAB for estimating the performance of the UWB-based Cognitive radio (CR). Fig. 2.2(a) shows an example of randomly decided interferers that takes 30% channel occupation of the UWB band, 3.1GHz to 10.6GHz. Contiguous 2.8GHz null-to-null frequency range is searched with the interferers' environment in order to accommodate the spectrum of the 1Gbps random triangular BPSK pulses. Fig. 2.2(b) shows the allocated at the vacant channel after searching 2.8GHz contiguous bandwidth where does not have interferers. Energy/bit is calculated at the allocated center frequency. The allocated channel carrier frequency is at around 9GHz in this example.

This operation is done repeatedly by 1000 times as changing the location of the interferers. The resolution of carrier frequency of the interferers is 10MHz from 3.1GHz to 10.6GHz. The random variables are generated with uniform distribution. On the other hand, the number of interferers is fixed during the 1000 iteration, which defines channel occupancy in the UWB band. Energy/bit is one of the figure of merits (FoM) to characterize the performance of a device, system or method. However, it does not count communication reliability, so it is not proper quantity parameter for measuring the CRs' performance. Thus, alternative quantity parameter of energy per useful bit (EPUB) is used to characterize the UWB-based CR. EPUB can be expressed as equation (2.1).

$$EPUB = P / (R^*(1-BER))$$

$$(2.1)$$

where P is power consumption, R is data rate, and BER is bit error rate of the system.

The EPUB of the single channel UWB-based CR can be estimated with specific channel occupation rate by averaging the 1000 different EPUB values.

Figure 2.2: (a) An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) and (b) a single-channel 1Gb/s UWB-based CR with triangular BPSK pulses.

Fig. 2.3 (a) shows the communication fail rate with different channel occupancy cases. When the interferes takes frequency range by over 20% of the whole band, the probability that there is no contiguous 2.8GHz BW to accommodate the spectrum of the 1Gbps random triangular BPSK pulses is increased. The case of no 2.8GHz BW in the band is defined as communication fail since desired signal will be corrupted with interferes.

Figure 2.3: (a) Communication fail rate due to non-contiguous 2.8GHz BW and (b) EPUB except communication fail cases for the single-channel UWB-based CR along with channel occupancy rate.

Fig. 2.3(b) shows the average EPUB with various channel occupancy except the communication fail cases. The average EPUB value starts increasing over 20% channel occupancy even if the communication failure cases are not counted. If the interferers are located at lower frequency range, the center frequency of the UWB-based CR is allocated at higher frequency as shown in Fig. 2.2(b). If the carrier frequency is high, free space path loss is getting higher than that

of the low frequency. The loss reduces SNR of the received signal and increases bit error rate (BER) as shown if Fig. 2.4. Thus, transmitter should send the same data repeatedly in order to receive a big data like high definition pictures or movies, which increases energy consumption on the communication.

Figure 2.4: (a) Free path loss and (b) the SNR at the receiver with center frequency

## 2.4 Multi-Channel UWB-based Cognitive Radio

Multi-channel UWB-based CR is investigated to get high energy efficiency by using discrete channel spectrum aggregation technique. This one can be regarded as previous channelized receiver [8], but previous channelized radio has fixed carrier frequency for each channel. All channels of the multi-channel UWB-based CR operate independently, but they are not allocated at the same carrier frequency and have channel spacing to each other.

Fig. 2.5 shows how the multi-channel UWB-based CR uses discrete channels efficiently in order to allocate each carrier frequency at low frequency bands. In this example, triple-channel CR

is used and the null-to-null BW of each channel is 933MHz. Three sub-channel spectrums are allocated at lower frequency to compensate the free space path loss. Compared to single channel radio in Fig. 2.2(b), the allocated channel carrier frequencies are around 4.5GHz, 6GHz, and 8.5GHz in this example, which are lower than that of single channel radio example in Fig. 2.2(b).

Figure 2.5: An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) and with a triple-channel 1Gb/s UWB-based CR with triangular BPSK pulses.

Fig. 2.5(a) shows the same example with Fig. 2.2(a). Fig. 2.5(b) shows how the multi-channel UWB-based CR uses discrete channels efficiently in order to allocate each carrier frequency at low frequency bands. In this example, triple-channel CR is used and the null-to-null BW of each channel is 933MHz. Three sub-channel spectrums are allocated at lower frequency to compensate the free space path loss. Compared to single channel radio in Fig. 2.2(b), the allocated channel

carrier frequencies are around 4.5GHz, 6GHz, and 8.5GHz in this example, which are lower than that of single channel radio example in Fig. 2.2(b).

Figure 2.6: EPUB with the number of sub-channels in multi-channel UWB-based CR for 1Gb/s data rate with 30% spectrum utilization environment.

The statistical analysis is done to find out the optimum number of sub-channels of the multichannel UWB-based CR for 1Gb/s data rate with 30% spectrum utilization environment. The number of channels is varied from two to four since five channels cannot be implemented since FCC allows UWB radios to have 500MHz of -10dB BW. Fig. 2.6 shows that three or four subchannels have lower EPUB than that of two channel radio because less than 933MHz of null-tonull BW can be easily allocated at the lower frequency band under 30% channel occupancy environment. Three-channel radio is optimal as considering chip area for the multi-channel radio.

Figure 2.7: Performance comparison between a single-channel and a triple-channel UWB-based CRs in terms of EPUB except communication fail cases of the single-channel CR along with channel occupancy rate.

Fig. 2.7 compares performance in terms of EPUB between a single-channel and a singlechannel and a triple-channel CRs. In case of the single-channel radio, communication failure cases are not counted. The triple-channel radio does not have any the failure to find out three subchannels of about 933MHz. When the channel occupancy is below 20%, single channel radio is more energy efficient than the triple-channel radio since the carrier frequency of the single-channel radio can be located at lower frequency with high probability, and the single-channel radio has lesser circuitry than that of the triple-channel radio. However, when the channel occupancy goes over 20%, triple channel radio is much more energy efficient than the single-channel radio due to low probability of finding 2.4GHz contiguous vacant channel for the single channel radio. On the other hand, the probability to find out three discrete 933MHz contiguous channels is 100% even up to 50% channel occupancy case.

## 2.5 Adaptive BW Multi-Channel UWB-based Cognitive

## Radio

Figure 2.8: An example of the interferers with 30% channel occupation in MATLAB simulation (The carrier frequency is randomly decided with 10MHz resolution from 3.1GHz to 10.6GHz) with a triple-channel 1Gb/s UWB-based CR with triangular BPSK pulses and adaptive BW for respective sub-channels.

Fig. 2.8 illustrates adaptive BW triple-channel UWB based cognitive radio with 30% channel occupation. Each channel BW is adjustable in order to be allocated more efficiently lower frequency band than the constant BW triple-channel cognitive radio. In this example, the null-to-null BWs are about 700MHz, 1.2GHz, and 900MHz respectively. The allocated channel carrier frequencies are 3.45GHz, 4.4GHz, and 5.45GHz. Compared to the constant BW triple-channel cognitive radio in Fig. 2.5, the carrier frequencies of the adaptive BW triple-channel radio are lower than those of the constant BW triple-channel cognitive radio.

Three sub-channel spectrums are allocated at lower frequency to compensate the free space path loss. Compared to single channel radio in Fig. 2.2(b), the allocated channel carrier frequencies are around 4.5GHz, 6GHz, and 8.5GHz in this example, which are lower than that of single channel radio example in Fig. 2.2(b).

Figure 2.9: Comparison between constant BW and adaptive BW of the triple-channel CR in terms of EPUB with channel resolution.

Fig. 2.9 compares performance in terms of EPUB between a constant BW and an adaptive BW of the triple-channel CRs with channel resolution variation. The channel resolution defines the carrier frequency tuning step. When the resolution is 500MHz, an adaptive-BW radio has better performance since adaptive BW channel allows one or two of three channels to have less than 933MHz BW. The small spectrum channel can be more easily allocated at lower frequency band. However, when the resolution is less than 250MHz, there is no big difference between two radios because of FCC regulation. FCC limits the minimum -10dB BW of 500MHz for UWB radios.

Thus, if the channel resolution is less than 500MHz, adaptive BW technique lose its own flexibility to shrink channel bandwidth to use small vacant channel in lower frequency UWB band. Moreover, Adaptive BW technique requires different baseband clock frequencies for each channel, which increases design complexity and increases power consumption of the system.

# 2.6 Link Budget for Triple Channel UWB-basedCognitive Radio

It is possible to do a rough link budget calculation for the UWB-based CR. It is worth noting that a typical link budget found in a textbook [28] is often intended only for narrowband systems and has a frequency-based derivation implicitly including narrowband assumptions (e.g. that the signal bandwidth is small enough that it experiences similar fading to the center frequency).

Care must be taken if this narrowband link budget model is used, as certain terms like "center frequency" or "sensitivity" may appear misleading. An UWB signal may be defined to have a center frequency, but what happens at that frequency may not accurately represent what happens over the entire bandwidth. Additionally, impulse-UWB systems have receiver sensitivity, but it is in part a function of the pulse shape and is better represented as a received power over some period of time than as a simple, single number. An ultra-wideband link budget may be created by expanding the narrowband Friis power transmission formula [29] to be a function of frequency and integrating over the desired bandwidth [30].

Carrier to noise ratio (CNR) can be calculated as equation (2.2).

$$CNR = (P_{TX} + G_{TX} - L_{FS} + G_{RX}) / (N_{CH} + NF_{RX})$$

(2.2)

The  $P_{TX}$  is transmitter output power in dBm as equation (2.3).

$$P_{TX} = -41.3 dBm + 10* log_{10} (BW*\eta)$$

(2.3)

where  $\eta$  is spectrum filling ratio. For example,  $\eta$  of the rectangular spectrum is 1. Real spectrum shape cannot be rectangular, so  $\eta$  is always less than 1. One of the purpose of pulse shaping for UWB radios is to maximize the value of the parameter,  $\eta$ .

$G_{TX}$  and  $G_{RX}$  are transmitter antenna gain and receiver antenna gain in dBi respectively. L<sub>FS</sub> is free space loss in dB as equation (2.4).

$$L_{FS} = 20*\log_{10}(4\pi*d/c) \tag{2.4}$$

NCH is additive white Gaussian noise (AWGN) as equation (2.5)

$$NCH = -114dBm + 10*log_{10}(BW)$$

(2.5)

NFRS is the noise figure of the receiver chain.

(2.6)

Signal to noise ratio (SNR) can be calculated with CNR, BW, and data rate (R) as equation (2.6).

$$SNR = CNR*3dB_BW/R$$

Bit error rate with BPSK can be calculated with Q-function as equation (2.7).

$$BER = Q(sqrt(2*SNR))$$

(2.7)

Table 2.1 summarizes target link budget with the single-channel UWB-based CR for 1Gb/s data rate. This estimation can also be applied to the triple-channel UWB-based CR since the target performance is the same with the single-channel radio. In this analysis, packet based communication is used, and the packet length is 1kb. The worst pack loss is 10%. The target BER is less than  $1 \times 10^{-4}$  with 8.3dB SNR of the required SNR with BPSK modulation.

| Data Rate                         | 1 Gb/s                 |

|-----------------------------------|------------------------|

| EIRP                              | -41.3 dBm/MHz          |

| Communication Distance            | 1m                     |

| Required Min. null-to-null BW     | ~ 2.8 GHz              |

| 3dB BW                            | ~ 1 GHz                |

| Spectrum Filling Ratio (η)        | 0.6                    |

| Packet Length                     | 1 kb                   |

| Worst Packet Loss                 | 0.1                    |

| BER                               | < 1 × 10 <sup>-4</sup> |

| Required SNR with BPSK @ Receiver | 8.3 dB                 |

Table 2.1: Link budget of the single-channel UWB-based CR for 1Gb/s data rate

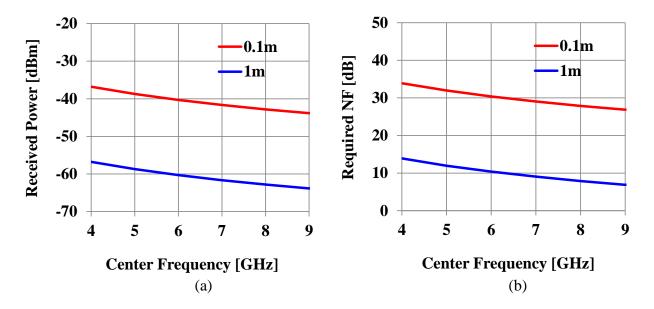

Target communication distance is from 0.1m to 1m, and the UWB-based CR uses whole UWB band from 3.1 to 10.6GHz. The result is plotted in Fig. 2.10 for different carrier frequencies from 4 to 9GHz with 0.1m and 1m communication distance. A single-channel UWB-based CR requires 2.8GHz null-to-null BW, so it can covers whole UWB band from 3.1 to 10.6GHz. This simple link budget predicts that the receiver sensitivity should be less than -63dBm and variable gain in receiver chain should provide 20dB gain variation. The required noise figure (NF) of the receiver chain is less than 7dB.

Figure 2.10: (a) Receiver sensitivity and (b) required noise figure of the receiver chain of the single-channel UWB-based CR with different carrier frequency and communication distance.

# 2.7 Group Delay of Multi-Channel UWB-basedCognitive Radio

One of the main challenges for a pulse-based system is the reliable generation of the timedomain pulses that meet the FCC's spectral mask. In addition to gain from the path loss reduction of the multi-channel UWB-based CR, it also mitigates the group-delay profile of a transmission path describing how the different spectral components of a signal arrive at the receiver, even in the absence of multipath fading and in a line-of-sight communication.

While designing a UWB antenna with a flat gain response and a good return loss is a challenge in itself, simultaneously maintaining a constant group delay over the signal BW only increases the difficulties [31]. Due to the group-delay distortion, the receiver performance can degrade significantly. Moreover, due to the changes in the location of the antenna and its surroundings, the channel transfer characteristics between the transmitter and the receiver change, and it is difficult to predict the group-delay profile of the complete communication path.

# Chapter 3. Dual-Resolution Analog Wavelet-based Wideband Spectrum Sensing

### 3.1 Spectrum Sensing in UWB band

Depending on the regimes of spectrum utilization, the front-end architecture of CRs can be quite different [32]. In early stage of CR network deployment, the spectrum utilization is expected to be low (around 5%) and there is little spectrum scarcity. In this case, the radio front-end starts with a tunable narrowband band pass filter (BPF) to search for one narrow band signal. Existing spectrum sensing techniques are largely categorized into energy detection [33] and cyclostationary feature detection [34]. When the spectrum utilization is medium (below 20%) resulting in medium spectrum scarcity, the radio front-end should adopt a wideband architecture to search over multiple frequency bands at a time. Multiple narrow band BPFs can be employed to form a filter bank for wideband, sensing [32], but this architecture requires an increased, number of components and the filter range of each BPF is preset. In future networks where spectrum utilization is high (above 20%), the significant spectrum scarcity would call for different spectrum sharing mechanisms for the UWB based cognitive radios, which in turn entail different sensing tasks for spectrum overlay.

### 3.2 Wideband Spectrum Sensing

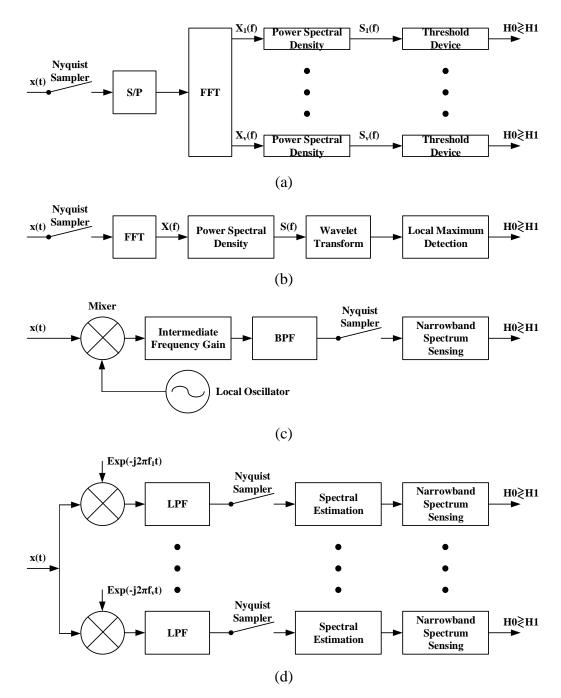

A simple approach to wideband spectrum sensing is to directly acquire the wideband signal using a high sampling rate ADC and then use digital signal processing techniques to detect spectral opportunities as shown in Fig. 3.1(a). Fast Fourier transform (FFT) is used to convert the wideband signals to the frequency domain. Finally, spectral opportunities were detected using binary hypotheses tests, where  $H_0$  denotes the absence of interferers and  $H_1$  denotes the presence of interferers. The optimal detection threshold was jointly chosen by using optimization techniques. Such an algorithm can achieve better performance than the single-band sensing case [35].

A wavelet-based spectrum sensing algorithm models the power spectral density (PSD) of the wideband spectrum as a train of consecutive frequency sub-bands, where the PSD is smooth within each sub-band but exhibits discontinuities and irregularities on the border of two neighboring sub-bands. The wavelet transform was then used to locate the singularities of the wideband PSD, and the wideband spectrum sensing was formulated as a spectral edge detection problem, as shown in Fig. 3.2(b) [36].

However, special attention should be paid to the signal sampling procedure. In these algorithms, sampling signals should follow Shannon's celebrated theorem: the sampling rate must be at least twice the maximum frequency present in the signal (known as Nyquist rate) in order to avoid spectral aliasing. Suppose that the wideband signal has frequency range 3~11 GHz; it should be uniformly sampled by a standard ADC at or above the Nyquist rate, 22 GHz, which will be unaffordable for next generation mobile networks.

Therefore, sensing wideband spectrum presents significant challenges in building sampling hardware that operates at a sufficiently high rate and designing high-speed signal processing algorithms. With current hardware technologies, high-rate ADCs with high resolution and reasonable power consumption (e.g., 22GHz sampling rate with 16 bits resolution) are difficult to implement. Even if it becomes true, the real-time digital signal processing of sampled data could be very expensive.

One naive approach that could relax the high sampling rate requirement is to use superheterodyne (frequency mixing) techniques that "sweep" across the frequency range of interest, as shown in Fig. 3.1(c). A local oscillator (LO) produces a sine wave that mixes with the wideband signal and down-converts it to a lower frequency. The down-converted signal is then filtered by a band pass filter (BPF), after which existing narrowband spectrum sensing techniques can be applied. This sweep-tune approach can be realized by using either a tunable BPF or a tunable LO. However, this approach is often slow and inflexible due to the sweep-tune operation.

Another solution is the filter bank algorithm as shown in Fig. 3.1(d) [37]. A bank of prototype filters (with different shifted central frequencies) was used to process the wideband signal. The baseband can be directly estimated by using a prototype filter, and other bands can be obtained through modulating the prototype filter. In each band, the corresponding portion of the spectrum for the wideband signal was down-converted to baseband and then low-pass filtered. This algorithm can therefore capture the dynamic nature of wideband spectrum by using low sampling rates. Unfortunately, due to the parallel structure of the filter bank, the implementation of this algorithm requires a large number of RF components.

Figure 3.1: Block diagrams for Nyquist wideband sensing algorithms of (a) multiband joint detection, (b) wavelet detection, (c) sweep-tune detection, and (d) filter-band detection.

Due to the drawbacks of high sampling rate or high implementation complexity in Nyquist systems, sub-Nyquist approaches are drawing more and more attention in both academia and

industry. Sub-Nyquist wideband sensing refers to the procedure of acquiring wideband signals using sampling rates lower than the Nyquist rate and detecting spectral opportunities using these partial measurements. Two important types of sub-Nyquist wideband sensing are compressive sensing-based wideband sensing and multichannel sub-Nyquist wideband sensing.

Compressive sensing is a technique that can efficiently acquire a signal using relatively few measurements, by which unique representation of the signal can be found based on the signal's sparseness or compressibility in some domain. As the wideband spectrum is inherently sparse due to its low spectrum utilization, compressive sensing becomes a promising candidate to realize wideband spectrum sensing by using sub-Nyquist sampling rates [38]. This technique used fewer samples closer to the information rate, rather than the inverse of the bandwidth, to perform wideband spectrum sensing. After reconstruction of the wideband spectrum, wavelet-based edge detection was used to detect spectral opportunities across wideband spectrum. However, compressive sensing has concentrated on finite-length and discrete-time signals. The analog compressive sensing [39] is proposed with an analog-to-information converter (AIC), which could be a good basis for the above-mentioned algorithms. As shown in Fig. 3.2(a), the AIC-based model consists of a pseudo-random number generator, a mixer, an accumulator, and a low-rate sampler. The pseudo-random number generator produces a discrete-time sequence that demodulates the signal x(t) by a mixer. The accumulator is used to sum the demodulated signal for 1/w s, while its output signal is sampled using a low sampling rate. After that, the sparse signal can be directly reconstructed from partial measurements using compressive sensing algorithms. Unfortunately, it has been identified that the performance of the AIC model can easily be affected by design imperfections or model mismatches.

Figure 3.2: Block diagrams for sub-Nyquist wideband sensing algorithms of (a) analog-toinformation converter based wideband sensing, (b) modulated wideband converterbased wideband sensing, (c) multi-coset sampling-based wideband sensing, and (d) multi-rate sub-Nyquist sampling-based wideband sensing.

To circumvent model mismatches, a modulated wideband converter (MWC) model was proposed in [40] by modifying the AIC model. The main difference between MWC and AIC is that MWC has multiple sampling channels, with the accumulator in each channel replaced by a general low-pass filter. One significant benefit of introducing a parallel channel structure in Fig. 3.2(b) is that it provides robustness against the noise and model mismatches. In addition, the dimension of the measurement matrix is reduced, making the spectral reconstruction more computationally efficient.

An alternative multichannel sub-Nyquist sampling approach is multi-coset sampling, as shown in Fig. 3.2(c). Multi-coset sampling is equivalent to choosing some samples from a uniform grid, which can be obtained using a sampling rate fs higher than the Nyquist rate. The uniform grid is then divided into blocks of m consecutive samples, and in each block v (v < m) samples are retained, while the rest of samples are skipped. Thus, multi-coset sampling is often implemented by using v sampling channels with sampling rate of fs/m, with different sampling channels having different time offsets. To obtain a unique solution for the wideband spectrum from these partial measurements, the sampling pattern should be carefully designed. In [41], some sampling patterns were proved to be valid for unique signal reconstruction. The advantage of the multi-coset approach is that the sampling rate in each channel is m times lower than the Nyquist rate. Moreover, the number of measurements is only (v–m)th of that in the Nyquist sampling case. One drawback of the multi-coset approach is that the channel synchronization should be met such that accurate time offsets between sampling channels are required to satisfy a specific sampling pattern for robust spectral reconstruction.

To relax the multichannel synchronization requirement, an asynchronous multi-rate wideband sensing approach was studied in [42]. In this approach, sub-Nyquist sampling was induced in each sampling channel to wrap the sparse spectrum occupancy map onto itself; the sampling rate can therefore be significantly reduced. By using different sampling rates in different sampling channels as shown in Fig. 3.2(d), the performance of wideband spectrum sensing can be improved. Specifically, in the same observation time, the numbers of samples in multiple sampling channels are chosen as different consecutive prime numbers. Furthermore, as only the magnitudes of sub-Nyquist spectra are of interest, such a multi-rate wideband sensing approach does not require perfect synchronization between multiple sampling channels, leading to easier implementation.

# 3.3 An Analog Wavelet-based Wideband Spectrum Sensing

In [38], wavelets are used for detecting edges in the PSD of a wideband channel. Once the edges, which correspond to transitions from an occupied band to an empty band or vice versa, are detected, the powers within bands between two edges are estimated. Using this information and edge positions, the frequency spectrum can be characterized as occupied or empty in a binary fashion. The assumptions made in [38], however, needs to be relaxed for building a practical sensing algorithm. The method proposed in [38] is extended in [43] by using sub-Nyquist sampling. Assuming that the signal spectrum is sparse, sub-Nyquist sampling is used to obtain a coarse spectrum knowledge in an efficient way.

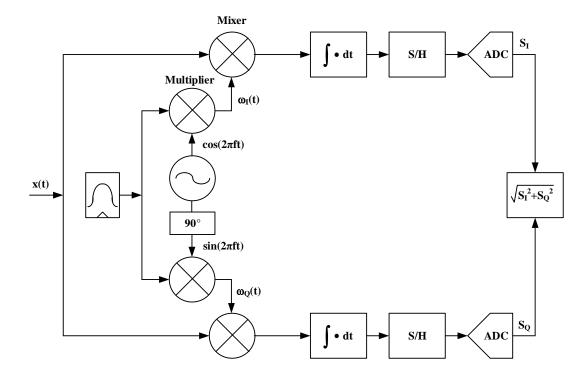

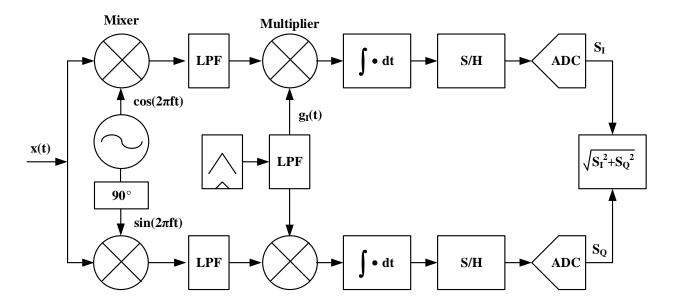

Analog implementation of wavelet-transform based sensing is proposed in [44] for wideband sensing. Multi-resolution spectrum sensing is achieved by changing the basis functions without severe modification to sensing circuitry as shown in Fig. 3.3. The basis function is changed by adjusting the wavelet's pulse width and carrier frequency. Hence, fast sensing is possible by focusing on the frequencies with active transmissions after an initial rough scanning. Fig. 3.3 shows the functional block diagram of the suggested analog multi resolution spectrum sensing (MRSS) technique. Building blocks consists of a wavelet waveform generator, multipliers, and integrators for computing correlation values, and low speed ADCs to digitize the calculated analog

correlation values. Since the MRSS processing is performed in the analog domain, low power and real time operations can be realized. Moreover, a wavelet pulse provides a band pass filtering effect for noisy RF input signals. Thus, image and noise rejection filters are not needed. The square root of S<sub>I</sub> and S<sub>Q</sub> that are the discrete values represents the spectral density at a specific frequency.

Figure 3.3: Functional block diagram of the analog wavelet-based spectrum sensing

The concept was implemented at VLSI [45, 46]. The basis function was generated by a digital window generator (DWG), which is one of the highest power consuming blocks in the system. The digital window generator (DWG) generates a window waveform with flexible durations. It is composed of a static RAMs (SRAMs), a DAC, and an LP. Changing the RAM address generates the window raw data for the DAC. The LPF reconstructs the digital window signal to an analog form by removing the harmonics of the clock frequencies from the DAC. The DWG consumes 18mW [45].

# 3.4 Spectrum Sensing Resolution for a UWB-basedCognitive Radios

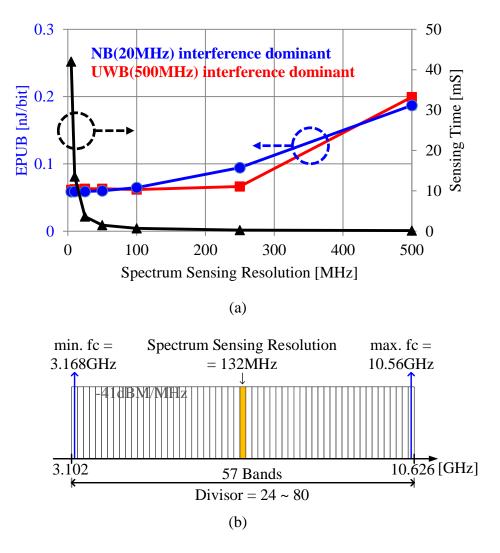

The resolution of the spectrum sensing can be decided by the trade-off between the spectrum utilization efficiency and the total sensing time. The channel utilization efficiency can be defined by EPUB of the cognitive radio. The narrower the resolution, the more efficient the usage of vacant spectrum can be. Narrow resolution, however, increases spectrum sensing time exponentially as shown in Fig. 3.4(a). The sensing time can be calculated as equation (3.1).

$$t_{sensing} = \left(\frac{f_{end} - f_{start}}{f_{resolution}} + 1\right) \times \left(N_{AVG} \times (t_{window} + t_{sw}) + t_{settling}\right)$$

(3.1)

where  $(f_{end} - f_{start})$  is the frequency sweep range of the phase locked loop (PLL), fstep is the amount of frequency change in PLL, N<sub>AVG</sub> is the number of averages at one PLL frequency, t<sub>window</sub> is the window duration as derived from wavelet window effect, tsw is a timing margin between consecutive windows, and t<sub>settling</sub> is maximum settling time of the PLL.

Statistical analysis including a narrow 40 MHz BW and a wide 500 MHz BW interferers shows that a 100 MHz resolution is approximately optimal in terms of signal detection and sensing time with 30% spectrum occupancy. The 132MHz resolution is chosen by considering the spectrum usage and the divider depth of the PLL in the UWB band. The minimum frequency of the PLL is 3.168 GHz, and the maximum is 10.56GHz with 132MHz spectrum sensing resolution, which leads to 57 bands in UWB band as shown in Fig. 3.4(b).

Figure 3.4: (a) Statistical Analysis in terms of the spectrum utilization efficiency and the sensing time, and (b) the quantized spectrum sensing resolution and maximum and minimum carrier frequency of the PLL.

Figure 3.5: Functional block diagram of the modified analog wavelet-based spectrum sensing

The Analog wavelet-based spectrum sensing is modified to separate local oscillator (LO) path and pulse template wave path as shown in Fig. 3.5. After a down-conversion mixer, a LPF is added to eliminate high frequency output of the mixer. The mathematical function is the exactly same with the previous architecture of [44].

# 3.5 Triangular waveform generation with Source

# Follower LPF for Side-lobe Reduction

#### 3.5.1 Characteristics of Triangular Waveform