# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

# **Title**

Programming Language Techniques for Improving ISA and HDL Design

# **Permalink**

https://escholarship.org/uc/item/7sz5r3vd

# **Author**

Christensen, Michael Alexandre

# **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# University of California Santa Barbara

# Programming Language Techniques for Improving ISA and HDL Design

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Computer Science

by

Michael Alexandre Christensen

# Committee in charge:

Professor Ben Hardekopf, Chair Professor Timothy Sherwood Professor Jonathan Balkind

December 2021

| Γhe Di | ssertation of Michael Alexandre Christensen is approv |

|--------|-------------------------------------------------------|

|        |                                                       |

|        | Professor Timothy Sherwood                            |

|        |                                                       |

|        | Professor Jonathan Balkind                            |

|        |                                                       |

|        | Professor Ben Hardekopf, Committee Chair              |

December 2021

# Programming Language Techniques for Improving ISA and HDL Design

Copyright © 2021

by

Michael Alexandre Christensen

Dedicated to my wife, Crystal, and my children, Brooklyn, Rhys, and Ira, for the joy they bring to my life.

# Acknowledgements

The past six years have been the best of my life. They were also a lot of work, and I have many people to thank for helping me get here:

- **Ben Hardekopf** For teaching me how to do research, giving me the freedom to discover my interests, and being supremely patient as I had three children along the way.

- **Tim Sherwood** For your unparalleled advice and encouragement. You helped me believe that my ideas were good and that I could finish my PhD.

- **Jonathan Balkind** For your invaluable insights into where the field is and where it's headed. You expanded my vision of what's possible when we use PL to solve computer architecture problems.

- **Rich Wolski** For your incredible passion for systems. I'm grateful to have been able to learn from, TA for, and work with you during the first years of my PhD.

- **Joseph McMahan** For being a great role model and even greater friend. I feel extremely lucky to have been able to work alongside you on Zarf starting my first year—thanks for everything.

- **Kyle Dewey** For being a mentor with a work ethic like no other. You were an anchor and example, always willing to lend a commiserating ear through the lows and rejoice in the highs of my PhD experience.

- **George Tzimpragos** For all the time you spent teaching me about the world of superconductor electronics. Your creativity and the depth and breadth of your knowledge continually amaze me.

- **Mehmet Emre** For your enviable ability to grok it all. We never have a conversation where I don't learn something new from you. Project Neptune forever.

- **Lawton Nichols** For teaching me the importance of consistency and perseverance. You motivate me to continue running, learning, and trying new things.

- Miroslav (Mika) Gavrilov For being the sweetest, most caring person I know. You're still Uncle Mika to my children, and they now know the cosmic entities of Lovecraft (and their alphabet) thanks to you.

- **The PL Lab** Harlan Kringen, Zach Sisco, Madhukar Kedlaya, Davina Zamanzadeh, and everyone not already mentioned, past and present, for the energy and creativity you brought to the lab.

- **The Arch Lab** Deeksha Dangwal, Jennifer Volk, Weilong Cui, and everyone not already mentioned, past and present, for helping a PL person feel welcome and for guiding me through the details.

- **John Shalf and George Michelogiannakis** For the opportunity to work on the interesting computer architecture problems of superconductor electronics.

- **Christophe Giraud-Carrier, Scott Burton, and Ryan Farrell** For introducing me to research and guiding my decision to attend graduate school.

- **Janis Smith** For being the best mother-in-law anyone could ask for.

- **My Parents** For your examples of hard work and for the many sacrifices you made that enabled me to pursue my passions.

- **Crystal** For your unwavering love and support through all of this. You're my best friend and continual source of strength, and I'm grateful to get to navigate this life with you.

# **Curriculum Vitæ**Michael Alexandre Christensen

| Education    |                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 2015 – 2021  | <ul> <li>Ph.D. in Computer Science, University of California, Santa Barbara</li> <li>M.S. in Computer Science awarded in March 2021</li> </ul> |

| 2007 – 2013  | <ul><li>B.S. in Computer Science, Brigham Young University, Provo</li><li>Minor in Mathematics</li></ul>                                       |

| Courses TA'd |                                                                                                                                                |

| Winter 2020  | UCSB CS 64: Computer Organization and Logic Design                                                                                             |

| Fall 2019    | UCSB CS 170: Operating Systems                                                                                                                 |

| Spring 2019  | UCSB CS 138: Formal Languages and Automata                                                                                                     |

| Winter 2017  | UCSB CS 162: Programming Languages                                                                                                             |

| Winter 2016  | UCSB CS 162: Programming Languages                                                                                                             |

| Fall 2015    | UCSB CS 64: Computer Organization and Logic Design                                                                                             |

| Winter 2013  | BYU CS 478: Machine Learning and Data Mining                                                                                                   |

| Experience   |                                                                                                                                                |

| 2015 – 2021  | Research Assistant, UCSB (Programming Languages Lab)                                                                                           |

| 2020 – 2021  | Research Assistant, Lawrence Berkeley National Lab<br>(Computer Architecture Group)                                                            |

| Summer 2020  | Software Engineer Intern, Facebook (Hack Language Team)                                                                                        |

| Summer 2019  | Software Engineer Intern, Facebook (Disaster Recovery Team)                                                                                    |

| 2014 – 2015  | Software Engineer II, Dell EMC (NetWorker Team)                                                                                                |

| 2013         | Research Assistant, BYU Data Mining Lab                                                                                                        |

|              |                                                                                                                                                |

### **Publications**

Summer 2012

**Michael Christensen**, Georgios Tzimpragos, Harlan Kringen, Jennifer Volk, Timothy Sherwood, Ben Hardekopf. "PyLSE: A Pulse-Transfer Level Language for Superconductor Electronics," *Under review*.

Software Engineer Intern, SerialTek

**Michael Christensen**, Timothy Sherwood, Jonathan Balkind, Ben Hardekopf. "Wire Sorts: A Language Abstraction for Safe Hardware Composition," *Proceedings of the 42nd ACM SIGPLAN International Conference on Programming Language Design and Implementation* (**PLDI**), June 2021. Virtual, Canada.

**Michael Christensen**, Joseph McMahan, Lawton Nichols, Jared Roesch, Timothy Sherwood, Ben Hardekopf. "Safe Functional Systems through Integrity Types and Verified Assembly," *Theoretical Computer Science*, 2021.

Joseph McMahan, **Michael Christensen**, Kyle Dewey, Ben Hardekopf, Timothy Sherwood. "Bouncer: Static Program Analysis in Hardware," *Proceedings of the 2019 ACM/IEEE 46th Annual International Symposium on Computer Architecture* (**ISCA**), June 2019. Phoenix, AZ, USA.

Joseph McMahan, **Michael Christensen**, Lawton Nichols, Jared Roesch, Sung-Yee Guo, Ben Hardekopf, and Timothy Sherwood. "An Architecture for Analysis," *IEEE Micro: Top Picks from the 2017 Computer Architecture Conferences* (**IEEE Micro - Top Picks**), vol. 38, no. 3, pp 107-115, May/June 2018.

Joseph McMahan, **Michael Christensen**, Lawton Nichols, Jared Roesch, Sung-Yee Guo, Ben Hardekopf, and Timothy Sherwood. "An Architecture Supporting Formal and Compositional Binary Analysis," *Proceedings of the Twenty-Second International Conference on Architectural Support for Programming Languages and Operating Systems* (**ASPLOS**), April 2017. Xi'an, China.

### Awards and Service

| June 2021   | Outstanding Teaching Assistant, Computer Science Department, UCSB (2020 – 2021 Academic Year) |

|-------------|-----------------------------------------------------------------------------------------------|

| June 2016   | Student Volunteer Co-Captain, PLDI                                                            |

| 2008 - 2010 | Volunteer Church Representative, The Church of Jesus Christ of                                |

|             | Latter-Day Saints (San José, Costa Rica)                                                      |

### **Abstract**

Programming Language Techniques for Improving ISA and HDL Design

by

### Michael Alexandre Christensen

Despite all the effort spent in testing, analyzing, and formally verifying software, a program is ultimately only as correct as the underlying hardware on which it runs. As processors become more performant, their microarchitectures become increasingly complex; this complexity often manifests in instruction set architectures (ISAs) that are bloated, imprecise, and therefore unamenable to formal verification. The ISA itself is realized as a hardware implementation written in a hardware description language (HDL). Unfortunately, modern HDLs lack the expressive, composable programming abstractions we've come to expect of traditional high-level programming languages, hampering innovation and correct-by-construction hardware design. Furthermore, the unique characteristics of emerging technologies like superconductor electronics (SCE) require us to rethink the HDLs we use and retool the entire design, simulation, and verification stack.

This thesis shows how various programming language techniques, applied to the realm of computer architecture and hardware design, help address these issues. I show that abstraction, formal semantics, and type theory can be used to create an ISA that is precise, concise, and amenable to formal reasoning by both human and machine. I also show how HDLs can better support composability via formalized notions of intermodular communication and dependency. Finally, I show that we can improve SCE behavioral modeling and system design using a new automata-based pulse-transfer level language.

# **Contents**

| Cı         | Curriculum Vitae vii |                                                                        |     |

|------------|----------------------|------------------------------------------------------------------------|-----|

| <b>A</b> l | bstrac               | et                                                                     | ix  |

| Li         | st of                | Figures                                                                | xii |

| Li         | st of                | Tables                                                                 | xiv |

| 1          | Intr                 | oduction                                                               | 1   |

|            | 1.1                  | Thesis Statement                                                       | 3   |

|            | 1.2                  | Organization of This Document                                          | 3   |

| 2          | Zari                 | e: An Architecture Supporting Formal and Compositional Binary Analysis | 6   |

|            | 2.1                  | Introduction                                                           | 6   |

|            | 2.2                  | Related Work                                                           | 10  |

|            | 2.3                  | Hardware Architecture and ISA                                          | 15  |

|            | 2.4                  | System Software                                                        | 24  |

|            | 2.5                  | ISA Semantics                                                          | 29  |

|            | 2.6                  | Verification                                                           | 38  |

|            | 2.7                  | Evaluation                                                             | 58  |

|            | 2.8                  | Conclusion                                                             | 60  |

| 3          | Bou                  | ncer: Static Program Analysis in Hardware                              | 62  |

|            | 3.1                  | Introduction                                                           | 62  |

|            | 3.2                  | Hardware Static Analysis                                               | 65  |

|            | 3.3                  | Static Analysis Strategy                                               | 71  |

|            | 3.4                  | Algorithm for Analysis                                                 | 92  |

|            | 3.5                  | BEU Implementation                                                     | 96  |

|            | 3.6                  | Provable Non-bypassability                                             | 101 |

|            | 3.7                  | Evaluation                                                             |     |

|            | 3.8                  | Related Work                                                           | 108 |

|            | 3.9                  | Conclusion                                                             | 111 |

| 4  | Wir   | e Sorts: A Language Abstraction for Safe Hardware Composition      | 113   |

|----|-------|--------------------------------------------------------------------|-------|

|    | 4.1   | Introduction                                                       | . 113 |

|    | 4.2   | Motivation and Related Work                                        |       |

|    | 4.3   | Wire Sorts and Well-Connectedness                                  |       |

|    | 4.4   | Implementation of Modular Well-Connectedness Checks                |       |

|    | 4.5   | Evaluation                                                         | . 138 |

|    | 4.6   | Conclusion                                                         | . 148 |

| 5  | PyL   | SE: A Pulse-Transfer Level Language for Superconductor Electronics | 149   |

|    | 5.1   | Introduction                                                       | . 149 |

|    | 5.2   | Defining Computation on Pulses                                     | . 151 |

|    | 5.3   | A Language Abstraction for Superconductor Electronics              | . 155 |

|    | 5.4   | PyLSE Language Design                                              | . 164 |

|    | 5.5   | Evaluation                                                         | . 177 |

|    | 5.6   | Related Work                                                       | . 195 |

|    | 5.7   | Conclusion                                                         | . 196 |

| 6  | Con   | clusions and Future Work                                           | 198   |

| A  | Zari  | f and Bouncer                                                      | 200   |

|    | A.1   | Small-Step Semantics                                               | . 200 |

|    |       | Big-Step Lazy Semantics for Typed Zarf                             |       |

| Bi | bliog | raphy                                                              | 211   |

# **List of Figures**

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11 | High-level Zarf system architecture9Abstract syntax of Zarf's functional ISA18Compiling high-level assembly into a Zarf binary22ECG filter process25Big-step semantics for Zarf's functional ISA30Big-step semantics helpers for Zarf's functional ISA31Coq extraction of verified application components39Integrity typing rules49Integrity typing rules helpers50Joining two types50Subtyping rules51 |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

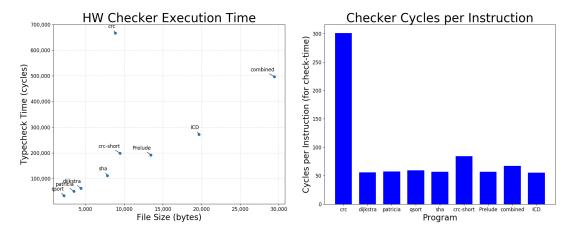

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                               | The Binary Exclusion Unit as a gatekeeper                                                                                                                                                                                                                                                                                                                                                               |

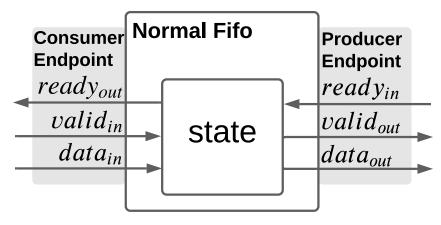

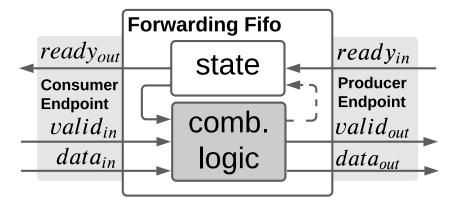

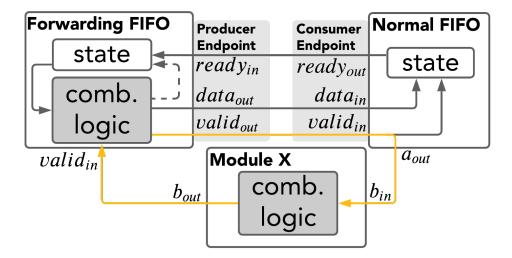

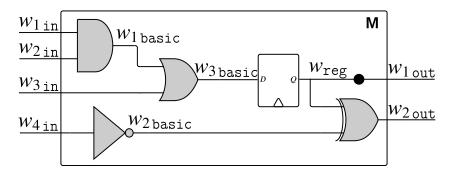

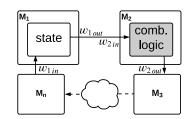

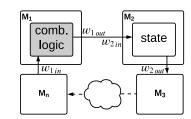

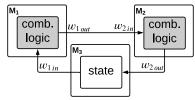

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                 | Normal FIFO queue                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1<br>5.2                                                                  | Abstraction levels in semiconducting and superconducting                                                                                                                                                                                                                                                                                                                                                |

| 5.3  | Schematic and Mealy machine of the Synchronous And Element 153                       |

|------|--------------------------------------------------------------------------------------|

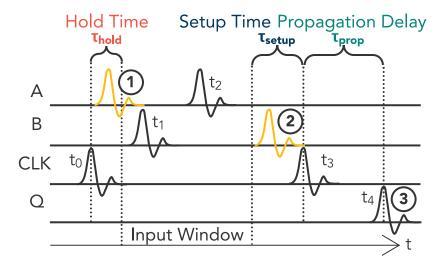

| 5.4  | Waveform with timing constraints of the Synchronous And Element 154                  |

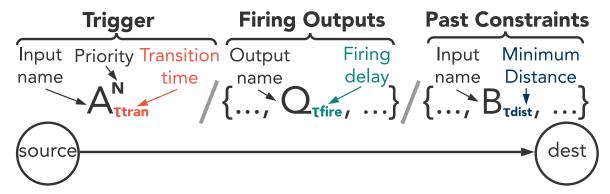

| 5.5  | Anatomy of a PyLSE Machine transition                                                |

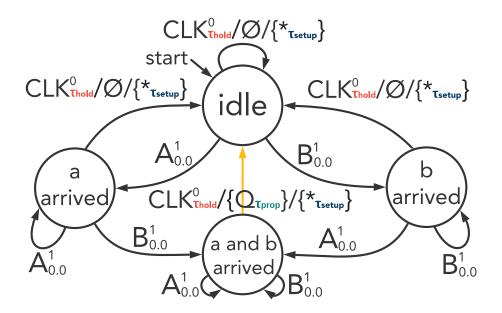

| 5.6  | PyLSE Machine for the Synchronous And Element                                        |

| 5.7  | Transition, Dispatch, Trace, and Network relations of the PyLSE Machine 160          |

| 5.8  | Synchronous And Element PyLSE code                                                   |

| 5.9  | Hole description of a memory                                                         |

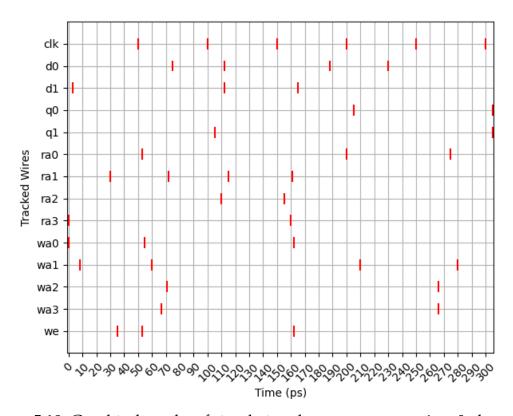

| 5.10 | Simulating the memory Functional class                                               |

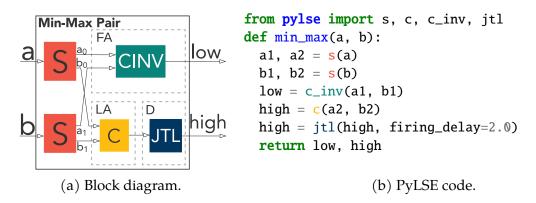

| 5.11 | Min-max pair PyLSE code and block diagram                                            |

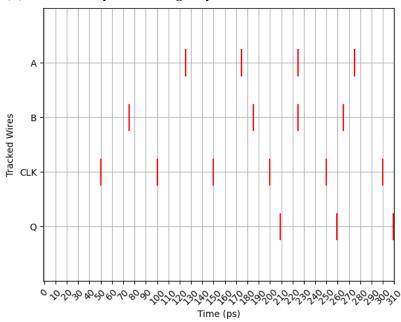

| 5.12 | Simulation of the Synchronous And Element in PyLSE 171                               |

| 5.13 | Example of error reporting during a PyLSE simulation                                 |

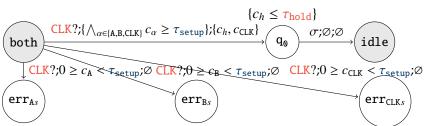

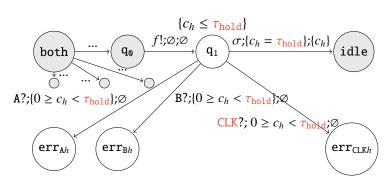

| 5.14 | Expanding a PyLSE Machine transition into TA transitions                             |

| 5.15 | Block diagram of an eight-input bitonic sorter                                       |

|      | <i>N</i> -input bitonic sorter written in PyLSE                                      |

|      | 8-input bitonic sorter implementation written in PyLSE 181                           |

| 5.18 | SPICE vs. PyLSE simulation results for the C Element                                 |

| 5.19 | SPICE vs. PyLSE simulation results for the Inverted C Element 183                    |

|      | SPICE vs. PyLSE simulation results for the min-max pair                              |

| 5.21 | SPICE vs. PyLSE simulation results for the eight-input bitonic sorter. $$ . $$ . 185 |

| 5.22 | PyLSE in the SCE Design Flow                                                         |

| A 1  | A1                                                                                   |

|      | Abstract syntax for the small-step semantics of Zarf's functional ISA 200            |

|      | Semantic domains for the small-step semantics of Zarf's functional ISA 201           |

|      | Semantic domains for the big-step semantics                                          |

| A.4  | Big-step lazy semantics of Zarf's functional ISA                                     |

# **List of Tables**

| 2.1               | Resource usage of Zart and basic MicroBlaze                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3 | 21 conditions requiring dynamic checks absent static type checking 68 Breakdown of states in the Binary Exclusion Unit's state machine 99 Examples of how the Binary Exclusion Unit identifies erroneous code 106 |

| 4.2<br>4.3        | Wire sorts of module ports for a subset of BaseJump STL                                                                                                                                                           |

| 5.1<br>5.2<br>5.3 | PyLSE encapsulating and support functions used in example code 172 Simulation times of PyLSE vs. SPICE-level models 184 Comparison of PyLSE Machines and UPPAAL-flavored Timed Automata 191                       |

| A.1               | Small-step state transition rules of Zarf's functional ISA                                                                                                                                                        |

# Chapter 1

# Introduction

Our programs are only as correct as the machines on which they run. This correctness is often taken for granted, with the software realm siloed off from the hardware realm and often oblivious to the intricacies of the processor running the code. However, if we are to truly tackle the spectre of full-stack program verification, we must adequately include our hardware in the discussion. In this thesis, I argue that to do so, we must change how we approach hardware design both *above and below the microarchitecture* as well for emerging technologies *beyond* CMOS.

Above the Microarchitecture The separation of concerns between hardware and software has given the hardware realm the freedom to focus on creating machines that meet particular power, efficiency, area, and security targets, all while interacting with software via the same interface. This interface, the instruction set architecture (ISA), serves as both an *abstraction* and a *contract* by presenting a set of assembly instructions and a specification (often in thousands of pages of plain prose and pseudocode) of how each instruction affects machine behavior. As processors have become increasingly performant, their microarchitectures have become increasingly large and complex;

unfortunately, this complexity has permeated the ISA abstraction boundary, manifesting as ISAs that are buggy, imprecise, ill-defined, and hard to reason about, model, and simulate.

Below the Microarchitecture ISAs are in turn implemented as processor microarchitectures using a hardware description language (HDL); these processors are just one example of *intellectual property* (IP) blocks—reusable hardware components, packaged into IP catalogs, that are then connected together. Systems on chip (SOCs) and manycore processors integrate hundreds of these components, and as design teams become larger and more remote, it becomes more important that these IPs, especially proprietary IPs, have detailed and precise interface specifications. Naively connecting hardware blocks together leads to bugs which are difficult to diagnose when looking at the interfaces alone and which are especially difficult to debug after synthesis. Thus, composability of IP becomes a major issue, and modern HDLs lack effective abstractions for dealing with this intermodular composability and communication beyond simple abstractions like the "module" associating "input" and "output" wires with each other via gates. Modern high-level programming languages, on the other hand, have many mechanisms supporting effective modularity, abstraction, and dependency specification, and we can use these techniques to be more precise about the surprisingly complex requirements imposed on the use of data and what compositions lead to well-defined digital designs.

**And Beyond** As we enter a post-Moore, post-Dennard scaling era in search of additional power, speed, and efficiency, we must to look beyond CMOS toward emerging technologies like superconductor electronics (SCE). The unique characteristics of SCE, such as its pulse-based information encoding and stateful gate primitives, require im-

proved language abstractions and that we rethink the entire design, simulation, and verification stack. Programming language theory again provides us insight into how we can use better mathematical foundations, such as automata theory, for improved SCE languages and simulation frameworks.

We need to ensure the correctness of the entire stack, from source code to silicon<sup>1</sup> die, and this thesis seeks to show that the precision of programming language theory can be effectively applied on the hardware side. This brings me to my thesis statement:

# 1.1 Thesis Statement

The application of programming language principles like abstraction and formal semantics can make it easier to write verifiably correct and secure hardware, tangibly improving both the interface which software uses to communicate with the machine (the *instruction set architecture*) and the means by which we design the machine itself (the *hardware description language*).

# 1.2 Organization of This Document

This thesis is structured as follows:

Chapter 2 This chapter discusses Zarf, an ISA resembling the untyped lambda calculus designed to bring the assembly closer to frameworks used for formal program analysis and reasoning, and which has been implemented as an FPGA prototype running an embedded medical application. I show that the architecture allows for the formal verification of multiple properties of the end-to-end system, including a proof

<sup>&</sup>lt;sup>1</sup>Niobium for SCE.

of correctness of the assembly-level implementation of the core algorithm, the integrity of trusted data via a non-interference proof, and a guarantee that our prototype meets critical timing requirements. It is based on work published in ASPLOS 2017 (Citation: [1]; DOI: 10.1145/3037697.3037733; © 2017 ACM), IEEE Micro Top Pick 2018 (Citation: [2]; DOI: 10.1109/MM.2018.032271067; © 2018 IEEE), and the Journal of Theoretical Computer Science 2021 (Citation: [3]; DOI: 10.1016/j.tcs.2020.09.039; © 2021 Elsevier) and which appeared as a portion of the PhD thesis of Joseph McMahan [4], co-author on the aforementioned publications. It is based on work supported by the National Science Foundation under Grant No. 1239567, 1162187, and 1563935.

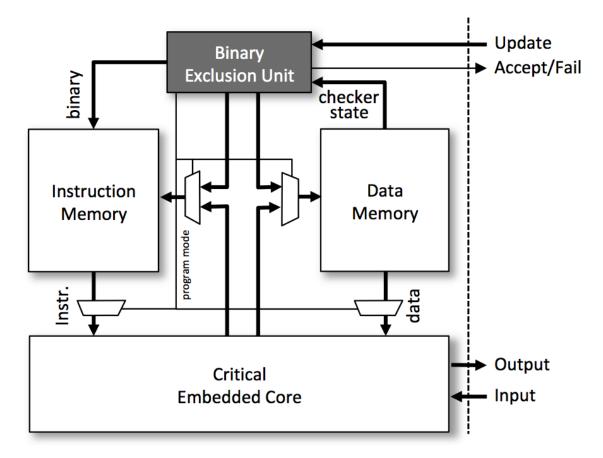

Chapter 3 This chapter discusses Bouncer, which extends Zarf with let-polymorphism to make it easier to correctly write and reason about Zarf binaries. Using special-purpose hardware, I show that we can use static analysis to prevent all program binaries with memory errors, invalid control flow, and other undesirable properties from ever being loaded onto the embedded program store. We can check this in a streaming and verifiably non-bypassable way, directly in hardware, resulting in a system that is small, efficient, and which guarantees freedom from many security and safety concerns. It is based on work published in ISCA 2019 (Citation: [5]; DOI: 10.1145/3307650.3322256; © 2019 ACM) and which also appeared as a portion of the aforementioned thesis by Joseph McMahan. It is based on work supported by the National Science Foundation under Grants No. 1740352, 1730309, 1717779, 1563935, 1350690, and a gift from Cisco Systems.

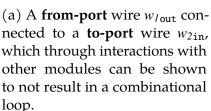

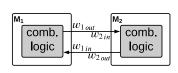

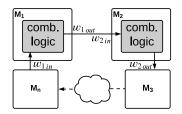

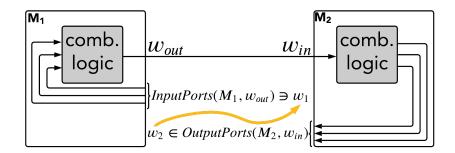

**Chapter 4** This chapter discusses **Wire Sorts**, an abstraction that makes it impossible to create certain classes of erroneous digital design and makes it easier to express interface requirements and compose IP. Using a taxonomy of sorts to soundly abstract even

complex combinational dependencies of arbitrary hardware modules, I show that we can facilitate modularity in digital design by escalating problematic aspects of module input/output interaction to the language-level interface specification. I also show how these sorts have been formalized and proven sound and demonstrate that they can be applied and even inferred automatically at scale via an examination of a variety of large open-source digital designs and libraries. It is based on work published in PLDI 2021 (Citation: [6]; DOI: 10.1145/3453483.3454037; © 2021 ACM) and supported by the National Science Foundation under Grants No. 1763699 and 1717779. Source code for this is available as an accompanying artifact at https://zenodo.org/record/4695169.

Chapter 5 This chapter discusses PyLSE, a new pulse-transfer level language for superconductor electronics built on the theory of automata. PyLSE enables the precise specification of gate semantics via a transition system-based Python embedded domain-specific language (DSL). I show that it is a effective framework for easily composing cells into larger designs and that it facilitates the identification of timing and logic errors through a mix of dynamic checks and sound static analysis. I also show how PyLSE can be formalized mathematically, demonstrating its capabilities through the creation, simulation, and verification of a selection of SCE designs. It is based on work that has been submitted to a conference and is currently under review. I am the first author on this work, and my co-authors are Georgios Tzimpragos, Harlan Kringen, Jennifer Volk, Timothy Sherwood, and Ben Hardekopf.

# Chapter 2

# Zarf: An Architecture Supporting Formal and Compositional Binary Analysis

# 2.1 Introduction

Embedded devices are ubiquitous, with many now playing roles that support human health, well-being, and safety. The critical nature of these systems — automotive, medical, cryptographic, avionic — is at odds with the increasing complexity of embedded software overall: even simple devices can easily include an HTTP server for monitoring purposes. Traditional processor interfaces are inherently global and stateful, making the task of isolating and verifying critical application subsets a significant challenge. Architectural extensions have been proposed that enhance the power, performance, and functionality of systems, but in contrast, we cover the first architecture designed with formal program analysis as a core motivating principle.

High-level, functional languages offer a remarkable ability to reason about the behav-

ior of programs, but are often unsuited to low-level embedded systems, where reasoning must be done at the assembly level to give a full picture of the code that will actually execute. At a high level, in a language designed for verification, reasoning typically requires relying on a language run-time that can be prohibitive for resource-constrained or real-time embedded systems, and/or require the assumption that thousands of lines of untrusted code in the language stack are correct.

Another approach is to directly model the processor interface by giving formal semantics to the ISA. However, reasoning about binary behavior on traditional architectures is difficult and often left incomplete. Unless *all* program components and architectural behaviors are included, any piece outside the expected model could mutate a piece of machine state and violate the assumptions of the verification effort. Even assuming that never happens, using a verified compiler, assuming other modules are correct, using only a subset of the ISA and assuming the rest is unused, program-specific reasoning is still difficult — i.e., reasoning about C still means reasoning about pointers, memory mutation, and countless imperative, effectful behaviors.

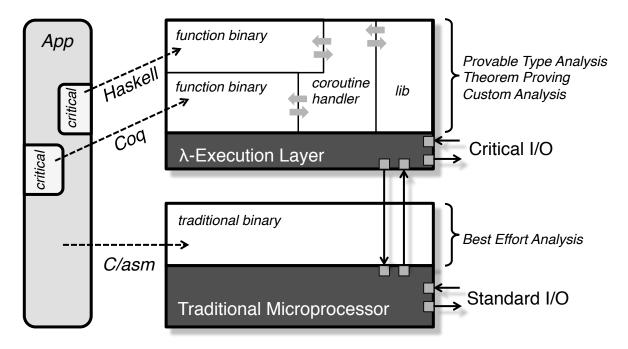

We propose a system where the critical code can execute at the assembly level in a way that is very similar to the underlying computational model upon which proof and reasoning systems are already built. Under such a mode of computation, properties such as isolation, composition, and correctness can be reasoned about incrementally, rather than monolithically. However, instead of requiring a complete reprogramming of all software in a system, we instead examine a novel system architecture consisting of two cooperating layers: one built around a traditional imperative ISA, which can execute arbitrary, untrusted code, and one built around a novel, complete, purely functional ISA designed specifically to enable reasoning about behavior at the binary level. Application behaviors that are mission critical can be hoisted piecemeal from the imperative to the functional world as needed.

Our proposed system, the Zarf Architecture for Recursive Functions, observes the following properties:

- 1. The functional ISA, "Zarf," is devoid of all global or mutable state, and provides a compact, complete, and mathematical semantics for the behavior of instructions;

- 2. The imperative ISA is strictly separated from the functional ISA, connected only via a communication channel through which the system components can pass values;

- 3. The subset of the application which operates on Zarf can be verified and reasoned about without regard to the operation of the imperative components, meaning that *only* the critical components need to be ported and modeled;

- 4. Reasoning on the functional ISA is provably composable i.e., two separate pieces can be statically shown to never interfere with each other.

To demonstrate the usefulness of this platform, we develop, model, and test a sample application which implements an Implantable Cardio-Defibrillator (ICD) — an embedded medical device which is implanted in a patient's chest cavity, monitors the heart, and administers shocks under certain conditions to prevent or counter cardiac arrest. Though ICDs provide life-saving treatment for patients with serious arrhythmia, these devices, along with other embedded medical devices, have seen thousands of recalls due to dangerous software bugs [7, 8]. By leveraging this two-layer approach, we are able to formally verify the correctness of a low-level implementation of the core functions in Coq and directly extract executable assembly code without needing software runtimes. The ISA semantics allow us to construct an integrity type system and formally prove that the rest of the code never corrupts the inputs or outputs of the critical functions. Furthermore, the functional abstraction built in to the binary code allows

Figure 2.1: High-level Zarf system architecture: by dividing the system into two hardware realms — one that provides a precise, mathematical semantics for reasoning about program behavior, and the other a standard imperative core for legacy software — we can formally verify and otherwise reason about critical subsets of applications without needing to model and verify the entire program.

us to bound worst-case execution time, even in the face of garbage collection. Taken altogether, we have an embedded medical application whose core components have been proven correct, where non-interference is guaranteed, where real-time deadlines are assured to be met, and where C code can execute arbitrary auxiliary functions in parallel for monitoring. The high-level system architecture is shown in Figure 2.1.

Given the significant amount of related efforts in verification and ISA design, we begin by summarizing how our work differs from previous efforts in the fields of verification and architecture (Section 2.2). We then describe the Zarf platform in more detail and describe a hardware implementation, which runs the application on an FPGA (Section 2.3). Details of our embedded ICD software application and the ways it can leverage the properties of the Zarf platform are described next (Section 2.4),

followed by a precise definition of Zarf's semantics (Section 2.5). We then discuss the verification of multiple properties of the critical sub-components of the ICD, covering correctness, timing, and non-interference (Section 2.6). Finally, we evaluate this system architecture and approach, presenting hardware resource requirements of the novel ISA, and examine the performance loss of the verified components when compared to an unverified C alternative (Section 2.7), and conclude (Section 2.8).

# 2.2 Related Work

### 2.2.1 Verification

Our dual ISA approach, where one is untrusted and the other trusted, draws in part on Rushby's work on security kernels [9]. He separates machine components into virtual "regimes" and proves isolation. Having done so, Rushby can then show that security is maintained when introducing clearly defined and limited channels of communication whose information flow can be tracked. Our imperative and functional ISAs behave as separate components, communicating only through a specified, dedicated channel, thus eliminating any insecure information flow — via memory contamination, for example.

Our security type system draws from the work done on the Secure Lambda (SLam) calculus by Heintze and Riecke [10] and its further development by Abadi et al. in their Core Calculus of Dependency [11]. It also draws inspiration from Volpano [12] et al., who created a type system for secure information flow for an imperative block-structured language. By showing that their type system is sound, they show the absence of flow from high-security data to lower-security output, or similarly, that low-security data does not affect the integrity of higher-security data. Other seminal work on secure information flow via the formulation of a type system include Denning [13], Goguen

[14], Pottier's information flow for ML [15], and Sabelfeld and Myers's survey on language-based information flow security [16].

Productive, expressive high-level languages that are also purely functional are excellent source platforms for Zarf. Even languages like Haskell, though, can have occasional weaknesses that can lead to runtime type-errors. Subsets such as Safe Haskell [17] shore up these loopholes, and provide extensions for sandboxing arbitrary untrusted code. Zarf provides isolation guarantees at the ISA level and does not require runtimes, but relies on languages like Safe Haskell for source code development.

Previous work on ISA-level verification has often involved either simplified or incomplete models of the architecture. These can be in the form of new "idealized" assembly-like languages: Yu et al. [18] use Coq to apply Hoare-style reasoning for assembly programs written in a simple RISC-like language. They also provide a certified memory management library for the machine they describe. Chlipala presents Bedrock, a framework that facilitates the implementation and verification of low-level programs [19], but limits available memory structures.

Kami [20] is a platform for specifying, implementing, and verifying hardware designs in Coq. By making the language of design the same as the language of verification, the gap that traditionally exists between high-level specification and actual hardware implementation is minimized. A key distinction between Kami and our work is that Zarf focuses on building a processor specifically to make software verification easier, while Kami focuses on the task of specifying and building verifiable hardware. The two are very complementary — you can build a traditional imperative machine using Kami (e.g. their pipelined RISC-V processor implementation), and you can build a Zarf machine using traditional hardware design.

Verification has also been done for subsets of existing machines. For example, a "substantial" subset of the Motorola MC68020 interface is modeled and used to

mechanically prove the correctness of quicksort, GCD, and binary search [21]; other examples include a formalization of the SPARC instruction set, including some of the more complex properties, such as branch delay slots [22]; and subsets of x86 [23]. One of the biggest efforts to date has been a formal model of the ARMv7 ISA using a monadic specification in HOL4 [24]. Moore developed Piton, a high level assembly language and a verified compiler for the FM8502 microprocessor [25], which complemented the verification work done on the FM8502 implementation [26]. These are large efforts because of the difficulty in reasoning about imperative systems. At higher levels of abstraction, entire journal issues have been devoted to works on Java bytecode verification [27].

In addition to proofs on machine code for existing machines, it is also possible to define new assembly abstractions that carry useful information. Typed assembly as an intermediate representation was previously identified as a method for Proof-Carrying Code [28], where machine-checked proofs guarantee properties of a program [29]. Typed assemblies and intermediate representations have seen extensive use in the verification community [30, 19, 31, 32] and have been extended with dependent types [33], allowing for more expressive programs and proofs at the assembly level.

Verified compilers are a popular topic in the verification community [34, 35, 36, 37], the most well-known example being CompCert [38], a verified C compiler. Verified compilers are usually equipped with a proof of semantics preservation, demonstrating that for every output program, the semantics match those of the corresponding input program. A verified compiler does not provide tools for, nor simplify the process of doing, program-specific reasoning. One needs a secondary tool-chain for reasoning about source programs, such as the Verified Software Toolchain (VST) [39] for CompCert. These frameworks often have a great cost, mandating the use of sophisticated program logics, such as higher-order separation logic in VST, in order to fully reason

about possible program behaviors.

Further, in many systems, it's possible that not all source code is available; without being able to reason about binary programs, guarantees made on a piece of the source program (and preserved by the verified compiler) may be violated by other components. Extensions to support combining the output of verified compilers, such as separate compilation and linking, are still an active research area [40, 41]. As work on verified compilers requires a semantic model of the ISA, it is complemented by our work, which gives complete and formal semantics for an ISA.

Previous work at the intersection of verification and biological systems has attempted to improve device reliability through modeling efforts. This includes work that formulates real-time automata models of the heart for device testing [42], formal models of pacing systems in Z notation [43], quantitative and automated checking of the interaction of heart-pacemaker automata to verify pacemaker properties [44], and semi-formal verification by combining platform-dependent and independent model checking to exhaustively check the state space of an embedded system [45]. Our work is complemented by verification works such as these that refine device specification by taking into account device-environment interactions.

### 2.2.2 Architecture

The SECD Machine [46] is an abstract machine for evaluating arithmetic expressions based in the lambda calculus, designed in 1963 as a target for functional language compilers. It describes the concept of "state" (consisting of a Stack, Environment, Control, and Dump) and transitions between states during said evaluation. Interpreters for SECD run on standard, imperative hardware. Hardware implementations of the SECD Machine have been produced [47], which explore the implementation of SECD

at the RTL and transistor level, but present the same high-level interface. The SECD hardware provides an abstract-machine semantics, indicating how the machine state changes with each instruction. Our verification layer makes machine components fully transparent, presenting a higher-level small-step operational semantics, where instructions affect an abstract environment, and a big-step semantics, which immediately reduces each operation to a value. These latter two versions of the semantics are more compact, precise, and useful for typical program-level reasoning.

The SKI Reduction Machine [48] was a hardware platform whose machine code was specially designed to do reductions on simple combinators, this being the basis of computation. Like our verification layer, it was garbage-collected and its language was purely applicative. The goal was to create a machine with a fast, simple, and complete ISA. The choice to use the "simpler" SKI model means that machine instructions are a step removed from the typically function-based, mathematical methods of reasoning about programs. Our functional ISA, while also simple and complete, chooses somewhat more robust instructions based on function application; though the implementation is more complicated, modern hardware resources can easily handle the resulting state machine, giving a simple ISA that is sufficiently high-level for program reasoning.

The most famous work on hardware support for functional programming was on Lisp Machines [49, 50, 51]. Lisp machines provided a specialized instruction set and data format to efficiently implement the most common list operations used in functional programming. For example, Knight [51] describes a machine with instructions for Lisp primitives such as CAR and CADR, and also for complex operations like CALL and MOVE. While these these machines partially inspired this work, Lisp Machines are not directly applicable to the problem at hand. Side-effects on global state at the ISA level are critical to the operation of these machines, and while fast function calls are supported, the stepwise register-memory-update model common to more traditional

ISAs is still a foundation of these Lisp Machine ISAs. In fact, several commercial Lisp Machine efforts attempted to capitalize on this fact by building Lisp Machines as a thin translation layer on top of other processors.

Flicker also dealt with architectural support for a smaller TCB in the presence of untrusted, imperative code, but did so with architectural extensions that could create small, independent, trusted bubbles within untrusted code [52]. Our architecture is almost inverted, with a trusted region providing the main control, calling out to an untrusted core as needed. Previous works such as NoHype [53] dealt with raising the level of abstraction of the ISA and factoring software responsibilities into the hardware. Our verification layer shares some of these characteristics, but deals with verification instead of virtualization, as well as being a complete, self-contained, functional ISA.

Previous work has explored the security vulnerabilities present in many embedded medical devices, as well as zero-power defenses against them [54, 55, 56]. The focus of our work is analysis and correctness properties, and we do not deal with security.

# 2.3 Hardware Architecture and ISA

Our system relies on two separate layers, running two different ISAs, connected only by a data channel. This allows one of the layers to be specialized to the execution of machine code with 1) a compact, precise, and complete semantics highly amenable to proofs, and 2) the ability to compose verified pieces safely. It is entirely possible that all code in the system be written to be purely functional and run on Zarf: the ISA for this layer is complete. However, embedded devices often contain a mix of software, including legacy code or nice-to-have features that do not affect the application's behavior, such as relaying data and diagnostic information to outside receivers. With a two-layer approach, we can run imperative code that is orthogonal to the operation of

critical application components while still connecting with the vetted, functional code in a structured way. This, in turn, allows code to be formally verified piecemeal, with functions "raised" into Zarf as deemed necessary.

The following subsections describe the interface and construction of Zarf, including the reasons we take an approach much closer to the lambda calculus underlying most software proof techniques, how we capture this style of execution in an instruction set, the semantics for that instruction set, and more practical considerations such as I/O, errors, and ALU functions.

# 2.3.1 Design Goals

Normal, imperative architectures have been difficult to model, and the task of composing verified components is still an open problem [40, 41]. We identify the following features as undesirable and counterproductive to the goal of assembly-level verification:

- Large amounts of global machine state (memory, stack, registers, etc.) directly

accessible to instructions, all of which must be modeled and managed in every

proof, and which inhibit modularity: state may be modified by code you haven't

seen.

- 2. The mutable nature of machine state, which prevents abstraction and composition when reasoning about functions or sets of instructions.

- 3. A large number of instructions and features: a complete model must incorporate all of them (e.g., fully modeling the behavior of the ARMv7 was 6,500 lines of HOL4 [24]).

- 4. Arbitrary control flow, which often requires complex and approximate analyses to soundly determine possible control flows [57].

- 5. Unenforced function call conventions, meaning one must prove that every function respects the convention.

- 6. Implicit instruction semantics, such as exceptions where "jump" becomes "jump and update registers on certain conditions."

To avoid these traits, we design an interface that is small, explicit in all arguments, and completely free of state manipulation and side effects — with the exception of I/O, which is necessary for programs to be useful. Without explicit state to reference (memory and registers), standard imperative operations become impossible, and we must raise the level of abstraction. Instead of imperative instructions acting as the building blocks of a program, our basic unit is the *function*. This is a major departure from a typical imperative assembly, where the notion of a "function" is a higher-level construct consisting of a label, control flow operations, and a calling convention enforced by the compiler — but which has no definition in the machine itself. By bringing the definition of functions to the ISA level, they become not just callable "methods" that serve to separate out independent routines, but are actually strict functions in the mathematical sense: they have no side effects, never mutate state, and simply map inputs to outputs. This change allows us to attach precise and formal semantics to the ISA operations.

# 2.3.2 Description and Semantics

Zarf's functional ISA is effectively an  $\bf a$ ) untyped,  $\bf b$ ) lambda-lifted,  $\bf c$ ) administrative normal form (ANF) lambda calculus. Those limitations are a result of the

```

x \in Variable \quad n \in \mathbb{Z} \quad fn, cn \in Name

p \in Program := \overrightarrow{decl} \text{ fun main } = e

decl \in Declaration ::= cons \mid func

cons \in Constructor := con \ cn \ \vec{x}

func \in Function ::= \mathbf{fun} \ fn \ \vec{x} = e

e \in Expression := let \mid case \mid res

let \in Let ::= let \ x = id \ \overrightarrow{arg} \ in \ e

case \in Case ::= case \ arg \ of \ \overrightarrow{br} \ else \ e

res \in Result ::= result arg

br \in Branch := cn \vec{x} \Rightarrow e \mid n \Rightarrow e

id \in Identifier := x \mid fn \mid cn \mid op

arg \in Argument := n \mid x

op \in PrimOp := + | - | \times | \div | =

| < | \le | \land | \lor | \bar{\land} | \lor

| ⊕ | ≪ | ≫ | sra | ¬

| getint | putint

```

Figure 2.2: Abstract syntax of Zarf's functional ISA. A program is a set of function and constructor declarations, where functions are composed solely of let, case, and result expressions, and constructors are tuples with unique names. Case expressions contain branches and serve as the mechanism for both control flow and deconstruction of constructor forms. An arrow over any metavariable (e.g.  $\vec{x}$ ) signifies a list of zero or more elements. *op* refers to a function that is implemented in hardware (such as ALU operations); though the execution of the function invokes a hardware unit instead of a piece of software, the functional interface is identical to program-defined functions.

implementation being done in real hardware: **a**) to avoid the complexity of a hardware typechecker, the assembly is untyped<sup>1</sup>; **b**) because every function must live somewhere in the global instruction memory, only top-level declarations of functions are allowed (lambda-lifted); **c**) because the instruction words are fixed-width with a static number of operands, nested expressions are not allowed and every sub-expression must be bound to its own variable (ANF). The abstract syntax of Zarf assembly is given in Figure 2.2.

All words in the machine are 32-bits. Each binary program starts with a magic word, a word-length integer N stating how many functions are contained in the program, and then a sequence of N functions. Each function starts with an informational word that lets the machine know the "fingerprint" of the function (including the number of arguments expected and how many locals will be used) and a word-length integer M to specify that the body of the function is M words long. The remaining M words of the function are then composed entirely of the individual instructions of the machine.

Each function, as it is loaded, is given a unique and sequential identifier. These function identifiers are the only globally visible state in the system and serve as both a kind of name and a kind of pointer back to the code. Other functions can refer to, test, and apply arguments to function identifiers. There are two varieties of function identifiers: those that refer to full functions that contain a body of code, and "constructors," which have no body at all. Constructors are essentially stub functions and cannot be executed. However, just like other functions, you can apply arguments to them. These special function identifiers thus can serve as a "name" for software data types, where arguments are the composed data elements. (In more formal terms, you can use our constructors to implement algebraic data types.)

<sup>&</sup>lt;sup>1</sup>The original ISA definition as presented in the paper was untyped; in later work, we extended the ISA to include type annotations and a hardware typechecker.

The words defining the body of a function are built out of just three instructions: let, case, and result, which we will describe below. Unlike RISC instructions, let and case can be multiple words long (depending on the number of arguments and branches, respectively). However, unlike most CISC instructions, each piece of the variable length instruction is also word-aligned and trivial to decode.

Zarf has no programmer-visible registers or memory addresses, but instructions will still need to reference particular data elements. Instructions can refer to data by its source and index, where the source is one of a predefined set — e.g., *local* and *arg*, which serve a purpose similar to the stack on a traditional machine. The *local* and *arg* indices might be analogous to stack offsets, while the actual addresses themselves are never visible.

The primary ways of generating Zarf assembly are via extraction from Coq and writing it by hand. We also have a Haskell compiler that supporting a subset of basic Haskell constructs. In our experience, Zarf assembly code resembles a typical functional programming language like desugared Haskell or OCaml, and the resultant expressibility makes directly writing assembly relatively easy; the user doesn't need to worry about memory address calculations, maintaining register or stack state across function calls, or the myriad other things that make programming traditional ISAs tedious and error-prone. For more information on automatic Coq extraction, see our discussion of the ICD implementation in Section 2.6.

Figure 2.5 gives the complete ISA behavior using a big-step semantics, which explains how each instruction reduces to a value. This semantics uses eager evaluation for simplicity; though the current hardware implementation uses lazy semantics, the difference is not observable in our application because I/O interactions are localized to a specific function and always evaluated immediately. The semantics use assembly keywords for readability; Figure 2.3 shows how the assembly maps one-to-one with

the binary encoding, and Figure 2.7 shows how low-level Coq code can be directly converted to our assembly.

# 2.3.3 Instruction Set

The let instruction applies a function to arguments and assigns it a *local* identifier. The first word in the let instruction indicates a function identifier or closure object and the number of argument words that follow. Note that unlike a function "call", let does not immediately change the control flow or force evaluation of arguments; rather it creates a new structure in memory (closure) tying the code (function identifier) to the data (arguments), which, when finally needed, can actually be evaluated (using lazy evaluation semantics). Additionally, the let instruction allows partial application, meaning that new functions (but not function identifiers) can be dynamically produced by applying a function identifier to some, but not all, of its arguments.

The case instruction provides pattern-matching for control flow. It takes a value, then makes a set of equality comparisons, one for each "pattern" provided. The first word of the case instruction indicates a piece of data to evaluate. As we need an actual value, this is the point in execution that forces evaluation of structures created with let — however, it is evaluated only enough to get a value with which comparisons can be made; specifically, until it results in either an integer or a constructor object<sup>2</sup>. The words following the instruction encode patterns (pattern\_literal and pattern\_cons) against which to match the case value. If the case value exactly equals the literal value or function (i.e. constructor) identifier, execution proceeds with the next instruction; otherwise, it skips the number of words specified in the pattern argument. A matching pattern\_else is required for every case which will be executed when no other matches

<sup>&</sup>lt;sup>2</sup>More precisely, evaluation of that argument will always produces a result in Weak Head-Normal Form (WHNF), but never a lambda abstraction.

Figure 2.3: How the high-level assembly instructions are directly compiled into a Zarf binary for execution. This example shows the map function, along with the list constructors, in (a) high-level untyped assembly, (b) machine assembly, and (c) binary. (a) The standard linked-list definition requires just two constructors: a list is either empty or a 2-element struct containing a head (a value) and a tail (a list) [lines 1-2]. The function map takes a function and a list as arguments [line 3]; it builds a new list, applying the function to each list element. If the argument list is empty, it returns an empty list [lines 5-6]. Otherwise, if the list matches against the head/tail constructor [line 7], it applies the function it was given to the list element [lines 8-9], calls map recursively on the list tail [lines 10-12], builds a new list [lines 13-15], and yields that new list [line 16]. The else branch is not shown. (b) In the lowering to machine assembly, names are replaced with local indices, addressing a value on the locals stack (e.g., list' becomes local 2 [line 13]). Function allocations are broken up so that each argument occupies its own word. (c) The binary is a direct mapping from the assembly in (b), simply translating ops to opcodes and data sources to integer identifiers. 'x' indicates an unused field. (d) Binary encoding. Each word of the binary is either the start of a function, the start of an instruction, or an argument word in a let instruction. With no architecturally visible state, data is accessed with a scoped system where the program identifies source and index; all data references use the same source/index pattern.

are found (and demarcates the end of the case instruction encoding). Case/pattern sequences not adhering to the encoding described are malformed and invalid — e.g., you cannot skip to the middle of a branch, or have a case without an else branch.

The result instruction is a single word, indicating a single piece of data that the current function should yield. Every branch of every function must terminate with a result instruction (disallowing re-convergent branches means the simple pattern-skip mechanism is all that is necessary for control flow). Functions that do not produce a value do not make sense in an environment without side effects, and so are disallowed. After a result, control flow passes to the case instruction where the function result was required.

We realize that this is a departure from traditional hardware instructions and suggest reference to Figure 2.3 to help ground our descriptions in a concrete example. Figure 2.3 shows a small function, map, written in high-level assembly, machine assembly, and encoded as a binary. A more thorough description of the semantics of each of these instructions is found in Section 2.5.

# 2.3.4 Built-In Functions, I/O, and Errors

ALU operations are, for the most part, already purely mathematical functions — they just map inputs to an output. The Zarf functional ISA is built around the notion of function calls, so no new mechanism or instructions are needed to use the hardware ALU. Invoking a hardware "add" is the same as invoking a program-supplied function. In our prototype, function indices less than 256 (0x100) are reserved for hardware operations; the first program-supplied function, main, is 0x100, with functions numbered up from there. During evaluation, if the machine encounters a function with an index less than 0x100, it knows to invoke the ALU instead of jumping to a space in instruction memory.

The only two functions with side-effects in the system, input and output, are also primitive functions. The input function takes one argument (a port number) and returns a single word from that port; the output function takes two arguments, a port and a value, and writes its result to the port, returning the value written. Since data dependencies are never violated in function evaluation, software can ensure I/O operations always occur in the right order even in a pure functional environment by introducing artificial data dependencies; this is the principle underlying the I/O monad [58, 59], used prominently in languages like Haskell.

In a purely functional system there are no side effects, and thus no notion of an "exception". For program-defined functions, this just requires that every branch of every case return a value (that value could be a program-defined error). However, some invalid conditions resulting from a malformed program can still occur at runtime. To respect the purely functional system, these must cause a non-effectful result that is still distinguishable from valid results. Our solution is to define a "runtime error constructor" in the space of reserved functions. Every function, both hardware- and software-defined, can potentially return an instance of the error constructor. The ISA semantics are undefined in these error cases, because it's very easy to avoid — compiling from any Hindley-Milner typechecked language will guarantee the absence of runtime type errors [60, 61].

# 2.4 System Software

This section describes the software architecture across the two realms (functional and imperative) of the system, and provides an overview of the ICD and the functional coroutines.

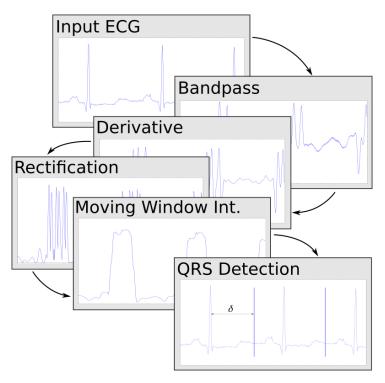

Figure 2.4: The ECG takes input signals sampled at 200 Hz and filters them multiple times, after which the peaks are classified and the rate of heartbeat determined. These values are fed to an ATP (antitachycardia pacing) procedure, which decides if ventricular tachycardia is occurring based on current and previous heart rate, and administers pacing shocks to prevent acceleration and ventricular fibrillation (a form of cardiac arrest).

## 2.4.1 Functional vs. Imperative

As our system is composed of two small and separate computational layers, the software is split across two different ISAs. For existing applications, or applications prototyped for existing platforms, the decision of which components to migrate to Zarf represents a trade-off of increased abstraction and verification capability for additional development effort and some decrease in performance. Section 2.7 provides some quantitative worst-case bounds for this trade-off.

Zarf runs a small microkernel based on cooperative coroutines [62, 63] to handle the scheduling and communication of different software components. This allows us to more easily group and reason about code in terms of higher-level behaviors — i.e., the small surface area of each coroutine means they can be considered (and occasionally verified) in blocks, as collections of functions with a single specification and interface. The cooperative nature of the system is a design choice that allows us to avoid interrupts, which would complicate proofs of a single coroutine's behavior. Timing analysis (section 2.6.2) ensures each coroutine always returns control.

Zarf enables reasoning about these coroutines at the assembly and binary level. Section 2.6 demonstrates different properties that can be verified. The integrity type system allows a developer to statically prove that a given set of coroutines (and the microkernel itself) will execute in cooperation without one coroutine corrupting values important to another. This *composability* of verification is extremely difficult on traditional architectures, as the global and mutable nature of all state makes it quite easy for any software component to affect any other.

The imperative layer — which can be any embedded CPU, but for our purposes is a Xilinx MicroBlaze processor — runs whatever pieces of the software are not placed on Zarf. This allows for monitoring software, low-level drivers, communication protocols,

and other complex, imperative code to exist and run without requiring modeling or pure-functional implementations. As this area of the system is untrusted and unverified, anything on which the critical components depend should be rewritten to run on Zarf.

In our sample application, three application coroutines are run on Zarf: one that handles the core ICD application, an I/O routine that handles the timing of reading the values from the patient's heart and outputting when shocks should occur, and a routine that sends values to the monitoring software on the imperative layer. The system operates in real-time, reading a single value from the heart, running ECG and ICD processing, and communicating the resulting value back out. In our application, the monitoring software tracks the number of times treatment occurs, and, when prompted from its communication channel, will output that number. This imperative software could be arbitrarily complex and handle more complicated monitoring and diagnosis, communication drivers to communicate with the outside world, or other features; as it is a standard imperative core, any embedded C code can be easily compiled for it with an off-the-shelf compiler.

#### 2.4.2 ICD

ICDs are small, battery-powered, embedded systems which are implanted in a patient's chest cavity and connect directly with the heart. For patients with arrhythmia and at risk for heart failure, an ICD is a potentially life-saving device. Currently, the primary use of ICDs is to detect dangerous arrhthymias (such as ventricular tachycardia, or VT) and administer pacing shocks (anti-tachycardia pacing, or ATP). These shocks help prevent the acceleration in heart rate leading to ventricular fibrillation, a form of cardiac arrest.

From 1990 to 2000, over 200,000 ICDs and pacemakers were recalled due to software

issues [7]. Between 2001 and 2015, over 150,000 implanted medical devices were recalled by the FDA because of life-threatening software bugs [8]. However, ICDs are credited with saving thousands of lives; for patients who have survived life-threatening arrhthymia, ICDs decrease mortality rates by 20-30% over medication [64, 65, 66]. Currently, around 10,000 new patients have an ICD implanted each month [67], and around 800,000 people are living with ICDs [68].

The core of our ICD is an embedded, real-time ECG algorithm that performs QRS<sup>3</sup> detection on raw electrocardiogram data to determine the timing between heartbeats. We work off of an established real-time QRS detection algorithm [69], which has seen wide use and been the subject of studies examining its performance and efficacy [70]. An open-source update of several versions of the algorithm [71] is available; we use the results of this open-source work as the basis of our algorithm's specification as well as the C alternative. After the ECG algorithm detects the pacing between heartbeats, the ATP function checks for signs of ventricular tachycardia and, if found, administers a series of pacing shocks. We implement the VT test and ATP treatment published in [72].

The I/O coroutine is passed the output of the previous iteration of the ICD coroutine. A hardware timer is used to ensure that I/O events occur at the correct frequency. When the correct time has elapsed (5 ms), the I/O coroutine outputs the given value and reads the next input value. It yields this value to the microkernel.

This input is then passed through to the ICD coroutine, which implements a series of filter passes to detect the spacing between QRS complexes (Figure 2.4 illustrates the ECG filter passes). If 18 of the last 24 beats had periods less than 360 ms (corresponding to a heart rate greater than 167 bpm), the ICD coroutine moves into a

<sup>&</sup>lt;sup>3</sup>The "QRS complex" is made up of the rapid sequence of Q, R, and S waves corresponding to the depolarization of the left and right ventricles of the heart, forming the distinctive peak in an ECG.

treatment-administering state, where it outputs three sequences of eight pulses at 88% of the current heartrate, with a 20 ms decrement between sequences. This is designed to prevent continued acceleration and restore a safe rhythm.

The monitoring software, which runs on the MicroBlaze, receives the output of the ICD coroutine each cycle. A command can be given on the diagnostic input channel for the software to output the number of times treatment has occurred.

I/O events occur at a fixed frequency of 200 Hz. Timing analysis in Section 2.6.2 confirms that, after an input event, the entire cycle of each coroutine running and yielding, including garbage collection, is able to conclude well within the 5 ms window, meaning that the entire system is always able to meet its real-time deadline.

## 2.5 ISA Semantics

Zarf has the core goal of providing concise, mathematical semantics for its hardware ISA. These can be found in Figure 2.5, which gives the complete ISA behavior using a big-step semantics, explaining how each instruction reduces to a value. This semantics uses eager evaluation for simplicity; though the current hardware implementation uses lazy semantics, the difference is not observable in our application because I/O interactions are localized to a specific function and always evaluated immediately.

The semantics are discussed in more detail in the following subsections. Note that terms introduced in the abstract syntax (Figure 2.2) are used in the semantics. Each rule (or helper function) is applicable in a different case, depending on what is under evaluation; the scenarios are all mutually exclusive, meaning that there is always exactly one rule that can (and should) be applied at every step.

$$c \in Constructor = Name \times \overrightarrow{Value} \qquad clo \in Closure = (\lambda \vec{x}.e) \times \overrightarrow{Value}$$

$$v \in Value = \mathbb{Z} \ \cup \ Constructor \ \cup \ Closure \qquad \rho \in Env = Variable \rightarrow Value$$

$$\frac{\vdash e \Downarrow v}{\vdash \overrightarrow{decl} \ \mathbf{fun} \ \mathbf{main} = e \Downarrow v} \qquad (PROGRAM) \qquad v = \rho(arg) \qquad (PROGRAM)$$

$$\rho \vdash \mathbf{result} \ arg \Downarrow v \qquad (RESULT)$$

$$\frac{\vec{v}_1 = \rho(\overrightarrow{arg}) \quad v_2 = \operatorname{applyCn}(cn, \vec{v}_1) \quad \rho[x \mapsto v_2] \vdash e \Downarrow v_3}{\rho \vdash \mathbf{let} \ x = cn \ \overrightarrow{arg} \ \mathbf{in} \ e \Downarrow v_3} \qquad (LET-CON)$$

$$\rho \vdash \mathbf{let} \ x = cn \ \overrightarrow{arg} \ \mathbf{in} \ e \Downarrow v_3 \qquad (LET-FUN)$$

$$\rho \vdash \mathbf{let} \ x_1 = fn \ \overrightarrow{arg} \ \mathbf{in} \ e_1 \Downarrow v_3 \qquad (LET-FUN)$$

$$\rho \vdash \mathbf{let} \ x_1 = fn \ \overrightarrow{arg} \ \mathbf{in} \ e_1 \Downarrow v_3 \qquad (LET-VAR)$$

$$\frac{\vec{v}_1 = \rho(\vec{arg}) \quad \vec{v}_2 = \rho(\vec{arg}) \quad \vec{v}_3 = \operatorname{applyFn}(v_1, \vec{v}_2, \rho) \quad \rho[x_1 \mapsto v_2] \vdash e_1 \Downarrow v_3 \qquad (LET-VAR)$$

$$\frac{\vec{v}_1 = \rho(\vec{arg}) \quad \vec{v}_2 = \operatorname{applyPrim}(o\rho, \vec{v}_1) \quad \rho[x \mapsto v_2] \vdash e \Downarrow v_3 \qquad (LET-VAR)$$

$$\frac{\vec{v}_1 = \rho(\vec{arg}) \quad v_2 = \operatorname{applyPrim}(o\rho, \vec{v}_1) \quad \rho[x \mapsto v_2] \vdash e \Downarrow v_3 \qquad (LET-VAR)$$

$$\rho \vdash \mathbf{let} \ x = op \ \overrightarrow{arg} \ \mathbf{in} \ e \Downarrow v_3 \qquad (CASE-CON)$$

$$\rho \vdash \mathbf{case} \ arg \ \mathbf{of} \ \overrightarrow{br} \ else \ e_2 \Downarrow v_2 \qquad (CASE-CON)$$

$$\rho \vdash \mathbf{case} \ arg \ \mathbf{of} \ \overrightarrow{br} \ else \ e_2 \Downarrow v_2 \qquad (CASE-LIT)$$

$$\rho \vdash \mathbf{case} \ arg \ \mathbf{of} \ \overrightarrow{br} \ else \ e_2 \Downarrow v_2 \qquad (CASE-LIT)$$

$$\rho \vdash \mathbf{case} \ arg \ \mathbf{of} \ \overrightarrow{br} \ else \ e_2 \Downarrow v_2 \qquad (CASE-ELSE)$$

$$n_2 \ \mathbf{is} \ \mathbf{input} \ \mathbf{from} \ \mathbf{port} \quad n_1 \ \mathbf{is} \ \mathbf{a} \ \mathbf{port} \quad n_2 = \rho(arg) \quad \rho[x \mapsto n_2] \vdash e \Downarrow v \qquad (CASE-ELSE)$$

$$\rho \vdash \mathbf{case} \ arg \ \mathbf{of} \ \overrightarrow{br} \ else \ e_2 \Downarrow v_2 \qquad (CASE-ELSE)$$

$$n_2 \ \mathbf{is} \ \mathbf{input} \ \mathbf{from} \ \mathbf{port} \quad n_1 \ \mathbf{is} \ \mathbf{a} \ \mathbf{port} \quad n_2 = \rho(arg) \quad \rho[x \mapsto n_2] \vdash e \Downarrow v \qquad (PUTINT)$$

$$\rho \vdash \mathbf{let} \ x = \mathbf{getint} \ n_1 \ \mathbf{in} \ \mathbf{arg} \ \mathbf{in} \ e \Downarrow v \qquad (PUTINT)$$

Figure 2.5: Big-step semantics for Zarf's functional ISA. It is a ternary relation on an environment; a **let**, **case**, or **result** expression; and the value to which it evaluates. Evaluation begins with the main function's body.  $\rho[x \mapsto v]$  returns an updated copy of the environment with x mapped to v. **getint** gets an integer from a specified port, and **putint** puts an integer onto a specified port; both are the only mechanisms for I/O.

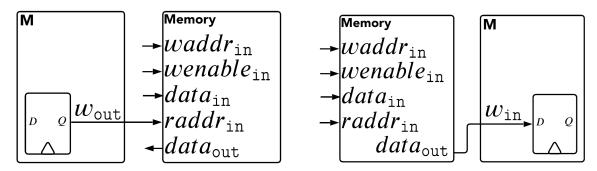

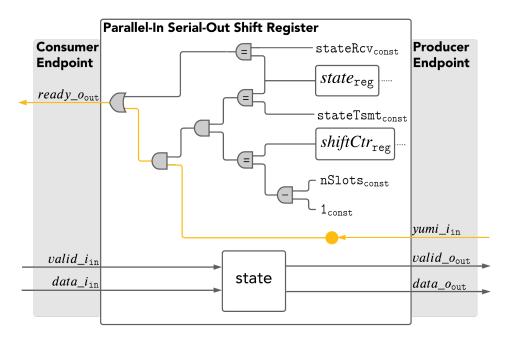

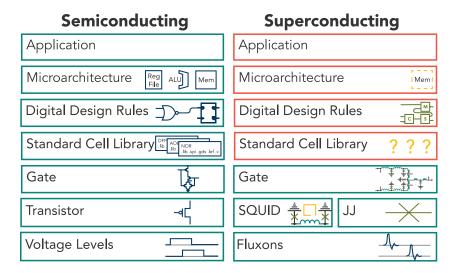

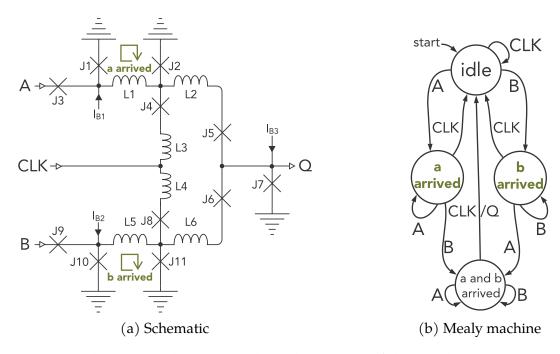

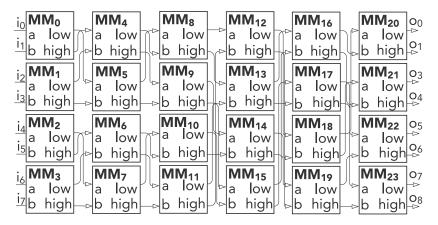

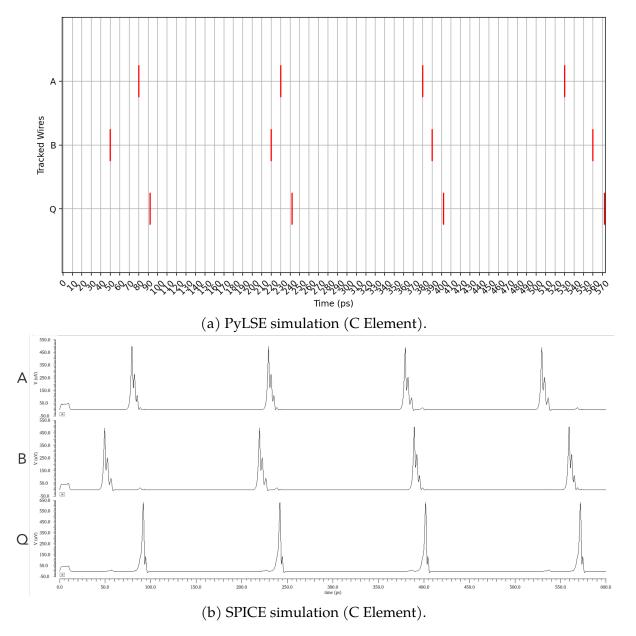

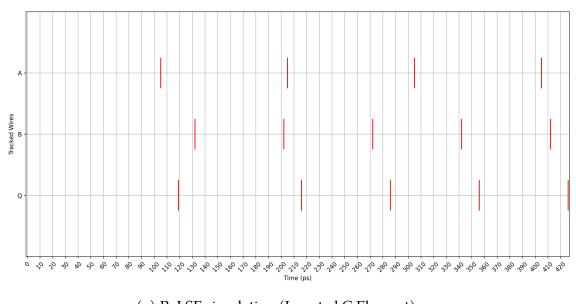

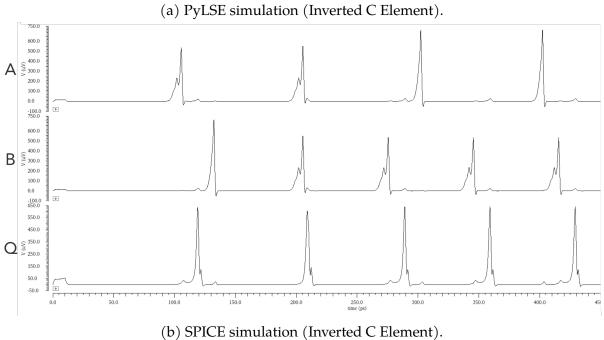

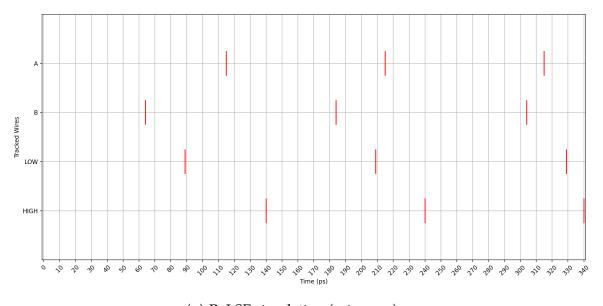

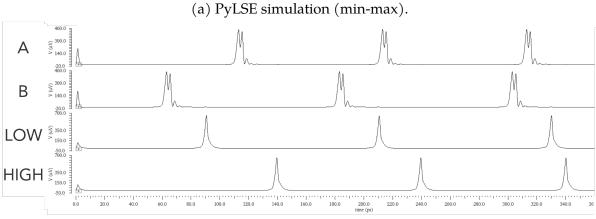

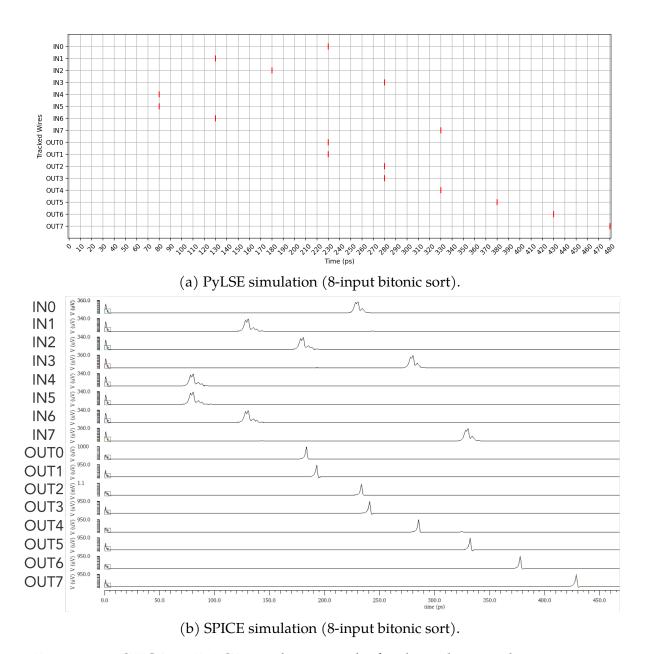

$$\begin{aligned} \operatorname{applyFn}((\lambda\vec{x}_1.e,\vec{v}_1),\vec{v}_2,\rho) &= \\ \begin{cases} v & \text{if } |\vec{v}_2| = 0, |\vec{v}_1| = |\vec{x}_1|, \text{ and} \\ \rho[\vec{x}_1 \mapsto \vec{v}_1] \vdash e \Downarrow v \\ \text{if } |\vec{v}_2| = 0 \text{ and } |\vec{v}_1| < |\vec{x}_1| \\ \operatorname{applyFn}((\lambda\vec{x}_1.e,\vec{v}_1 :+ \operatorname{hd}(\vec{v}_2)),\operatorname{tl}(\vec{v}_2),\rho) & \text{if } |\vec{v}_2| > 0 \text{ and } |\vec{v}_1| < |\vec{x}_1| \\ \operatorname{applyFn}((\lambda\vec{x}_2.e',\vec{v}_3),\vec{v}_2,\rho) & \text{if } |\vec{v}_2| > 0, |\vec{x}_1| = |\vec{v}_1|, \text{ and} \\ \rho[\vec{x}_1 \mapsto \vec{v}_1] \vdash e \Downarrow (\lambda\vec{x}_2.e',\vec{v}_3) \end{aligned}$$