# **UC Davis**

## **UC Davis Electronic Theses and Dissertations**

#### **Title**

A Framework for Managing Heterogeneous Memory for Large Scale Machine Learning Workloads

#### **Permalink**

https://escholarship.org/uc/item/7k32s3tv

#### **Author**

Hildebrand, Mark

#### **Publication Date**

2022

Peer reviewed|Thesis/dissertation

A Framework for Managing Heterogeneous Memory for Large Scale Machine Learning Workloads

By

# MARK HILDEBRAND DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Venkatesh Akella, Chair

Jason Lowe-Power

Soheil Ghiasi

${\bf Committee \ in \ Charge}$

2022

# Contents

|        | tract<br>nowledgments                                                          | iv<br>vi |

|--------|--------------------------------------------------------------------------------|----------|

| Chapte | er 1. Introduction                                                             | 1        |

| 1.1.   | Introduction                                                                   | 1        |

| 1.2.   | Intel Optane DC PMM                                                            | 2        |

| 1.3.   | Research Motivation                                                            | 5        |

| 1.4.   | Dissertation Contributions and Organization                                    | 6        |

| Chapte | er 2. Limitations of Hardware Managed Gigascale DRAM Caches                    | 8        |

| 2.1.   | Introduction                                                                   | 8        |

| 2.2.   | Background and Related Work                                                    | 10       |

| 2.3.   | Evaluation Methodology and Validation                                          | 10       |

| 2.4.   | DRAM Cache / 2LM Mode                                                          | 15       |

| 2.5.   | Case Study 1: Convolutional Neural Networks                                    | 20       |

| 2.6.   | Case Study 2: Graph Processing                                                 | 25       |

| 2.7.   | Discussion and Mitigation Strategies                                           | 29       |

| Chapte | er 3. Compiler-Based Heterogeneous Memory Management for Statically Analyzable |          |

|        | Workloads                                                                      | 31       |

| 3.1.   | Introduction                                                                   | 31       |

| 3.2.   | Background                                                                     | 33       |

| 3.3.   | $\operatorname{AutoTM}$                                                        | 36       |

| 3.4.   | Implementation Details                                                         | 41       |

| 3.5.   | Evaluation Methodology                                                         | 43       |

| 3.6.   | Results                                                                        | 45       |

| 3.7.   | Extending AutoTM                                                               | 53       |

| 3.8.   | Related Work                                                                   | 57       |

| 3.9.   | Conclusions                                                                    | 58       |

| Chapte | er 4. Generalizing Heterogeneous Memory Management                             | 60       |

| 4.1.   | Introduction                                                                   | 60       |

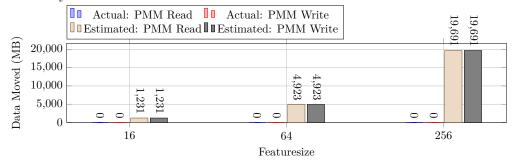

| 4.2.   | A Generic Heterogeneous Memory Management System                               | 61       |

| 4.3.   | Basis for the Data Manager and Modular Policy                                  | 69       |

| 4.4.   | CachedArrays Implementation                                                    | 77       |

| 4.5.   | Annotations for CNN Workloads                                                  | 81       |

| 4.6.   | Evaluation Methodology                                                         | 85       |

| 4.7.   | Results                                                                        | 90       |

| 4.8.   | Related Work                                                                   | 95       |

| 4.9. Discussion                                      | 96  |

|------------------------------------------------------|-----|

| Chapter 5. DLRM Case Study                           | 100 |

| 5.1. Introduction                                    | 100 |

| 5.2. Embedding Table Implementation                  | 102 |

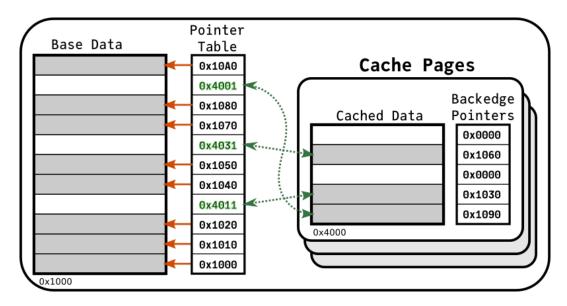

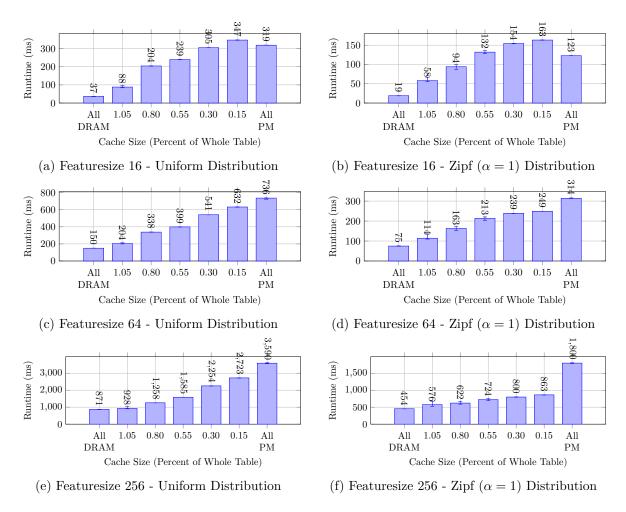

| 5.3. Embedding Table Experiments                     | 107 |

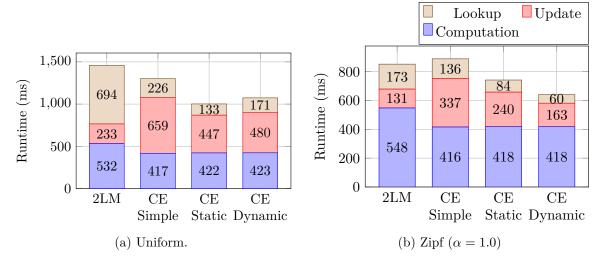

| 5.4. Software Caches for Gigascale Embedding Tables  | 116 |

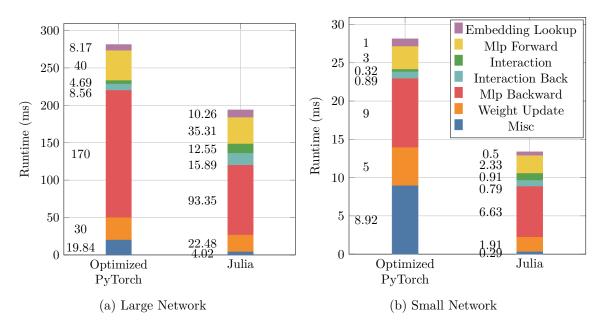

| 5.5. DLRM Implementation                             | 123 |

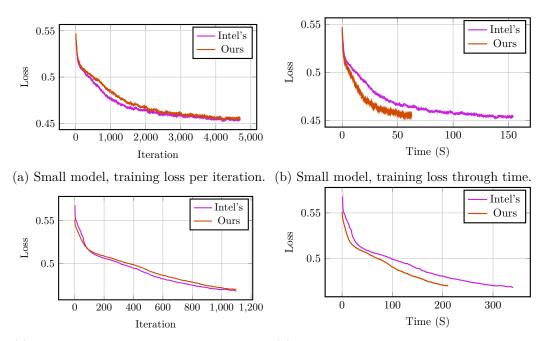

| 5.6. End-to-End DLRM Performance of CachedEmbeddings | 126 |

| 5.7. Related Work                                    | 130 |

| Chapter 6. Conclusions and Future Work               | 132 |

| 6.1. Limitations                                     | 132 |

| 6.2. Hardware Support for Data Tiering               | 133 |

| Appendix A. OneDNN Wrapper                           | 136 |

| A.1. OneDNN Summary                                  | 136 |

| A.2. Exposing the C API                              | 137 |

| A.3. Exposing Types to Julia                         | 140 |

| A.4. Putting it all Together                         | 142 |

| Bibliography                                         | 144 |

#### Abstract

The memory requirements of emerging applications, especially in the domain of machine learning workloads, is outpacing the capacity of traditional memory devices like DRAM. At the same time, heterogeneity in the memory hierarchy is emerging on multiple fronts both with high-capacity, low-bandwidth devices like Intel Optane Data-Center (DC) Persistent Memory Modules (PMM), and low-capacity, high-bandwidth devices like High Bandwidth Memory (HBM). A fundamental question introduced by this heterogeneity is: how do we efficiently manage application data to fully exploit the properties of the underlying memory technologies? This work explores techniques and ideas towards answering this question and understanding the performance implications of heterogeneous memory.

First, Intel's DRAM cache mode for Optane DC is reverse engineered using a suite of microbenchmarks and large scale machine learning applications. It is discovered that for machine learning training applications with large memory footprints and large-scale graph analytics, the DRAM cache behaves poorly with significant access amplification and low bandwidth utilization. There are three reasons for this performance degradation: (1) inflexible direct mapped policy leading to conflict misses, (2) poor traffic shaping cause by on-demand accesses and metadata management, and (3) lack of program semantic insight leading to many unnecessary and slow dirty data writebacks.

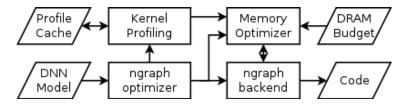

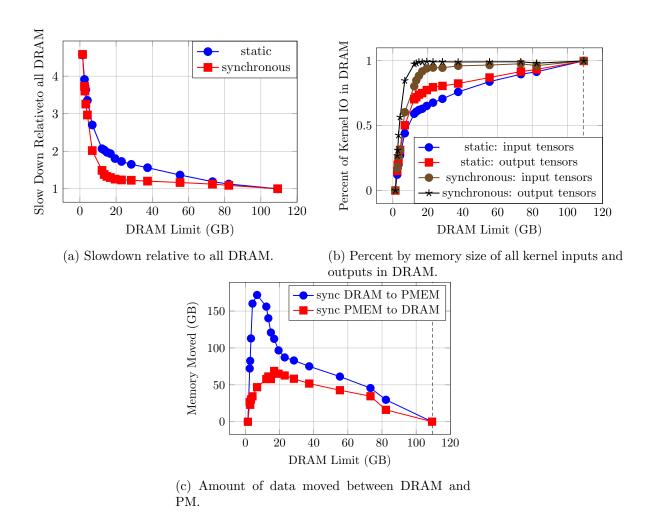

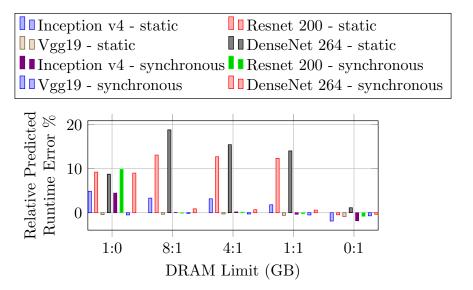

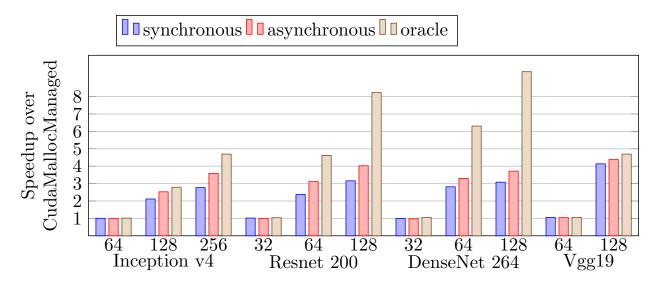

Next, AutoTM, a profile-guided compiler-based optimization technique that uses Integer Linear Programming to derive optimal tensor placement and movement for machine learning training in heterogeneous memory systems, is presented. The nGraph compiler is modified to implement AutoTM for two different systems: a CPU-based system with a combination of DRAM and Optane DC and a GPU-based system capable of using both GPU and CPU memory For DRAM/Optane DC systems, AutoTM outperforms the DRAM cache by as much as  $3\times$  and as much as  $4\times$  for the transparent cudaMallocManaged for GPU/CPU systems.

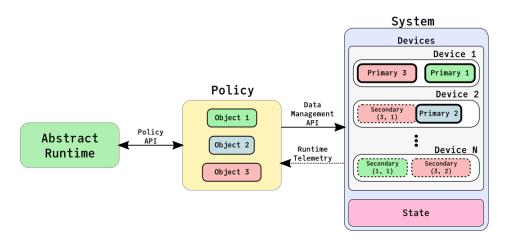

The third part of this work generalizes memory management primitives. A generic heterogeneous memory management framework can be broken into three parts: the *system* (the entity responsible for managing data and metadata), the *policy* (the entity orchestrating the placement and movement of data), and the *abstract runtime* (the application or runtime that is actually using the data). The key insight is the modularity of this organization. Upon this framework is built

CachedArrays, a policy/system package implemented in the Julia programming language. Unlike AutoTM, CachedArrays works for applications with dynamic control flow and improves end-to-end convolutional neural network (CNN) training performance by up to  $2\times$  over the DRAM cache.

Finally, to demonstrate the generality of this framework, it is applied to gigabyte scale embedding tables for large DLRM workloads. A performance analysis of the design space embedding table lookup and update operations on Xeon CPUs is conducted. This leads to the implementation of CachedEmbeddings, an instance of the generic heterogeneous memory management framework optimized for small-sized random memory accesses. Using a high-performance DLRM implementation, CachedEmbeddings out performs the DRAM cache for end-to-end DLRM training by up to  $1.45\times$  by using a modular, distribution-dependant policy.

#### Acknowledgments

This dissertation would never have seen the light of day were it not the selfless aid of many individuals along the way.

First, I wish to express my sincere gratitude towards my advisors and mentors Professor Venkatesh Akella and Professor Jason Lowe-Power. Venkatesh recruited my to work with something called "Optane" at a crucial point in my degree adventure, and I'll forever be grateful for his patience, guidance, and expertise, both for this dissertation and for the papers published along the way. Jason is the one of the best researchers I have ever met and is a role model professor in all areas. I am very grateful to have worked with him.

Special thanks to Professor Soheil Ghiasi for serving on my dissertation and qualifying examination committees. I appreciate your valuable feedback and insightful questions. I also wish to thank Professors Zhou Yu and Houman Homayoun for serving on my qualifying examination committee.

This work would not have been possible without the support Jawad B. Khan and Sanjeev Trika, the project's sponsors at Intel. I deeply appreciate their expertise, feedback, and insights regarding Optane DC memory. It was a joy working with you two! I would also like to thank the Intel corporation and especially the IT professionals working there for providing access to Optane equipped servers for running experiments.

Many thanks to Terry O'Neill for his mentorship and worldly wisdom. I am also thankful for Julian T. Angeles for our collaboration in understanding the implications of Intel's DRAM cache and for our adventures in general programming mayhem. Thanks should also go to Bobby Bruce for his endless encouragement and bottomless pot of coffee.

Thanks should also go to the other members of the Davis Architecture Research Group not previously mentioned, including but by no means limited to Mahyar Samani, Maryam Babaie, Ayaz Akram, Hoa Nguyen, Kaustav Goswami, Toluwanimi Odemuyiwa, Marjan Fariborz, Kramer Straube, Professor Matthew Farrens, Professor Chris Nitta, Melissa Katherine Jost, Kelly Nguyen, Bradley Wang, Nikitha Muddireddy, and Nima Ganjehloo.

I would also like to acknowledge the members of the VLSI Computation Lab where I spent the first few years of my PhD journey. In particular, Professor Bevan Baas, Brent Bohnenstiehl, Timothy Andreas, Satyabrata Sarangi, Shifu Wu, Professor Aaron Stillmaker, Jon Pimentel, Arthur Hlaing, and Filipe Borges.

I want to express my deepest gratitude towards my friend Matthew Toney. I do not think I would have seen this through without your support and steadfast example. You are an inspiration Matt!

I also want to thank Fishstix for all the joy the furry feline brought into my life. May she rest in peace.

Thank you to all my coworkers at the Rocknasium for creating a comfortable and supportive atmosphere. It has been such a blessing to be able to retreat to the climbing gym over these years.

Finally, I wish to extend my sincerest appreciation towards my brother and parents for all their support. To my father, Brent Hildebrand, in particular, who passed away before I finished my degree: thank you for everything. I will try to live my life with honor and integrity, as you did yours.

#### CHAPTER 1

#### Introduction

#### 1.1. Introduction

For years, researchers, scientists, and engineers have been claiming the death of Moore's Law, the observation of exponential growth in silicon-based transistor density. And while foundries like TSMC continue to extract more performance out of silicon, it is undeniable that we have entered a new age of computer architecture design and programming paradigms. Programmers can not rely on general purpose hardware simply getting faster to fulfill the needs of modern data-center and machine learning workloads. Instead, we've entered an era of specialization.

In particular, the memory requirement of modern applications, particularly those related to machine learning (ML), are outpacing the improvement in capacities of memory devices. Often brought up in discussions about increasing memory pressure are the absurdly large language models being developed by the likes of OpenAI, Microsoft, and NVidia. For instance, in early February 2020, Microsoft announced Turing-NLG<sup>1</sup>, a 17-billion parameter language model. Later that same year, OpenAI announced the 175-billion parameter GPT-3 in 2020 [10]. Not to be out-done, Microsoft teamed up with NVidia to produce Megatron-Turing NLG in late 2021, with a memory footprint of nearly 17 TB required for training [98]. It can be debated whether further language model inflation is the best way of improving model performance versus, for example, improving model architecture. Nevertheless, this provides an example of workloads taxing the memory capacity of server-scale computers.

Deploying and training such models requires significant infrastructure, consisting of hundreds of GPUs. To illustrate how extreme this gets, results from MLPerf Training 0.7 [63] (a benchmark suite for comparing system performance for Machine Learning (ML) models) shows Nvidia distributing training to over 2000 GPUs and Google using over 4000 TPU-v3<sup>2</sup>. The cost of these large

$<sup>^{1}</sup> https://www.microsoft.com/en-us/research/blog/turing-nlg-a-17-billion-parameter-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft/linear-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-microsoft-language-model-by-mi$

<sup>&</sup>lt;sup>2</sup>https://mlperf.org/training-results-0-7

scale deployments is such that only the largest companies are capable of pushing the boundaries in large scale ML research.

As models continue to grow, memory capacity and bandwidth will continue to be key bottlenecks. Existing approaches to distribute these models such as data parallelism and model parallelism

might not be sufficient. For example, data parallelism requires large batchsizes to achieve high computational performance on each worker. However, too large a batchsize may require more time to

train a network due to poor convergence [64]. Model parallelism is promising, but brings with it

its own challenges including effectively managing communication delay and synchronization.

At the same time, the computing industry is moving more and more towards heterogeneity in the memory system [8, 39, 48, 101]. This heterogeneity introduces different memory technologies within the same computing system, with various trade-offs. One such example is Intel Optane Data-Center (DC) [39], an emerging non-volatile memory technology offering significantly higher memory capacities than DRAM albeit with lower performance. Applications with increasing memory requirement may take advantage of the capacity offered by this technology, but only if doing so does not incur an unacceptable performance penalty. In this dissertation, we will investigate techniques for managing heterogeneous memory systems, for deciding when to place data in a small fast memory (e.g., DRAM) or a large slow memory (e.g., Optane DC) to utilize the advantages of both. Thanks to the generosity of this project's sponsors, a real DRAM/Optane DC based system will be used as a test-bed for the ideas presented within this dissertation. However, it is hoped that these ideas generalize to the broader landscape of emerging heterogeneous memory systems.

#### 1.2. Intel Optane DC PMM

Intel Optane Data-Center (DC) Persistent Memory Modules (PMM) are non-volatile random access memory (NVRAM) devices based on phase change memory designed for direct load/store random access similar to DRAM [39,48]. The first two generations of these devices were designed to live on the DRAM bus, using a modified protocol called "DDRT". Due to the modified DDRT protocol, Optane DC required CPUs with modified memory controllers. Because of their residence on the DDR bus, direct loads and stores to these devices are possible.

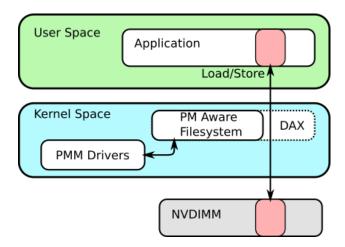

FIGURE 1.1. App Direct persistent memory programming model.

Low-level configuration provisioning of these devices is performed through the **ipmctl**<sup>3</sup> tool and the **ndctl**<sup>4</sup> tool is used to expose these devices to the host operating system and user-level applications. There are three main ways in which persistent memory (PM) is available to applications.

1.2.1. App Direct. Unlike traditional block-based storage devices, persistent memory (PM) devices support "direct access" (DAX) file systems (Figure 1.1). Using this type of file system changes the behavior of memory mapping files. Instead of maintaining a DRAM buffer, the kernel instead directly memory maps the backing file into the user application. After mapping, any loads and stores to the corresponding virtual addresses go directly to the underlying media, bypassing kernel layers entirely [48].

When used as *volatile* memory (i.e., persistence is not required), an application can treat the memory obtained from this memory mapping exactly as it would normal memory. However, if persistence *is* required, than care needs to be taken by the application to preserve data integrity in the case of an interrupting event. For example, a power failure midway through a large write can result in a torn write, leaving the file on persistent memory in an inconsistent state. To that end, libraries like PMDK<sup>5</sup> and new x86 hardware instructions like **clflushopt** and **clwb** (described in Table 1.1) allow write to PM to occur transactionally (i.e., either completely succeed or completely fail).

<sup>3</sup>https://github.com/intel/ipmctl

<sup>4</sup>https://github.com/pmem/ndctl

<sup>5</sup>https://github.com/pmem/pmdk

| Instruction | Description                                                          |  |  |  |  |  |

|-------------|----------------------------------------------------------------------|--|--|--|--|--|

| clflushopt  | Evict the corresponding cache line from all levels of the CPU cache  |  |  |  |  |  |

|             | hierarchy. Unlike the older clflush operation, clflushopt may be     |  |  |  |  |  |

|             | executed out of order with other clflushopt instructions, leading to |  |  |  |  |  |

|             | potentially better performance of many such instructions.            |  |  |  |  |  |

| clwb        | Write back the corresponding cache line to main memory. The cache    |  |  |  |  |  |

|             | line may be retained in the CPU cache hierarchy.                     |  |  |  |  |  |

TABLE 1.1. Extensions to the x86 ISA to support persistent memory. When cache line writes destined for PM reach the memory controller, they enter the persistency domain where they are guaranteed to commit even in the event of a power failure [81].

The focus of this dissertation is on using PM as volatile memory for bandwidth intense applications. As such, we will not explore the implications of PM transactions. While conceptually simple to use in an application, Optane DC cannot serve as a drop-in replacement for DRAM as load/store latency is on the order of 3× higher than DRAM with 60% lower bandwidth [109]. What these devices offer, instead is capacity with up to 512 GB per module. At this size, a Xeon CPU with 6 memory channels can have up to 3 TB of random access persistent memory in addition to DRAM.

Because of these trade-offs (higher capacity, but lower bandwidth/higher latency), Optane DC serve as an excellent real-world test case for heterogeneous data tiering and management.

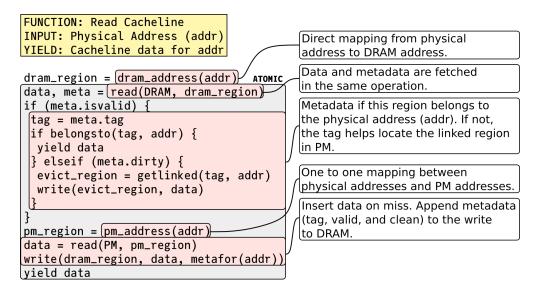

1.2.2. Memory Mode (2LM). Persistent memory modules can be used in the so-called 2LM (also known as memory mode or cached) [48], where PM act transparently as system memory. In this mode, system DRAM serves as a direct mapped cache for the non-volatile memory. The access granularity of this cache is 64B, matching the cache line size of the underlying CPU. While not mentioned explicitly, Intel patents suggest that cache tags are stored along with ECC data [84]. ECC DRAM is implemented by adding an extra DRAM module to each DIMM. Thus, each 64B data transaction for each DIMM is accompanied by 8 B (64 bits) of ECC. Of these 64 bits of ECC data, only 20 [13] are required to provide Single Error Correction/Double Error Detection redundancy, leaving ample room for tag metadata, including both physical address and cache line state. Our data is consistent with this approach.

This operating mode was likely introduced as a way to lower the barrier to adoption of PM, though only for the capacity aspect and not for persistence. For example, when operating in 2LM, a system like that described above may see as much as 3 TB of memory per socket. DRAM caches have been well studied in simulation [17,18,50,51,59,61,80]. However, these previous works have not taken all of the realistic implementation details (e.g., tracking "coherence" of request issued to PM) leaving gaps between research proposals and the actual implementation. Chapter 2 will discuss the design of this DRAM cache in detail and outline many of the performance problems introduced by such a cache.

1.2.3. PM as a NUMA Node. A third way to use to PM as volatile memory is to use the daxctl<sup>6</sup> tool expose the persistent memory modules as extra NUMA nodes. This allows existing NUMA aware allocation and memory pinning to take advantage of the extra capacity offered by PM. However, this still does not address the main question: how to efficiently use this memory?

#### 1.3. Research Motivation

The question to answer in heterogeneous memory systems, regardless of whether it's for machine learning or more general applications, is where to place data and when should it be moved between memory devices. One approach is to simply use something like the transparent DRAM cache described in the previous section. Unfortunately, as we will show in Chapter 2, this can lead to sub-optimal performance. For machine learning training on GPUs, bespoke solutions like vDNN [89] and ZeRO [83] use application specific knowledge to answer this question. However, these specialized approaches approaches only apply to heterogeneous memory systems where only memory in the "device local" memory location is directly byte-level accessible. This is quite different from what emerging heterogeneous memory systems will look like.

1.3.1. Examples of Emerging Heterogeneous Memory Systems. Recent advances in interconnect technology and device packaging have lead to new classes of heterogeneous memory systems. One example is the previously mentioned Optane DC, which allow byte-level access through the DDR bus. Additionally, emerging technologies like CXL will extend byte-level addressability and cache-coherence to fabric-attached devices [101]. New generations of Intel CPUs like Sapphire Rapids, in addition to CXL attach Optane PM, will also include on-package high-bandwidth memory (HBM) for yet another level of heterogeneous memory. [8].

<sup>6</sup>https://github.com/pmem/ndctl/tree/main/daxctl

All of these emerging technologies and many more like them will involve different trade-offs and decisions to be made when it comes to heterogeneous memory management. Existing solutions like block-based caches [43,48], virtual page-management [54,108], and manual programmer development [33] are either not efficient enough or scalable enough. Furthermore, while tools like Intel's Persistent Memory Development Kit<sup>7</sup> and Samsung's recent Scalable Memory Development Kit<sup>8</sup> are providing tools for exposing heterogeneous memory to an application, there's still the question of how to use this memory effectively.

1.3.2. Summary. In this work, we seek to understand some of the potential performance pit-falls associated with Optane PM and develop techniques for scalably managing the proliferation of emerging heterogeneous memory technologies. While the bulk of this dissertation targets a heterogeneous CPU-based system with DRAM and Optane PM targeting machine learning workloads, the goal is for the techniques and insights developed here to generalize to other similar systems as well. For example, in Chapter 3, we will show that the techniques developed indeed generalize to a GPU-CPU heterogeneous system. Finally, while extracting the best performance of a system requires a detailed understanding of the memory technologies involved and their respective tradeoffs, we will show in Chapters 4 and 5.1 that a common approach to developing a heterogeneous memory management framework can be used for two very different classes of problems.

#### 1.4. Dissertation Contributions and Organization

The rest of this dissertation is organized as follows. Chapter 2 reverse engineers the so called "2LM" DRAM cache implementation on Intel Cascade-Lake servers. Using several machine learning and graph processing benchmarks running on real hardware, it is shown that the hardware only nature of this approach to heterogeneous memory management suffers in a number of key areas such as low bandwidth utilization and a lack of program semantic information.

Chapter 3 introduces AutoTM, a Integer Linear Programming (ILP) based technique for optimizing memory location and movement between DRAM and Optane PM for CNN training. This technique yields up to a 3x performance over the native 2LM hardware DRAM cache. AutoTM is further extended to manage GPU-CPU memory for GPU-based training.

<sup>&</sup>lt;sup>7</sup>https://github.com/pmem/pmdk

<sup>8</sup>https://github.com/OpenMPDK/SMDK

Chapter 4, we demonstrate a generalized runtime framework for managing heterogeneous memory. A generalized API for a multi-level memory manager is presented and implemented in the Julia programming language. Using this approach, the dependency for incorporating heterogeneous memory into application development can be inverted. That is, this framework may be used as a compositional building block for application development rather than developing bespoke memory management solutions for applications, such as the case in AutoTM.

Chapter 5.1 builds on the memory management API to implement two-level memory management for the fine-grained memory access pattern found Deep Learning Recommendation Model (DLRM) embedding table lookups. An abstract API for embedding table lookup and updates is presented the DLRM implemented with it outperforms a state-of-the-art PyTorch implementation from Intel.

#### CHAPTER 2

## Limitations of Hardware Managed Gigascale DRAM Caches

#### 2.1. Introduction

Large scale machine learning and large scale graph analytics represent workloads of interest for high performance server in the forseeable future. Emerging machine learning models in NLP and recommendation engines (such as GPT3 [10] and DLRM [67]) can have over 100 billion parameters requiring hundreds of gigabytes to terabytes of memory for training. Similarly real world graphs can have hundreds of billions of edges, requiring hundreds of gigabytes to just store the graphs [72]. As a result, the cost of memory (DRAM) is becoming an important concern in datacenters and other high performance computing facilities dealing with large scale data analysis [30, 31].

To address this challenge Intel, as mentioned in Chapter 1, introduced Optane Data-Center Persistent-Memory-Modules (DC PMM), a persistent memory  $(PM)^1$ ) technology based on phase change memory that can serve as a drop-in replacement for conventional DRAM [39]. While programmers can use the PM as a main memory DRAM replacement using normal load and store instructions, the latency is  $3 \times$  higher and the bandwidth is at least 60% lower than DRAM [109]. Traditionally, to hide high memory latency and limited bandwidth, computer architects have turned to hardware caches. In this tradition, Intel Cascade Lake systems implement a DRAM cache for PM. DRAM caches have been well studied in simulation [17,18,50,51,59,61,80]. These previous works have not taken all of the realistic implementation details (e.g., tracking "coherence" of request issued to PM) leaving gaps between research proposals and the actual implementation.

In this chapter, we analyze the performance of an actual implementation of the DRAM cache in Intel's Cascade Lake based servers on workloads whose memory footprint greatly exceeds the capacity of DRAM. We first analyze the behavior of the DRAM cache with microbenchmarks to reverse engineer its design and understand pathological performance cliffs. It is well known that

<sup>&</sup>lt;sup>1</sup>This chapter uses the term "PM" to refer to memory located on the Optane DC DIMMs.

this DRAM cache is implemented as a direct-mapped [48], and we find that the tags are stored ECC bits of the DRAM DIMMs to limits the access overhead. However, we also find that in many cases there are extra DRAM accesses required to update the cache metadata (e.g., tag reads before writes) which can significantly decrease the performance of miss-heavy workloads. In fact, using microbenchmarks on real hardware, we find that a single demand request can require up to 5 memory accesses.

After using microbenchmarks to understand the cache behavior and implementation, we analyze two memory capacity limited workloads: training large convolutional neural networks (CNNs) [41, 46,97,100] and graph analytics [33]. We show that in these realistic workloads, the DRAM cache can hurt performance even with a modest cache miss rate. We show that for the CNN workload, software management can increase performance by up to  $3\times$  over the DRAM cache. Furthermore, we show significant access amplification and bandwidth reduction for graph based workloads.

Fundamentally, we find three characteristics of this DRAM cache implementation which causes performance degradation for workloads with large working sets.

- (1) The direct-mapped, insert on miss cache is inflexible and many conflicts can increase the miss rate.

- (2) Under high miss rates, memory bandwidth is poorly utilized with extra bandwidth used for non-demand accesses (e.g., fills, writebacks, and tag checks).

- (3) For some workloads the data in the DRAM cache is *temporary* or *dead* from the program's perspective leading to wasted data movement.

While some of these characteristics may be alleviated in future hardware, we can use these three insights on today's hardware to improve the performance of heterogeneous memory systems.

The rest of the chapter is organized as follows. We start with the quick background on Intel's PM technology and related work in the area of benchmarking PM from recent literature. In Section 2.3 we present the details of the evaluation and validation framework. Section 2.4 follows up with a detailed analysis of the DRAM cache in these systems. Next we use two representative case studies from deep learning and graph analytics to corroborate the findings from the microbenchmark experiments. We end the chapter with a discussion of the results and ideas for software based mitigation strategies in Section 2.7.

#### 2.2. Background and Related Work

There have been several efforts in research literature that focus on evaluating the system level performance of Optane DC [48, 76, 77, 92, 102], especially in comparison with DRAM. More recently, Wang et. al [107] developed a profiler and PM simulator to model the microarchitecture of PM in general. However, to the best of our knowledge there has been no effort in trying understand the performance of DRAM caches in large scale PM-based systems. However, the tools described by Wang [107] could be used for hardware/software codesign of DRAM caches in the future, building on the findings in this chapter.

On the application front there has been work on the design of data structures and algorithms to mitigate the disadvantages of PM, chiefly the slower and asymmetric read/write latency and bandwidth [12,26,71,75,95]. Dhulipala et. al [26] and Gill et. al [33] evaluate the performance of large scale graph analytics on PM based systems. These works focus on application performance evaluation and optimization but do not delve into the details of behavior of the DRAM cache (the 2LM mode) and why they do not work well on these applications. The goal of this work is to fill this gap. In fact, one could view Sage [26] as a software technique to mitigate the limitations of DRAM caches in PM based systems as discussed in Section 2.6 and Section 2.7

#### 2.3. Evaluation Methodology and Validation

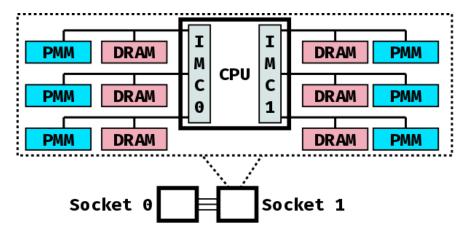

2.3.1. Test System. Our test machine is a two-socket Xeon server (illustrated in Figure 2.1) equipped with 24-core Cascade Lake engineering sample CPUs. The CPU on each socket has two integrated memory controllers (IMC), each with three memory channels. Integrated memory controllers are responsible for performing the actual reads and writes to DRAM and PM. Each memory channel is populated with a 32 GiB DDR4 DRAM DIMM and a 512 GiB Optane DC DIMM.

#### 2.3.2. Evaluation Methodology.

2.3.2.1. Kernel Benchmark Generator. To test the basic bandwidth performance of DRAM and PM, both in 1LM and 2LM, we made a custom open source benchmark generator<sup>2</sup> written in Julia [7]. The generator uses Julia's metaprogramming and just-in-time compilation to generate

<sup>&</sup>lt;sup>2</sup>https://github.com/darchr/KernelBenchmarks.jl

FIGURE 2.1. Diagram of our test platform. Each socket has 192 GiB of DRAM and 3 TB of PM spread across six memory channels.

custom low overhead load and store loops. Memory can be accessed either sequentially or pseudorandomly. When accessed pseudo-randomly, we ensure that each addresses is touched exactly once (i.e. no repeats) using a maximum length Linear Feedback Shift Register to generate array indices. Furthermore, for pseudo-random iteration, access granularity ranges from 64 B to 512 B. We found sequential iteration is largely indifferent to access granularity, so only a single result for sequential access is reported. For these experiments, we used read-only, write-only, and read-modify-write operations. We explore both *standard* or *nontemporal* instructions for all stores. *Nontemporal* stores bypass the on-chip cache, allowing us to directly study the behavior of LLC writes to the memory controller. Data is partitioned evenly across threads when multithreading is used.

Listing 2.1 shows the generated x86 code for a 512 B, nontemporal write-only workload that pseudo-randomly accesses array addresses using a LFSR. Lines 1-3 load arguments where r8 is the base pointer for the array segment and r9 is the starting seed for the LFSR. The write-only data is broadcast to the 64 B AVX512 register (zmm0) in lines 4 and 5. The main loop body encompases lines 7 to 32. The 512 B write takes 8 nontemporal vector stores (vmovnts). Lines 22 to 32 implement the LFSR as annotated in the listing. Listing 2.2 illustrates x86 assembly for a sequential read-modify-write kernel that uses 16 B loads and stores. As can be seen, the generated assembly for these microbenchmarks is minimal, providing high-performance implementations of the kernels in question.

```

1

mov rax, qword ptr [rdi]

2

mov r8, qword ptr [rax]

mov r9, qword ptr [rsi + 16]

3

4

movabs rax, offset .rodata.cst4

5

vbroadcastss

zmm0, dword ptr [rax]

6

mov rdx, r9

7

L29:

8

mov rax, rdx

shl rax, 9

10

vmovntps

zmmword ptr [rax + r8 - 512], zmm0 # + 512 B contiguous write.

11

vmovntps

zmmword ptr [rax + r8 - 448], zmm0 #

zmmword ptr [rax + r8 - 384], zmm0 #

12

vmovntps

13

[rax + r8 - 320], zmm0 #

vmovntps

zmmword ptr

[rax + r8 - 256], zmm0 #

14

vmovntps

zmmword ptr

zmmword ptr [rax + r8 - 192], zmm0 #

15

vmovntps

zmmword ptr [rax + r8 - 128], zmm0 #

vmovntps

16

zmmword ptr [rax + r8 - 64], zmm0 #

17

vmovntps

18

mov rdi, qword ptr [rsi]

19

mov rax, qword ptr [rsi + 8]

20

nop dword ptr [rax + rax]

21

L112:

22

mov ecx, edx # + Generate the next term in the LFSR sequence.

23

and ecx, 1

24

neg rcx

25

and rcx, rax #

26

27

sar rdx

xor rdx, rcx # +

cmp rdx, r9 # + Compare with seed (if equal, done with iteration).

28

29

je L141

30

cmp rdx, rdi # + Compare with max length. If exceeding, iterate again to yield an

jg L112

31

# + in-bounds index.

32

jmp L29

33

L141:

34

vzeroupper

35

nop word ptr cs:[rax + rax]

36

```

LISTING 2.1. Auto Generated code for 512B non-temporal writes using pseudorandom array indexing.

2.3.2.2. Hardware Performance Counters. To measure DRAM and PM traffic, we use uncore hardware performance counters located in each IMC. These counters capture column access strobes (CAS) for DRAM reads and writes. The Cascade Lake generation added IMC counters for PM read and write requests, and 2LM tag statistics including tag hit, tag miss clean, and tag miss dirty, which will be explained in more detail later. Event codes and masks for the counters used in this work are given in Table 2.1. Results from the hardware performance counters are validated with the expected data movement and benchmark wall clock time.

```

mov rcx, qword ptr [rsi]

1

2

mov rax, qword ptr [rsi + 8]

3

sub rax, rcx

4

jl L81

5

+ Bounds check and prepare loop induction variable.

mov rdx, qword ptr [rdi]

6

mov rdx, qword ptr [rdx]

7

mov rsi, qword ptr [rdi + 8] #

8

shl rsi, 2

9

#

shl rcx, 4

10

add rcx, rsi

11

add rcx, rdx

12

add rcx, -20

13

inc rax

14

movabs rdx, offset .rodata.cst4

# + Broadcast increment variable to register.

15

xmm0, dword ptr [rdx] # +

vbroadcastss

16

nop word ptr [rax + rax]

L64:

17

18

vaddps xmm1, xmm0, xmmword ptr [rcx] # + Main loop body.

19

vmovaps xmmword ptr [rcx], xmm1

#

20

add rcx, 16

# |

21

dec rax

22

23

jne L64

# +

L81:

24

ret

25

nop word ptr cs:[rax + rax]

```

LISTING 2.2. Generated code for a sequential read-modify-write kernel using 16 B loads and stores.

| Metric             | Event Code | Umask |

|--------------------|------------|-------|

| DRAM Reads         | 0x04       | 0x3   |

| DRAM Writes        | 0x04       | 0xC   |

| PM Reads           | 0xEA       | 0x2   |

| PM Writes          | 0xEA       | 0x4   |

| 2LM Tag Hit        | 0xD3       | 0x1   |

| 2LM Tag Miss Clean | 0xD3       | 0x2   |

| 2LM Tag Miss Dirty | 0xD3       | 0x4   |

TABLE 2.1. Event codes and umasks for IMC performance counters used to gather data on DRAM, PM, and 2LM behavior. The events listed here all count 64B transactions. Events highlighed in bold were introduced in the Cascade Lake generation of processors.

Each benchmark was executed on a quiet system. Unless otherwise specified, all six Optane DC DIMMs are configured as a single interleaved set and experiments are run on a single socket to avoid NUMA overheads.

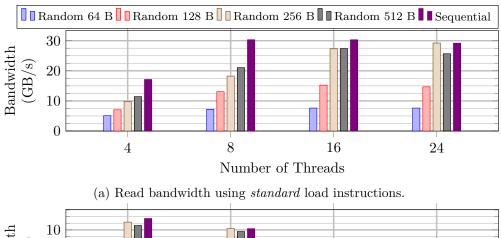

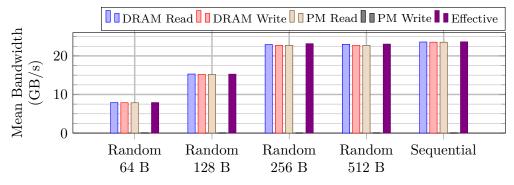

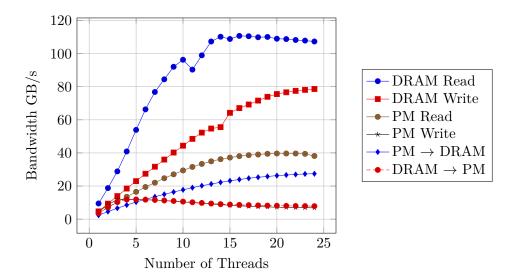

**2.3.3. PM Performance Results.** The results obtained here are in line with observations made by other researchers [33,48,76,92]. We highlight results that are relevant to our upcoming

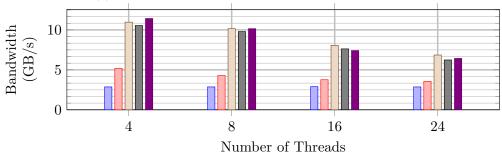

(b) Write bandwidth using nontemporal store instructions.

FIGURE 2.2. Bandwidth to 6 interleaved 512 GiB PM DIMMs.

discussion in Section 2.4 on the 2LM DRAM cache. Since read and write bandwidth to Optane DC is asymmetric, we will consider these separately. Figure 2.2a shows the read bandwidth of six interleaved 512 GB PM modules under varying thread counts. Sequential bandwidth scales with the number of threads up to a maximum 30 GB/s with 8 threads, at which it stops increasing. This result is slightly different than the 39 GB/s reported in other works [48] because our system uses 512 GiB DIMMs instead of 128 GiB or 256 GiB DIMMs. The 512 GiB DIMMs provide a maximum read bandwidth of 5.3 GB/s read bandwidth per DIMM while the others provide 6.8 GB/s [21].

Figure 2.2b demonstrates the write bandwidth of PM when using *nontemporal* stores. In addition to bypassing the on-chip cache, *nontemporal* stores do not need a Read-For-Ownership (RFO), a step in Intel's usual cache coherence protocol [22], and are critical for high PM write bandwidth [109]. Write bandwidth peaks with four threads, and is roughly the same for sequential and random access exceeding 256 B. Limited buffer space within the Optane DIMM decreases the media controller's ability to merge sequential 64 B writes into a single 256 B write, leading to write

TABLE 2.2. Summary of generated reads and writes for 2LM. Figure 2.3 shows details of why these requests generate these actions. The dirty data optimization (DDO) allows the IMC to elide the tag check for some writes.

|               | LLC Read |       |       | LLC Write |       |       |     |

|---------------|----------|-------|-------|-----------|-------|-------|-----|

|               | Hit      | Miss  |       | Hit       | Miss  |       | DDO |

|               |          | Clean | Dirty |           | Clean | Dirty |     |

| DRAM Read     | 1        | 1     | 1     | 1         | 1     | 1     |     |

| DRAM Write    |          | 1     | 1     | 1         | 2     | 2     | 1   |

| PM Read       |          | 1     | 1     |           | 1     | 1     |     |

| PM Write      |          |       | 1     |           |       | 1     |     |

| Amplification | 1        | 3     | 4     | 2         | 4     | 5     | 1   |

amplification and the observed drop in bandwidth [109]. In summary, with this system we can achieve just over to 30 GB/s read and 11 GB/s write to PM.

#### 2.4. DRAM Cache / 2LM Mode

As discussed in Section 1.2, Optane DIMs can act as system memory with DRAM operating as a transparent, hardware managed, direct-maped cache. In this section, we use microbenchmarks to try to deduce the performance implications of the Cascade Lake DRAM cache design. Our results are summarized in Table 2.2 and Figure 2.3.

2.4.1. Methodology. To study the behavior of the 2LM DRAM cache, we used the same benchmarks discussed in Section 2.3 and the same methodology for measuring bandwidth. In this case, data gathered from the performance counters allows us to differentiate DRAM and PM traffic. Furthermore, the tag related performance counters in each IMC allows us to correlate tag events with memory traffic. Each IMC only allows four events types to be recorded at a time. Since our benchmarks are long running and largely deterministic, we run them twice to obtain both bandwidth and tag events.

Table 2.2 summarizes the observed actions required for each type of access to the IMC. We define two types of requests to the IMC. An *LLC Read* is a request from the LLC for data from the DRAM cache or PM. This request is generated on a load or store miss at the LLC. Stores can generate an LLC read as they may require a RFO. An *LLC Write* is a request from the LLC to write back dirty data to the DRAM cache. LLC write requests are generated either when a dirty line is evicted from the LLC or from a *nontemporal* store.

Furthermore, the hardware performance counters differentiate between three different types of cache accesses: hit, clean miss, and dirty miss. A hit implies that address accessed by an LLC request is present in DRAM. A miss means that an address is not resident in DRAM and must be fetched from PM. Since this cache is direct mapped, a miss implies that some other data is occupying the set corresponding to the requested address. A miss is dirty if this aliasing data has been modified since its original insertion and thus must be written back to PM upon eviction.

To study read and write hits, we use the read-only and write-only benchmarks respectively on a 51 GiB array backed by 1 GiB hugepages to mitigate TLB overheads. Because the array is far larger than the 38 MB LLC cache, each CPU load generates an LLC read and each CPU nontemporal store generates an LLC write. This array is also small enough to fit in the DRAM cache without aliasing. Thus, all LLC reads/writes accesses will be cache hits.

Generating clean LLC read misses and dirty LLC write misses is also straightforward. We use a 420 GB array, which is over twice the size of the 192 GB DRAM cache per socket. Applying the read-only benchmark to this array for several iterations ensures a clean LLC read misses for each CPU load. Similarly, the write-only benchmark ensures that each *nontemporal* store generates a dirty LLC write miss.

Testing dirty LLC read misses and clean LLC write misses is more complicated. For dirty LLC read misses, we first prepare the 420 GB array from before by writing to it, making the entire DRAM cache is dirty. We then perform a single iteration of the read-only kernel. Thus, each CPU load early in the iteration generate LLC reads that will be a dirty miss in the cache. As the iteration progresses, however, a larger portion of these loads become clean misses as the dirty cache is replaced by clean data. Consequently, we determine cache behavior based on data collected early in the iteration. We use a similar procedure to prime and test clean LLC write misses.

When testing the behavior of the cache, we use *nontemporal* stores when writing. This ensures that the behavior shown by the IMC is purely the result of the incoming store and not an earlier RFO. For all benchmarks, we also compute an *effective* bandwidth as seen by the application. This is obtained using the size of the array and wall clock time for each benchmark.

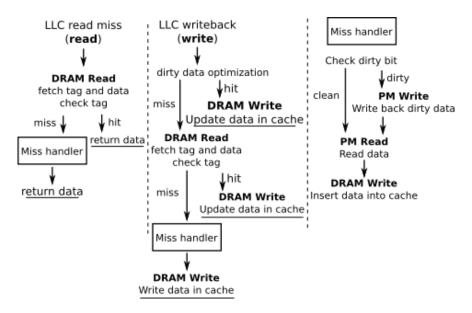

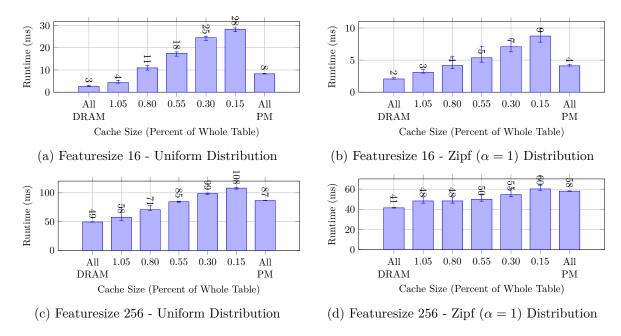

FIGURE 2.3. Flowchart showing the operation of the DRAM for LLC read misses which occur on a processor load or store which misses in the LLC and LLC write-backs which occur when a dirty block is evicted from the LLC. The miss handler is the same for reads and writes and is factored out on the right. Underlines indicate where the actions end, and bold shows the hardware actions. A summary of total memory accesses is given in Table 2.2.

While we only outlined several key benchmarks to test the different regimes of the DRAM cache, we also applied a whole range of microbenchmarks with different thread counts and access patterns to fully characterize the behavior of the cache and validate the results presented here.

**2.4.2. 2LM Observations.** Table 2.2 summarizes our findings for the cache events and Figure 2.3 demonstrates a flow chart of IMC logic that models this behavior. We describe each of these columns in turn. To help with our discussion, we use the term **access amplification** [62] as the ratio of *memory* accesses (i.e., both DRAM and PM) to demand accesses.

LLC read hits are simple. The IMC initiates a DRAM read, which fetches data along with the tag in the ECC bits. A tag check is performed and since the tag matches, the data is immediately forwarded with no access amplification.

Figure 2.4a shows bandwidth for the read-only benchmark in the 100% clean miss scenario. Note a 3× access amplification for each miss. Essentially, the tag miss is serviced by a miss handler, which fetches the requested cache line from PM, inserts into DRAM, and forwards to the CPU.

Dirty read misses are handled much the same as clean read misses. The only change is that the cache line evicted from DRAM must be written back to PM.

LLC write hits incur a  $2\times$  access amplification because the IMC must first emit a DRAM read to perform a tag check. Only upon verification of the tag can the line be safely written.

Next, we discuss dirty LLC write misses. Figure 2.4b shows collected bandwidth for the write-only benchmark where each nontemporal store is a dirty tag miss. Observe a 2× access amplification in DRAM writes alone. Upon receiving a completely dirty cache line store yielding a tag miss, we would expect the IMC to write the evicted line to PM and directly insert the incoming line to DRAM. This would yield a total of 1 DRAM read (for the tag check), 1 PM write, and 1 DRAM write. However, the data in Figure 2.4b suggests that this is not the case. Our best guess is that the memory controller always inserts on a miss (regardless of whether that miss was a read or write). The second DRAM write is thus the actual write of cache line to DRAM. Clean LLC write misses are similar dirty write misses without the PM write back.

2.4.3. Dirty Data Optimization. Finally, this brings us to the phenomenon that we call the Dirty Data Optimization (DDO). At times, the memory controller is able to elide the tag check (i.e. DRAM read) and instead directly forward LLC writes to DRAM. This can be seen in Figure 2.4c which shows the distribution of traffic for the read-modify-write benchmark in a 100% dirty LLC miss scenario using standard stores. The CPU load initiates a dirty LLC read miss (dirty from a previous write), accounting for one DRAM read (tag check) plus the traffic associated with a cache insert. Since standard stores are used, the subsequent CPU store will remain in the LLC for some time before being evicted and written to memory. Thus, there is low temporal locality between a cache line's load and its write back.

Due to this low locality, we would *expect* this delayed LLC write to require another tag check, resulting in a total of two DRAM reads per CPU load-store pair. However, this is not the case and it appears this second tag check is elided. While this could be explained by an inclusive cache, we found that this is not the case as it is possible to have small amounts (< 8 KiB) of aliasing data simultaneously within the CPU cache. Thus, we are not sure the exact mechanism driving this optimization.

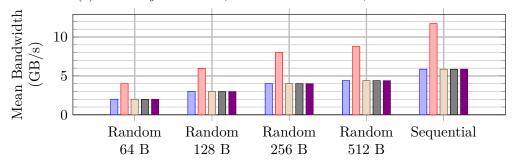

(a) Read-only benchmark, clean LLC read misses, 24 threads.

(b)  $\it Write-only$  benchmark, dirty LLC write misses, 24 threads,  $\it nontemporal$  stores. Using 4 threads only increases the maximum write bandwidth by 1 GB/s.

(c) Read-modify-write benchmark, dirty LLC read miss followed by a later DDO LLC write, 4 threads, standard stores. Sequential achieves the highest PM write bandwidth of any 2LM benchmark with neglibile difference between nontemporal and standard stores.

FIGURE 2.4. Benchmark results on a large array exceeding the size of the DRAM cache. Because the array size exceeds DRAM, the miss rate in the DRAM cache is 100%. The "effective" bar illustrates performance as seen by the application, computed by wall clock time and data accessed.

**2.4.4. Discussion.** We described our observation of 2LM's mechanics, but what does this mean for user applications? There are two points we want to make. First, contrast Figure 2.4, which shows the effective NVDIMM bandwidth in 2LM with a high miss rate, with Figures 2.2a and

2.2b, showing the maximum speed of PM. The highest PM read bandwidth in 2LM (Figure 2.4a) is 23 GB/s and the highest write bandwidth (Figure 2.4b) is 8 GB/s. This is 60% and 72% the demonstrated achievable bandwidth of our system's PM. This is the ideal case with well formed traffic. We expect applications with a large memory footprint (exactly those that would benefit from the large memory pool provided by PM) and a high DRAM cache miss rate to experience a severe bandwidth bottleneck. Second, cache misses are costly in terms of extra traffic generated, with LLC read and write misses generating up to  $3\times$  and  $5\times$  access amplification. This is costly both in terms of energy and lost bandwidth.

So far, we have demonstrated the potential for applications to experience bandwidth bottlenecks in 2LM. In the next two sections, we provide case studies demonstrating this effect on real applications.

#### 2.5. Case Study 1: Convolutional Neural Networks

In this section, we will take a deep dive into some of pitfalls a bandwidth and compute heavy application can fall into when running under 2LM. Specifically, we consider the problem of training deep Convolutional Neural Networks (CNNs) whose working set size greatly exceeds the physical DRAM of a system, requiring the extra memory provided by PM.

CNNs are typically expressed as a directed acyclic graph of computation primitives such as convolutions and matrix multiplications, that are heavy on compute, and operations such as batch normalization and concatenation that are heavy on bandwidth requirements. At a high level, a single *iteration* of training consists of a *forward* pass, during which the network is evaluated (almost) normally on a batch of training data (some kernels like Batch Normalization have slightly different versions for training and inference [47]). The output of the forward pass is compared to an expected output to generate a loss value, which is used in the backward pass to compute the partial derivative of the loss with respect to each of the trainable parameters of the network. The parameters of the network are adjusted based on the these derivatives. An important aspect of the backpropagation algorithm is that many intermediate values computed during the forward pass must be preserved to compute the backward pass. Thus, the active memory footprint of the network during an iteration

of training increases during the forward pass, then decreases during the backward pass. It takes many such iterations of training across different input samples to fully train a CNN.

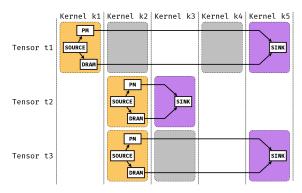

2.5.1. Methodology. We implemented three popular large CNNs: Inception v4 [100], Resnet 200 [41], and DenseNet [46] using the ngraph compiler [24] on the PM-based system described earlier. Intel's ngraph compiler is an optimizing compiler specifically targeting static deep neural networks that takes advantage of the Xeon CPU ISA. For these large networks, we scaled the training batch size until the overall footprint of these applications exceeded 650 GB, well beyond the capacity of the DRAM cache. All networks were run on a single NUMA node and assigned all 24 physical cores on that node with no hyper-threading. These networks were run for two warm up iterations to trigger on-demand paging by the OS and to prepare the state of the DRAM cache.

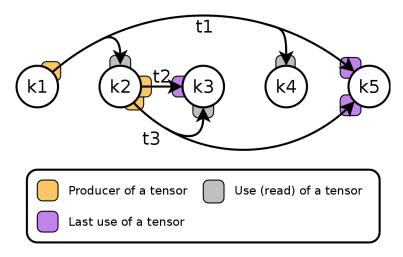

During the execution of these networks, we sampled hardware performance counters for bandwidth and tag statistics. Furthermore, we modified the *ngraph* compiler in two ways. First, we added an option to emit high resolution timestamps when beginning the execution of each compute kernel, allowing us to correlate these events with performance counter data. Second, we exposed information regarding the memory assignment of intermediate tensors. This allows us to examine which regions of memory are being accessed throughout the network execution.

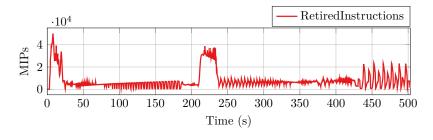

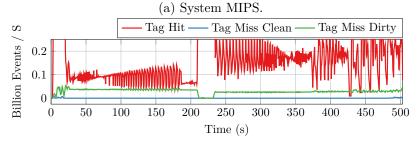

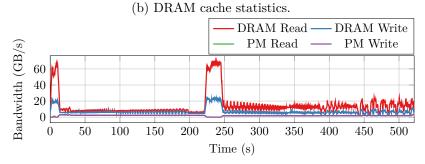

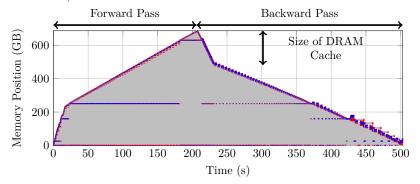

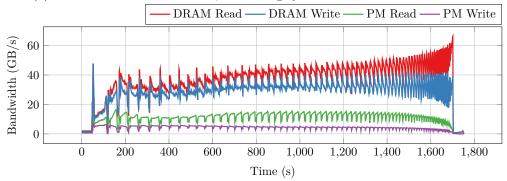

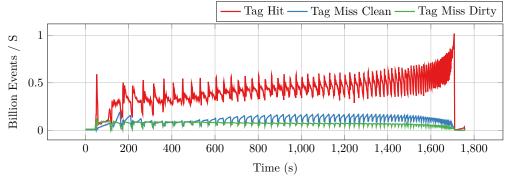

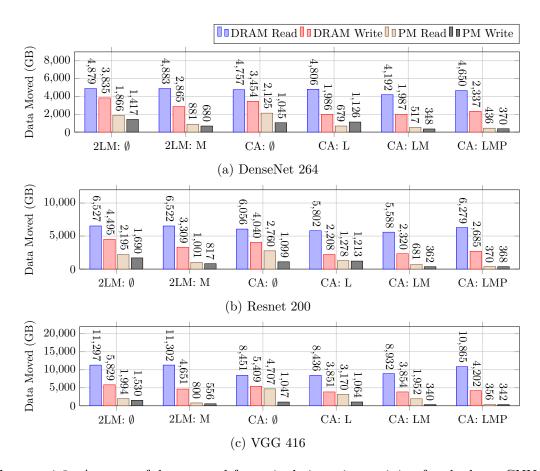

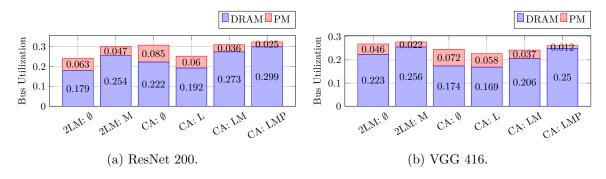

2.5.2. Results. For the deep dive, we present the results for DenseNet [46], a CNN with a complicated dataflow pattern. In Figure 2.5 we break down the bottlenecks of a single iteration of training for DenseNet 264 with batchsize 3072. The baseline memory footprint for this application is around 688 GB. Figure 2.5a demonstrates the system's retired instruction rate through time. Figure 2.5b shows the number of tag hits, dirty tag misses, and clean tag misses throughout the iteration.

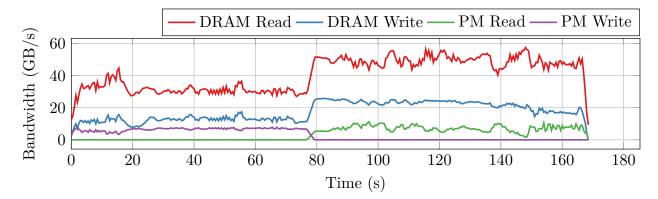

Key observations to make are: (1) there very few clean tag misses, (2) there is a high percentage of dirty tag misses, both in the forward pass and the backward pass, and (3) there noticeable regions of high tag hits at the beginning of the forward and backward passes with a corresponding drop in dirty tag misses. Finally, Figure 2.5c breaks down the read and write bandwidths to DRAM and PM. Regions of high dirty miss rate correspond to low bandwidth and instruction throughput. Reasonable system performance is only achieved when the hit rate is high.

(c) Memory bandwidth through time. PM read and write bandwidths are similar, thus the PM read line is hidden behind the PM write line.

(d) Live memory in the *ngraph* heap. Memory that is highlighted *gray* indicates memory that will be read before written (i.e., live memory). *Blue* indicates a write is happening. *Red* indicates a read is happening. *White* shows memory that will be written before read.

FIGURE 2.5. Memory behavior of a single iteration of training for DenseNet 264 with a batchsize of 3072.

So, a good question at this point is - Why are so many dirty tag misses generated, and why are there regions of high cache hit rate? Two related phenomena can explain this.

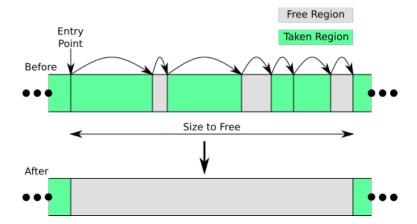

Figure 2.5d shows the memory usage of DenseNet through time for a single iteration of training. Before execution, the *ngraph* compiler allocates a single buffer for the *entire* network. The offset from the base of this buffer is shown on the vertical axis of Figure 2.5d. The change in memory state through time is shown using different colors. The color *white* indicates that the region of memory is **free** (semantically speaking). That is, it will always be written to before it is read by the program. A *blue* highlight indicates that a region of memory is being actively written to, *red* indicates a read, and *gray* indicates that the memory will be read from in the future.

For an iteration of training, first the *forward* pass of the model is computed (up to time around 220, annotated in Figure 2.5d). Throughout the forward pass, some of the generated intermediate tensors must be held in memory to facilitate computation of the backward pass. Thus, the amount of live memory (gray) accumulates through the forward pass. Once a preserved tensor is used on the backward pass, the region in memory where it was stored is free for further use (white). The *ngraph* compiler takes advantage of this newly freed area to allocate intermediate tensors required to compute the backward pass. This is the very subtle streak of blue on the right shoulder of Figure 2.5d.

However, from the perspective of the 2LM cache, the fact that writes are occurring to a region of memory on the backward pass makes memory is dirty with respect to the DRAM cache. Hence, even when this region of memory is semantically free from the program's perspective, the cache must still generate a dirty write back upon eviction. Because the DRAM cache is unaware of the meaningful lifetime of memory, it generates a large amount of unnecessary traffic.

Finally, the regions of high DRAM cache hit rate occur at the beginning of the forward and backward pass because the area of active memory folds back on itself. Recent data is in the cache, so all accesses are cache hits. This continues until the entire cache has been read, at which point further accesses are cache misses.

2.5.3. Problematic Kernels. To wrap up this section, we will explain the relatively high frequency periodic behavior that is noticeable in the Tag Hit line of Figure 2.5b. DenseNet is composed of a linear chain of "dense blocks" where each dense block consists of a sequence of

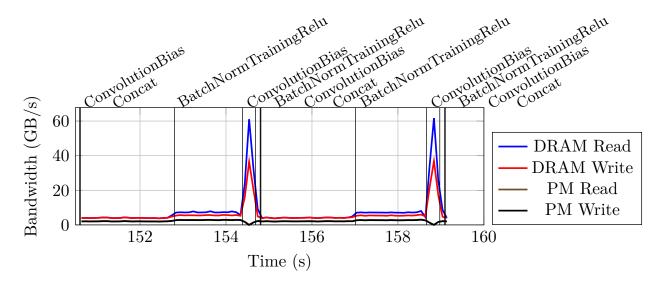

FIGURE 2.6. Snapshot of periodic bandwidth behavior during the forward pass of training DenseNet 264 in 2LM. Vertical bars mark the start of kernel execution. Very short running kernels have been excluded for clarity.

Concat, BatchNorm, Conv, BatchNorm, and Conv operators. Figure 2.6 shows a high resolution snapshot of the bandwidth for two such dense blocks during the forward pass of DenseNet. The point where kernels begin execution is annotated on the graph. The main performance bottlenecks apparent in Figure 2.6 are Concat and BatchNorm. These are both memory-bound kernels with little data reuse and are more affected by the low bandwidth associated with a high dirty tag miss rate. The second BatchNorm within each dense block operates on much smaller intermediate tensors, and is thus less impactful on overall performance. Similar problematic kernels exist on the backwards pass as well, including BatchNormBackprop and the back-propagation kernels for the filter/bias inputs of 3x3 convolutions.

**2.5.4. Discussion.** In summary, the overall performance of CNN training in 2LM mode in PM-based systems is affected by two factors: (1) low effective bandwidth with a high miss rate and (2) a significant amount of unnecessary dirty writebacks. From the microbenchmarks, the first of these is not too surprising. However, the second exposes a performance pathology *not* demonstrated by the microbenchmarks, made worse by the relatively low write bandwidth of PM. Next, we will look at a different class of algorithms that suffer similarly.

#### 2.6. Case Study 2: Graph Processing

In this section, we perform a preliminary study on applications known for having diverse performance characteristics and irregular memory access patterns. To accomplish this, we evaluate a variety of graph processing algorithms on large real world graph inputs using Galois [68], a high performance shared memory graph analytics framework.

2.6.1. Background. Large graph processing has garnered substantial research interest across a variety of use cases, including the identification of social media influencers and decision makers, or finding fraudulent actors within a business network. These real world large systems require frameworks process representative graphs with tens of billions of nodes and trillions of edges, incurring a high memory footprint that is expensive to accommodate in DRAM. Depending on the topology of the input graph and the processing algorithm being used, the memory access pattern can vary wildly. This presents a challenge when optimizing such workloads for systems with limited main memory.

To address this issues, several efforts [26,33] have explored leveraging PM for graph analytics on a single machine. However, such works focused on performing an analysis and comparison of different graph processing frameworks and system settings to optimize the use of Optane for graph workloads. Here, we evaluate the bandwidth characteristics of such irregular workloads in 2LM.

**2.6.2. Methodology.** Graph kernel experiments were run on the shared memory graph analytics framework Galois. Specifically, our evaluations consisted of 4 benchmarks from the lonestar suite: breadth-first search (bfs) [20], connected components (cc) [93, 96], k-core decomposition (kcore) [25], and pagerank-push (pr) [73]. These kernels were chosen based on their diverse execution characteristics [6]. Our workloads were run with the settings by Gill et al. [33]. For bfs, the source node was the maximum out-degree node. The tolerance of pr was set to  $10^{-6}$  and we used the k = 100 for kcore. Each kernel ran until convergence, except for pr which ran for 100 rounds.

We used two realistic unweighted massive input graphs: wdc12 [72], the largest publicly available graph, and kron30 [60], a randomized scale free graph generated using a graph500 based kronecker generator [34]. Each were chosen to highlight the differences between when a graph fit and did not fit in the DRAM cache. While these graphs have different structures, we can still draw

conclusions from kernels' relative performance on these graphs. Both were processed using the provided graph-converter in Galois and resulted in binaries of size 507 GB and 73 GB respectively.

In 2LM, all benchmarks were run on two NUMA nodes and assigned all 96 threads. Since two sockets are used, the size of the DRAM cache is effectively doubled to 384 GB with 6 TB of PM. The total NUMA interleaving and 2 MiB hugepages were used with no page migration to maximize performance [33].

To find the baseline data movement required by the algorithms, we configured the PM regions on each socket as extra NUMA nodes. This is facilitated through the daxctl<sup>3</sup> tool with the machine in 1LM. Since Galois uses a NUMA preferred policy, the threads on each socket will initially allocate memory on that socket's DRAM. When DRAM is exhausted, further allocations are serviced by PM. By summing the traffic to DRAM and PM, we can establish the baseline memory traffic required by each application.

As with our previous experiments, measurements on bandwidth and tag statistics were gathered using hardware performance counters.

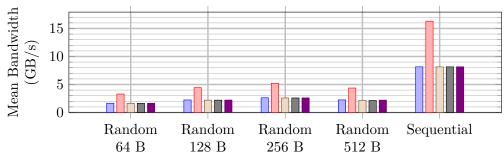

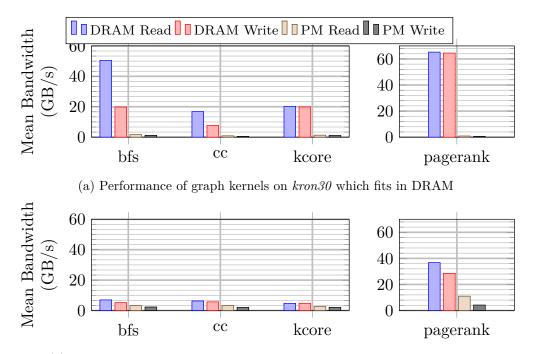

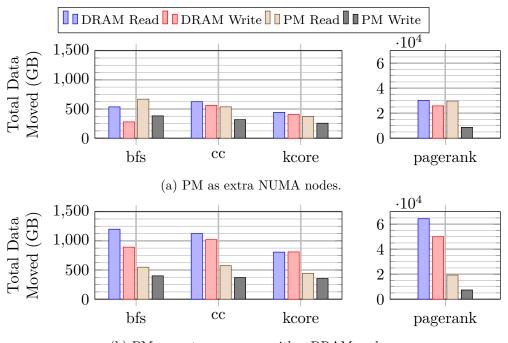

**2.6.3.** Results. Figure 2.7 compares the observed bandwidth when running the graph kernels on *kron30* and *wdc12*. When processing *kron30*, the kernels have a working set that largely fits within the DRAM cache while the working set when processing *wdc12* greatly exceeds the DRAM cache. When the working set does not fit in the DRAM cache, there is a significant decrease in DRAM bandwidth during an algorithm's execution.

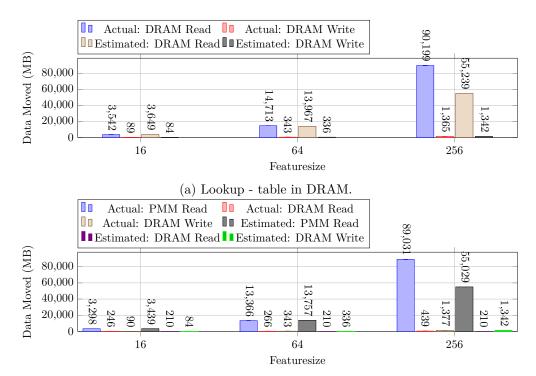

Figure 2.8 shows the total amount of data moved in the NUMA and 2LM configurations for PM. Since page migration was disabled, Figure 2.8a shows the true demand accesses of the workload. Comparing this with Figure 2.8b we see significant access amplification.

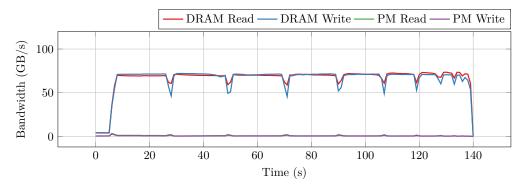

Figure 2.9 shows the workload characteristics of the pagerank-push algorithm for both kron30 and wdc12. Figure 2.9a shows the algorithm's bandwidth when its working set largely fits in the cache. Bandwidth is stable at 70 GB/s with roughly equal DRAM reads and writes.

On the other hand, Figure 2.9b demonstrates the bandwidth of pagerank-push when its working set *does not* fit in the DRAM cache. Not only is the average bandwidth significantly lower, but there is also an excess of DRAM reads coupled with heavy PM traffic. The tag metrics shown in

<sup>3</sup>https://docs.pmem.io/ndctl-user-guide/daxctl-man-pages

(b) Performance of graph kernels on wdc12 which exceeds DRAM capacity

FIGURE 2.7. Graph kernel performance in 2LM run on 96 threads. When the input graph does not fit in the DRAM cache, bandwidth significantly drops.

(b) PM as system memory with a DRAM cache.

FIGURE 2.8. Total amount of data moved during the execution of a graph kernel when the input graph does not fit in the DRAM cache.

(a) Bandwidth trace for kron30, which largely fits within the DRAM cache.

(b) Bandwidth trace for wdc12, which greatly exceeds the capcity of the the DRAM cache.

(c) Tag trace for wdc12.

FIGURE 2.9. Traces for the *pagerank-push* algorithm. Figure 2.9a demonstrates behavior when the graph largely fits within the DRAM cache. Conversely, Figures 2.9b and 2.9c shows behavior when the working set greatly exceeds the DRAM cache.

Figure 2.9c show the presence of both clean and dirty tag misses as well as the correlation between hit rate and DRAM bandwidth.

**2.6.4. Discussion.** As with CNN training, large scale graph processing is a workload with a high DRAM cache miss rate. This is made worse since traditional graph algorithm implementations involve mutating the in-memory representation of the graph [33]. In 2LM, this mutation will mark the corresponding memory as dirty. Thus, not only is the miss rate high, but many of these misses require PM write backs, which we have demonstrated to be inefficient. As a result, it is not surprising that 2LM behaves poorly for these particular implementations.

# 2.7. Discussion and Mitigation Strategies

In this chapter, we demonstrated that the DRAM cache as currently implemented in Intel's Cascade Lake systems performs poorly for applications with a high miss rate. We showed that a DRAM cache miss can cause 3–5× more memory accesses than the original demand requests. Further, we showed that this causes performance degradation in two bandwidth-limited workloads: CNN training and graph analytics which are important use cases for PM since they have extremely large memory footprints. Furthermore, we show that certain data reuse semantics at the program level can cause severe degradation.

For instance, in the deep neural network training workload, a significant amount of the data movement from the DRAM cache to PM is useless as this data was only meant to be used temporarily by the program and will be overwritten before it is read again. This dirty temporary data dominates the DRAM cache leading to more misses than necessary and limiting performance to the smaller PM write bandwidth.

2.7.1. Software-managed multi-level memory. So what can be done about this? In this section, we look briefly at an example of software-managed memory for graph analytics. We propose that through software-managed memory, better performance can be obtained than using the hardware-managed cache in 2LM mode for these miss heavy bandwidth-bound workloads. In the next chapter, we will look at software management techniques for tackling memory management for CNN training.

Software management relies on decoupling the DRAM and PM memory pools. So far, this chapter focused on the 2LM (or "memory mode") of the PM systems, these systems can also be

configured in "app-direct mode" or 1LM where the programmer has full control over the data location and movement. PM is simply mapped into a program's address space.

2.7.1.1. Graph Analytics. As pointed out in Section 2.6, graph algorithm implementations in Galois and other graph frameworks often mutate graph data structure. With PM, this is an issue due its low write bandwidth (which is further exacerbated by 2LM's write amplification). To tackle this issue, the authors of Sage [33] designed that software specifically with PM in mind. Their key approach is to (as much as possible) use PM for read only data.

When running algorithms that require tracking state (such a nodes visited for bfs), an auxiliary DRAM-based data structure is used. This data structure is greatly compressed and supplements the read-only PM-based adjacency list. Mutation is only performed on the auxiliary data structure, and hence write traffic is only generated to DRAM. To optimize for multiple sockets, Sage takes advantage of PM's capacity to keep a full copy of the graph on both CPU sockets. With these techniques, they were able to design algorithms 1.87× faster on average than GBBS and 1.94× faster on average than Galois in 2LM [33].

This is an example demonstrating that clever software management can over come the bandwidth limitations of PM. Conversely, these same limitations are exacerbated by access amplification caused by the DRAM cache.

2.7.1.2. Techniques for CNNs. In the next chapter, we will present AutoTM, a heterogeneous memory management technique for CNNs. Unlike Sage's approach to graph analytics, CNN's cannot use PM as just read-only memory. Thus, AutoTM uses mathematical optimization to determine where to place intermediate data and when to move this data between memory pools.

#### CHAPTER 3

# Compiler-Based Heterogeneous Memory Management for Statically Analyzable Workloads

#### 3.1. Introduction

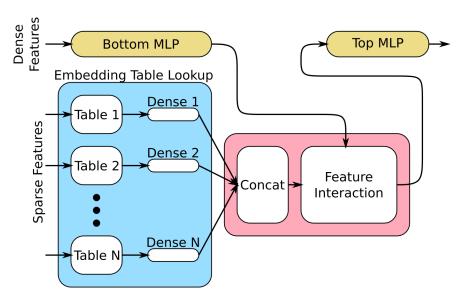

Deep Neural Networks (DNNs) have been dramatically successful over the past decade across many domains including computer vision [57], machine translation and language modeling [99], recommendation systems [67], speech [110] and image synthesis [111], and real-time strategy game control [105]. This success has in turn led practitioners to pursue larger, more expressive models. Today, state of the art models in language modeling and translation have 100s of billions of parameters [94] which requires 100s of GB of active working memory for training. For instance, large models such as BigGAN [9] found significant benefits from increasing both model size and training batch size, and Facebook's recent DLRM recommendation system [67] contains orders of magnitude more parameters than conventional networks. Additionally, to reach beyond human-level accuracy these models are expected to grow even larger with possibly  $100 \times$  more parameters [42]. The large memory footprints of these models limits training to systems with large amounts of DRAM which incur high costs.

As the memory capacity demands of DNN training are growing, new high density memory devices are finally being produced. Specifically, Intel® Optane<sup>TM</sup> DC Persistent Memory Modules (PM) [33, 48] can now be purchased and are up to  $2.1 \times$  lower price per capacity than DRAM. These devices are on the main memory bus, allowing applications direct access via load and store instructions and can be used as working memory. Thus, in this chapter we ask the question "what are the design tradeoffs of using PM in training large DNN models, and more specifically, can PM be used as a DRAM replacement when training for large DNN models?"

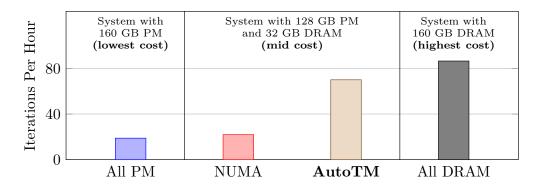

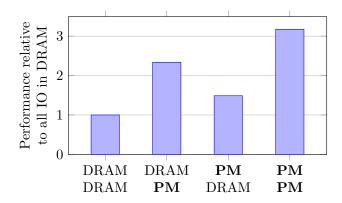

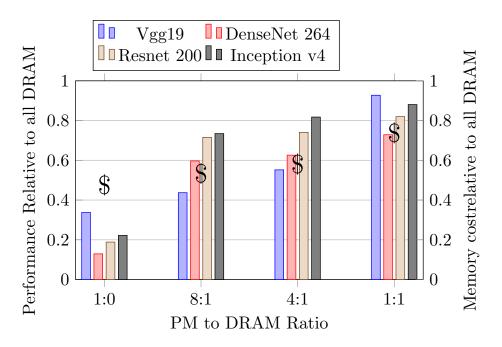

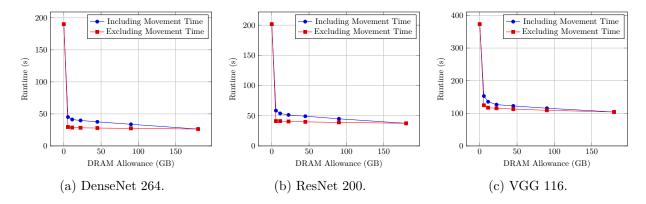

Figure 3.1 shows the training performance for three different memory systems: an all PM system (lowest cost), an all DRAM system (highest cost), and a heterogeneous system (moderate

FIGURE 3.1. Performance of Inception v4. Batch size of 1472.

cost). The all PM bar shows that naively replacing DRAM with PM results in poor performance (about  $5 \times$  slowdown) for training large DNN models. The first-touch NUMA [56] bar shows that current system support for heterogeneous memory is lacking, providing only a small benefit over the all PM case. However, AutoTM provides  $3.7 \times$  speedup over the PM case and is within 20% of the all DRAM system. Thus, we find that a small fraction of DRAM reduces the performance gap between PM and DRAM, but only if we use *smart data movement*.

Use of heterogeneous memory to reduce DRAM has been studied in the past. Facebook has used SSDs to reduce the DRAM footprint of databases [30]. Bandana [31] uses SSD based persistent memory to store deep learning embedding tables [19] with DRAM as a small software cache. In the context of machine learning, vDNN [89], moDNN [15], and SuperNeurons [106] develope system-specific heuristics to tackle heterogeneous memory management between the GPU and CPU to overcome the low memory capacity of GPUs. Furthermore, future HPC systems will be increasingly heterogeneous with DRAM, PM, and HBM [82], so we need a solution that is general and automatic.

In this chapter we introduce AutoTM—a framework to automatically move DNN training data (tensors) between heterogeneous memory devices. AutoTM enables training models with 100s of billions of parameters and/or with large batch sizes efficiently on a single machine. We exploit the static nature of DNN training computation graphs to develop an Integer Linear Programming (ILP) [91] formulation which takes a profile driven approach to automatically optimize the location and movement of intermediate tensors between DRAM and PM given a DRAM capacity constraint.

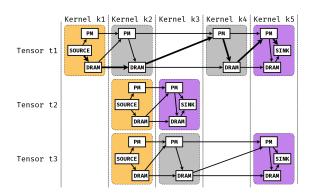

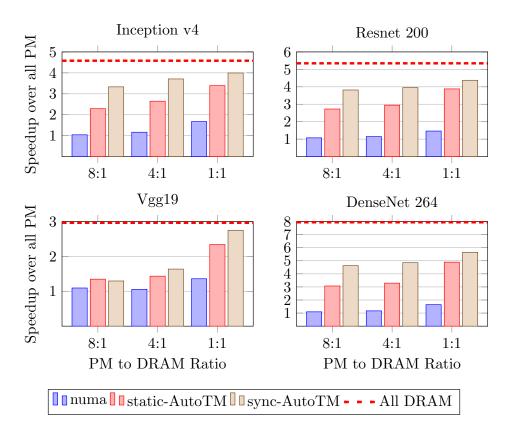

We evaluate the effectiveness of AutoTM on a real system with Optane PM by implementing our approach in the nGraph compiler [24]. Our experiments show that naive use of PM is not effective, but intelligent use of PM and DRAM is required. Furthermore, using initial public pricing information, we evaluate the cost-performance benefits DRAM-PM based systems. We show that ratios of 8:1 or 4:1 of PM to DRAM can be more cost effective than only DRAM or only PM.

We also compare our approach to the existing hardware DRAM cache implemented in current Intel platforms [48] and find AutoTM offers up to 2× performance improvement over hardware-managed caching.

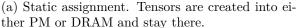

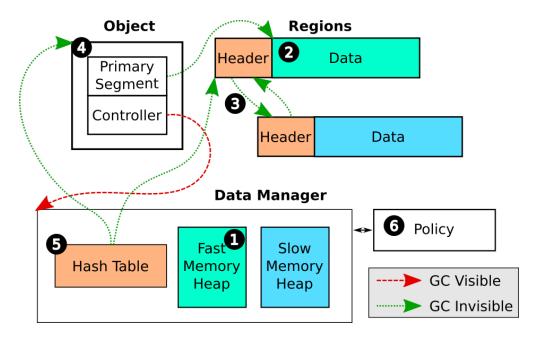

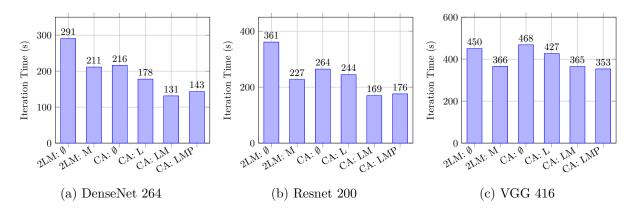

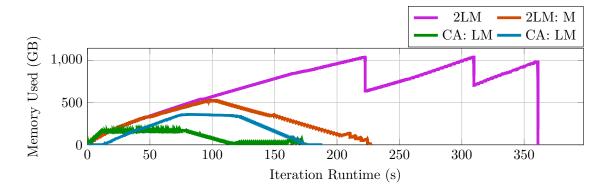

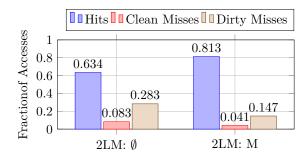

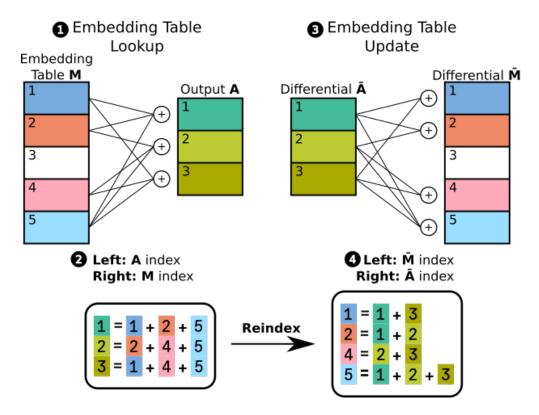

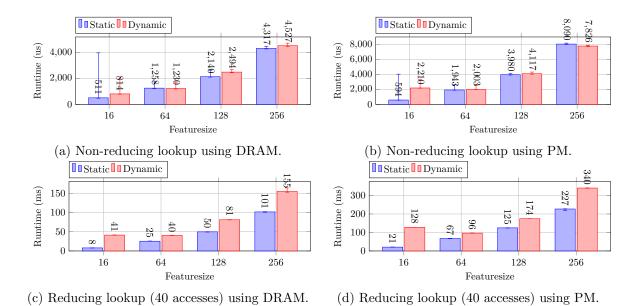

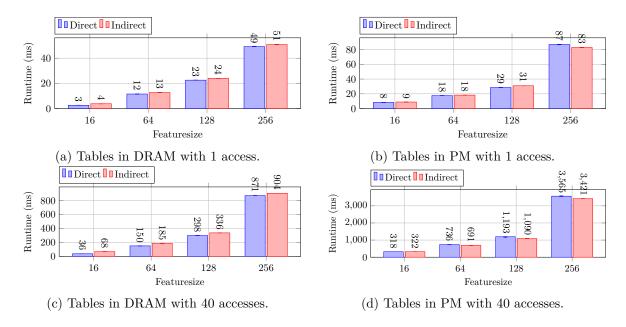

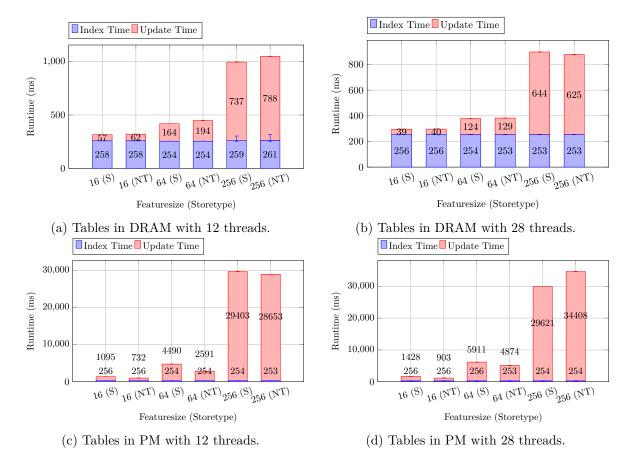

Finally, we demonstrate that AutoTM can be further generalized beyond PM-DRAM heterogeneity by applying AutoTM to CPU-GPU systems. The approach taken by AutoTM uses minimal problem specific heuristics and is thus a general approach toward memory management for many different heterogeneous systems.