## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Switched Capacitor DC-DC Converter: Superior where the Buck Converter has Dominated

#### **Permalink**

https://escholarship.org/uc/item/7f06p9g0

#### **Author**

Ng, Vincent Wai-Shan

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

#### Switched Capacitor DC-DC Converter: Superior where the Buck Converter has Dominated

By

Vincent Wai-Shan Ng

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Seth Sanders, Chair Professor Elad Alon Professor Roberto Horowitz

Fall 2011

#### **Abstract**

Switched Capacitor DC-DC Converter: Superior where the Buck Converter has Dominated

By

Vincent Wai-Shan Ng

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Seth R. Sanders, Chair

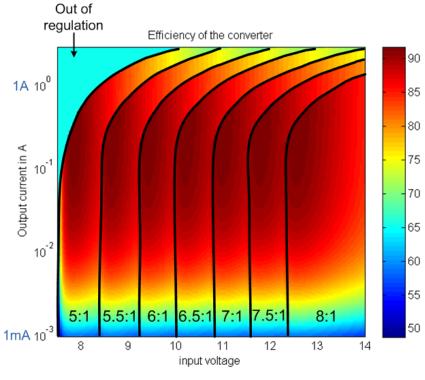

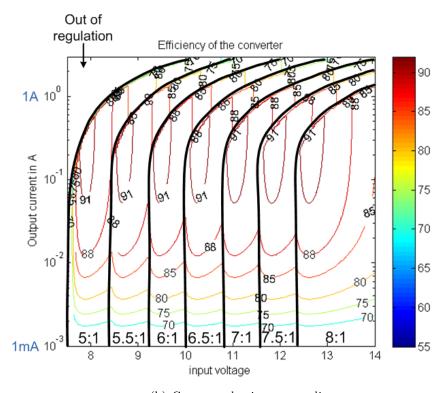

The traditional inductor-based buck converter has been the default design for switched-mode voltage regulators for decades. Switched capacitor (SC) dc-dc converters, on the other hand, have traditionally been used in low power (<10mW) and low conversion ratio (<4:1) applications where neither regulation nor efficiency is critical. This work encompasses the complete successful design, fabrication, and test of a CMOS based switched capacitor dc-dc converter, addressing the ubiquitous 12 V to 1.5 V board-mounted point-of-load application, which the buck converter has dominated. In particular, the circuit developed in this work attains higher efficiency (92% peak, and >80% over a load range of 5 mA to 1 A) than surveyed competitive buck converters, while requiring less board area and less costly passive components. The topology and controller enable a wide input range of 7.5 V to 13.5 V. Controls based on feedback and feedforward provide tight regulation under worst case line and load step conditions. This work shows that the SC converter can outperform the buck converter, and thus the scope of SC converter application can and should be expanded.

CONTENTS

## Contents

| 0 | Exe            | ecutive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1 | Intr           | coduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8  |

|   | 1.1            | The model used for SC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

|   |                | 1.1.1 SSL model of SC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 |

|   | 1.2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|   | 1.3            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

|   |                | O II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 2 | $\mathbf{Arc}$ | hitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

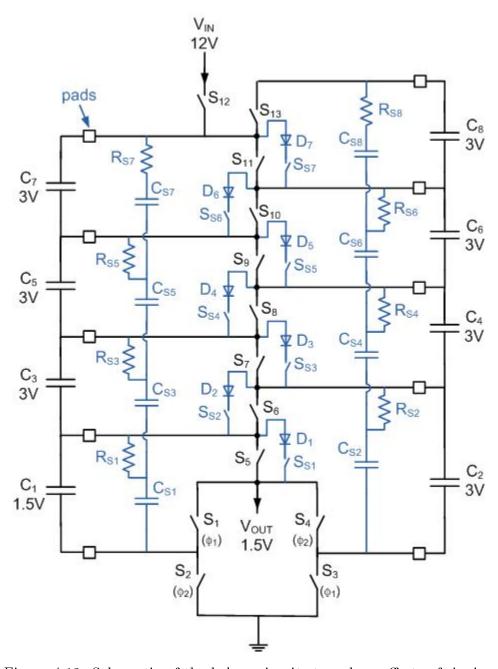

|   | 2.1            | Topology choice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

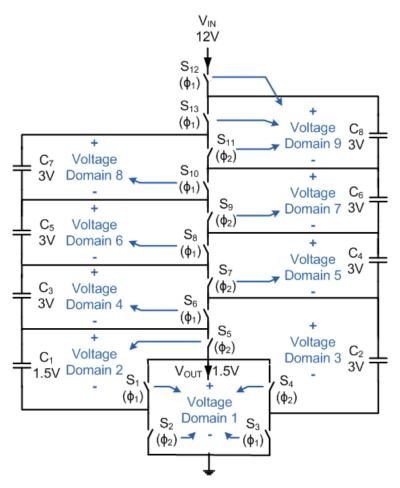

|   | 2.2            | Multiple voltage domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 |

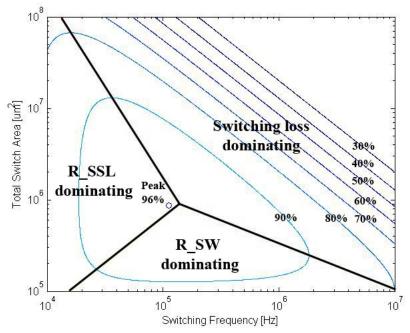

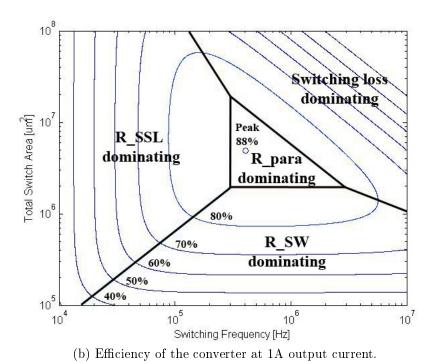

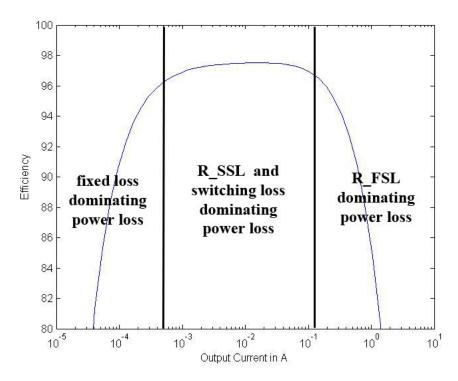

|   | 2.3            | Device sizing and optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23 |

|   |                | 2.3.1 Capacitor Sizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

|   |                | 2.3.2 Switch sizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

|   |                | 2.3.3 Overall optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

|   | 2.4            | Multi-conversion-ratio design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

|   | 2.5            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

|   |                | 2.5.1 Shutdown protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

|   |                | 2.5.2 Startup scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

|   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3 | $\mathbf{Reg}$ | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

|   | 3.1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

|   |                | 0 552                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

|   |                | 0 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35 |

|   |                | 3.1.3 Control through conversion ratio, $n 	cdots 	cdots $ | 35 |

|   |                | 3.1.4 Hybrid control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

|   | 3.2            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

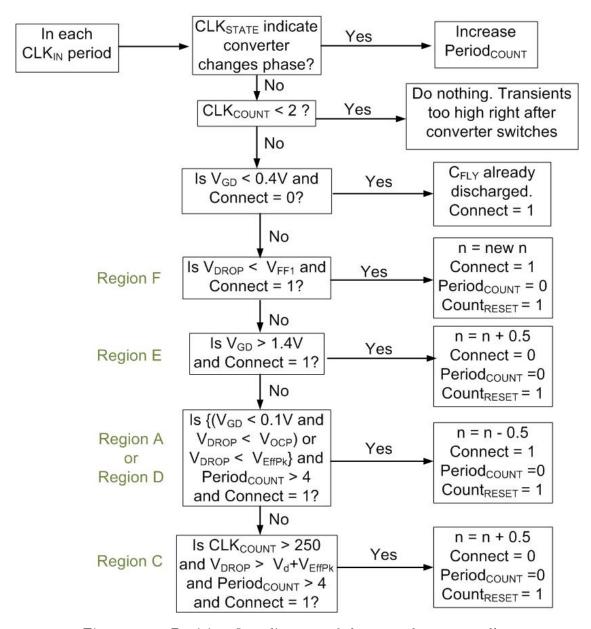

|   |                | 3.2.1 Conversion ratio selection algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37 |

*CONTENTS* ii

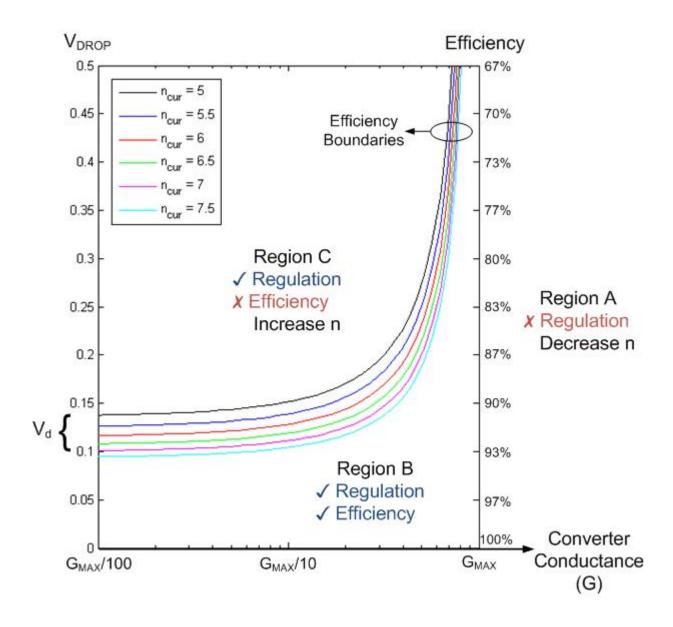

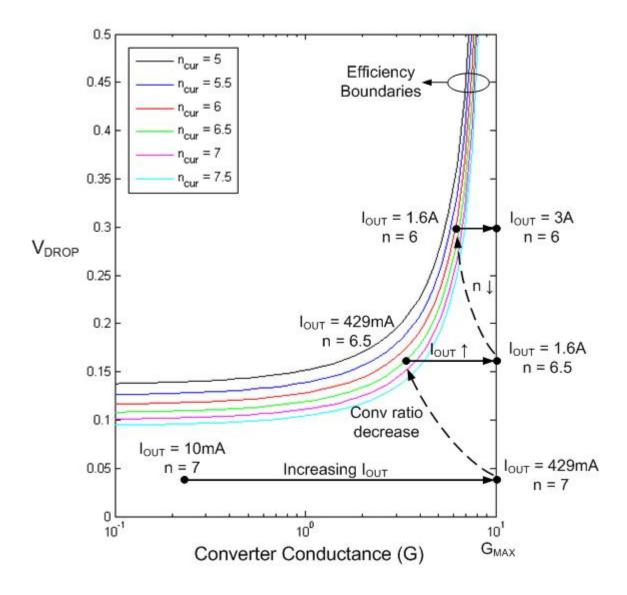

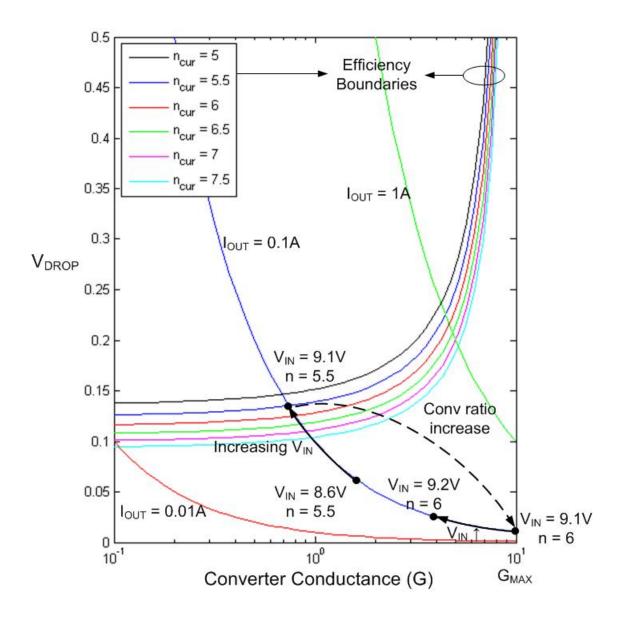

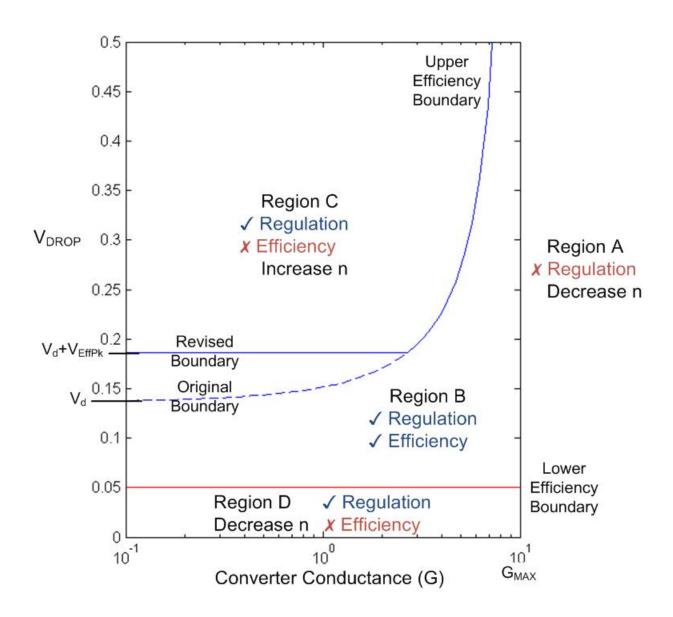

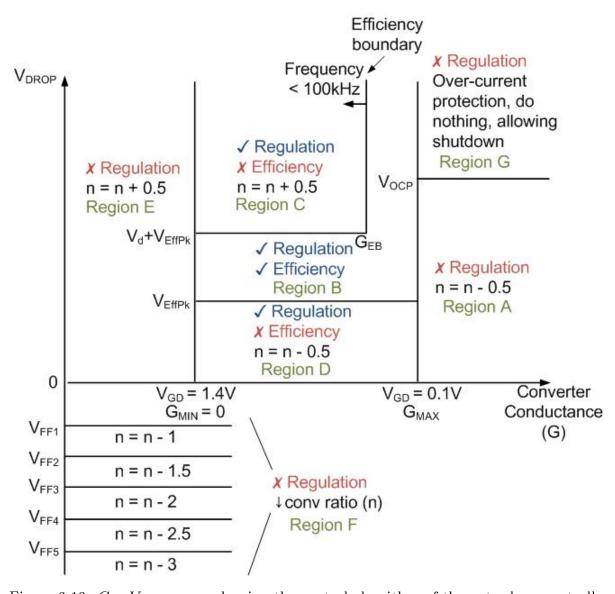

|   |      | 3.2.2       | Control through $G - V_{DROP}$ state space                                               | 40  |

|---|------|-------------|------------------------------------------------------------------------------------------|-----|

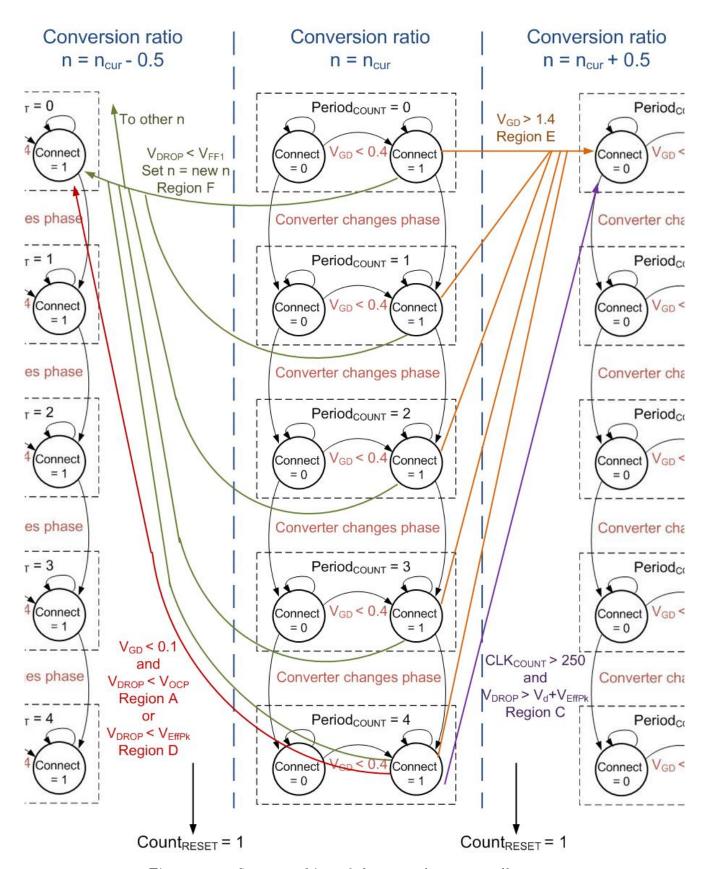

|   |      | 3.2.3       | Refined analysis of the outer loop algorithm                                             | 40  |

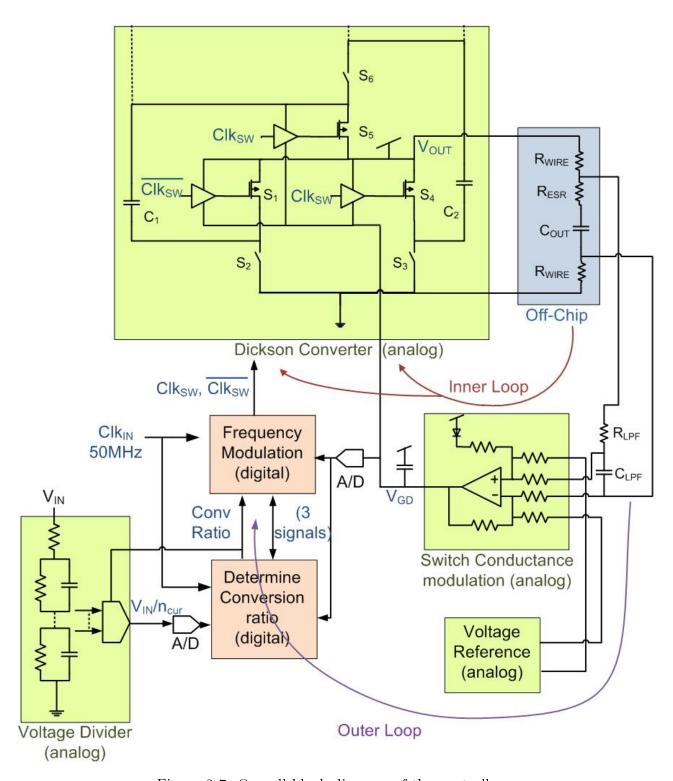

|   | 3.3  | Contro      | oller implementation                                                                     | 45  |

|   |      | 3.3.1       | Inner loop dynamics design                                                               | 47  |

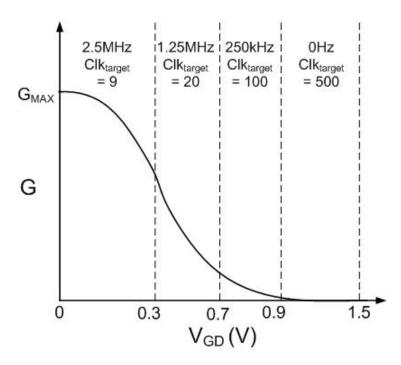

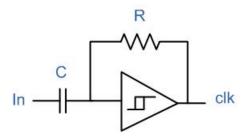

|   |      | 3.3.2       | Inner loop frequency controller                                                          | 49  |

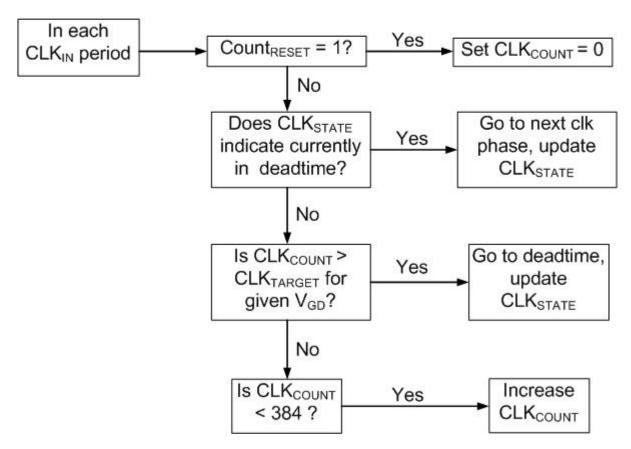

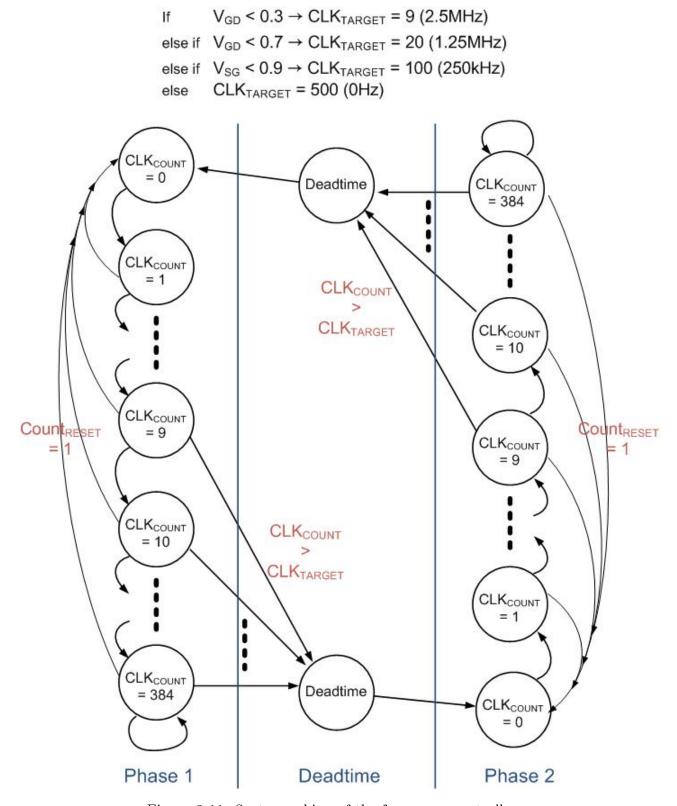

|   |      | 3.3.3       | Outer loop controller algorithm                                                          | 53  |

|   |      | 3.3.4       | Outer loop controller state machine                                                      | 54  |

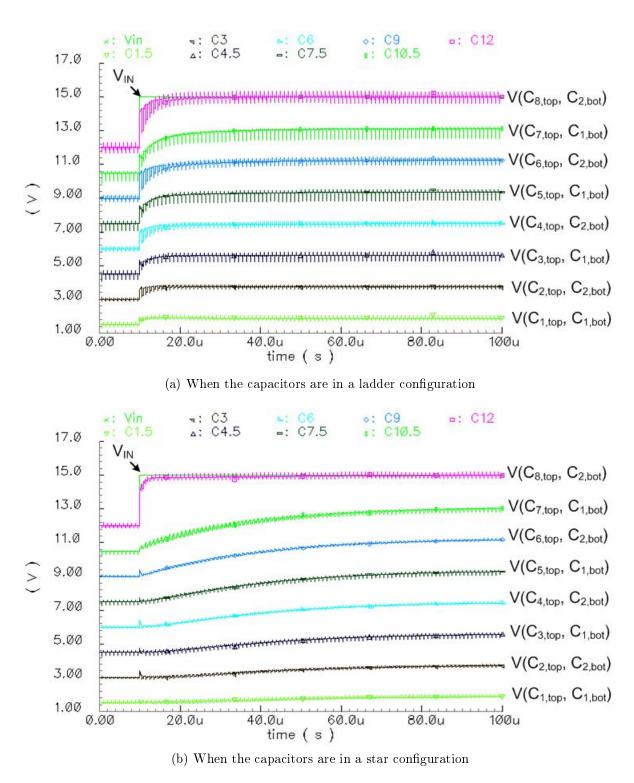

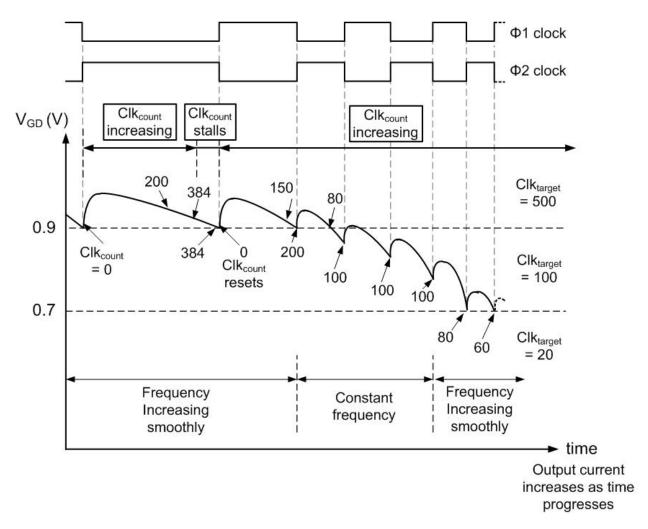

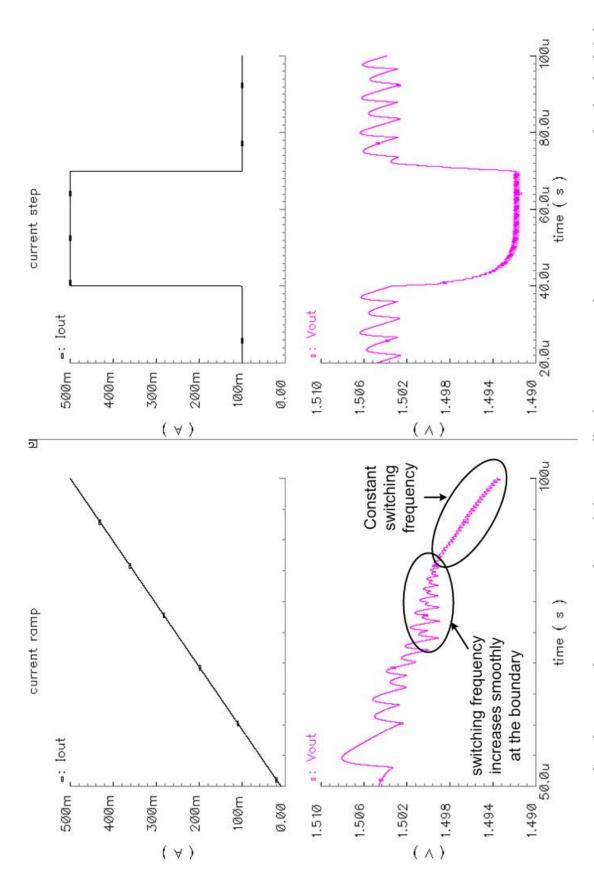

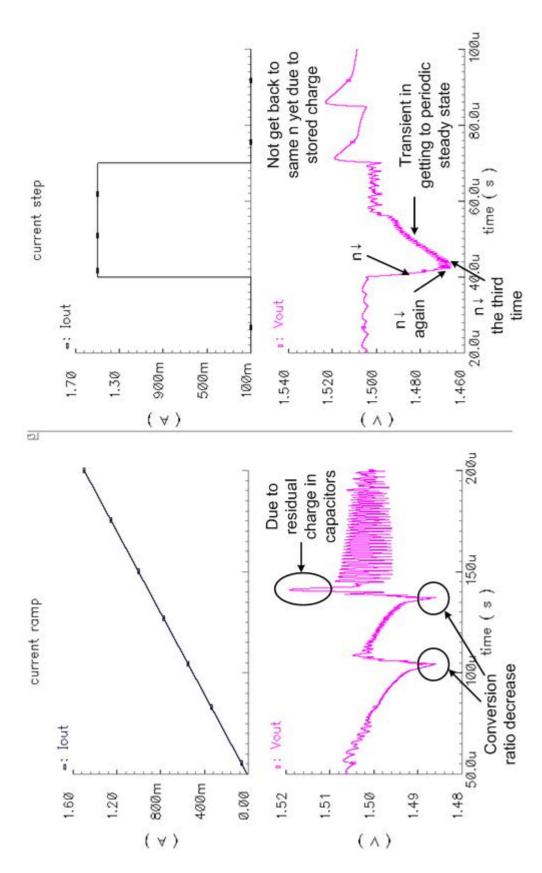

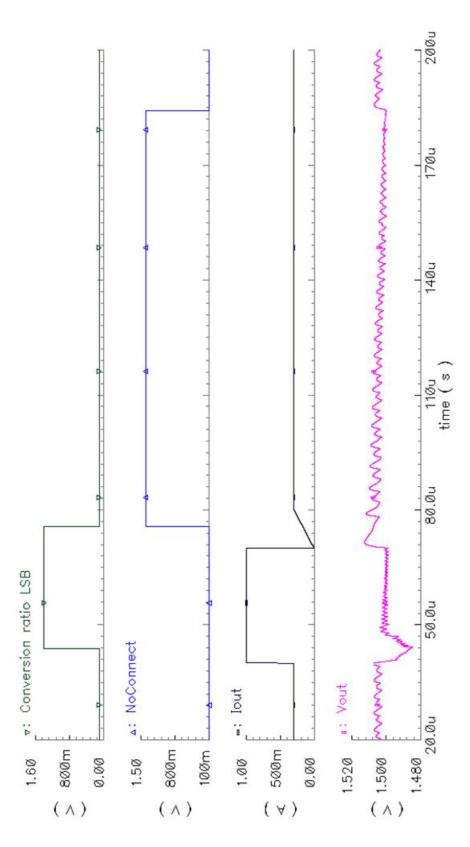

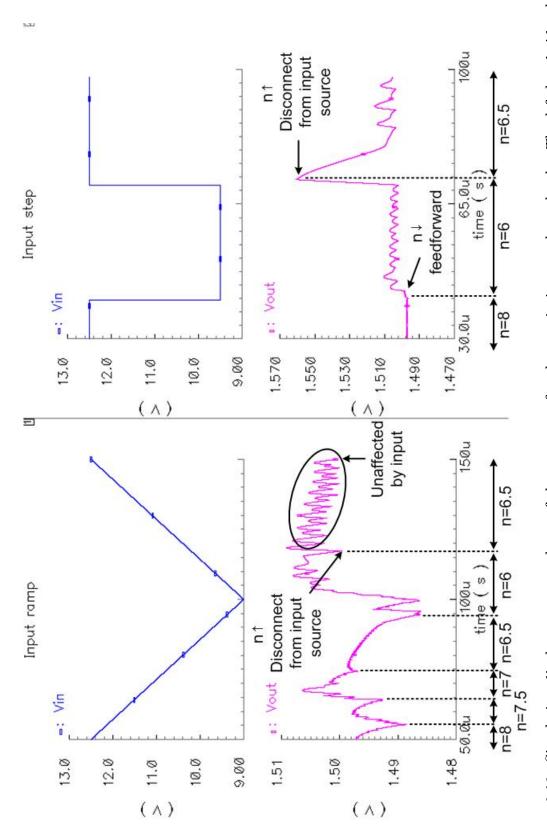

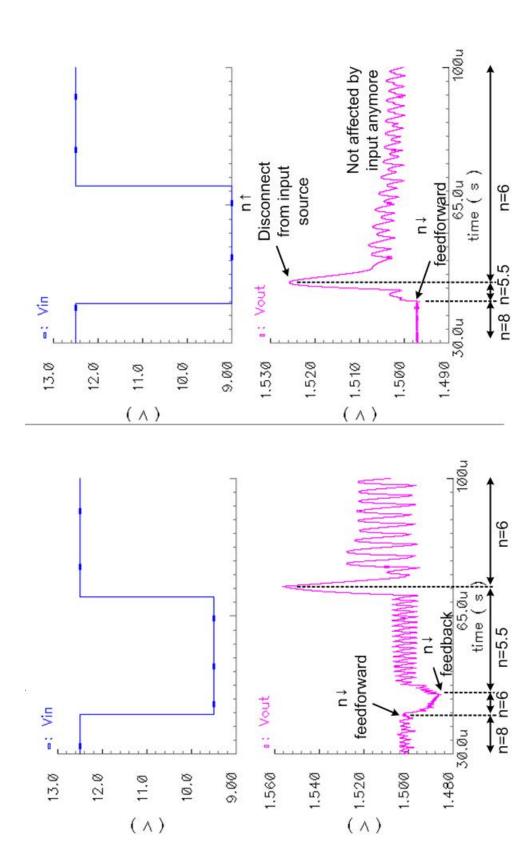

|   |      | 3.3.5       | Controller simulation results                                                            | 59  |

|   |      | 3.3.6       | Startup controller                                                                       | 65  |

| 4 | Circ | ${ m uits}$ |                                                                                          | 68  |

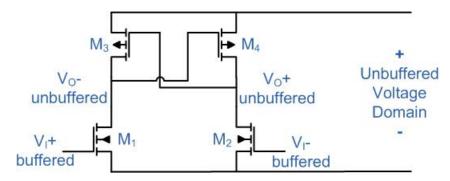

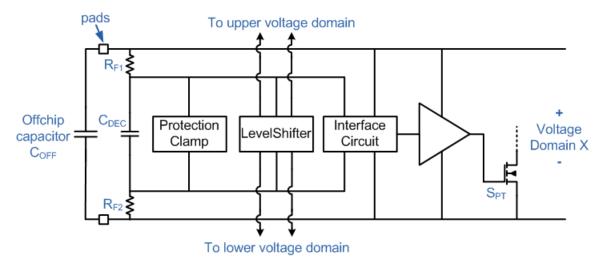

|   | 4.1  | Levelsh     | hifters                                                                                  | 68  |

|   | 4.2  | Shutdo      | own protection clamps                                                                    | 70  |

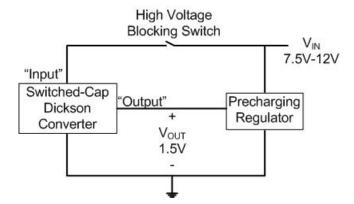

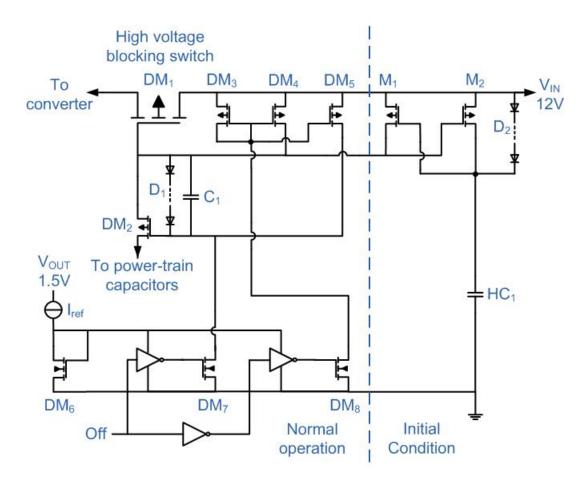

|   | 4.3  | Startuj     | p helper circuits                                                                        | 71  |

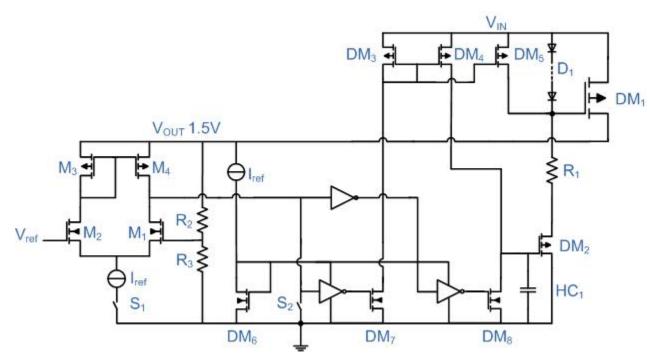

|   | 4.4  |             | voltage blocking switch                                                                  | 73  |

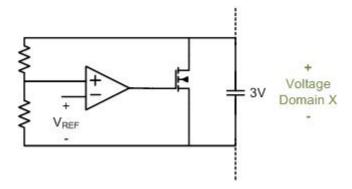

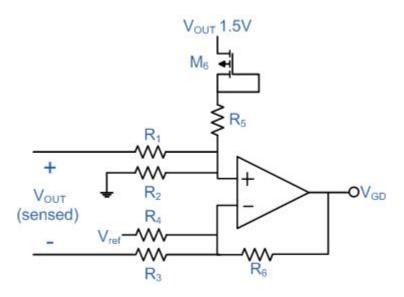

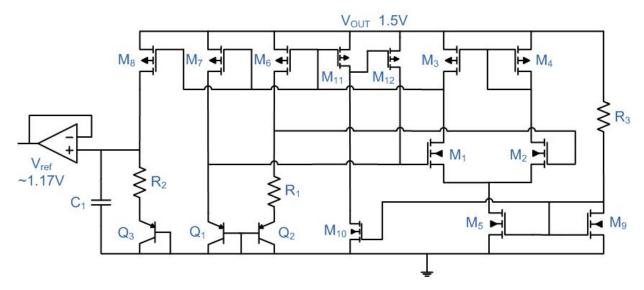

|   | 4.5  |             | arging regulator                                                                         | 74  |

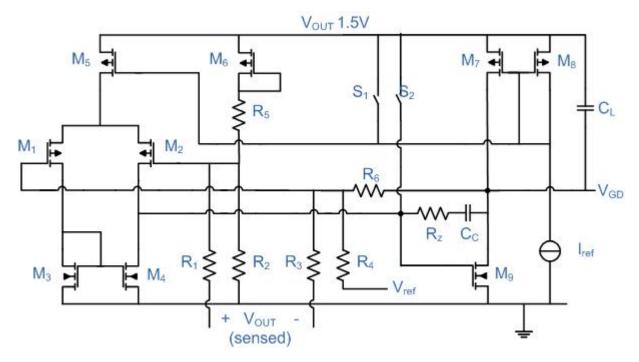

|   | 4.6  | Error a     | amplifier                                                                                | 77  |

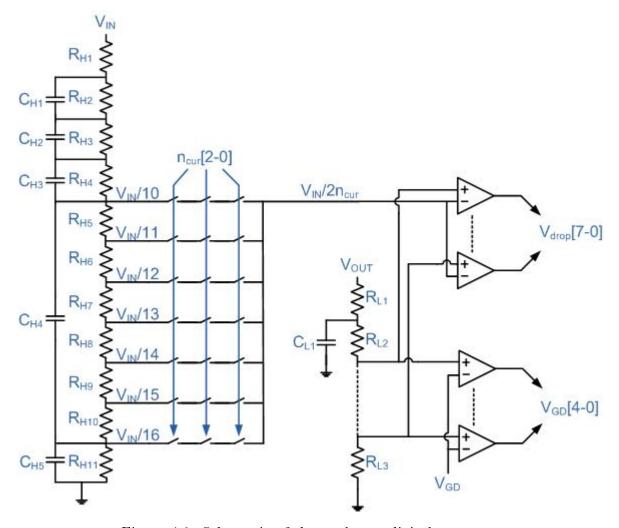

|   | 4.7  |             | g to Digital Converter                                                                   | 78  |

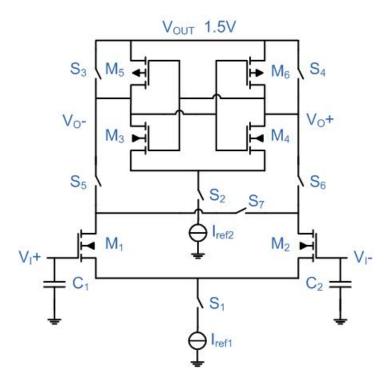

|   | 4.8  |             | arators                                                                                  | 79  |

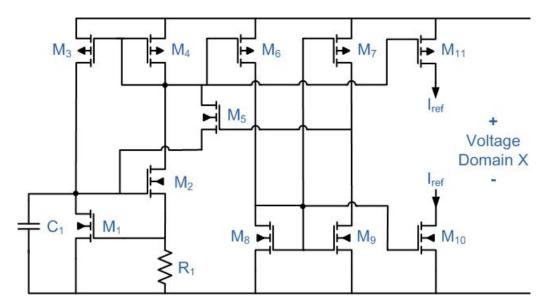

|   | 4.9  | Curren      | nt reference                                                                             | 81  |

|   | 4.10 | Voltage     | e reference                                                                              | 81  |

|   | 4.11 | Ringin      | g protection scheme                                                                      | 82  |

|   | 4.12 | Non ov      | verlapping clock generator                                                               | 85  |

|   | 4.13 | Digital     | l circuits                                                                               | 86  |

| 5 | Exp  | erimen      | ntal Results                                                                             | 87  |

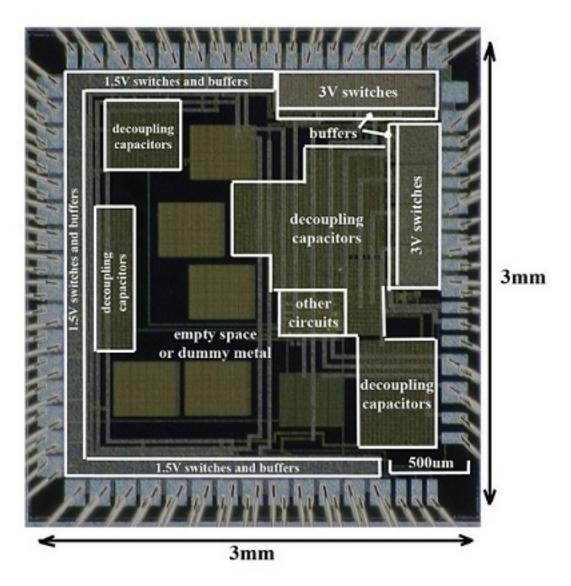

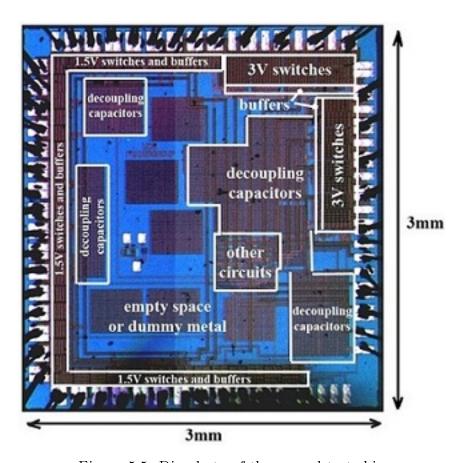

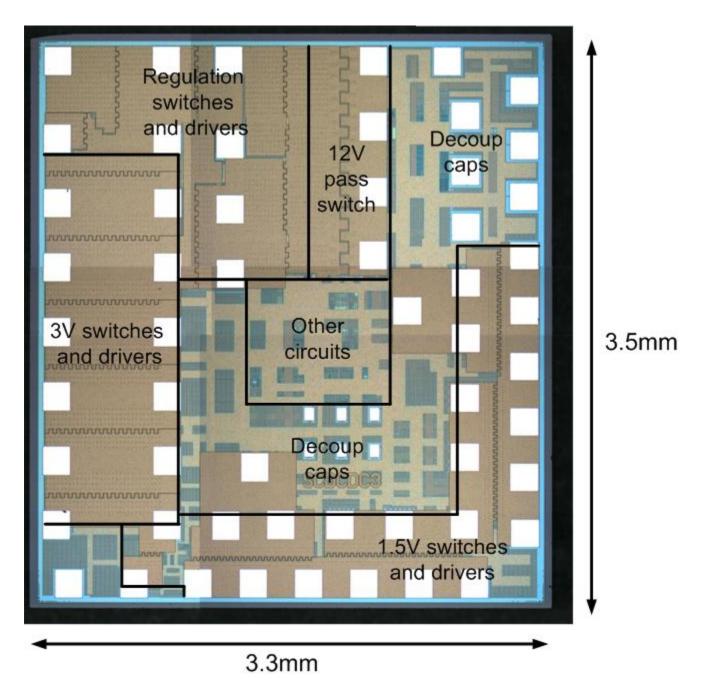

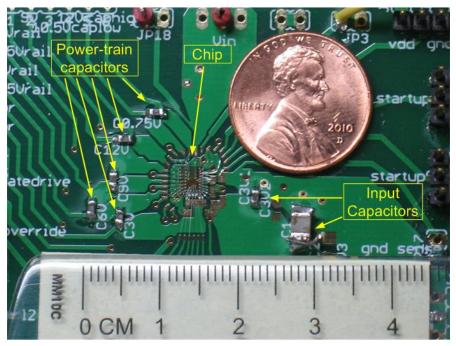

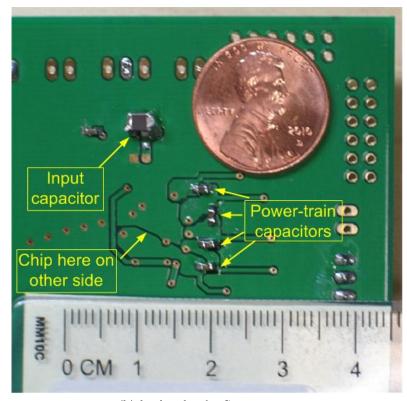

|   | 5.1  |             | est chip                                                                                 | 87  |

|   | 5.2  | Second      | l test chip                                                                              | 92  |

|   | 5.3  |             | test chip                                                                                | 96  |

|   | 5.4  |             | $\mathbf{n}$ and final test chip $\dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 102 |

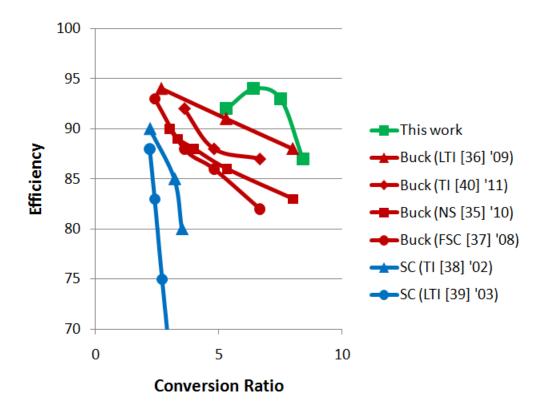

|   | 5.5  |             | arison with other works                                                                  | 115 |

| 6 | Con  | clusion     | n                                                                                        | 117 |

LIST OF FIGURES

# List of Figures

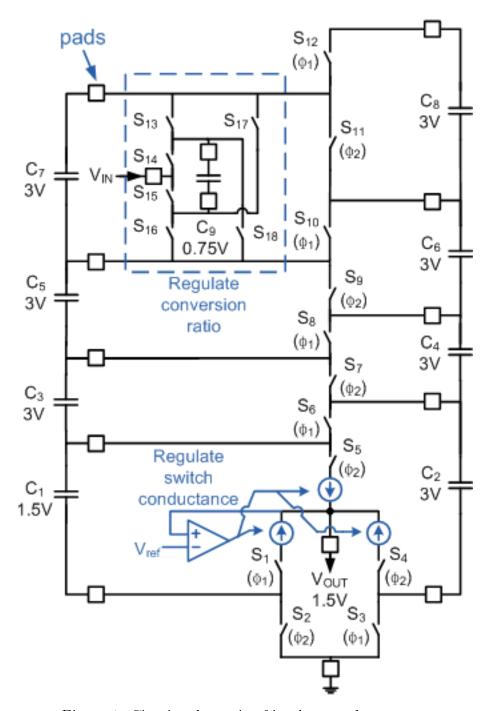

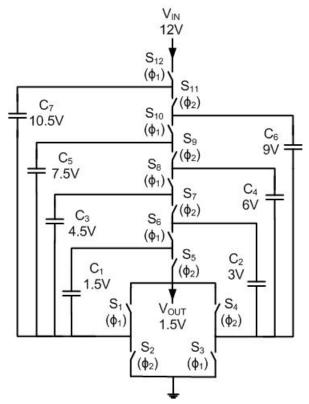

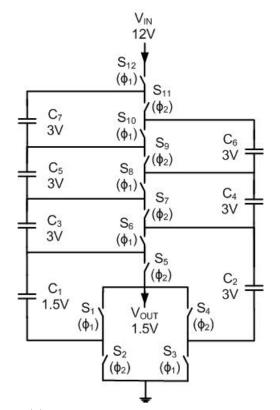

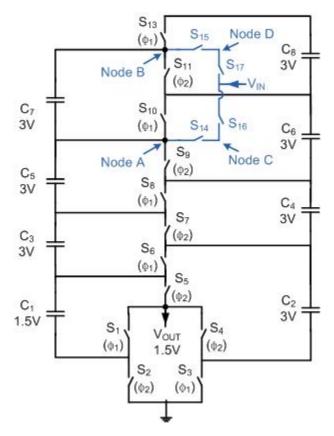

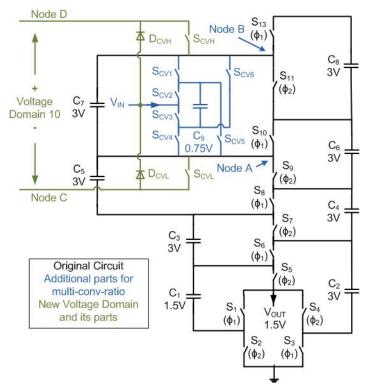

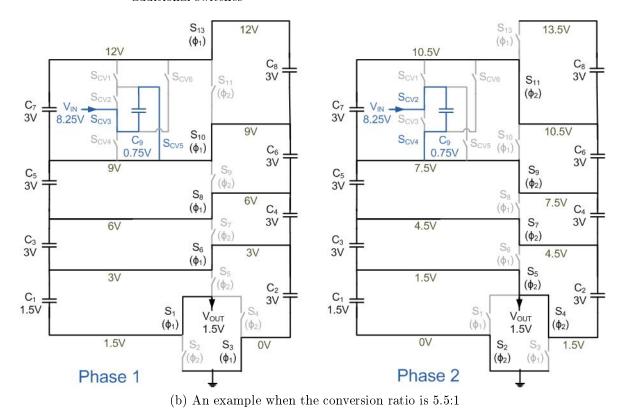

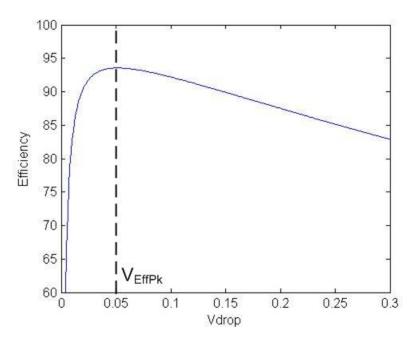

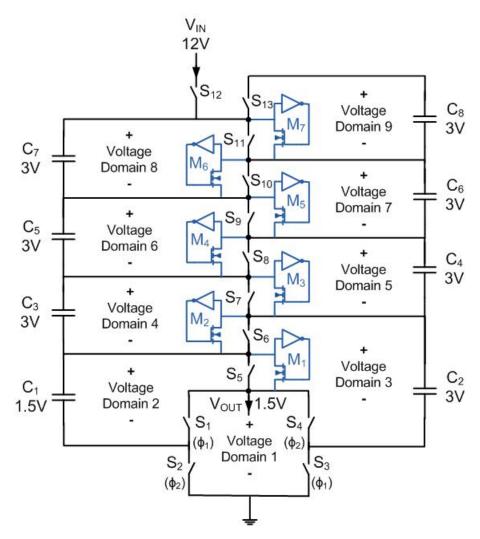

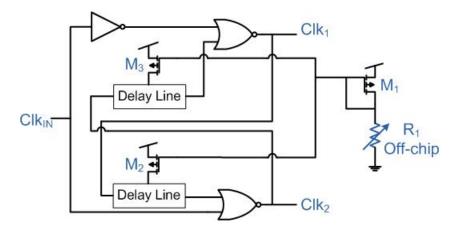

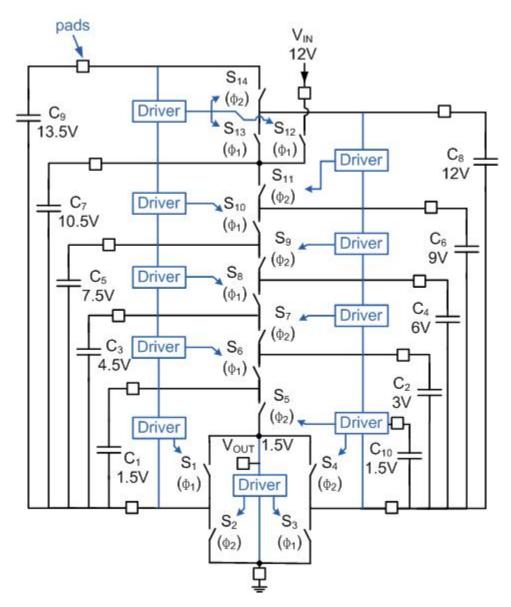

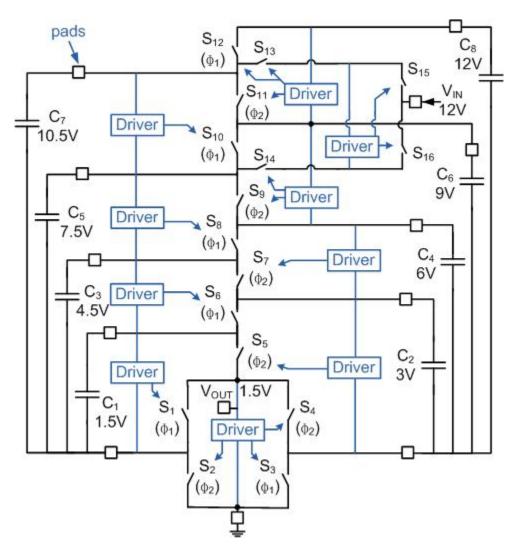

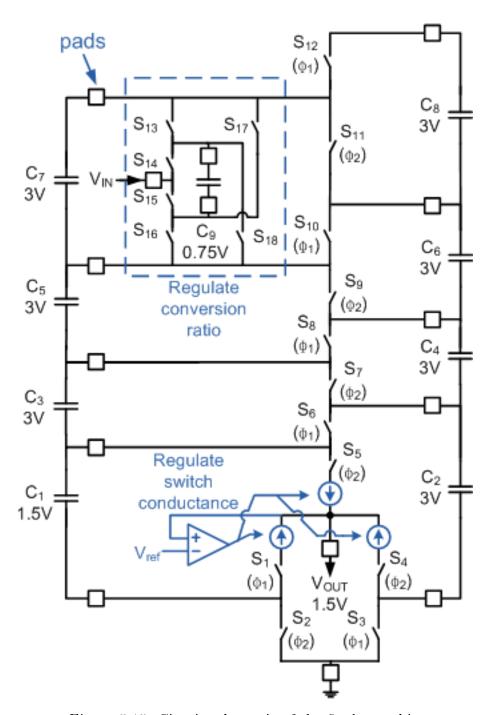

| 1   | Circuit schematic of implemented converter                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

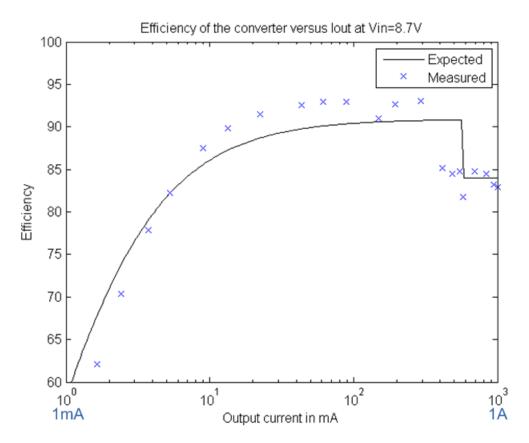

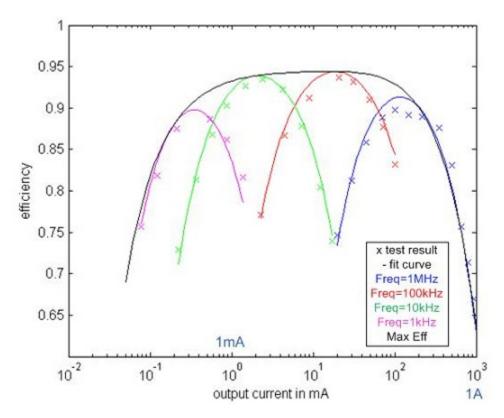

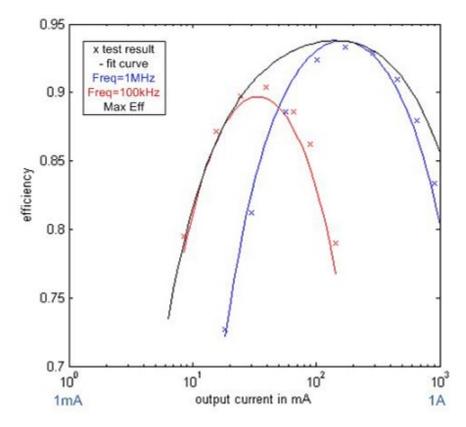

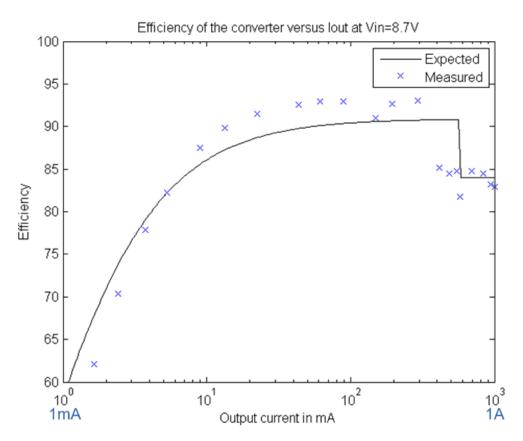

| 2   | Efficiency versus $I_{OUT}$ at around $V_{IN}=8.7\mathrm{V}$                                                                                            |

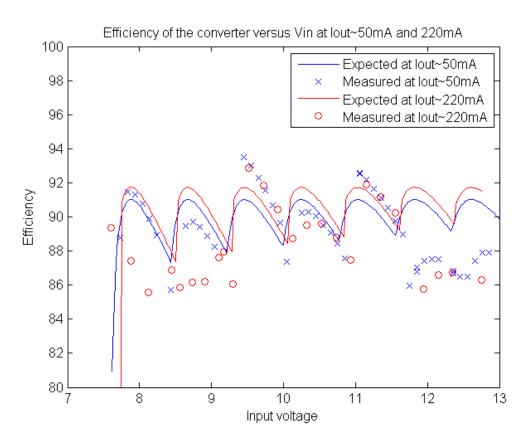

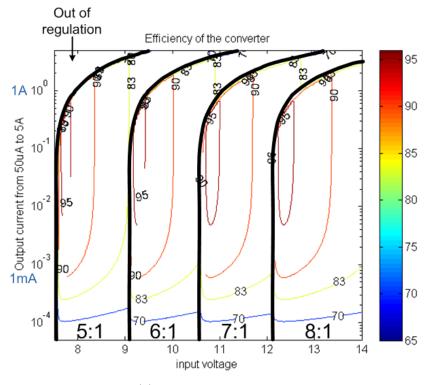

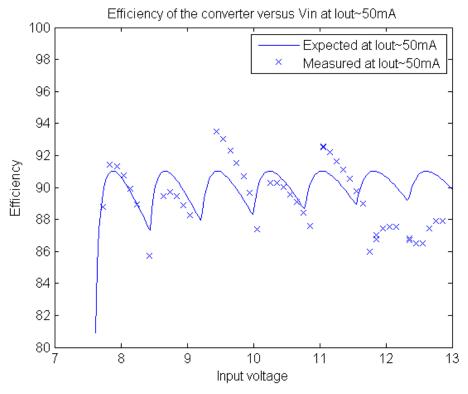

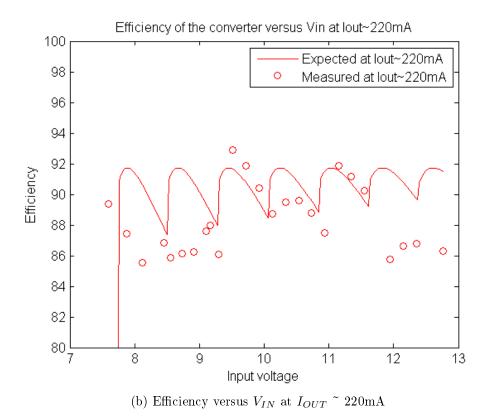

| 3   | Efficiency versus $V_{IN}$ at $I_{OUT}$ ~ 50mA and 220mA                                                                                                |

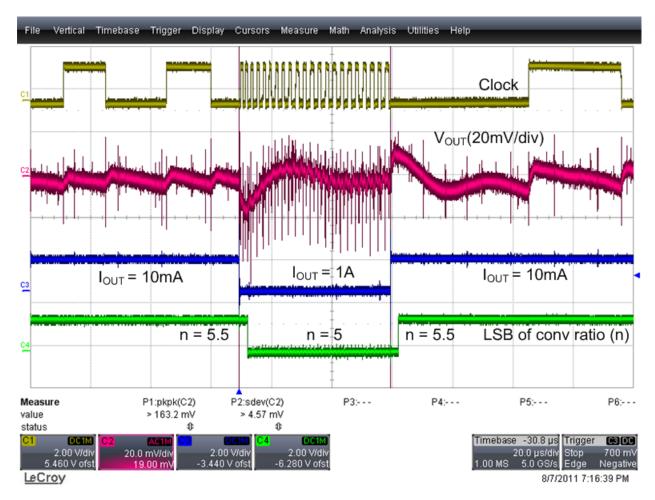

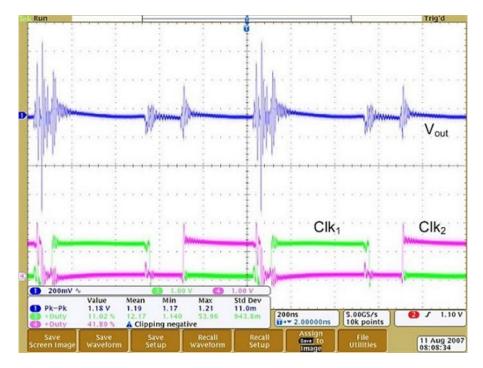

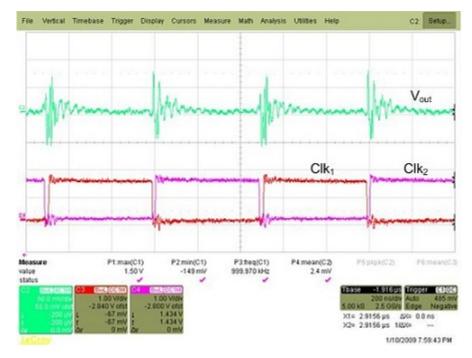

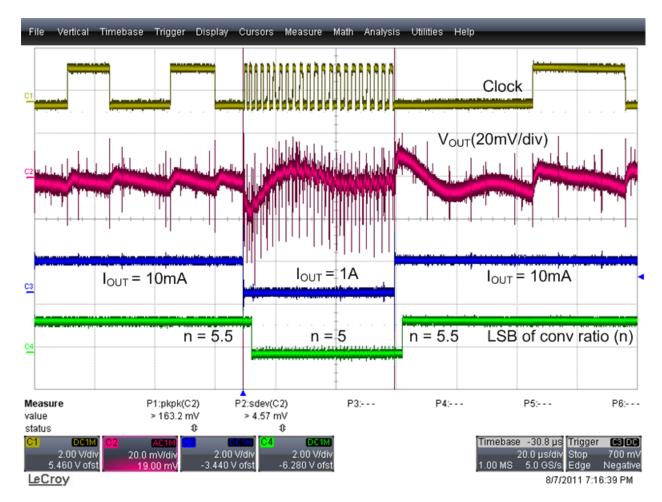

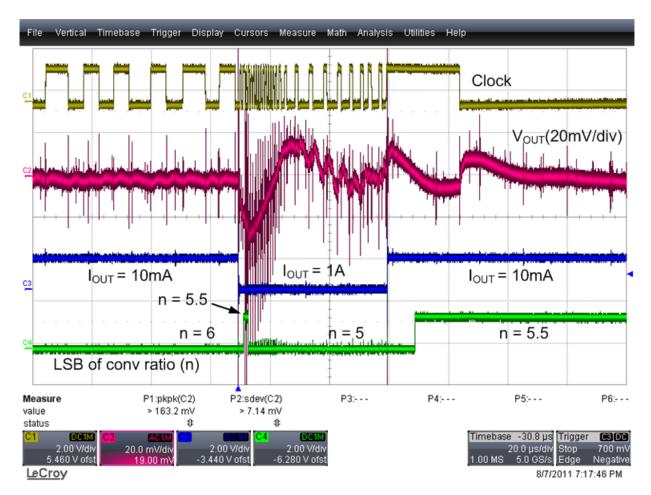

| 4   | Oscilloscope plot of loading and unloading $I_{OUT}$ step of 1A at $V_{IN} = 9V$ . The                                                                  |

|     | top waveform is the switching clock of the converter. The second waveform is                                                                            |

|     | an AC coupled signal of the output voltage in 20mV/div. The third waveform                                                                              |

|     | shows the drain of a MOSFET that switches in three $4\Omega$ resistors in parallel                                                                      |

|     | to the output. The fourth waveform shows the least significant bit of the conversion ratio, indicating that the converter changes conversion ratio back |

|     | and forth by one step during the measurement. The timescale is $20\mu s/div$ .                                                                          |

| 5   | Comparison of peak efficiency between this work and similar works                                                                                       |

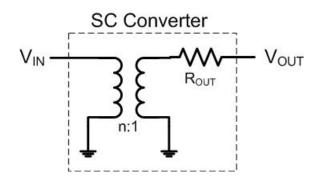

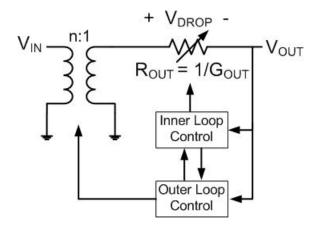

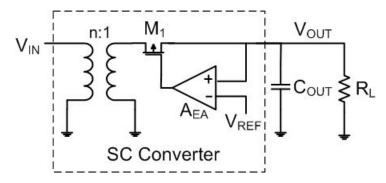

| 1.1 | Basic model for an SC converter                                                                                                                         |

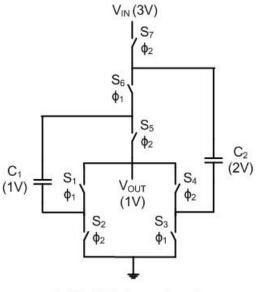

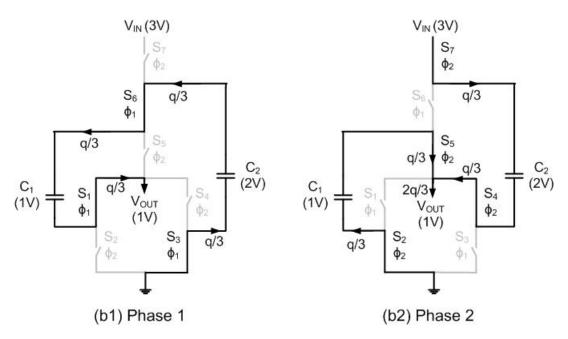

| 1.2 | (a) Schematic and (b) charge flow of the 3V-to-1V Dickson Converter in the                                                                              |

| 1.0 | two clock phases                                                                                                                                        |

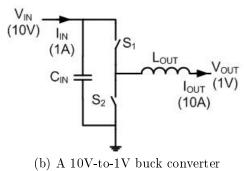

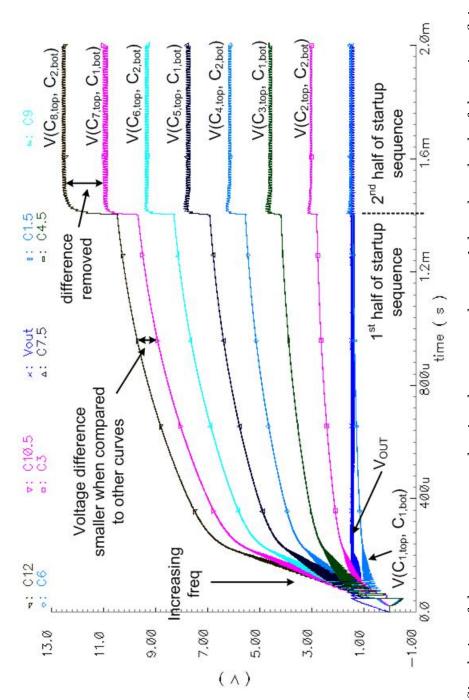

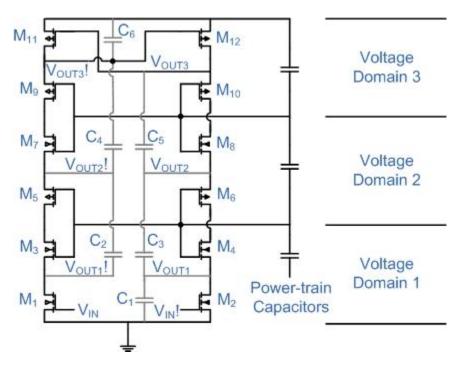

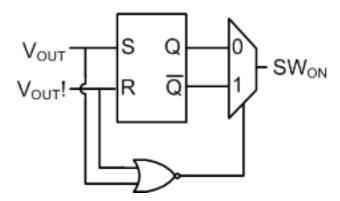

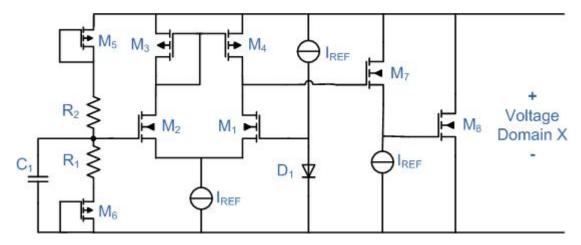

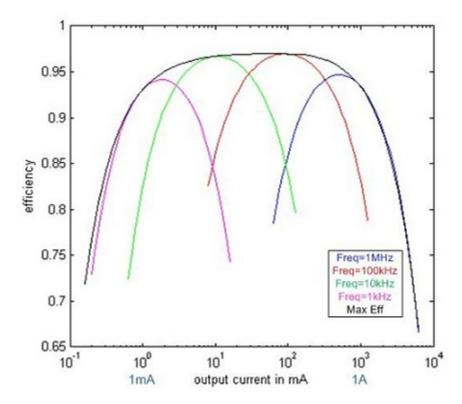

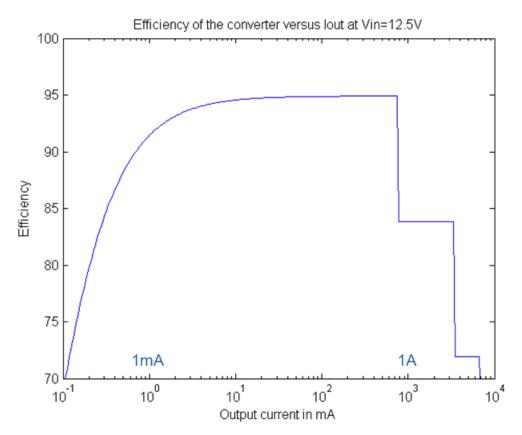

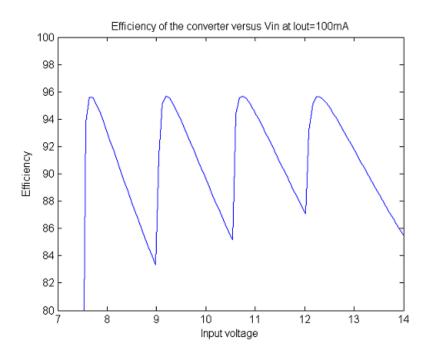

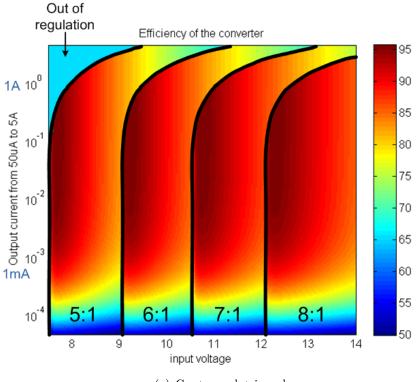

| 1.3 | 10V-to-1V SC converter and buck converter                                                                                                               |