# UC Santa Cruz UC Santa Cruz Electronic Theses and Dissertations

## Title

High-Performance, Reliable Object-Based NVRAM Devices

# Permalink

https://escholarship.org/uc/item/7533t92h

### **Author** Kang, Yangwook

Publication Date

2014

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

### HIGH-PERFORMANCE, RELIABLE OBJECT-BASED NVRAM DEVICES

A dissertation submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### COMPUTER SCIENCE

by

### Yangwook Kang

September 2014

The Dissertation of Yangwook Kang is approved:

Ethan L. Miller, Chair

Darrell D.E. Long

Sam H. Noh

Andy Hospodor

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by Yangwook Kang 2014

# **Table of Contents**

| Li | List of Figures vi |                                               |      |  |  |  |

|----|--------------------|-----------------------------------------------|------|--|--|--|

| Li | st of T            | Fables                                        | viii |  |  |  |

| Ał | ostrac             | t                                             | ix   |  |  |  |

| 1  | Intro              | oduction                                      | 1    |  |  |  |

|    | 1.1                | NVRAM Access Model                            | 2    |  |  |  |

|    | 1.2                | NVRAM Key-Value Store                         | 4    |  |  |  |

|    | 1.3                | In-Storage Processing                         | 5    |  |  |  |

| 2  | Bacl               | kground                                       | 8    |  |  |  |

|    | 2.1                | Non-volatile memory                           | 8    |  |  |  |

|    | 2.2                | Existing approaches to access NVRAMs          | 9    |  |  |  |

|    |                    | 2.2.1 Direct access model                     | 10   |  |  |  |

|    |                    | 2.2.2 FTL-based model                         | 11   |  |  |  |

|    |                    | 2.2.3 Object-based access model               | 12   |  |  |  |

|    | 2.3                | In-Storage Processing                         | 13   |  |  |  |

|    | 2.4                | Key-Value Store                               | 16   |  |  |  |

|    |                    | 2.4.1 Versioning Flash Systems                | 16   |  |  |  |

|    |                    | 2.4.2 Hashing and Bloom filters               | 17   |  |  |  |

|    | 2.5                | Byte-addressable NVRAMs                       | 18   |  |  |  |

| 3  | Obje               | ect-based Storage Model for NVRAM             | 19   |  |  |  |

|    | 3.1                | Components                                    | 19   |  |  |  |

|    |                    | 3.1.1 Object-based File System                | 21   |  |  |  |

|    |                    | 3.1.2 Object-based Storage Devices for NVRAMs | 22   |  |  |  |

|    | 3.2                | Primitive Object Operations                   | 25   |  |  |  |

| 4  | Data               | a Placement Policies For Object-based Flash   | 27   |  |  |  |

|    | 4.1                | Design                                        | 27   |  |  |  |

|    | 4.2                | Implementation                                | 31   |  |  |  |

|    | 4.3                | Evaluation                                    | 34   |  |  |  |

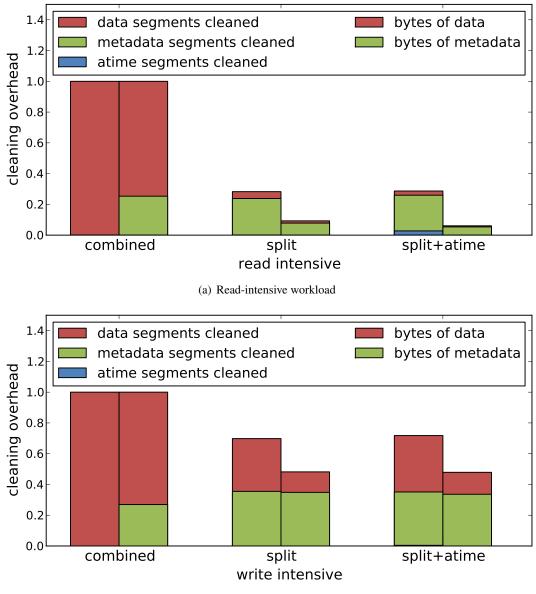

|   |      | 4.3.1    | Cleaning Overhead of Data Placement Policies                                            |

|---|------|----------|-----------------------------------------------------------------------------------------|

|   |      | 4.3.2    | Effects of cleaning thresholds                                                          |

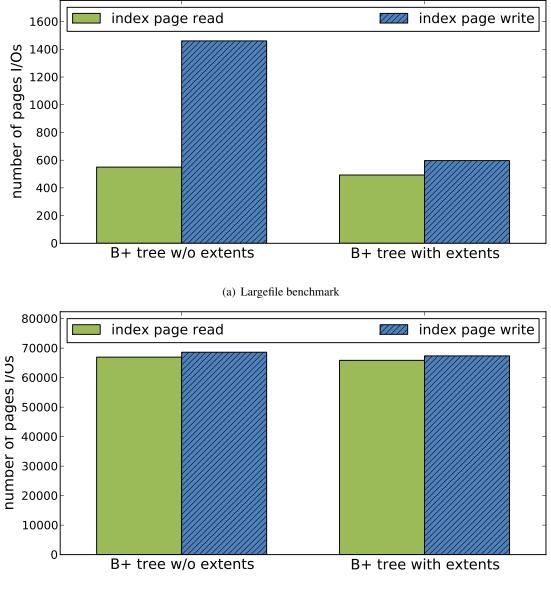

|   |      | 4.3.3    | Index Structures                                                                        |

|   |      | 4.3.4    | Effects of Informed Placement                                                           |

|   |      | 4.3.5    | Object-level Reliability                                                                |

|   |      | 4.3.6    | Overall Performance 42                                                                  |

|   | 4.4  | Summ     | ary 43                                                                                  |

| 5 | Vers | ioning   | Flash Key-Value Store44                                                                 |

|   | 5.1  | Munin    | n                                                                                       |

|   |      | 5.1.1    | Host-Device Communications                                                              |

|   |      | 5.1.2    | Hash-based Data Placement                                                               |

|   |      | 5.1.3    | Search                                                                                  |

|   |      | 5.1.4    | Version Management Layer                                                                |

|   |      | 5.1.5    | Consistency                                                                             |

|   | 5.2  | Analys   | sis                                                                                     |

|   | 5.3  | Evalua   | ttion                                                                                   |

|   |      | 5.3.1    | Segment Utilization and Memory Usage                                                    |

|   |      | 5.3.2    | False Positive Rate    57                                                               |

|   |      | 5.3.3    | Read/Write Amplification and Performance                                                |

|   |      | 5.3.4    | Versioning Overhead                                                                     |

|   |      | 5.3.5    | Cleaning Threshold                                                                      |

|   | 5.4  | Summ     | ary                                                                                     |

| 6 | In-S | torage ] | Processing 61                                                                           |

|   | 6.1  |          | are Capabilities of SSDs                                                                |

|   | 6.2  |          | SSD Model                                                                               |

|   | 6.3  |          | nart SSD Architecture                                                                   |

|   |      | 6.3.1    | Modern SSD Architecture                                                                 |

|   |      | 6.3.2    | In-Storage Processing Model for SSD                                                     |

|   |      | 6.3.3    | Host-Device Communication                                                               |

|   |      | 6.3.4    | Tasklet Programming    68                                                               |

|   | 6.4  | Impler   | nentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ 70 |

|   |      | -        | In-Storage Processing (ISP) Engine                                                      |

|   |      | 6.4.2    | Extended Hadoop MapReduce Framework                                                     |

|   |      | 6.4.3    | Communication Layer                                                                     |

|   | 6.5  | Experi   | ments                                                                                   |

|   |      | 6.5.1    | System Configuration                                                                    |

|   |      | 6.5.2    | Microbenchmark                                                                          |

|   |      | 6.5.3    | Applications                                                                            |

|   |      | 6.5.4    | Future SSD Architecture for In-Storage Processing                                       |

|   | 6.6  |          | Work                                                                                    |

|   | 6.7  |          | ary                                                                                     |

|   |      |          | -                                                                                       |

| 7 | NVI  | RAM W   | /ear-leveling                   | 87    |

|---|------|---------|---------------------------------|-------|

|   | 7.1  | Endura  | ance of Byte-addressable NVRAMs | . 88  |

|   | 7.2  | Probab  | pilistic Wear-leveling          | . 89  |

|   | 7.3  | Object  | t-based NVRAM                   | . 92  |

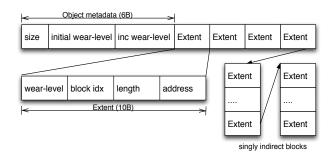

|   |      | 7.3.1   | User Objects                    | . 93  |

|   |      | 7.3.2   | Wear-aware B+ Tree              | . 96  |

|   |      | 7.3.3   | Wear-aware Buddy Allocator      | . 98  |

|   | 7.4  | Evalua  | ation                           | . 100 |

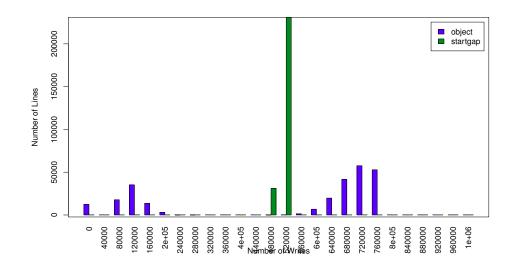

|   |      | 7.4.1   | Write Distribution and Lifetime | . 101 |

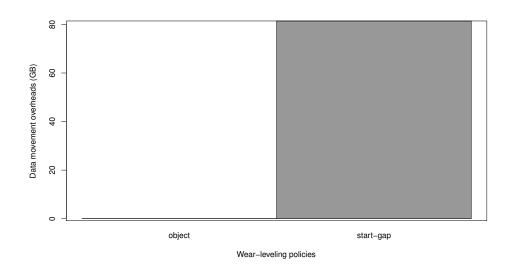

|   |      | 7.4.2   | Wear-leveling overhead          | . 105 |

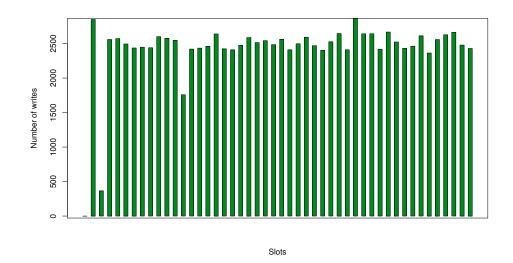

|   |      | 7.4.3   | Internal wear-leveling          | . 105 |

|   | 7.5  | Summ    | ary                             | . 106 |

| 8 | Futu | ire wor | k and Conclusion                | 107   |

# **List of Figures**

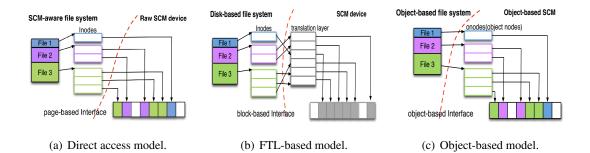

| 2.1 | Three approaches to access NVRAMs from file system                            | 11 |

|-----|-------------------------------------------------------------------------------|----|

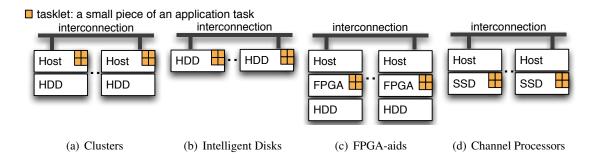

| 2.2 | Comparison of computing models                                                | 13 |

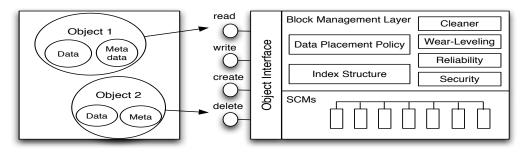

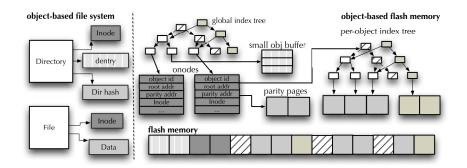

| 3.1 | System overview of object-based NVRAMs                                        | 21 |

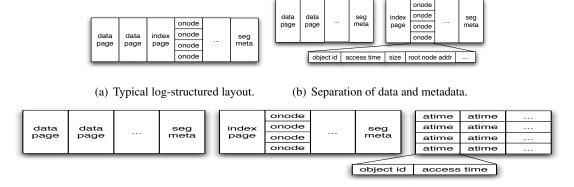

| 4.1 | Three kinds of data allocation policies                                       | 28 |

| 4.2 | Implementation of object-based flash memory                                   | 31 |

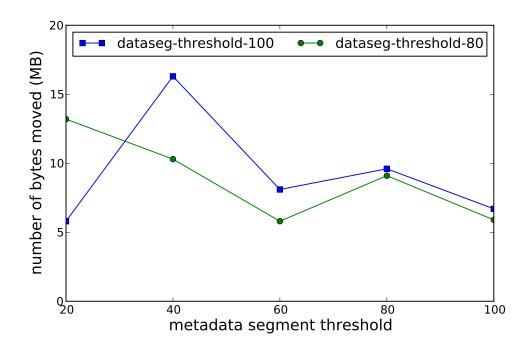

| 4.3 | Effects of cleaning thresholds for different types of segments                | 36 |

| 4.4 | Cleaning overhead of the three data placement policies. The X-axis represents |    |

|     | three data placement policies and the Y-axis is the cleaning overhead normal- |    |

|     | ized to combined policy                                                       | 37 |

| 4.5 | Effects of an extent-based allocation                                         | 39 |

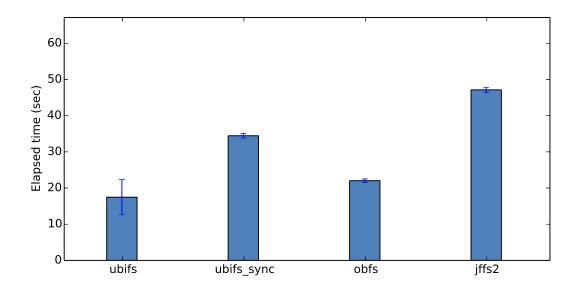

| 4.6 | Overall performance                                                           | 42 |

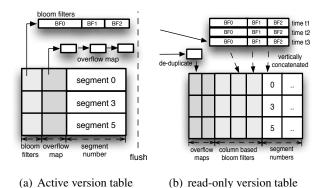

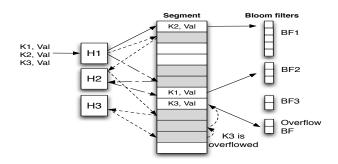

| 5.1 | Overview of Muninn                                                            | 46 |

| 5.2 | Insert a key-value pair to an active version table                            | 47 |

| 5.3 | Flushing BFs to a read-only table                                             | 49 |

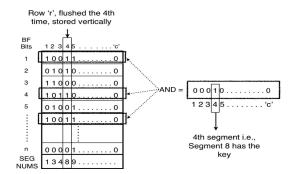

| 5.4 | Searching a key-value pair in a read-only version table                       | 50 |

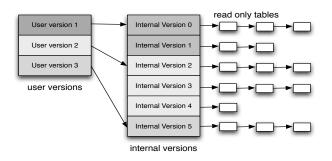

| 5.5 | User versions and internal versions                                           | 51 |

| 5.6 | Segment utilization and memory usage; the S8/7 case used the smallest amount  |    |

|     | of memory while achieving 92% segment utilization.                            | 56 |

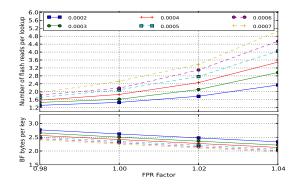

| 5.7 | Effects of false positive rate on memory overheads and read amplification     | 57 |

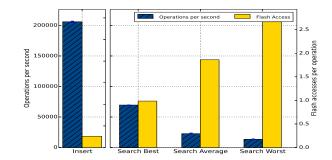

| 5.8 | Read/Write amplification                                                      | 59 |

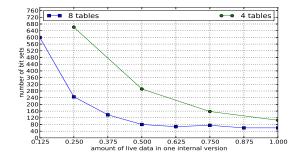

| 5.9 | Cleaning threshold for selecting a target internal version                    | 60 |

|     |                                                                               |    |

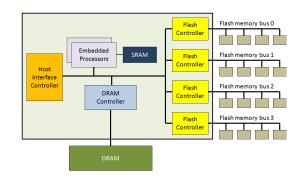

| 6.1 | The typical architecture of modern flash-based SSDs                           | 63 |

| 6.2 | Smart SSD Model                                                               | 65 |

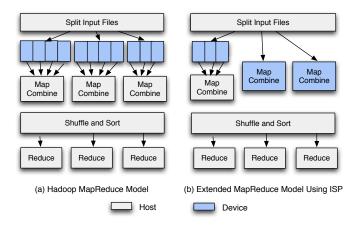

| 6.3 | Extended MapReduce framework                                                  | 67 |

| 6.4 | In-storage processing architecture for Smart SSD                              | 69 |

| 6.5 | Protocol diagram for ISP using the object interfaces                          | 71 |

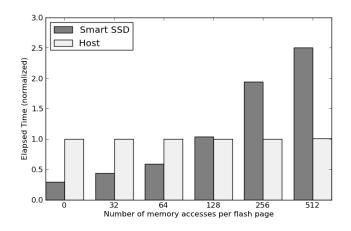

| 6.6 | Performance of in-storage processing: for each memory access, Smart SSD       |    |

|     | reads one 4 byte integer and performs one integer comparison. The performance |    |

|     | of the Smart SSD is normalized to the access time at the host side            | 74 |

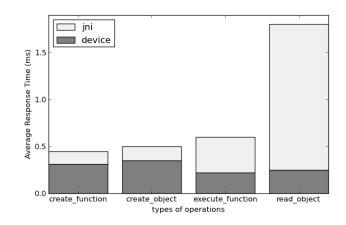

| 6.7        | Overhead of an object interface implemented on top of SATA protocol; the raw                |            |

|------------|---------------------------------------------------------------------------------------------|------------|

|            | I/O latency of the create command is higher than that in the execute and read               |            |

|            | commands, because it requires two vendor-specific commands. The JNI over-                   |            |

|            | head of the read command is high due to the additional processing for polling               |            |

|            | interval and memory copy overhead.                                                          | 77         |

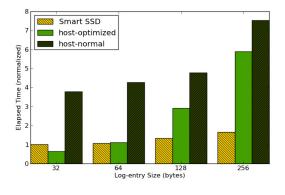

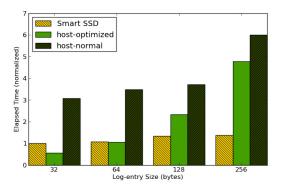

| 6.8        | Performance of log-analysis with two query scenarios. Smart SSD benefits from               |            |

|            | high internal bandwidth and no data transfer between a host and a device, losing            |            |

|            | performance slowly as the dataset size increases. However, the host-only com-               |            |

|            | puting models suffer from large data movements on larger datasets, decreasing               |            |

|            | performance                                                                                 | 78         |

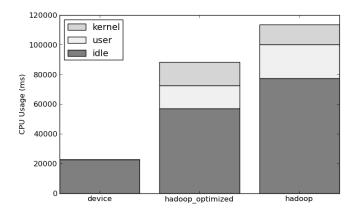

| 6.9        | CPU usage (including all cores). The Smart SSD version of the application uses              |            |

|            | almost no host resources while the host versions of applications require kernel             |            |

|            | time to process I/Os and user time to process map processes                                 | 81         |

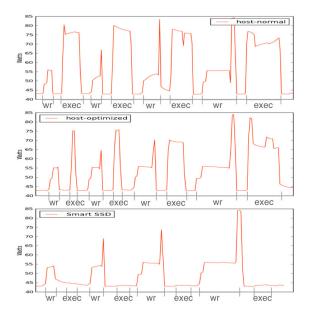

| 6.10       | For each dataset, data to be processed is first written ( <i>wr</i> phase) before executing |            |

|            | the tasklet (exec phase). In the exec phase, the system that uses Smart SSD                 |            |

|            | consumes less than 50% of the energy compared to the system that uses host-                 |            |

|            | side processing, including idle power consumption, due to the internal, low-                |            |

|            | power processing.                                                                           | 83         |

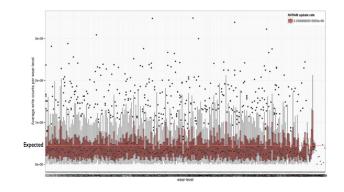

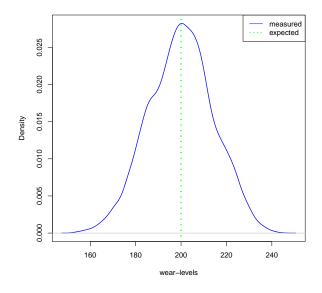

| 7.1        | Accuracy of a probabilistic wear-level tracking                                             | 90         |

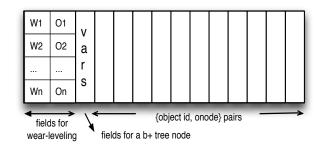

| 7.2        | Structure of an onode                                                                       | 93         |

| 7.3        | Structure of a wear-aware B+ tree node                                                      | 96         |

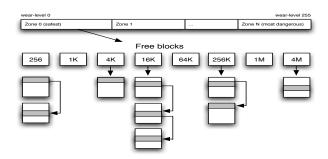

| 7.4        | Free space manager                                                                          | 98         |

|            |                                                                                             | 20         |

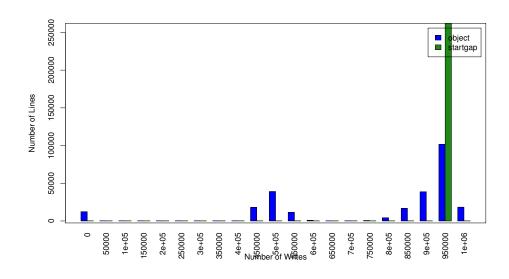

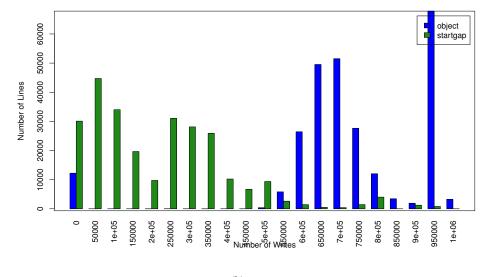

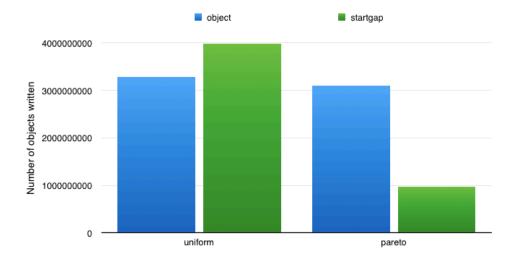

| 7.5        | Write distribution                                                                          | 102        |

| 7.5<br>7.6 |                                                                                             |            |

|            | Write distribution                                                                          | 102        |

| 7.6        | Write distribution                                                                          | 102<br>103 |

# **List of Tables**

| 2.1 | NVRAM characteristics. [41]   | • | • | • | • | • | • | • | • | • | • | 10 |

|-----|-------------------------------|---|---|---|---|---|---|---|---|---|---|----|

| 3.1 | Primitive object commands     | • |   | • |   |   |   |   |   | • | • | 25 |

|     | Effects of informed-placement |   |   |   |   |   |   |   |   |   |   |    |

| 5.1 | Design parameters             | • | • | • |   | • |   |   | • | • | • | 54 |

#### Abstract

#### High-Performance, Reliable Object-Based NVRAM Devices

by

### Yangwook Kang

Non-volatile memory (NVRAM) storage devices are increasingly used in both consumer and enterprise systems, providing high performance and low energy consumption compared to hard drives. Unfortunately, an inflexible block interface and multiple I/O subsystems designed for slow hard drives make it difficult to utilize NVRAMs in a portable and efficient manner. For example, in the OS storage stack, I/O workloads are reshaped and throttled to generate a small number of concurrent I/O requests, though NVRAMs can handle much higher workloads, and unnecessary address mapping is performed in a file system. Using NVRAM as memory can be difficult with a block interface because of small reads and writes that are common in memory workloads. At a device level, NVRAM devices need to perform a number of heuristics to attempt to recover filesystem-level semantics lost during the transmission through a block interface. As a result of these legacy interfaces, the current architecture is limited in achieving portability, efficiency, and extensibility, leaving behind more complicated problems, such as supporting heterogeneous NVRAM devices and utilizing device features.

This thesis proposes the use of the object-based storage model as a way of addressing the shortfalls of the current NVRAM architecture. More specifically, we show that the ondevice NVRAM management layer can be as efficient as that of a native file system designed for a specific type of NVRAM while providing tightly coupled hardware optimizations and drop-in replacement for new types of NVRAMs. To explore the design flexibility given by this model, we investigate several data placement policies for flash memory exploiting the rich metadata coming from an object-interface. We also design an object-based byte-addressable NVRAM device to demonstrate that the object model allows more reliable, efficient NVRAM management by integrating its core data structures and a wear-leveling policy together. Our wear-leveling policy enables a low overhead, multi-granularity wear-level tracking for byteaddressable memories by exploiting the uniformity of a random function. We also investigate its extensibility and efficiency by designing Muninn, a object-based versioning key-value store for flash memory. Realizing the object storage model requires changes in several subsystems of operating systems and hardware components, but no further system changes will be required to support new types of NVRAM. Even with the current storage stack, we hypothesize that some of the features of this model can be adopted to better utilize device hardware and improve overall efficiency of the storage system. To demonstrate these capabilities, we introduce Smart SSD, which pairs in-device processing with a powerful host system capable of handling data-oriented tasks without modifying operating system code. Our system is built on a real SATA-based SSD and extends the Hadoop MapReduce framework to support in-storage processing. Our experiments show that total energy consumption is reduced by 50% due to the low-power processing inside a Smart SSD. Moreover, a system with a Smart SSD can outperform host-side processing by a factor of two or three by efficiently utilizing internal parallelism when applications have light traffic to the device DRAM under the current architecture.

# Chapter 1

# Introduction

Non-Volatile Random Access Memories (NVRAMs) are becoming increasingly important in the storage hierarchy as the need for energy-efficient and high performance storage media increases in both consumer and enterprise markets. The recent deployment of Solid State Disks (SSDs) has accelerated this tendency by supporting backward compatibility with block devices. For example, consumer products such as laptops and smart phones are adopting flash memory to enhance their battery life and response time replacing hard drives. For enterprises, SSDs are used as a large long-term secondary cache residing between DRAM and hard drives, or replacements for 10,000/15,000 rpm hard drives and tape devices.

Beyond flash memory, several other types of non-volatile memories are currently being sold or actively developed, competing for the future storage or memory medium. For example, Phase Change RAM (PCRAM) promises high density and byte-addressability, but providing long-term resistance and high synchronous read/write performance is still challenging [1]. Ferroelectric RAM (FeRAM) provides high-performance and low power consumption, but has low density and destructive reads [28, 2]. Other types of NVRAMs such as memristors, carbon nanotube, and Spin-Torque-Transfer RAM (STT-RAM) are under development, promising superior characteristics than those currently on the market [51].

Unfortunately, despite the increasing importance of NVRAMs, storage and memory subsystems in current operating systems are not providing an efficient, portable way to adopt this technology shift yet. For example, several storage subsystems such as I/O schedulers and device queues are incurring overheads rather then contributing towards better I/O performance, and current interrupt and locking mechanisms can incur high context-switching overheads [91, 23]. At the device level, due to the limited flexibility of a block-based interface, the design of device subsystems such as mapping and wear-leveling is restricted and complicated, providing sub-optimal performance [45]. Moreover, it is not known whether this block-based access model can still be used for byte-addressable NVRAMs while efficiently hiding and handling their quirks.

In this thesis, we look towards the object-based storage model as a way of addressing the shortfalls of the current interfaces. More specifically, we show that the NVRAM management layer can be as efficient as that of a native file system designed for a specific type of NVRAM while providing tightly coupled hardware optimization and drop-in replacement for new types of NVRAMs. To demonstrate this, we explored object-based data placement and cleaning policies for flash memory, and integrated wear-leveling mechanism for byteaddressable NVRAMs. We investigate its efficiency and extensibility by designing two specialized devices: versioning flash device and smart SSD. We show that primitive object-based operations can also be served as the unified access model for these devices without sacrificing efficiency or portability, while existing protocols require dedicated command sets for each type of devices.

### 1.1 NVRAM Access Model

One of the biggest challenges in supporting NVRAM is the need for architectural changes including device-host communication, programming models for applications, file systems and operating system storage stack. Since NVRAMs are evolving technologies, these changes must cover a diverse range of NVRAM media without sacrificing their performance or capability. This leads to the first question we address in this thesis: *Given NVRAM hardware trends and their characteristics, what would be an efficient access model for NVRAMs?*

Some of the early flash storage systems, for example, designed their own flash-aware file system and devised a flash-friendly communication layer so it can directly access the flash memory controller [7, 89, 38]. This approach provides high efficiency but it is not cost-effective and lacks portability and compatibility, because file systems and communication layers were implemented and optimized for given hardware components. Today, many storage systems use SSDs, which internally have their own data management layer exposing a hard disk interface for compatibility with legacy software and systems. While not requiring hardware changes

in this model, SSDs provide sub-optimal performance, because most of file system semantics are not delivered to SSDs and unnecessary components exist in the data path. Recently, several optimizations improving the inefficiency of SSD block management layer have been proposed [15, 94, 13]. While these approaches can eventually solve many of efficiency and architecture issues, they require significant amount of changes to the operating systems and these changes are not independent to the NVRAM medium; new changes to operating systems are required to adopt different types of NVRAMs.

To allow applications and operating systems to fully utilize the features of NVRAM devices, we thought the NVRAM storage stack needs to be efficient, reliable, extensible, and portable. More specifically, it should be capable of processing both small and large I/O requests efficiently and reliably, and provide a simple but efficient byte-addressable interface while being able to adapt to NVRAM technology shifts. To find such an efficient access model that meets the requirements, we explore the current access models for flash memory and hard disks, and other models recently proposed such as T10 object-based storage devices and nameless writes [85, 94]. Then, we evaluate the suitability and efficiency of the object-based model by designing and implementing an object-based file system and a device, and comparing the differences with the other approaches.

Through experiments on various data placement and cleaning policies in our prototype, we demonstrate that data structures in the in-device block management layer can be as efficient as that of flash-aware file systems due to the rich file system semantics enabled by an object interface. Compared to typical logical block number-to-page mapping schemes in SSDs, our object-based data allocation scheme and its cleaning policy significantly reduce the cleaning overhead. Additionally, several optimizations exploiting the existence of objects such as object-based reliability and embedding small files are adopted in our prototype, providing better reliability and space efficiency. In an operating system, since there is no block management layer in a file system, it can focus on name resolution and directory management, being independent to the underlying medium. This allows file systems to support multiple different NVRAM devices without introducing any management overhead on the host side or efficiency issues on the device. It is to be noted that unlike flash-aware file systems, the performance of this model can be further improved by tightly-coupled optimizations between the block management layer and a device hardware.

### **1.2 NVRAM Key-Value Store**

With the growing need for data replication, fast retrieval and append performance, and scalability, more storage systems are adopting key-value stores rather than widely used relational database systems [80, 66]. Without requiring a relational schema, key-value stores provide a highly optimized insertion and retrieval performance to applications, sacrificing some of the searching capability such as a ranged search and a filtering. Since each key-value pair is independent to each other, managing replications across multiple distributed nodes and resolving conflicts become easier.

While key-value stores using hard disks are typically implemented at the user level, NVRAM key-value stores need to be in a device for better efficiency, similar to the block management layer in file systems. In addition, we notice that an object-interface can naturally support a key-value interface by considering an object id as a key and an object as a value. By doing so, we can allow object-based NVRAM devices to be used as a memory device, taking a memory address as a key. This leads to our second question in this thesis: *Can an object-based access model help system builders make more efficient and reliable NVRAM storage/memory systems?*

To answer this question, we design two NVRAM key-values stores: Muninn, a versioning object-based key-value flash device, which offers a transparent versioning using an object identifier to encode a version number, and an object-based NVRAM device that provides high reliability using probabilistic wear-leveling. More specifically, Muninn provides a hashbased key-value placement using multiple different-size Bloom filters [19], reducing metadata update overheads exploiting the copy-on-write nature of flash devices. It provides a transparent versioning to any legacy file system or user application at a low cost. While special devices, like in-device key-value stores, typically require special communication protocols, we show that without sacrificing usability or performance, the primitive object-based operations can be used as the unified access model, instead of adding dedicated SCSI commands every time a new feature needs to be added. Unlike the host-side key-value stores, which have two levels of data mappings and use host system resources, Muninn uses one efficient data management layer, providing a low write amplification factor and comparable read amplification factor compared to host-side key-value stores while not using any host resource. Users can roll back to a previous system checkpoint, and undo the changes to individual objects. Since users can control when to version and what to version in Muninn, it can be used for protecting some parts of data, *i. e.*, protecting operating system code, data generated by a specific application as well as system-wide checkpoints. This also allows users to mount the object based key-value store with different versions without having to roll back to a certain point.

The limited write endurance is one of the obstacles in using high density byte-addressable non-volatile memories as storage medium. Most proposed solutions are either constantly managing the wear-levels of all the lines, or adopting a coarse-grained wear-leveling based on a global counter, causing the lifetime of a device to be bounded by the weakest endurance cell or an inaccurate wear-leveling. We introduce a probabilistic wear-leveling technique for byteaddressable NVRAMs that enables low overhead, multi-granularity wear-leveling. Our wearlevel counter requires only 1 B of space and are updated infrequently, exploiting the uniformity of a random function. We integrate this technique into each object-based NVRAM data structure, allowing various swapping mechanisms depending on its data type, and eliminating the need for additional address mapping. Compared to consistent wear-leveling mechanisms, it minimizes data movements for wear-leveling by moving objects only when needed and allows a worn-out region management at no extra cost.

### **1.3 In-Storage Processing**

In contrast to hard drives where the performance is determined by the performance of the mechanical parts such as disk rotation and head movement speeds, the performance of NVRAM devices are determined by their processing power and the aggregate bandwidth to the underlying storage medium. More specifically, these devices tend to increase the number of independent data buses to the medium and use faster and more powerful processors to improve their ability to handle concurrent I/Os, hiding the overhead of data management. For instance, modern enterprise SSDs have multiple processors, large DRAM caches, and 8 to 16 or more flash channels, providing their peak performance when there are many large concurrent I/O requests available.

Despite the increasing hardware capability of SSDs, however, the performance at the application end is still limited due to legacy hardware and software designed for hard drives. While SSDs require a large number of concurrent I/O requests to maximize their performance, legacy storage subsystems typically throttle the number of pending I/O requests, and their lock-

ing and interrupt mechanisms sometimes introduce more overhead than processing an I/O request [92]. Block interfaces such as SAS and SATA are neither fast nor rich enough to leverage the potential of SSDs. The NVMe (Non-Volatile Memory Extension) standard for PCI Express [36] is designed to exploit the native performance of devices, but it is not yet robust, and requires applications to understand the characteristics of the underlying media to optimize their performance.

We may build new storage systems and applications for SSDs to alleviate the efficiency issues, but this requires too many changes to the current architecture, increasing complexity of each storage stack and losing portability. Instead, we note that NVRAM devices can be seen as a small computer system that has multiple processors, DRAM, and storage medium. Therefore, rather than processing simple read and write requests, devices can process complex I/O tasks defined by users, leveraging their internal parallelism and reducing the host system usage. By assigning jobs to devices, devices can carefully schedule internal I/O jobs in a way that the whole available bandwidth is utilized, maximizing the device performance. At the application end, it is necessary to generate and manage multiple independent I/O tasks so they can be executed concurrently across multiple devices. This leads to the third question we want to address in this thesis *How can we provide an efficient environment for both NVRAM devices and host systems that perform in-storage processing?*

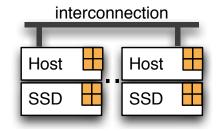

To realize this idea, we introduce the Smart SSD model, which allows host systems to fully exploit the performance of SSDs without requiring operating systems and applications to understand the particular characteristics of SSDs by offloading data-intensive tasks from a host application to Smart SSDs. Each Smart SSD has an internal execution engine for processing locally stored data, and the host machine coordinates the sub-tasks as well as directly processing some parts of the tasks. By isolating data traffic within a device, the execution engine can schedule the I/O requests more efficiently; it can decide to fully utilize all the I/O channels and processes when the device is idle, or pause the data processing when there are many pending requests from users. This model also enables energy-efficient data processing, because power-hungry host-system resources such as host DRAMs and CPUs are not used.

In addition to the firmware enhancement, we also build a prototype of the host infrastructure to leverage Smart SSDs. The communication between a Smart SSD and a host system is handled by an object-interface implemented on top of a SATA interface to provide a compatible and flexible interface to applications and operating systems. We introduced two primitives called *select\_object* and *execute\_object* that select objects to be processed and execute an in-storage process on selected objects respectively. The Hadoop MapReduce framework [4] is used as an application interface to utilize Smart SSDs while hiding the details of the communications; the MapReduce framework provides independent sets of data that can be run concurrently across multiple Smart SSDs. The results show that the overhead of object-based commands implemented on top of SATA protocol is sightly slower than that of one sector write, because bi-directional communication is not allowed. With a web log analyzer example, in-storage processing outperforms host-side I/O processing while saving 98% of energy per operation.

The rest of this thesis is organized as follows. Chapters 2 provides a background on the subjects covered in this thesis. In Chapter 3, we discuss the design flexibility of the objectbased access model compared to existing models, and subsequently in Chapter 4, we show the performance effects of rich file system semantics by prototyping the object-based storage model based on flash memory.Chapter 5 discusses the design goals of the key-value store we are going to provide. Chapter 6 presents the use of object-based interface on a real SSD implementing in-storage functionality, and Chapter 7 introduces probabilistic wear-leveling integrated into NVRAM data structure. Conclusions as well as possible directions for future work is given in Chapter 8.

# **Chapter 2**

# Background

Various types of non-volatile memories have become available with the rapid development of semiconductor technologies. However, the unique characteristics of these memories and the restrictions imposed by a block interface have led to many different storage system designs. In this chapter, we introduce these existing NVRAM storage system designs, and provide the background information needed to evaluate our use of the object-based storage model for NVRAM. First, we discuss the characteristics of NVRAMs, and various storage system designs to access and utilize them. This includes efficiency and portability issues that remain unsolved in current architectures. Second, we describe the current use of the object-based model in distributed systems and why it can be useful in supporting NVRAM devices. Third, we provide a discussion of in-storage processing, one way to take advantage of the full performance of an NVRAM device without requiring host operating system change. Fourth, we describe several host-side flash key-value stores, whose interfaces are natively supported by object-based devices, and versioning file systems, Bloom filters, hash functions that are relevant to the design of Muninn. The final section describes the current interfaces and wear-leveling techniques for byte-addressable NVRAMs.

### 2.1 Non-volatile memory

Non-volatile memory(NVRAM) is a class of memory that provides fast random I/O performance and non-volatility, including flash, FeRAM, magnetic RAM, phase-change memory (PCM), and carbon nanotube memory [51, 63, 21]. NVRAM blurs the distinction between

main memory and secondary storage devices at a cheaper price than DRAM, and faster random access than disks. However, the direct use of NVRAMs in current systems requires detailed knowledge of the hardware for extracting higher performance and perhaps even proper operation.

The cell-level characteristics of these NVRAMs are well known and summarized at Table 2.1. Flash memory supports page-level access but does not support overwrites due to the need to erase a block, which consists of multiple pages, before rewriting it. While other types of NVRAMs such as PCM and MRAM provide byte-addressability and in-place update, each of them is also different in characteristics such as scalability, reliability, wear resistance, performance, and retention-differences that might favor different storage system designs. For example, flash-aware file systems usually use a log-structure to support out-of-place updates, and use a cleaner to reclaim invalidated blocks to generate free blocks for future writing [8, 43, 37]. PCM has the highest density and lowest endurance requiring wear-leveling. While other technologies such as STT-MRAM and carbon nanotube NVRAM are promising more DRAM-like characteristics, they are still early in development and except for PCM, their characteristics at a few hundred Gb density has not been revealed so we do not know what characteristics future NVRAM storage devices would have yet. For example, pushing these NVRAMs to higher densities would make endurance worse as we have seen on TLC NAND flash memory. Moreover, other technologies may have their own drawbacks such as destructive read in FeRAM. Since byte-addressable NVRAM are evolving technologies and there are a number of candidates, it is not feasible to change the host system whenever a new type of NVRAM is available. Thus, portability, reliability and performance are primary issues in designing a NVRAM-based storage system.

### 2.2 Existing approaches to access NVRAMs

Currently, there are two approaches to access NVRAM devices. These approaches either use a direct access model on the host side (Figure 2.1(a)) or an FTL-based model embedded in the underlying hardware (Figure 2.1(b)).

|                   | NAND            | PRAM   | FeRAM | MRAM  |

|-------------------|-----------------|--------|-------|-------|

| read              | 15 µs           | 68 ns  | 70 ns | 35 ns |

| write             | 200 µ s         | 180 ns | 70 ns | 35 ns |

| erase             | 2 ms            | none   | none  | none  |

| in-place update   | No              | Yes    | Yes   | Yes   |

| cleaner           | Yes             | No     | No    | No    |

| write endurance   | 10 <sup>5</sup> | 108    | 1015  | 1015  |

| access unit       | Page            | Byte   | Byte  | Byte  |

| power consumption | High            | High   | Low   | Low   |

|                   |                 |        |       |       |

Table 2.1: NVRAM characteristics. [41]

### 2.2.1 Direct access model

The direct access model, shown in Figure 2.1(a), supports direct access to NVRAMs by either placing them on the main memory data path, or designing a specific file system that allows NVRAMs to work properly in the system. For instance, flash-aware file systems such as YAFFS [8], JFFS2 [90], RCFFS [43], and UBIFS [38] directly access flash memory via device drivers. Some storage systems for byte-addressable NVRAMs place them on the main memory bus, and use them as memory [58, 27], or secondary storage for metadata [49, 32].

The main advantage of this approach is that the core functionalities of the file systems such as indexing and data placement policy can be efficiently implemented for high performance. Since the characteristics of the underlying medium are understood by the file system and the raw medium can be accessed directly, the file system can fully control the medium. For example, flash-aware file systems such as YAFFS [8] and JFFS2 [90] use a log-structured mechanism [76] to meet out-of-place requirement in flash memory. While these two early flash file systems do not store indices on flash, the next version of JFFS2, UBIFS [37], uses a wandering tree, which supports out-of-place update, to store the on-flash indices, reducing memory footprint. Several approaches have been proposed to further improve the index efficiency and data placement for flash-aware file systems. Kang *et al.* developed the  $\mu$ -tree [42], which is a variation of a wandering tree that packs several nodes modified by the change of a single leaf node into one page. Lim and Park place data and metadata to separate flash blocks to reduce

Figure 2.1: Three approaches to access NVRAMs from file system

the cleaning overhead by a pseudo hot-cold separation [54].

However, since a NVRAM controller, a file system, and associated storage stacks need to be designed and developed, deploying highly optimized systems often require a long development time; while file system developers need to know the details of the underlying hardware configuration for optimizations, they do not tend to have early access to hardware, making it a longer delay to getting the whole system working. Thus, instead of relying on the features of the underlying hardware, many file systems are designed to use a fixed set of APIs — such as read\_page and write\_page — that are supported by lower storage stacks. However, these lower storage stacks have less information than file systems. They may lose the chance of more tightly-coupled optimizations enabled in the FTL-based model. For example, a file system may want to place data and metadata to different dies so they can be retrieved at the same time. But device drivers can not tell which request contains metadata. In addition, the migration from one type of NVRAMs to another is also problematic, because it requires both hardware and software to be re-implemented or at least a file system needs to be modified or developed. A lack of generic interfaces for NVRAMs and the need for both hardware and software changes for each NVRAM make this model difficult to adopt in commodity systems.

#### 2.2.2 FTL-based model

The second approach, widely used in modern SSD-based systems, is to access NVRAMs via a block translation layer. As depicted in Figure 2.1(b), the NVRAM device in this model contains a sector-to-page mapping table, and exposes a block interface to the host, allowing legacy file systems to access the NVRAM as a block-based storage device. Thus, FTL-based storage devices can replace current hard disks without modifications to the operating system.

However, compatibility with legacy systems comes at a high cost. Since the block interface is designed for disks and supports only read and write sector operations, the device cannot acquire essential information such as type of operations and data type to place or reclaim data blocks. As a result, there have been many efforts to improve the performance of the flash translation layer that propose mapping schemes, cache strategies and heuristics [25, 69, 47, 52]. For example, the use of the TRIM command in flash memory allows the device to recognize delete operations so that the device can invalidate data blocks belonging to a deleted file [79]. In spite of these efforts, they are not as efficient as the direct access model and are often very complex, due to a number of heuristics to catch the filesystem-level information lost during the transmission. Moreover, a fundamental problem of the FTL-based model is the existence of two translation layers in the data path, one in the file system, and one in the device.

Two approaches have recently been proposed to overcome the limitations of the FTLbased model by removing or minimizing the mapping table in the device. Arpaci-Dusseau, *et al.* proposed *nameless writes*, allowing the file system to directly manage the mapping table [14]. In this model, the device returns the physical page number to the file system so that it can store a mapping between a logical block number and a physical page number in an inode. DFS is a flash file system that uses a similar approach [40]. It also removes the mapping table from the device, and moves it to the virtualized flash storage layer, which is an FTL that resides in the operating system. Both approaches focus on reducing the complexity of the device and allow the operating system to control the device. However, *nameless writes* has some limitations in optimizing the flash device, since the file system has no information about the underlying medium except for a physical page number. In DFS, drop-in replacement for other types of NVRAMs are not easy because they would require a new file system for the underlying NVRAM or suffer from performance issues of using the block interface.

#### 2.2.3 Object-based access model

The object-based access model has been used in high-performance and large-scale distributed storage systems [22, 33, 84]. These systems, including Panasas [62], Ceph [86], and Slice [12], use object-based storage devices (OSDs) to make each disk-based device work independently of the master server, and add more functionality to the device such as replica management, load-balancing, and data placement. In these systems, the object-based storage

Figure 2.2: Comparison of computing models

model allows devices to map IDs to variable-length blobs so they can recognize the size and type of each data locally stored, and process them without any coordination from a host system. Thus, the system can achieve high scalability and robustness.

While disk-based OSDs provide useful features in distributed systems, they have not gained much attention as a replacement for block based devices, because disks work efficiently with block interface since disks rarely remap blocks. Recently, however, Rajimwale *et al.* proposed the use of an object-based interface for flash memory [73]. In systems using NVRAMs where a richer interface than block interface is required, however, this model could alleviate several problems of the existing approaches: the lack of file system level information in the FTL-based model, portability in the direct access model, and efficiency of implementation in both. Under this model, the device can optimize the performance of the device using informed optimizations. Moreover, this approach allows a single file system to support multiple OSDs, making it easy to switch to a new type of OSD or even include multiple device types in a single file system. More advanced features exploiting the existence of objects such as object-level reliability and compression can be provided independent of the file system.

## 2.3 In-Storage Processing

In contrast to hard drives, where the performance is limited by the movement speed of mechanical parts, the performance of NVRAM devices depends on the performance of processors, the amount of memory, and internal I/O bandwith. This allows NVRAM devices to be capable of processing offloaded jobs from host systems without requiring additional hardware components. The idea of disk-resident processing delegating system intelligence from host CPU to peripherals was first introduced a few decades ago for database machines. Early systems mainly focused on improving the performance of hard disks through dedicating a processor per head, track, or disk [67, 81]. However, they failed to survive because the high manufacturing cost could not be justified for marginal performance improvement. As computer systems were commoditized, however, the idea was resurrected in the late 1990s, and the intelligent disks (disk-resident processing) were actively investigated [46, 74, 75]. The studies on intelligent disks regard a disk as a complete computer system for efficient data processing and assume that the aggregation of compute capacity of less powerful but scalable processors performs better than the host-based approaches with dumb disks (Figure 2.2(a)).

Keeton *et al.* introduced the concept of IDISK (intelligent disk) for scalable decision support databases [46]. The basic idea behind this approach is to offload the data processing from desktop processors to lower-power processors to improve cost-performance. Thus, IDISK is designed as a general purpose network node that can replace costly cluster nodes. However, it was not able to be fully realized at that time because of the physical space constraint and the limited power and cooling supply issues. Riedel *et al.* proposed a similar concept called Active Disk (Figure 2.2(b)) that combines on-drive processing and large memory to allow disks to execute application level functions at the device [74, 75]. Another Active Disk [5] by Acharya *et al.* focused on the programming model and algorithm rather than the device architecture. They proposed a streaming programming model for application development, a sandbox model for secure task execution, and operating system supports both at the device level and at the host level. However, none of the previous approaches were implemented on commercially-available hardware. For example, Active Disk was designed to exploit internal disk components, but the experiments used an additional 64 MB bytes of RAM and an external processor to simulate a 4 GB disk.

More recently, there has been a resurgance in interest in in-storage processing, as exemplified by FAWN (Fast Array of Wimpy Nodes) [11], which uses low-power processors and flash to do data placement. However, FAWN KV is designed to handle PUT-GET style requests rather than coordinating and offloading the arbitrary I/O processing tasks. In this architecture, *all* data processing is offloaded to the flash nodes, requiring each node to consider data placement. There is no central coordination in the system, requiring distributed protocols

to spread work around. This model works well for PUT-GET requests, but is poorly suited to Map-Reduce style processing. In addition, as it needs raw accesses to flash, a custom-designed embedded hardware is required, decreasing portability.

The concept of an intelligent disk was also adopted in the system-level solutions beyond a single device. Mueller *et al.* introduced an external module (*e. g.*, FPGA) attached to a disk (Figure 2.2(c)) that implements the system intelligence [59, 60]. IBM Netezza's Blade server [64] is a commercial version of this approach. In contrast, Oracle's Exadata is a commodity-based solution of an approach in which commodity storage servers reduce the amount of traffic by filtering data [88]. However, these solutions either require additional hardware components, or need an entire system that supports a specific type of in-storage processing.

Recently, several researchers have explored the potentials of SSD-based on-disk processing. Kim *et al.* investigated the benefits of ISP on SSD with the database scan operation [50]. They claimed the old lesson that the magnetic disk is the bottleneck of storage architecture for legacy database machines is no longer true because the fast storage medium and the increased parallelism in SSDs make the other components—embedded processors and memory—the bottleneck. Based on this intuition, a FMC (Flash Management Controller) with a scan function (Figure 2.2(d)) was simulated to filter data along the flash data path. However, due to the limited processing power, the limited amount of memory, and real-time contraints in a FMC, its applications are limited to relatively simple data processing such as filtering.

Boboila *et al.* proposed the approach of Active Flash to enable the out-of-core data analytics [20]. This study provides an analytical model that shows the performance-energy tradeoffs in moving data processing to SSDs in an HPC (High Performance Computing) context. Using a SSD simulator based on DiskSim, it shows that, with careful job scheduling that considers both the garbage collection overheads and idleness of SSDs, a significant amount of energy can be saved with only minor performance degradation. While the results are well aligned with our measurements on real SSDs, we found that the current SSD architecture is not sufficient to support the complex tasks. We also provide the in-storage processing model, which defines a host and application interface.

### 2.4 Key-Value Store

Key-value stores are specialized file systems optimized for insert and retrieval of small data associated with a fixed length key, replacing the needs for complex data base systems. These Key-Value stores are typically designed to work with SSDs, allowing better I/O performance. However, similar to legacy file systems using SSDs, two levels of data mapping are performed and host resources are used to manage the key-value pairs. Therefore, the memory usage and CPU usage become an important factor in achieving not only the performance, but also scalability.

FlashStore [30] is a key-value store used as a cache for hard-disk based key-value storage system. It uses a single in-memory hash table to index all keys on flash and hence achieve one read per lookup. SkimpyStash [31] indexes the flash via a hash table with linear chaining to achieve low memory footprint. However, it requires on average 5 flash reads per lookup. BufferHash [10] maintains multiple hash tables—one in memory and the others on flash and a small set of Bloom filters to indicate whether a key might be present in a hash table.

BloomStore [56] is a recent key-value store based entirely on Bloom filters (BF). They append incoming Key-Value pairs to Flash page and maintains one BF per Flash page. Hence, the system contains many BFs and lookups have to search all the BFs in parallel and in batches to locate a key. Aiming to achieve low memory footprint, they store the large amounts of older BFs in Flash and read them in for lookups, hence increasing read amplification. The increased false positive rate of having multiple BFs has not been addressed properly. SILT [53] achieves a low memory footprint and a low read and write amplification using log store, hash store and sorted store. In this approach, key-value pairs are first written to a log store, then get converted to a hash store merges with it, requiring a large amount of free space. However, the number of flash read and write accesses can be much higher than a per-request amplification factor due to the background processes, moving data between stores. Supporting failure recovery and deletion can also be difficult.

### 2.4.1 Versioning Flash Systems

Versioning file systems keep a number of old copies of each file so the system can recover the previous status of each file on demand. Versioning is similar to a periodic backup, but the granularity of versioning is controlled by the file system; backup can be generated per file, device, and partition. Since out-of-place updates are required in flash memory, every flash device has multiple versions of the modified data. However, not many flash storage systems of-fer versioning, because it has to preserve the write order, which contains the full history of each file or data chunk, and store metadata and require additional user commands such as snapshot and rollback. It is not easy in most FTL schemes where the location of invalidated metadata is not easily trackable without reading many segments, and recognizing file boundary is not possible. For example, Lightweight Time-shift FTL (LTFTL) [82] enables to create version states at any time and go back in time to desired states. However, although it supports snapshots, finer-grained full versioning such as per-file versioning and per-directory versioning is not provided. Similar to Muninn, Tango [17] provides snapshots, but it is designed to support consistent replication without using complex distributed protocols, not focusing on directly managing flash memory or providing per-object versioning.

#### 2.4.2 Hashing and Bloom filters

Hash-based data placement schemes were actively explored in 1980s [57, 55, 77, 93]. However, due to the uniformity of the hash-based distributions, these methods were not the ideal choices for hard disks where reducing the head movements is a primary design factor. The characteristics of flash memory and byte-addressable NVRAMs make hashing an interesting choice today, because the access latency is the same regardless of its address and metadata overhead can be minimized by not storing the actual key-page mapping.

Bloom filters are interesting alternatives for the mapping structure in hash-based placement, because it requires less space and provides high insert and look-up performance. While traditionally Bloom filters focus on how to manage static data set, there are several types of Bloom filters for dynamic data sets. Dynamic Bloom filter[34] increases or decreases the siz of the Bloom filter as the number of keys in each Bloom filter changes. Scalable Bloom filters [9] the false positive rate of each Bloom filter keeps decreasing as the number of Bloom filters increases To reduce the compounded error probability.

### 2.5 Byte-addressable NVRAMs

This section describes next-generation byte-addressable NVRAMs and file systems and algorithms designed for them. There have been largely two issues in adopting NVRAMs in storage systems; communication model that defines responsibilities of operating systems and devices and NVRAM characteristics. We will summarize the NVRAM characteristics first, and then discuss data structures, algorithms, and communication models designed for byteaddressable NVRAM.

Wear-leveling policies designed for byte-addressable NVRAMs can be classified into two categories: finer-grained, consistent wear-leveling and coarse-grained wear-leveling. The consistent wear-leveling techniques such as Start-Gap [72] and hardware bit-shifting [] keep the wear-level of all memory regions be within a certain range, by moving data periodically, usually based on a global counter. Depending on a frequency of data movements, they can achieve low overhead and good wear-leveling performance. However, data has to be moved even when the lines are still young and it makes it difficult to support a worn-out region management, which makes the lifetime of a device bounded by a weakest line. That is critical when there are high endurance variances between cells.

Coarse-grained wear-leveling policies are mostly used in file systems, exploiting the prior knowledge about their writing policies and data structures; they achieve low tracking overhead sacrificing some accuracy. For example, PFFS [70] uses a segment swapping and page shifting based on a log structure. However, unlike flash, data in segments can still be updated in place. When a large portion of a segment are frequently updated, it might incur a large data movement overheads, leading to a shorter device lifetime.

Unlike these two groups of policies, our policy is designed to support both fine and coarse-grained wear-leveling where a device can use different granularities on different data structures while minimizing tracking overhead as coarse-grained wear-leveling.

In flash memory, the use of a log-structure has been popular because of its requirement for out-of-place update. For byte-addressable NVRAMs, there are more data structures available to use. NV-heap implements a heap data structure that supports ACID transactions and prevents pointer corruption [26]. BPFS [27] uses a variant of B+ tree as an index structure optimized for PCM. They are detached from wear-leveling policies making it portable, but losing possible opportunities to reduce wear-leveling overheads.

# **Chapter 3**

# **Object-based Storage Model for NVRAM**

While NVRAMs have the potential to alleviate the trade-off between performance, reliability, and energy in storage and memory subsystems, the legacy block interface and storage subsystems designed for dumb slow I/O devices make it difficult to efficiently exploit NVRAMs in a portable and extensible way.

In this chapter, we describe the use of the object-based storage model as a way of addressing the shortfalls of the current interfaces. We first discuss the two main components in this model and how each storage layer is re-located in this model. Then, we discuss the problems of the current ANSI T10 OSD standard [61], and propose the primitive operations for NVRAM devices.

### 3.1 Components

The object-based model, shown in Figure 3.1, consists of two main components: the object-based file system and object-based devices. The file system and OSDs communicate via an object-interface, which exposes various types of object commands. Each operation contains an object, which includes a variable-length data and metadata associated with the data, describing one file-level or user-level I/O request. By exposing enough operations to capture file system operations as depicted in Figure 3.1(b), this eliminates the needs for host system utilities such as TRIM, which informs the devices whenever a file is deleted. Small-size requests, byte-addressable NVRAMs can be better supported.

Unlike a block-based file system, an object-based file system only provides the name

resolution, offloading the storage management layer to the OSD. By isolating device-specific technology behind a metadata-rich object interface, the host-level file system becomes independent of the underlying storage medium while being able to deliver full file system level semantics to the devices. Thus, a single object-based file system can efficiently support multiple heterogeneous OSDs, in contrast to the current approaches that either require significant changes in the system or sacrifice I/O performance. Since the device manufacturers have better knowledge about the hardware configuration of NVRAM devices than file system designers, this model typically enables better hardware optimizations than native NVRAM-aware file systems.

When a hybrid NVRAM device becomes available, for example, both NVRAMaware systems and FTL-based systems would require a host system change. A host file system and its I/O subsystems need to understand the characteristics of multiple NVRAM medium in NVRAM-aware systems. FTL-based systems would require an intelligent layer in a host system that can deliver file-system or user-level semantics to the device, otherwise, the use of NVRAMs is limited to a write buffer for file system blocks. Optimizations such as *nameless writes*, can provide such layer in the system. However, it will require a host system change whenever a target NVRAM media changes.

The block interface is limited in that it only delivers the sector number and the request type (read or write) to the device. In contrast, the object-based interface delivers objects (which contain both data and associated metadata) and recognizes all types of requests that the file system does. By doing so, the OSD is able to receive the same level of information that the file system maintains, allowing devices to provide features such as hot/cold separation to reduce cleaning overhead that have traditionally been provided by native file systems [45]. For small objects, OSDs can achieve better space efficiency than block-based devices due to the lack of a minimum allocation size. OSDs can reduce index overheads by using extent-based allocation for large, infrequently updated objects. In addition, by encapsulating data in objects, OSDs can provide more advanced features, such as object-level reliability, compression, and execution-in-place. Moreover, adding an object interface will not significantly complicate the existing FTL firmware design since NVRAM devices already need a translation layer for data placement and segment management. For example, when hybrid phase-change/flash memory is used, the file system can store data efficiently by simply sending a write-object request to the OSD; the file

(a) Object-based file system.

(b) Object-based device.

Figure 3.1: System overview of object-based NVRAMs

system need not know about the two types of memory in the device.

### 3.1.1 Object-based File System

An object-based file system maintains files consisting of one or more data objects, which contain the file data, and a single inode object, which records metadata information about the file, such as permission and ownership. However, the inode does not point to the physical blocks, but rather the objects that make up the file, a mapping that can be done algorithmically by having the objects be identified by a combination of the unique file ID and the object's offset in the file [86].

*Flat namespace* Objects are identified by a 128-bit unique identifier, not by humanreadable names. Thus, the identifier does not have any information about the logical relationship among objects unlike directory hierarchies, offering more flexibility when assigning and distributing objects. For example, the file system can assign a certain range of objects to each distributed node, so it can retrieve the location of object without searching and make the object sharing easy. Multiple independent sub directory hierarchies can also be built within each object range.

**POSIX interface** The object-based storage model can support both POSIX interface and an object-interface as a user interface. When the POSIX interface is used, the Virtual File System (VFS) in an operating system passes an inode number and an offset to an object-based file system. Then, the file system generates an object identifier, and sends data, and necessary metadata for the given type of request to the OSD via an object interface. Although the OSDs maintain a flat namespace internally, the directory support can also be implemented in the file system. When an application directly accesses the OSD via an object interface, the application can send higher level information to optimize its data path. For example, full text searching can be executed within a device, sending only the results of the search to the host, not the whole contents of an object.

When a file request comes in from the VFS layer, the file system finds objects related to the request based on an inode number and a file offset, and generates an object request for the data. Then it determines whether the requests can be deferred before sending, because the OSD can deal better with a large object, instead of multiple small objects. For directory operations, the file system can assign an object for each directory entry or store directory entries in a data object for a directory. Although an object-based model uses a flat namespace, supporting directories is not very different from that of typical file systems, since typical file systems also need to convert the directory and file name into unique inode numbers in order to maintain a hierarchy. For example, when receiving a delete request, the file system only needs to finds a set of object IDs, and send one or several delete\_object() requests to the OSD, instead of generating several read\_block and write\_block operations to the device as is done in traditional block-based file systems.

### 3.1.2 Object-based Storage Devices for NVRAMs

Similar to SSDs, an OSD consists of NVRAM chips and multiple subsystems required to handle the characteristics of the medium such as a data placement policy and a wear-leveling mechanism, as shown in Figure 3.1(b). However, the design of its subsystems are more similar to that of typical native block managers for NVRAMs, because OSD subsystems can exploit the same level of information that native file systems have while SSDs require many heuristic algorithms to alleviate the problems of using the block interface.

By having rich information about the requests and a block management layer in the device, the OSD approach enables better hardware optimizations as well as simple and efficient subsystems. For example, device manufacturers can split a large write request into small concurrent write requests to multiple NVRAM chips in order to improve performance. Moreover, OSDs can further exploit the existence of objects to provide more advanced features such as object-level reliability and compression.

*Object-level reliability.* Most NVRAM devices used today rely on per-page error correction algorithms, which can detect and correct a certain number of bytes in a page depending on the size of the ECC. However, this approach cannot protect data against whole page failures, reading the wrong data back, or misdirected writes, which store the requested page to the wrong address and return a success code to the file system [16]. However, an object-based NVRAM can recover from this type of error by providing per-object parity. The device generates one group of parities for all data pages, and another group of parities for an object whenever it is modified. By reading all data blocks belonging to an object and comparing against the parity, it can detect and correct misdirected writes and whole page failures as well as bit-flips. The amount of parity can be adjusted based on the error rates of the medium by the device manufacturers or specified by the user on a per-object basis. In our prototype, described in Chapter 4, we maintain one parity for data pages and one parity for index nodes for each object.

*Object-level compression and encryption.* Since OSDs can access to object metadata, they can infer an object's type and determine whether it is a worthwhile for compression. The type of object, such as text or multimedia, can be inferred by reading a hint from a user or by reading the first few bytes of an object. Both compression and encryption can be done by specialized hardware chips in the device to improve I/O performance as well as reducing CPU utilization at the host.

Data compression and encryption can improve the space-efficiency and security as well as overall performance in NVRAM devices. In object-based NVRAMs, the device can provide either system-wide encryption or per-object basis encryption. The device can determine which object to encrypt based on its content, or users can specify that an object should be encrypted by setting a flag as a hint when sending a request. Thus, the NVRAM device could set different security levels for different types of objects and do encryption per-object, perhaps using different keys for different objects. Moreover, if the device does both compression and encryption, it can do it in the right order: compression followed by encryption.

*Client library for object-based NVRAMs.* A client library can allow users to customize OSD behavior by providing hints to the device. For example, users can provide an encryption key or specify the level of reliability for a specific object. Moreover, the library can provide an interface that bypasses the VFS layer to achieve a smaller memory footprint for small files by avoiding the need to have the VFS assign 4 KB pages to those small files before

sending them to the file system. Moreover, an OSD is capable of managing variable-length objects efficiently; in our prototype, we have the file system send a hint to embed inode objects in onodes to reduce index records and page I/Os.

*Object-level transaction.* Supporting transactions in block-based devices is a difficult feature to implement because the device does not have any information about file system semantics. In object-based storage devices, however, because metadata is handled inside the device and an object can send a hint from the upper layer to the device, the devices can provide transactions without requiring modifications to the host system. For example, users can start the transaction by setting a common transaction ID to objects in the same transaction. The OSD can use this transaction ID to establish a dependency hierarchy and complete the transaction when a top-level object in the hierarchy is being created or deleted. One way to implement the transaction in the device is to use copy-on-write, which writes modifications to a different place until the commit begins, as commonly used in the process subsystem. Moreover, OSDs can seamlessly support per-object transactions, guaranteeing atomic object I/Os.

In this thesis, we explored object reliability, which adds parity pages per object, the use of client library in supporting versioning and in-storage processing. The same technique described in object-level transaction is used to deliver a version ID to a Muninn device.

While providing advanced and efficient data processing in this model, the hardware manufacturing cost of an object-based device can remain as low as SSDs, because SSDs already have multiple powerful embedded processors, large memory, and multiple high-bandwidth independent I/O channels to the underlying medium to process mapping and wear-leveling. Handling object requests and the sparse namespace are only the additional overhead to the SSD. However, since the block management layer can be much more efficient than SSDs, it may not be necessary to improve the hardware configuration. Also, considering the estimated cost of IPhone 4 processor is around \$10 [35], adding more powerful processors for advanced data management would not increase the cost much.

In summary, the object-based storage model allows device manufacturers to provide NVRAM devices with various levels of functionality depending on the needs of their customers and make them fully customizable without host system changes. This model has the advantages of both FTL-based storage devices and native file systems: portability and efficiency. It also provides an abstraction of a request that can be used in various subsystems to provide intelli-

| Command        | Description                         |  |  |  |  |  |

|----------------|-------------------------------------|--|--|--|--|--|

| publish        | publish available events and        |  |  |  |  |  |

|                | built-in functions to a host        |  |  |  |  |  |

| subscribe      | selects the events to be pro-       |  |  |  |  |  |

|                | cessed or parameters in a host      |  |  |  |  |  |

|                | system                              |  |  |  |  |  |

| list           | provides a list of objects          |  |  |  |  |  |

| read_object    | read an object                      |  |  |  |  |  |

| write_object   | write an object                     |  |  |  |  |  |

| execute_object | t run an executable object in a de- |  |  |  |  |  |

|                | vice                                |  |  |  |  |  |

Table 3.1: Primitive object commands

gence to the device.

### **3.2 Primitive Object Operations**

The SCSI command set for object-based storage devices has been standardized since 2004. This T10 OSD standard supports objects, specified by 64-bit object and partition identifiers, using a fixed set of operations such as *read\_object* and *write\_object*. In addition, object-metadata can be accessed by *get\_attributes* and *set\_attributes*, and a list of objects can be retrieved by the *list* command. The newer version includes more functionality such as snapshots and collections.

However, the current standard is limited in that supporting various types of objectbased NVRAM devices such as versioning stores and active disks, are difficult without extending the interface. Thus, instead of using T10 OSD standard, we define a small set of extensible object commands that can support an arbitrary number of device functionality, and use it as the default interface of Muninn.

Table 3.1 summarizes the primitive operations we propose. The initial handshaking is performed using *publish* and *subscribe* when a user mounts the device in the system. The publish commands provides the information about the device such as available built-in func-

tions, device events, and other device parameters to a host. The host system can then use the subscribe command to register interesting events coming from the device, and device-wide parameters such as compression can be enabled by subscribing into this option. For example, a list of built-in function object ids can be built in a host, and the event handlers for disk capacity changes can be registered during the handshake.