# UCLA UCLA Electronic Theses and Dissertations

**Title** Enabling Accelerator Centric Computing

**Permalink** https://escholarship.org/uc/item/6tx9h1wf

Author Gill, Michael Anthony

Publication Date 2015

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

Enabling Accelerator Centric Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

${\rm by}$

Michael Anthony Gill

2015

© Copyright by Michael Anthony Gill 2015

#### Abstract of the Dissertation

Enabling Accelerator Centric Computing

by

Michael Anthony Gill Doctor of Philosophy in Computer Science University of California, Los Angeles, 2015 Professor Glenn D. Reinman, Chair

With power limitations imposing hard bounds on the amount of a chip that can be powered simultaneously, but advances in manufacturing technologies continuing to pay dividends in terms of feature density [1], together leading to the presence of dark silicon [2], it becomes clear that continued advances in performance will come in the form of energy efficiency and customization rather than scaling processor count and cache size. This observation is the basis for the argument that accelerators, highly customized logic blocks that perform a particular task with both high performance and energy efficiency, are going to become increasingly relevant in future processors. It is predicted that the number of these accelerators will exceed 1500 by 2022 [1].

As accelerators become more responsible for shouldering a greater portion of computation, it becomes important to elevate accelerators to be considered a first-class computational primitive, rather than an unusual device that requires extraordinary measures to interact with. Simply having a powerful compute engine in a machine is meaningless if it is impossible to efficiently communicate with it, or if software that uses an accelerator is hard to write, or if interacting with the device involves complicated performance considerations which make it difficult to predict whether any benefit would be had by using the accelerator.

The work described herein attempts to address this issue, and providing architectural extensions that allow for accelerators to become a high performance, highly efficient, and highly utilized compute elements. The effort comes from two directions: 1) introducing enabling technologies that allow accelerators to be efficiently used by software, and 2) redesigning system components to allow for accelerators to perform well and leverage existing system resources efficiently. This results in accelerator-centric designs, where conventional processing cores act more as choreographers for a communicating network of accelerators as opposed to cores acting as the primary mechanism of performing computation. The intent is to accomplish this in such a way as to place undue burden on application programmers, by introducing accelerators in such a way as to be compilerfriendly. The dissertation of Michael Anthony Gill is approved.

Alex Bui

Todd Millstein

Jason Cong

Glenn D. Reinman, Committee Chair

University of California, Los Angeles2015

## TABLE OF CONTENTS

| 1        | Intr | oducti  | ion                                                   | 1          |

|----------|------|---------|-------------------------------------------------------|------------|

| <b>2</b> | Arc  | hitectu | ure Support for Accelerator-Rich CMPs                 | 6          |

|          | 2.1  | Micros  | architecture of ARC                                   | 6          |

|          |      | 2.1.1   | Instruction Set Extension                             | 7          |

|          |      | 2.1.2   | Light-Weight Interrupt Support                        | 9          |

|          |      | 2.1.3   | Programming Interface to ARC                          | 12         |

|          |      | 2.1.4   | Invoking Accelerators                                 | 12         |

|          |      | 2.1.5   | Sharing Accelerators                                  | 13         |

|          |      | 2.1.6   | Accelerator Composition                               | 15         |

|          | 2.2  | Evalua  | ation Methodology                                     | 17         |

|          |      | 2.2.1   | Benchmarks                                            | 17         |

|          |      | 2.2.2   | Simulation Tool-Chain                                 | 18         |

|          |      | 2.2.3   | Simulation Platform                                   | 20         |

|          |      | 2.2.4   | Area/Timing/Power Measurements                        | 21         |

|          | 2.3  | Exper   | imental Results                                       | 22         |

|          |      | 2.3.1   | Speedup and energy improvements                       | 24         |

|          |      | 2.3.2   | Accelerator Sharing Results                           | 26         |

|          |      | 2.3.3   | Accelerator Virtualization Results                    | 26         |

|          |      | 2.3.4   | Benefits of Light-Weight Interrupt                    | 26         |

|          |      | 2.3.5   | Benefits of Hardware-Based GAM                        | 27         |

| 0        | 017  |         |                                                       |            |

| 3        |      |         | A Composable Heterogeneous Accelerator-Rich Micropro- | 28         |

|          | 0001 |         |                                                       | <b>_</b> 0 |

|   | 3.1  | Microa  | architecture of CHARM                | 29             |

|---|------|---------|--------------------------------------|----------------|

|   |      | 3.1.1   | CHARM Software Infrastructure        | 29             |

|   |      | 3.1.2   | Hardware Infrastructure              | 31             |

|   | 3.2  | Evalua  | ation Methodology                    | 36             |

|   | 3.3  | Experi  | imental Results                      | 38             |

|   |      | 3.3.1   | Improvement over LCA-based systems   | 40             |

|   |      | 3.3.2   | Effect of adding accelerators        | 41             |

|   |      | 3.3.3   | Effect of changing task-grain        | 43             |

|   |      | 3.3.4   | Platform flexibility                 | 45             |

| 4 | Droc | rnogg o | on Developing                        |                |

|   |      |         | 1 0                                  | 46             |

|   |      |         |                                      | <del>1</del> 0 |

|   | 4.1  | 0       | ess on Developing                    |                |

|   |      | Accele  | erator-Rich Architectures            | 46             |

|   | 4.2  | Ongoin  | ng Research on Composable            |                |

|   |      | Accele  | erator-Rich Platforms                | 49             |

|   |      | 4.2.1   | Anatomy of an ABB Island             | 49             |

|   |      | 4.2.2   | Design Space Exploration Parameters  | 50             |

|   | 4.3  | Simula  | ation and modeling details           | 51             |

|   | 4.4  | Result  | S                                    | 52             |

|   |      | 4.4.1   | SPM Sharing                          | 52             |

|   |      | 4.4.2   | Chaining-Optimized Crossbar Topology | 54             |

|   |      | 4.4.3   | Ring Network Width & Ring Count      | 55             |

|   |      | 4.4.4   | SPM Porting                          | 56             |

|   |      | 4.4.5   | Performance                          | 57             |

|   |      | 4.4.6   | Energy & Energy Per Computation      | 58             |

|   |      |         |                                      |                |

|          |          | 4.4.7   | Area & Compute Density                                                 | 58  |

|----------|----------|---------|------------------------------------------------------------------------|-----|

|          |          | 4.4.8   | Comparison to Chip Multi-Processor (CMP) $\ldots \ldots \ldots \ldots$ | 59  |

| <b>5</b> | Con      | nposab  | le Accelerator-rich Microprocessor                                     |     |

| Eı       | nhano    | ced for | Adaptability and Longevity                                             | 60  |

|          | 5.1      | Microa  | architecture of CAMEL                                                  | 61  |

|          |          | 5.1.1   | ABB Islands                                                            | 62  |

|          |          | 5.1.2   | Programmable Fabric                                                    | 63  |

|          |          | 5.1.3   | Runtime PF Allocation                                                  | 64  |

|          |          | 5.1.4   | Compiler Support                                                       | 65  |

|          | 5.2      | Evalua  | tion Methodology                                                       | 66  |

|          |          | 5.2.1   | Tool Chain                                                             | 66  |

|          |          | 5.2.2   | Domains                                                                | 66  |

|          |          | 5.2.3   | ABB Characterization                                                   | 68  |

|          |          | 5.2.4   | Case Studies                                                           | 69  |

|          | 5.3      | Experi  | mental Results                                                         | 70  |

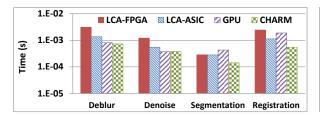

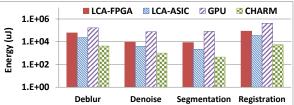

|          |          | 5.3.1   | Comparison Between Acceleration Schemes                                | 71  |

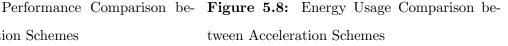

|          |          | 5.3.2   | Effect on Domain-Span                                                  | 71  |

|          |          | 5.3.3   | Effect on Domain Longevity                                             | 73  |

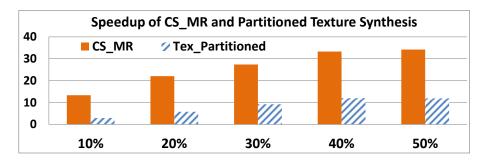

|          |          | 5.3.4   | Graph Partitioning for Lower-Capacity Hardware                         | 73  |

| 6        | AIN      | ling to | • Topple the Memory Wall                                               | 76  |

|          | 6.1      | 0       | ration Platform                                                        | 79  |

|          | <b>.</b> | 6.1.1   | Accelerator Integrated DIMM Architecture                               | 79  |

|          |          | 6.1.2   | Accelerator Use                                                        | 83  |

|          |          | 6.1.3   | Memory Layout                                                          | 84  |

|          |          | 0.1.0   | momory hayout                                                          | ) I |

|   | 6.2 | Standa | ards Compliance                                                                                                                 |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------------|

|   |     | 6.2.1  | Timing                                                                                                                          |

|   |     | 6.2.2  | Communication with CPU                                                                                                          |

|   |     | 6.2.3  | Routing of Configuration Messages                                                                                               |

|   |     | 6.2.4  | Consideration of Alternative Protocols                                                                                          |

|   | 6.3 | Evalua | ation Methodology                                                                                                               |

|   |     | 6.3.1  | Evaluated Systems                                                                                                               |

|   |     | 6.3.2  | Benchmarks                                                                                                                      |

|   |     | 6.3.3  | System Modeling                                                                                                                 |

|   | 6.4 | Result | 92 s                                                                                                                            |

|   |     | 6.4.1  | Performance                                                                                                                     |

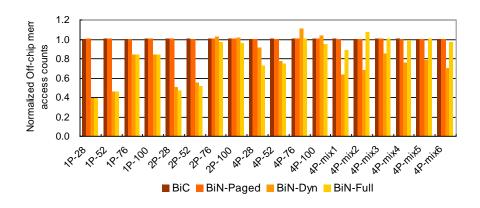

|   |     | 6.4.2  | Memory Activity                                                                                                                 |

|   |     | 6.4.3  | Memory Network Utilization                                                                                                      |

| 7 | BiN | : Buff | er-in-NUCA for Accelerator-Rich CMPs                                                                                            |

|   | 7.1 | BiN A  | $rchitecture \dots \dots$ |

|   |     | 7.1.1  | Overall Infrastructure                                                                                                          |

|   |     | 7.1.2  | Dynamic Interval-based Global (DIG) Buffer Allocation 103                                                                       |

|   |     | 7.1.3  | Flexible Paged Buffer Allocation                                                                                                |

|   |     | 7.1.4  | Buffer Allocation in NUCA 107                                                                                                   |

|   |     | 7.1.5  | Hardware Overhead                                                                                                               |

|   | 7.2 | Comp   | iler-Based BB-Curve Analysis                                                                                                    |

|   |     | 7.2.1  | Analysis Flow Overview                                                                                                          |

|   |     | 7.2.2  | Data Reuse Modeling                                                                                                             |

|   | 7.3 | Evalua | ation Methodology                                                                                                               |

|   |      | 7.3.1  | Simulation Infrastructure                                                                        | 112 |

|---|------|--------|--------------------------------------------------------------------------------------------------|-----|

|   |      | 7.3.2  | Benchmarks and Accelerators                                                                      | 112 |

|   |      | 7.3.3  | Reference Designs                                                                                | 113 |

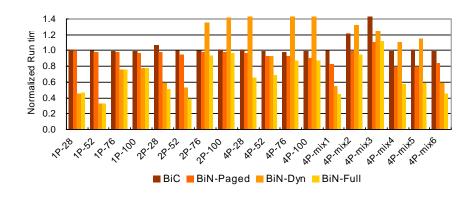

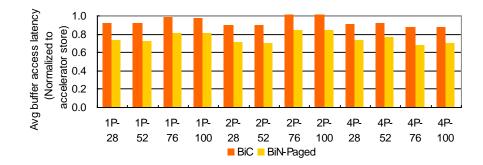

|   | 7.4  | Result | S                                                                                                | 114 |

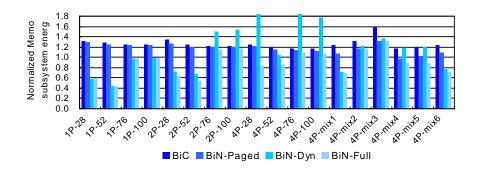

|   |      | 7.4.1  | Impact of DIG Buffer Allocation                                                                  | 115 |

|   |      | 7.4.2  | Impact of Paged Buffer Allocation                                                                | 116 |

|   |      | 7.4.3  | Impact on Energy                                                                                 | 116 |

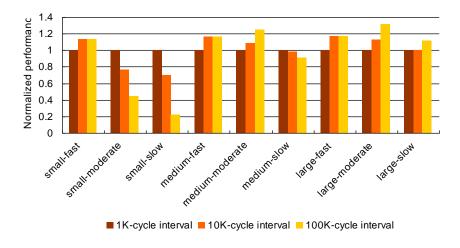

|   |      | 7.4.4  | Impact of DIG Allocation Interval Length                                                         | 117 |

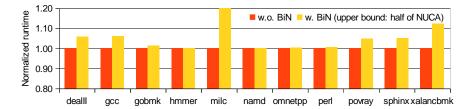

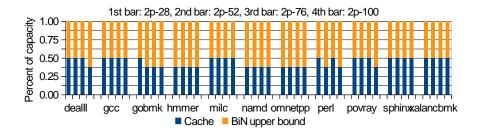

|   |      | 7.4.5  | Impact on Cache                                                                                  | 119 |

| 8 | Stre | am Ar  | bitration: Towards Efficient Bandwidth Utilization for Emerg                                     | _   |

|   |      |        | Interconnects                                                                                    |     |

|   | 8.1  | Introd | uction $\ldots$ | 129 |

|   | 8.2  | Stream | Arbitration: Scheme and Example                                                                  | 133 |

|   |      | 8.2.1  | Stream Arbitration Scheme                                                                        | 133 |

|   |      | 8.2.2  | Example of Stream Arbitration                                                                    | 137 |

|   | 8.3  | Stream | Arbitration in RF-I                                                                              | 138 |

|   |      | 8.3.1  | RF-Interconnect                                                                                  | 138 |

|   |      | 8.3.2  | Curled Transmission Line for Stream Circulation                                                  | 140 |

|   |      | 8.3.3  | Time Division Modulation Multicast for Stream Augmentation                                       | 142 |

|   |      | 8.3.4  | Power and Area                                                                                   | 143 |

|   | 8.4  | Evalua | tion Methodology                                                                                 | 145 |

|   |      | 8.4.1  | Simulation Infrastructure                                                                        | 145 |

|   |      | 8.4.2  | Benchmarks                                                                                       | 147 |

|   |      | 8.4.3  | Reference Scheme                                                                                 | 148 |

|    | 8.5    | Results and Discussions                   |

|----|--------|-------------------------------------------|

|    |        | 8.5.1 Performance as Bandwidth Scales     |

|    |        | 8.5.2 Energy Consumption                  |

|    |        | 8.5.3 Bandwidth Allocation for Channels   |

|    |        | 8.5.4 Data Channel Utilization            |

|    | 8.6    | Scalability                               |

|    |        | 8.6.1 Hierarchical Stream Arbitration     |

|    |        | 8.6.2 Trace-Driven Evaulation Methodology |

|    |        | 8.6.3 Results                             |

| 9  | Cor    | e Design After Acceleration               |

|    | 9.1    | Platform Model                            |

|    |        | 9.1.1 Accelerator Architecture            |

|    |        | 9.1.2 Compilation                         |

|    | 9.2    | Methodology                               |

|    |        | 9.2.1 Benchmark                           |

|    | 9.3    | Results                                   |

|    | 9.4    | Accelerator Resource Utilization          |

|    | 9.5    | Core Utilization                          |

|    |        | 9.5.1 Memory System Utilization           |

| 10 | ) Rela | ted Work                                  |

|    | 10.1   | On-Chip Accelerators                      |

|    | 10.2   | Off-Chip Near-Memory Accelerators         |

|    | 10.3   | Emerging Network Technology               |

| 11 | onclusion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $18$ | 36 |

|----|----------------------------------------------------------------------|----|

|    | .1 Future work                                                       | 87 |

## LIST OF FIGURES

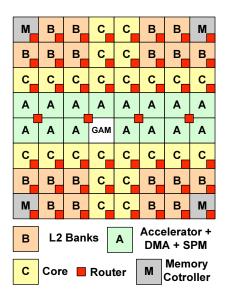

| 2.1  | Overall architecture of ARC                                                          | 7  |

|------|--------------------------------------------------------------------------------------|----|

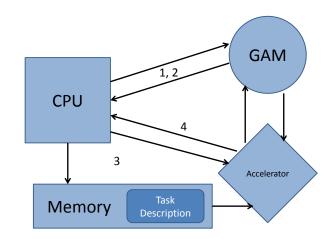

| 2.2  | Communication between core, GAM, and accelerator                                     | 7  |

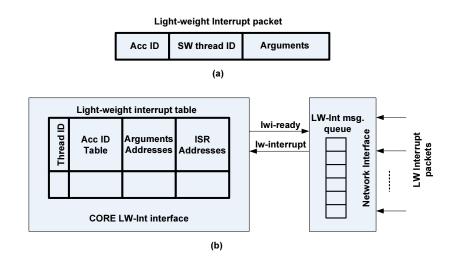

| 2.3  | Light-weight interrupt support                                                       | 8  |

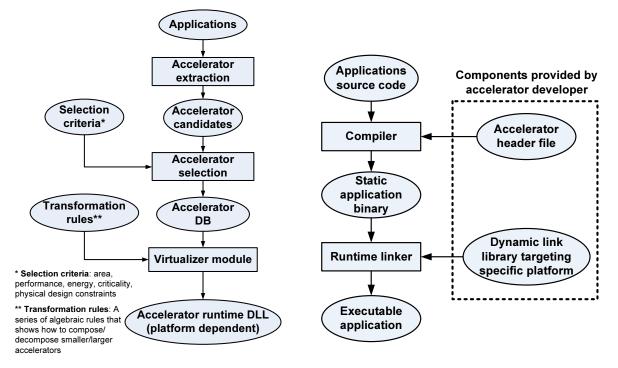

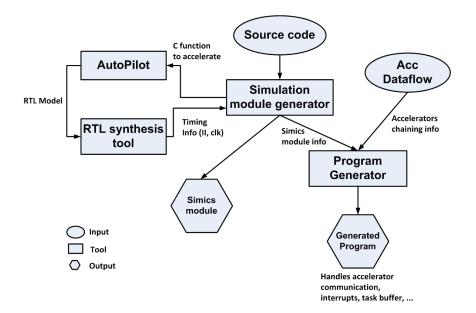

| 2.4  | Accelerator extraction methodology                                                   | 11 |

| 2.5  | ARC development flow                                                                 | 11 |

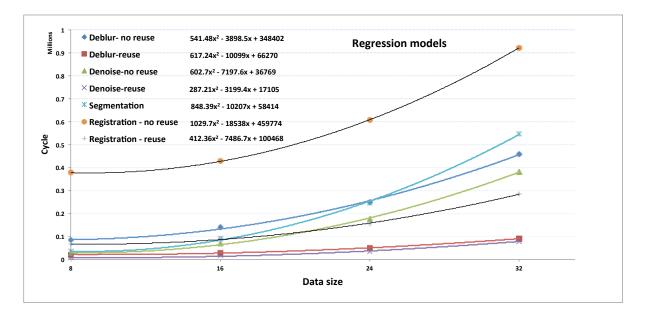

| 2.6  | Regression models for medical imaging benchmarks                                     | 14 |

| 2.7  | An example of accelerator composition                                                | 16 |

| 2.8  | Accelerator composition steps                                                        | 17 |

| 2.9  | Process used to generate simulation structures and accelerated programs              | 20 |

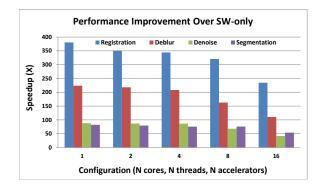

| 2.10 | MI – Speedup over SW-only                                                            | 22 |

| 2.11 | MI – Speedup over OS+Acc                                                             | 22 |

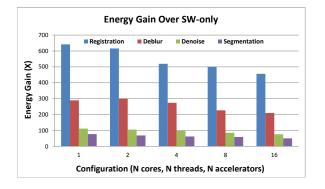

| 2.12 | MI – Energy gain over SW-only                                                        | 22 |

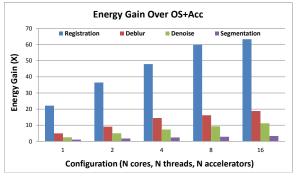

| 2.13 | MI – Energy gain over OS+Acc                                                         | 22 |

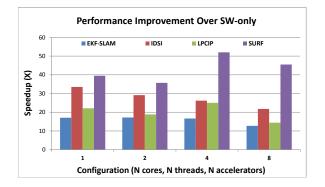

| 2.14 | VN – Speedup over SW-only                                                            | 23 |

| 2.15 | VN – Speedup over OS+Acc                                                             | 23 |

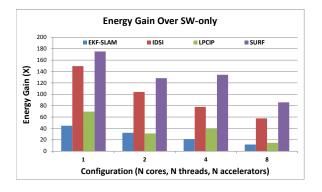

| 2.16 | VN – Energy gain over SW-only                                                        | 23 |

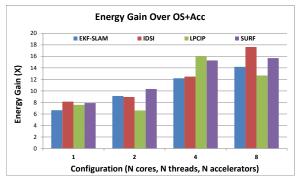

| 2.17 | VN – Energy gain over OS+Acc                                                         | 23 |

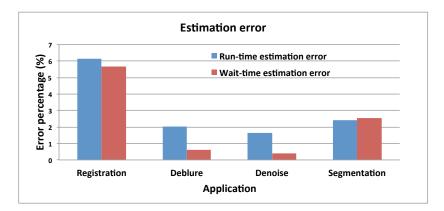

| 2.18 | Core and GAM estimation error                                                        | 24 |

| 2.19 | FFT virtualization (2D and 3D) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 24 |

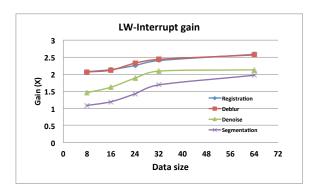

| 2.20 | Benefit of using lw-int                                                              | 24 |

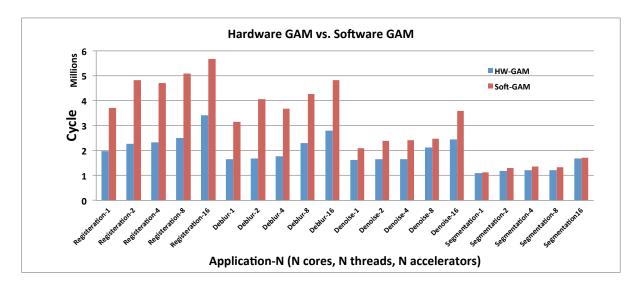

| 2.21 | Benefit of using hardware GAM over SW-GAM                                            | 25 |

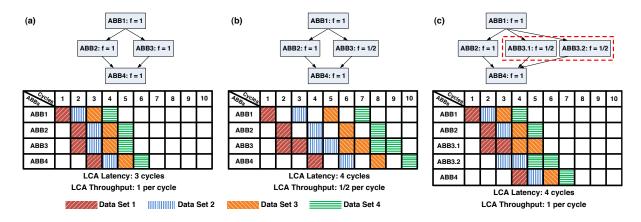

| 3.1  | Composition                                                                          | 30 |

| 3.2  | Microarchitecture of CHARM                                                           | 30 |

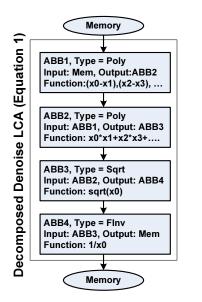

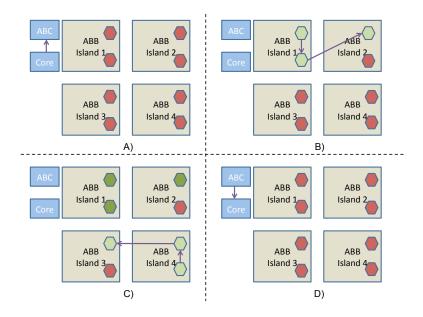

| 3.3  | LCA composition example: A) A core sends a request for an LCA to the                                            |    |

|------|-----------------------------------------------------------------------------------------------------------------|----|

|      | ABC; B) An LCA instance is allocated; C) An LCA instance is allocated                                           |    |

|      | with consideration for balancing DMA utilization; D) The ABC signals                                            |    |

|      | completion to the core                                                                                          | 34 |

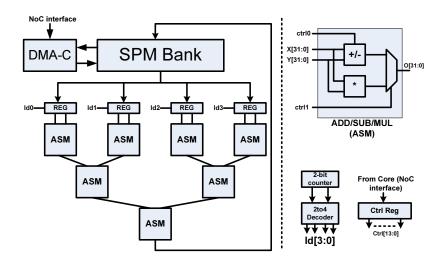

| 3.4  | Poly ABB Details                                                                                                | 37 |

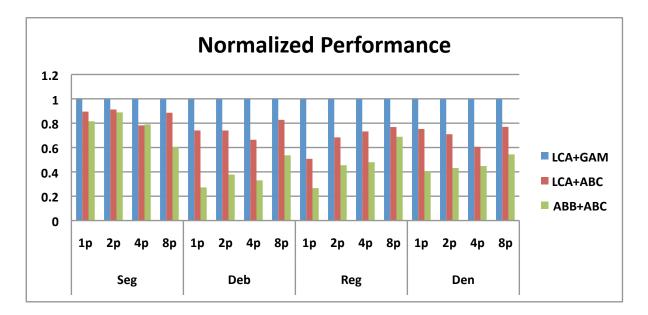

| 3.5  | Performance improvement                                                                                         | 39 |

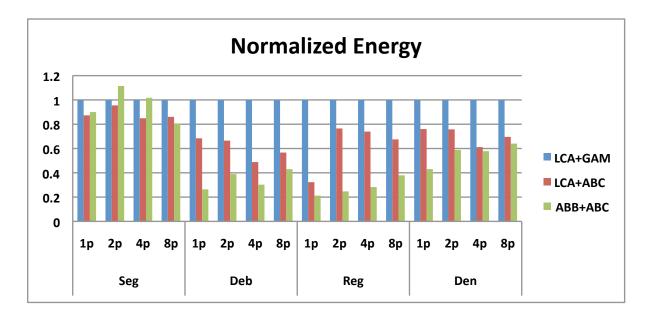

| 3.6  | Energy improvement                                                                                              | 40 |

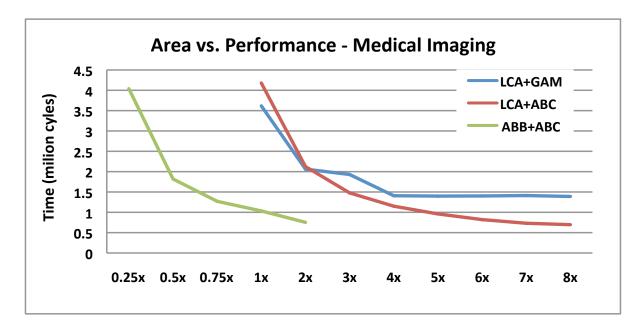

| 3.7  | Effect of increasing accelerators                                                                               | 41 |

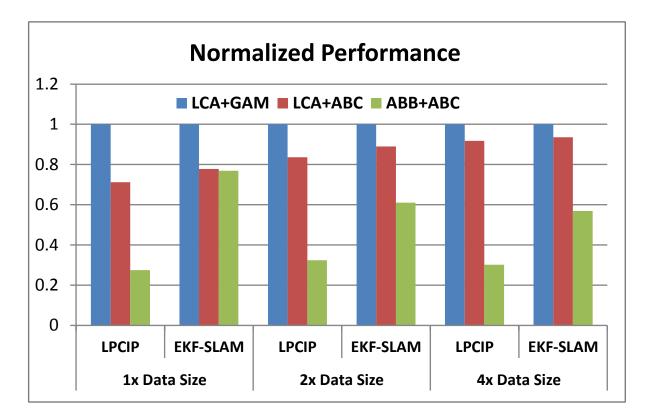

| 3.8  | Performance improvement for computer vision and navigation                                                      | 42 |

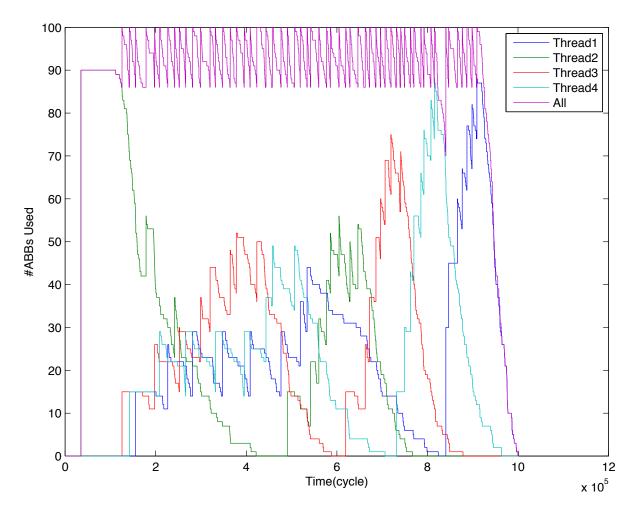

| 3.9  | Utilization of ABBs given a task-grain of 8                                                                     | 43 |

| 3.10 | Utilization of ABBs given a task-grain of 128                                                                   | 44 |

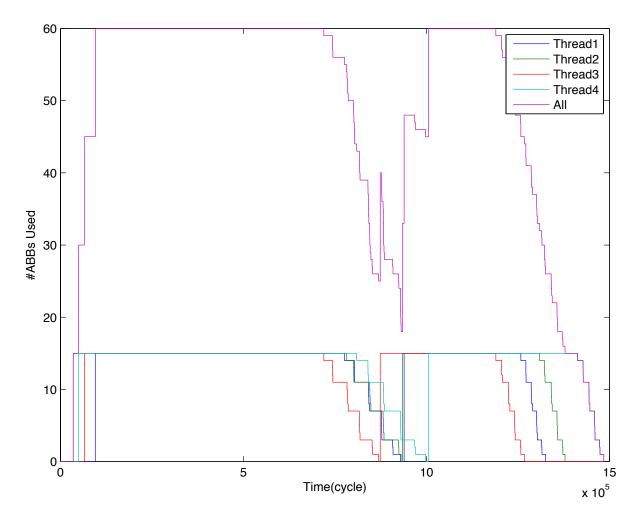

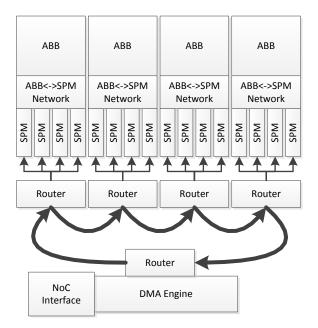

| 4.1  | Overview (not to scale) of accelerator-rich architectures: (A) ARC; (B)                                         |    |

|      | CHARM; (C) CAMEL                                                                                                | 47 |

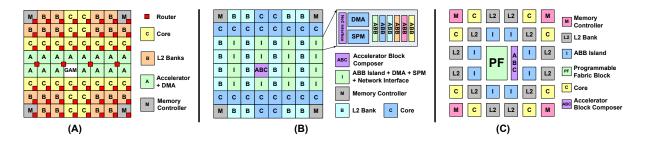

| 4.2  | Island design using ring for SPM $\leftrightarrow$ DMA network $\ldots \ldots \ldots \ldots \ldots$             | 51 |

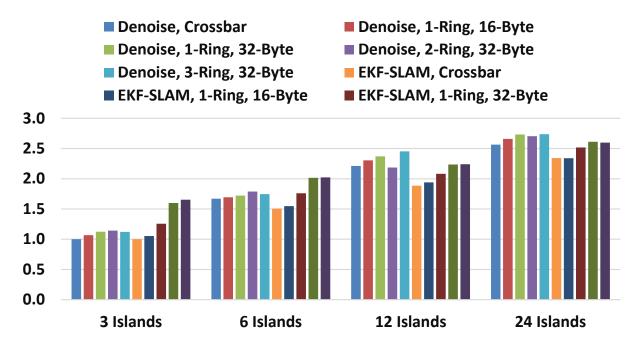

| 4.3  | Performance impact of utilizing different SPM $\leftrightarrow \rm DMA$ networks while ad-                      |    |

|      | justing number and size of ABB islands; normalized to baseline for 3 islands                                    | 53 |

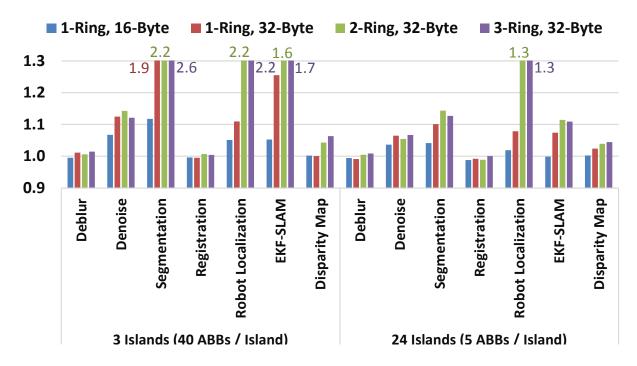

| 4.4  | Performance of various SPM $\leftrightarrow$ DMA ring networks; shown for 3 islands (40                         |    |

|      | ABBs / island) and 24 islands (5 ABBs / island); normalized to baseline                                         |    |

|      | for respective number of islands $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 54 |

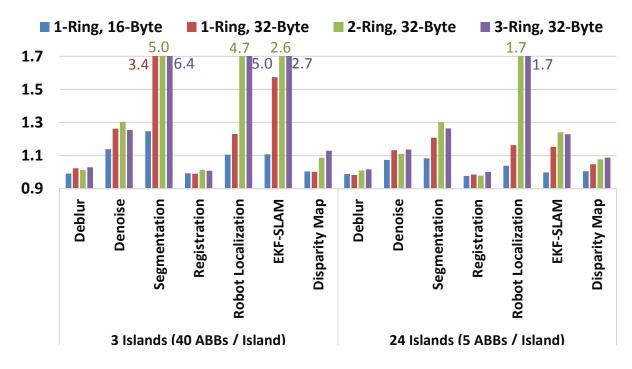

| 4.5  | Performance per unit energy of selected designs; normalized to baseline                                         |    |

|      | for respective number of islands $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 55 |

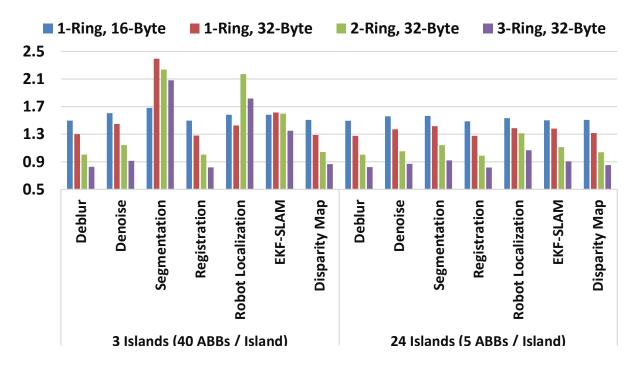

| 4.6  | Performance per unit area of selected designs; normalized to baseline for                                       |    |

|      | respective number of islands                                                                                    | 56 |

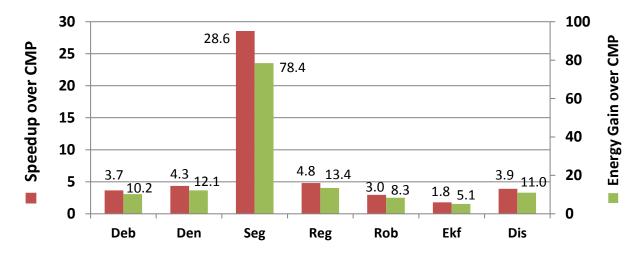

| 4.7  | Performance and energy gains of "best" accelerator-rich design configura-                                       |    |

|      | tion over chip multi-processor (CMP) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                         | 59 |

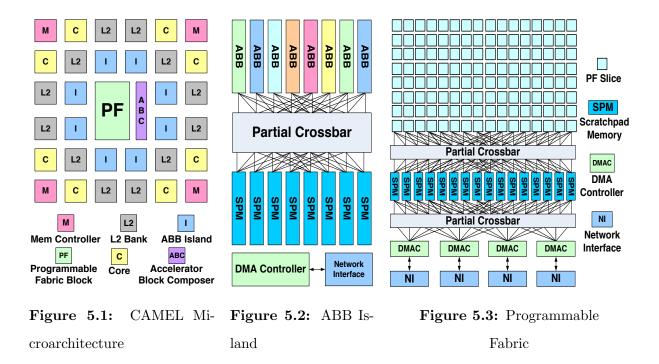

| 5.1  | CAMEL Microarchitecture                                                                                         | 62 |

| 5.2        | ABB Island                                                                                                                                                                                                                        | 62       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.3        | Programmable Fabric                                                                                                                                                                                                               | 62       |

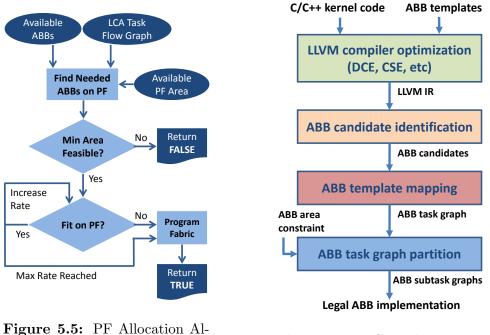

| 5.4        | Motivational Example of Applying Rate-Matching on PF                                                                                                                                                                              | 63       |

| 5.5        | PF Allocation Algorithm                                                                                                                                                                                                           | 65       |

| 5.6        | Compiler Framework                                                                                                                                                                                                                | 65       |

| 5.7        | Performance Comparison between Acceleration Schemes                                                                                                                                                                               | 71       |

| 5.8        | Energy Usage Comparison between Acceleration Schemes                                                                                                                                                                              | 71       |

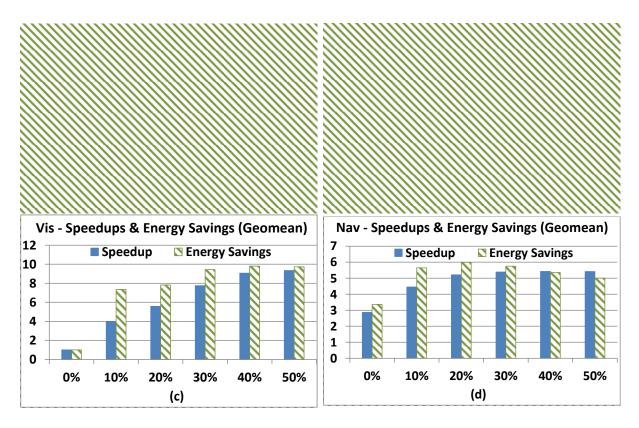

| 5.9        | Geometric Mean of All Speedups and Energy Savings                                                                                                                                                                                 | 73       |

| 5.10       | Geometric Mean of Speedup and Energy Savings for Each Domain                                                                                                                                                                      | 74       |

| 5.11       | Domain Longevity and Graph Partitioning                                                                                                                                                                                           | 75       |

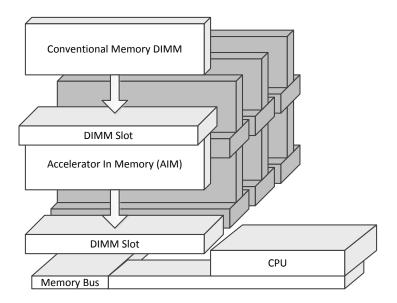

| 6.1        | How a set of AIMs physically connect to an existing system                                                                                                                                                                        | 80       |

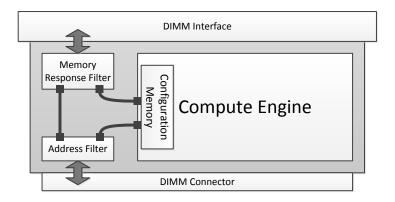

| 6.2        | The internals of a sample AIM                                                                                                                                                                                                     | 81       |

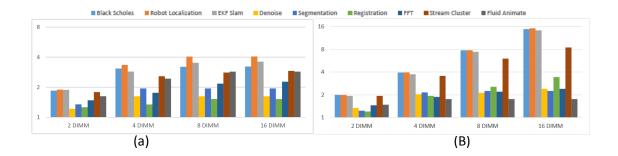

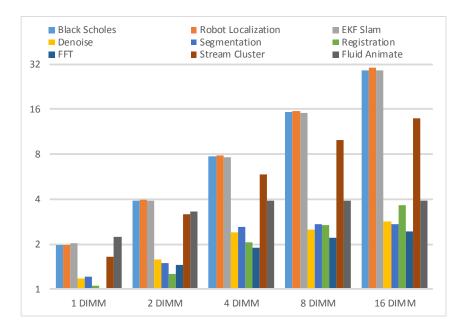

| 6.3        | Shows the performance scalability of systems with and without AIMs as                                                                                                                                                             |          |

|            | the number of DIMMs in the system is increased. (a) shows a system with                                                                                                                                                           |          |

|            | AIMs normalized to the performance of a system with AIMs and only 1                                                                                                                                                               |          |

|            | memory DIMM, (b) shows the baseline system without AIMs normalized                                                                                                                                                                |          |

|            |                                                                                                                                                                                                                                   |          |

|            | to the performance of a system without AIMs and only 1 memory DIMM.                                                                                                                                                               | 93       |

| 6.4        | to the performance of a system without AIMs and only 1 memory DIMM.<br>Shows performance of a system featuring AIMs compared normalized to                                                                                        | 93       |

| 6.4        |                                                                                                                                                                                                                                   | 93<br>94 |

| 6.4<br>6.5 | Shows performance of a system featuring AIMs compared normalized to                                                                                                                                                               |          |

|            | Shows performance of a system featuring AIMs compared normalized to<br>the performance of the baseline system with 1 memory DIMM                                                                                                  |          |

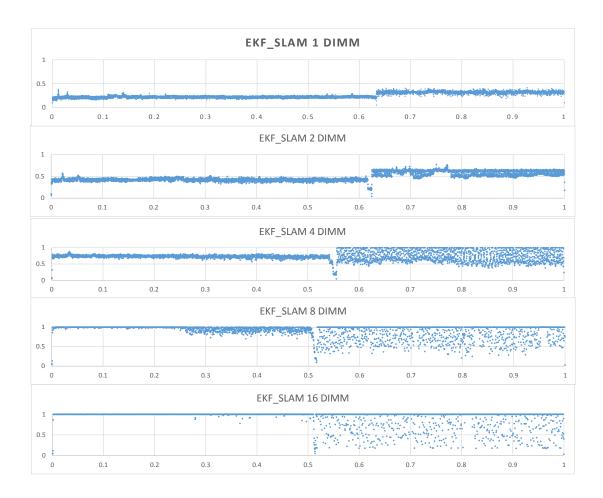

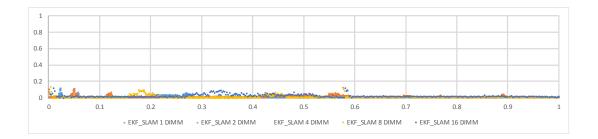

|            | Shows performance of a system featuring AIMs compared normalized to<br>the performance of the baseline system with 1 memory DIMM<br>Shows the bandwidth consumption on the memory network for the baseline                        | 94       |

| 6.5        | Shows performance of a system featuring AIMs compared normalized to<br>the performance of the baseline system with 1 memory DIMM<br>Shows the bandwidth consumption on the memory network for the baseline<br>system for EKF_SLAM | 94       |

| 6.5        | Shows performance of a system featuring AIMs compared normalized to<br>the performance of the baseline system with 1 memory DIMM<br>Shows the bandwidth consumption on the memory network for the baseline<br>system for EKF_SLAM | 94<br>99 |

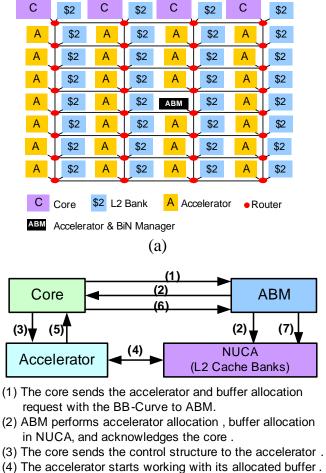

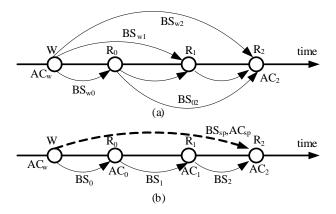

| 7.3  | (a) Overall architecture of AXR-CMP with BiN. (b) Communications be-                    |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | tween core, ABM, accelerator, and NUCA                                                  | 121 |

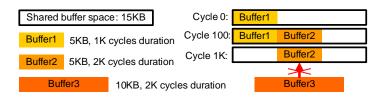

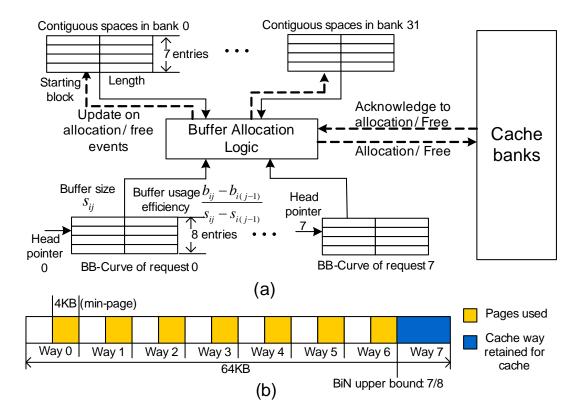

| 7.4  | An example of the DIG buffer allocation scheme                                          | 122 |

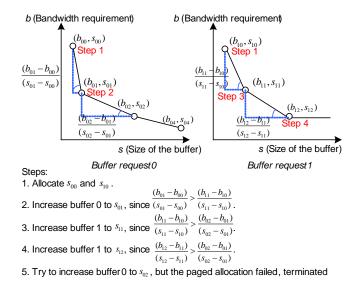

| 7.5  | An example of the flexible paged buffer allocation $\ldots \ldots \ldots \ldots \ldots$ | 122 |

| 7.6  | (a) The buffer allocation module in ABM. (b) Worst-case buffer fragmen-                 |     |

|      | tation in a cache bank                                                                  | 123 |

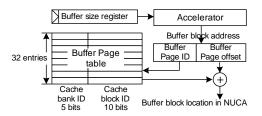

| 7.7  | Block addresses generation with the page table                                          | 123 |

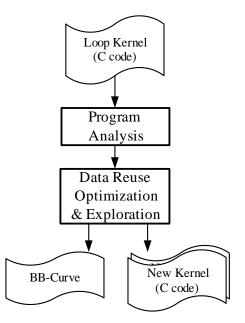

| 7.8  | Data reuse analysis for BB-Curve                                                        | 124 |

| 7.9  | (a) Full data reuse graph. (b) Simplified data reuse graph                              | 124 |

| 7.10 | (a) Full data reuse graph. (b) Simplified data reuse graph                              | 125 |

| 7.11 | Comparison results of runtime                                                           | 125 |

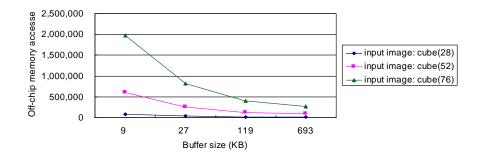

| 7.12 | Comparison results of off-chip memory accesses                                          | 125 |

| 7.13 | Comparison results of buffer access latency                                             | 126 |

| 7.14 | Energy comparison of the memory subsystem                                               | 126 |

| 7.15 | Impact of DIG allocation interval length                                                | 126 |

| 7.16 | Impact of BiN with a fixed upper bound (half of the NUCA size) on the                   |     |

|      | runtime of SPEC benchmarks                                                              | 127 |

| 7.17 | Partitions via dynamic upper bound tuning                                               | 127 |

| 7.18 | Runtime of dynamic partitioning compared to a fixed upper bound (half                   |     |

|      | of NUCA)                                                                                | 127 |

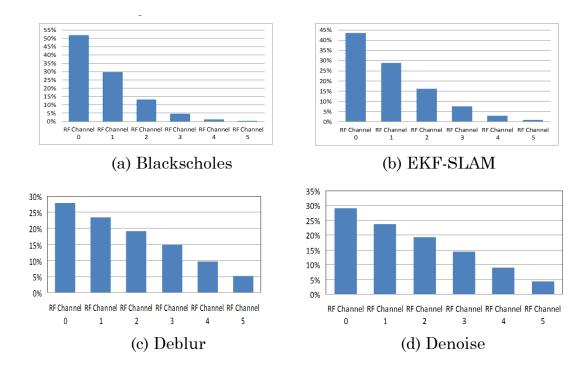

| 8.1  | Percent of received flits per node in a Token-based RF-I NoC                            | 131 |

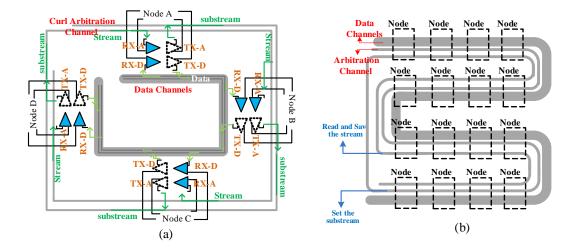

| 8.2  | The substream augmented by each node as the stream passed by                            | 135 |

| 8.3  | An example of the stream arbitration scheme                                             | 137 |

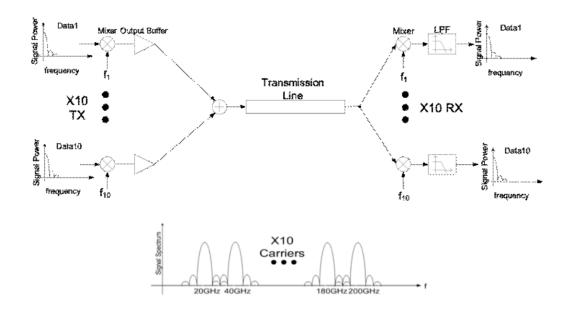

| 8.4  | A ten carrier RF-Interconnect and corresponding waveform at the trans-                  |     |

|      | mission line                                                                            | 139 |

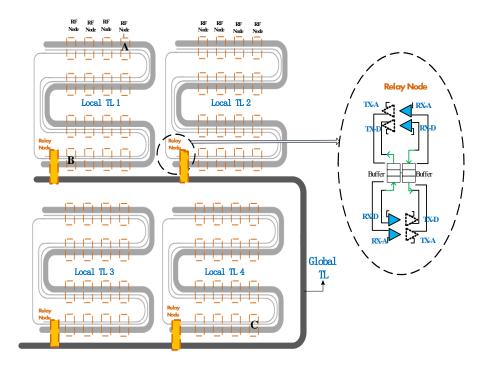

| 8.5  | Multi-cast RF-Interconnect system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 140 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.6  | The curl transmission line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140 |

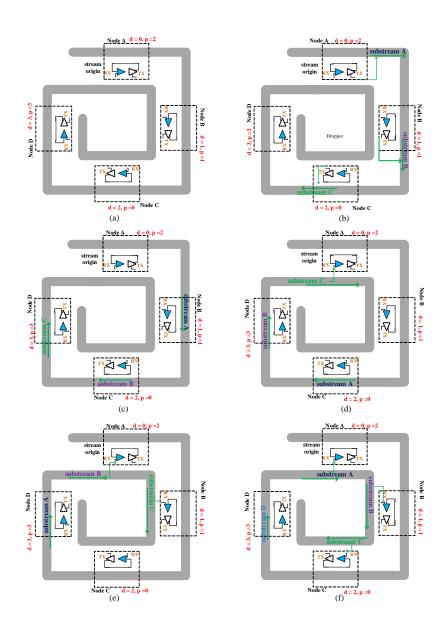

| 8.7  | An example of TDM multicast for stream augmentation with priority ro-<br>tation: (a) t=0 and t= $\lambda$ : no substream is modulated. (b) t= $2\lambda$ : node C,<br>B, A modulate their substreams simultaneously. (c) t= $3\lambda$ : substream C,<br>B, A achieves node D, C, B, respectively. (d) t= $4\lambda$ : substream C, B, A<br>achieves node A (inner), D, C, respectively. Substream C is received by<br>node A. (e) t= $5\lambda$ : substream C, B, A achieves node B (inner), A (inner),<br>D, respectively. Substream C and B is received by node B and A, respec-<br>tively. (f) t= $6\lambda$ : node D modulates its substream. Substream C, B, A |     |

|      | achieves node C (inner), B (inner), A (inner), respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 159 |

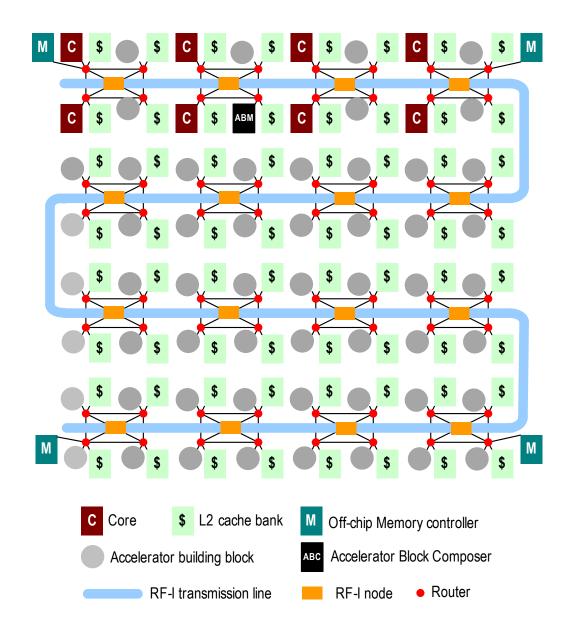

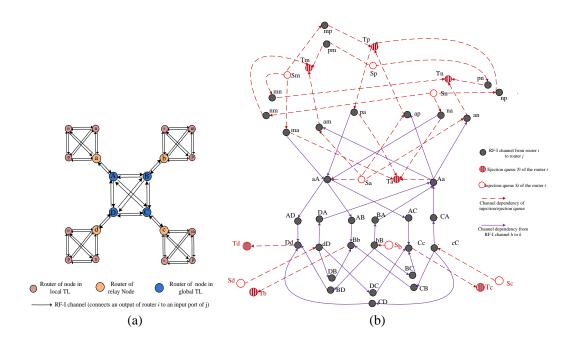

| 8.8  | Overall diagram of the evaluated CHARM architecture with RFI overlaid         NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 160 |

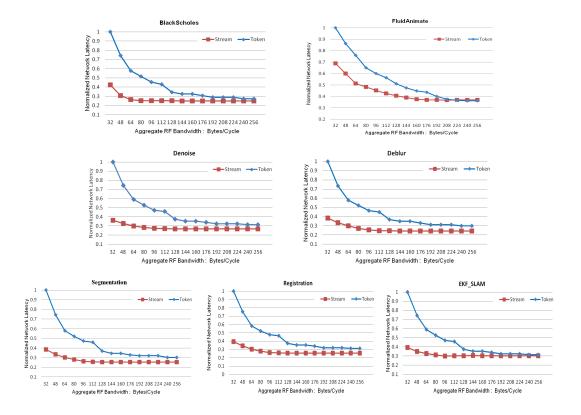

| 8.9  | Comparison results of average network flit latency at various aggregate<br>bandwidths (normalized to token arbitration with 32 Byte/Cycle aggre-<br>gate bandwidth)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 161 |

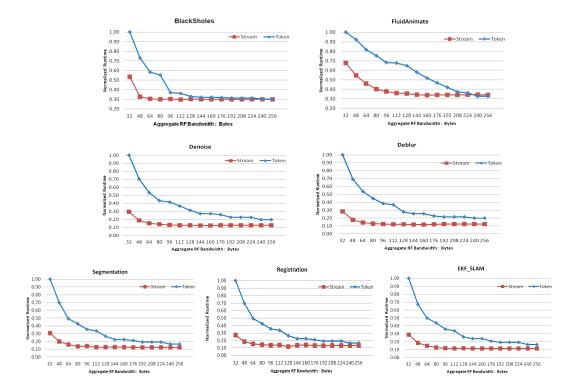

| 8.10 | Comparison results of application runtime at various aggregate band-<br>widths (normalized to token arbitration with 32 Byte/Cycle aggregate<br>bandwidth)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 162 |

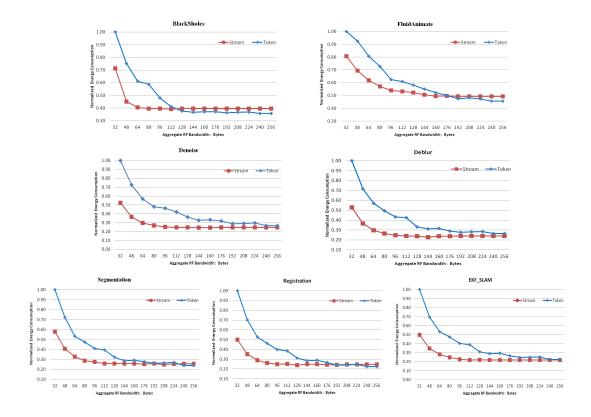

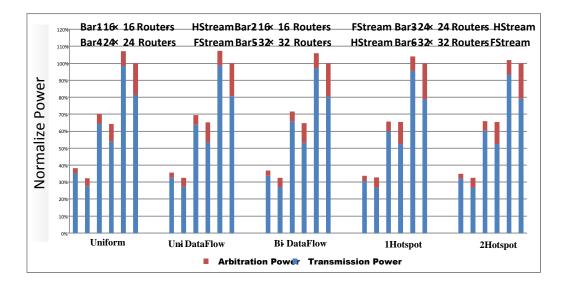

| 8.11 | Comparison results of application Network power consumption at various aggregate bandwidths (normalized to token arbitration with 32 Byte/Cycle aggregate bandwidth)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 163 |

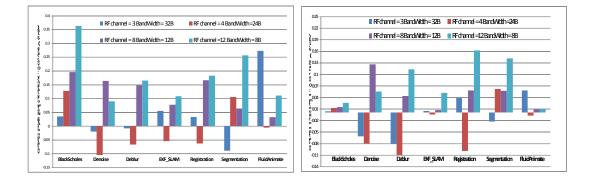

| 8.12 | <ul> <li>Impact of channel bandwidth allocation: (a) Average network flit latency.</li> <li>(b) Application runtime (The results is the variation over the case of RF channel =6, Bandwidth = 16 Byte/Cycle)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              | 163 |

| 8.13 | RFI data channel utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 164 |

| 8.14 | Hierarchical stream arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 164 |

| 8.15 | Hierarchical NoC topology characterization graph of (a) TG, (b) CDG $$ .    | 165 |

|------|-----------------------------------------------------------------------------|-----|

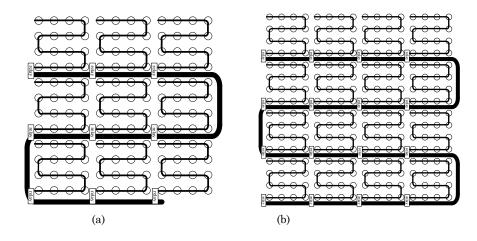

| 8.16 | Hierarchical architecture of (a) 12x12 RF nodes for a 24x24 routers NoC;    |     |

|      | (b) 16x16 RF nodes for a 32x32 router NoC. Each 2x2 routers share 1 RF      |     |

|      | node                                                                        | 165 |

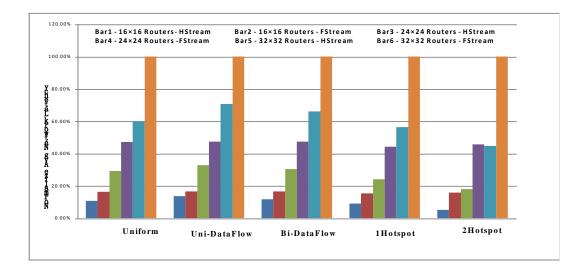

| 8.17 | Performance (average network flit latency) gain through hierarchical stream |     |

|      | arbitration (normalized to Flat Stream of $32^*32$ topology for each appli- |     |

|      | cation)                                                                     | 166 |

| 8.18 | Power savings through hierarchical stream arbitration (normalized to Flat   |     |

|      | Stream of $32^*32$ topology for each application)                           | 166 |

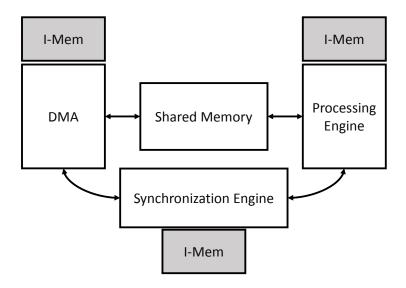

| 9.1  | Architectural overview of the programmable accelerator model                | 169 |

| 9.2  | Internal design of the Synchronization Engine (SE)                          | 170 |

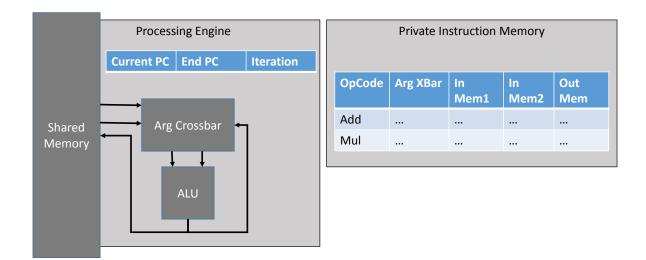

| 9.3  | Internal design of the Processing Engine (SE)                               | 171 |

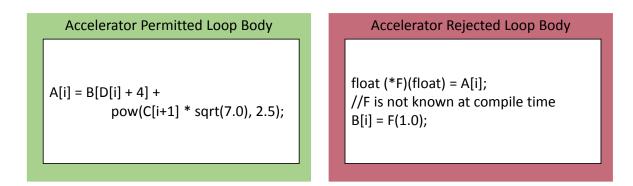

| 9.4  | Examples for admissible and inadmissible loop bodies.                       | 173 |

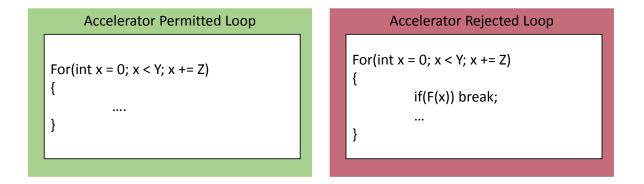

| 9.5  | Examples for admissible and inadmissible loops, not including loop bodies.  | 173 |

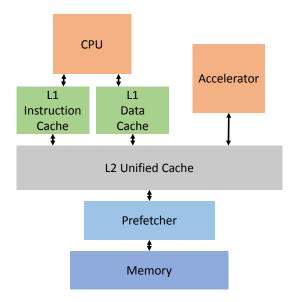

| 9.6  | System architecture of evaluated system                                     | 175 |

## LIST OF TABLES

| 2.1 | Instructions used to interact with accelerators                                              | 9   |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | Instructions to handle light-weight interrupts.                                              | 9   |

| 2.3 | OS overhead to access accelerators(cycles)                                                   | 9   |

| 2.4 | Accelerated medical imaging algorithms                                                       | 18  |

| 2.5 | Accelerated computer vision and navigation algorithms                                        | 19  |

| 2.6 | Simics+GEMS configuration                                                                    | 21  |

| 2.7 | Synthesis results                                                                            | 21  |

| 3.1 | Simulation parameters                                                                        | 36  |

| 3.2 | Area/Power results – CHARM                                                                   | 37  |

| 3.3 | Area/Power results – LCAs                                                                    | 38  |

| 3.4 | Area $(mm^2)$ for various chip components $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 38  |

| 5.1 | Simulation Parameters                                                                        | 67  |

| 5.2 | Tools for Timing and Power Models                                                            | 67  |

| 5.3 | ABB Types, PF Synthesis, Domain Numbers, and Func                                            | 69  |

| 5.4 | Power and Area for CAMEL Base Platform                                                       | 69  |

| 5.5 | Number of ABBs and PF Slices in CAMEL-x% $\hfill \ldots \ldots \ldots \ldots$                | 69  |

| 6.1 | Characteristics of the evaluated system(s) $\ldots \ldots \ldots \ldots \ldots \ldots$       | 90  |

| 6.2 | Description of evaluated benchmarks                                                          | 100 |

| 7.1 | System configuration of Simics/GEMS simulation                                               | 112 |

| 8.1 | Power Parameters of Point-to-Point RF Transceiver in 32nm Technology                         | 143 |

| 8.2 | Power Parameters of Arbitration RF Transceiver in 32nm Technology $\ .$ .                    | 143 |

| 8.3 | Evaluated system configuration                                           | 146 |

|-----|--------------------------------------------------------------------------|-----|

| 9.1 | Characteristics of the evaluated system                                  | 176 |

| 9.2 | Impact on processor resource utilization over all benchmarks. Rows indi- |     |

|     | cating removed events show number of events that occur in the CPU only   |     |

|     | case as compared to the CPU and accelerator case. Acc- indicates systems |     |

|     | that feature only conventional CPUs, while Acc+ indicates systems that   |     |

|     | feature CPUs and accelerators. All numbers are percentages. Values that  |     |

|     | were greater than 99.95% were rounded up to 100 $\ldots$                 | 177 |

### VITA

| 2007      | B.S. (Computer Science), California Polytechnic in Pomona.                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 2010      | M.S. (Computer Science), University of California in Los Angeles.                                                                               |

| 2007      | Teaching Assistant, Computer Science Department, CalPoly.<br>Taught networking and parallel/distributed computing.                              |

| 2011      | Teaching Assistant, Computer Science Department, UCLA.<br>Taught Introduction to Computer Science and Introduction to<br>Computer Organization. |

| 2011-2015 | Graduate Student Researcher for The Center for Domain Spe-<br>cific Computing (CDSC).                                                           |

| 2013-2015 | Graduate Student Researcher for The Center for Future Archi-<br>tectures Research (C-FAR).                                                      |

| 2012      | Intern at Xilinx. Modified compiler and tool chain for targeting experimental platform.                                                         |

| 2014      | Intern at Intel. Implemented simulation models and compila-<br>tion tool-chain for hardware accelerators.                                       |

### PUBLICATIONS

AXR-CMP: Architecture support for accelerator-rich CMPs (SAW '12)

Compilation and Architecture support for custom vector instruction extensions (ASP-

DAC '12)

BiN: A Buffer-in-NUCA for accelerator-rich CMPs (ISLPED '12)

CHARM: A composable heterogeneous accelerator-rich microprocessor (ISLPED '12)

Stream Arbitration: Toward efficient bandwidth utilization for emerging on-chip interconnects (TACO '13)

Composable accelerator-rich microprocessor enhanced for adaptivity and longevity (ISLPED '13)

Architecture support for domain-specific accelerator-rich CMPs (TECS '14)

Accelerator-rich architectures: Opportunities and Progress (DAC'14)

## CHAPTER 1

### Introduction

Power-efficiency has become one of the primary design goals in the many-core era. While ASIC/FPGA designs can provide orders of magnitude improvement in power-efficiency over general-purpose processors, they lack reusability across different application domains, and significantly increase the overall design time and cost [3]. On the other hand, general-purpose designs can amortize their cost over many application domains, but can be 1,000 to 1,000,000 times less efficient in terms of performance/power ratio in some cases [3]. A recent industry trend to address this is the use of on-chip accelerators in many-core designs [4–6]. According to an ITRS prediction [1], this trend is expected to continue as accelerators become more common and present in greater numbers (close to 1500 by 2022). On-chip accelerators are application-specific implementations that provide power-efficient implementations of a particular functionality, and can range from simple tasks (i.e., a multiply accumulate operation) to tasks of more moderate complexity (i.e., an FFT or DCT) to even more complex tasks (i.e., complex encryption/decryption or video encoding/decoding algorithms). On-chip accelerators are combined with generalpurpose cores in an effort to amortize the cost of the design across many application domains. Accelerators can capture the most commonly executed kernels of one or more application domains. They are relatively simple to design/optimize (compared to the entire application), and the general-purpose cores can be used to handle the rest of the application.

Accelerator-rich architectures also offer a good solution to overcome the *utilization* wall as articulated in the recent study reported in [7]. It demonstrated that a 45nm chip filled with 64-bit operators would only have around 6.5% utilization (assuming a power budget of 80W). The remaining *un-utilizable* transistors are ideal candidates for accelerator implementations, as we do not expect all the accelerators to be used all the time. Moreover, once an accelerator is used, it provides much higher performance/power efficiency, due to its customized implementation, compared to the general-purpose cores.

In order to increase the utilization of accelerators, and allow application developers to take advantage of the performance and energy consumption benefits they offer, it is necessary to reduce the overhead involved in their use. Currently, this overhead comes both in the form of a performance penalty rooted in operating system(OS) and driver interaction, along with logistical problems associated with actually interacting with the accelerator and authoring programs that make use of specialized hardware. Because accelerator designs are not universal, programmers need to write code that explicitly makes use of accelerators, and thus requires refactoring to the design of the program, knowledge of what accelerators are available in a given platform, and restricting a program to execute exclusively to a specific platform.

These issues gave rise to the work discussed in this document. This work focuses on simplifying the use of accelerators, and simplifying their use. While specific compute engine designs are referenced within this work, they are not the focus of it. The focus of this work is resource management, and eliminating barriers that make accelerators attractive in the abstract, but impractical in reality. By analyzing the strengths of hardware and the needs of software, this work aims to design hardware that can be efficiently used by software, instead of designing the fastest possible hardware, and rendering the platform unusable by software. This takes the form of four independent works, which can be briefly introduces as follows:

• ARC: Resource management and arbitration is conventionally the responsibility of software drivers, and OS calls designed to allow for interaction with drivers. These calls not only introduce their own overhead, but also introduce long-lasting impacts on program performance, such as flushing translation look-aside buffers (TLBs) or local caches as a result of switches between process memory spaces.

ARC introduces the first architectural accelerator resource manager that aims to extend all of the benefits conventionally extended by a driver, while eliminating the performance overhead. ARC pushes the use of accelerators entirely into userspace, and eliminates the interaction of the OS entirely. This work is discussed in Chapter 2

- **CHARM:** Large accelerators are highly efficient and feature high performance, but come with two shortcomings: 1) because they are highly specialized, they are often infrequently utilized, and 2) it is intractable to automate the process of finding occurrences of large accelerators in source code, and thus a programmer needs to explicitly invoke a large accelerator. To address these issues, the CHARM architecture breaks accelerators up into small parts, and expresses a complex accelerator as a network of small communicating accelerators. Because these pieces can communicate with one another in an arbitrary way, any given component is capable of being used in many different configurations. For this reason, it becomes possible to achieve high utilization of these small accelerators. To achieve additional performance and utilization, CHARM also introduces hardware-assisted work distribution, thus allowing a great number of accelerators to contribute toward the computation of even simple compute tasks. Additionally, these small accelerators can be found in arbitrary program code, and thus it is possible to compile programs for this platform without requiring specialized knowledge from a programmer. This work is discussed in greater detail in Chapter 3

- **CAMEL**: To further improve on the utilization benefits realized in the CHARM architecture, CAMEL introduces an amount of programmable fabric for the purpose of instancing infrequently used accelerators. This allows for ASIC resources to be dedicated to implementing a greater amount of frequently needed accelerators, rather than being dedicated to rarely used accelerators for the purposes of achieving workload coverage. CAMEL also introduces elements facilitating the management of programmable fabric, that allows the system to continue to operate as a cohesive

whole, entirely within user space. CAMEL is discussed in Chapter 5

• *AIM*: Nearly all proposals for introducing accelerators to a platform involve extensive modifications to a number of components of a system, including the cpu, memory, operating system, and often the communication mechanisms and protocols between these components. While these are not problems in the context of an academic study, it does make it extremely difficult to actually introduce accelerators in an actual platform, due to the number of industry players and different organizations whose cooperation would be required. The AIM project puts forward a design intended to introduce acceleration in a more down-to-earth way, in a fashion that can be introduced to existing systems without requiring modification of any existing components. This is done while achieving many of the desirable qualities of the previous works as well, such as operating over shared memory. This is done by introducing a new device that seats into an existing systems' DRAM memory interfaces. This also comes with the advantage that it is possible to construct large systems of accelerators, since the accelerator resources would scale relative to the size of the memory system. This work is discussed in Chapter 6

Additionally, my experience with working with accelerator-centric platforms led me to pursue a number of additional works that deviated from my primary interest, and instead focus on performance concerns of accelerators themselves from a system-wide perspective. Two selected works of this type are introduced below:

• **BiN**: Some accelerators benefit from large local memory for internal use, and are able to compute more efficiently if they can internalize a portion of memory reuse. If many such accelerators are on a chip, it becomes unreasonable to construct large private memories for each accelerator, due to space constraints. To address this issue, we propose a method of allocating and managing buffers in a non-uniform cache architecture (NUCA). This work, Buffer in NUCA (BiN), aims to allow for compute engines to operate efficiently on larger amounts of data without requiring private buffers. For algorithms whose computational efficiency coorelates well

with the amount of data being operated over at a given time, this can improve performance substantially. BiN is discussed in Chapter 7.

• STREAM: While designing high performance compute engines is relatively easy, developing mechanisms to deliver necessary data to a compute engine is much more difficult. We examine trends in network on chip (NoC) design and developed a protocol in the context of emerging network technologies. We evaluated radio frequency interconnection (RF-I) networks, and developed a protocol named STREAM that enables efficient exploitation of the enormous bandwidth potential of new network technology. This work is further discussed in Chapter 8.

## CHAPTER 2

## Architecture Support for Accelerator-Rich CMPs

Conventional accelerators, such as GPUs or other dedicated PCI devices, conventionally use a set of drivers to allow user software to interact with hardware. This driver primarily provides two services: 1) a portal through which software can communicate with a device, and 2) an opportunity for an operating system to ensure some measure of safety and process isolation. A driver however is a complicated and heavy bit of software, and comes with many performance penalties, as will be shown. In an accelerator-rich system, these penalties constitute a non-trivial cost, and complicates the performance expectations that a programmer may have of a presumably higher performing device.

This work, entitle Accelerator-Rich CMPs(ARC) [8], is the first work to argue for addressing these performance penalties with a dedicated hardware resource manager, and eliminating the concept of a device driver entirely. This work was intended to elevate an accelerator to a first-order primitive, providing hardware primitives that allow for an accelerator to operate directly over shared memory in process space, without involving the operating system or any other auxiliary software abstractions. This results in accelerators being usable for small tasks, and managed as an as-needed set of compute engines that software can tap into, and simplifies the performance model associated with using an accelerator.

#### 2.1 Microarchitecture of ARC

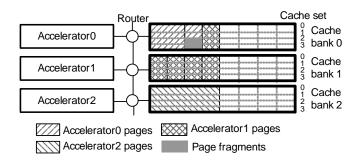

Figure 2.1 shows the overall architecture of ARC which is composed of cores, accelerators, the global accelerator manager (GAM), shared L2 cache banks and shared NoC routers

Figure 2.1: Overall architecture of ARC

Figure 2.2: Communication between core, GAM, and accelerator

between multiple accelerators. All of the mentioned components are connected by the NoC. Accelerator nodes include a dedicated DMA controller (DMA-C) and scratchpad memory (SPM) for local storage and a small translation look-aside buffer (TLB) for virtual to physical address translation. GAM is introduced to handle accelerator sharing and arbitration.

#### 2.1.1 Instruction Set Extension

In order to interact with accelerators more efficiently, we have introduced an extension to the instruction set consisting of four instructions used specifically for interacting with accelerators. These instructions are briefly described in Table 2.1. A processor uses *lcaccreq* to request information about accelerator availability, consisting of pairs of accelerator identifiers and predicted wait times for each available accelerator. A processor will then use *lcacc-rsv* to request use of a specific accelerator. *lcacc-cmd* is used for interacting directly with an accelerator. When a job is completed, *lcacc-free* is used to release an accelerator to be used by another cpu. These instructions are accessible directly from user code, and do not require OS interaction. Communication with accelerators is done

Figure 2.3: Light-weight interrupt support

with the use of virtual addresses, accessing resources that are already accessible from user code. Execution of each of these instructions results in a message being sent to a device on the network, either the GAM or an accelerator. Attached to each of these messages is the thread ID of the executing thread that can be used to track requesting threads in an environment where context switches are possible.

Figure 2.2 shows the communication between a core, the GAM, an accelerator and the shared memory detailing the use of an accelerator by a core. The numbers on the arrows in Figure 2.2 show the steps taken when a core uses a single accelerator. They are described below.

- The core requests an enumeration of all accelerators it may potentially need from the GAM (*lcacc-req*). The GAM responds with a list of accelerator IDs and associated estimated wait times.

- 2. The core sends a sequences of reservations (*lcacc-rsv*) for specific accelerators to the GAM. The core waits for the GAM to give it permission to use these accelerators. The GAM also configures the reserved accelerators for use by the requesting core.

- 3. The core writes a task description detailing the computation to be performed to the shared memory. It then sends a command to the accelerator (*lcacc-cmd*) iden-

| lcacc-req x        | Request information from GAM about availability of         |  |  |  |

|--------------------|------------------------------------------------------------|--|--|--|

|                    | accelerators implementing functionality $x$                |  |  |  |

| lcacc-rsv x y      | Reserve the accelerator with ID $x$ for a                  |  |  |  |

|                    | predicted duration $y$                                     |  |  |  |

| lcacc-cmd accl cmd | Send a command $cmd$ to an accelerator $accl$ with         |  |  |  |

| $addr \ x \ y \ z$ | parameters $x, y$ , and $z$ . Performs an address          |  |  |  |

|                    | translation on $addr$ , sending both logical and           |  |  |  |

|                    | physical address.                                          |  |  |  |

| lcacc-free accl    | Sends a message to GAM releasing accelerator <i>accl</i> . |  |  |  |

Table 2.1: Instructions used to interact with accelerators.

Table 2.2: Instructions to handle light-weight interrupts.

| lwi-reg $x y z$ | Register service routine $y$ to service interrupts arriving      |

|-----------------|------------------------------------------------------------------|

|                 | from accelerator $x$ . LWI message packet will be written to $z$ |

| lwi-ret         | Return from an interrupt service routine.                        |

tifying the memory address of the task description. The accelerator loads this task description, and begins working.

4. When the accelerator finishes working, it notifies the core. The core then sends a message to the GAM freeing the accelerator (*lcacc-free*).

#### 2.1.2 Light-Weight Interrupt Support

| <b>Table 2.3:</b> | OS | overhead | $\operatorname{to}$ | $\operatorname{access}$ | accelerators | (cyc) | es | ) |

|-------------------|----|----------|---------------------|-------------------------|--------------|-------|----|---|

|-------------------|----|----------|---------------------|-------------------------|--------------|-------|----|---|

| Operation         | 1 Core  | 2 Cores | 4 Cores  | 8 Cores | 16 Cores   |

|-------------------|---------|---------|----------|---------|------------|

| Open driver       | 214,413 | 256,401 | 266, 133 | 308,434 | 316,161    |

| ioctl (average)   | 703     | 725     | 781      | 837     | 885        |

| Interrupt latency | 16,383  | 20,361  | 24,022   | 26,572  | $28,\!572$ |

A platform that features accelerators requires a mechanism for a processor to be notified of the progress of an accelerator. In the ARC platform, we handle this issue with the use of light-weight interrupts. ARC light-weight interrupts are interrupts handled entirely as user code, and do not involve OS interaction, as this interaction can be a major source of inefficiency. Table 2.3 shows the cost in cycles of interacting with accelerators through a device driver and the overhead associated with OS interrupts.

There are three main sources of interrupts associated with accelerator interaction: (1) GAM responses, (2) TLB misses, and (3) notifications that the accelerators have finished working. GAM responses come either because a core sent a request or a reserve message. TLB misses occur when an accelerator fails to perform address translation with the use of its own private TLB, and requires a core's assistance in performing the lookup. Interrupts notifying the completion of work arrive when an accelerator has completed all work given to it.

Figure 2.3 shows the microarchitecture components added to the cores in ARC in order to support the light-weight interrupt. An interrupt is sent via an interrupt packet (shown in Figure 2.3-a) through the NoC to the core requested accelerator. Each interrupt packet includes the thread ID which identifies the thread which this interrupt belongs to, and a set of interrupt-specific information. The main microarchitectural components added to support the light-weight interrupt are listed below:

- 1. Interrupt controller located at the core's network interface. This is responsible for receiving the interrupt packets and queuing them until being serviced by the core.

- 2. Light-weight interrupt interface in the core. This is responsible for: (1) receiving the interrupt from the interrupt controller, and (2) providing a software interface to setup the information needed to service the interrupt.

The interrupt controller has a queue for buffering the received interrupt packets, so they don't get lost if the core is busy handling other interrupts. Without loss of generality we assume that for each thread we can only have one level nest for interrupt.

Figure 2.5: ARC development flow

Figure 2.4: Accelerator extraction methodology

This means no other light-weight interrupt will be serviced, while servicing another lightweight interrupt. If an interrupt arrives for a thread that is currently scheduled, it is executed immediately. If the thread is not scheduled, a normal OS-based interrupt occurs.

In order to support light-weight user-level interrupts, we introduce a set of instructions to enable user code to handle interrupts. These instructions are described in Table 2.2. *lwi-reg* registers the interrupt handlers. *lwi-ret* returns from an interrupt handler routine. A program segment using accelerators is then designed as a series of interrupt service routines.

#### 2.1.2.1 Accelerator Extraction Methodology

Figure 2.4 shows the block diagram for accelerator extraction from a given application. Given an application, using a combination of static analysis and profiling, a list of candidates for accelerators are extracted. These candidates are weighted using a series of selection criteria, such as area, performance, energy, criticality, and physical design constraints. This step generates an accelerator database, which can be used together with a series of transformation rules to create larger or smaller accelerators from the available accelerators in the platform. This step is handled by a module called the *virtualizer*, which outputs a DLL that is used to link to executable files, as shown in Figure 2.5.

#### 2.1.3 Programming Interface to ARC

The application programming interface (API) involved in using accelerators is presented in Figure 2.5. For each type of accelerator, one dynamic linked library (DLL) is provided. This DLL is specific to a target platform, and provides a mapping from accelerator calls to actual invocations of physical accelerators. Calls to accelerators have their implementations dynamically linked to application code.

#### 2.1.4 Invoking Accelerators

In this work, we assume an accelerator will be used to process a relatively large amount of data. The initial overhead associated with acquiring permissions to use an accelerator is large enough that it should be amortized over a large amount of work. To that end, we introduce two accelerator features that explicitly deal with efficiently processing large amounts of data: (1) task descriptions to limit communication between accelerators and the controlling core, and (2) methods to handle TLB misses.

To communicate with an accelerator, a program would first write to a region of shared memory a description of the work to be performed. This description includes location of arguments, data layout, which accelerators are involved in the computation, the computation to be performed, and the order in which to perform necessary operations. This detail is included to allow accelerators to both be general as well as allow coordination of accelerators in groups that perform more complex tasks (described in Section 2.1.6). Evaluating the task description yields a series of steps to be performed in order, with each step consisting of a set of memory transfers and computations that can be executed concurrently. This allows accelerators to overlap computation with memory transfer within a given step. When all computations and memory transfers of a given step are completed, the accelerator moves onto the next step. In this work, we refer to these individual steps as tasks, and the structure detailing a sequence of tasks as a task description.

To further decouple the accelerator from the controlling core, each accelerator contains a small local TLB. This is required because the accelerator operates within the same virtual address space as the software thread that is using the accelerator. The accelerator relies on the controlling core to service any detected TLB misses. It does this by sending a light-weight interrupt to the controlling core when a TLB miss occurs with the address that caused the TLB miss. Handling this interrupt would involve the core executing the same TLB miss handler that is executed when the core normally encounters a miss in its own TLB. Because this is an OS action, and involves trapping to an OS handler regardless, it is not actually necessary that the original software thread that is using the accelerator be currently scheduled. If it is scheduled, the lightweight interrupt interface can be used to limit overhead associated with interrupt handling. Otherwise, the OS can be notified directly (e.g. by invoking a software interrupt or real hardware interrupt) without having to wait for or force a context switch to reschedule the controlling thread. The resolved address is then sent back to the accelerator that had encountered the TLB miss.

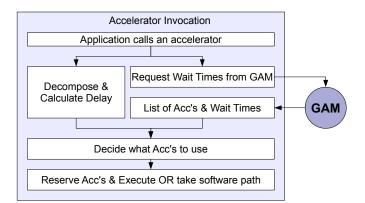

#### 2.1.5 Sharing Accelerators

When accelerators are shared among all the on-chip cores, it is possible for there to be several cores competing for the same accelerator. Even in architectures with large numbers of accelerators, there may be a limited number of one particular type of accelerator that is suddenly in high demand. In this situation, some of these cores may choose to eschew the use of the accelerator and simply execute the task to be offloaded using their own core resources. While the core is certainly less power efficient in executing this task, it may make sense for it to do so in situations where the wait time for an accelerator

Figure 2.6: Regression models for medical imaging benchmarks

will eliminate any potential gains. In this paper we propose a sharing and management scheme which can dynamically determine whether the core should wait to use an accelerator or should instead choose a software path, based on an estimated waiting time. This proposed sharing and management strategy is performed by the GAM. The GAM tracks: 1) the types of available accelerators; 2) the number of accelerators of each type; 3) the jobs currently running or waiting to run on accelerators, their starting time and estimated execution time (Section 2.1.5.1); 4) the waiting list for each accelerator and the estimated run time for each job in the waiting list (Section 2.1.5.2).

# 2.1.5.1 Accelerator Run-Time Estimation (by the Core)

The execution time of a certain job on an accelerator is data-dependent. When an accelerator is reserved, the requesting thread submits an estimation of the duration for which the accelerator will be used. This estimate is determined with the use of a data-size-parameterized regression model, which has been constructed based on profiled executions. We empirically found that a simple second order polynomial is sufficient to estimate execution time within 1-2% on average (at most 6%). Once a model is generated for an accelerator, it is provided to the rest of the development flow via the accelerator DLL

(see Figure 2.5). Figure 2.6 shows the models we used in this work.

### 2.1.5.2 Wait-Time Estimation Algorithm (by the GAM)

After receiving the reserve request message from the core, the GAM will add the requesting core's ID to the tail of the waiting list for that accelerator. Note that the tasks being tracked in this waiting list are issued on a first-come-first-served (FCFS) basis. Hence, the estimated wait-time for the task being added to the end of the list can be derived by summing up the expected execution times of all jobs that already exist in the waiting list for that accelerator. This estimation algorithm is both simple and practical for hardware implementation.

## 2.1.6 Accelerator Composition

A key contribution of our work is the increased utilization of the available resources by either chaining accelerators together or otherwise composing accelerators to virtualize larger ones. In the next two subsections we discuss these techniques.

# 2.1.6.1 Accelerator Chaining

In an accelerator-rich platform, there are many cases when the output of one accelerator feeds the input of another accelerator (like many streaming applications). In a traditional system, these two accelerators communicate through system memory, i.e., the controlling core reads the output of the first accelerator from its SPM, stores it to shared memory, and writes it to the second accelerator's SPM. To remove this inefficiency, two DMA controllers can communicate and the source DMA controller can send the content of its SPM to another DMA controller to be written in its SPM.

Figure 2.7: An example of accelerator composition

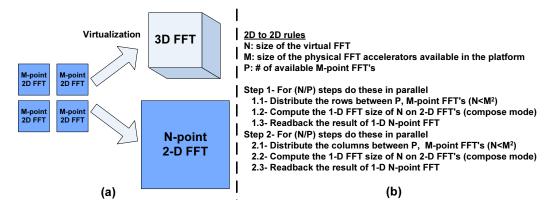

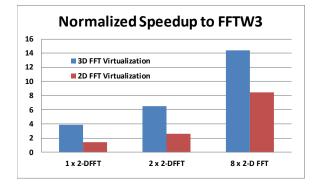

#### 2.1.6.2 Accelerator Virtualization

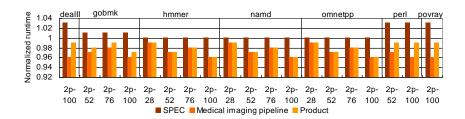

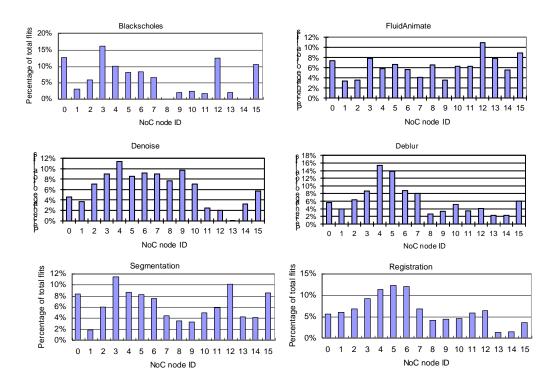

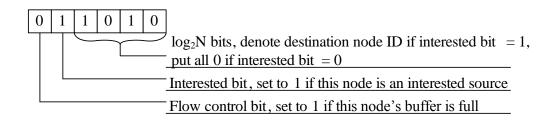

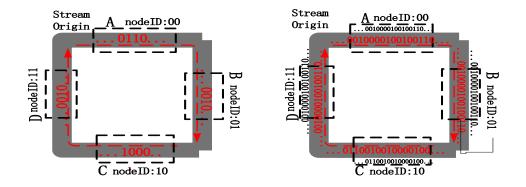

For many types of problems, it is not practical to provide an accelerator to directly solve each possible problem instance. Additionally, it is not practical to demand that an application author target a single architecture. For this reason, we provide a set of virtual accelerators to decouple hardware design and software development. A virtual accelerator is an accelerator that is implemented as a series of calls to other physical accelerators, available in hardware (Figure 2.7(a)). A large library of virtual accelerators can be provided to the application author as if they were implemented in hardware. These accelerators would actually be implemented as a series of decomposition rules that break down a large problem into a number of smaller problems (Figure 2.7(b)), similar in style to the approach presented in [9]. These small problems would then be solved directly by hardware. These rules describe two things: 1) computation that must be performed by accelerators capable of solving sub-problem instances, and 2) how data is communicated to, from, and between these various smaller accelerators. Rules would be applied recursively to express an implementation for each virtual accelerator in terms of calls to physical accelerators.