# UCLA UCLA Electronic Theses and Dissertations

Title

Modeling and Optimization for High-speed Links and 3D IC

**Permalink** https://escholarship.org/uc/item/5f2003tx

**Author** Yao, Wei

Publication Date 2012

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Modeling and Optimization for High-speed Links and 3D IC

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Wei Yao

2012

© Copyright by Wei Yao 2012

### Abstract of the Dissertation

## Modeling and Optimization for High-speed Links and 3D IC

by

#### Wei Yao

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2012 Professor Lei He, Chair

The advance of modern integrated circuit (IC) processes has supported increasing date rates on chip-to-chip communications in many consumer and professional applications, such as multimedia and optical networking. Serial links have successfully evolved and achieved the bit-rate of several tens of Gb/s per channel by applying new generations of IC process and advanced circuit techniques. However, as process technologies further scale down, severe process variations significantly impact the performance of high speed serial links and makes todays circuit designs have to be optimized not only for nominal performance but also for a reasonable yield. On the other hand, three-dimensional (3D) IC provides a smaller form factor, higher performance, and lower power consumption than conventional 2D integration by stacking multiple dies vertically. Through-silicon-via (TSV) enables the vertical connectivity between stacked dies or interposer and is a key technology for 3D IC. However, electrical signaling over TSVs presents a unique set of design challenges and thus requires accurate modeling and detailed signal and power integrity analysis.

In this research, the bottlenecks in TSV modeling, variation-aware circuit optimization and efficient performance evaluation for high bit-rate applications are analyzed, and solutions are presented. A simple yet accurate pair-based model for multi-port TSV networks (e.g., coupled TSV array) is proposed by decomposing the network into a number of TSV pairs and then applying circuit models for each TSV pair. This methodology is first verified against full-wave electromagnetic (EM) simulation for up to 20GHz and subsequently employed for a variety of examples of signal and power integrity analysis. For high speed serial links, an optimization framework is proposed for the joint design time and post-silicon tuning optimization for digitally tuned analog circuits, and can be used to maximize the yield in serial link transmitter design and the phase-locked-loop (PLL) design subject to the area and power constraints. Moreover, an efficient mathematical method is proposed to capture the worst-case data-dependent jitter and noise without lengthy simulations. These modeling and optimization methodologies can be applied to accurately explore the chip-to-chip integration and signaling schemes at early design stage in today's and tomorrow's 3D IC and high speed serial link design. The dissertation of Wei Yao is approved.

M.-C. Frank Chang

Sudhakar Pamarti

Rupak Majumdar

Lei He, Committee Chair

University of California, Los Angeles2012

To My Family and Friends.

### TABLE OF CONTENTS

| 1        | Intr  | oducti  | ion                                                   | 1        |

|----------|-------|---------|-------------------------------------------------------|----------|

| <b>2</b> | Wo    | rst-Ca  | se Data-Dependent Jitter and Amplitude Noise for Dif- |          |

| fe       | renti | al Sigr | naling                                                | <b>5</b> |

|          | 2.1   | Introd  | luction                                               | 5        |

|          | 2.2   | Prelin  | ninaries                                              | 8        |

|          |       | 2.2.1   | RLGC Model for Transmission Line                      | 8        |

|          |       | 2.2.2   | Parallel Transmission Lines                           | 9        |

|          |       | 2.2.3   | Pre-emphasis Filter                                   | 12       |

|          | 2.3   | Jitter  | and Amplitude Noise Model                             | 13       |

|          |       | 2.3.1   | Subcomponents of Jitter and Amplitude Noise           | 14       |

|          |       | 2.3.2   | Modeling of Data-Dependent Jitter and Noise           | 15       |

|          | 2.4   | Worst   | -case Timing Jitter                                   | 17       |

|          |       | 2.4.1   | Problem Formulation                                   | 18       |

|          |       | 2.4.2   | Relaxation Based Binary Search                        | 19       |

|          |       | 2.4.3   | Pseudo-Boolean Optimization                           | 20       |

|          |       | 2.4.4   | Proposed Heuristic                                    | 21       |

|          | 2.5   | Worst   | -case Amplitude Noise                                 | 24       |

|          | 2.6   |         | imental Results                                       | 25       |

|          |       | 2.6.1   | Jitter and Amplitude Noise Model Validation           | 25       |

|          |       | 2.6.2   | Worst-case Jitter and Amplitude Noise Calculation     | 27       |

|          | 2.7   |         |                                                       | <br>29   |

| 3  | Joir | nt Desi | ign-Time and Post-Silicon Optimization                                                           | for | Digitally |    |

|----|------|---------|--------------------------------------------------------------------------------------------------|-----|-----------|----|

| Τι | uned | Analo   | g Circuits                                                                                       |     |           | 30 |

|    | 3.1  | Introd  | uction $\ldots$ |     |           | 30 |

|    | 3.2  | Prelim  | inaries on Digitally Tuned Analog Circuits                                                       |     |           | 33 |

|    | 3.3  | Proble  | m Formulation                                                                                    |     |           | 35 |

|    | 3.4  | Optim   | ization Framework                                                                                |     |           | 37 |

|    |      | 3.4.1   | Algorithm Overview                                                                               |     |           | 38 |

|    |      | 3.4.2   | Partitioning and Bound Estimation                                                                |     |           | 40 |

|    |      | 3.4.3   | Gradient Ascent Method                                                                           |     |           | 41 |

|    | 3.5  | Transr  | nitter Design in High-speed Serial Link                                                          |     |           | 42 |

|    |      | 3.5.1   | Design-time Optimization                                                                         |     |           | 44 |

|    |      | 3.5.2   | Post-silicon Tuning and Joint Optimization                                                       |     |           | 46 |

|    | 3.6  | PLL D   | Design in High-speed Serial Link                                                                 |     |           | 47 |

|    |      | 3.6.1   | Design-time Optimization                                                                         |     |           | 48 |

|    |      | 3.6.2   | Post-silicon Tuning and Joint Optimization                                                       |     |           | 50 |

|    | 3.7  | Experi  | mental Results                                                                                   |     |           | 52 |

|    |      | 3.7.1   | Transmitter Design                                                                               |     |           | 52 |

|    |      | 3.7.2   | PLL Design                                                                                       |     |           | 56 |

|    | 3.8  |         | usions                                                                                           |     |           | 57 |

|    |      |         |                                                                                                  |     |           |    |

| 4  |      | U       | and Application of Multi-Port TSV Net                                                            |     |           |    |

| IC | ]    |         |                                                                                                  |     |           | 58 |

|    | 4.1  | Introd  | uction                                                                                           |     |           | 58 |

|    | 4.2  | Prelim  | inary on TSV Modeling                                                                            |     |           | 60 |

|    | 4.3  | Multi-  | port TSV Network Modeling                                                                        |     |           | 63 |

|          |     | 4.3.1   | Framework Overview                                          | 64  |

|----------|-----|---------|-------------------------------------------------------------|-----|

|          |     | 4.3.2   | Pair-based Equivalent Circuit Model                         | 69  |

|          |     | 4.3.3   | Model Validation via Simulation                             | 71  |

|          | 4.4 | Multi-  | port TSV Network Characteristics in Signal and Power In-    |     |

|          |     | tegrity | *                                                           | 72  |

|          |     | 4.4.1   | Crosstalk Analysis for Chip-to-chip TSV Networks in Silicon |     |

|          |     |         | Interposer                                                  | 73  |

|          |     | 4.4.2   | Impedance Analysis for Power/Ground TSV Array in 3D         |     |

|          |     |         | Power Distributed Network (PDN)                             | 77  |

|          | 4.5 | TSV A   | Array Bandwidth Analysis for 3D IC                          | 79  |

|          | 4.6 | Conclu  | isions                                                      | 82  |

| <b>5</b> | Moo | deling  | of RDL Coplanar Waveguide on Silicon Interposer .           | 83  |

|          | 5.1 | Introd  | uction                                                      | 83  |

|          | 5.2 | CPW     | Equivalent Circuit Model: Shunt Admittance                  | 84  |

|          | 5.3 | CPW     | Equivalent Circuit Model: Series Impedance                  | 88  |

|          | 5.4 | Model   | Validation via Simulation                                   | 91  |

|          | 5.5 | Conclu  | 1sion                                                       | 92  |

| 6        | Pow | ver-Ba  | ndwidth Trade-off on TSV Array and TSV-RDL Junc-            | _   |

| tic      |     |         | Challenges on Silicon Interposer                            | 94  |

|          | 6.1 | Introd  | uction                                                      | 94  |

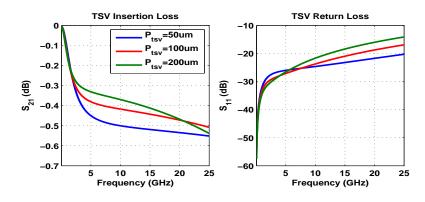

|          | 6.2 | Signal  | Integrity Analysis on TSV Array                             | 96  |

|          | 6.3 | TSV I   | Power and Bandwidth Trade-off Analysis                      | 99  |

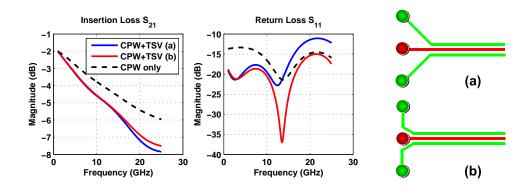

|          | 6.4 |         | Challenges on Junction Structures between TSV and RDL       |     |

|          |     | Ũ       | · · · · · · · · · · · · · · · · · · ·                       | 103 |

|    | 6.5 Conclusions                                    | 106 |

|----|----------------------------------------------------|-----|

| 7  | Conclusion                                         | 107 |

| A  | Mathematical Proof for Pair-based TSV Array Model  | 109 |

| В  | 3D IC Technology and TSV Dimension in ITRS Roadmap | 112 |

| Re | eferences                                          | 114 |

### LIST OF FIGURES

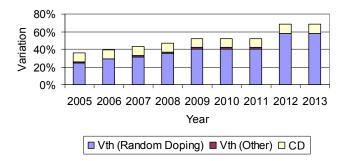

| 1.1  | CMOS threshold voltage variation                                                                         | 1  |

|------|----------------------------------------------------------------------------------------------------------|----|

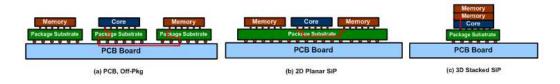

| 1.2  | Beyond-die Integration Options                                                                           | 2  |

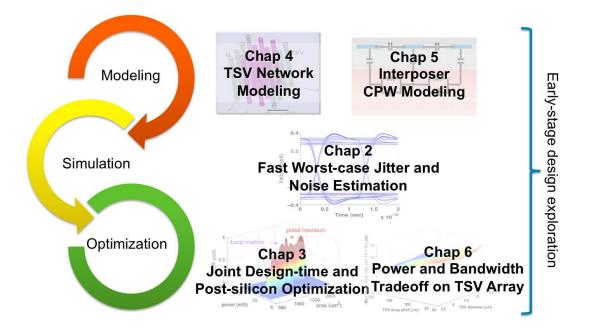

| 1.3  | Structure of the dissertation, showing how the various topics relate                                     |    |

|      | to each other. $\ldots$ | 3  |

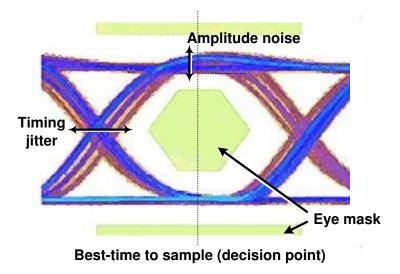

| 2.1  | Eye diagram and eye mask                                                                                 | 6  |

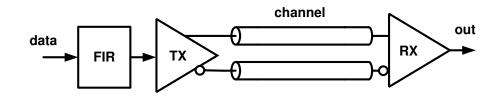

| 2.2  | Transceiver block diagram for differential signaling                                                     | 7  |

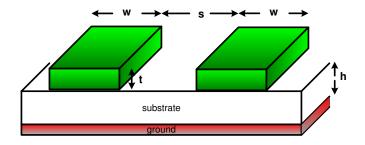

| 2.3  | Section of differential microstrip line                                                                  | 8  |

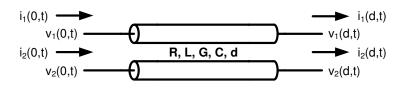

| 2.4  | Parallel transmission lines                                                                              | 11 |

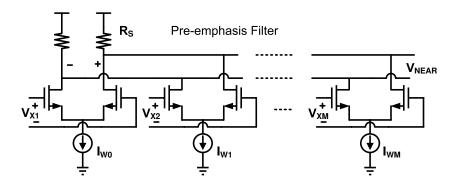

| 2.5  | Pre-emphasis filter at transmitter end for CML differential signaling                                    | 13 |

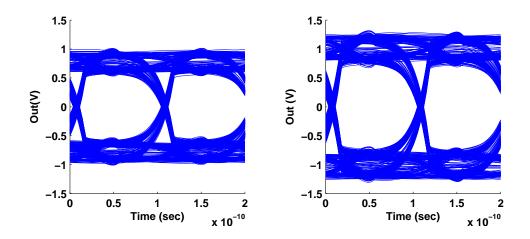

| 2.6  | Eye diagram (left) without the pre-emphasis filter and (right) with                                      |    |

|      | applying a 4-taps pre-emphasis filter                                                                    | 14 |

| 2.7  | Differential signaling with parallel transmission lines and termination                                  | 16 |

| 2.8  | Time domain response of the channel                                                                      | 18 |

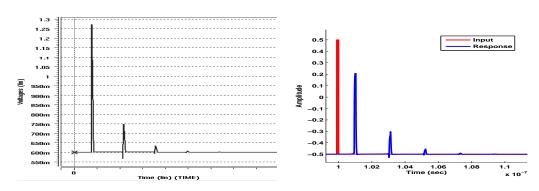

| 2.9  | Transient simulation comparison between (left) SPICE and (right)                                         |    |

|      | our model. The origin point is different.                                                                | 26 |

| 2.10 | Time domain response: SPICE simulation(left) and MATLAB sim-                                             |    |

|      | ulation with our model<br>(right). The origin point is different                                         | 27 |

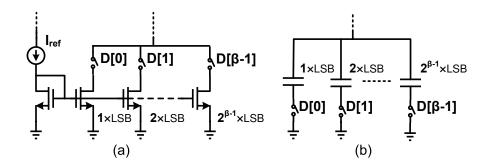

| 3.1  | Examples of digitally tuned analog circuits: (a) CMOS current                                            |    |

|      | source and (b) capacitance array                                                                         | 31 |

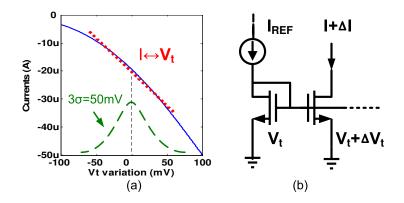

| 3.2  | $V_{th}$ variation model (a) and current mirror with $V_{th}$ mismatch (b).                              | 34 |

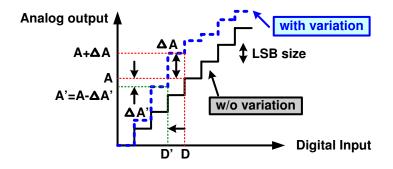

| 3.3  | Post-silicon tuning through DAC                                                                          | 35 |

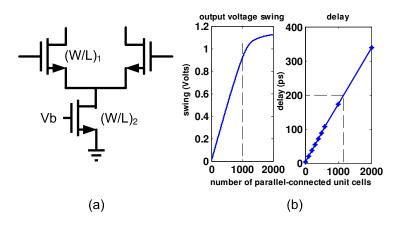

| 3.4  | (a) Unit cell design. (b) Swing and delay vs. number of parallel-              |    |

|------|--------------------------------------------------------------------------------|----|

|      | connected cells                                                                | 39 |

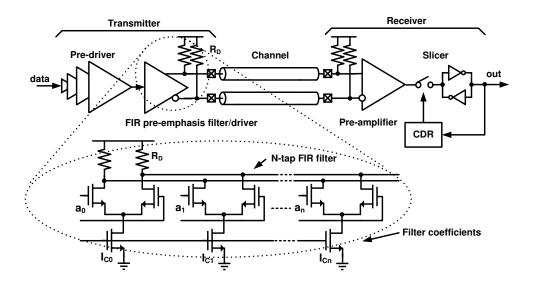

| 3.5  | System diagram of a high-speed serial link                                     | 43 |

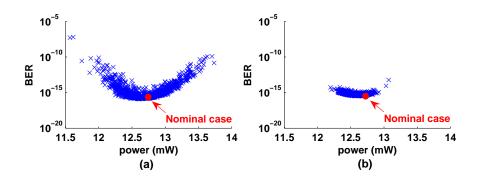

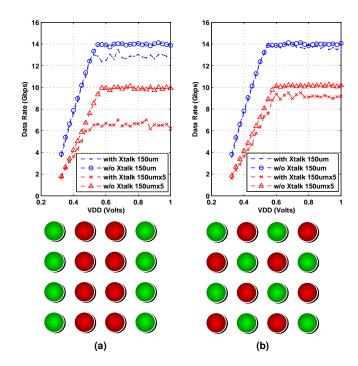

| 3.6  | Power and performance variation for 1000 die samples by Monte                  |    |

|      | Carlo simulation: (a) without tuning and (b) with tuning. $\ldots$             | 46 |

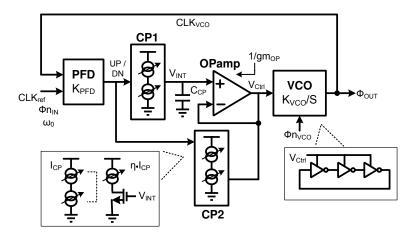

| 3.7  | Tunable and adaptive bandwidth PLL. [SLK00] $\ldots$                           | 48 |

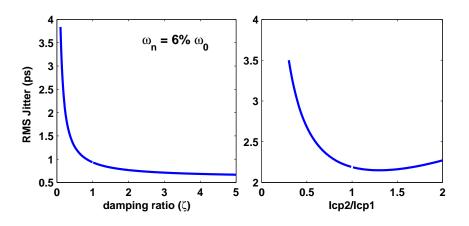

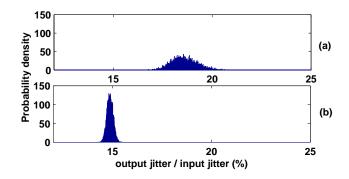

| 3.8  | Output jitter sensitivity to the (a) loop damping factor $\zeta$ and (b)       |    |

|      | charge pump current ratio $I_{CP2}/I_{CP1}$                                    | 49 |

| 3.9  | Probability density for output jitter(%). (a) without tuning (b)               |    |

|      | with tuning circuit and optimized digital control. $\ldots$ $\ldots$ $\ldots$  | 51 |

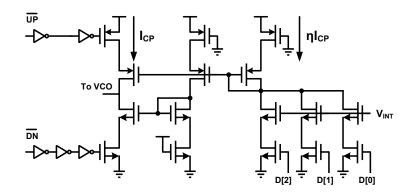

| 3.10 | Charge pump schematic [SLK00]                                                  | 52 |

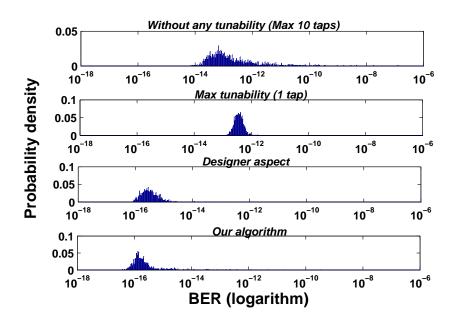

| 3.11 | BER distribution for four different designs                                    | 53 |

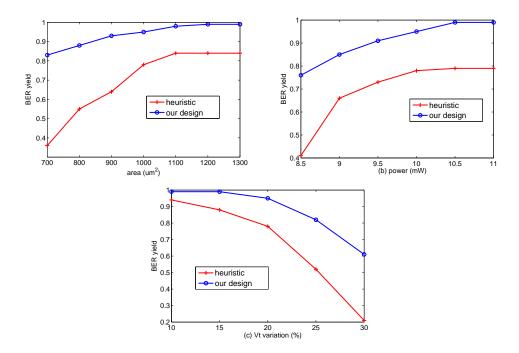

| 3.12 | Yield curves for our designs and design heuristic with respect to              |    |

|      | area (a), power (b) and $V_{th}$ (c)                                           | 55 |

| 3.13 | Yield for our algorithms and design heuristic w.r.t power (a) and              |    |

|      | $V_{th}$ (b) in the PLL                                                        | 56 |

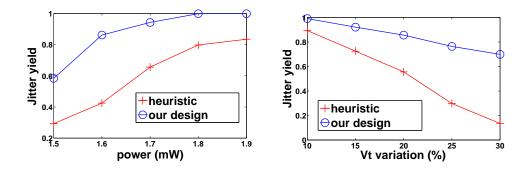

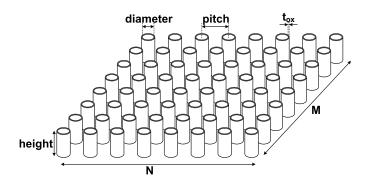

| 4.1  | Multi-port TSV network example: A $M \times N$ TSV array                       | 59 |

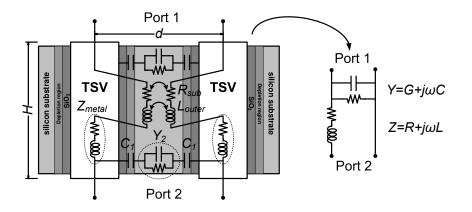

| 4.2  | Structures and dimensional variables of a single TSV pair and its              |    |

|      | RLGC equivalent circuit model [XLS10]                                          | 61 |

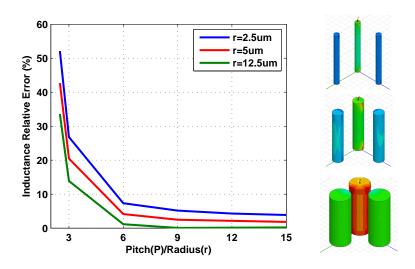

| 4.3  | The charge distribution and the inductance comparison of a 3-TSV               |    |

|      | network show the proximity effect can be neglected when TSV pitch              |    |

|      | is larger than $6\times$ TSV radius. The equivalent inductance is calcu-       |    |

|      | lated at 20GHz based on our methodology and the TSV pair model $% \mathcal{A}$ |    |

|      | in [XKS11]. The results are compared to Ansoft Q3D [ANS] with                  |    |

|      | various TSV radius and pitch/radius ratios.                                    | 65 |

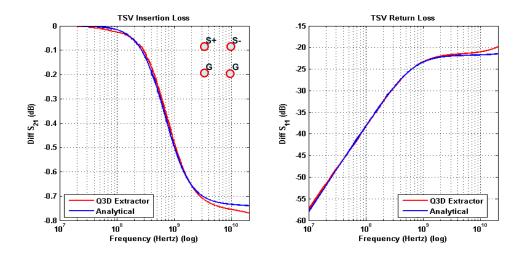

| 4.4  | 2x2 TSV differential pair differential S-parameter comparison. The                                   |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | TSV diameter is $25\mu m$ and pitch is $150\mu m$                                                    | 71 |

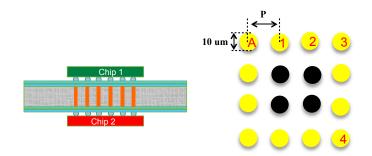

| 4.5  | TSV Networks in silicon interposer for 2.5D chip-to-chip commu-                                      |    |

|      | nication                                                                                             | 72 |

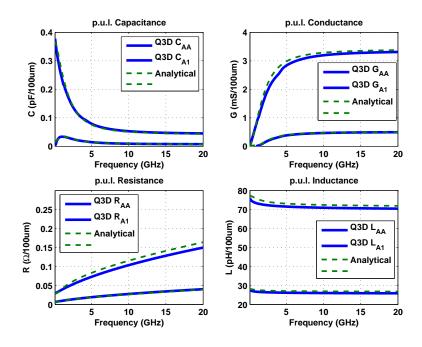

| 4.6  | 4x4 TSV array RLGC comparison for (1) self terms of $TSV_A$ and                                      |    |

|      | (2) mutual terms between $TSV_A$ and $TSV_1$                                                         | 73 |

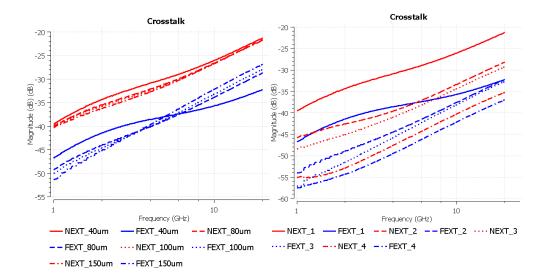

| 4.7  | S Parameters of NEXT and FEXT between $TSV_A$ and $TSV_1$ with                                       |    |

|      | different pitch sizes and between $TSV_A$ and other TSVs with pitch                                  |    |

|      | $40\mu m$                                                                                            | 74 |

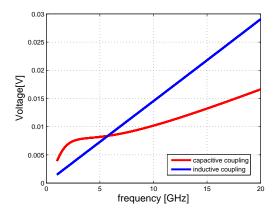

| 4.8  | Normalized crosstalk voltages between $TSV_A$ and $TSV_1$ . The noise                                |    |

|      | voltages are separated to capacitive and inductive couplings using                                   |    |

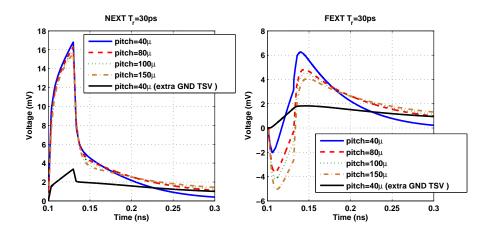

|      | (4.40) and (4.41). The pitch size is 40 $\mu$ m                                                      | 75 |

| 4.9  | Time-domain crosstalk voltage at near and far ends between $TSV_A$                                   |    |

|      | and $TSV_1$ , with 1V signal strength and 30ps rise time                                             | 77 |

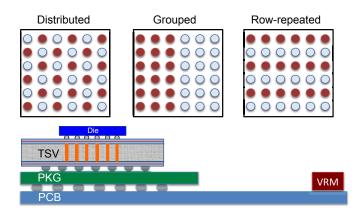

| 4.10 | Power/ground TSV array arrangements and system-level power dis-                                      |    |

|      | tribution network (PDN)                                                                              | 78 |

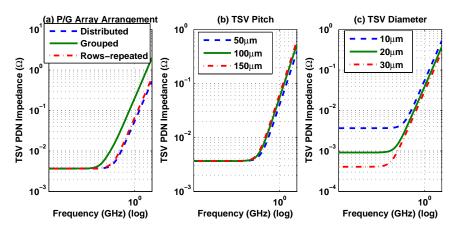

| 4.11 | $\mathrm{P}/\mathrm{G}$ TSV array impedance v.s. (a) different $\mathrm{P}/\mathrm{G}$ TSV array ar- |    |

|      | rangement (b) different pitch size and (c) different diameter                                        | 78 |

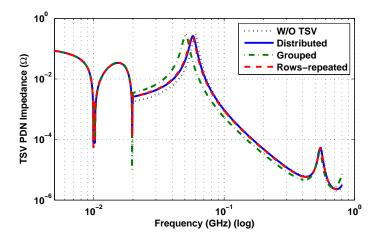

| 4.12 | 3D PDN impedance comparison between different P/G TSV array                                          |    |

|      | arrangements.                                                                                        | 79 |

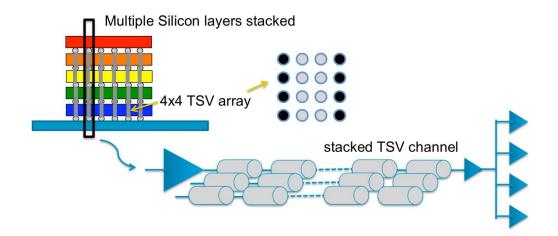

| 4.13 | 3D IC TSV array bandwidth analysis considering different layers                                      |    |

|      | of stacking and different CMOS technology nodes                                                      | 80 |

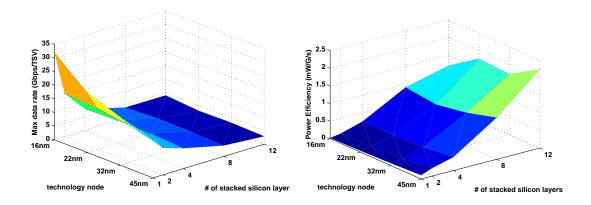

| 4.14 | TSV array date rate per TSV and power efficiency vs number of                                        |    |

|      | stacked silicon layers and technology nodes.                                                         | 80 |

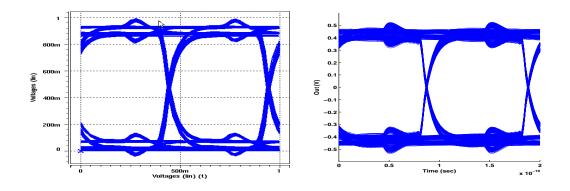

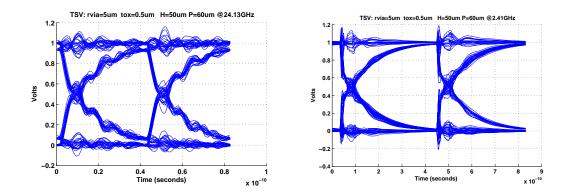

| 4.15 | Eye diagram of (a) 1 layer of $4 \times 4$ TSV array at 24.13Gbps and (b) |    |

|------|---------------------------------------------------------------------------|----|

|      | 12 layers of $4 \times 4$ TSV arrays at 2.41Gbps. Both cases are assumed  |    |

|      | using 16nm technology and with the same driver driving strength.          | 81 |

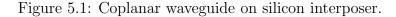

| 5.1  | Coplanar waveguide on silicon interposer                                  | 85 |

| 5.2  | Geometries to calculate the coefficients in the $p_s$ matrix              | 87 |

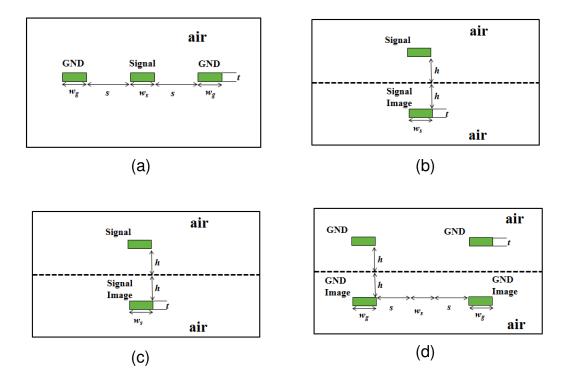

| 5.3  | Equivalent circuit model for the shunt admittance between signal          |    |

|      | and ground conductors of CPW                                              | 88 |

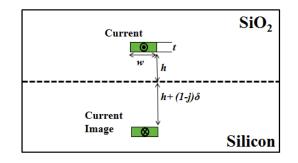

| 5.4  | Complex image of line current source in $SiO_2$ -Silicon media. The       |    |

|      | current flows in the opposite direction in the image lines                | 89 |

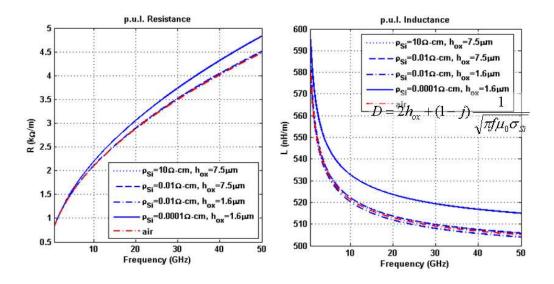

| 5.5  | Comparisons of the series impedance for on-chip CPW structures            |    |

|      | between different silicon conductivity                                    | 90 |

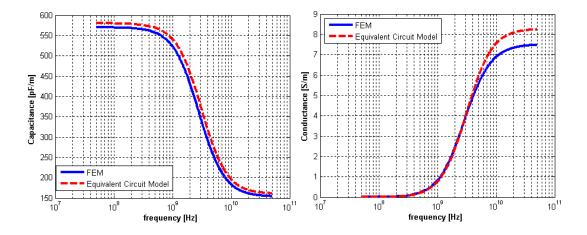

| 5.6  | Shunt admittance obtained from our model is compared with sim-            |    |

|      | ulated results using FEM: (left) capacitance (right) conductance          | 91 |

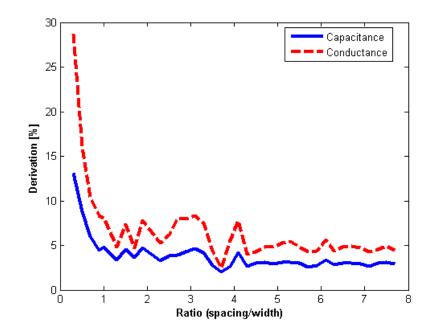

| 5.7  | Derivations of capacitance and conductance for on-chip CPW us-            |    |

|      | ing FEM and the model proposed. The x-axis is the ratio of trace          |    |

|      | spacing to trace width. The y-axis is the average deviation in per-       |    |

|      | centage from 50 MHz to 50 GHz                                             | 92 |

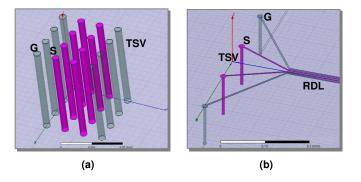

| 6.1  | Concept of 3D IC using TSV and silicon interposer                         | 95 |

| 6.2  | (a) $4 \times 4$ TSV array and (b) an example of junction structure be-   |    |

|      | tween TSVs and interposer RDL traces                                      | 95 |

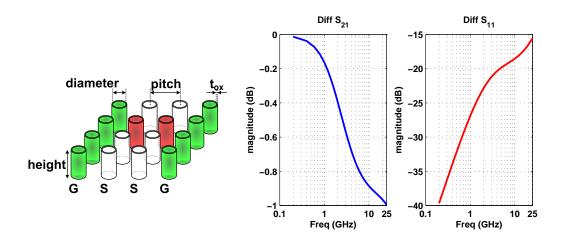

| 6.3  | An array of cylindrical Cu-filled TSVs and the differential $S_{21}$ and  |    |

|      | $S_{11}$ on one of the differential TSV pair (marked in red)              | 96 |

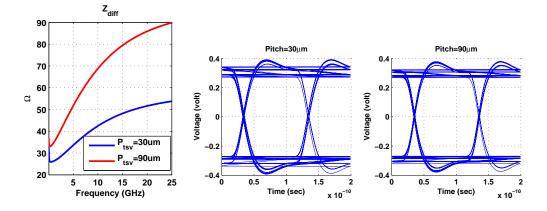

| 6.4  | The differential impedance $(Z_{diff})$ and eye diagram comparison be-    |    |

|      | tween $30\mu m$ and $90\mu m$ TSV array pitch. The TSV diameter is        |    |

|      | $10\mu m$ and height is $150\mu m$ .                                      | 97 |

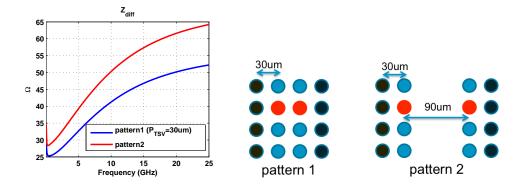

| 6.5  | The differential impedance $(Z_{diff})$ comparison when changing the          |     |

|------|-------------------------------------------------------------------------------|-----|

|      | center-to-center distance between differential signal TSVs from $30 \mu m$    |     |

|      | to $90\mu m$ while keeping the signal to ground distance fixed at $30\mu m$ . | 98  |

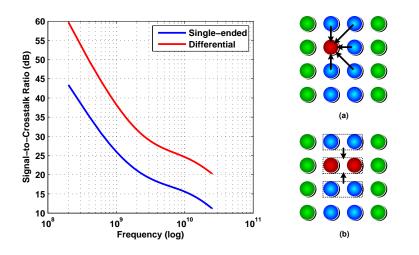

| 6.6  | Signal-to-Crosstalk-Ratio (SCR) comparison on the $4\times4$ TSV ar-          |     |

|      | ray when considering (a) single-ended signaling and (b) differential          |     |

|      | signaling.                                                                    | 99  |

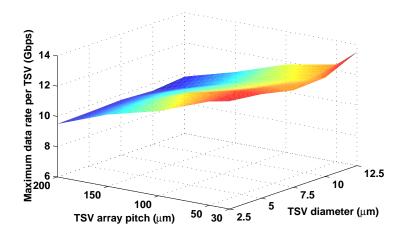

| 6.7  | Maximum achievable data rate per TSV in a $4\!\times\!4$ TSV array versus     |     |

|      | various TSV pitches and diameters                                             | 100 |

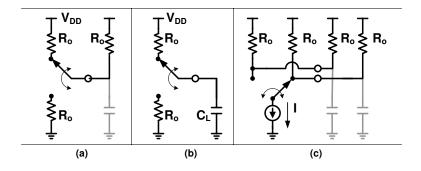

| 6.8  | Different types of drivers and terminations: (a) push-pull single-            |     |

|      | ended with resistive termination, (b) push-pull single-ended with             |     |

|      | pure capacitive loading, and (c) differential CML driver. $R_0 = 40\Omega$    |     |

|      | and $C = 2pF$                                                                 | 101 |

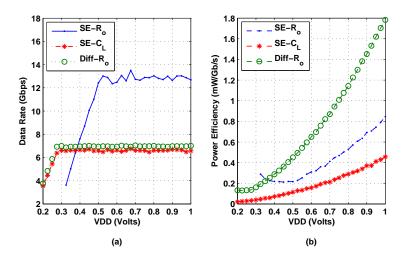

| 6.9  | (a) Maximum achievable data rate per TSV versus input swing                   |     |

|      | voltages and (b) corresponding power efficiency versus input swing            |     |

|      | voltages for various output drivers and terminations shown in Fig.            |     |

|      | 6.8                                                                           | 101 |

| 6.10 | Maximum achievable data rate per TSV using single-ended signal-               |     |

|      | ing versus driver input swing with different TSV array patterns: (a)          |     |

|      | G-S-S-G column-by-column and (b) distributed signal and ground.               | 102 |

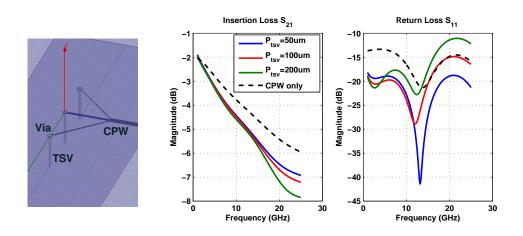

| 6.11 | Fanout-like junction structure between TSV and RDL and the full               |     |

|      | link $S_{21}$ and $S_{11}$ comparison for different TSV pitches               | 104 |

| 6.12 | G-S-G TSV $S_{21}$ and $S_{11}$ comparison for different TSV pitches          | 104 |

| 6.13 | Full link $S_{21}$ and $S_{11}$ comparison between two different junction     |     |

|      | structure between TSV and RDL                                                 | 105 |

### LIST OF TABLES

| 2.1 | Differential transmission line test<br>bench design information: width(w),                                                                                                   |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | $\operatorname{spacing}(s)$ , $\operatorname{thickness}(t)$ , $\operatorname{dielectric} \operatorname{height}(h)$ , $\operatorname{length}(L)$ and $\operatorname{charac-}$ |     |

|     | teristic impedance.                                                                                                                                                          | 26  |

| 2.2 | Jitter and amplitude noise model validation                                                                                                                                  | 27  |

| 2.3 | Worst-case jitter, amplitude noise and runtime comparison: PRBS                                                                                                              |     |

|     | denotes pseudo-random bit sequence. For worst-case jitter, relaxation-                                                                                                       | -   |

|     | based binary search (BS) is used along with pseudo-Boolean opti-                                                                                                             |     |

|     | mizer (PBO) or our heuristic algorithm (Heuristic). For worst-case                                                                                                           |     |

|     | noise, LP denotes directly solving linear programming. $\ . \ . \ .$ .                                                                                                       | 28  |

| 4.1 | Mutual inductance and capacitance between $TSV_A$ and $TSV_1$ at                                                                                                             |     |

|     | 10GHz with different pitch sizes                                                                                                                                             | 76  |

| B.1 | High-density TSV projections in 2008 ITRS update [Ass08]                                                                                                                     | 113 |

### Vita

- 1998–2002 B.S., Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan.

- 2002–2004 M.S., Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan.

- 2006-present Ph.D. program, Department of Electrical Engineering, University of California, Los Angeles, California, USA. Teaching Assistant, Digital Design Laboratory, Fall 2007, Winter 2008. Teaching Assistant, Logic Design for Digital Systems, Winter 2009, Fall 2010. Graduate Student Researcher, UCLA Design Automation Lab, 2006-present.

- 2004–2006 Engineer, Synopsys, Inc., Taipei, Taiwan. Worked on chip-level static and dynamic IR drop analysis and power EM analysis tool, PrimeRail<sup>®</sup>.

- 2009-2010 Engineer, Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan. Worked on ASIC design flows, including decap insertion, signal EM, ERC, and low-power design netlist check.

- 2011 Research Intern, Cisco Systems, Inc., San Jose, California, USA. Worked on SiP power integrity, TSV modeling and its signal integrity, and 3D IC design exploration.

### PUBLICATIONS

Yiyu Shi, **Wei Yao**, Jinjun Xiong, and Lei He, "Incremental and On-demand Random Walk for Iterative Power Distribution Network Analysis," *Asia and South Pacific Design Automation Conference*, 2009.

Wei Yao, Yiyu Shi, Lei He and Sudhakar Pamarti, "Worst Case Timing Jitter and Amplitude Noise in Differential Signaling," *International Symposium on Quality Electronic Design*, 2009.

Wei Yao, Yiyu Shi, Lei He, and Sudhakar Pamarti, "Joint Design-Time and Post-Silicon Optimization for Digitally Tuned Analog Circuit," *International Conference on Computer Aided Design*, 2009.

Yiyu Shi, **Wei Yao**, Lei He, and Sudhakar Pamarti, "Joint Design-Time and Post-Silicon Optimization for Analog Circuits: Case Study using High-Speed Transmitter," *Semiconductor Research Corporation Techcon Conference*, 2009.

Wei Yao, Yiyu Shi, Lei He, and Sudhakar Pamarti, "Timing Jitter and Amplitude Noise Modeling and Estimation for Differential Signaling," *Semiconductor Research Corporation Techcon Conference*, 2009.

Lei He, Shauki Elassaad, Yiyu Shi, Yu Hu and **Wei Yao**, "System-in-Package: Electrical and Layout Perspectives," *Foundations and Trends in Electronic Design Automation*, 2011.

Wei Yao, Yiyu Shi, Lei He, and Sudhakar Pamarti, "Worst-Case Estimation for

Data-Dependent Timing Jitter and Amplitude Noise in High-Speed Differential Link," *IEEE Transactions on Very Large Scale Integration Systems*, 2012.

Wei Yao, Feng Shi, Lei He, Siming Pan, Brice Achkir, and Li Li, "Power-Bandwidth Trade-off on TSV Array in 3D IC and TSV-RDL Junction Design Challenges,", *Electrical Performance of Electronic Packaging and Systems Conference*, 2012.

Wei Yao, Siming Pan, Jun Fan, Brice Achkir, and Lei He, "Modeling and Application of Multi-Port TSV Networks in 3D IC,", reviewed by *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and System, 2012.

### CHAPTER 1

### Introduction

High-speed I/O links for digital communication systems is dramatically developed and improved in this decade. Per-pin bit rate of multi-processor interconnections and processor-to-memory interfaces have been aggressively increased to scale aggregate I/O bandwidth. However, as process technologies are scaled down to finer feature size and circuit applications move to higher frequency bands, analog/mixed-signal design faces several new challenges. First, device models have become increasingly complex in order to capture the physical behavior of nanoscale transistors at high operation frequencies. Also, parasitic couplings become more important and more complex. Moreover, because of the sub-wavelength photo-lithography and random doping fluctuation, process variation become a critical issue and significantly impact the performance of mixed-signal circuit [Ass05], as shown in Fig. 1.1.

As the variation increases along with the technology scaling, tradition corner-

Figure 1.1: CMOS threshold voltage variation

Figure 1.2: Beyond-die Integration Options.

based design methodology is becoming insufficient and may not be viable eventually. Statistical design, on one hand, is proposed to analyze the performance distribution from process variation and defines *parametric yield* as the probability of the design meeting a specified performance or power constraint [BKN03, MSO06]. Today's mixed-signal circuit designs, as a result, not only have to be optimized for nominal performance but also for robustness in order to maintain a reasonable yield.

On the other hand, three-dimensional integration to create multilayer chips (3D ICs) offers an exciting alternative to traditional scaling and provides high integration density, fast signal transmission, low power consumption, and heterogeneous integration opportunities in the "More-than-Moore" era [BSK01, BAC07], as shown in Fig. 1.2. Through-silicon-via (TSV) has been well regarded as a key component in 3D integration, connecting chips vertically with shortened electrical delay and providing extremely dense I/O connections. While TSV fabrication technologies have progressed [PBW08], it is vitally important to understand TSV electrical properties accurately and efficiently for 3D system-performance analysis and subsequent design optimization. At the same time, though TSV could potentially provide thousands of multi-Gb/s I/O and support for tens of Tb/s data bandwidth between local chips due to its short distance and superior signal integrity [LLF12, SCA10], detailed analysis considering various TSV array patterns and geometries with different signaling and termination techniques is still desperately required in order to find a balance between power and bandwidth under different design constraints.

Figure 1.3: Structure of the dissertation, showing how the various topics relate to each other.

The main topics addressed in this dissertation and how they are related to each other are illustrated in Fig. 1.3. The reminder of this dissertation is organized as follows. In order to quickly evaluate the high-speed link's signal integrity performance, an efficient mathematical method is proposed to calculate the worst-case data-dependent jitter and noise for differential signaling. In Chapter 2, we first propose formula-based jitter and noise models considering the combined effect of ISI, crosstalk, and pre-emphasis filter. Moreover, using the formula-based models, we develop mathematical programming algorithms to directly find out the input patterns for worst-case jitter and worst-case amplitude noise. This performance metric can be used for efficient circuit evaluation instead of lengthy simulation and measurements. In Chapter 3, a joint design time and post-silicon optimization framework based on the branch-and-bound algorithm and gradient ascent method is proposed for digitally tuned analog circuits to maximize the parametric yield, subject to power and area constraints. We demonstrate our framework with two examples in high-speed serial link, the transmitter design and the phaselocked-loop (PLL) design. Simulation results show the proposed joint design-time and post-silicon optimization can significantly improve the yield from the design heuristic in analog designers' perspective.

In Chapter 4, a simple yet accurate pair-based model for multi-port TSV networks (e.g., coupled TSV array) is proposed by decomposing the network into a number of TSV pairs and then applying circuit models for each TSV pair. The model is first verified against a commercial electromagnetic solver for up to 20GHz and subsequently employed for a variety of examples for signal and power integrity analysis. Chapter 5 derives a rigorous frequency-dependent circuit model for horizontal coplanar waveguide (CPW) on silicon interposer based on partial equivalent element circuit (PEEC) in layered metal-isolator-semiconductor (MIS) media. Chapter 6 studies the signal integrity issues of TSV-based 3D IC with high-speed signaling based on 3D electromagnetic field solver and SPICE simulations. Power and bandwidth trade-off on TSV array are also analyzed between different signaling and termination techniques, such as single-ended, differential and reduced-swing signaling. Beyond TSV, critical design challenges for the junction structure between TSVs and RDL traces are also revealed and analyzed in Chapter 6 as well.

### CHAPTER 2

# Worst-Case Data-Dependent Jitter and Amplitude Noise for Differential Signaling

### 2.1 Introduction

Differential signaling has been widely used in high-speed I/O interconnect standards like PCI-Express and Serial ATA. It has several advantages, such as a high transmission rate due to low signal swing, little electromagnetic interference (EMI), and common-mode noise immunity. Considerable signal integrity issues, however, still limit the link performance and become bottlenecks during system integration. Such issues include resistive losses, reflections, inductive ringing and crosstalk between differential pairs [SH03, BH05].

To evaluate the combined effect of these impairments on the overall system performance, the associated eye diagram [Hay00,Bre05] has been used as an effective measure. As shown in Fig. 2.1, the eye diagram is defined as the synchronized superposition of all possible realizations of the signal viewed within a particular signal interval. It provides a fast evaluation of system performance. The width of the eye opening defines the time interval over which the received signal can be sampled without error. The height of the eye opening with the amount of amplitude noise at a specified sampling time defines the signal-to-noise-ratio of the received signal [Hay00].

Consider the eye diagram shown in Fig. 2.1. The amounts of timing jitter and amplitude noise determine the width and height of the eye. Jitter is defined as

Figure 2.1: Eye diagram and eye mask

the deviation of the zero-crossing from its ideal occurrence time and decreases the eye's width [KRF05]. Amplitude noise, on the other hand, decreases the signal-to-noise ratio (SNR) and, accordingly, the eye's height. As a result, to determine the performance of the interconnect, we need to consider both timing jitter and amplitude noise simultaneously.

Specifically, inter-symbol interference (ISI) and crosstalk are two major factors that induce jitter and amplitude noise. ISI is defined as one symbol interfering with subsequent symbols and is caused by channel impairments such as attenuation, reflection, and group delay distortion. Crosstalk, on the other hand, is caused by electromagnetic coupling between transmission lines. To counteract ISI, a finite impulse response (FIR) pre-emphasis filter at the transmitter side is widely used to emphasize the signal prior to the impact of the channel [LWT04, TBP05, KLS06]. Pre-emphasized signal, on the other hand, also affects coupled electromagnetic energy and changes crosstalk behavior. As a result, for both ISI and crosstalk, it is important to take pre-emphasis filter into consideration.

Traditionally, the eye diagram is obtained through lengthy time domain simulation with pseudo-random bit sequences as the input data. In the litera-

Figure 2.2: Transceiver block diagram for differential signaling

ture, several types of techniques were proposed to model the eye diagram and tried to efficiently predict the jitter and amplitude noise at the design phase [HST07, PKT07, BAH04, BA04, OFK04, SYZ08]. However, [HST07] considers reflection and attenuation with only one input pattern, and [PKT07] only considers a lossless transmission line. As a result, those models are far from accurate. [BAH04, BA04] and [OFK04] have a better model because they consider lossy transmission lines, but they still take only a few input patterns into account and use an inaccurate linear approximation. To efficiently handle the input patterns in adequate length, [SYZ08] uses the pull-up and pull-down transitions of the signal step response to predict the worst-case eye diagram. This waveform-based method, however, is very sensitive to the transmission environment and only applies to single transmission line without any crosstalk noise. Most importantly, all existing works fail to consider the effect of the pre-emphasis filter, which effectively reduces ISI, as shown in Fig. 2.6 in Section II, but at the same time affects crosstalk.

In this chapter, we first propose formula-based jitter and amplitude noise models that consider the combined effect of ISI, crosstalk, and the pre-emphasis filter for differential signaling. With the same set of input patterns, experiment shows our models achieve within 5% difference compared to SPICE simulation. Note that we apply a RLGC lossy transmission line model according to differential microstrip line geometry, and we represent the channel impairments and crosstalk through transmission line time domain response. By using these formula-based

Figure 2.3: Section of differential microstrip line

models, we then develop algorithms to directly predict the input patterns that cause worst-case jitter and worst-case amplitude noise through pseudo-Boolean optimization and mathematically programming. Moreover, heuristic algorithm is proposed to further reduce runtime. Experiments show our algorithms obtain more reliable worst-case jitter and noise compared to pseudo-random bit sequences simulation and, meanwhile, reduce runtime by  $25 \times$  when using general PBO solver and by  $150 \times$  when using our proposed heuristic algorithm.

### 2.2 Preliminaries

We first review the RLGC model for parallel transmission lines and the frequency domain relationships between input and output ports. Next, an overview of the transmitter pre-emphasis filter is provided and its impact on eye diagram is also demonstrated.

#### 2.2.1 RLGC Model for Transmission Line

A cross-section of the differential microstrip line is shown in Fig. 2.3. We assume the lines are homogeneous, uniform, and parallel to each other without any variation [PKT07]. The dielectric is assumed to be homogeneous with constant permittivity  $\varepsilon$  and permeability  $\mu$ . The distributed self and mutual inductances are computed with the method of images [YNM03]: the effect of the ground plane is replaced with the image currents. The rectangular shapes of conductors were changed into circular ones for geometry simplification and the following expressions were found for the perunit-length self and mutual inductances [YNM03]:

$$l = \frac{\mu}{2\pi} ln \left( 1 + \frac{2H_{eq}}{r_{eq}} \right) \tag{2.1}$$

$$m = \frac{\mu}{4\pi} ln \left( \frac{(s_{eq} + 2r_{eq})^2 + (r_{eq} + 2H_{eq})^2}{(s_{eq} + 2r_{eq})^2 + r_{eq}^2} \right),$$

(2.2)

where  $H_{eq}$ ,  $r_{eq}$ , and  $s_{eq}$  are the equivalent height, thickness and spacing of the differential microstrip line. l is self inductances and m is mutual inductance. The distributed capacitances may be calculated as follows [Pau06]

$$c_p = \frac{\mu \epsilon m}{l^2 + m^2} \tag{2.3}$$

$$c = \frac{\mu\epsilon l}{l^2 + m^2},\tag{2.4}$$

where c is the distributed capacitance between the conductor and the ground and  $c_p$  is the distributed parasitic capacitance between the conductor lines.

By using these analytical parasitics models, the RLGC per-unit-length model for the differential microstrip lines can be established. Note that other fieldsolver-based tools can also be used for RLGC extraction and our jitter and noise modeling and estimation algorithm still apply.

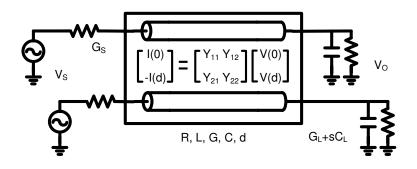

#### 2.2.2 Parallel Transmission Lines

High-speed signal propagation on an interconnect can be influenced by several effects, such as delay, attenuation, reflection, slew rate limitation, and crosstalk. All of these effects, which are also known as transmission line effects [AN01], can be captured by distributed transmission line equations with accurate RLGC perunit-length model. To analyze the three-wire differential signaling, as shown in Fig. 2.4, we first consider the general multiconductor transmission line system. Transmission line characteristics are in general described by Telegrapher's equations and per-unit-length R, L, G, C matrices [AN01, TN92]:

$$\frac{\partial}{\partial x}\boldsymbol{v}(x,t) = -\boldsymbol{R}\boldsymbol{i}(x,t) - \boldsymbol{L}\frac{\partial}{\partial x}\boldsymbol{i}(x,t)$$

(2.5)

$$\frac{\partial}{\partial x}\boldsymbol{i}(x,t) = -\boldsymbol{G}\boldsymbol{v}(x,t) - \boldsymbol{C}\frac{\partial}{\partial x}\boldsymbol{v}(x,t), \qquad (2.6)$$

where  $\boldsymbol{v}$  and  $\boldsymbol{i}$  are voltage and current vectors.  $\boldsymbol{R}, \boldsymbol{L}, \boldsymbol{G}, \boldsymbol{C}$  are the per-unit-length resistance, inductance, conductance, and capacitance matrix for the transmission line. Taking the Laplace transform of (2.5) and (2.6), we can get

$$\frac{\partial}{\partial x} \boldsymbol{V}(x,s) = -\boldsymbol{Z} \boldsymbol{I}(x,s) \tag{2.7}$$

$$\frac{\partial}{\partial x} I(x,s) = -\mathbf{Y} \mathbf{V}(x,s), \qquad (2.8)$$

where Z and Y are the impedance and admittance matrices, given by

$$\boldsymbol{Z} = \boldsymbol{R} + s\boldsymbol{L}, \boldsymbol{Y} = \boldsymbol{G} + s\boldsymbol{C}. \tag{2.9}$$

Further derivation could be achieved through multiconductor transmission line decoupling [Pau06, AN01, TN92] for lossy identical transmission lines. First differentiating the partial differential equations given in equations (2.7) and (2.8) with respect to x, we get following two coupled equations:

$$\frac{\partial^2}{\partial x^2} \boldsymbol{V}(x,s) = -\boldsymbol{Z} \boldsymbol{Y} \boldsymbol{V}(x,s)$$

(2.10)

$$\frac{\partial^2}{\partial x^2} \boldsymbol{I}(x,s) = -\boldsymbol{Y} \boldsymbol{Z} \boldsymbol{I}(x,s).$$

(2.11)

Decoupling of equations (2.10) and (2.11) can be achieved by introducing a transformation matrix  $\boldsymbol{W}$  relating to actual circuit voltage  $\boldsymbol{V}$  and modal voltage  $\tilde{\boldsymbol{V}}$  [AN01].

$$\boldsymbol{V}(x,s) = \boldsymbol{W}\tilde{\boldsymbol{V}}(x,s). \tag{2.12}$$

Using equation (2.12), we could rewritten equations (2.10) as

$$\frac{\partial^2}{\partial x^2} \tilde{\boldsymbol{V}}(x,s) = -(\boldsymbol{W}^{-1} \boldsymbol{Z} \boldsymbol{Y} \boldsymbol{W}) \tilde{\boldsymbol{V}}(x,s).$$

(2.13)

Figure 2.4: Parallel transmission lines

To successfully decouple the equations, the matrix product in parenthesis of equation (2.13) must be a diagonal matrix as

$$\boldsymbol{W}^{-1}\boldsymbol{Z}\boldsymbol{Y}\boldsymbol{W} = \begin{bmatrix} \gamma_1^2 & 0 & 0\\ 0 & \cdots & 0\\ 0 & 0 & \gamma_N^2 \end{bmatrix}, \qquad (2.14)$$

where the transformation matrix  $\boldsymbol{W}$  corresponding to the eigenvectors of product  $\boldsymbol{Z}\boldsymbol{Y}$ . And the resulting diagonal matrix contains the eigenvalues  $(\gamma_1, \dots, \gamma_N)$  of product  $\boldsymbol{Z}\boldsymbol{Y}$ . The solution of equation (2.13) can then be written as

$$\tilde{\mathbf{V}}(x) = [\mathbf{E}(x)]C_1 + [\mathbf{E}(x)]^{-1}C_2,$$

(2.15)

and

$$\boldsymbol{V}(x) = \boldsymbol{W}[\boldsymbol{E}(x)]C_1 + \boldsymbol{W}[\boldsymbol{E}(x)]^{-1}C_2, \qquad (2.16)$$

where  $\boldsymbol{E}(x) = diag[e^{-\gamma_1 x}, \cdots, e^{-\gamma_N x}]$  and  $(C_1, C_2)$  are constants determined by boundary conditions.

Substituting equation (2.16) back to equation (2.7), we have

$$\boldsymbol{I}(x) = \boldsymbol{W}_{\boldsymbol{i}}[\boldsymbol{E}(x)]C_1 + \boldsymbol{W}_{\boldsymbol{i}}[\boldsymbol{E}(x)]^{-1}C_2, \qquad (2.17)$$

where

$$W_i = Z^{-1} W \Gamma \tag{2.18}$$

$$\mathbf{\Gamma} = \begin{bmatrix} \gamma_1 & 0 & 0 \\ 0 & \cdots & 0 \\ 0 & 0 & \gamma_N \end{bmatrix}.$$

(2.19)

Combining equations (2.16) and (2.17) to eliminate constants  $(C_1, C_2)$ , the voltagecurrent relationships between x = 0 and x = d, in frequency domain can be expressed as

$$\begin{bmatrix} I(0) \\ -I(d) \end{bmatrix} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} \begin{bmatrix} V(0) \\ V(d) \end{bmatrix}$$

(2.20)

$$= \begin{bmatrix} W_i E_1 W^{-1} & W_i E_2 W^{-1} \\ W_i E_2 W^{-1} & W_i E_1 W^{-1} \end{bmatrix} \begin{bmatrix} V(0) \\ V(d) \end{bmatrix},$$

where

$$\boldsymbol{E_1} = diag\{\frac{1 + e^{-2\gamma_k d}}{1 - e^{-2\gamma_k d}}\}$$

(2.21)

$$\boldsymbol{E_2} = diag\{\frac{-2e^{-2\gamma_k d}}{1 - e^{-2\gamma_k d}}\}, \qquad k = 1, 2, \dots, N$$

(2.22)

with I(0), I(d), V(0) and V(d) are Laplace transforms of i(0,t), i(d,t), v(0,t)and v(d,t), respectively. Here  $Y_{11}, Y_{12}, Y_{21}, Y_{22}$  form the equivalent admittance matrix or Y-parameters of the transmission line. Please note that the admittance matrix can also be directly obtained from measured response or measured Sparameters.

#### 2.2.3 Pre-emphasis Filter

Using a symbol-spaced finite impulse response (FIR) filter to pre-emphasize the signal at the transmitter end is a common way to counteract ISI. The filter can be expressed as

$$y(n) = \sum_{i=-N}^{M} W_i x(n-i), \qquad (2.23)$$

where  $W_i$  is the coefficient for each filter tap and x(n) and y(n) are the corresponding filter input and output signal. A circuit implementation of the current-mode logic (CML) pre-emphasis driver is shown in Fig. 2.5. The coefficient of each tap is realized by the current source and requires a dedicated differential pair to drive

Figure 2.5: Pre-emphasis filter at transmitter end for CML differential signaling the output. Normally, the number of taps ranges from 2 to 5 because of power and area constraints.

The coefficient of each tap is directly related to the channel characteristic mentioned in the previous sub-section and can be determined adaptively by the least-mean-square (LMS) algorithm [LWT04, TBP05]:

$$W_i^{k+1} = W_i^k + \mu \epsilon_k x_{k-i}, (2.24)$$

where W is the tap coefficient and  $\mu$  is the step size.  $\epsilon_k$  is the error signal and is defined as the difference between the received signal value and the transmitted value. The convergence of errors drives the coefficients to their optimal value.

To demonstrate the effectiveness of the pre-emphasis filter, the eye diagram with and without the pre-emphasis filter is compared in Fig. 2.6. The SNR improvement can be clearly seen. As a result, jitter and amplitude noise models can't capture the actual link performance without considering the existence of pre-emphasis filter.

### 2.3 Jitter and Amplitude Noise Model

The jitter and amplitude noise are actual stochastic processes and can be divided into two categories: random and deterministic. The random part is usually described through a probability density function (PDF) or its root-mean-square

Figure 2.6: Eye diagram (left) without the pre-emphasis filter and (right) with applying a 4-taps pre-emphasis filter

(rms) value. On the other hand, the deterministic part is predictable and makes the dominant contribution to the shape of eye diagram [KHK05].

#### 2.3.1 Subcomponents of Jitter and Amplitude Noise

Take timing jitter as an example, the total jitter (TJ) is subdivided into two categories: random jitter (RJ) and deterministic jitter (DJ). RJ is a random process and is usually assumed to have a Gaussian distribution because it is mainly contributed by thermal noise [OFK04]. In contrast, DJ is repeatable and predictable. The peak-to-peak value of deterministic jitter is bounded due to its predictable nature. Data-Dependent Jitter (DDJ), one of the most important sub-component of DJ, is dependent on the bit pattern transmitted on the link under test and is caused by duty-cycle distortion (DCD) and inter-symbol interference (ISI).

Typical crosstalk noise coupling from adjacent data-carrying links belongs to bounded uncorrelated jitter (BUJ). BUJ is bounded due to finite coupling strength, and uncorrelated because there is no correlation to the channels own data pattern. In this work, we consider the crosstalk from the adjacent differential link and, as a result, the jitter becomes part of DDJ since we exactly know the transmitted data pattern on the adjacent link.

The PDF of data-dependent jitter and noise are always a series of pulses at the locations where a specific bit pattern experiences a cross over. Therefore, in order to get an accurate measure of the worst-case, a large number of bit patterns must be analyzed. As a result, it is critical to find out the worst-case input pattern without doing lengthy simulations. In order to efficiently find out the worst-case, we start with formula-based jitter and noise models in the following subsection.

#### 2.3.2 Modeling of Data-Dependent Jitter and Noise

To start with, we model the CML transmitter shown in Fig. 2.5 as an independent voltage source,  $V_s$ , with matching conductance  $G_s$ . At the receiver end,  $G_L$  and  $C_L$  are used to model the loading conductance and parasitic capacitance of the CML receiver, as shown in Fig. 2.7. Therefore, the termination constraints become

$$V(0) = V_s - \frac{I(0)}{G_s},$$

(2.25)

and

$$I(d) = (G_L + sC_L)V(d), (2.26)$$

and we can derive the frequency domain transfer function using (2.20), (2.25) and (2.26). The result is as follows:

$$V(d) = \tilde{H}V_s(s) = (Y_{12} + (Gs + Y_{11})\tilde{Y})^{-1}Gs \cdot V_s(s), \qquad (2.27)$$

where

$$\tilde{Y} = Y_{21}^{-1}(-Y_{22} - G_L - sC_L).$$

(2.28)

Note that  $G_s, G_L$ , and  $C_L$  are all  $2 \times 2$  diagonal matrices.  $\tilde{H}$  describes the complete two-port relationship and includes the effect of signal distortion, dispersion, reflection and all other channel impairments. The frequency domain relationship

Figure 2.7: Differential signaling with parallel transmission lines and termination between differential input and differential output now becomes

$$H(s) = \begin{bmatrix} 1 & -1 \end{bmatrix} \tilde{H} \begin{bmatrix} \frac{1}{2} \\ -\frac{1}{2} \end{bmatrix}.$$

(2.29)

In order to find the time domain response, (2.29) is approximated into the following pole-residue form:

$$H(s) = c + \sum_{i=1}^{q} \frac{k_i}{s - p_i},$$

(2.30)

by using a least-square-approximation-based method [BS98], where c is a constant, and  $p_i$  and  $k_i$  are the  $i_{th}$  out of q poles and residues of H(s). In this way, the time domain step response s(t) can be obtained through the inverse Laplace transform of H(s)/s and we get

$$s(t) = c \cdot u(t) + \sum_{i=1}^{q} \frac{k_i}{p_i} (e^{p_i t} - 1) u(t), \qquad (2.31)$$

where u(t) is the unit step function.

The received signal r(t) at the far-end of the transmission line now can be expressed as

$$r(t) = \sum_{i=-\infty}^{\infty} b_i p(t - iT), \qquad (2.32)$$

where p(t) = s(t) - s(t - T) is the time-domain response of a non-return-to-zero (NRZ) symbol, and  $b_i$  is the filter's output which can be evaluated as

$$b_i = \sum_{j=0}^{m-1} W_j a_{i+j}, \qquad (2.33)$$

with  $W_j$  as the pre-emphasis filter coefficient and  $a_i$  as the input symbol pattern. m is the number of taps in the filter and is the same as shown in (2.23). Note here we assume the input symbol pattern  $a_i$  is uncorrelated with each other. But any linear data correlation, such as encoded data using block coding, can be taken into consideration and the same problem formulation can be applied when we combine the correlation with the pre-emphasis filter using one sigle linear expression similar to (2.33).

We define the reference time point  $t_0$  as the time when the waveform, without interference from neighboring symbols, crosses a certain threshold  $V_{th}$  [BAH04, BA04]. In other words,  $t_0$  can be solved with

$$p(t_0) = V_{th}, \quad 0 \le t_0 < T.$$

(2.34)

Jitter is the deviation from such a time point. For a given input pattern, the jitter can be computed as

$$|t_1 - t_0|, (2.35)$$

where  $r(t_1) = V_{th}$ . On the other hand, the amplitude noise is defined as the amplitude variation at the optimal sampling time, that is

$$|r(t_s) - p(t_s)|, (2.36)$$

where

$$t_s = \arg\max_t \{p(t)\}.$$

(2.37)

## 2.4 Worst-case Timing Jitter

The data-dependent jitter and amplitude noise highly depend on the input pattern. In this section, we develop algorithms that, by using mathematical programming, can directly find out the input patterns for worst-case jitter and worst-case noise without doing lengthy simulations. To start with, the algorithm for worstcase jitter is proposed in this section.

Figure 2.8: Time domain response of the channel.

#### 2.4.1 Problem Formulation

The worst jitter is the sum of the maximal positive deviation  $t_1 - t_0$   $(t_1 > t_0)$  and the maximal negative deviation  $t_0 - t_1$   $(t_0 > t_1)$ . For simplicity of presentation, we only discuss how to compute the maximal positive deviation. It should be understood that the same procedure can be applied to compute the maximal negative deviation as well. We can formulate the maximal positive deviation as the following integer non-convex programming problem (**P1**)

$$(\mathbf{P1}) \quad \max_{a_i} \quad t_1 - t_0 \tag{2.38}$$

s.t.

$$\sum_{i=-\infty}^{\infty} b_i r(t_1 - iT) = V_{th}$$

(2.39)

$$t_0 \le t_1 < T \tag{2.40}$$

$$b_i = \sum_{j=0}^{m-1} W_j a_{i+j} \tag{2.41}$$

$$a_i \in \{0, 1\},$$

(2.42)

where  $t_0$  is defined in (2.34) given zero-crossing threshold  $V_{th}$ . r(t) is the timedomain response for one-bit transmission as shown in Fig. 2.8.  $a_i$  and  $b_i$  are pre-emphasis filter's input and output with  $W_j$  is the filter's coefficient for tap j.

Note that r(t) attenuates quickly as time goes to infinity, as shown in Fig. 2.8.

Thus (2.39) can be well approximated by

$$\sum_{i=-N}^{N} b_i r(t_1 - iT) = V_{th}, \qquad (2.43)$$

where N can be decided such that the error is within certain bound

$$|b_N r(t - NT)| < |\epsilon r(t)|, \forall 0 \le t < T$$

(2.44)

and  $\epsilon$  is in [0, 1] and is specified by user. A larger  $\epsilon$  reduces the problem complexity, but introduces more significant error.

#### 2.4.2 Relaxation Based Binary Search

Ĵ

If we assign a set of values to  $t_1$ , then the problem becomes a non-linear feasibility problem and can be solved through an efficient heuristic method, i.e., for each value of  $t_1$ , we test whether a combination of the symbols  $a_i$  can be found such that (2.39) holds, and then pick the  $t_1$  that maximizes  $t_1 - t_0$  among all the feasible solutions. Such a problem structure enables us to use the binary search technique on  $t_1$ , which is bounded in  $[t_0, T)$ . However, the main difficulty lies in the fact that the feasible space for  $t_1$  is not continuous. If we randomly assign values to  $t_1$ , the chance for it to be feasible is slim.

To overcome this difficulty, instead of finding a set of symbols that satisfies (2.39), we look for a nearby feasible value as an alternative, if possible. This is done by the following procedure. Suppose  $t_1$  is assigned with value  $\tilde{t}_1$ . Then the corresponding feasibility problem would be

$$\sum_{j=-N}^{N} b_j r(\tilde{t}_1 - jT) = V_{th}$$

(2.45)

$$0 \le \tilde{t}_1 < T \tag{2.46}$$

$$b_j = \sum_{i=0}^{m-1} W_i a_{i+j} \quad -N \le j \le N \tag{2.47}$$

$$a_j \in \{0, 1\} - N \le j \le N + m - 1,$$

(2.48)

#### 2.4.3 Pseudo-Boolean Optimization

We first show how to re-formulate the problem so that we can use a general pseudo-Boolean solver as the core of our binary search algorithm.

Once  $t_1$  is assigned with value  $\tilde{t}_1$  within binary search, the value of  $r(\tilde{t}_1 - jT)$ in (2.45) can be calculated easily and become a known variable to us, denoted as  $r_j$ . Along with (2.47), as a result, the constraints in the original feasibility problem now becomes:

$$\sum_{j=-N}^{N+m-1} c_j a_j = d \tag{2.49}$$

$$a_j \in \{0, 1\} - N \le j \le N + m - 1,$$

(2.50)

where  $c_j = \sum_{k=-N}^{j} r_k W_{j-k}$  and  $d = V_{th}$  are some constants that can be derived from (2.45) and (2.47), given the value of  $\tilde{t}_1$ . The resulted problem becomes that can we find at least one feasible solution, which each  $a_j$  is restricted to either 0 or 1, satisfies a linear equality constraint.

To solve this problem, we can simply relax the equality constraint by adding an error term  $\epsilon$  and convert the equality constraint into two inequality constraints, as shown in problem (P2): (**P2**)

$$(\mathbf{P2}) \quad \min \quad t \tag{2.51}$$

s.t.

$$\sum_{j=-N}^{N} c_j a_j \le d + \epsilon t \tag{2.52}$$

$$\sum_{j=-N}^{N} (-c_j)a_j \le -d + \epsilon t \tag{2.53}$$

$$a_j \in \{0, 1\} \quad t \in \{0, 1\}$$

(2.54)

$$-N \le j \le N + m - 1.$$

(2.55)

Note that an extra variable t is added to convert the feasibility problem into an optimization problem.

(P2) is actually an instance of the pseudo-Boolean optimization (PBO) problem, which generally has the following structure:

$$\min \qquad \sum_{j=1}^{n} c_j \cdot x_j \tag{2.56}$$

$$s.t. \qquad \sum_{j=1}^{n} b_{ij} l_j \le d_i \tag{2.57}$$

$$x_j \in \{0, 1\}, \quad i \in \{1 \cdots m\},$$

(2.58)

where  $x_j$  is a Boolean variable and a literal  $l_j$  denotes either a variable  $x_j$  or its complement  $\bar{x}_j$ . The PBO can be solved by using existing pseudo-Boolean solver. In this work, we use miniSAT+ [ES06], a SAT-based pseudo-Boolean solver, to solve (P2) in our experiment, given the error bound defined by  $\epsilon$ . Note that if a given  $t_1$  value is feasible with error bound  $\epsilon$ , the SAT-based pseudo-Boolean solver returns a feasible input pattern  $\tilde{a}_j$ . Then we can use the pattern to calculate the timing jitter  $t_1$  using (2.43) and use it as the new bound in the binary search algorithm.

Note that due to the complexity of our original problem, there is neither guarantee for optimal solution nor meaningful upper bound of runtime complexity for the combined relaxation-based binary search and pseudo-Boolean optimization. Experimental results, however, show that our algorithm gives more pessimistic result than brute-force enumeration method, yet achieve significant runtime reduction. In the following section, we further propose a heuristic algorithm replacing PBO solver to reduce runtime.

#### 2.4.4 Proposed Heuristic

Instead of solving the feasibility problem through pseudo-Boolean solver, in this section, we propose a heuristic algorithm based on the specific structure of our problem so that we can solve it more efficiently.

To begin with, we first relax the integer constraint (2.48) to

$$0 \le a_j \le 1 \quad -N \le j \le N+m-1, \tag{2.59}$$

and solve the problem  $(\mathbf{P3})$

(**P3**) max

$$\sum_{j=-N}^{N+m-1} |a_j - 0.5|$$

(2.60)

s.t.

$$b_j = \sum_{i=0}^{m-1} W_i a_{i+j} - N \le j \le N$$

(2.61)

$$\sum_{j=-N}^{N} b_j r(\tilde{t}_1 - jT) = V_{th}$$

(2.62)

$$0 \le a_j \le 1 - N \le j \le N + m - 1.$$

(2.63)

The objective function (2.60) tries to find the solution set  $a_j$  that is as close to the integer as possible. For the time being, let's assume that we know how to solve (**P3**). Then we denote the optimal solution as  $\tilde{a}_j$  and round it to 0 or 1. After that, we can get  $\tilde{b}_j$  from (2.61), and insert them in the equation

$$\sum_{j=-N}^{N} \tilde{b}_{j} r(t_{1} - jT) = V_{th}$$

(2.64)

to solve for  $t_1$ , which is close to  $\tilde{t}_1$  and yet is a feasible solution of the original problem. This procedure can now be used as the core for the binary search. The overall algorithm for jitter computation is shown in Algorithm 1, where  $\epsilon_0$  is used to control the termination condition: when the lower bound and upper bound have a difference smaller than  $\epsilon_0$ , the search stops.

Now we discuss how problem (**P3**) can be solved efficiently. For the sake of efficiency, we propose an heuristic to obtain its solution directly from the structure of (**P3**). Let

$$x_j = a_j - 0.5 \quad -N \le j \le N + m - 1,$$

(2.65)

and insert (2.61) into (2.62). Then  $(\mathbf{P3})$  can be transformed into an equivalent

form

$$\max \quad \sum_{j=-N}^{N+m-1} |x_j| \tag{2.66}$$

s.t.

$$\sum_{j=-N}^{N+m-1} c_j x_j = d$$

(2.67)

$$-0.5 \le x_j \le 0.5 \quad -N \le j \le N+m-1, \tag{2.68}$$

where  $c_j$  and d are some constants that can be derived easily.

The incentive of the heuristic to be proposed below is to let as many  $x_i$  take the maximum absolute value as possible. Due to the symmetry of the problem, without loss of generosity, we can assume

$$|c_{-N}| \le |c_{-N+1}| \dots \le |c_k| \le |c_{k+1}| \le |c_{N+m-1}|$$

(2.69)

Then according to this ascending order of  $|c_i|$ , we assign -0.5 or 0.5 as the optimal value  $\tilde{x}_i$  based on the following criteria

$$\tilde{x}_i = \begin{cases} -sgn(c_i) \times 0.5 & \text{if } d - \sum_{j=-N}^{i-1} c_j x_j > 0\\ sgn(c_i) \times 0.5 & \text{otherwise} \end{cases}$$

(2.70)

This assignment is continued until

$$\sum_{j=i+1}^{N+m-1} 0.5|c_j| < d - \sum_{j=-N}^{i} c_j \tilde{x}_j.$$

(2.71)

And the solutions for the remaining  $x_i$  are

$$\tilde{x}_i = sgn(c_i) \times \frac{\sum_{j=-N}^i c_j \tilde{x}_j - d}{|c_i|}.$$

(2.72)

Again, due to the complexity of the original problem, we cannot guarantee that the solution obtained from our algorithm is optimal (or even locally-optimal). However, experimental results show that our algorithm gives a result that is very close or more pessimistic to the enumeration method, yet achieves further speedup compared to using PBO solver. The overall algorithm for solving problem (**P1**) is summarized in Algorithm 1.

Algorithm 1 Algorithm for solving problem (P1).

Initialize:  $t_1^{lb} = t_0$ ;  $t_1^{ub} = T$ ; while  $t_1^{lb} < t_1^{ub} - \epsilon_0$  do  $\tilde{t}_1 = (t_1^{lb} + t_1^{ub})/2$ ; Solve problem (P3) for  $\tilde{a}_i$  and round it to 0 or 1. Compute  $\tilde{b}_i$  based on the rounded  $\tilde{a}_i$  from (2.61); Solve (2.64) for  $t_1$ ; if  $t_1 > t_1^{lb}$  then  $t_1^{lb} = t_1$ ; else  $t_1^{ub} = \tilde{t}_1$ ; Return  $t_1^{lb}$ ;

## 2.5 Worst-case Amplitude Noise

The amplitude noise is the difference between the maximum amplitude deviation and the minimum amplitude deviation, at the optimal sampling time. To find the worst-case noise, we could use the following formulation:

(P4) max or min

<sub>$$a_i$$</sub>  $\sum_{i=-N}^{N} b_i r(t_s - iT)$  (2.73)

s.t.

$$b_i = \sum_{i=0}^{m-1} W_j a_{i+j}$$

(2.74)

$$a_i \in \{0, 1\},$$

(2.75)

where

$$t_s = \arg\max_{t}\{p(t)\}\tag{2.76}$$

is the optimal sampling time. The difference between maximum and minimum deviation determines the peak-to-peak amplitude noise for the eye diagram. Given the  $t_s$  calculated from (2.76), we can rewrite (**P4**) as (use the maximum problem as an example)

$$\max_{a_i} \sum_{i=-N}^{N+m-1} c_i a_i$$

(2.77)

s.t.

$$a_i \in \{0, 1\}$$

(2.78)

where  $c_i = \sum_{k=-N}^{i} r_k W_{i-k}$  and  $r_k = r(t_s - kT)$  can be derived from (2.73) and (2.74). As a result, it is a linear programming problem and, moreover, the solution can be obtained directly without calling the general linear programming solver. Obviously, to maximize the objective function, we just let  $a_i$  be 1 if  $c_i$  is positive and be 0 if  $c_i$  is negative [HWM05]. For the minimum case, it is vice versa. So the amplitude noise can be expressed as

Λ

$$\sum_{i=-N}^{l+m-1} |c_i|, \tag{2.79}$$

and the complexity is  $O(N^2)$  given  $m \ll N$ .

## 2.6 Experimental Results

In this section, we report our experiments on a Pentium 4 computer with 2.66G CPU and 1G RAM.

#### 2.6.1 Jitter and Amplitude Noise Model Validation

We first verify our transmission line channel model. Table 2.1 lists the detailed design information for our various testbench. And Fig. 2.9 shows the comparison of the transient simulation result between our analytical channel model and SPICE simulation for Design 1, given the same RLGC model for channel and the same pre-emphasis filter coefficients. The RLGC value for the channel can be calculated by giving the geometry parameters and using the methods as discussed in Section II.A. For example, the resulted RLGC values for Design 1 are  $r = 17.24\Omega$ , l =325nH, m = 119nH, c = 135pF, and  $c_p = 49pF$ . From Fig. 2.9, we can find out that the transient behavior is pretty similar and both give the same amount of timing jitter and amplitude noise. Note that the origin point is different between SPICE and our model. This is due to different input setting and does not affect the noise and jitter measurement.

Table 2.1: Differential transmission line testbench design information: width(w), spacing(s), thickness(t), dielectric height(h), length(L) and characteristic impedance.

| Design | w    | s      | t    | h    | L    | Char.     |

|--------|------|--------|------|------|------|-----------|

|        | (um) | (um)   | (um) | (um) | (cm) | impedance |

| #1     | 100  | 193.86 | 10   | 300  | 15   | 49.03     |

| #2     | 50   | 117.48 | 50   | 200  | 15   | 49.2      |

| #3     | 50   | 117.48 | 50   | 200  | 25   | 49.2      |

| #4     | 100  | 80     | 10   | 300  | 15   | 52.51     |

| #5     | 50   | 500    | 10   | 300  | 30   | 58.55     |

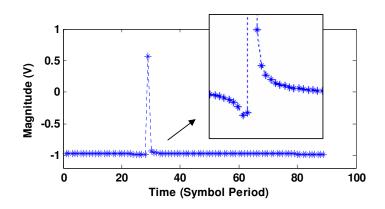

Figure 2.9: Transient simulation comparison between (left) SPICE and (right) our model. The origin point is different.

Next, we verify our jitter and noise model with SPICE given the same set of input patterns in Table 2.2. The test pattern contains 100 symbol with a data rate at 10Gb/s. From Table 2.2, we discover that, given the same input pattern, our model can accurately calculate jitter and noise with similar runtime, compared to SPICE results. The error is within 4.5% for timing jitter and 5% for amplitude noise. Although the runtime improvement is not much, our model is easier to be embedded into other tools or algorithms.

To emphasize the importance of considering a long period of time domain response, Fig. 2.10 shows the time domain response for Design 5, but with unmatched termination resistance. The impedance mismatch at the receiver end

|                     | SPICE  |       |         | Our Model |       |         |  |

|---------------------|--------|-------|---------|-----------|-------|---------|--|

|                     | Jitter | Noise | Runtime | Jitter    | Noise | Runtime |  |

|                     | (ps)   | (V)   | (sec)   | (ps)      | (V)   | (sec)   |  |

| #1                  | 11.8   | 0.27  | 0.26    | 11.9      | 0.27  | 0.17    |  |

| #2                  | 5.0    | 0.20  | 0.26    | 5.0       | 0.21  | 0.17    |  |

| #3                  | 4.6    | 0.20  | 0.25    | 4.7       | 0.19  | 0.16    |  |

| #4                  | 11.0   | 0.29  | 0.26    | 10.5      | 0.30  | 0.17    |  |

| #5                  | 7.7    | 0.11  | 0.23    | 7.7       | 0.11  | 0.18    |  |

| Avg. relative error |        |       |         | 1.1%      | 2.8%  |         |  |

Table 2.2: Jitter and amplitude noise model validation.

Figure 2.10: Time domain response: SPICE simulation(left) and MATLAB simulation with our model(right). The origin point is different.

will cause severe signal reflection. From Fig. 2.10, both SPICE simulation and our model clearly illustrate the signal reflection behavior. As a result, only a few taps of time domain response is not sufficient to determine the jitter and noise performance.

## 2.6.2 Worst-case Jitter and Amplitude Noise Calculation

The worst-case jitter, amplitude noise, and runtime comparison for various design cases are listed in Table 2.3. The pre-emphasis filter is optimized in advance for different channel characteristics. The jitter and amplitude performance is calculated through our formula-based model and we consider 40 taps of transmission line time domain response. We first test 10000 sets of pseudo-random bit se-

Table 2.3: Worst-case jitter, amplitude noise and runtime comparison: PRBS denotes pseudo-random bit sequence. For worst-case jitter, relaxation-based binary search (BS) is used along with pseudo-Boolean optimizer (PBO) or our heuristic algorithm (Heuristic). For worst-case noise, LP denotes directly solving linear programming.

|    | Worst-case Jitter (ps) |        |              | Worst-case Noise (volts) |      | Total runtime (sec) |           |                 |

|----|------------------------|--------|--------------|--------------------------|------|---------------------|-----------|-----------------|

|    | PRBS                   | BS+PBO | BS+Heuristic | PRBS                     | LP   | PRBS                | BS+PBO+LP | BS+Heuristic+LP |

| #1 | 16                     | 15     | 16           | 0.34                     | 0.36 | 37.8                | 1.56      | 0.25            |

| #2 | 8                      | 8      | 8            | 0.25                     | 0.27 | 38.9                | 1.55      | 0.25            |

| #3 | 9                      | 10     | 9            | 0.25                     | 0.30 | 38.2                | 1.56      | 0.26            |

| #4 | 20                     | 25     | 24           | 0.37                     | 0.41 | 37.8                | 1.50      | 0.26            |

| #5 | 12                     | 12     | 12           | 0.14                     | 0.17 | 37.9                | 1.55      | 0.26            |

quences (PRBS) in order to find the worst-case scenario for both jitter and noise. We then use relaxation-based binary search to directly determine the required input pattern for the worst-case jitter and solve the linear programming (LP) problem for the worst-case amplitude noise. Moreover, within the relaxation-based binary search for worst-case jitter, two different methods are compared: pseudo-Boolean optimization (PBO) using miniSAT+ [ES06] and our proposed heuristic algorithm. Table 2.3 shows that, for all the cases, our algorithm obtains more reliable worst-case jitter and noise compared to PRBS simulations. For worst-case jitter, the results are similar no matter we use PBO solver or the proposed heuristic algorithm but the heuristic algorithm provides better runtime. From Table 2.3, it shows our algorithm obtains worst-case jitter and noise by up to 20% bigger than PRBS. At the same time, our algorithm is  $25 \times$  faster than PRBS when we use binary search and PBO solver for worst-case jitter and solve LP for worst-case noise. And  $150 \times$  faster than PRBS when we replace the PBO solver with our proposed heuristic algorithm.

## 2.7 Conclusion

In this chapter, we develop efficient algorithms to calculate the worst-case datadependent jitter and noise directly for a differential microstrip line without lengthy simulation. We first propose formula-based jitter and noise models that consider the combined effect of ISI, crosstalk and the pre-emphasis filter. With the same set of input patterns, our models achieve within 5% difference compared to SPICE simulation. By utilizing these formula-based models, we then use binary search along with pseudo-Boolean optimization and mathematical programming to directly predict the input patterns that cause worst-case jitter and worst-case amplitude noise. Experiments show our algorithms obtain more reliable worst-case jitter and noise compared to PRBS simulation and, meanwhile, achieve a  $25 \times$ runtime reduction when using binary search and PBO solver for worst-case jitter and solving LP for worst-case noise. In addition, by replacing the PBO solver with our proposed heuristic algorithm, a further  $150 \times$  runtime reduction compared to PRBS can be achieved. Note that our modeling and algorithms are not restricted to differential signaling and can be applied to any multiconductor transmission lines.

## CHAPTER 3

# Joint Design-Time and Post-Silicon Optimization for Digitally Tuned Analog Circuits

## 3.1 Introduction

As process technologies scale down to 90nm and below, traditional circuit design methodologies are confronted by the prominent problem of process variation. To deal with process variation for analog circuits, which are highly sensitive to device matching, traditional corner-based design is adopted to guarantee performance in the worst-case scenarios at the cost of substantial circuit overhead. Such cornerbased design methodology, however, is becoming insufficient and may eventually be inviable as variation increases with technology scaling.

Statistical design is proposed to analyze the performance distribution from process variation and defines *parametric yield* as the probability the design meets a specified performance or power constraint. Different techniques exist to maximize the parametric yield for analog circuits and generally fall into two complementary categories: *design-time optimization* and *post-silicon tuning*.

Design-time optimization techniques explore the design space at system-level and device-level to maximize the yield for analog circuits. At system-level, different circuit architectures are explored for a trade-off between power, area, and performance. Moreover, some architectures such as closed-loop negative feedback

Figure 3.1: Examples of digitally tuned analog circuits: (a) CMOS current source and (b) capacitance array.

have good immunity from process variation. On the other hand, the impact of process variation can also be reduced by device-level optimization such as transistor sizing [PDW89] and layout optimization. Design-time optimization, however, has difficulty covering all process corners in a cost efficient fashion and may result in high area/power overhead.