### **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

### **Title**

Parallel Routing for FPGAs with Sparse Intra-Cluster Routing Crossbars

### **Permalink**

https://escholarship.org/uc/item/53x3x96f

### **Author**

Ould Mohamed Moctar, Yehdhih

### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

# Parallel Routing for Field Programmable Gate Arrays With Sparse Intra-Cluster Routing Crossbars

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy in

Computer Science

by

Yehdhih Ould Mohamed Moctar

June 2014

Dissertation Committee:

Dr. Philip Brisk, Chairperson

Dr. Walid Najjar

Dr. Frank Vahid

Dr. Qi Zhu

Copyright by Yehdhih Ould Mohamed Moctar 2014

| The Dissertation of | Yehdhih Ould Mohamed Moctar is approved: |

|---------------------|------------------------------------------|

|                     |                                          |

| -                   |                                          |

|                     |                                          |

| -                   |                                          |

|                     |                                          |

| -                   |                                          |

|                     |                                          |

| -                   |                                          |

|                     | Committee Chairperson                    |

University of California, Riverside

### **ACKNOWLEDGMENTS**

Thanks are due first to my advisor, Philip Brisk, for the guidance, technical advice, and moral support he provided throughout my Ph.D. Philip's enthusiasm and confidence in me were invaluable during my research, and I learned a great deal about how to conduct research him. I would also like to thank the other members of my dissertation committee; Professor Walid Najjar, Professor Frank Vahid, and Dr. Qi Zhu for accepting to be on my dissertation committee and for giving me valuable suggestions.

I would also like to thank the other members of Philip's group – Daniel Grissom, Jeff Mc Daniel, Joseph Tarango, Kennet O'Neal -- for the many insightful discussions they provided. Special thanks are due to Professor Walid Najjar's students; Robert Halsted, Roger Moussaoui, and Robert Skyler for giving me access to their GPU and Multicore servers; that were critical for parallelizing the FPGA router.

I would also like to thank my research collaborators; Professor Guy Lemieux from the University of British Columbia, Professor Keshav Pingali and his student Donald Nguyen from the University of Texas, Austin, and Professor Paolo Ienne and his students Hadi-Parandeh Afshar and Nithin George from l'Ecole Polytechnique Federale de Lausanne (EPFL) for their help in using the Galois deterministic scheduler. I am also very thankful to Dr. Wolfgang Roesner (IBM Fellow) and Vasantha Vuyyuru and the rest of their IBM Electronic Design Automation Group, for giving me the opportunity to present my research and for their valuable advice; and to Dr. Kees Vissers from Xilinx for his insightful advice.

I am very grateful for the support, encouragement and patience of my wife, Oum El Banina, and my son Mohamed Moctar El Yadaly, throughout the years I worked toward my Ph.D. Many thanks are due to my brothers and sisters, and all the members of my extended family. I owe my friends and my extended family a debt of gratitude for their support and encouragement throughout all my years of schooling.

Finally, I appreciate the financial support for this project provided by the Department of Defense in the form of a SMART scholarship.

## **DEDICATION**

To my parents; Aicha Mint Sidiya & Mohamed Moctar El Yadaly. Who always stood behind me and knew I would succeed. Gone now but never forgotten. I will miss them always and love them forever. Thanks for all you did.

#### ABSTRACT OF THE DISSERTATION

Parallel Routing for Field Programmable Gate Arrays With Sparse Intra-Cluster Routing Crossbars

by

#### Yehdhih Ould Mohamed Moctar

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, June 2014 Dr. Philip Brisk, Chairperson

Routing is the most time consuming step of the process of synthesizing an electronic design on a Field Programmable Gate Array (FPGA). It involves the creation of a Routing Resource Graph (RRG); a large data structure representing the physical architecture of the FPGA. In this work, we first introduce two scalable routing heuristics for FPGAs with sparse intra-cluster routing crossbars: Selective RRG Expansion (SERRGE), which compresses the RRG, and dynamically decompresses it during routing, and Partial Pre-Routing (PPR), which locally routes all nets in each cluster, and routes global nets afterwards. Our experiments show that: (1) PPR and SERRGE converge faster than a traditional router using a fully-expanded RRG; (2) they both achieve better routability than the traditional router, given a limited runtime budget; and

(3) PPR uses far less memory and runs much faster than SERRGE, making it ideal for high capacity FPGAs.

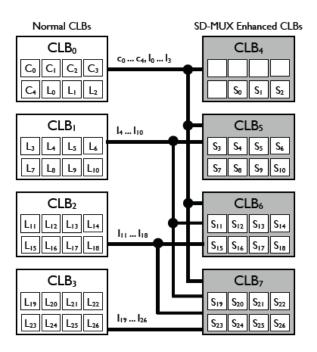

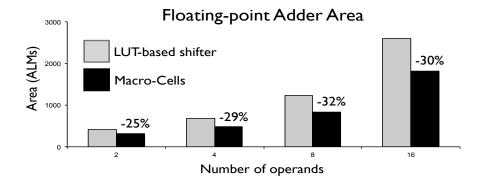

We then introduce a new dynamic-multiplexing based hybrid logic blocks that can be configured to operate as regular configurable logic blocks, or to implement shifting operations required for mantissa alignment and normalization in floating point operations. We show that: (1) the number of CLBs required for shifting operations is reduced by 67%, and if shifting is not required, these hybrid logic blocks can be configured for normal operation, so no functionality is sacrificed; (2) the area overhead incurred by these modifications is small, and (3) there is no negative impact in terms of clock frequency or routability for benchmarks that do not use floating point shifting.

Finally, we investigate the parallelization of FPGA routing on Multicore, shared memory CPUs, using a speculation-based approach. The router is a parallel implementation of PathFinder, which is the basis for most commercial FPGA routers. Our results demonstrate scalability for large benchmarks and that the amount of available parallelism depends primarily on the circuit size, not the inter-dependence of signals. Our experimental results show an average speedup of approximately 5.5x in comparison to the single threaded router implemented in the publicly available Versatile Place and Route (VPR) framework [46].

## TABLE OF CONTENTS

| Acknowled   | dgments                          | iv   |

|-------------|----------------------------------|------|

| Dedication  | ı                                | vi   |

| ABSTRAC     | CT OF THE DISSERTATION           | vii  |

| List of Fig | ures                             | xiii |

| List of Tab | oles                             | xvi  |

| Chapter 1.  | Introduction                     | 1    |

| 1.1 Mo      | otivation                        | 1    |

| 1.2 Ch      | nallenges                        | 2    |

| 1.3 Th      | nesis Approach & Organization    | 5    |

| Chapter 2.  | Background and Related Work      | 7    |

| 2.1 FP      | PGA Architecture                 | 7    |

| 2.1.1.      | Configurable Logic Block (CLB)   | 9    |

| 2.1.2.      | Hybrid Configurable Logic Blocks | 11   |

| 2.1.3.      | FPGA Routing Architecture        | 16   |

| 2.1.4.      | Intra-CLB Routing Crossbars      | 19   |

| 2.2 CA      | AD for FPGAs                     | 23   |

| 2.2.1.      | Overview                         | 23   |

| 2.2.2.      | Placement                        | 25   |

| 2.2.3.      | Routing                          | 28   |

| 2.3 Ro      | outing in Sparse Crossbars       | 38   |

| 2.4 Ro      | outing For Hybrid CLBs           | 44   |

| 2.4.1.      | Fundamental Challenges           | 44   |

| 2.4.2.      | CAD Support For Hybrid CLBs      | 45   |

| 2.5 Par    | allel Routing for FPGAs                                | 46  |

|------------|--------------------------------------------------------|-----|

| 2.5.1.     | Overview                                               | 46  |

| 2.5.2.     | Parallel Routing on Multicore shared memory systems    | 48  |

| 2.6 Sun    | nmary                                                  | 56  |

| Chapter 3. | Routing in FPGAs with Sparse crossbars                 | 58  |

| 3.1 Ove    | erview                                                 | 58  |

| 3.2.1.     | RRG Terminology                                        | 61  |

| 3.2.2.     | Baseline Router                                        | 61  |

| 3.2.3.     | Routing with SElective RRG Expansion (SERRGE)          | 66  |

| 3.2.4.     | Routing with Partial Pre-Routing (PPR)                 | 73  |

| 3.3 Exp    | perimental Setup and Methodology                       | 75  |

| 3.3.1.     | Experimental Platform                                  | 75  |

| 3.3.2.     | Experimental Parameters                                | 75  |

| 3.3.3.     | Timing and Area Models                                 | 77  |

| 3.3.4.     | Benchmarks                                             | 78  |

| 3.4 Exp    | perimental Results                                     | 79  |

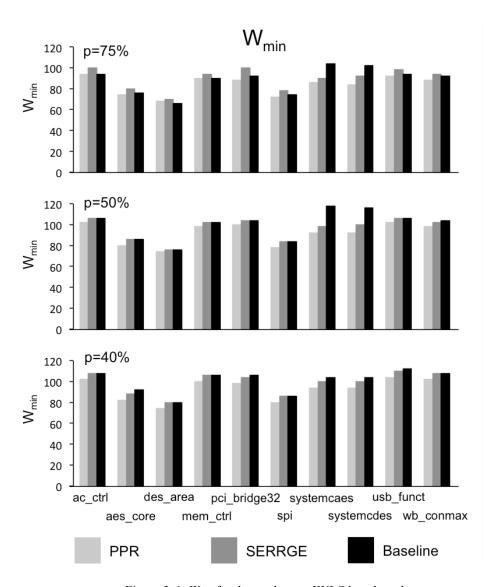

| 3.4.1.     | W <sub>min</sub> and Routability                       | 79  |

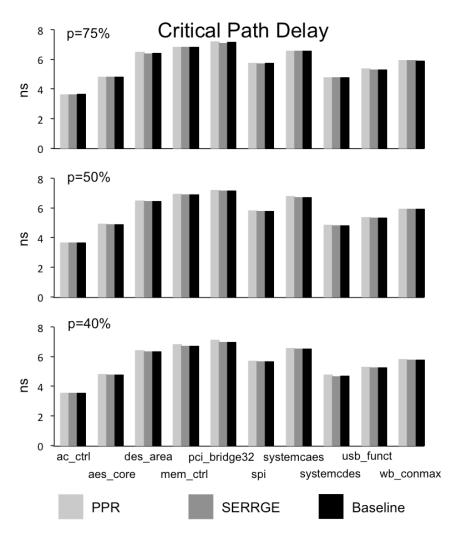

| 3.4.2.     | Critical Path Delay                                    | 81  |

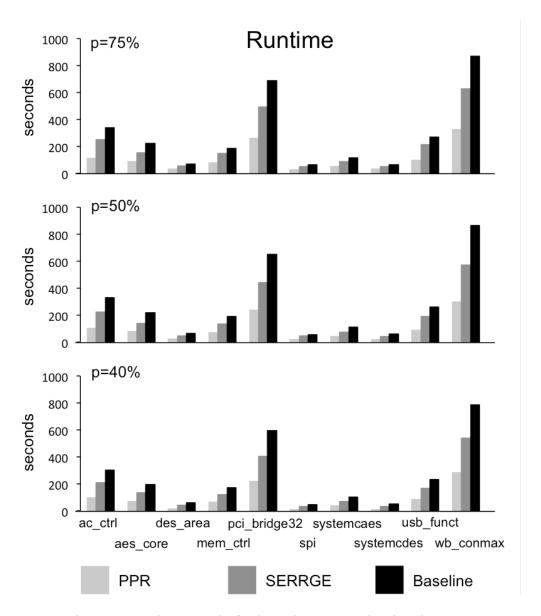

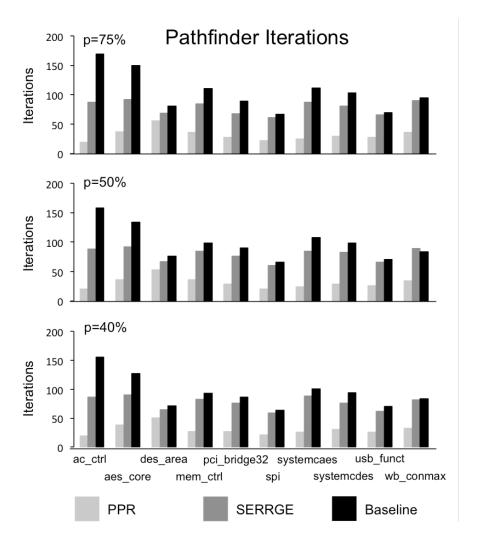

| 3.4.3.     | Runtime and Number of PathFinder Iterations            | 82  |

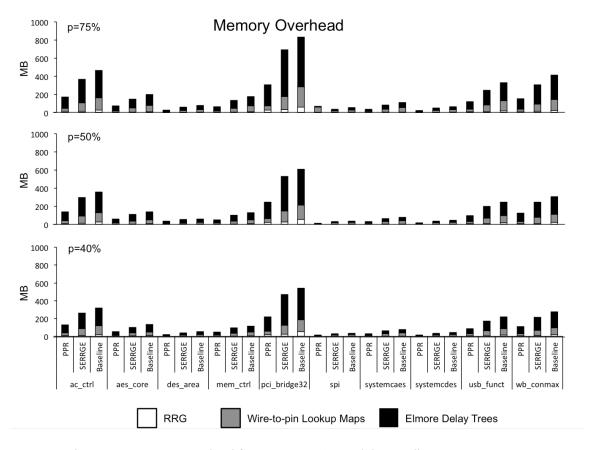

| 3.4.4.     | Memory Consumption                                     | 85  |

| 3.5 Sun    | nmary                                                  | 86  |

| Chapter 4. | A New Hybrid Logic blocks                              | 88  |

| 4.1 Inte   | grating SD-MUXES Into FPGAS                            | 88  |

| 4.1.1.     | Integrating SD-MUXES into the C Block                  | 90  |

| 4.1.2.     | Integrating SD-MUXES Into FPGAS Intra-Cluster Routing  | 94  |

| 4.2 Ens    | suring Routability with Macro-Cells                    | 101 |

| 4.3 CA     | D SUPPORT FOR MACRO-CELLS                              | 101 |

| 4.3.1.     | Programming Model, Assumptions, and Technology Mapping | 102 |

| 4 3 2      | Macro-cell Placement and Routing                       | 103 |

| 4.3.3.     | Global Placement and Routing  | 103 |

|------------|-------------------------------|-----|

| 4.4 EX     | PERIMENTAL RESULTS            | 104 |

| 4.4.1.     | Floating-Point Operators      | 104 |

| 4.4.2.     | Experimental Setup: VPR       | 105 |

| 4.4.3.     | Benchmarks                    | 106 |

| 4.4.4.     | Routability                   | 109 |

| 4.5 Sur    | nmary                         | 111 |

| Chapter 5. | Parallel Routing for FPGAs    | 113 |

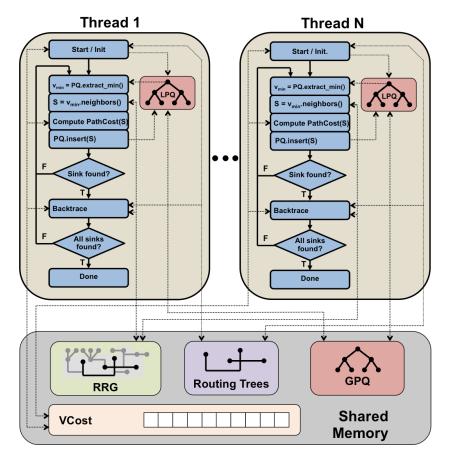

| 5.1 Pat    | hFinder in Galois             | 113 |

| 5.1.1.     | PathFinder components         | 113 |

| 5.1.2.     | The GALOIS framework          | 114 |

| 5.1.3.     | Bottlenecks                   | 115 |

| 5.1.4.     | Optimizations using Galois    | 115 |

| 5.2 PA     | RALLEL PATHFINDER IN GALOIS   | 117 |

| 5.2.1.     | PARALLEL Maze Router          | 117 |

| 5.2.2.     | Maze Expansion Operators      | 118 |

| 5.2.3.     | PARALLEL Signal Router        | 119 |

| 5.3 EX     | PERIMENTAL SETUP              | 120 |

| 5.3.1.     | VPR Implementation in Galois  | 120 |

| 5.3.2.     | VPR Architectural Parameters  | 121 |

| 5.3.3.     | Benchmarks                    | 121 |

| 5.3.4.     | Synthesis Flow                | 122 |

| 5.3.5.     | Experimental Platform         | 123 |

| 5.4 EX     | PERIMENTAL RESULTS            | 123 |

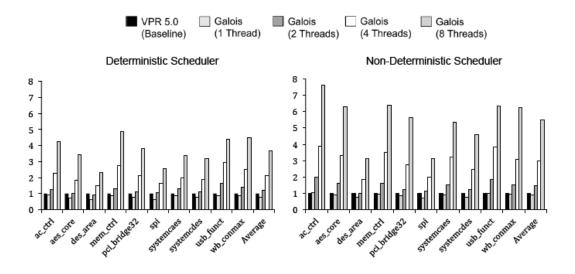

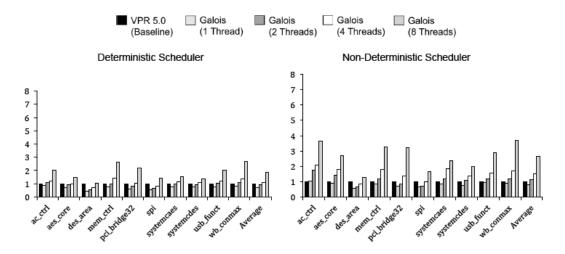

| 5.4.1.     | Routability                   | 124 |

| 5.4.2.     | Speedup                       | 124 |

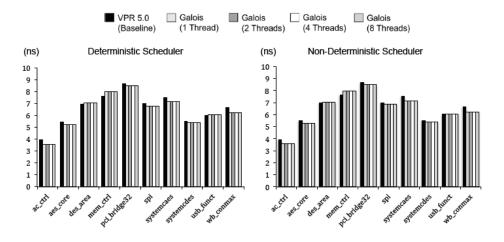

| 5.4.3.     | Critical Path Delay Variation | 126 |

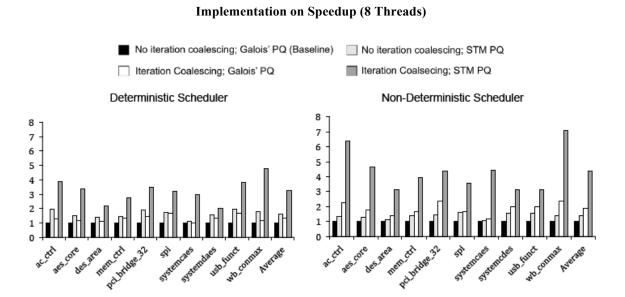

| 5.4.4.     | Implementation Choices        | 127 |

| 5.5 Sur    | nmary                         | 129 |

| Chapte | r 6. Conclusions | 130 |

|--------|------------------|-----|

| 6.1    | Contribution     | 130 |

| 6.2    | Future Work      | 131 |

| Refere | nces             | 133 |

## **LIST OF FIGURES**

| Figure 2-1: Generic Island-style FPGA[1].                                        | 8  |

|----------------------------------------------------------------------------------|----|

| Figure 2-2: SRAM bit cell.                                                       | 9  |

| Figure 2-3: Types of Programmable switches used in SRAM-based FPGAs              | 9  |

| Figure 2-4: SRAM-based implementation of a 2-inpout lookup table (LUT)           | 10 |

| Figure 2-5: The Basic Logic Element (BLE) of an FPGA.                            | 11 |

| Figure 2-6: A Multiplexer in a traditional FPGA routing network.                 | 12 |

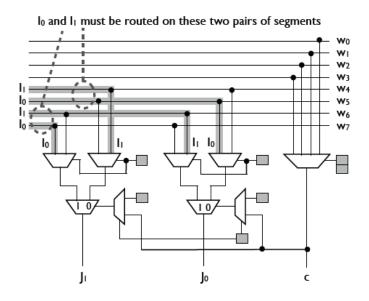

| Figure 2-7: Routing challenges of dynamic multiplexers                           | 15 |

| Figure 2-8: Generic Island-style FPGA.                                           | 17 |

| Figure 2-9: CLB and its adjacent routing channels.                               | 18 |

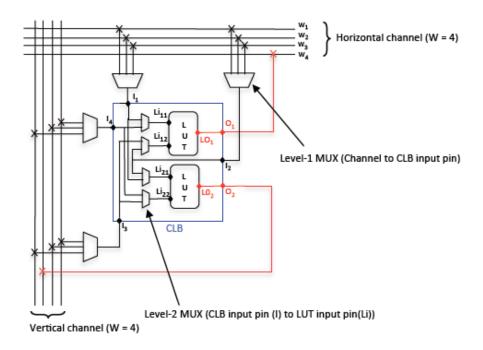

| Figure 2-10: CLBs with sparsely connected intra cluster routing crossbars        | 20 |

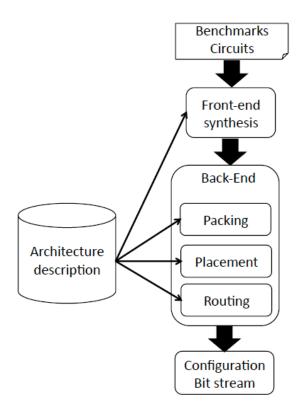

| Figure 2-11: Typical CAD flow for an FPGA.                                       | 24 |

| Figure 2-12: Pseudo-code for the FPGA placement algorithm.                       | 26 |

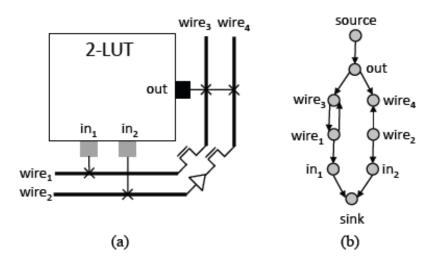

| Figure 2-13: A small FPGA fragment (a) and its corresponding RRG (b)             | 28 |

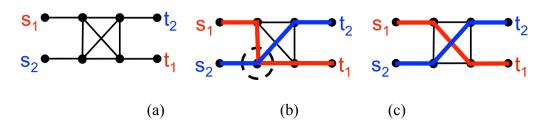

| Figure 2-14: A simple instance of the disjoint path problem.                     | 29 |

| Figure 2-15: Logic equivalency of LUT inputs.                                    | 31 |

| Figure 2-16: Pseudocode for the PathFinder FPGA routing algorithm                | 33 |

| Figure 2-17: Logic equivalency for LUT pins.                                     | 39 |

| Figure 2-18: CLBs with fully connected (a) and sparsely connected (b) crossbars. | 40 |

| Figure 2-19: the maze expansion of a net in the routing resource graph (RRG      | 52 |

| Figure 3-1: RRG expansion for the Baseline router.                               | 63  |

|----------------------------------------------------------------------------------|-----|

| Figure 3-2: (a) Pseudocode to allocate and initialize t wire-to-pin lookup map . | 64  |

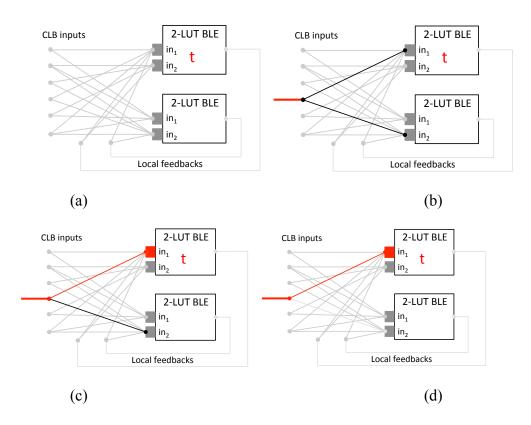

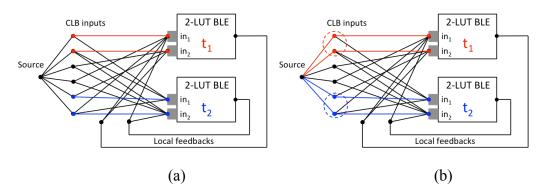

| Figure 3-3: Illustration of the basic behavior of SERRGE.                        | 70  |

| Figure 3-4: Pseudocode to initialize 1-dimensional wire-to-pin map               | 71  |

| Figure 3-5: PPR Intra-CLB routing operation                                      | 73  |

| Figure 3-6: $W_{min}$ for the ten largest IWLS benchmarks                        | 80  |

| Figure 3-7: The critical path delay for the ten largest IWLS benchmarks          | 81  |

| Figure 3-8: Runtime (seconds) for the ten largest IWLS benchmarks                | 83  |

| Figure 3-9: The number of PathFinder iterations                                  | 84  |

| Figure 3-10: Memory overhead for PPR, SERRGE, and the Baseline routers           | 86  |

| Figure 4-1: A C Block modified to implement a conditional swap                   | 90  |

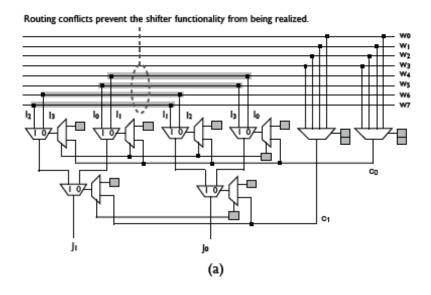

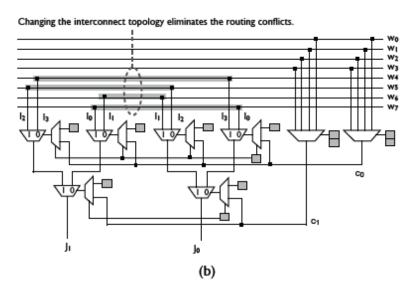

| Figure 4-2: A conflict in the interconnect topology.                             | 93  |

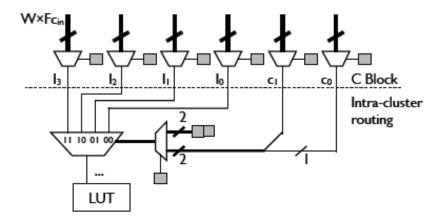

| Figure 4-3: Integrating an SD-MUX into intra-cluster routing                     | 95  |

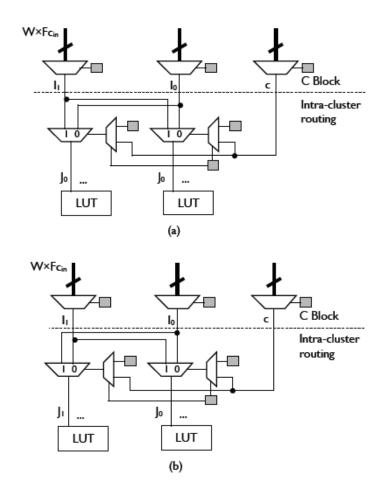

| Figure 4-4: Integrating SD-MUXes into intra-cluster routing.                     | 96  |

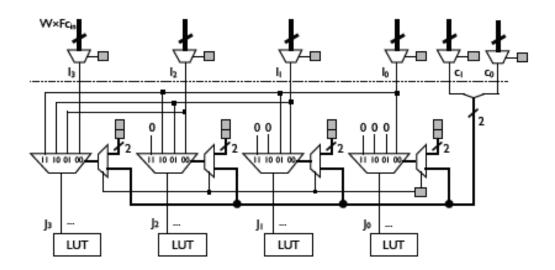

| Figure 4-5: Intra-cluster routing with SD-MUXes to support a 4-bit left shift    | 97  |

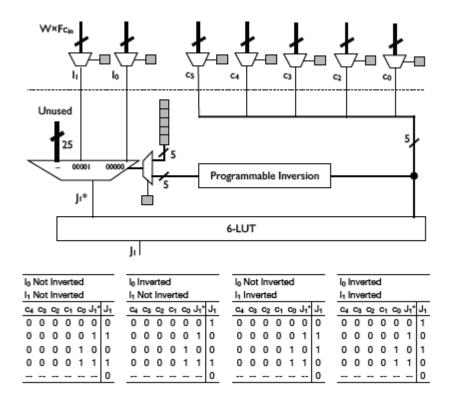

| Figure 4-6: LUT used in conjunction with an SD-MUX                               | 98  |

| Figure 4-7: A macro-cell for a 27-bit shifter.                                   | 102 |

| Figure 4-8: Area savings obtained by macro-cells for 24- and 27-bit shifters     | 106 |

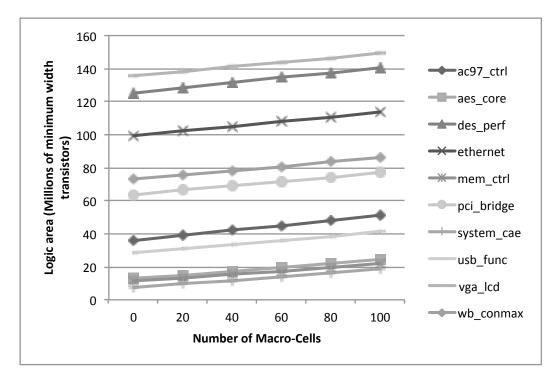

| Figure 4-9: Area of the 10 circuits synthesized using VPR 5.0.                   | 108 |

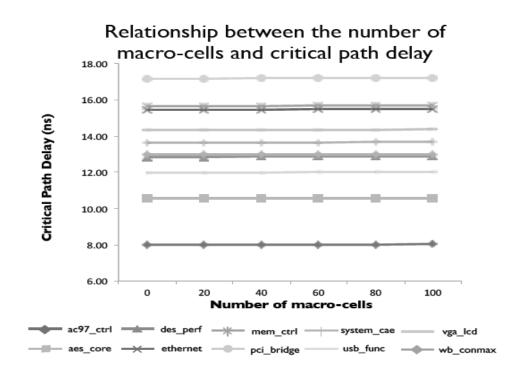

| Figure 4-10: Effects of macro-cells on the critical path delay                   | 110 |

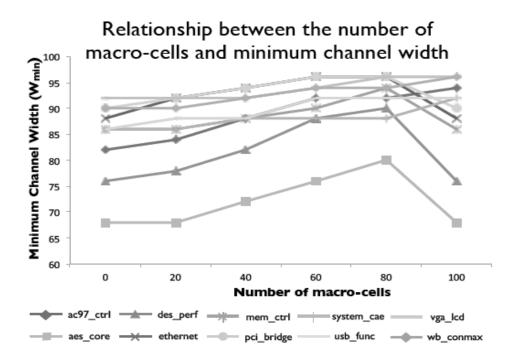

| Figure 4-11: Effects of macro-cells on minimum channel width.                    | 111 |

| Figure 5-1: Multi-threaded parallelization strategy                              | 118 |

| Figure 5-2: Pseudo-code for the Signal router                    | . 120 |

|------------------------------------------------------------------|-------|

| Figure 5-3: Speedup (normalized to VPR 5.0) of the Maze Router   | . 124 |

| Figure 5-4: Speedup (normalized to VPR 5.0) of the Signal Router | . 125 |

| Figure 5-5: Critical path delay for the Maze Router              | . 126 |

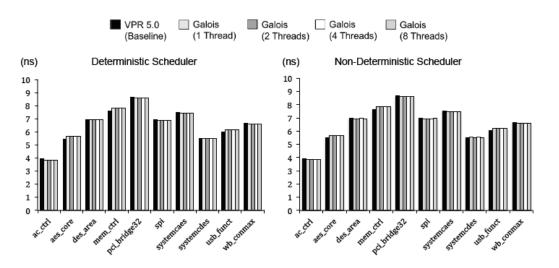

| Figure 5-6: Critical path delay for the Signal Router.           | . 127 |

| Figure 5-7: Normalized speedups for optimized Maze Router.       | . 128 |

## LIST OF TABLES

| Table 3-1: FPGA architectural parameters                      | 76  |

|---------------------------------------------------------------|-----|

| Table 3-2: 10 of the largest IWLS Benchmarks                  | 78  |

| Table 4-1: FPGA architectural parameters                      | 107 |

| Table 4-2: Ten Largest IWLS Benchmarks                        | 107 |

| Table 5-1: FPGA architectural parameters for 65nm CMOS (BPTM) | 121 |

| Table 5-2: Benchmark summary                                  | 122 |

### **Chapter 1. Introduction**

### 1.1 MOTIVATION

Since their inception in the mid-80s, Field Programmable Gate Arrays (FPGAs) have experienced an exponential growth at a rate faster than the rest of the semiconductor industry [14]. They evolved from as little as 64 LUTs (Xilinx XC2064)[11] to as much as over a million LUTs, and a large number of hard-wired macro blocks (embedded memories, DSP blocks, and embedded processors), and high speed IOs in the latest ALTERA and XILINX devices (Stratix 10 and Virtex 7) [3] [76]; an increase of more than 10,000 times in their logic capacity.

These FPGA devices are being used across many industries to implement highly complex system-on-chip (SoC) designs [14], and in many cases as accelerators for many computationally intensive applications. There is also considerable interest in using FPGAs to accelerate scientific applications that are dominated by floating-point computations. Commercial FPGAs currently use dedicated hard blocks such as DSPs and embedded processors for floating point operations. However, applications that are not floating-point intensive will be unable to use these blocks. In this thesis, we investigate an alternative strategy that leverages the abundant spatial parallelism in FPGAs, and provides an optimized floating-point datapath to minimize the size of each operator, as doing so maximizes the number of operators that can be synthesized onto a device of fixed size; which, in turn, maximizes throughput.

To support the design of these complex FPGA architectures, computer-aided design (CAD) tools play a decisive role in delivering high-performance, high-density, and low power design solutions using these high-end FPGAs. However, the process of synthesizing an industrial-scale circuit on a high-capacity commercial FPGA can easily take hours, days or even weeks, depending on the size of the circuit and the target device. This long runtime is one of the biggest concerns to FPGA architects and circuit designers, and a major impediment to the adoption of FPGAs as mainstream accelerators of many computationally intensive applications. Prior research in this area has identified Routing to be the most time consuming step of the CAD process[24]. Consequently, in this thesis we investigate two aspects of the routing problem; routing for FPGAs that employ sparse crossbars in their intra-cluster routing, and parallelizing the router on multicore, shared memory systems.

The focus of this thesis is therefore on investigating logic block architecture to provide better support for floating-point shifters, and exploring different ways of parallelizing and reducing the run time and memory footprint of the routing model for FPGAs with intra-cluster routing crossbars.

### 1.2 CHALLENGES

We are interested in island style FPGAs, consisting of an array of configurable logic blocks, which implement the logic of the circuit, and the programmable routing which allows the logic blocks to be inter-connected. In this thesis we investigate two issues related to the FPGA routing model, and one issue related to the logic block architecture.

The first issue we investigate is routing in FPGAs that employ sparse crossbars in their intera-cluster routing. The process of routing a design on an FPGA is often lengthy and memory-intensive. In particular, the *Routing Resource Graph (RRG)* of a commercial-grade FPGA can be very large, due to the inordinate quantity of uniquely programmable routing resources that are present in the architecture.

One of the significant contributors to overall RRG size is the presence of sparse intra-cluster routing crossbars within the FPGA routing network [20][42][43][73]. In early FPGA generations, intra-cluster routing crossbars were fully connected, which allowed the RRG to implicitly represent them. When the crossbars become sparse, the implicit representation is no longer accurate, so the need to explicitly enumerate their connectivity significantly enlarges the overall RRG size.

Prior research in this area addressed the sparness of crossbars and attempted to provide a model for estimating the routability of sparse crossbars, using analytical and architectural approaches. It didn't however, investigate how routing is performed in FPGAs with intra-cluster routing crossbars.

The second issue we investigate is the enhancement of the configurable logic block to provide better support for floating-point shifting operations. This involves the introduction of dynamic multiplexing in the intra-cluster routing fabric of certain logic blocks. Dynamic multiplexing gives the FPGA programmer the ability to configure the SRAM bits of a multiplexer, after they have been set by the routing model. Even tough this technique can be beneficial for circuits that require a significant amount of

multiplexing, it comes at a non-negligible cost, and creates new challenges for physical design tools. The following issues must be addressed in order to justify the inclusion of dynamic multiplexers in an FPGA fabric:

- (1) Given that FPGA routing networks consume as much as 90% of on-chip area [7], is the area overhead of replacing static multiplexers justifiable?

- (2) When multiplexers are configured for dynamic control, how can the router overcome the lack of flexibility arising from the fact that input signals must be routed to multiplexer inputs in a pre-specified order? How is routability achieved in the general case?

- (3) How are the dynamic control bits generated, and how are they routed?

Our work address these issues using a CAD-driven architectural approach that evaluates the tradeoffs in terms of area and delays associated with the introduction of dynamic multiplexing into the intra-cluster routing of the FPGA.

The last issue addressed in this thesis is the reduction of CAD runtime through the parallelization of FPGA routing. Among the different stages in a typical CAD flow, *routing* is often the most significant in terms of runtime and performance, since it directly affects the achievable clock frequency. Practically, all commercial FPGA routers have their origins in the *PathFinder* algorithm, introduced in 1995 by McMurchie and Ebeling [50]. PathFinder employs an algorithmic approach called *negotiated congestion*, in which individual nets in the user circuit are allowed to share FPGA routing resources; as the algorithm proceeds, the negotiation process ensures that at most one net is routed along each resource.

The challenges associated with parallelizing PathFinder depend primarily on the strategy used, and the underlying hardware architecture. At a coarse-grained level, one can route the nets in parallel and use a shared congestion map to control the negotiation process. The biggest challenge of this approach is to introduce an efficient mechanism to handle contention and communication among concurrent threads. At the fine-grained level, nets can be routed serially, while parallelizing the maze expansion of individual nets. As the maze expansion is typically a directed breadth-first or A\* search on the RRG, the main concern is finding a mechanism for implementing the priority queue such that it is optimized for multithreading operations.

In this work we investigate parallelizing at both levels (coarse-grained & fine-grained) on multicore, shared memory CPU architectures.

### 1.3 THESIS APPROACH & ORGANIZATION

The research approach used in this thesis is experimental; we have selected circuits from the 2005 IWLS benchmark suite [28]. We used ABC for logic optimization and technology mapping [6]. We then incorporated our enhancements and modifications into the academic Versatile Place and Route (VPR) physical design tool [46], and use it to pack, place and route our design circuits. We evaluate our approaches using FPGA architectures from the iFAR repository [33][34] made public by the University of Toronto, and report area models and delay estimates provided by VPR.

The next chapter provides background information and details some of the previous work in both the relevant areas of CAD and FPGA architecture. Chapter 3 describes the

two approaches we introduced to perform routing in FPGAs that employ sparse crossbars in the intra-cluster of their logic blocks. In Chapter 4 we detail the enhancement we have made to dynamically reconfigure the logic blocks in order to reduce the cost of floating point mantissa alignment and normalization in FPGAs. Chapter 5 presents our speculation-based model for parallelizing an FPGA router on multicore, shared memory CPU architecture. The final chapter summarizes the thesis conclusions and provides suggestions for future work.

## Chapter 2. BACKGROUND AND RELATED WORK

This chapter provides background information about FPGA architecture, and the CAD flow used to automatically map circuits into FPGAs that employ sparse crossbars in their Configurable Logic Blocks (CLBs). It also presents the fundamental concepts and techniques of parallel computing essential to parallelizing an FPGA router on multi-core, shared memory CPU architectures, and briefly describes the prior work relevant to this thesis.

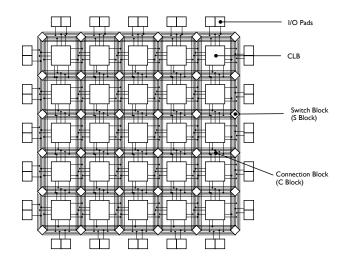

### 2.1 FPGA ARCHITECTURE

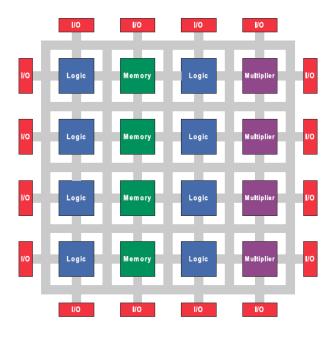

The architecture of a modern FPGA as depicted in **Figure 2-1**, consists of an array of inter-connected programmable logic blocks surrounded by programmable input/output (I/O) blocks. The main components of this architecture are the configurable logic blocks (CLBs), the memory and multiplier blocks, the I/O blocks, and the programmable routing fabric. Mapping a design on an FPGA involves configuring the programmable logic blocks to implement the logic required by the design and using the I/O blocks as input and output pads for interfacing with external devices. The programmable routing fabric allows the logic blocks and I/O blocks to be programmatically interconnected.

Figure 2-1: Generic Island-style FPGA[1].

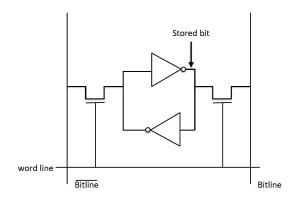

FPGAs are programmed by configuring the switches of the CLBs and the programmable routing fabric, using one of three techniques; SRAM-based, Flash-based, or Anti-fuse [7]. Among these techniques, SRAM-based is the most popular, and it is the technology of choice of Xilinx and Altera; the two major commercial FPGA vendors[2][75]. Consequently, in this thesis we will only investigate the SRAM-based FPGAs. Basically, this technology makes FPGAs programmable by using SRAM cells to control pass transistors, multiplexers and tri-state buffers in order to configure the programmable routing and logic blocks as required. These SRAM cells are stored in static memory as an array of latches. **Figure 2-2** shows these SRAM-based switches. The next section briefly describes how the logic blocks are configured using the SRAM cells. Sections 2.1.2 and 2.1.3 then describe some of the different architectures and prior

research into FPGA logic blocks and routing, respectively.

Figure 2-2: SRAM bit cell.

Figure 2-3: Types of Programmable switches used in SRAM-based FPGAs[7].

### 2.1.1. CONFIGURABLE LOGIC BLOCK (CLB)

The purpose of a logic block in an FPGA is to provide the basic computation and storage elements used in digital logic systems. Even though many different logic blocks have been used to provide this functionality, most current commercial FPGAs are using configurable logic blocks based on look-up tables (LUTs)[3][4][76]. In this CLB

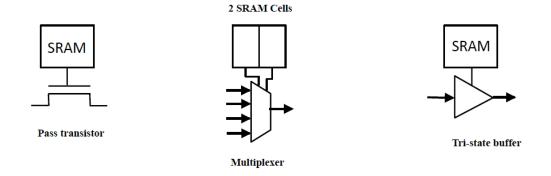

architecture, the atomic unit is a K-input LookUp Table (K-LUT); **Figure 2-3** shows how a 2-input LUT can be implemented in an SRAM-based FPGA, a k-input LUT requires 2<sup>k</sup> SRAM cells and 2<sup>k</sup>-input multiplexers. A k-input LUT can be configured to implement any K-input, 1-output logic function; one simply programs the 2<sup>k</sup> SRAM cells to be the truth table of the desired function[7].

Figure 2-4: SRAM-based implementation of a 2-inpout lookup table (LUT)

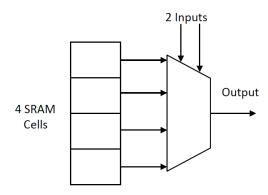

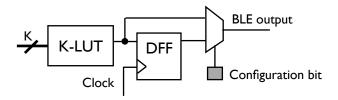

A Basic Logic Element (BLE) is a K-LUT coupled with a bypassable flip-flop, as shown in Figure 2-5. BLEs are clustered in groups called Configurable Logic Blocks (CLBs). Each CLB contains N BLEs, along with an intra-cluster routing crossbar. In early FPGAs, the intra-cluster routing crossbar was fully connected; in more recent devices, it has become sparse [43]. Section 2.1.3 provides detailed discussion about the architecture of the routing fabric; including the intra-cluster routing crossbars. The next section presents some modifications to the intra-cluster routing multiplexers, which can reduce the number of CLBs required to implement floating point adders by 67%.

Figure 2-5: The Basic Logic Element (BLE) of an FPGA.

### 2.1.2. HYBRID CONFIGURABLE LOGIC BLOCKS

We have introduced a new type of logic blocks that can be configured to operate as regular configurable logic blocks, or to implement shifting operations required for mantissa alignment and normalization in floating point operations. If the logic block is configured for shifting operations, the routing MUXes of the intra-cluster routing crossbar are used in conjunction with the LUTs of the logic block to implement shifting operations. This configuration is made possible by the use of dynamic multiplexing; a technique that gives the FPGA programmer a direct control over the intra-cluster routing MUXes. This is a deviation from traditional FPGA Multiplexing that place the Multiplexers under static control, i.e. once configured after routing, they cannot be reconfigured until the FPGA is reprogrammed. The next section describes this technique and give a motivating example showing the potential area savings resulting from using these hybrid blocks to implement floating point shifters.

#### 2.1.2.1. STATIC VS DYNAMIC MULTIPLEXING

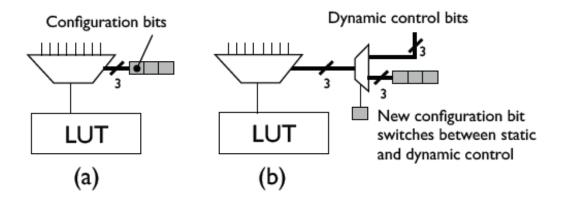

Statically controlled MUX (S-MUX) is a multiplexer controlled by the FPGA bitstream, and is not generally accessible to the programmer. In contrast, dynamically

controlled MUX (D-MUX) is a multiplexer that can be configured by the programmer. An SD-MUX is a multiplexer that can be configured by the programmer to be either S-MUX or a D-MUX. One way to make S-MUX accessible to the FPGA programmer is to add dynamic configurability as shown in **Figure 2-6** (b). Figure **Figure 2-6**(a) shows a traditional FPGA MUX that is statically controlled by the configuration bitstream; in Figure **Figure 2-6** (b) the static MUX is extended so that it can be dynamically configured as an S-MUX or a D-MUX. In the next section we show that this hybrid configuration of the MUXes can convert the CLB to implement a shifter. So, converting the S-MUXes of the intra-cluster routing of a CLB into SD-MUXes results in a new, hybrid CLB architecture accessible by the programmer. The next section presents a motivating example showing how this hybrid CLB can be configured to implement a floating-point shifter significantly reducing the number of CLBs.

Figure 2-6: A Multiplexer in a traditional FPGA routing network.

### 2.1.2.2. Converting Hybrid Blocks to Implement Shifters

Shifters implemented as a Multiplexer-based logic maps inefficiently onto LUTs [52]. This inefficiency can however be reduced significantly by using the intra-CLB routing MUXes in conjunction with LUTs to implement the shifters required for mantissa alignment and normalization in floating-point addition. As a motivating example, consider the 8:1 multiplexer shown in **Figure 2-6**(a), which drives one input of a LUT; the other LUT inputs are driven by similar multiplexers, which are not shown. Three FPGA configuration bits drive the multiplexer's selection inputs. The purpose of this multiplexer is to provide some flexibility to the FPGA CAD tools—in particular, the router -when synthesizing a circuit onto the FPGA. In this case, there are 8 physical wires within the FPGA that can connect to this LUT input, via the multiplexer. One signal must route to that particular LUT input, and the router is given 8 possible wires to use. Once the route is complete, the configuration bits are set to select the chosen wire. This configuration is *static*, i.e., it does not change until the FPGA is reprogrammed. As there is no possibility to dynamically drive the selection inputs of this multiplexer, there is no possibility for the user to utilize it as an actual 8:1 multiplexer. As it is not architecturally visible, the typical user—who is not an FPGA architect—will be completely unaware of its existence

As illustrated in **Figure 2-6** (b), a *Static-Dynamic Multiplexer (SD-MUX)* can be configured for either static or dynamic control. A 2:1 multiplexer now drives the configuration inputs of the 8:1 multiplexer. The 2:1 multiplexer can select either the control bits or a set of wires that are available to the user to provide dynamic control. An

extra configuration bit drives the selection input of the 2:1 multiplexer, thus allowing the user to configure the 8:1 multiplexer to provide either static or dynamic control. This basic idea easily generalizes to a multiplexer with any number of inputs, as long as a sufficient number of control bits are provided. When the SD-MUX is configured to provide static control, one signal can be routed to any of the 8 multiplexer inputs, and the configuration bits are set accordingly, as noted earlier, this provides flexibility to the router, as there is fierce competition for routing resources. When the SD-MUX is configured as a dynamic multiplexer, as shown in **Figure 2-7**(b), 8 signals are routed to the 8 multiplexer inputs in pre-specified order; e.g., if the user logic expects the multiplexer to select signal *x* when the selection bits are 010, then *x* must be routed to multiplexer input 010 in order to preserve this functionality; thus, the flexibility afforded to the router in the static case is sacrificed.

If we assume that the multiplexers in the routing network are 27:1 or larger, then 24 of them can implement mantissa alignment, and 27 can implement normalization. If we ignore the other LUT inputs, and configure the LUT to implement the identity function, then these two shifters can be implemented using 51 LUTs: a savings of 66.7% over the LUT-based implementation. Chapter 2 presents a solution that realizes this best-case savings.

Under static control, one signal can route to any of the 8 multiplexer inputs.

Under dynamic control, 8 signals must route to the 8 multiplexer inputs in the correct order.

How are the dynamic control signals generated and how are they routed into the dynamic multiplexer?

(a) (b)

Figure 2-7: Routing challenges of dynamic multiplexers.

The goal of converting CLBs to implement shifters is to reduce the cost of mantissa alignment and normalization in floating-point operations. One alternative is to integrate floating-point units as hard blocks [5][30][36]; however, applications that are not floating-point intensive will be unable to use these blocks. To date, FPGA vendors do not sell device families with dedicated blocks for floating-point applications.

Beauchamp et al. [5] advocate integrating hard shifters or 4:1 multiplexors in parallel with FPGA logic; however, when the shifters are not used, the nearby routing resource are wasted; and when the 4:1 multiplexors are used, significant routing resources are still required to form large shifters.

Shifters and multiplexers can be synthesized onto multipliers in the DSP blocks [30][21], and Xilinx has added 17-bit barrel shifters to their DSP48E1 blocks [72]; however, a DSP block used for shifting, cannot perform other operations. Benchmarks that require multiplication and shifting can still benefit from FPGAs containing DSP blocks and macro-cells. Floating-point datapath compilers use arithmetic transformations

to synthesize floating-point operations efficiently on FPGAs [18][36][37]; reducing the cost of normalization is one of their goals. These compilers achieve better performance and logic density than using 2-input operators, but they sacrifice IEEE compliance. Our approach is amenable to IEEE-compliant operators. A patent by Kaviani (*Xilinx*) [32] exposes the selection bits of C block multiplexers to the programmer; the idea is similar to Xilinx Virtex FPGAs, which do not have intra-cluster routing. No CAD tools are described, so the affect on routability is unknown. The next section presents the FPGA routing architecture, and illustrates the approach employed to model the intra-cluster routing resources in order to realize the hybrid CLB architecture.

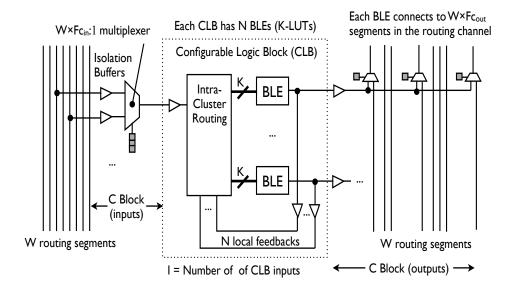

### 2.1.3. FPGA ROUTING ARCHITECTURE

The routing fabric of an island-style FPGA can be viewed as a network of interconnected MUXes that is divided into two parts: the Intra-CLB routing, which is used to route signals from CLB input pins and feedbacks (i.e., BLE outputs in the same cluster) to LUT inputs; and the *inter-CLB routing*, which is used to route signals from BLE outputs to their destination clusters (or specifically, the routing tracks that drive the destination clusters). In this thesis we adhere to the inter-CLB routing architecture used in VPR [46], but present an intra-CLB routing model completely different from VPR, that share some similarities with the work of Guy and Lewis in [43], and Feng and Kaptanoglu [20]. The inter-CLB routing is a single connected structure for the whole device, while there is one intra-CLB routing for each cluster. **Figure 2-8** depicts an island style FPGA in which the Configurable Logic Blocks (CLBs) are surrounded by routing channels of pre-fabricated wiring segments on all four sides. A Connection Block (C

Block) of programmable switches connects each CLB input or output pin to a subset of the wires in the adjacent routing channel. **Figure 2-8** illustrates the FPGA floorplan. Switch Blocks (S Blocks) are programmable intersections between horizontal and vertical routing channels. They are simply a set of programmable switches that allow some of the wire segments incident to the switch block to be connected to other segments. By turning on the appropriate switches, short wire segments can be connected together to form longer connections.

Figure 2-8: Generic Island-style FPGA.

The multiplexers, shown on the right-hand side of Figure 2-9, are implemented in the S Blocks, which are shown (without detail) in Figure 2-9. Figure 2-9 depicts inputs coming in from the left hand side of the CLB and outputs leaving to the right; in actuality, inputs and outputs may enter and exit from all four sides.

Figure 2-9: CLB and its adjacent routing channels.

Configurable Logic Block (CLB) contains several BLEs with fast local interconnect provided by the intra-cluster routing crossbar; the Connection Block (C Block) inputs and outputs interface the CLB with the global routing network Figure 2-9.

We use the same notation employed in VPR [46], originally introduced by Brown and Rose [9], for describing some of the parameters of an FPGA's routing architecture. The number of LUT inputs (LUT size) is denoted K, and N is the number of LUTs per CLB (Cluster size). I is the number of CLB input pins, and W denotes the number of segments per routing channel. The number of wires in each channel to which a logic block pin can connect is called the connection block flexibility, or  $F_c$ . The number of wires to which each incoming wire can connect in a switch box is called the switch block flexibility, or  $F_s$ . Each C Block input multiplexer in Figure 2-9 selects one of W×Fc wires, and each

BLE drives W×Fc<sub>out</sub> segments in the adjacent routing channels. Most FPGAs use single driver routing [7], so the C Block output is a conceptual description of the routing topology.

Prior work conducted by Vaughn Betz and Jonathan Rose in [7] and implemented in VPR [46], has extensively investigated the inter-CLB routing architecture, including the tradeoffs between the different parameters of this architecture, but only considered fully connected intra-cluster routing crossbars. In this work, we use their inter-CLB model but investigate the use of sparse crossbars in the Intra-cluster routing of the FPGA. The next section presents our proposed sparse crossbar model and section 2.3 describes the routing approaches we introduce for FPGAs with sparse intra-cluster routing crossbars.

### 2.1.4. INTRA-CLB ROUTING CROSSBARS

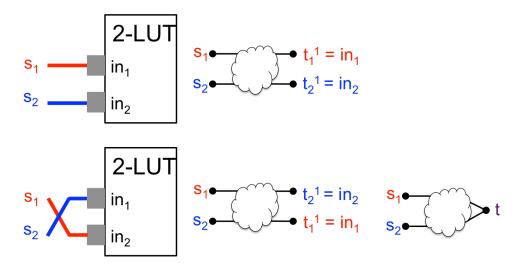

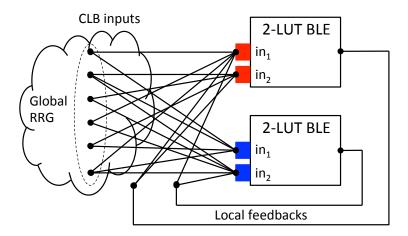

Intra-cluster routing crossbar can be viewed as a network of MUXes connecting the CLB pins to the LUT pins. Fully connected crossbars guarantee that there is a path in the intra-cluster routing network from each CLB pin to each LUT pin. When the crossbars are sparse this full connectivity is no longer guaranteed. **Figure 2-10** show the Intra-cluster connectivity pattern; **Figure 2-10**(a) depicts a fully connected crossbar, while **Figure 2-10**(b) shows a sparse crossbar.

Figure 2-10: CLBs with sparsely connected intra cluster routing crossbars.

We model this intra-cluster routing connectivity as a 2-dimensional binary matrix B, with I+N columns and KN rows. Each column corresponds to an input (a CLB input pin or a local feedback from a BLE in the cluster), and each row corresponds to a BLE input. B(i,j)=1 if a signal can route from input i to BLE input j, and 0 otherwise. It is important to note that B simply models the CLB-input-to-BLE-input connectivity of the crossbar, but does not model its internal architecture.

As an example, we model a CLB with N=2, K=2 (e.g., it contains two 2-LUTs); the four BLE inputs are denoted  $b_{00}$ ,  $b_{01}$ ,  $b_{10}$ , and  $b_{11}$ . The CLB has three input pins,  $I_0$ ,  $I_1$ , and  $I_2$ , and two local feedbacks from the BLEs,  $O_0$  and  $O_1$ :

$$B = \begin{bmatrix} 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} b_{00} \\ b_{01} \\ b_{10} \\ b_{11} \end{bmatrix}$$

In this example, there is a connection from CLB input pin  $I_0$  to LUT input pins  $b_{00}$  and  $b_{01}$ , but not  $b_{10}$  and  $b_{11}$ ; also, the local feedbacks are not used.

We used a tool developed by Lemieux et al. [42] to generate routable sparse crossbars with a user-provided density function p. The tool generates matrix B such that each row, column, and the entire matrix all have a population percentage of approximately p, i.e.:

$$\sum_{j} B(i,j) = \lceil p(I+N) \rceil \pm 1 \qquad (2.1)$$

$$\sum_{i} B(i,j) = \lceil pkN \rceil \pm 1 \text{ , and } \qquad (2.2)$$

$$\sum_{i,j} B(i,j) = [pk(I+N)] \pm 1$$

(2.3)

Now that we have a logical mapping between the CLB pins and LUT pins we can model crossbars of any density and extend the routing resource graph to include the routing resources of these crossbars.

In the past decade, there has been some interest in investigating FPGAs that employ sparse crossbars in their intra-cluster routing, Lemieux et Lewis presented an algorithm to generate and evaluate routable sparse crossbars [42], and later proposed their usage for FPGA with intra-cluster routing; to improve routability they added spare CLB input pins [43]. Later work by Feng and Kaptanoglu [20] used entropy counting to design intra-cluster routing crossbars that offer greater routability; however, there is concern that CLB inputs and local feedbacks cannot reach fast inputs for LUTs with non-uniform delay [20].

Ye [73] showed how the equivalence of LUT inputs can be leveraged to reduce the population density of the intra-cluster routing crossbar without compromising routability; however, it is unclear if this approach is compatible with more advanced logic block features such as fracturable LUTs and carry chains, where LUT inputs can no longer be treated as logically equivalent. Chin and Wilton [16] extended Ye's work to investigate high-capacity hierarchical CLBs with multi-layer sparse crossbar interconnects, and showed that this approach reduced the placement and routing problem sizes significantly, thereby yielding faster and more robust CAD algorithms.

In terms of commercial FPGAs, Xilinx employs a C-block (**Figure 2-1**) without an intra-cluster routing crossbar, while Altera and Microsemi (formerly Actel) employ an intra-cluster routing crossbar in conjunction with a C-block. We presume that Xilinx's C-block is much denser than Altera's or Microsemi's, although no formal comparative study has been published, to the best of our knowledge.

Altera has disclosed that their Stratix-series devices employ a sparse intra-cluster routing crossbar [43]; although no details regarding the topology were presented. Microsemi disclosed that their FPGAs employ a 3-layer Clos network, where the third layer is subsumed by LUTs [42].

None of the previous work, however, investigated how routing is accomplished in the presence of sparse crossbars; section 2.3 briefly describes the proposed routing heuristics, and Chapter 3 presents the routing algorithms we employed to perform routing in FPGAs with intra-cluster routing crossbars.

# 2.2 CAD FOR FPGAS

### **2.2.1. OVERVIEW**

Computer-Aided Design (CAD) has played a key role in the advancement and adoption of FPGAs across many industries. Due to the complexity of FPGA devices, the use of CAD tools has become an integral part of the process of synthesizing circuit designs onto an FPGA. A typical CAD flow takes as input a user circuit specified using a hardware description language (HDL) or a schematic along with a description of the target FPGA device. The CAD software then converts the high-level description into a binary file specifying the state of every configuration bit in the FPGA. This process is too complex to be modeled as one monolithic problem; it is therefore broken into a series of interdependent sub-problems, which are solved in sequence, as shown in **Figure 2-11**.

Figure 2-11: Typical CAD flow for an FPGA.

The first stage of this flow is called front-end synthesis. This step typically involves HDL elaboration, logic optimizations, and technology-mapping which maps the logic of the circuit into the LUTs of the FPGA. Front-end synthesis produces a netlist of FPGA logic blocks optimized in terms of logic blocks count and/or circuit speed.

The netlist then passes through the back-end flow, which involves packing, placement and routing. In the packing stage, the logic blocks of the technology-mapped netlist are clustered together, to determine which blocks are clustered together in the same CLBs; clustering logic blocks together creates opportunities for many types of efficiencies, such as CLB input sharing (if a net fans out to multiple logic blocks clustered in the same CLB), and the usage of the fast local feedbacks within the CLB,

rather than using the global FPGA routing network. The placement stage assigns each clustered logic block in the netlist to a physical CLB in the FPGA. Routing determines the paths in the routing fabric for individual signals in the netlist. The output of this flow is a configuration bitstream necessary to program the circuit on the FPGA.

A substantial amount of work has been published on the different stages of this CAD flow. Despite this work, publicly available CAD tools cannot model the hybrid logic blocks described earlier and offer limited to no capability for modeling sparse crossbars. Furthermore, synthesizing an industrial-scale circuit on a high-capacity commercial FPGA can easily take hours, days or even weeks, depending on the size of the circuit and the target device. The major contributions of this thesis in terms of FPGA CAD tool enhancement are mostly related to physical design (placement and routing). Specifically, we investigate the placement and routing of macro-cells, routing for FPGA with sparse crossbars, and parallel FPGA routing on multi-core, shared memory CPU architectures. The following two sections describe the placement and routing problems in the context of sparse crossbar routing model, and hybrid CLB architecture. Section 2.5 presents our parallel model targeting multi-core CPUs, and the final section summarizes this chapter.

### 2.2.2. PLACEMENT

Placement algorithms assign each clustered logic block to a physical CLB in the FPGA. This mapping has significant impact on the performance and routability of the circuit; as it determines the amount of interconnect in the FPGA, which is the major bottleneck of circuit performance. To minimize the impact of this bottleneck, the placer is often optimized for wire-length, routability, and timing. The mostly widely recognized

approach for FPGA placement is iterative improvement, specifically via simulated annealing; this is the approach taken by VPR [7].

```

S = RandomPlacement();

T = Initial Temperature();

R_{Limit} = InitialR_{Limit} ();

while (ExitCriterion () == False) {

/*"Outer loop"*/

/*"Inner loop"*/

while (InnerLoopCriterion () == False) {

S_{new} = GenerateViaMove (S, R_{Limit});

\Delta C = Cost(S_{now}) - Cost(S)

r = random (0, 1);

if (r < e^{-\Delta C/T}) {

S = S_{new};

/* End "Inner loop"*/

T = UpdateTemperature();

R_{Limit} = UpdateR_{Limit} ();

/* End "Outer loop"*/

}

```

Figure 2-12: Pseudo-code for the FPGA placement algorithm.

Simulated annealing is a stochastic optimization method for finding the global minimum of a cost function; which may possess many local minima. It mimics the annealing process used to gradually cool molten metal to produce high-quality metal objects [71]. Pseudo-code for a generic simulated annealing-based placer is shown in **Figure 2-12**. The quality of any placement of logic blocks is evaluated by a cost function; which, for a wirelength-driven placement could be, the sum over all nets of the half-perimeter of their bounding boxes [7]. VPR placer creates an initial placement by assigning logic blocks randomly to the available locations in the FPGA.

The algorithm then performs a large number of moves to gradually improve the placement. The moves are evaluated based on the changes they instigate on the cost

function. Moves that decrease the cost are always accepted, if the cost would increase, the move is not automatically rejected. Rather, the acceptance of the move is decided using a probability of acceptance given by  $r < e^{-\Delta C/T}$ , where  $\Delta C$  is the (positive) change in cost, and T the temperature of the annealing [71] that controls the likelihood of accepting moves that make the placement worse. VPR's placer sets T very high initially, so almost all moves are accepted; it gradually decreases T as the placement is refined, reducing the probability of accepting a move that negatively impacts the current placement solution. The algorithm terminates when the annealing process cannot generate better moves. VPR uses an adaptive annealing schedule that control the rate at which temperature is decreased, the exit criterion for terminating the anneal, the number of moves attempted at each temperature, and the generation of potential moves [7].

The work presented in this thesis uses the VPR 5.0 placement engine [46], with some modifications introduced in order to investigate the best approach for placing the macrocells. The macro-cells are placed offline, prior to the rest of the circuit, and we attempted to optimize for routability and delay. More details on this will be provided in Chapter 2.

The next section covers the routing step, which constitutes the bulk of this work. We first present a general description of routing, then we show how routing is performed in a sparse crossbar, and macro-cells. Section 2.5 describes our parallelization of PathFinder on multi-core, shared memmory CPU architectures.

### **2.2.3. ROUTING**

### **2.2.3.1. OVERVIEW**

After the circuit placement has been chosen, routing is performed to configure the programmable switches of the routing fabric to connect the logic blocks and the I/O pads of the circuit. To establish a connection, the router must find a sequence of unused routing resources along a path from the source to the sink for each signal in the netlist. Routing usually involves the creation of a graph [7] representing the routing resources of the FPGA, commonly called the routing resource graph (RRG).

Figure 2-13: A small FPGA fragment (a) and its corresponding RRG (b) [8, Fig. 4].

As shown in Figure 2-13, the nodes of the RRG represent wires and pins of the FPGA and the edges represent switches or feasible connections between two nodes.

Each signal of the input circuit is represented by one source along with a subset of nodes corresponding to its sinks. Routing a signal involves assigning

routing resources such that all the sinks are reachable from the source. To minimize routing resources usage, this path has to be as short as possible. When routing a set of signals sequentially, the order in which the signals are routed may be critical since some routing resources needed by a signal may be occupied by signals that are routed earlier. For this reason, FPGA routers must employ a congestion avoidance mechanism to resolve contention for routing resources. Since most of the delay in FPGAs is due to routing, the critical path delay for a circuit should be kept minimal by using fast routing resources and shortest paths to route nets on or near the critical path. Routers that optimize the critical path delay are called timing-driven; others are generally classified as being routability-driven.

### 2.2.3.2. PROBLEM FORMULATION

#### C. Problem Formulation

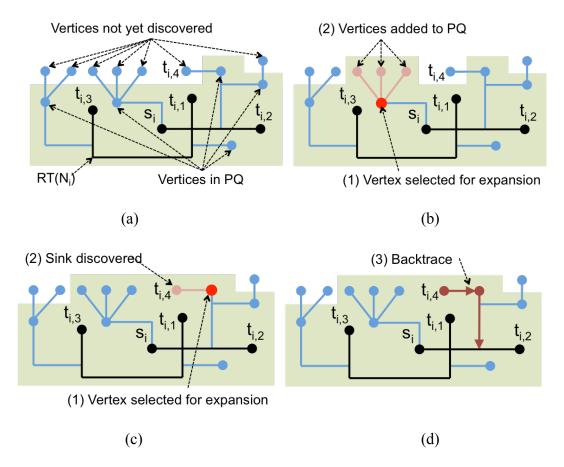

FPGA routing is a technology-specific variation of the disjoint path problem from graph theory, which is one of Karp's original NP-complete problems [31]. In a graph, two paths are disjoint if they share no vertices or edges. **Figure 2-14** provides an example of disjoint and non-disjoint paths.

Figure 2-14: A simple instance of the disjoint path problem.

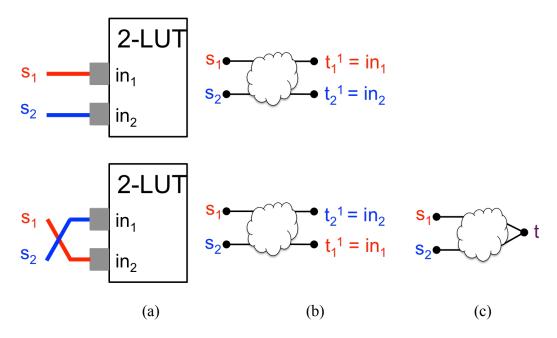

Figure 2-14 shows an instance of the disjoint path problem; Figure 2-14(a) shows a graph G(V, E) with sources  $S = \{s_1, s_2\}$  and sinks  $T = \{t_1, t_2\}$ ; an illegal solution, i.e., two non-disjoint paths that share a common vertex is shown in Figure 2-14 (b); Figure 2-14 (c) shows a legal solution, i.e., two disjoint paths that share no common vertices.

An instance of the disjoint path problem is a graph G(V, E), and two sets of vertices: a set of sources  $S = \{s_1, s_2, ..., s_k\}$  and a set of sinks  $T = \{t_1, t_2, ..., t_k\}$ . A legal solution is a set of paths  $P = \{p_1, p_2, ..., p_k\}$  where  $p_i$  is a path from  $s_i$  to  $t_i$  in G, such that the paths in P are disjoint. The NP-complete decision problem is whether or not a set P of disjoint paths exists, given G, S, and T; corresponding optimization problems may try to minimize the total lengths of the paths in P, the length of the longest path in P. In the routing problem for FPGAs, the graph G is the RRG, and the set of sources and corresponding sinks is derived from the placement solution. One important difference is that each path in the FPGA represents a net in a digital circuit, where a source may fan-out to drive multiple sinks. Each net has the form  $N_i = (s_i, T_i)$ , where  $s_i$  is the source and  $T_i = \{t_i^1, t_i^2, ..., t_i^n\}$  is the set of n sinks driven by source  $s_i$ ; thus,  $p_i$  is actually a hyper-path (tree) that connects  $s_i$  to the sinks in  $T_i$ .

A second important difference involves the equivalence of sinks. Because LUTs are programmable logic functions, their inputs are equivalent. Without loss of generality, if a 2-input LUT is configured to perform a logic function  $f(s_1, s_2)$ , then there is an equivalent logic function  $f'(s_2, s_1) = f(s_1, s_2)$ , yielding a symmetric source/sink assignment, shown in **Figure 2-15**(a). Explicitly listing either pair as the one possible legal solution, as shown in **Figure 2-15**(b), is overly restrictive. Thus, it is necessary to introduce a single vertex t

to represent a common sink, as shown in **Figure 2-15**(c). Therefore, any legal routing solution must be node disjoint, *except at the common sink*.

Figure 2-15: Logic equivalency of LUT inputs. Due to the equivalence of LUT inputs, different source-sink pairs may be legal solutions (a); however, enforcing specific source-sink pairs may be overly restrictive (b); the solution is to create a common sink (t) that represents all equivalent LUT inputs (c).

The objective of an FPGA router is twofold: (1) find a legal route, supposing the one exists; and (2) minimize the delay of the critical path in the circuit, which may involve the concatenation of several disjoint paths in the RRG. Many aspects of this delay will be technology-specific, including the logic delay through the BLEs on the path, delays relating to fanout, delays through routing multiplexers, wire delays in the routing network, etc.

Even though there have been several attempts at solving the routing problem in FPGAs [9] [40], mainly inspired by global routing for standard cells[63], by far the most successful approach is an algorithm called PathFinder [50], which is based on the

principle of negotiated congestion; both of VPR's routers are based on PathFinder, with some non-trivial modifications [46]. The next section presents the key elements of VPR's implementation of PathFinder, and highlights the limitations of the routing model in VPR, which motivated our work in modeling the intra-CLB routing resources as well as studying the routability issue in FPGAs that employ sparse intra-cluster routing crossbars.

#### 2.2.3.3. PATHFINDER

This section summarizes the PathFinder FPGA routing algorithm [50]. PathFinder is based on the paradigm of *Negotiated Congestion (NC)*, which computes illegal routing solutions in which several nets may share a single wire (RRG vertex). The negotiation process dynamically adjusts a cost function, which, over time, pushes nets away from congested wires, and yields a globally legal routing solution.

Figure 2-16 presents pseudocode for PathFinder. The outer loop, called the *Global Router*, iterates until a legal routing solution is found (i.e., all nets are routed on unique RRG nodes). The pseudocode assumes that a legal routing solution *can* be found. In practice, the global router is often replaced with a fixed number of iterations; if a legal global route is not found, then routing is assumed to fail.

The *Signal Router* (lines 2-27) is oblivious to the notion of congestion (i.e., several nets sharing the same RRG vertex); a cost function (described below) is computed for each RRG vertex and is dynamically updated to dissuade the usage of congested vertices during routing. The objective of the signal router is to find a route that minimizes the aggregate cost of the RRG vertices that comprise the route.

```

// Global Router

1. While at least two nets share a common routing resource

// Signal Router

2.

For each net N_i

Rip up routing tree RT_i for net N_i = (s_i, T_i)

3.

4.

Reinitialize RT_i to contain only the source s_i

For each sink t_i^j T_i

5.

Initialize priority queue PQ to RT_i with cost 0

6.

7.

While t_i^j RT_i

8.

Remove min. cost vertex u from PQ

9.

Insert u into RT_i

If u \neq t_i^J

10.

For each RRG edge (u, v)

11.

12.

If v RT_i and v PQ

Insert v into PQ with cost f_v = g_{u,v} + d_v^{j}

13.

and predecessor edge (u, v)

Else If v RT_i and v PQ and f_v > g_{u,v} + d_v^j

14.

Change the cost of v in PQ to

15.

f_{v} = g_{u,v} + d_{v}^{j}

Change the pred. edge of v in PQ to (u, v)

16.

17.

EndIf

EndFor

18.

EndIf

19.

EndWhile

20.

EndFor

21.

For each sink t_i^J T_i

For each node v in reverse path from t_i^j to s_i

22.

23.

Update cost c_v

24.

Add v to RT_i

25

EndFor

26.

EndFor

27.

EndFor

28. EndWhile

```

Figure 2-16: Pseudocode for the PathFinder FPGA routing algorithm.

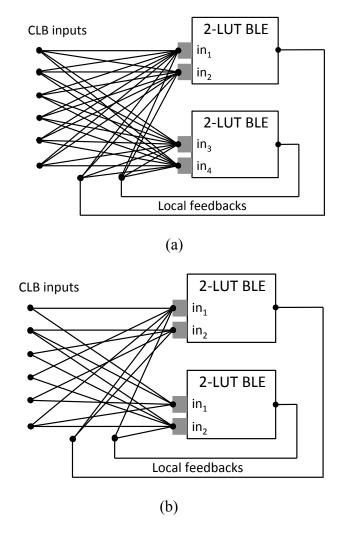

The Signal Router routes one net a time; the routing tree  $RT_i$  for net  $N_i$  is expanded in search of each sink  $t_i^T T_i$ , one sink at a time, and in-order. The routing tree  $RT_i$  for net  $N_i$ , computed during the previous iteration, is discarded, and a new route is computed.

The new route may be computed using a priority-driven breadth-first search [50], similar to the *maze expansion* step of Lee's Maze Router [38]; more efficient routes can

be computed using an A\* cost function, which includes an additional term that directs the search toward the target sink  $t_i^j$  [7][50][69].

The first search starts from source  $s_i$  of the current net  $N_i$  to the first sink,  $t_i^{\ l}$ , resulting in a routing path. Subsequent searches expand the routing path into a routing tree,  $RT_i$ . Inductively, suppose that  $RT_i$  connects  $s_i$  to the first j-l sinks,  $\{t_i^{\ l}, t_i^{\ l}, ..., t_i^{\ l}\}$ . The search will find a path that connects one vertex in  $RT_i$  to the j<sup>th</sup> sink,  $t_i^{\ l}$ .

Each search initializes a priority queue PQ to contain the vertices in  $RT_i$  at zero cost. After processing these vertices, PQ will contain each vertex that (1) has at least one neighbor in  $RT_i$ , and (2) does not belong to  $RT_i$  itself. The search works as follows: the lowest cost vertex v is removed from PQ and added to  $RT_i$ . The vertices adjacent to v are then examined and inserted into PQ accordingly. This process repeats until the current sink  $t_i^j$  is found. PQ includes an adjacent neighbor u of v that belongs to  $RT_i$ ; thus, v and adjacent edge (u, v) are added together to  $RT_i$ .

Cost Function: An important implementation detail is the cost computed for each vertex when it is inserted into PQ. Different PathFinder implementations use different cost functions [7][50] [69], with different objectives and strategies. Let v be the vertex, and u be a vertex adjacent to v that has already been added to  $RT_i$ ; in other words, if the search selects v for inclusion in  $RT_i$ , it will include edge (u, v) as well. Let  $f_u$  denote the cost of the path from source i to node u, and  $c_v$  denote the cost of adding node v to the route. Then the cost of routing from the source to v is:

$$g_{u,v} = f_u + c_v$$

(2.4)

To accommodate an A\* cost function, let  $d_v^j$  be an estimate of the cost of completing

the route from node v to sink  $t_i^j$ . Then the cost of the path from source i to sink  $t_i^j$  along RRG edge (u, v) is

$$f_{v} = g_{u,v} + d_{v}^{j}$$

(2.5)

A breath-first search, i.e., a Lee-style maze expansion [38], then corresponds to the case where  $d_v^j = 0$ . Several modifications have been proposed to assign relative weights to the the breadth-first and A\* components of the cost function

When adding a new vertex u into  $RT_i$ , each neighbor v of u is processed and added to PQ, unless v already belongs to  $RT_i$ . If is possible that a different neighbor w of v is also part of  $RT_i$ , so v may already be in the priority queue with some cost function

$$f_v = g_{w,v} + c_v.$$

In principle, it is now possible to add v to  $RT_i$  either via edge (u, v) or (w, v). The best choice is the one that minimizes  $f_v$ . Therefore, the cost and predecessor of v in PQ are changed from w to u if  $g_{u,v} < g_{w,v}$ , or, equivalently, if  $g_{u,v} + c_v$  is less than the current value of  $f_v$ .

Several different variants of the node cost function  $c_v$  have also been proposed:

$$c_v = (b_v + h_v)p_v$$

, and [1] ......(2.8)

where  $b_v$  is the *base cost* of v (typically its intrinsic delay),  $h_v$  is the *history cost* of v, which depends on the number of nets that are routed through v during previous iterations,

We ignore the *BendCost(...)* term from Eq. (4.3) in Ref. [7] because we are performing combined global-detailed routing.

<sup>&</sup>lt;sup>2</sup> In combined global-detailed routing, which is the approach taken by VPR, the capacity of each routing resource is

and  $p_v$  is a *penalty function* associated with the number of nets routed through v in the current solution. PathFinder dynamically updates  $h_v$  and  $p_v$  accordingly as routing proceeds. According to Ref. [7], the advantage of Eq. (2.9) over Eq. (2.8) is that multiplying the  $b_v$  and  $h_v$  terms, rather than adding them, eliminates the need to normalize them; one possible drawback, not mentioned by [7], is that  $b_v h_v > b_v + h_v$  for  $b_v$ ,  $h_v > 2$ , so there is a greater chance of arithmetic overflow if both terms grow significantly as the algorithm iterates.

The difference between  $h_v$  and  $p_v$  is that  $h_v$  permanently increases the cost of using v to ensure that routes through other vertices are attempted, while  $p_v$  is based primarily on the current routing solution. Recall that PathFinder routes nets one-at-a-time. Suppose that nets  $N_I$  and  $N_2$  are being routed in subscript order. The history cost could potentially dissuade PathFinder from routing both  $N_I$  and  $N_2$  through v during the current iteration, especially if v has a history of congestion. Now, supposing that PathFinder routes  $N_I$  through v despite the value  $h_v$ , then increasing  $p_v$  in response would dissuade PathFinder from routing  $N_2$  through v, to increase the likelihood of converging to a legal solution.

A generalized form of the  $c_v$  terms that favors delay-minimization for source-sink pairs whose delay is expected to near-critical is

$$c_{v} = Crit_{i,j}delay_{v} + (1 - Crit_{i,j})(b_{v} + h_{v})p_{v}, \text{ or}$$

$$c_{v} = Crit_{i,j}delay_{v} + (1 - Crit_{i,j})b_{v}h_{v}p_{v}, \text{ such that}$$

$$Crit_{i,j} = 1 - Slack_{i,j}/D_{max},$$

$$(2.10)$$

where  $delay_v$  is the intrinsic delay of RRG node v,  $Slack_{i,j}$  is the estimated amount of delay that could be added to the source-sink path from i to j before it becomes critical,

and  $D_{max}$  is the estimated critical path delay of the placed-and-routed circuits. In VPR's timing-driven router [[7], Section 4.4], the  $delay_v$  term is based on the Elmore delay model, which is derived from the existing routing tree  $RT_i$ , including the prospective path from i to v; additionally, the  $Crit_{i,j}$  term is more complex; details are omitted to conserve space.

The original PathFinder paper did not describe precisely which functions are used for  $h_v$  and  $p_v$  [50]. In VPR,  $p_v$  is reset and recomputed every time a routing tree is ripped up and rerouted, while  $h_v$  is defined as a recurrence relation which varies from iteration to iteration of the global router.

Let  $h_v^k$  denote the history cost of vertex v during the  $k^{th}$  iteration of the global router; for the first iteration,  $h_v^l = 1$ . The  $p_v$  and  $h_v^k$  terms are then defined as follows:

$$h_v^k = h_v^{k-1} + occupancy_v h_{fac}, k > 1,$$

[7, Eq. (4.5)<sup>2</sup>] ......(2.14)

where  $occupancy_v$  is the number of nets that are current routed through RRG node v, and  $p_{fac}$  and  $h_{fac}$  are scaling factors. Ref. [[7], Section 4.3.1] suggests that  $p_{fac}$  should be at most 0.5 for the first iteration, and then increased by a factor of 1.5x to 2x for subsequent iterations, and that  $h_{fac}$  should remain constant and that any value between 0.2 and 1 should suffice.

<sup>&</sup>lt;sup>2</sup> In combined global-detailed routing, which is the approach taken by VPR, the capacity of each routing resource is 1, which allows us to eliminate the *capacity(...)* term from Eqs. (4.4) and (4.5) in Ref. [7].

The enhancements to PathFinder introduced in this thesis, PPR and SERRGE, are compatible with any cost function (breadth-first or A\* search) described in previous literature. We have implemented PPR and SERRGE in VPR 5.0, and all of our experimental results reported in Section 3.6 use VPR's timing-driven router [[7], Section 4.4].

# 2.3 ROUTING IN SPARSE CROSSBARS

A full intra-cluster routing crossbar is a configuration of the routing fabric inside the CLB in which a programmable routing connection exists between *every* CLB input and *every* BLE input within the CLB. This means that the router only needs to algorithmically compute routes from sources to CLB inputs, not BLE inputs; with a full crossbar connecting CLB inputs to BLE inputs, it is trivial to complete the route. A sparse intra-cluster routing crossbar on the other hand is a crossbar configuration in which each CLB pin is only connected to a subset of the BLE inputs. In this configuration, the router must find a full path from the sources to the BLE inputs; as CLB inputs are no longer connected to every BLE input. This means that the RRG has to include the routing resources inside the CLB.

In full crossbar architecture, the intra-cluster routing can be omitted from the RRG; this has been standard in VPR since its inception, although the assumption has since been lifted since the release of VPR 6.0. This also makes the CLB inputs logically equivalent; as each CLB input can connect to any BLE input. For sparse crossbars the CLB inputs

are no longer logically equivalent but for a given BLE the inputs are logically equivalent. As shown in Figure 2-17, due to the equivalence of LUT inputs, different source-sink pairs may be legal solutions; however, enforcing specific source-sink pairs may be overly restrictive; the solution is to create a common sink (t) that represents all equivalent LUT inputs.

Figure 2-17: Logic equivalency for LUT pins.

Now that the crossbar is sparsely connected, in order for the router to complete a legal disjoint path routing solution, it is necessary to explicitly represent the intra-cluster routing crossbar in the RRG. This enlarges the size of the RRG: the set of vertices must include each CLB input and each BLE input (before, the CLB inputs could be represented as a single sink, akin to **Figure 2-18**, while BLE inputs were omitted altogether); and the number of edges that are added to the RRG depends on the population density of the crossbar. Taken in aggregation across the entire FPGA, the RRG size can increase significantly.

Figure 2-18: CLBs with fully connected (a) and sparsely connected (b) intra cluster routing crossbars.

This potential growth in the RRG size translates into significant increase in PathFinder's runtime and memory footprint. We present two heuristics for routing in FPGA with intra-cluster routing crossbars that reduces the runtime and memory footprint of the PathFinder FPGA routing algorithm for FPGAs with sparse intra-cluster routing crossbar. The two approaches are introduced with different characteristics in terms of runtime, memory usage, and quality of solution. *SElective RRG Expansion (SERRGE)* employs a memory manager that compresses the RRG and decompresses relevant

portions of it as the router executes, thereby eliminating the need to fully expand it prior to routing. A second, heuristic, *Partial Pre-Routing (PPR)* computes routes for each intra-cluster routing crossbar a-priori, and then routes the rest of the circuit using the global routing resources of the FPGA. Between the two, PPR achieves shorter runtimes and consumes less memory, while SERGGE tends to find legal routing solutions with lower critical path delays, equating to higher clock frequencies. Our results demonstrate that SERRGE and PPR address the routing challenge imposed by FPGAs with sparse intra-cluster routing crossbars, as they offer a clear and unequivocal improvement over the state-of-the-art in FPGA routing algorithms.

Prior work in this area has mostly investigated the routability of sparse crossbars. VPR's routability-driven and timing-driven routers, both based on PathFinder [50], have introduced sparse intra-cluster routing crossbars since the release of VPR6.0 [47]; using an approach similar to PPR to perform routing. The main difference with our work is that VPR integrates the partial pre-routing phase into the packer [47], as a legality check. In other words, any packing solution that cannot be routed locally within a CLB is disallowed. The router (which follows packing and placement) is similar to PPR's global router, described in Chapter 3 of this thesis.

In its original description, PathFinder computes a route from each source to each sink. For a multi-terminal net, the wavefront expansion obtained when routing to the  $i^{th}$  sink is discarded before routing to the  $(i+1)^{st}$ . VPR's implementation does not discard the wavefront, and continues expansion until all sinks are discovered.

If a global iteration of PathFinder fails to find a legal solution, all nets are ripped up and rerouted, which partially eliminates the dependence on net ordering when routing. Mulpuri and Hauck [54] modified PathFinder to exclusively rip up nets routed through oversubscribed resources. Although this modification speeds up PathFinder's convergence time significantly, a non-negligible increase in critical path delay was observed for all benchmarks; for this reason, we do not consider this implementation choice in our experiments.

Gort and Anderson [22] reduce contention for CLB output pins by forcing a multi-sink net to use the same output pin for all sinks during wavefront expansion while exclusively ripping up and re-routing nets that route through oversubscribed resources, similar to Mulpuri and Hauck; they reported a 3x speedup in router runtime coupled with a 2% increase in critical path delay and wirelength. Subsequently, Gort and Anderson [24] observed that PathFinder spends up to 40% of its runtime resolving congestion among nets that have been routed legally. They allow PathFinder to converge when the routing solution is almost legal on a coarsened RRG, and then legalize the result using a SAT solver. In principle, this approach is also compatible with either PPR or SERRGE.

Chin and Wilton [15] developed an RRG compression scheme that takes advantage of the regular tiled nature of an FPGA. An RRG is instantiated for each tile, and inter-tile connections are represented using "wrap-around" edges. Different tile types are instantiated for programmable logic, embedded blocks, and I/Os. Extensions are presented to handle long wires and sparse intra-cluster routing crossbars, including the heterogeneous depopulation schemes that vary from tile-to-tile. Separate storage is

maintained for the costs associated with each edge in the fully expanded RRG; this information is not compressed. The additional steps added to the router to enable the compressed RRG representation increase the router's runtime by a factor of 2.16x, on average. In contrast, PPR and SERRGE reduce the runtime of the router, although the reductions in RRG size reported here are far more modest in comparison to Chin and Wilton's scheme.

So [67] introduced a delay budgeting scheme to reduce the critical path delay of a circuit synthesized on an FPGA; since this is a post-processing step, it could improve the quality of results; however, it significantly increases the router runtime by a factor of at least 7x and also increases the memory footprint.

Rubin and DeHon [66] observed that small perturbations in initial conditions (e.g., the order in which nets are routed; variations in intrinsic delays associated with routing resources) yield significant variations in the critical path delays reported by VPR's implementation of PathFinder. They introduced noise mitigation strategies that repeatedly re-route each circuit with variations in parameters that express a timing constraint. In principle, this approach could be used in conjunction with either PPR or SERRGE, as long as the runtime overhead of repeatedly routing the circuit is tolerable.

We present a detailed description of our algorithms (PPR and SERRGE) in Chapter 3. The next section presents our approach to placement and routing of hybrid logic blocks capable of implementing floating point shifters.

# 2.4 ROUTING FOR HYBRID CLBS

In section 2.1.2 we have described dynamic configuration of multiplexers, and showed how this technique can be used to configure a regular Configurable Logic Block to implement shifting operations required by floating point mantissa alignment and normalization. We have also shown that by combining 8 hybrid blocks we can efficiently implement a 27-bit shifter. This section briefly describes how these hybrid CLBs can be placed and routed as part of a modern FPGA CAD flow.

### 2.4.1. FUNDAMENTAL CHALLENGES