## **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Towards Data Reliable, Low-Power, and Repairable Resistive Random Access Memories

#### **Permalink**

https://escholarship.org/uc/item/4v22d8gz

#### **Author**

Ghofrani, Amirali

#### **Publication Date**

2016

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

## Towards Data Reliable, Low-Power, and Repairable Resistive Random Access Memories

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Amirali Ghofrani

## Committee in charge:

Professor Kwang-Ting Cheng, Chair Professor Dmitri Strukov Professor Luke Theogarajan Professor Malgorzata Marek-Sadowska

| The Dissertation of Amirali Ghofrani is approved | d. |

|--------------------------------------------------|----|

|                                                  |    |

| Professor Dmitri Strukov                         |    |

|                                                  |    |

| Professor Luke Theogarajan                       |    |

|                                                  |    |

| Professor Malgorzata Marek-Sadowska              |    |

| Professor Kwang-Ting Cheng, Committee Chai       |    |

March 2016

# Towards Data Reliable, Low-Power, and Repairable Resistive Random Access Memories

Copyright © 2016

by

Amirali Ghofrani

To my loving parents, Saeed and Farideh, with their unconditional and never-ending love and support. And to my sister and brother, Mishka and Reza, that are the best siblings that one can ever ask for.

## Acknowledgements

It was quite a journey for me to finish my PhD, and there are many people that I would like to acknowledge.

I am deeply indebted to my research advisor Prof. Kwang-Ting Cheng for his support, patience, and understanding throughout my PhD study. He showed what it takes to be a great advisor. Under his guidance, I became a better researcher and a better writer. He looks after his students like a real father, and puts lots of time and effort in making his students independent thinkers. Thank you Tim, you are awesome!

I would also like to thank the rest of my dissertation committee, Prof. Dmitri Strukov, Prof. Luke Theogarajan, and Prof. Malgorzata Marek-Sadowska for their insightful comments that helped me improve the quality of this work. Specially, Dmitri always encouraged me and his door was always open for discussions.

I should thank Prof. Wei Lu, Prof. Valeria Bertacco, Prof. Luca Benini, Prof. Rajesh Gupta, Dr. Siddharth Gaba, Dr. Bhaswar Chakrabarti, Dr. Farnood Merrikh-Bayat, Advait Madhavan, Justin rofeh, Dawen Xu, and Ritesh Parikh, for the fruitful collaborations that we had.

I thank my current and past fellow labmates in SoC Design and Test Lab at the University of California, Santa Barbara: Dr. Saeed Shamshiri, Dr. Peter Lisherness, Dr. Ming Gao, Dr. Hsiu-Ming (Sherman) Chang, Dr. Yan Zheng, Dr. Xin Yang, Dr. Yi-chu Wang, Miguel Lastras, Nicole Fern, Chun-Kai Hsu, Fan (Fred) Lin, Rui Wu, Yuyang Wang, and Lei-lai Shao. It was a pleasure working with you all.

And of course, research is not possible with empty pockets! I would like to thank AFOSR-MURI and GSRC for funding most of the research, the ECE department for giving me TA positions, and the OISS for their generous work-study awards.

I was truly blessed to have many wonderful people around me during the many years of my PhD studies. Without their presence, this work was either not possible, or would have been a painful experience! I should thank: Miguel Lastras, for being my brother throughout all these years of PhD. Melika Payvand, for being a great friend, caring for me in good days and bad days alike. Zhinous, Seyyed, Samaneh, Ehsan, Omid, Behzad, Sayyad, and Mohammad, a.k.a "Khodemoon", for being a truly wonderful group of friends that I am blessed to have. Specially, Zhinous Marzi, for all the moral support and the brainstorming in the last months of this dissertation on top of her priceless friendship. Dr. Borzooyeh Naji, for being my best friend for  $\approx 30$  years. Dr. Abbas Rahimi, for his support with open arms when I needed it the most. I will never forget that. Hedieh Ekhlasi, for her invaluable care and support. Nahid, Kambiz, and Shireen Garrousi, for being my family in USA. Dr. Saeed Shamshiri for mentoring me when I first came here. And Dr. Shahab Karimi, Majid Namaki, Nima Tayyebi, Hossein Mazloumi, Dr. Elaheh Ahmadi, Dr. Ali Nabi, Parviz Alvandi, Avantika Sodhi, Kourosh and Soheila Mohsenzadegan, Saeed and Razieh Hashemi, Hadi and Elham Rasouli, and Fatemeh and Mehran Rajaeian, for touching my life in different ways, with their kindness and friendship. And thanks to my other friends in Iranian Graduate Student Association (IGSA), Persian Student Group (PSG), Heroes indoor soccer team, and the camping group!

And last but not least, I would like to express my sincerest appreciations to my parents, Farideh Khoshghalb and Saeed Ghofrani, and my siblings, Mishka and Reza. I am so happy to have you in my life.

### Curriculum Vitæ Amirali Ghofrani

#### **Education**

| 2016 | Ph.D. in Computer Engineering, University of California, Santa Barbara. |

|------|-------------------------------------------------------------------------|

| 2013 | M.Sc. in Computer Engineering, University of California, Santa Barbara. |

| 2010 | M.Sc. in Computer Engineering, University of Tehran, Iran.              |

| 2007 | B.Sc. in Computer Engineering, University of Tehran, Iran.              |

#### **Publications**

- 1. **A. Ghofrani**, M. A. Lastras-Montaño, Y. Wang, K.-T. Cheng, "In-place Repair for Resistive Memories Utilizing Complimentary Resistive Switches", submitted to International Symposium on Low Power Electronics and Design, San Francisco, USA, August 2016.

- 2. M. A. Lastras-Montaño, **A. Ghofrani**, K.-T. Cheng, "A Low-Power Hybrid Reconfigurable Architecture for Resistive Random-Access Memories", accepted in *22nd IEEE Symposium on High Performance Computer Architecture (HPCA)*, Barcelona, Spain, March 2016.

- 3. **A.Ghofrani**, A. Rahimi, M. A. Lastras-Montaño, L. Benini, R. K. Gupta, K.-T. Cheng, "Associative Memristive Memory for Approximate Computing in GPUs", accepted in *IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS)*.

- 4. **A. Ghofrani**, M. A. Lastras-Montaño, S. Gaba, M. Payvand, W. Lu, L. Theogarajan, K.-T. Cheng, "A Low-Power Variation-Aware Adaptive Write Scheme for Access-Transistor-Free Memristive Memory", *ACM Journal on Emerging Technologies in Computing Systems (JETC)*, Vol. 12, Issue 1, July 2015.

- 5. M. A. Lastras-Montaño, A. Ghofrani, K-T. Cheng, "Architecting Energy Efficient Crossbarbased Memristive Random Access Memories", *Intl. Symposium on Nanoscale Architectures (NANOARCH15)*, Boston, USA, July 2015.

- 6. J. Rofeh, A. Sodhi, M. Payvand, M. A. Lastras-Montaño, A. Ghofrani, A. Madhavan, S. Yemenicioglu, K.-T. Cheng, L. Theogarajan, "Vertical Integration of Memristors onto Foundry CMOS Dies using Wafer-Scale Integration", *IEEE Electronic Components and Technology Conference (ECTC15)*, San Diego, USA, May 2015.

- 7. M. Payvand, A. Madhavan, M. A. Lastras-Montaño, A. Ghofrani, J. Rofeh, K.-T. Cheng, D. Strukov, L. Theogarajan, "A Configurable CMOS Memory Platform for 3D Integrated Memristors", *IEEE International Symposium on Circuits and Systems (ISCAS15)*, Lisbon, Portugal, May 2015.

- 8. A. Rahimi, **A. Ghofrani**, K.-T. Cheng, L. Benini, R. Gupta, "Approximate Associative Memristive Memory for Energy-Efficient GPUs", *Design, Automation, and Test in Europe (DATE15)*, Grenoble, France, March 2015.

- 9. M. A. Lastras-Montaño, **A. Ghofrani**, K.-T. Cheng, "HReRAM, A Hybrid Reconfigurable Resistive Random Access Memory", *Design*, *Automation*, *and Test in Europe (DATE15)*, Grenoble, France, March 2015.

- A. Ghofrani, M. A. Lastras-Montaño, K-T. Cheng, "Toward Large-Scale Access-Transistor-Free Memristive Crossbars", invited to Asia South Pacific Design Automation Conference (ASPDAC15), Tokyo, Japan, Jan 2015.

- 11. A. Rahimi, **A. Ghofrani**, M. A. Lastras-Montaño, K.-T. Cheng, L. Benini, R. Gupta, "Energy-Efficient GPGPU Architectures via Collaborative Compilation and Memristive Memory-Based Computing", *51st Design Automation Conference (DAC14)*, San Francisco, USA, June 2014.

- 12. **A. Ghofrani**, M. A. Lastras-Montaño, K-T. Cheng, "Towards Data Reliable Crossbar-Based Memristive Memories," *IEEE International Test Conference (ITC13)*, Anaheim, USA, Sep 2013.

- 13. M. A. Lastras-Montaño, **A. Ghofrani**, K.-T. Cheng, "Architecting Low Power Crossbar-Based Memristive RAM", *Non-Volatile Memory Workshop (NVMW13)*, San Diego, USA, Mar 2013.

- 14. D. Xu, H. Li, **A. Ghofrani**, K.-T. Cheng, Y. Han, X. Li, "Test Quality Optimization for Variable n-Detection of Transition Faults", *IEEE Transaction on Very Large Scale Integration systems*, Vol. PP, Issue 99, Jul 2013.

- 15. **A. Ghofrani**, R. Parikh, S. Shamshiri, A. DeOrio, K-T. Cheng, V. Bertacco, "Comprehensive Online Defect Diagnosis in On-Chip Networks", *30th VLSI Test Symposium (VTS12)*, Maui, USA, Apr 2012.

- 16. Y. Zheng, P. Lisherness, S. Shamshiri, A. Ghofrani, S. Yang, K.-T. Cheng, "Post-Fabrication Reconfiguration for Power-Optimized Tuning of Optically Connected Multi-Core Systems", *17th Asia and South Pacific Design Automation Conference (ASPDAC12)*, Australia, Jan 2012.

- 17. S. Shamshiri, **A.Ghofrani**, K.T. Cheng, "End to End Error Correction and Online Diagnosis for On-Chip Networks", *IEEE International Test Conference (ITC11)*, Anaheim, USA, Sep 2011.

#### Awards

2015 UCSB Electrical and Computer Engineering Department Dissertation Fellowship (Spring)

2013 Gerald W. Gordon Award, IEEE Philadelphia Section, Test Technology Technical Council (TTTC), and International Test Conference (ITC)

2013 GSA Dixon-Levy Service Award, UCSB

2012-2013 Leslie Griffin Lawson Award for Outstanding Leadership, UCSB

2012-2013 Graduate Individual Co-Curricular Leadership and Activities Award, UCSB

2011 Best Student Paper Award, International Test Conference (ITC)

#### **Abstract**

# Towards Data Reliable, Low-Power, and Repairable Resistive Random Access Memories

by

#### Amirali Ghofrani

A series of breakthroughs in memristive devices have demonstrated the potential of memristor arrays to serve as next generation resistive random access memories (ReRAM), which are fast, low-power, ultra-dense, and non-volatile. However, memristors' unique device characteristics also make them prone to several sources of error. Owing to the stochastic filamentary nature of memristive devices, various recoverable errors can affect the data reliability of a ReRAM. Permanent device failures further limit the lifetime of a ReRAM. This dissertation developed low-power solutions for more reliable and longer-enduring ReRAM systems.

In this thesis, we first look into a data reliability issue known as write disturbance. Writing into a memristor in a crossbar could disturb the stored values in other memristors that are on the same memory line as the target cell. Such disturbance is accumulative over time which may lead to complete data corruption. To address this problem, we propose the use of two regular memristors on each word to keep track of the disturbance accumulation and trigger a refresh to restore the weakened data, once it becomes necessary.

We also investigate the considerable variation in the write-time characteristics of individual memristors. With such variation, conventional fixed-pulse write schemes not only waste significant energy, but also cannot guarantee reliable completion of the write operations. We address such variation by proposing an adaptive write scheme that adjusts the width of the write pulses for each memristor. Our scheme embeds an online monitor to detect the completion of a write operation and takes into account the parasitic effect of line-shared devices in access-

transistor-free memristive arrays. We further investigate the use of this method to shorten the test time of memory march algorithms by eliminating the need of a verifying read right after a write, which is commonly employed in the test sequences of march algorithms.

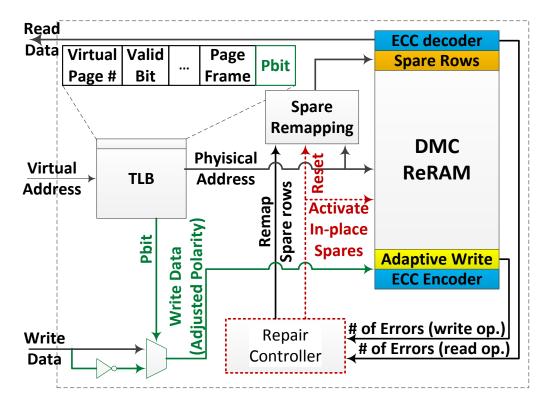

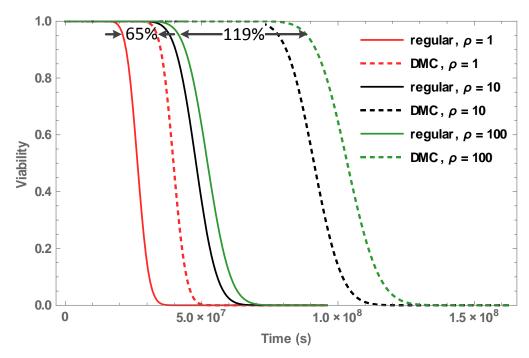

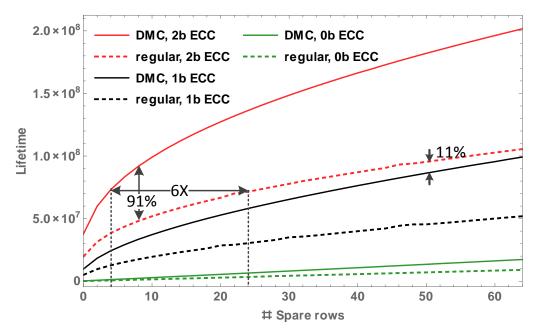

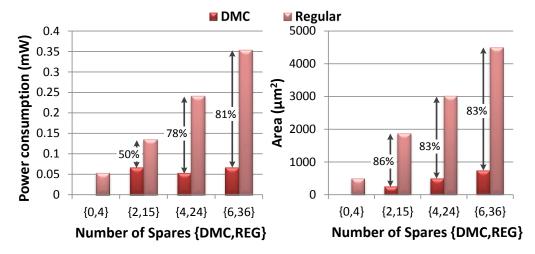

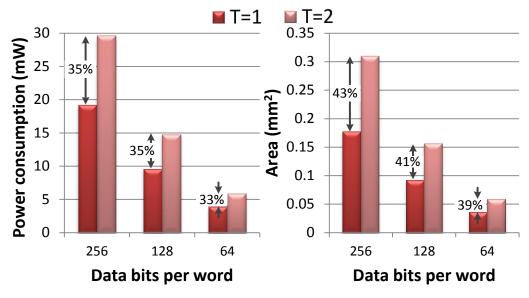

Finally, we propose a novel mechanism to extend the lifetime of a ReRAM by protecting it against hard errors through the exploitation of a unique feature of bipolar memristive devices. Our solution proposes an unorthodox use of *complementary resistive switches* (a particular implementation of memristive devices) to provide an "in-place spare" for each memory cell at negligible extra cost. The in-place spares are then utilized by a repair scheme to repair memristive devices that have failed at a stuck-at-ON state at a page-level granularity. Furthermore, we explore the use of in-place spares in lieu of other memory reliability and yield enhancement solutions, such as error correction codes (ECC) and spare rows. We demonstrate that with the in-place spares, we can yield the same lifetime as a baseline ReRAM with either significantly fewer spare rows or a lighter-weight ECC, both of which can save on energy consumption and area.

# **Contents**

| Cı       | Curriculum Vitae |                                                                              |       |  |  |

|----------|------------------|------------------------------------------------------------------------------|-------|--|--|

| Abstract |                  |                                                                              |       |  |  |

| 1        | Intr             | oduction                                                                     | 1     |  |  |

|          | 1.1              | Motivation                                                                   | 1     |  |  |

|          | 1.2              | Addressing Write Disturbance                                                 | 3     |  |  |

|          | 1.3              | Addressing Write Time Variation                                              | 5     |  |  |

|          | 1.4              | Extending ReRAM Lifetime                                                     | 7     |  |  |

|          | 1.5              | Permissions and Attributions                                                 | 7     |  |  |

| 2        | Tow              | ards Data Reliable Crossbar-Based Memristive Memories                        | 9     |  |  |

|          | 2.1              | Introduction                                                                 | 10    |  |  |

|          | 2.2              | Background on Memristors                                                     | 13    |  |  |

|          | 2.3              | Data Reliability Issues in Memristive Memories                               | 18    |  |  |

|          | 2.4              | Addressing Memristor Data Reliability                                        | 21    |  |  |

|          | 2.5              | Experimental Results                                                         | 28    |  |  |

|          | 2.6              | Conclusion                                                                   | 37    |  |  |

| 3        | A Lo             | ow-Power Variation-Aware Adaptive Write Scheme for Access-Transistor-Free    |       |  |  |

|          | Men              | nristive Memory                                                              | 39    |  |  |

|          | 3.1              | Introduction                                                                 | 40    |  |  |

|          | 3.2              | Background on Memristors                                                     | 42    |  |  |

|          | 3.3              | Write Time Variation in Memristors                                           | 46    |  |  |

|          | 3.4              | Low-Power Variation-Aware Writing Scheme                                     | 49    |  |  |

|          | 3.5              | Results                                                                      | 53    |  |  |

|          | 3.6              | Conclusion                                                                   | 64    |  |  |

| 4        | In-p             | lace Repair for Resistive Memories Utilizing Complementary Resistive Switche | es 65 |  |  |

|          | 4.1              | Introduction                                                                 |       |  |  |

|          | 4.2              | Background                                                                   | 68    |  |  |

| Bi           | ibliography |                                  |    |  |  |  |  |

|--------------|-------------|----------------------------------|----|--|--|--|--|

| 5 Conclusion |             |                                  | 87 |  |  |  |  |

|              |             | Analysis and Results             |    |  |  |  |  |

|              | 4.4         | Failure Mechanisms and Solutions | 74 |  |  |  |  |

|              |             |                                  |    |  |  |  |  |

# Chapter 1

## Introduction

## 1.1 Motivation

CMOS-based memory technologies cannot keep up with the ever-increasing demand for denser and lower-power memories. As the memory cell size is mainly limited by the size of its access-transistor, CMOS technology scaling is reaching its limit due to the increased leakage current of the access-transistors and the yield drop induced by fabrication imprecision [1].

As an alternative, emerging resistive memory technologies such as phase change memories (PCM) [2], spin-transfer torque magneto-resistive memories (STT-MRAM) [3], and metal oxide valence change resistive random access memories (ReRAM) [4] have been investigated recently that offer ultra-small and low-power memory elements with fast switching speeds. Among them, metal oxide valence change ReRAMs, generally referred to as memristors [5], are especially promising as they exhibit unique electrical characteristics which enable the elimination of the access-transistor, while maintaining the same power/speed/endurance advantages [6].

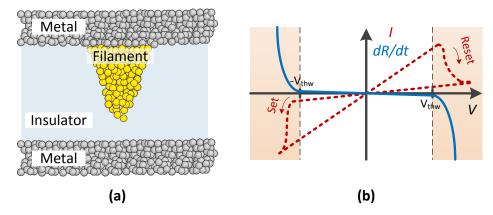

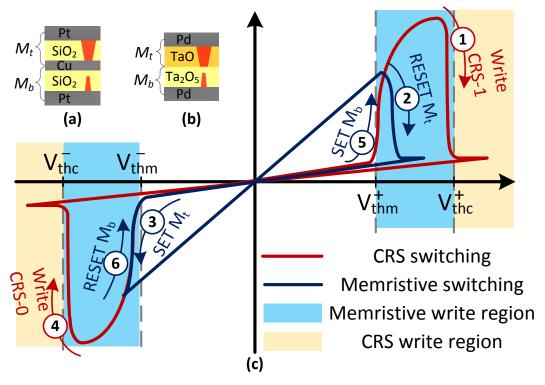

A memristor is a two-terminal passive programmable resistor, which typically has a metal/insulator/metal (MIM) structure shown in Figure 1.1a. The resistance of a memristor is maintained in the absence of an electric field. 0/1 logic values can be represented by

Figure 1.1: A memristor's exemplar realization, and its non-linear dR/dt-V characteristic. a) A typical metal/inuslator/metal structure. Formation of a conductive filament inside the insulator layer changes the resistance of the device. b) Electrical characteristics of memristive devices: the solid line shows the non-linearity in the rate of change for the resistance of the device based on the applied voltage. The dashed lines shows the linear I-V characteristic observed in a typical memristive device.

ranges of high/low resistances. The resistance of the device can be changed by applying adequate voltage (or current) pulses. The change in the resistance happens due to the non-volatile formation of a conductive filament inside the insulating oxide layer and has a strong non-linear dependency on the amplitude of the applied pulse [7], as shown in Figure 1.1b: while applying voltages above a write threshold,  $V_{thw}$ , effectively switches the internal state of the device, applying voltages below  $V_{thw}$  has negligible effect on the device's state. This non-linearity combined with proper voltage application schemes could effectively provide the functionality of an access-transistor, and thus, obviate the need for an access-transistor for each memory cell.

The elimination of the access-transistor and the simple structure of memristors facilitates the realization of ultra-high density access-transistor-free (ATF) memory arrays with sub 10-nm feature sizes [8]. Such arrays demonstrate lower power consumption than existing technologies, verified by analysis and preliminary experimental measurements, due to the ATF memory structure and the passiveness of the devices [9, 10]. Such characteristics make memristive memories attractive as an extremely dense and low-power non-volatile memory [6]. Several nanoscale memristive crossbars have been successfully demonstrated recently [11, 12, 13].

However, the elimination of the access transistor as well as the intrinsic characteristics of the memristive devices, also introduce several challenges. Such challenges should be addressed to enable the use of memristive devices as the next generation memory technology. Data reliability issues arise from the elimination of the access-transistors, where the logic value of non-selected devices might get affected during a write operation due to what is known as the *write disturbance* problem. Furthermore, successful write operations cannot be guaranteed for memristive devices, as memristors have a significant *write time variation*. Finally, memristive devices are prone to device failures, necessitating low-cost repair schemes to replace the failed devices in order to improve the lifetime of memristive memories. In this thesis, we focus on finding innovative and low-cost solutions to address these problems.

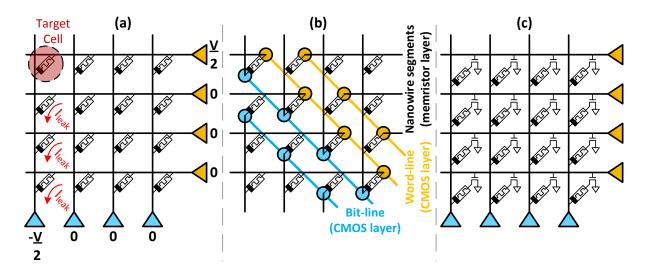

## 1.2 Addressing Write Disturbance

Write disturbance is an undesired coupling effect during write operation that affects several other memristors that share the same word- and/or bit-line [14, 11]. Due to the write disturbance, writing a logic value into one memristor may disturb the resistance of the line-shared memristors that store the opposite logic value. This effect is due to the access-transistor-free structure of the memory array, in which writing into a target cell also applies a notable partial voltage  $(e.g., V_w/2)$  across line-shared devices. The resistance degradation due to the write disturbance could accumulate over several write cycles and may eventually result in corruption or complete inversion of the stored logic value.

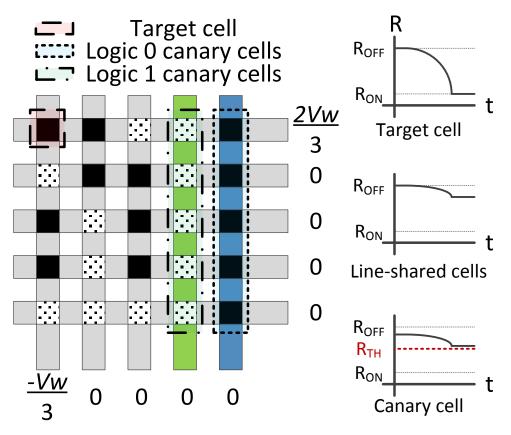

Here we propose a solution [15] to address this problem. Our solution confines the write disturbance effect to word-line-shared devices by applying asymmetric voltages to the word-line and the bit-line  $(e.g., -V_w/3)$  on target bit-line and  $2V_w/3$  on target word-line): bit-line-shared devices will experience less partial bias  $(e.g., V_w/3)$ , which has a very negligible write-disturbance effect. Then, two regular devices on each word-line are assigned as *canary cells*,

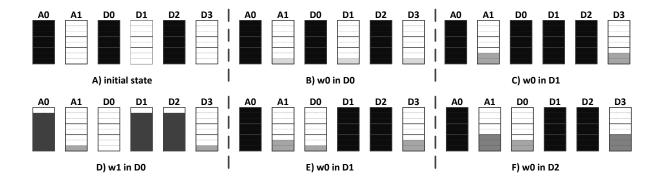

Figure 1.2: Write disturbance effect and solution. Applying  $V_w$  across the target cell effectively switches the target device to logic 1 (top-right), while degrading the logic 0 stored in other line-shared devices (middle-right). Two regular memristors per word-line, storing logic 1 and 0 respectively and placed on green and blue bit-lines, keep track of the worst-case logic 1 and 0 write disturbance effect on the line (bottom-right), and trigger a refresh operation when the degraded resistance reaches a close-to-corruption threshold,  $R_{TH}$ .

in which undisturbed logics 1 and 0 are stored initially. The canary cells cannot be accessed through the standard write interface and are meant to keep track of the worst-case, cumulative write disturbance effect for their corresponding logic on each word-line: while they are affected by the write disturbance effect similar to other memristors on the same word-line, they cannot be restored to the strong logic values via the standard write operations.

During a write operation on word-line W, the resistance values of W's two canary cells are monitored to avoid data corruption: As canary cells experience the worst disturbance accumulation of all devices on W (explained in the last paragraph), therefore, as long as the

resistance value of each canary cell is in its valid range, the validity of the data stored on other devices on W can be guaranteed. Whenever the resistance value of a canary cell reaches a known close-to-corruption threshold,  $R_{TH}$ , a refresh operation is triggered that refreshes all memristive devices on W. Fig. 1.2 illustrates write disturbance effect as well as the proposed solution. Chapter 2 discusses the write disturbance problem and the proposed solution in more details.

## 1.3 Addressing Write Time Variation

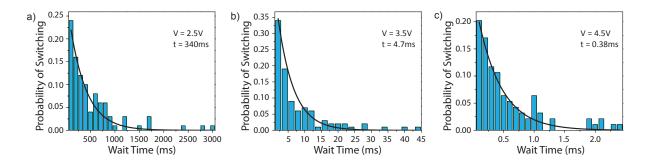

Another intrinsic issue with the memristive devices is the significant variation in their write time characteristics. The length of the required write pulse to switch the state of a device, varies from device to device, and even from cycle to cycle for the same device, and is not known beforehand. Hence, a method is required to find the proper length of a write pulse for each device/cycle to ensure a successful write operation.

Adaptive methods are commonly utilized for this purpose. In an adaptive write operation, the length of the write pulse is adjusted for individual devices by terminating the write pulse as soon as the target device completes the switching. This is typically done by monitoring (*i.e.*, sensing) the write-current through the target cell,  $I_{target}$ , to detect a sudden jump in the current that indicates the completion of switching.

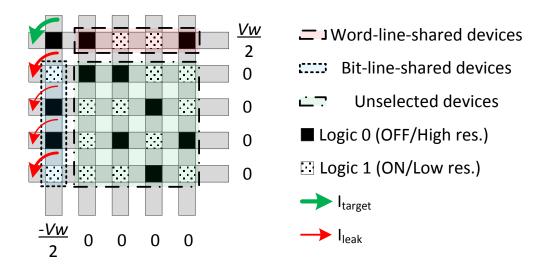

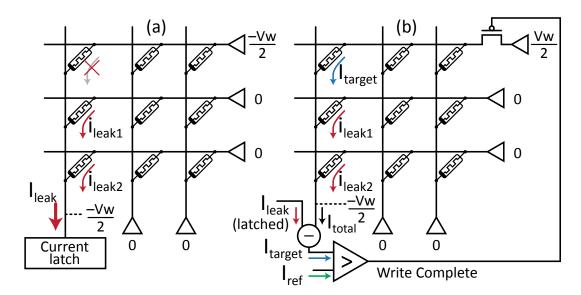

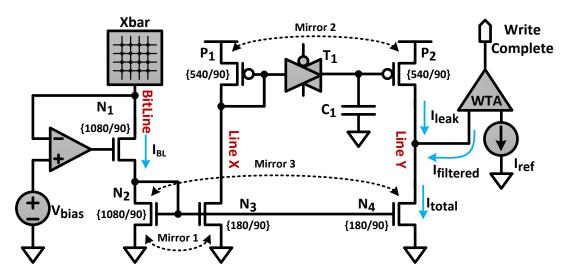

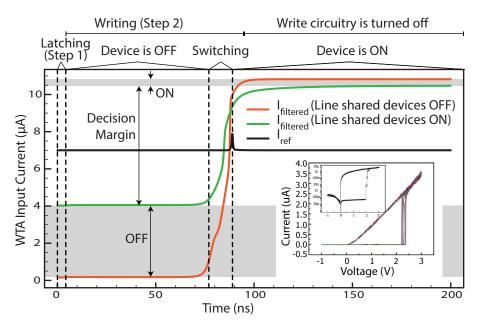

However, the existence of partially-selected devices in an ATF crossbar renders the conventional adaptive schemes useless: During the write operation, line-shared devices are partially-biased. Such a partial voltage introduces a *leakage current* on the target bit-line, as shown in Fig. 1.3. The leakage current is also data-dependent: the larger the number of ON devices on the bit-line, the greater the leakage current. Hence, in ATF crossbars,  $I_{target}$  is mounted on top of a considerable data-dependent leakage current  $I_{leak}$ , due to the bit-line-shared devices. A typical sensing circuitry cannot detect the switching in such noisy conditions.

Figure 1.3:  $V_w/2$  voltage application scheme for a write operation. Black (dotted white) cells represent stored logic 0 (1). Highlighted areas show the word- and bit-line-shared devices and the unselected devices respectively. A leakage current inversely proportional to the resistance of the bit-line-shared devices leaks into the bit-line during the write operation.

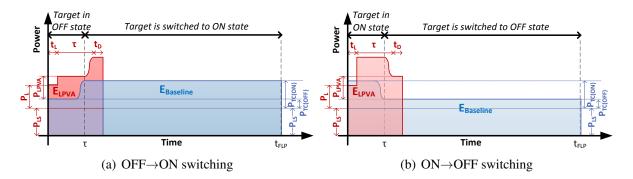

To address this problem, we propose a leakage-current-filtering mechanism. In this method, each adaptive write operation consists of two stages. In the first stage, the data-dependent leakage current of the bit-line-shared devices is latched. The latched  $I_{leak}$  is then subtracted from the total current observed on the bit-line in the second stage, to obtain the write-current contributed only by the target cell, *i.e.*,  $I_{target}$ . This filtered current is then sensed by a typical sensing circuit to detect the switching event. As there exists significant temporal variation in memristive devices for a complete switching of the write operation [16], this method yields a considerable energy saving in ATF memristive crossbars by enabling adaptive write operation in such crossbars. Chapter 3 provides more details on the write-time variation problem and the proposed solution.

## 1.4 Extending ReRAM Lifetime

Owing to their stochastic filamentary nature, memristive devices are prone to device failures [17]. Physical defects and endurance problems could lead to permanent "hard errors" that can adversely affect the lifetime of memristive memory modules. This necessitates low-cost repair schemes to replace the failed devices in order to improve the lifetime of memristive memories. Several solutions exist for conventional memory technologies to address hard errors, such as error correction codes (ECC) [18] and spare row/columns [19]. However, such solutions impose significant area and energy overheads on the memory module. When applied to memristive memories, such overhead becomes even more noticeable, considering the highly dense and ultra-low-power characteristics of memristive memories.

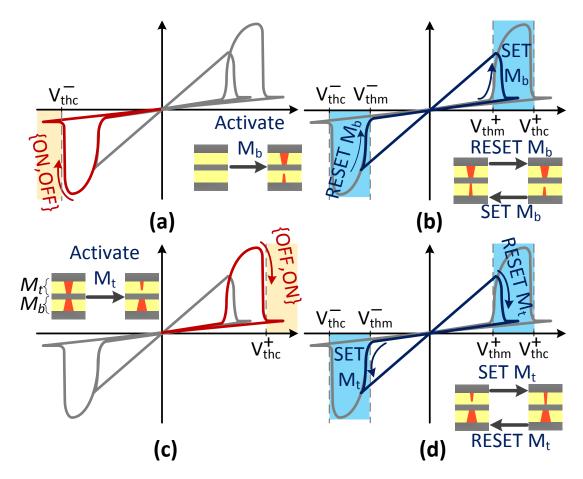

In chapter 4, we propose a zero-area-overhead in-place spare for each bit to repair the failed devices [20]. The proposed low-cost memory repair scheme is inspired by the possibility of stacking two memristive devices at the footprint of a single device at negligible extra cost, shown in *complementary resistive switches* [21]. The proposed method requires only minor modifications to the memory architecture. We further explore the possibility of using our in-place spares to enable lighter-weight ECC for the memory module while yielding a similar lifetime as a baseline ReRAM.

## 1.5 Permissions and Attributions

- Chapter 1 contains material taken from "Toward Large-Scale Access-Transistor-Free Memristive Crossbars," by Amirali Ghofrani, Miguel-Angel Lastras Montaño, and Kwang-Ting Cheng, which appears in IEEE Asia South-Pacific Design Automation Conference (ASPDAC), 2015.

- 2. Chapter 2 contains material taken from "Towards Data Reliable Crossbar-Based Memris-

tive Memories," by Amirali Ghofrani, Miguel-Angel Lastras Montaño, and Kwang-Ting Cheng, which appears in IEEE International Test Conference (ITC), 2013.

- 3. Chapter 3 contains material taken from "A Low-Power Variation-Aware Adaptive Write Scheme for Access-Transistor-Free Memristive Memory," by Amirali Ghofrani, Miguel-Angel Lastras Montaño, Melika Payvand, Siddharth Gaba, Wei Lu, Luke Theogarajan, and Kwang-Ting Cheng, which appears in ACM Journal on Emerging Technologies in Computing Systems (JETC), Vol. 12, Issue 1, July 2015.

- 4. Chapter 4 contains material taken from "In-place Repair for Resistive Memories Utilizing Complementary Resistive Switches" by Amriali Ghofrani, Miguel-Angel Lastras Montaño, Yuyang Wang, and Kwang-Ting Cheng, which is submitted to International Symposium on Low Power Electronics and Design (ISLPED), 2016.

# Chapter 2

# **Towards Data Reliable Crossbar-Based**

# **Memristive Memories**

A series of breakthroughs in memristive devices have demonstrated the potential of using crossbar-based memristor arrays as ultra-high-density and low-power memory. However, their unique device characteristics could cause data disturbance for both read and write operations resulting in serious data reliability problems.

This chapter discusses such reliability issues in detail and proposes a comprehensive yet low area-/performance-/energy-overhead solution addressing these problems. The proposed solution applies asymmetric voltages for disturbance confinement, inserts redundancy for disturbance detection, and employs a refreshing mechanism to restore weakened data. The results of a case study show that the average overheads of area, performance and energy consumption for achieving data reliability, over a baseline unreliable memory system, are 3%, 4%, and 19% respectively.

## 2.1 Introduction

The evolutionary improvement of current memory technologies cannot keep up with the fast-growing demand for denser, lower-power, and higher-bandwidth memories. In traditional transistor-based memories, high leakage current is becoming a major concern, and imprecision in the fabrication process is reducing the yield to an alarming level as the technology feature size continues to shrink [22]. To address such problems, several new memory technologies have been proposed. Redox-Based Resistive Switching Memories [4], Phase Change Memories [2], and Spin-Transfer Torque Magneto-resistive Memories [3] are some of the emerging technologies that could possibly serve as the next-generation memories for various applications. Among these candidates, metal oxide valence change ReRAMs (more generally referred as memristor [5]) are especially promising due to excellent scaling prospects, high endurance and high speed which can also be combined with great retention [23, 24].

A memristor is a passive non-linear resistive device, the resistance of which depends on the time integral of current applied across its terminals. Hence, it maintains its resistance in the absence of electrical current, which makes it suitable as a non-volatile memory element. The theoretical foundation of memristors goes back to 1971, when L. Chua predicted the existence of such a device [25]. However, it took researchers decades to unify the theory with experimental observations [26].

There have been very active research efforts recently, in both industry and academia on various aspects of memristors [27, 28, 7, 29, 30]. Memristive devices of a feature size 15 nm has been fabricated in academia [31] to form a crossbar-based memory array [11]. A crossbar architecture has been used due to its high density and regularity. It is anticipated that feature sizes as small as 3 nm are feasible [32] due to simpler and imprecision-resistant fabrication process [33]. The fabrication process is CMOS-friendly [34], and efficient methods exist to stack layers of such memories [35] which facilitate the integration of 3D memristive

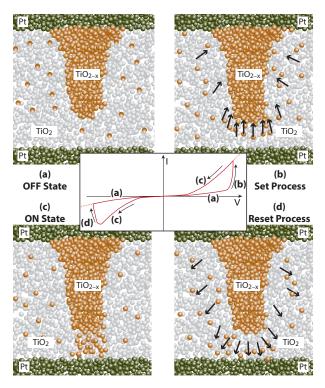

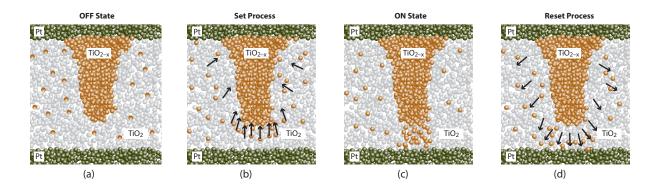

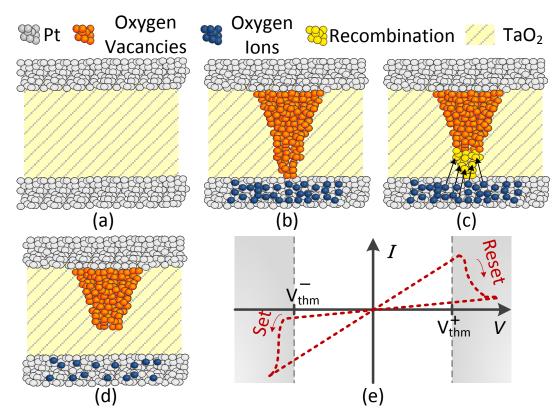

Figure 2.1: Memristor realization and typical hysteretic I-V behavior. (a) OFF state: An initial filament is formed during a one-time formation process. No conductive channel exists, thus the device is in high resistance state. (b) Set process: Applying a positive voltage drifts the dopants toward the filament, forming a channel, and decreasing the resistance. (c) ON state: a low-resistance channel is formed between the two electrodes. (d) Reset process: Applying a negative voltage repels the dopants and ruptures the channel, increasing the resistance.

memories with CMOS computing cores and decoding logic. Estimations as well as preliminary experimental measurements in their power consumption show considerable improvement over existing technologies [9, 23], as maintaining the data stored in memory does not incur any power consumption, and there is no active leakage current (as they are two-terminal passive elements). Reported experimental data show very fast write operations [36], while the speed of a read operation is limited by that of its CMOS sensing circuitry. All these characteristics make memristive memories ideal for integration with computing cores as an extremely dense and low-power on-chip non-volatile memory in the near future [6, 37].

However, there are some intrinsic characteristics of memristive memories that result in data reliability issues when memristors are used to form a crossbar-based memory. One issue

with such memories is an undesired coupling effect with which writing into one memristor may affect the data in several other memristors sharing the same word and/or bit lines. The effect is referred to as *write disturbance* [14, 11]. Moreover, as the resistance of a memristor is current-history-dependent, reading its resistance value by applying a read voltage across the memristor and measuring the resulting current can slightly change the strength of the stored data [38]. This effect is referred to as *read disturbance*. Both effects could be accumulative for a series of read/write operations which could result in data corruption and degrade the reliability of memory data. Thus these issues must be addressed before memristive memories can serve as system memories.

In this chapter, we first describe the data reliability issues of memristive memories in detail, and then present a comprehensive solution to address them. Our proposal is based on restraining the write disturbance effect, detecting data corruption by adding redundancy, and restoring/refreshing the disturbed data before corruption. We then evaluate the cost of the proposed solution in terms of the area, performance and energy overheads beyond the baseline crossbar structure.

The main contribution of this work is that it solves the data reliability problems of crossbarbased memristive memories. In addition, the proposed solution achieves the following goals:

- Incurring low area-, performance-, and energy-overheads.

- Using only standard memristive elements without adding any special elements, thus preserving the regularity and the scalability to achieve high-density memristor arrays.

The rest of the chapter is organized as follows: Section 2.2 provides the readers with the necessary background on memristors and memristive memory architectures. Section 2.3 describes the data reliability issues of memristive memories in detail. Section 2.4 presents our proposed solution followed by the experimental results in Section 2.5. We also elaborate on a comprehensive electrical model for the memristor crossbar array which is used to analyze the

performance and energy overheads of our solution. Section 2.6 concludes the chapter.

## 2.2 Background on Memristors

## 2.2.1 Device Physics

Figure 2.1 shows one possible realization of memristors. A simple memristor consists of three layers: two metallic electrodes, such as Pt, on top and bottom, and a doped thin film, such as TiO<sub>2</sub>, in between.

In the initial state, a filament of conductive  $TiO_{2-x}$  is formed in the non-conductive  $TiO_2$  film in an irreversible forming step [39]. However, the filament does not connect the two electrodes together, thus the device is in a High Resistance State (HRS). In order to turn ON the device, a sufficiently high positive voltage is applied across the electrodes of the device. This makes the filament connected to the top electrode attract positively charged vacancies in the oxide. This essentially grows the filament, as the vacancies start to drift in the applied electric field through the most favorable diffusion paths, and form a channel between the two electrodes [39]. Once such highly conductive channels are formed, the device is in Low Resistance State (LRS) and considered as ON.

To switch the device to the high resistance OFF state, a voltage with the opposite polarity should be applied on the electrodes. This repels away the vacancies that formed the conductive channel, thus shifting the device back to its high resistance state.

The state of the device and thus its resistance only changes when an electric current is passing through the device, and this change is continuous between two extremes: the  $R_{HRS}$  and the  $R_{LRS}$ . The change can be modeled according to the time integral of the current.  $R_{HRS}$  and  $R_{LRS}$  depend on the initial filament and are set in the forming step. However, forming free-devices are also under research [40].

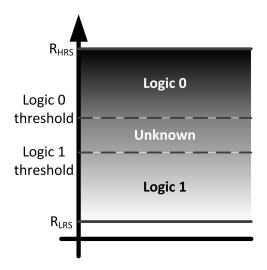

Figure 2.2: Different resistance regions.

## 2.2.2 Data Storage

In order to use memristors as memory elements to store binary data, the possible resistance range of the memristor is divided into three regions, as illustrated in Figure 2.2. Lower resistances are considered as logic 1 and higher resistances are considered as logic 0. Any resistance that falls in the marginal region in between is considered as unknown to ensure accurate distinction of logic 0 and 1.

Throughout this chapter, the term *value* is used to refer to a memristor's resistance value, while the actual binary data is referred to as *data*. Moreover, the term LRS (HRS) is generally used to refer to the range of resistance values representing logic 1 (logic 0).

## 2.2.3 Read and Write Operations

In order to write a binary data into a memristor, a proper write voltage  $(V_w)$  pulse of width  $t_{write}$  is applied across the device to set its resistance to the desired value.  $V_w$  and  $t_{write}$  are chosen so that the write pulse can completely shift the memristor's resistance to  $R_{HRS}$  or  $R_{LRS}$ , based on the polarity. That is, a negative pulse shifts the resistance toward  $R_{HRS}$  and a positive

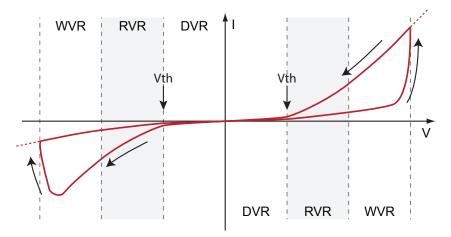

Figure 2.3: A typical I-V characteristic of a memristor. Three different voltage regions can be observed.

pulse shifts it toward R<sub>LRS</sub>.

The read operation decides if the resistance is in LRS or HRS. To do so, a read voltage  $(V_r)$  is applied across the memristor terminals. This results in the injection of a current through the memristor, the magnitude of which depends on the memristor's resistance. The stored data can be read by measuring this current.

#### 2.2.4 I-V Characteristics

Without loss of generality, Figure 2.3 can be used as a model of a memristor's I-V characteristics [41], based on which the following three regions can be defined:

• **Diode Voltage Region (DVR):** Applying a small voltage across the memristor terminals would not generate any noticeable current, and ideally would not change the device resistance. For example, this could be due to integrated Metal-Insulator-Metal (MIM) structure in series with the memristive layer. For a relatively small applied voltage, the bias would drop mostly across the MIM layer resulting in a negligible change of the resistance in the memristor.

However, as the resulting current is negligible regardless of the memristor resistance,

an applied voltage in this region cannot determine the stored data. This kind of diode behavior has been further strengthened by the introduction of complementary resistive switches [42].

- **Read Voltage Region (RVR):** As the applied voltage rises above a certain threshold, the resulting current starts to increase considerably. This current is still small and just slightly changes the resistance of the device, but is large enough to differentiate between the current of a memristor in HRS or LRS and determine the stored data. Voltages in this range (both negative or positive) can be used for the read operations.

- Write Voltage Region (WVR): By further increasing the applied voltage, the resulting current increases even further, having exponentially higher altering effect on the resistance of the memristor. This is due to the highly nonlinear kinetics typically associated with truly non-volatile memristors [24]. Such voltages can effectively change the memristor's state from LRS to HRS (or vice versa, depending on the polarity of the applied voltage), and are used to write data into a memristor.

## 2.2.5 Memory Architecture

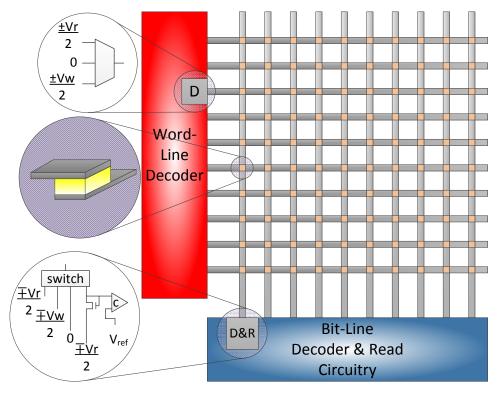

Different architectures have been proposed to utilize memristors to form a memory array. The most popular architecture is the crossbar organization, shown in Figure 2.4, which consists of two perpendicular layers of parallel nanowires forming a memristor at each cross section. The memory controller and address decoding circuitry are implemented in a peripheral CMOS subsystem [11].

However, the simple crossbar architecture encounters some scalability limitations: (1) voltage drop along long nanowires, can prevent effective application of read or write voltages on the desired cross-point, and (2) there is an upper limit on the maximum possible number of cross-points on each nanowire, imposed by noise margin requirements. To address such

limitations, in [43], authors proposed an innovative crossbar-based architecture called CMOL, that addresses the scalability issues by segmenting the crossbar nanowires, thus limiting their length and the number of cross-points per nanowire, while preserving the cross-point density.

In this chapter we use the simple crossbar architecture as the underlying memory architecture to illustrate the problem and our solution for the following reasons:

- It is easier, but without losing generality, to explain the concept using the simple crossbar architecture.

- Currently functional memristive memories are built in the form of a simple crossbar [11].

- The proposed solution can also be generalized to architectures such as [43], which are variants of the simple crossbar architecture, with minor modifications.

Here we are assuming an n-by-n crossbar memory, where  $M_{ij}$  refers to the memristor at the cross section of  $i^{th}$  row (also referred to as word-line) and  $j^{th}$  column (also referred to as bit-line).

## 2.2.6 Read and Write Operations in Crossbar

To write data into  $M_{ij}$ , a sufficiently wide pulse with an amplitude  $V_w$  in the WVR is applied across its terminals. Among several methods proposed to apply the  $V_w$  on the memristor [44, 30], the least intrusive one is applying  $V_w/2$  on the  $i^{th}$  word-line,  $-V_w/2$  on the  $j^{th}$  bit-line, and grounding all other word- and bit-lines.

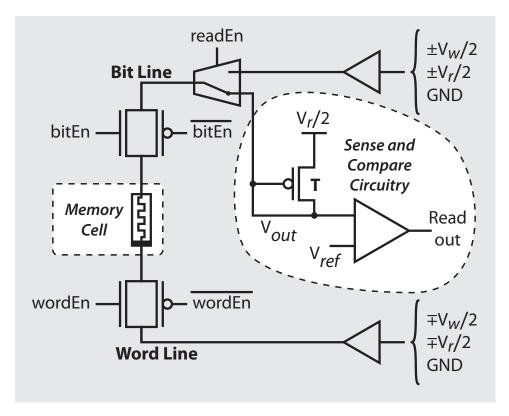

For a read operation, a sufficiently wide pulse of amplitude  $V_r$  in the RVR is applied across the memristor in a similar way. Then a sensing and comparing (S&C) circuitry is used to read the resistance value. One possible implementation of such circuitry is shown in Figure 2.5. As the current passing through a transistor is a function of its gate-source voltage, the diodeconnected transistor T in S&C circuitry makes the gate voltage ( $V_{out}$ ) follow the transistor's

Figure 2.4: Crossbar memory architecture. To access each memristor, a bit-line and a word-line are selected and applied with appropriate voltages which depend on the read or write access. Other lines are grounded.

current, essentially converting the current to a voltage. Since the transistor's and the memristor's currents are identical, and depend on the memristor's resistance,  $V_{out}$  reflects the value of the memristor's resistance. This voltage is then compared with a reference voltage ( $V_{ref}$ ) to determine the stored binary data. Ideally,  $V_{ref}$  is set between the  $V_{out}$  of a memristor in LRS and that of a memristor in HRS.

## 2.3 Data Reliability Issues in Memristive Memories

### 2.3.1 Read Disturbance

As current flows through the device during the read time, the device's resistance might slightly change. This *read disturbance* effect, mostly affects the target memristor, and not the

Figure 2.5: Sensing and Comparing circuitry. The comparator is an Op-Amp. The memristor's read current passes through transistor T. By connecting T's gate to its drain, the drain voltage  $V_{out}$  reflects the read current, as T's current depends on its  $V_{GS}$ .

other memristors in the crossbar array. The read voltage  $V_r$  is chosen to meet two criteria: (1) it is within RVR, and (2)  $V_r/2$ , the voltage applied to other memristors that share the same word-or bit-line with the target memristor, falls within the DVR. The second criterion ensures that the side-effect of the read operation on other line-shared memristors is negligible.

It should be noted that not every read operation is disturbing. For a given polarity of  $V_r$ , only one of the two logic values will be disturbed. For example, assume a positive  $V_r$  is applied for the read operation. If the stored data is logic 0 (i.e. its resistance value is within HRS), the resulting current will slightly shift its resistance toward  $R_{LRS}$ , making the stored data a weaker 0. However, if the stored data is logic 1 (i.e. LRS) the read current will have a healing effect, by shifting its resistance toward  $R_{LRS}$ , thus making the stored data a stronger 1.

Few articles in the literature addressed the read disturbance problem. In [38] the authors

propose the use of more complex read pulses consisting of alternating  $V_r$  and  $-V_r$  pulses to compensate for the destructive effect of the read operation. The alternate pulse, appended to the original read pulse, heals the destructive effect of the original read. However, this method doubles the read time and energy unnecessarily, as not all read operations are disturbing. The incurred overhead is particularly expensive as the read operations are more time consuming than the write operations for memristive memories.

In Section 2.4, we propose a couple of different restoring schemes to address this issue. Our solution reduces energy overhead of a reliable read operation by triggering data restoration only for disturbing reads and expedites the data restoration by utilizing other existing voltages in the system.

#### 2.3.2 Write Disturbance

Applying  $V_w/2$  and  $-V_w/2$  on the word- and bit-lines respectively to write data to a memristor has an undesired side effect: a  $V_w/2$  voltage (which falls within RVR) is also applied to all memristors that share either the word- or the bit-line with the memristor under write, which can slightly change their resistances. This effect can be disturbing or healing based on the written logic and the logic stored in the line-shared memristors: If memristor M stores a logic 0, writing a logic 1 (logic 0) to one of its line-shared memristors shifts M's resistance toward logic 1 (logic 0), weakening (strengthening) the stored logic. Same thing happens to all other memristors on the same line as the memristor-under-write and storing a logic 0. Note that the write disturbance problem is harder to deal with than read disturbance due to its broad impact. Figure 2.6 illustrates the effect of write disturbance on other line-shared memristors.

One solution is to add a switch (i.e. transistor) for each memristor to enable the isolation of a memristor from the rest of the memory array [45] (referred to as the 1T-1M technique), thus avoiding the destructive effect on the line-shared memristors. However, this technique

encounters the same technology scaling limitations as other transistor-based memories, due to the integration of the transistors.

In Section 2.4, we propose a solution to this problem by having additional ordinary memristors with known data content in the memristor layer. These extra memristors are used as references for detecting possible data corruption. This solution, to the best of our knowledge, is the first solution to the write disturbance problem that preserves the scalability advantages of the memristor technology.

#### 2.3.3 Disturbance Accumulation

The data reliability problem arises from the fact that the effects of read and write disturbances are accumulative and could eventually lead to data corruption. That is, a memristor's resistance can be shifted to the unknown region or even the opposite logic region. Figure 2.7 illustrates the disturbance accumulation after a sequence of write operations.

## 2.4 Addressing Memristor Data Reliability

Read and write disturbances are intrinsic features of memristors, which if not addressed, will result in frequent data errors, that cannot be handled only by system-level solutions such as Error Correction Codes (ECC). Here we try to prevent, detect, and resolve data errors caused by such disturbances by proposing a circuit- and architecture- level solution. However, ECC can always be used in conjunction with our method to provide additional protection.

#### 2.4.1 Read-Restore solution for Read Disturbance

The read-restore mechanism in [38] can be optimized for energy efficiency by detecting destructive reads. Then, only in case of a destructive read, the read operation is extended by

Figure 2.6: Write Disturbance.  $V_w$  is applied between times  $t_1$  and  $t_2$  to set the memristor-under-write to logic 1 (LRS). Black (white) memristors are in HRS (LRS). The data is written into the target memristor correctly (top-right). The white memristors sharing the same row or column are either not affected (top-left) or slightly healed (bottom-left), but the black ones are slightly disturbed (bottom-right).

applying a voltage of an opposite polarity to heal the destruction. That is, if the original read uses  $V_r$  ( $-V_r$ ) which causes disturbance, then the value is restored by applying  $-V_r$  ( $V_r$ ). Note that after the original read operation, both the stored data and the polarity of  $V_r$  are known. Hence it is known if the read operation was destructive or not. The peripheral memory controller circuitry is extended to differentiate a disturbing read from a non-disturbing one. Moreover, during restoration, the power-hungry S&C circuitry is turned off which helps minimizing the energy overhead.

However, restoring by applying  $V_r$  roughly doubles the read time, because the restoring pulse with the opposite polarity needs to have the same pulse width as the original read pulse in order to recover the disturbing effect.

To accelerate the restoring process, we propose applying a larger voltage  $V_w$  instead. This can improve the performance of restoring operation by one order of magnitude since the higher

Figure 2.7: Adding redundancy for corruption detection. (A) The initial state of the memory. The gray-scale color coding is used to show the resistance (i.e. Black for logic 0, and white for logic 1). Discrete resistance levels are assumed for illustration. A1 contains logic 1 and A0 contains logic 0, while the rest of cells have random data. (B) Status after writing logic 0 (w0) to D0. As D0's resistance was already R<sub>HRS</sub>, it is not changed. However, it shifts the resistance of the cells storing logic 1, referred to as 1-bits hereafter, (D1, D3 and A1) one level toward logic 0. (C) Status after w0 in D1. This changes the value of D1, and further weakens the data in 1-bits. (D) Status after writing 1 (w1) in D0. This changes the value of D0, weakens the data in memristors storing logic 0, called 0-bits hereafter, (D1, D2 and A0), but strengthens the data in 1-bits (A1 and D3). (E) Status after w0 in D1. This changes the value of D1, weakens the data in 1-bits (A1, D0, D3), and strengthens the data in 0-bits (A0 and D2). (F) Status after w0 in D2. At this point, the resistance value of A1 has reached the corruption level, which triggers the refreshing of 1-bits (A1, D0, D3). It can be observed that A1 has the worst-case disturbance among the 1-bits on the word-line, since other bits are either equally or less disturbed.

$V_w$  can heal the degraded data faster and more efficiently. Moreover, since the voltage  $V_w$  is already available, as it is used for the write operation, no extra voltage resources are needed to implement this method.

The potential problem with the idea of restoring by  $V_w$  is the write disturbance effect on other line-shared cells. However, our write disturbance solution described in the next subsection, resolves this side-effect and makes it possible to use the  $V_w$  for data restoration. Note that the width of a restorative  $V_w$  pulse is shorter than that of a normal write  $V_w$  pulse, thus its negative effect is also less significant.

Applying a higher restorative voltage  $V_w$  incurs higher energy consumption as: (1) larger current passes through the target memristor, (2) other line-shared memristors will experience

higher partial voltage  $V_w/2$ , which is in RVR region, thus generates more current. The energy and performance trade-offs of this method will be illustrated in Section 2.5.

#### 2.4.2 Redundancy-based Corruption Detection for Write Disturbance

Write disturbance affects all memristors sharing the same word- or bit-line with the target memristor. Our solution addresses the problem by employing the following principles: (1) limiting the disturbance to only those memristors sharing the same word-line with the target, (2) adding the capability of detecting the disturbance accretion, and (3) refreshing the disturbed data before it is corrupted.

The reason that both word- and bit-lines are affected by the write operation is the common assumption of applying symmetric voltages of  $\pm V_w/2$  on word-lines (bit-lines). In order to confine the domain of disturbed memristors, we propose asymmetric application of  $V_w$ , i.e., applying a higher absolute voltage on the word-lines, and a lower voltage which falls within the DVR of memristors, on the bit-lines. This makes it easier to address the write disturbance effect, by protecting the memristors on the bit-line from write disturbance at the cost of having more destructive effect on the word-line-shared memristors. For asymmetric voltage application, we propose applying  $2V_w/3$  on the word-line and  $-V_w/3$  on the bit-line, where we assume:

$$\frac{V_w}{3} = \frac{V_r}{2} \Rightarrow \frac{2V_w}{3} = V_r \tag{2.1}$$

This offers several advantages: (1) the bit-line-shared memristors will not experience write disturbance as  $V_w/3$  (i.e.  $V_r/2$ ) is always within the DVR. (2) The voltage applied to the word-line-shared memristors is equal to  $V_r$ , making it possible to read other cells in the same word-line simultaneously as the target memristor is written, by just enabling their S&C circuitry (i.e. sensing and comparing). (3) The number of required voltage levels remains the same (i.e.  $\{\pm 2V_w/3, \pm V_w/3, \text{GND}\}$  instead of  $\{\pm V_w/2, \pm V_r/2, \text{GND}\}$ ). Note that while other asymmetric

voltage applications are also feasible (i.e.  $\pm 3Vw/4$  and  $\mp Vw/4$ , etc.), that will increase the number of required voltage levels.

In the next step, we add the capability of detecting data corruption before the resistance change accumulates to the level of moving the memristor to the unknown state. The key difficulty for such detection is that if the correct data stored in the memristor is unknown, it is not possible to distinguish a weakened but correct data from an already corrupted (inverted) data.

To address this challenge, we propose the addition of an always-1 (A1) and an always-0 (A0) memristors in each word-line, as shown in Figure 2.8, to facilitate the detection of data corruption. Such bits are ordinary memristors, initially set to their corresponding states (LRS for A1 and HRS for A0). The only difference is that the user does not have write access to these cells, which can be ensured by a proper decoder design. There are two nice features of having such bits on the word-line: (1) As their correct binary data is always known, detection of data corruption for them becomes feasible, and (2) A write operation disturbs them in the same way as it disturbs other memristors on the same word-line. This makes them experience the worst possible case of accumulated disturbances among all cells on the same word-line, as they are never written into through standard memory accesses. Unlike them, other cells may have been written into by write accesses, which offset the accumulated disturbance.

This means that the A0 (A1) cell always has the weakest 0 (1) on their word-line. Thus, as long as the resistance value of the A0/A1 cells stays within the correct range, which can be ensured by continuously monitoring them, the integrity of the data stored in other cells on the same word-line can be guaranteed. Figure 2.7 illustrates the idea.

According to the asymmetric voltage application for the write operation which applies  $2V_w/3$ , that is  $V_r$ , to the memristors on the word-line, the value of other cells on the same word-line, thus the A0 and A1 cells, can be read and monitored simultaneously in every write cycle, using the same Sense and Compare (S&C) circuitry as shown in Figure 2.5.

Note that A0/A1 bits intend to detect a potential corruption *before it actually happens* to trigger the refreshing mechanism. Hence, the reference voltages ( $V_{ref}$ ) of the S&C circuitry on the A0 and A1 bit-lines, are chosen accordingly to ensure that the output of the comparator is asserted close to but *before* the corruption. When this happens, a refresh is required on the close-to-corruption logic. That is, if the output of the A0 (A1) bit-line is asserted, all the memristors on the same word-line storing a 0 (1) should be refreshed.

Note that here it is assumed that A0 and A1 are disturbed exactly in the same way as any other memristor on the word-line for clarification purposes. In general case, there might be small variations. The small resistance of the nanowires may result in a voltage drop along the line, which in turn causes the memristors to experience slightly different disturbing effect. This can be addressed by placing the A0/A1 bits closest to the word-line driver. Hence, they experience the worst case disturbance effect, as they are not affected by the voltage drop. Moreover, the disturbing effect might slightly differ among memristors due to the process variation. Conservative adjustment of A0/A1 corruption threshold ( $V_{ref}$ ), can take this variation into account to consider the worst case.

The next step is refreshing the close-to-corruption data. That is, if A0 cell's 0 becomes too weak, all the 0s on the line are refreshed. Refreshing the memristors storing logic 0 (0-bits) consists of two steps: (1) Finding out which memristors are 0-bits, for which all bits on the word-line of interest are read simultaneously, by applying  $V_r = 2V_w/3$  on the target word-line, grounding all bit-lines, and turning on the S&C circuitry, and (2) Refreshing the 0-bits simultaneously by applying a write voltage  $-2V_w/3$  on the word-line, and  $V_w/3$  on all the bit-lines whose corresponding memristors need to be refreshed, while grounding other bit-lines.

During the refresh procedure, A0 is also refreshed, thus it experiences the same refreshing imperfection, if any, that other 0-bits might encounter (e.g. not wide enough refreshing pulses, etc.). Similarly, during the refresh, the A1 bit on the same word-line will experience the same side-effects as other memristors storing logic 1 (e.g. disturbance of their value due to the

## Word Line A0 A1 D0 D1 D2 D3 2it Line

Figure 2.8: The configuration of the A0 and A1 on the word-line, assuming a word-line of 4 bits. All the word-lines would be similar.

refreshing of 0-bits). Hence the method is robust and will not be affected by such imperfections or side-effects.

The main parameter affecting the refresh rate is the *Write Disturbance Tolerance* (WDT), which is defined as the number of consecutive writes of only logic 1 (0) before corrupting the resistance of the line-shared memristors from a strong 0 (1) to the unknown state. The higher the WDT, the lower the number of refreshes needed. This number depends on two factors: (1) the applied write voltage  $V_w$ , as a lower write voltage has a smaller destructive effect, and (2) the non-linearity of the device's I-V curve, as higher non-linearity would help decrease the destructive side effects of write accesses. Hence, with technology advancement and introduction of devices with better non-linear kinetics, WDT would continue to improve. Measurements in [16] show that applying partial voltage of  $2/3V_w$  (i.e. the partial voltage that causes write disturbance) takes  $100 \times$  more time (i.e. 100 write operations) to completely change the state of the device compared to when  $V_w$  is applied. Hence, assuming equal division of the possible resistance range into logic 0, logic 1, and unknown regions, it can be deduced that WDT for current memristive devices is  $\approx 33$  (i.e.  $\frac{100}{3}$ ).

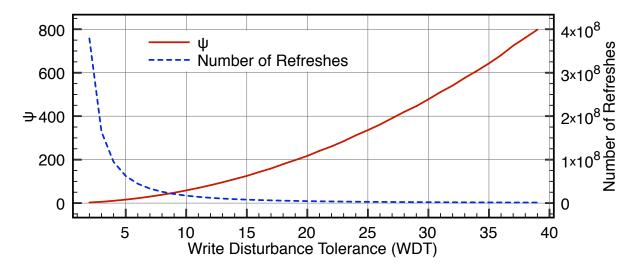

The average number of random write operations (logic 0 or 1) that necessitates a refresh is estimated based on WDT and is called  $\psi_{(WDT)}$  hereafter.  $\psi$  is used for energy and performance overhead estimation and is calculated by Monte Carlo simulations. In that, we count the number of refreshes required during a run of  $10^9$  write operations for different WDTs.  $\psi$  is then obtained by dividing the total number of write operations by the number of refreshes. Figure 2.9 shows the number of refreshes and the resulting  $\psi$  versus WDT.

As the disturbance effect is confined to the word-lines, the number of bit-lines has no effect on  $\psi$ . Moreover, as it is assumed that write operations on any memristor on the word-line affect the A0/A1 bits similarly, the number of memristors on the word-line does not affect  $\psi$  either. It should be noted that the proposed method guarantees the data integrity regardless of  $\psi_{(WDT)}$ , which only changes the refresh rate.

The energy and performance overheads of the proposed solution, as well as the effect of WDT on those metrics will be discussed in Section 2.5.

#### 2.5 Experimental Results

We derived an electrical model for crossbar-based memories using the Cadence Virtuoso tool, and designed the peripheral CMOS Comparing and Sensing, and decoding circuits. With these circuits and models, we simulated the electrical properties of the crossbar and evaluated the energy consumption and performance of the proposed solution.

In the following, we first elaborate on the electrical model, based on which we discuss the overhead figures of our solution.

#### 2.5.1 Electrical Model and Experimental Setup

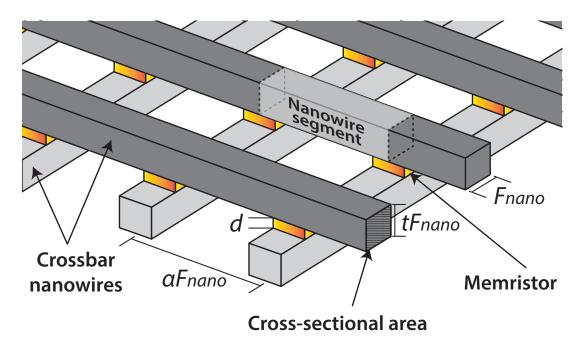

The crossbar structure is shown in Figure 2.10, which is represented as two perpendicular layers of parallel nanowires. The separation of parallel nanowires is  $\alpha \times F_{\text{nano}}$ , where  $F_{\text{nano}}$  is the width of the nanowire and  $\alpha$  would be 2 for the highest density.  $t \times F_{\text{nano}}$  in Figure 2.10 represents the thickness of nanowires.

In order to electrically model each nanowire, they are partitioned into nanowire segments of length  $\alpha F_{\text{nano}}$  and a resistor and a capacitor are used to model each segment. The resistance per nanowire segment can be extracted using the cross-sectional area and the resistivity  $\rho$  of the

Figure 2.9: The number of required refreshes in a run of  $10^9$  write operations (dashed) and the average number of writes before a refresh is required, called  $\psi$  (solid), for different WDT numbers. As WDT increases, the number of refreshes drops significantly, which in turn increases  $\psi$  considerably.

material:

$$R_{\text{seg}} = \rho \frac{\alpha F_{\text{nano}}}{t F_{\text{nano}}^2} = \rho \frac{\alpha}{t F_{\text{nano}}}$$

(2.2)

It is a well-known effect that in nanometric scales, the electrical resistivity  $(\rho)$  of a material increases when the mean free path of the electrons in the bulk material becomes comparable to the dimensions of the structure. The expected increment in the resistivity [46] is considered and is plugged in Equation 2.2 to estimate the resistance of the segment.

As for the capacitive effect, we use the results obtained in [37] in which the capacitance per nanowire segment can be approximated as:

$$C_{\text{seg}} \approx 0.48 \times 10^{-10} \varepsilon \alpha F_{\text{nano}}$$

(2.3)

where  $\varepsilon$  is the relative dielectric constant of the insulating material. For SiO<sub>2</sub>,  $\varepsilon = 3.9$ .

Hence, for a given feature size  $F_{\text{nano}}$ , pitch  $\alpha F_{\text{nano}}$ , and relative wire thickness t, we can

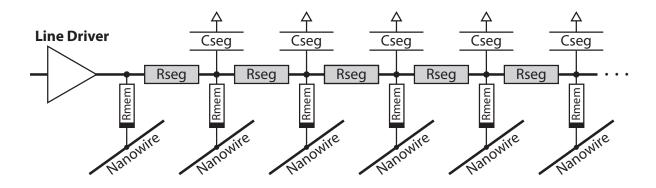

extract the capacitive and resistive components for each nanowire segment and form an RC network that is driven by lateral circuitry, as shown in Figure 2.11.

The memristive devices, formed at every cross-point, are modeled based on the model proposed in [47] which considers the dynamic characteristics of the device.

The peripheral S&C circuitry (i.e. Sense and Compare) is implemented in 45 nm CMOS technology and uses a latch-based comparator based on [48] to produce the output. This comparator only latches the output at selected times and is effectively turned off at other times for energy saving. However, the energy consumption of read operation is mainly consumed in the S&C circuitry.

Crossbar memories of size 1Kb to 64Kb are modeled and simulated to estimate the performance and energy overheads. We do not show simulation results for larger memory due to the following reasons: (1) The use of spice-level simulation limits the memory size for simulation. (2) Simple crossbar does not scale well for larger memories. Instead, as stated earlier, other crossbar-based architectures such as CMOL [43], enhanced from the simple crossbar but with a similar number of cross-points per nanowire segment, has a much larger capacity and thus addresses the scalability issue. While the proposed method can be adapted to these architectures, in order to show results of a significantly larger memory size under these architectures, the results must accompany an in-depth explanation of these architectures which is prevented due to space limitation. Therefore, we illustrate the trends using the memory sizes in the range of 1Kb to 64Kb (i.e. 32 to 256 cross-points per nanowire) under simple crossbar architecture. Larger memories under those enhanced architectures should follow a similar trend.

Table 2.1 summarizes the estimated energy consumption and timing numbers of baseline (unreliable) read and write operations, based on our electrical model. Memories with higher number of cross-points per nanowire have considerably higher energy consumption due to the increase in the number of partially activated line-shared devices.

Figure 2.10: Physical characteristics of crossbars

#### 2.5.2 Read Disturbance

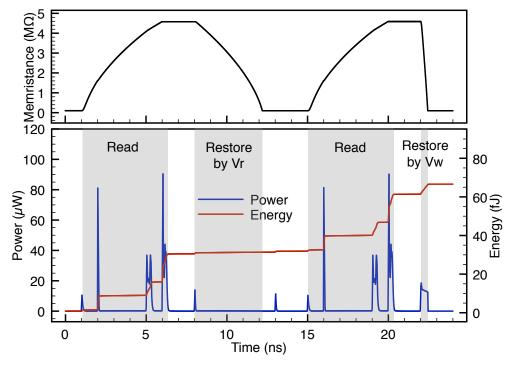

Figure 2.12 illustrates the timing and energy consumption of different restoring methods in our simulations. The estimated energy consumption and timing numbers of those methods are demonstrated in Table 2.2 for different memory sizes. Performance and energy overheads are calculated over the baseline read operation, based on the numbers shown in Table 2.1.

It can be observed in the sixth column that restoring by  $V_r$  has a prohibitively large ( $\approx 80\%$ )

Table 2.1: estimated energy consumption and timing numbers for baseline read and write operations

| Size                |                | Time (ns) |       |         | Energy (fJ) |       |         |

|---------------------|----------------|-----------|-------|---------|-------------|-------|---------|

| Xpoint per nanowire | Memory<br>(Kb) | read      | write | decoder | read        | write | decoder |

| 32                  | 1              | 5.00      | 2.44  | 0.30    | 36.7        | 37.2  | 160     |

| 64                  | 4              | 5.00      | 2.45  | 0.34    | 36.9        | 49.7  | 130     |

| 128                 | 16             | 5.00      | 2.48  | 0.38    | 37.6        | 74.1  | 120     |

| 256                 | 64             | 5.00      | 2.52  | 0.43    | 39.1        | 119.8 | 118     |

performance overhead, as the restorative pulse has approximately the same width as the original read pulse to heal the destructive effect. However, as shown in the eighth column, this method offers very low energy overhead (<1%), because the power-hungry S&C circuitry for the typical read operation is turned off during restore operation. Moreover, the restorative pulse width is a bit shorter than the original pulse, as it is directly applied to the bit-line, rather than being applied through the sensing circuitry that delays the effective application of the voltage. This also contributes to the lower energy overhead.

By applying a restorative  $V_w$  pulse instead, the performance overhead can be improved significantly (to  $\approx 8\%$ ), as shown in the seventh column. This is due to the high non-linearity of memristive devices: a higher voltage changes the device state significantly faster. However, as demonstrated in the ninth column, this method incurs higher energy consumption (<4%), since the partial voltage on the line-shared memristors is not in the DVR range anymore, thus injecting more current through those partially selected memristors.

It can be observed that the energy consumption increases with more memristive devices on each nanowire, as more devices will be partially activated due to the partial restorative voltage applied on the line-shared memristors. However, the effect of memory size on performance is negligible, as the increase in restoring time is small.

There is an energy-performance trade-off between the proposed restoring methods. However, considering the fact that memristors offer a huge improvement in energy rather than

Table 2.2: estimated energy consumption, timing, and overheads of the reliable read operation

Performance **Energy** Time (ns) Size Energy (fJ) Overhead (%) Overhead (%) **Xpoint per** restore restore restore restore restore restore restore restore nanowire by Vr by Vw by Vr by Vw by Vr by Vw by Vr by Vw 32 4.32 0.435 0.73 0.185 2.00 81.4 8.20 0.51

64 4.23 0.436 3.38 8.16 0.257 1.01 0.86 79.1 128 4.20 0.441 1.18 6.24 77.9 8.19 0.374 1.98 256 4.22 0.462 1.95 12.32 77.8 8.52 0.623 3.93

Figure 2.11: Electrical model of a nanowire in the crossbar

in performance, using restorative  $V_w$  pulses would be a better choice. Application of other restorative voltages is also feasible, but generating additional voltage levels would increase energy consumption and is not desirable.

#### 2.5.3 Write Disturbance

The performance overhead of our write disturbance solution is due to the refresh operation. The refresh procedure takes  $t_{read} + t_{write}$ , which is due to (1) simultaneous read of all memristors on the word-line, and (2) concurrent refreshing of those memristors storing the close-to-corruption data.

The meantime between refreshes (MTBR) depends on: (1)  $\psi_{(WDT)}$  (i.e. the average number of random writes before a refresh is required), and (2) the probability of having write accesses, as lower write probabilities ( $P_{write}$ ) slows down the accumulation of the write disturbances, thus decreases the refresh frequency. That is, if  $\alpha = P_{read}/P_{write}$ , then for every  $\psi_{(WDT)}$  write operations (that on average necessitate a refresh),  $\alpha \times \psi_{(WDT)}$  read operations have been performed, which increases the MTBR, thus reducing the performance overhead. Moreover, since each read/write operation should be decoded as well,  $t_{dec}$  (i.e. decoding time) is also considered for every operation.

Figure 2.12: Different restoring schemes. The top part shows the target memristor's resistance that is disturbed during the read operation. Applying  $V_r$  takes longer to restore the value with negligible energy overhead, while a restoring  $V_w$  pulse quickly restores the value but with larger energy overhead.

Equation 2.4 estimates the performance overhead of the proposed method:

Perf. Ovhd. =

$$\frac{t_{refresh}}{\text{Meantime between refreshes}}$$

$$= \frac{t_{read} + t_{write}}{\psi_{\text{(WDT)}} \left( (1 + \alpha) t_{dec} + \alpha t_{read} + t_{write} \right)}$$

(2.4)

Assuming equal read/write access probabilities, WDT equal to 33, and timing parameters extracted from simulation (Table 2.1), the performance overhead would be  $\approx 0.15\%$ , which is insignificant.

The energy overhead of the proposed method is due to the energy consumed for: (1) reading the A0/A1 bits, which is required for every write operation, and (2) performing the occasional refreshing process.

Refreshing energy overhead is caused by: (1) reading the value of all memristors on the

word-line, and (2) writing data back in those cells which should be refreshed. Hence, as multiple memristors should be read/refreshed, the refreshing energy also depends on the number of memristors on the word-line, WS, and the number of cells to be refreshed, RC. Since refresh procedure is triggered only when necessary, the refreshing energy should be divided among all the write operations performed between two refreshes (i.e.  $\psi_{(WDT)}$ ) to get the average energy overhead per write operation.

Equation 2.5 estimates the average energy overhead, where  $E_x$  shows the energy consumption of operation x:

$$Energy Overhead = \frac{2 \cdot E_{read} + \frac{WS \cdot E_{read} + RC \cdot E_{write}}{\Psi_{(WDT)}}}{E_{write} + E_{decode}}$$

(2.5)

Table 2.3 summarizes the estimated energy and performance overheads of the reliable write operation, calculated based on Equations 2.4 and 2.5 and the timing and energy numbers presented in Table 2.1. Numbers are calculated for exemplar WDT value equal to 33.

Memories with fewer number of cross-points per nanowire have lower ( $\approx$ 40%) energy overheads, as fewer memristors are written (refreshed) and the energy consumption per write operation is small, while decoding is done in CMOS and consumes more energy. As the number of cross-points per nanowire increases, the energy consumption due to refreshing increases since:

Table 2.3: Energy and performance overhead of the reliable write operation over the baseline write operation for different memory sizes.

|   | Xpoint per nanowire | Memory Size<br>(Kb) | Performance<br>Overhead (%) | Energy Overhead (%) |

|---|---------------------|---------------------|-----------------------------|---------------------|

| _ | 32                  | 1                   | 0.161                       | 38.7                |

|   | 64                  | 4                   | 0.159                       | 45.0                |

|   | 128                 | 16                  | 0.157                       | 47.3                |

|   | 256                 | 64                  | 0.156                       | 51.5                |

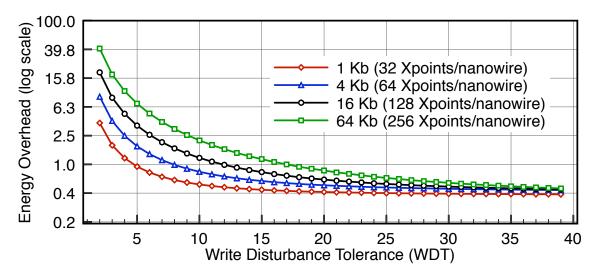

Figure 2.13: Write Disturbance Tolerance (WDT) vs. energy overhead of a reliable write over the baseline write.

(1) more memristors should be refreshed, and (2) the refreshing is more energy consuming due to the increase in the number of partially activated devices (due to the partial  $2V_w/3$  on the word-line-shared memristors). However, note that in scalable crossbar-based architectures such as CMOL [43], the number of cross-points per nanowire segment does not increase as the memory scales. Thus, when applied to such structures, our proposed method will not suffer from this increment in energy overhead.

Figure 2.13 shows the effect of different WDT's on reliable write operation's energy overhead for different memory sizes in logarithmic scale. Smaller Write Disturbance Tolerances (WDT) necessitate frequent refresh operations, thus increasing the energy overhead of a reliable write operation. As WDT increases, the refresh rate and thus the energy overhead of a reliable write operation decreases to  $\approx 40\%$ . It is also shown that having higher number of cross-points per nanowire increases the energy overhead, as described before.

As for area overhead, the proposed method adds only two memristors (i.e. A0 and A1) on each word-line regardless of the word size. Hence, the area overhead depends on the word size and is equal to  $\frac{2}{\text{Word Size}}$ . For an exemplar word-line containing 64 memristors, this overhead is

3.12%.

#### 2.5.4 Discussion on the Effect of the Device Variation