# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Specialization as a Candle in the Dark Silicon Regime

### **Permalink**

https://escholarship.org/uc/item/4dw7b9cb

#### **Author**

Goulding-Hotta, Nathan

## **Publication Date**

2020

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

Specialization as a Candle in the Dark Silicon Regime

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science

by

Nathan Goulding-Hotta

## Committee in charge:

Professor Steven Swanson, Co-Chair Professor Michael Bedford Taylor, Co-Chair Professor Rajesh Gupta Professor Ryan Kastner Professor Ramesh Rao

Copyright

Nathan Goulding-Hotta, 2020

All rights reserved.

| The Dissertation of Nathan Goulding-Hotta is approved, and it is  | acceptable in |

|-------------------------------------------------------------------|---------------|

| quality and form for publication on microfilm and electronically: |               |

|                                                                   |               |

|                                                                   |               |

|                                                                   | _             |

|                                                                   |               |

|                                                                   |               |

|                                                                   | Co-Chair      |

|                                                                   | C. Ch.        |

|                                                                   | Co-Chair      |

University of California San Diego 2020

# **DEDICATION**

To those who embrace humanity (and a sense of humor).

# **EPIGRAPH**

| Maybe in order to understand mankind, we have to look at the word itself. "Mankind." |

|--------------------------------------------------------------------------------------|

| Basically, it's made up of two separate words—"mank" and "ind."                      |

| What do these words mean? It's a mystery, and that's why so is mankind.              |

| —Jack Handey                                                                         |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

| Hofstadter's Law:                                                                    |

| It always takes longer than you expect,                                              |

| even when you take into account Hofstadter's Law.                                    |

|                                                                                      |

| —Douglas Hofstadter                                                                  |

|                                                                                      |

|                                                                                      |

# TABLE OF CONTENTS

| Signature           | e Page                                                                                                                                                                                                                                                                                                                   | iii                                           |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Dedication          | on                                                                                                                                                                                                                                                                                                                       | iv                                            |

| Epigraph            | 1                                                                                                                                                                                                                                                                                                                        | V                                             |

| Table of            | Contents                                                                                                                                                                                                                                                                                                                 | vi                                            |

| List of F           | igures                                                                                                                                                                                                                                                                                                                   | ix                                            |

| List of T           | ables                                                                                                                                                                                                                                                                                                                    | xi                                            |

| List of L           | istings                                                                                                                                                                                                                                                                                                                  | xii                                           |

| Acknow              | ledgements                                                                                                                                                                                                                                                                                                               | xiii                                          |

| Vita                |                                                                                                                                                                                                                                                                                                                          | xvii                                          |

| Abstract            | of the Dissertation                                                                                                                                                                                                                                                                                                      | xix                                           |

| Chapter             | 1 Introduction                                                                                                                                                                                                                                                                                                           | 1                                             |

| 2.1<br>2.2<br>2.3   | The Rise of Dark Silicon The Utilization Wall  2.1.1 CMOS Scaling Theory 2.1.2 The End of Dennard Scaling 2.1.3 The Utilization Wall Dark Silicon 2.2.1 The Dark Silicon Problem 2.2.2 Dark Silicon Solutions Specialization as a Candle in the Dark 2.3.1 Benefits of Specialization 2.3.2 Challenges of Specialization | 5<br>6<br>6<br>8<br>9<br>11<br>12<br>13<br>14 |

| 2.4                 | 2.3.3 Predictions Come True: Industry Trends                                                                                                                                                                                                                                                                             | 16<br>17                                      |

| Chapter 3.1 3.2 3.3 | 3 Conservation Cores.  System Overview.  C-core Architecture.  3.2.1 Baseline C-core Architecture.  3.2.2 Improvements to C-cores.  Integration with CPU.  3.3.1 Shared L1 Data Cache.                                                                                                                                   | 19<br>19<br>21<br>21<br>23<br>26<br>27        |

|                     | 3.3.2 Control Interface                                                                                                                                                                                                                                                                                                  | 27                                            |

| 3.4        | Programming and Execution Model                  | 29 |

|------------|--------------------------------------------------|----|

| 3.5        | Patching Support                                 | 30 |

| 3.6        | Toolchain for Automatic C-core Generation        | 32 |

|            | 3.6.1 C-core Selection                           | 32 |

|            | 3.6.2 Compiler Toolchain                         | 34 |

|            | 3.6.3 C-core Simulation                          | 35 |

|            | 3.6.4 ASIC Synthesis.                            | 35 |

|            | 3.6.5 Power Estimation                           | 36 |

| 3.7        | Summary                                          | 37 |

| 3.7        | Summary                                          | 31 |

| Chapter    |                                                  | 39 |

| 4.1        | Application Processors                           | 39 |

| 4.2        | Android's Suitability to C-cores                 | 40 |

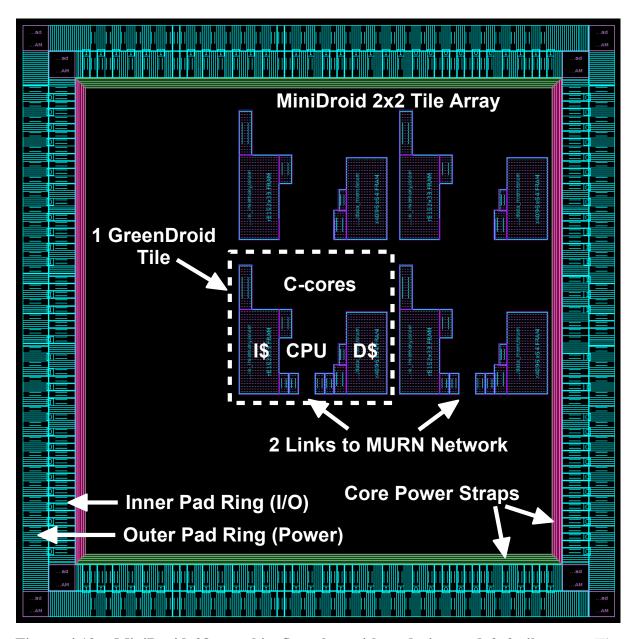

| 4.3        | GreenDroid Architecture                          | 43 |

|            | 4.3.1 System Architecture                        | 43 |

|            | 4.3.2 Tile Architecture                          | 44 |

| 4.4        | Generating C-cores for Android                   | 45 |

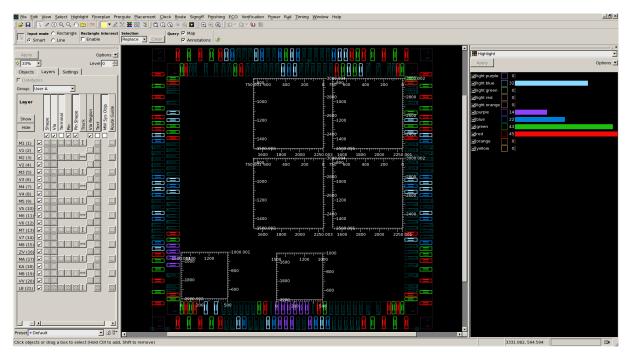

| 4.5        | Placed-and-Routed GreenDroid Tile                | 47 |

| 4.6        | GreenDroid in 28 nm: MiniDroid                   | 51 |

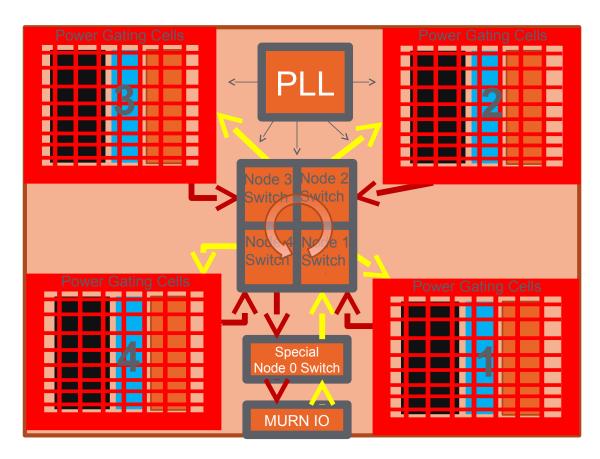

|            | 4.6.1 Chip Architecture                          | 51 |

|            | 4.6.2 Catalyst CAD Flow                          | 55 |

|            | 4.6.3 MiniDroid Physical Implementation          | 57 |

| 4.7        | Summary                                          | 60 |

| Chapter    | 5 Image Processing Unit                          | 62 |

| 5.1        | IPU Motivation                                   | 63 |

| 3.1        |                                                  | 64 |

| <i>5</i> 2 | 5.1.1 Image Processing and Stencil Computations  |    |

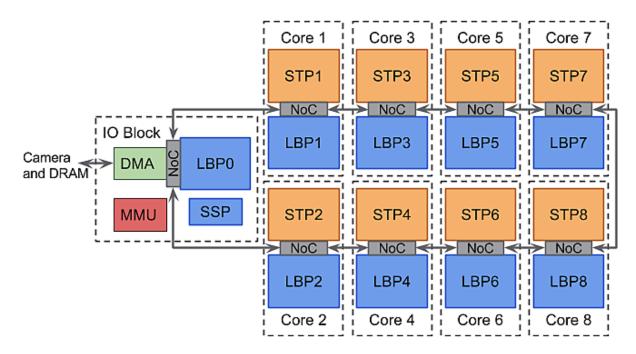

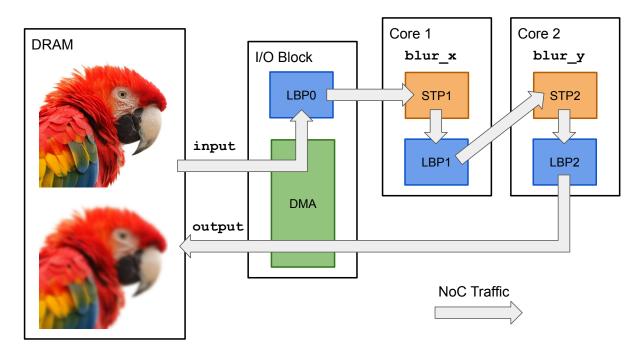

| 5.2        | IPU Architecture                                 | 67 |

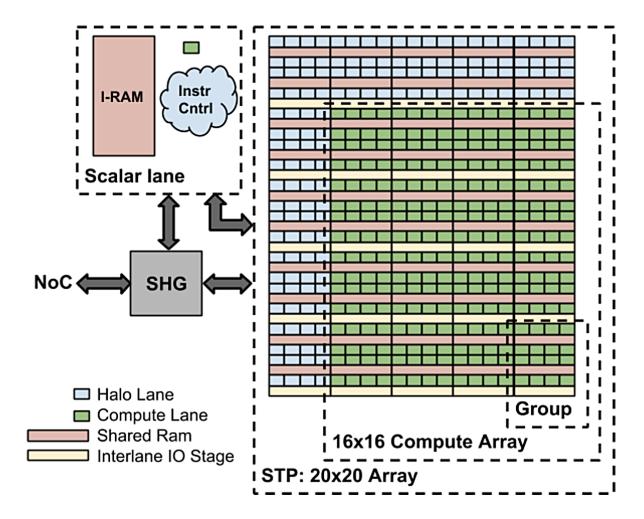

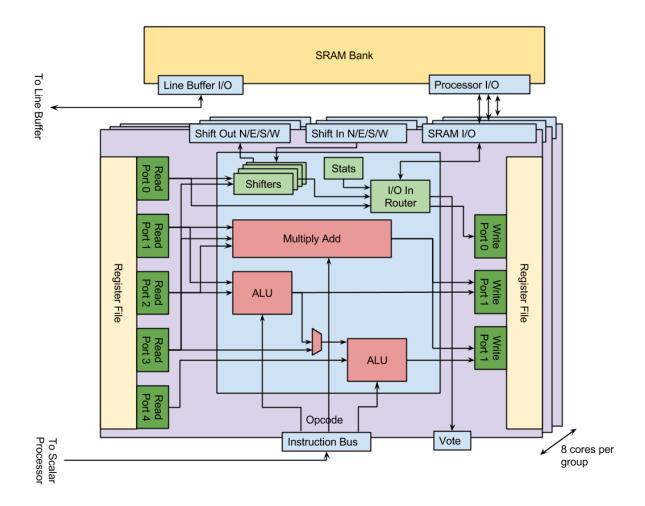

|            | 5.2.1 Stencil Processor                          | 68 |

|            | 5.2.2 Line Buffer Pool                           | 72 |

|            | 5.2.3 Network-on-Chip                            | 72 |

|            | 5.2.4 I/O Block                                  | 73 |

|            | 5.2.5 Scalability                                | 73 |

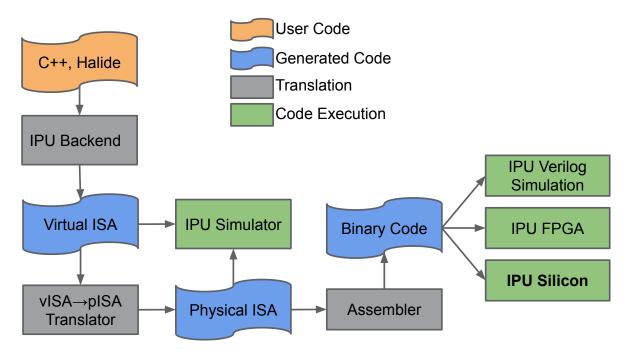

| 5.3        | IPU Programming                                  | 73 |

|            | 5.3.1 Halide Language                            | 75 |

|            | 5.3.2 Halide for IPU Programming                 | 76 |

|            | 5.3.3 Virtual Instruction Set (vISA)             | 77 |

|            | 5.3.4 Physical Instruction Set (pISA)            | 79 |

| 5.4        | Execution Model                                  | 82 |

|            | 5.4.1 PVC and IPU Runtime Boot Sequence          | 82 |

|            | 5.4.2 PVC and IPU Runtime Job Execution Sequence | 83 |

| 5.5        | Summary                                          | 84 |

| Chapter    | 6 Pixel Visual Core                              | 85 |

| Chaptel    | 0 1 1/01 1 10 111 1 10 11 1 1 1 1 1 1 1          | 0J |

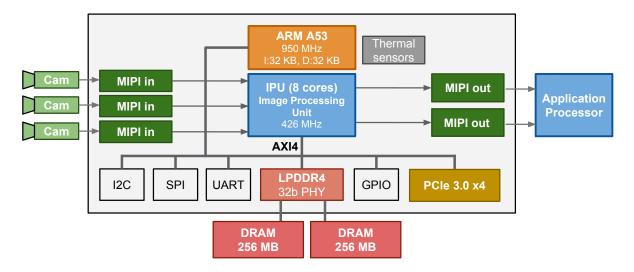

| 6.1      | Chip  | Architecture               | 86  |

|----------|-------|----------------------------|-----|

|          | 6.1.1 | Image Processing Unit      | 86  |

|          | 6.1.2 | Control Processor          | 87  |

|          | 6.1.3 | Interconnect               | 87  |

|          | 6.1.4 | I/O Interfaces             | 87  |

|          | 6.1.5 | DRAM                       | 89  |

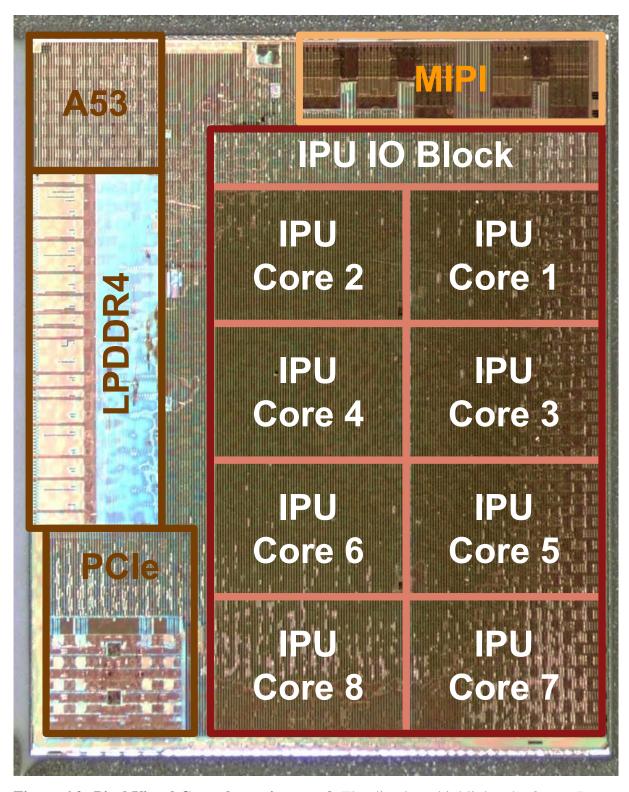

| 6.2      | Phys  | ical Implementation        | 89  |

|          | 6.2.1 | Process Technology         | 89  |

|          | 6.2.2 | SoC Die                    | 90  |

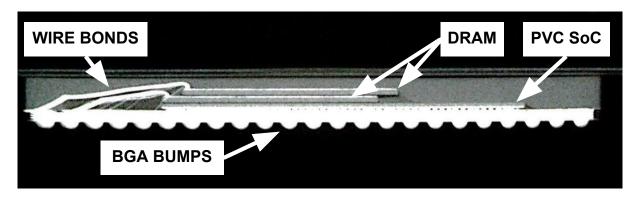

|          | 6.2.3 | System-in-Package          | 90  |

| 6.3      | Eval  | uation                     | 93  |

|          | 6.3.1 | Maximum Performance        | 93  |

|          | 6.3.2 | HDR+ Benchmarks            | 93  |

| 6.4      | Sum   | mary                       | 95  |

| Chapter  | 7     | Related Work               | 96  |

| 7.1      | Dark  | Silicon Research           | 96  |

| 7.2      | Mob   | ile Phone/SoC Accelerators | 99  |

| Chapter  | 8     | Synthesis and Conclusion   | 101 |

| Appendi  | хА    | Acronyms                   | 106 |

| Rihliogr | anhv  |                            | 108 |

# LIST OF FIGURES

| Figure 2.1.  | Spectrum of multicore designs in the dark silicon regime           | 10 |

|--------------|--------------------------------------------------------------------|----|

| Figure 2.2.  | Efficiency spectrum of general-purpose versus specialized hardware | 13 |

| Figure 2.3.  | iPhone accelerator count                                           | 16 |

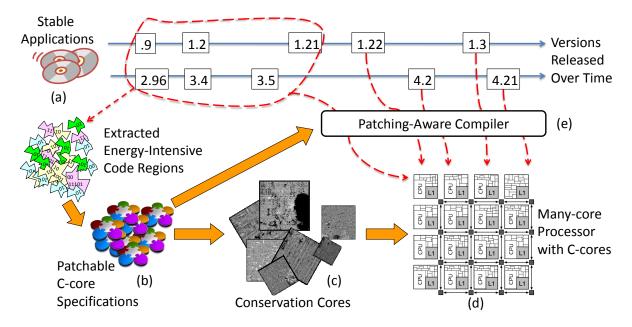

| Figure 3.1.  | Organization of a c-core-based system                              | 20 |

| Figure 3.2.  | Conservation core life cycle                                       | 21 |

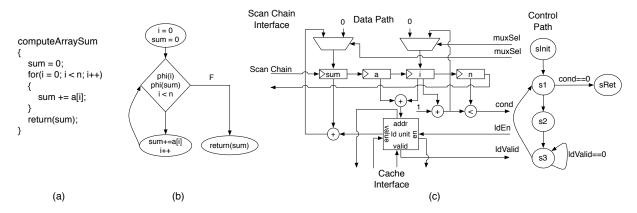

| Figure 3.3.  | C-core example translation from source code                        | 22 |

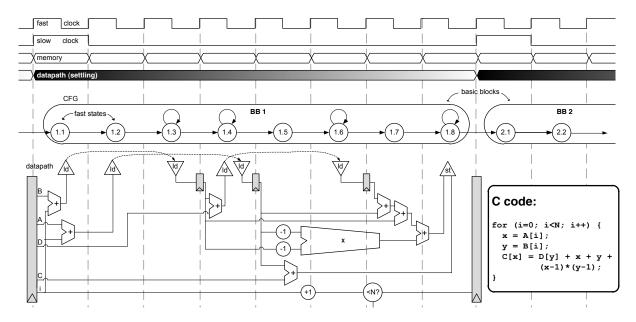

| Figure 3.4.  | Selective depipelining in c-cores                                  | 24 |

| Figure 3.5.  | Using selective depipelining to remove registers                   | 25 |

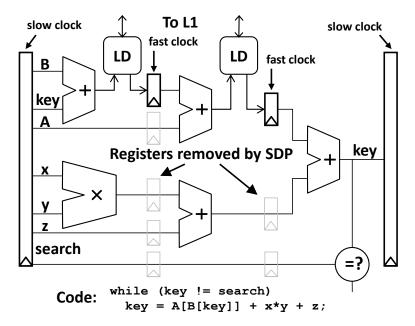

| Figure 3.6.  | C-core cachelet architecture                                       | 25 |

| Figure 3.7.  | C-core state tree address format                                   | 28 |

| Figure 3.8.  | C-core toolchain                                                   | 33 |

| Figure 4.1.  | Android software stack                                             | 41 |

| Figure 4.2.  | GreenDroid architecture and tile floorplan                         | 43 |

| Figure 4.3.  | Android dynamic execution code coverage                            | 46 |

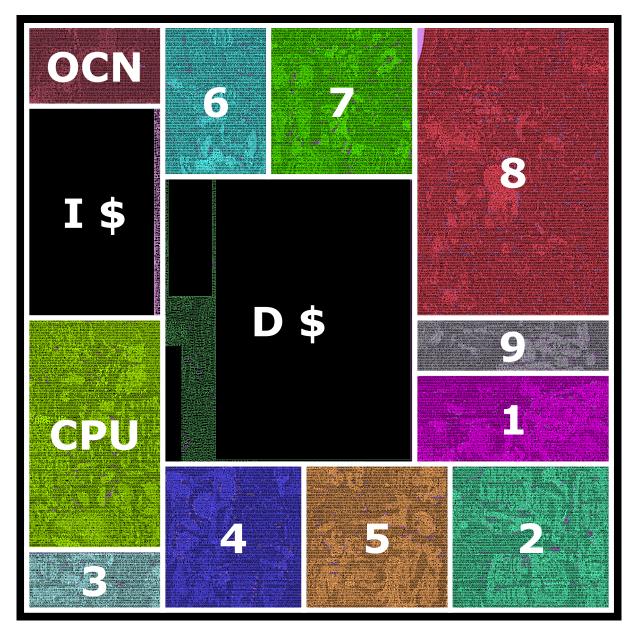

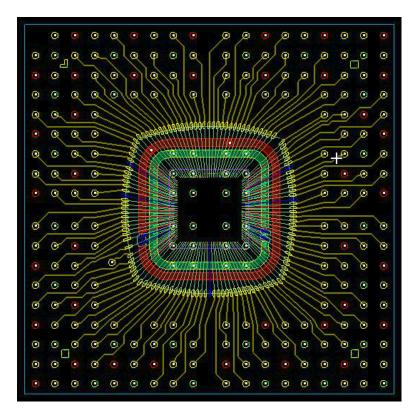

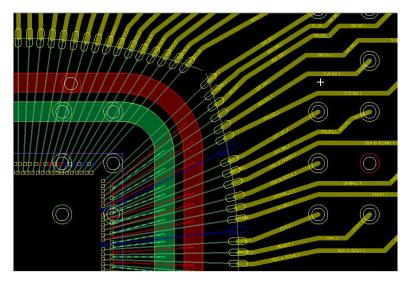

| Figure 4.4.  | Placed-and-routed GreenDroid tile with 9 Android c-cores           | 48 |

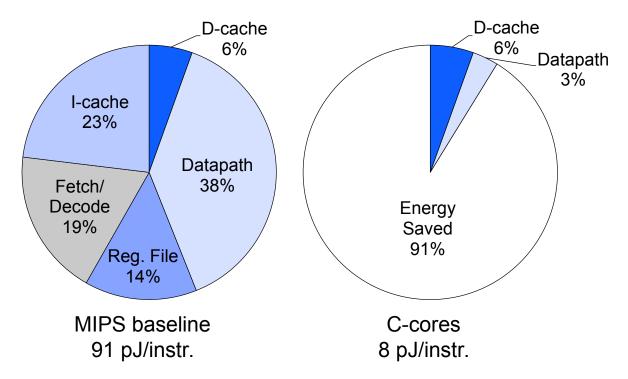

| Figure 4.5.  | Energy savings in c-cores compared to CPU                          | 49 |

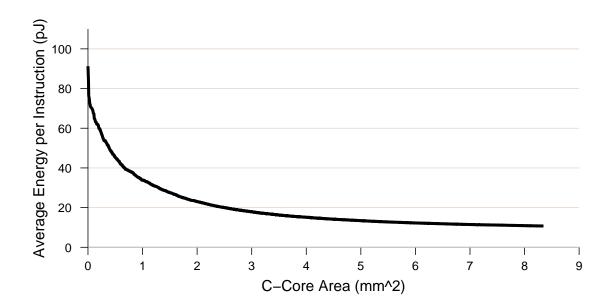

| Figure 4.6.  | Energy vs. area tradeoff for GreenDroid c-cores                    | 50 |

| Figure 4.7.  | MURN conceptual diagram with on-chip ring network                  | 52 |

| Figure 4.8.  | MURN network packet format                                         | 53 |

| Figure 4.9.  | MiniDroid package layout                                           | 56 |

| Figure 4.10. | MiniDroid package layout detail                                    | 56 |

| Figure 4.11. | Sketching a MiniDroid floorplan                                    | 58 |

| Figure 4.12. | MiniDroid 28-nm chip floorplan with pad ring and 2x2 tile array    | 59 |

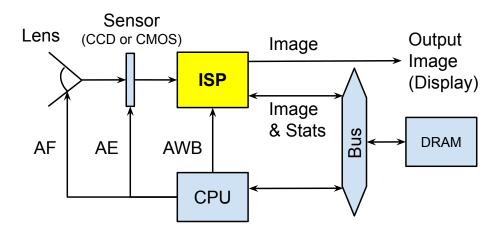

| Figure 5.1.  | Organization of a digital camera's lens, sensor, and ISP    | 64 |

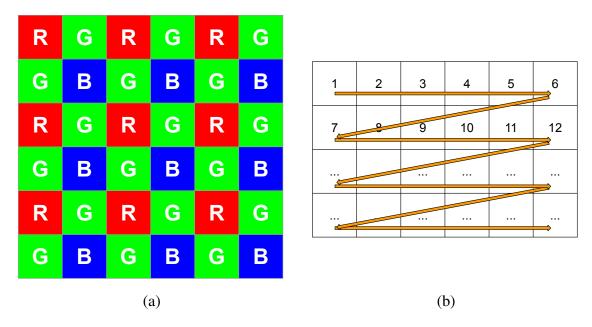

|--------------|-------------------------------------------------------------|----|

| Figure 5.2.  | Bayer pattern generated in raster scan order                | 65 |

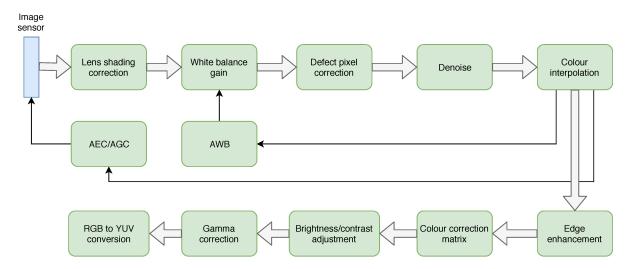

| Figure 5.3.  | Image Signal Processor (ISP) pipeline example               | 65 |

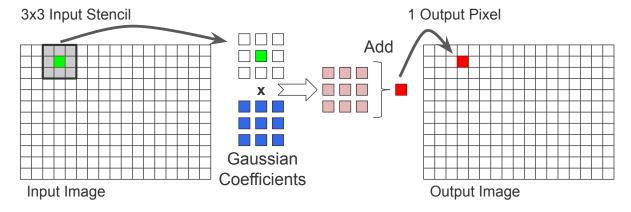

| Figure 5.4.  | Stencil computation with a 3x3-pixel support region         | 66 |

| Figure 5.5.  | Image Processing Unit architecture                          | 67 |

| Figure 5.6.  | IPU Stencil Processor architecture                          | 68 |

| Figure 5.7.  | Stencil Processor compute lane                              | 70 |

| Figure 5.8.  | IPU toolchain                                               | 74 |

| Figure 5.9.  | 3x3 blur mapped onto IPU                                    | 77 |

| Figure 5.10. | pISA VLIW instruction format                                | 80 |

| Figure 6.1.  | Pixel Visual Core SoC architecture                          | 86 |

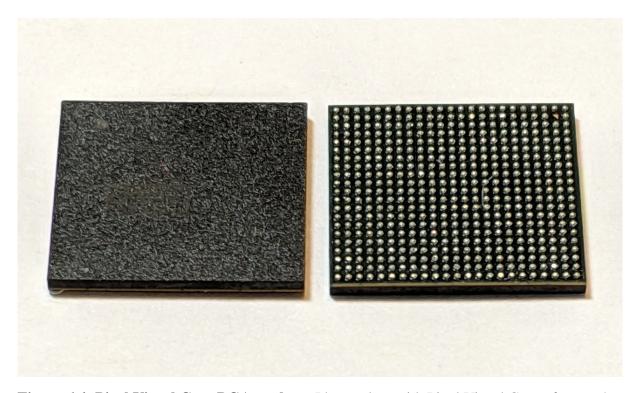

| Figure 6.2.  | Pixel Visual Core photomicrograph                           | 91 |

| Figure 6.3.  | X-ray radiograph of the Pixel Visual Core system-in-package | 92 |

| Figure 6.4.  | Pixel Visual Core BGA package                               | 92 |

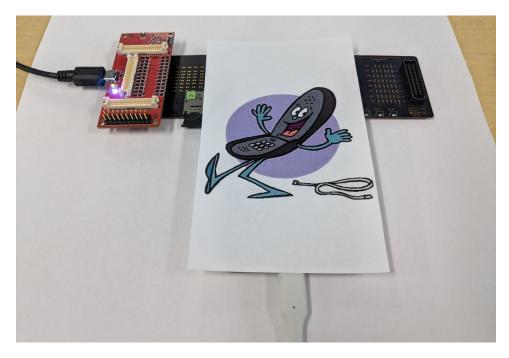

| Figure 6.5.  | Pixel Visual Core experimental setup                        | 94 |

# LIST OF TABLES

| Table 2.1. | CMOS scaling theory and the utilization wall                     | 7  |

|------------|------------------------------------------------------------------|----|

| Table 2.2. | Experiments quantifying the utilization wall                     | ç  |

| Table 4.1. | Android c-cores generated for one GreenDroid tile                | 49 |

| Table 4.2. | MiniDroid chip pads                                              | 54 |

| Table 4.3. | MiniDroid metal stack                                            | 60 |

| Table 6.1. | Pixel Visual Core power and performance results for HDR+ kernels | 94 |

# LIST OF LISTINGS

| Listing 3.1. | Example multicycle timing constraint from one c-core           | 36 |

|--------------|----------------------------------------------------------------|----|

| Listing 5.1. | Halide code for 3x3 blur [hal][DB18]                           | 75 |

| Listing 5.2. | Halide blur code from Listing 5.1, scheduled to run on the IPU | 76 |

| Listing 5.3. | vISA code for the 3x1 blur_x kernel from Listing 5.2           | 78 |

| Listing 5.4. | An example pISA instruction                                    | 81 |

#### **ACKNOWLEDGEMENTS**

This dissertation would not have been possible without the help of myriad giants. I'm eternally grateful to the people listed here and countless others for their support over the years. I'm only using first names to protect the innocent (and not-so-innocent—you know who you are).

First and foremost, I'd like to express my deepest appreciation for my amazing advisors, Professor Steven Swanson and Professor Michael Taylor. Ever supportive, they have guided and encouraged me since the beginning, and they never gave up on me finishing. Steve, a paper, grant, and code writing machine, you taught me the value of efficiency, higher standards of one's best effort, and how to draw a good graph (among other things). Michael, a tenacious uberhacker, you taught me to attempt the impossible, to persevere, and how to tell a great story about it afterward. You both gave me the foundation necessary to succeed in life after UCSD.

Thank you to my committee members, Professors Rajesh Gupta, Ryan Kastner, and Ramesh Rao, for your work that inspired me, your thoughtful feedback, and your willingness to serve on the committee for nearly a decade. Thanks also go to Julie Conner, for dusting off my file again and answering my never-ending questions.

The work presented in this dissertation was in close collaboration with a great number of highly-talented individuals. I'm especially thankful to my partners in crime, Jack and Ganesh. Jack, a walking Wikipedia, you taught me something about everything and everything about some things. Your generosity and creativity are exemplified by your primordial dinner parties. Ganesh, for someone so easygoing you sure get a lot done. It was a blast working with you late nights; I laughed the hardest with you. I'm also grateful to my other coauthors, especially Sravanthi, Qiaoshi, Sat, Vikram, and Jose. I could not have asked for a better research group.

Thank you to my classmates, office mates, roommates, foosball mates, and Chez Bob mates, for making UCSD such a fun place to be: Emmett, Laura, Adrian, Anshuman, Donghwan, Pat, Ravi, Zach, Jan, Joel, John, Justin, Ming, Hung-Wei, Edward, and so many more. Steve Checkoway saved me enormous time with his invaluable LATEX dissertation template [Che].

Special thanks to Professors Ranjit Jhala and Sorin Lerner, for stimulating impromptu discussions every time they stopped by our office providing (or in search of) snacks. And thank you to Ryoko-san, for filling the halls with music.

I'd like to acknowledge the support of my colleagues at UCSC and GlobalFoundries: Professor Jose Renau, Rigo, Luigi, Vito, Edward, Shobhit, and the whole group, for welcoming me with open arms, for teaching me how to tackle the CAD tools, and for always helping me fix one last DRC.

I'm extremely grateful to and humbled by my fellow Googlers and Paintboxers, a team of serious superstars: Adam, Albert, Alex, Andrea, Artem, Ashok, Asif, Ben, Bill, Bobbie, Cheng, Daniel, Dave, Don, Ed, Hua, Hyunchul, Jason, Ji, John, Jolin, Jon, Karthika, Masumi, Michelle, Neeti, Penny, Rolf, Scott, Sean, Sha, Todd, Trevor, Victor, and intern-turned-distinguished-software-engineer Professor Dave Patterson. A very special thank you to Ofer Shacham, who, with his big heart and dedication, showed me what it means to be a true leader.

Thank you to my friends and family for their constant support and patience. To my BFFs, Alex and Carlos, for their subtle and not-so-subtle encouragement until I finished. To my brother Kevin, for all his helpful "ideas;" to my sister Emily, whose bubbliness and inside jokes always make me feel special; and to my niece and nephews, who put a smile on my face during tough times writing this dissertation. To my loving and lovely parents, for instilling confidence and unbridled optimism in me, and for teaching me how to always see life with light and laughter.

Finally, my biggest and heartfeltest thank you to Kana, my partner, my best friend, and my favorite person in the world. (Don't tell my BFFs I said that.)

Thank you!

Chapters 2 and 3 contain material from "Conservation Cores: Reducing the Energy of Mature Computations," by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, and Michael Bedford Taylor, which has appeared in the Proceedings of the 15th International Conference on Architectural Support for Programming Languages and Operating Systems, ©2010 ACM. The dissertation author is a primary contributor and third author of this paper.

Chapters 2 and 4 contain material from "GreenDroid: A Mobile Application Processor for a Future of Dark Silicon," by Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Jonathan Babb, Michael Bedford Taylor, and Steven Swanson, which has appeared in Hot Chips 22: A Symposium on High Performance Chips, ©2010 IEEE. The dissertation author is a primary contributor and first author of this paper.

Chapter 3 contains material from "Efficient Complex Operators for Irregular Codes," by Jack Sampson, Ganesh Venkatesh, Nathan Goulding-Hotta, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, which has appeared in the Proceedings of the 17th International Symposium on High Performance Computer Architecture, ©2011 IEEE. The dissertation author is a primary contributor and third author of this paper.

Chapter 3 contains material from "QsCores: Trading Dark Silicon for Scalable Energy Efficiency with Quasi-Specific Cores," by Ganesh Venkatesh, Jack Sampson, Nathan Goulding-Hotta, Sravanthi Kota Venkata, Michael Bedford Taylor, and Steven Swanson, which has appeared in the Proceedings of the 44th Annual IEEE/ACM International Symposium on Microarchitecture, ©2011 IEEE/ACM. The dissertation author is a contributor and third author of this paper.

Chapter 4 contains material from "The GreenDroid Mobile Application Processor: An Architecture for Silicon's Dark Future," by Nathan Goulding-Hotta, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Po-Chao Huang, Manish Arora, Siddhartha Nath, Vikram Bhatt, Jonathan Babb, Steven Swanson, and Michael Bedford Taylor, which has appeared in IEEE Micro, ©2011 IEEE. The dissertation author is a primary contributor and first author of

this paper.

Chapters 5 and 6 contain material from "Pixel Visual Core: Google's Fully Programmable Image, Vision and AI Processor for Mobile Devices," by Jason Redgrave, Albert Meixner, Nathan Goulding-Hotta, Artem Vasilyev, and Ofer Shacham, which has appeared in Hot Chips 30: A Symposium on High Performance Chips, ©2018 IEEE. The dissertation author is a primary contributor and third author of this paper.

This dissertation was powered by 346 cups of tea.

#### VITA

| 2007  | B.S. in Electrical Engineering<br>New Mexico Tech                 |

|-------|-------------------------------------------------------------------|

| 2007  | B.S. in Computer Science<br>New Mexico Tech                       |

| 2011  | M.S. in Computer Science<br>University of California San Diego    |

| 2011  | C.Phil. in Computer Science<br>University of California San Diego |

| 2015– | Diplomatic Hardware Engineer<br>Google                            |

| 2020  | Ph.D. in Computer Science<br>University of California San Diego   |

#### **PUBLICATIONS**

Jason Redgrave, Albert Meixner, Nathan Goulding-Hotta, Artem Vasilyev, and Ofer Shacham, "Pixel Visual Core: Google's Fully Programmable Image, Vision and AI Processor for Mobile Devices," Hot Chips 30, Cupertino, CA, Aug. 2018.

Qiaoshi Zheng, Nathan Goulding-Hotta, Scott Ricketts, Steven Swanson, Michael Bedford Taylor, and Jack Sampson, "Exploring Energy Scalability in Coprocessor-Dominated Architectures for Dark Silicon," ACM Transactions on Embedded Computing Systems, Apr. 2014.

Vikram Bhatt, Nathan Goulding-Hotta, Qiaoshi Zheng, Jack Sampson, Steven Swanson, and Michael Bedford Taylor, "SiChrome: Mobile Web Browsing in Hardware to Save Energy," 1st Dark Silicon Workshop (DaSi), 39th International Symposium on Computer Architecture (ISCA), Portland, OR, Jun. 2012.

Nathan Goulding-Hotta, Jack Sampson, Qiaoshi Zheng, Vikram Bhatt, Joe Auricchio, Steven Swanson, and Michael Bedford Taylor, "GreenDroid: An Architecture for the Dark Silicon Age," 17th Asia and South Pacific Design Automation Conference (ASP-DAC), Sydney, Australia, Feb. 2012.

Ganesh Venkatesh, Jack Sampson, Nathan Goulding-Hotta, Sravanthi Kota Venkata, Michael Bedford Taylor, and Steven Swanson, "QsCores: Trading Dark Silicon for Scalable Energy Efficiency with Quasi-Specific Cores," 44th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Porto Alegre, Brazil, Dec. 2011.

Jack Sampson, Manish Arora, Nathan Goulding-Hotta, Ganesh Venkatesh, Jonathan Babb, Vikram Bhatt, Steven Swanson, and Michael Bedford Taylor, "An Evaluation of Selective Depipelining for FPGA-based Energy-Reducing Irregular Code Coprocessors," 2011 International Conference on Field Programmable Logic and Applications (FPL), Crete, Greece, Sep. 2011.

Manish Arora, Jack Sampson, Nathan Goulding-Hotta, Jonathan Babb, Ganesh Venkatesh, Michael Bedford Taylor, and Steven Swanson, "Reducing the Energy Cost of Irregular Code Bases in Soft Processor Systems," 19th Annual International IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM), Salt Lake City, UT, May 2011.

Nathan Goulding-Hotta, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Po-Chao Huang, Manish Arora, Siddhartha Nath, Vikram Bhatt, Jonathan Babb, Steven Swanson, and Michael Bedford Taylor, "The GreenDroid Mobile Application Processor: An Architecture for Silicon's Dark Future," IEEE Micro, Mar./Apr. 2011.

Jack Sampson, Ganesh Venkatesh, Nathan Goulding-Hotta, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, "Efficient Complex Operators for Irregular Codes," 17th IEEE International Symposium on High Performance Computer Architecture (HPCA), San Antonio, TX, Feb. 2011.

Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Jonathan Babb, Michael Bedford Taylor, and Steven Swanson, "GreenDroid: A Mobile Application Processor for a Future of Dark Silicon," Hot Chips 22, Stanford, CA, Aug. 2010.

Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, and Michael Bedford Taylor, "Conservation Cores: Reducing the Energy of Mature Computations," 15th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Pittsburgh, PA, Mar. 2010.

Nathan Goulding, Gopi Tummala, Emmett McQuinn, and Steven Swanson, "ReMOS Technology and the Mighty Morphin Microprocessor," Wild and Crazy Ideas session of ASPLOS 2010, Pittsburgh, PA, Mar. 2010.

Thomas Claytor, Joel Marquez, Lian-Jie Huang, Brett Nadler, Nathan Goulding, and Emily Prewett, "Ultrasonic Imaging Techniques for Early Breast Cancer Detection," Review of Progress in Quantitative Nondestructive Evaluation (QNDE), Golden, CO, Jul. 2007.

Nathan Goulding, Joel Marquez, Emily Prewett, Thomas Claytor, Lian-Jie Huang, and Brett Nadler, "Ultrasonic Imaging Techniques for Breast Cancer Detection," International Modal Analysis Conference, Orlando, FL, Feb. 2007.

Nathan Goulding, Jason Hamlet, Gar Hassall, Furqan Chiragh, and Scott Cason, "An Expressive Stereoscopic Vision Tracking System," Electrical Manufacturing Expo, Indianapolis, IN, Sep. 2006.

#### ABSTRACT OF THE DISSERTATION

Specialization as a Candle in the Dark Silicon Regime

by

Nathan Goulding-Hotta

Doctor of Philosophy in Computer Science

University of California San Diego, 2020

Professor Steven Swanson, Co-Chair Professor Michael Bedford Taylor, Co-Chair

For decades computer architects have taken advantage of Moore's law to get bigger, faster, and more energy-efficient chips "for free," reaping the benefits of silicon process improvements and shrinking technology nodes. Each new technology node brought exponentially more transistors, balanced by exponentially lower transistor switching power, allowing the power budget for a fixed silicon area to remain relatively constant. Architects could count on more transistors—and use them to build more complex designs—without substantially increasing the total power budget for a chip.

Today, however, rising CMOS leakage currents have limited further reductions in supply

voltage, leading to a power-limited utilization wall and an end to classical Dennard scaling. This breakdown results in a new regime of *dark silicon*, in which vast swaths of silicon area must remain "dark" (powered down or under-clocked) most of the time. Architects must turn to novel approaches to squeeze ever more performance out of every last square-millimeter of silicon.

This dissertation demonstrates that one viable approach to the dark silicon problem is *specialization*. Rather than relying solely on bigger, faster, general-purpose processors, chip architects have been increasingly augmenting their systems with special-purpose *accelerators*. These accelerators can speed up a given computation, allow it to run with less energy, or both. Using less energy frees up power and thermal budgets, allowing more computations to run in parallel and extending the computational capabilities we've come to demand from silicon.

This dissertation presents two such specialized architectures. The first is GreenDroid, a mobile application processor built with custom accelerators targeting Android. The accelerators are energy-saving specialized circuits called conservation cores, or c-cores. In a 45-nm process, just 7 mm<sup>2</sup> of silicon dedicated to c-cores covers approximately 95% of our Android workload. Powered by c-cores, GreenDroid uses 11× less energy on average than a general-purpose CPU.

The second is Pixel Visual Core, a commercial accelerator from Google that enables energy-efficient computational photography and machine learning in the Pixel 2 and Pixel 3 smartphones. Pixel Visual Core is powered by an 8-core Image Processing Unit with 4,096 16-bit ALUs capable of performing 3.1 Tera-operations/second in under 5 watts. Compared to a 10-nm general-purpose application processor, the 28-nm Pixel Visual Core runs key compute kernels  $3-6\times$  faster and with  $7-16\times$  less energy.

# Chapter 1

# Introduction

For more than five decades chip architects and programmers have taken advantage of Moore's law to get bigger, faster, and more energy-efficient chips "for free," reaping the benefits of silicon process improvements and shrinking technology nodes. Each new technology node brought exponentially more transistors, balanced by exponentially lower transistor switching power, which meant the power budget for a fixed silicon area remained relatively constant. Architects could count on more transistors—and use them to build more complex designs—without substantially increasing the total power budget for a chip.

Today, however, rising leakage currents have limited further reductions in supply voltage, so architects no longer see an exponential decrease in transistor switching power. As a result, chips have run up against a *utilization wall* [VSG<sup>+</sup>10]: With each successive process generation, the percentage of a chip that can actively switch drops exponentially because of power constraints.

The utilization wall and breakdown of classical CMOS scaling results in a new regime of *dark silicon* [GSV<sup>+</sup>10]. Under the dark silicon regime, vast swaths of silicon area must remain "dark" (powered down or under-clocked) most of the time. Architects must turn to novel approaches to squeeze ever more performance out of every last square-millimeter of silicon.

This dissertation demonstrates that one viable approach to the dark silicon problem is *specialization*. Rather than relying solely on bigger, faster, general-purpose processors, chip architects have been increasingly augmenting their systems with special-purpose *accelerators*.

These accelerators can speed up a given computation, allow it to run with less energy, or both. Using less energy frees up power and thermal budgets, allowing more computations to run in parallel and extending the computational capabilities we've come to demand from silicon.

Specialization itself is not new (e.g., in 1980 Intel introduced a discrete coprocessor, the 8087 floating point unit, to augment its 8086 line of processors). But what is new is the number and variety of specialized architectures that have gained popularity in recent years. This dissertation explains two such specialized architectures in detail. The first is a research prototype called *GreenDroid*, a multicore application processor with custom accelerators for Android. The second is a commercial chip called *Pixel Visual Core*, an image and machine learning accelerator in Google's Pixel 2 and Pixel 3 smartphones. Both architectures demonstrate the viability of specialization.

The dissertation is organized as follows. First, Chapter 2 explains the dark silicon problem and proposes specialization as a viable solution to continued scaling. The chapter starts with background material on CMOS scaling theory. We show how the classical scaling model has broken down under rising leakage currents, resulting in the utilization wall. Our research on the utilization wall predicted the rise of dark silicon, and we discuss some approaches to the problem. The most promising of these approaches is specialization. Our early research predicted the appearance of larger and larger numbers of specialized accelerators as a path forward in the dark silicon regime.

Chapter 3 describes our first approach to address dark silicon: a class of specialized accelerators called *conservation cores*. Conservation cores, or *c-cores*, are application-specific hardware circuits created to improve performance and reduce the energy consumption of computationally-heavy applications. Whereas traditional accelerators focus on improving performance, at a potentially worse, equal, or better energy efficiency, conservation cores focus primarily on reducing energy and energy-delay. This chapter describes the c-core architecture and execution model, as well as our toolchain for automatically synthesizing c-cores directly from program source code.

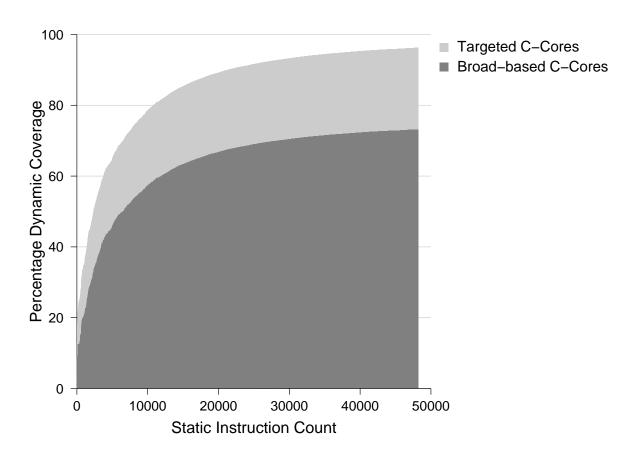

Chapter 4 shows how c-cores can be applied to mobile SoCs running Android. Android is well-suited for c-cores because the hot code is concentrated—in application libraries, the virtual machine, and Linux kernel—meaning a relatively small amount of silicon dedicated for hardware accelerators can cover a relatively large percentage of dynamic execution. We propose a c-core-based application processor called GreenDroid and detail its architecture. This chapter presents our experiments with a fully placed-and-routed GreenDroid tile that includes 9 c-cores generated from Android source code. We show how this tile could be included in a larger many-tile system to cover modern Android workloads. The dissertation author also collaborated with researchers at the University of California, Santa Cruz and GlobalFoundries to design a 28-nm, 2x2-tile version of GreenDroid called MiniDroid. This chapter concludes with the MiniDroid physical implementation in GlobalFoundries' 28-nm SLP process.

The remainder of the dissertation shows how our original predictions on dark silicon and the rise of specialization have come to pass in industry. After working on conservation cores and GreenDroid at UCSD, the dissertation author worked as part of a broad team at Google to design and implement a specialized programmable accelerator called the *Image Processing Unit*, or *IPU*.

Chapter 5 describes the IPU architecture in detail, starting with the motivation and need for a programmable image processing accelerator. Traditional Image Signal Processors (ISPs) are built from fixed-function hardware with limited computational power and minimal or no ability to update the hardened image processing algorithms after manufacture. In contrast, the IPU provides a programmable, energy-efficient, and high-performance compute engine that enables the latest computational photography techniques on mobile devices. We describe the IPU's architecture and programming model, and show how the IPU can accelerate HDR+ image processing.

Chapter 6 introduces the first implementation of the IPU in silicon, Google's *Pixel Visual Core*. Pixel Visual Core (PVC) is included in Google's Pixel 2 and Pixel 3 smartphones. It comprises an 8-core IPU accelerator along with control processor, on-chip interconnect, I/O

interfaces, and stacked DRAM dies in one system-in-package. PVC provides raw performance up to 3.1 Tera-ops/second (1.7 Tera-ops/sec arithmetic) on 16-bit integer data. It achieves about 0.84 pJ/op, or 1.5 pJ/op including only arithmetic operations without data movement. Despite a three-generation process gap, the 28-nm PVC runs key HDR+ kernels  $3-6\times$  faster and with  $7-16\times$  less energy than a 10-nm general-purpose application processor with DSP.

In the intermediate years between the author's work on GreenDroid and Pixel Visual Core, academia and industry have created many other examples of specialized silicon architectures. Chapter 7 reviews related work in dark silicon research, as well as accelerators for mobile, datacenter, and ambient computing domains. Each of these domains includes accelerators to optimize for different metrics—for example, performance per watt, total cost of ownership (TCO), latency, or ultra-low power. Yet all share a common goal of reaping the benefits of specialization.

Finally, in Chapter 8 we summarize the contributions of this dissertation in the context of related work in specialization and accelerators, and conclude with some final remarks.

# Chapter 2

# The Rise of Dark Silicon

For more than five decades chip architects and programmers have taken advantage of Moore's law [Moo65] to get bigger, faster, and more energy-efficient chips "for free," reaping the benefits of silicon process improvements and shrinking technology nodes. Each new technology node brought exponentially more transistors, balanced by exponentially lower transistor switching power, which meant the power budget for a fixed silicon area remained relatively constant. Architects could count on more transistors—and use them to build more complex designs—without substantially increasing the total power budget for a chip.

Today, however, limits on threshold voltage scaling have stopped the downward scaling of per-transistor switching power. Consequently, the rate at which we can switch transistors is far outpacing our ability to dissipate the heat created by those transistors. The result is a technology-imposed *utilization wall* [VSG<sup>+</sup>10] that limits the fraction of a chip that we can use at full speed at one time. The utilization wall forces chip architects into a new regime of *dark silicon* [GSV<sup>+</sup>10], in which the majority of a chip must remain off most of the time.

This chapter describes the fundamental breakdown of classical CMOS scaling in the face of rising leakage currents, the utilization wall, and the resulting dark silicon problem. But the dark silicon problem also presents a tremendous opportunity, ushering in a new computing era of extreme specialization.

# 2.1 The Utilization Wall

This section provides background in CMOS scaling theory, shows how traditional scaling breaks down in the face of rising leakage currents, and describes the resulting utilization wall.

## 2.1.1 CMOS Scaling Theory

Table 2.1 shows the classical CMOS scaling theory as described by Dennard [DGR<sup>+</sup>74]. The parameter S is the scaling factor between technology nodes, typically  $\sqrt{2} \approx 1.4 \times$ . In the classical scaling regime, transistor threshold voltage  $V_t$  continues to decrease as 1/S because of improvements in material science and transistor manufacturing. Meanwhile transistor supply voltage  $V_{dd}$  is constrained by  $V_t$  (typically  $V_{dd}$  must be at least  $3 \times$  higher), so  $V_{dd}$  also decreases as 1/S. Decreasing  $V_t$  leads to increasing leakage current, but leakage was still a small fraction of overall chip power in process nodes up to  $\sim$ 130 nm.

Each new process node also brings an  $S^2$  increase in the per-unit-area number of transistors, and a factor of S increase in clock frequency. This would increase power by the same factor ( $S^3$ ), but a 1/S lower  $V_{dd}$  brings with it a corresponding  $1/S^2$  decrease in per-transistor switching power, on top of 1/S lower gate capacitance, balancing the increase in per-transistor switching power. Multiplied together, this means the total chip power at full frequency remained relatively constant across process generations. In other words, in the classical scaling regime chip architects could still use all of the new transistors simultaneously—i.e., at fixed power, utilization U = 100% across process generations.

# 2.1.2 The End of Dennard Scaling

Starting beyond the 130-nm process node, rising transistor leakage currents started to become a significant fraction of total chip power and could no longer be ignored [HAP<sup>+</sup>05]. Leakage is highly dependent on threshold voltage  $V_t$ , so in the leakage-limited regime  $V_t$  can no longer continue scaling by 1/S [SKS<sup>+</sup>13]. As a result, supply voltage  $V_{dd}$  also stops scaling by

Table 2.1. CMOS scaling theory and the utilization wall The utilization wall is a consequence of CMOS scaling theory and current-day technology constraints, assuming fixed power and chip area. The parameter S is the scaling factor between technology nodes, typically  $\sqrt{2} \approx 1.4 \times$ . The Classical Scaling column assumes that  $V_t$  can be lowered arbitrarily. In the Leakage Limited case, constraints on  $V_t$ , necessary to prevent unmanageable leakage currents, hinder scaling and create the utilization wall.

| Param.           | Description                       | Relation                         | Classical<br>Scaling<br>(>130 nm) | Leakage<br>Limited<br>(<90 nm) |

|------------------|-----------------------------------|----------------------------------|-----------------------------------|--------------------------------|

| В                | power budget                      |                                  | 1                                 | 1                              |

| A                | chip size                         |                                  | 1                                 | 1                              |

| $V_t$            | threshold voltage                 |                                  | 1/S                               | 1                              |

| $V_{dd}$         | supply voltage                    | $\sim V_t \times 3$              | 1/S                               | 1                              |

| $t_{ox}$         | oxide thickness                   |                                  | 1/S                               | 1/S                            |

| W, L             | transistor dimensions             |                                  | 1/S                               | 1/S                            |

| I <sub>sat</sub> | saturation current                | $WV_{dd}/t_{ox}$                 | 1/S                               | 1                              |

| p                | device power at full frequency    | $I_{sat}V_{dd}$                  | $1/S^2$                           | 1                              |

| $C_{gate}$       | capacitance                       | $WL/t_{ox}$                      | 1/S                               | 1/S                            |

| F                | device frequency                  | $\frac{I_{sat}}{C_{gate}V_{dd}}$ | S                                 | S                              |

| D                | devices per chip                  | A/(WL)                           | $S^2$                             | $S^2$                          |

| P                | full die, full<br>frequency power | $D \times p$                     | 1                                 | S <sup>2</sup>                 |

| U                | utilization at fixed power        | B/P                              | 1                                 | 1/S <sup>2</sup>               |

1/S and must be held relatively constant. As shown in the Leakage Limited column of Table 2.1, device power at full frequency (p) no longer scales with each process generation.

### 2.1.3 The Utilization Wall

Traditionally, thanks to Moore's law, chip architects could count on exponentially more transistors with each process generation. They could use these transistors to build faster and more complex designs, such as superscalar, out of order, and multicore CPUs. And because individual transistor switching power also decreased, the total power for a fixed die area did not increase substantially.

Today, however, with the end of Dennard scaling, architects no longer see an exponential decrease in transistor switching power. As a result chips have run up against the *utilization wall*, which states:

With each successive process generation, the percentage of a chip that can actively switch drops exponentially because of power constraints.

Consider an example when scaling from 32 nm to 22 nm [Tay13]. In this example  $S = 32/22 = 1.4 \times$ . According to classical scaling theory, in the newer node we should have  $2 \times$  more transistors running at  $1.4 \times$  higher clock frequency, for a total of  $2.8 \times$  better computational capability. But the utilization wall limits us to achieving only  $1.4 \times$  of this benefit—a gap of  $2 \times$ . This is a serious problem that gets exponentially worse with every generation.

To quantify the impact of the utilization wall, we synthesized several datapaths using Synopsys Design Compiler and IC Compiler. Table 2.2 summarizes the results. For each process, we used the corresponding TSMC standard cell libraries to evaluate the power and area of a 40-mm<sup>2</sup> chip filled with 64-bit operators, to approximate the active logic in a mobile processor. Each operator is a 64-bit adder with registered inputs, running at maximum frequency for that process. In a 90-nm TSMC process, running this chip at full frequency would require 61 W, which means that only 8.2% of the chip could be used simultaneously within a 5-W power budget. In a 45-nm process, a similar design would require 163 W, resulting in just 3.1% utilization for

**Table 2.2. Experiments quantifying the utilization wall** Our experiments used Synopsys CAD tools and TSMC standard cell libraries to evaluate the power and utilization of a 40-mm<sup>2</sup> chip filled with 64-bit adders, separated by registers, which is used to approximate active logic in a mobile processor. At a fixed power budget the utilization drops exponentially with each process node, a phenomenon called the utilization wall.

| Process                 | 90 nm TSMC | 45 nm TSMC | 32 nm ITRS |

|-------------------------|------------|------------|------------|

| Frequency (GHz)         | 2.1        | 5.2        | 7.3        |

| mm <sup>2</sup> Per Op. | .00724     | .00164     | .00082     |

| # Operators             | 5.5k       | 24k        | 49k        |

| Full Chip Watts         | 61         | 163        | 320        |

| Utilization at 5 W      | 8.2%       | 3.1%       | 1.6%       |

the same 5-W power budget. Table 2.2 also extrapolates to 32 nm based on ITRS<sup>1</sup> data for 45-and 32-nm processes. Based on ITRS data the full chip running at full frequency would require 320 W, resulting in just 1.6% utilization.

As we'll show in the next section, the utilization wall fundamentally changes the way silicon architects must think about continued performance scaling.

# 2.2 Dark Silicon

Because of the utilization wall, ever smaller fractions of a chip can remain simultaneously active at full frequency. Huge regions of a chip must remain under-used, under-clocked, or entirely powered off most of the time—these regions are known as *dark silicon* [Mer09] [GSV<sup>+</sup>10]. The next two sections introduce the dark silicon problem, and recast dark silicon as an opportunity ushering in a new era in specialized computing.

#### 2.2.1 The Dark Silicon Problem

Dark silicon is a huge problem, and it gets exponentially worse with each process generation. For each new process node, instead of the expected 2.8× scaling in compute performance

<sup>&</sup>lt;sup>1</sup>International Technology Roadmap for Semiconductors [itr09], succeeded in 2017 by the International Roadmap for Devices and Systems [ird17].

# **Utilization Wall: Dark Implications for Multicore**

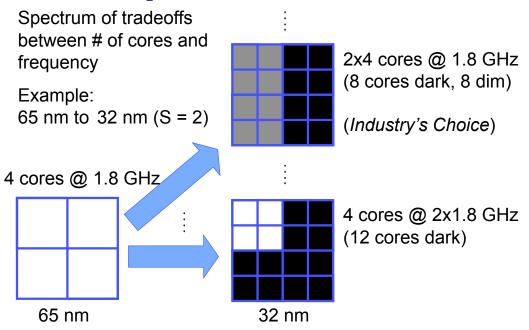

**Figure 2.1. Spectrum of multicore designs in the dark silicon regime** In newer process generations, architects can choose between more cores running at approximately the same clock frequency (dark silicon), or fewer cores running in bursts at higher clock frequencies (dim silicon). Figure from [GSV<sup>+</sup>10].

predicted by Dennard scaling, in the dark silicon regime we see only  $1.4\times$  improvement—a gap of  $2\times$ .

Industry's initial response to the dark silicon problem was switching to multicore designs. Figure 2.1 shows a spectrum of multicore options, with tradeoffs between the number of active cores and the clock frequencies of those cores. Architects can either have fewer cores running at higher clock frequencies, or more cores running at lower clock frequencies (an approach called "dim" silicon). Industry has primarily chosen the dim silicon approach.

Unfortunately, just switching to multicore designs is not a long-term scalable solution

[GSV<sup>+</sup>10][VSG<sup>+</sup>10][EBA<sup>+</sup>11]. Even with optimistic ITRS projections, multicore scaling is limited to a fraction of expected Moore's law gains.

## 2.2.2 Dark Silicon Solutions

As dire as the dark silicon problem appears, it also creates new opportunities for rethinking traditional computer architecture and chip design. In [Tay12], Taylor describes four potential approaches to handling the influx of dark silicon:

#### **Shrinking Silicon**

Per-chip cost is proportional to silicon area, so one approach to dark silicon is to just build smaller, cheaper chips. Although this could provide a short-term cost reduction, the approach has several problems at scale. The cost of the silicon die is just a fraction of the total chip cost after considering packaging, testing, NRE, and other costs. As dies shrink these other costs grow proportionally. Smaller chips are also not always feasible, since smaller chips can quickly become dominated by I/O pad area, which has not scaled as well as transistors. Finally, just building smaller chips forfeits the Moore's law performance benefits architects have come to depend on, meaning an end to "free" performance scaling. For these reasons shrinking chips is likely only a last resort, if we can find no more practical uses for dark silicon.

#### **Dim Silicon**

Dim silicon refers to general-purpose logic that is typically underclocked or used infrequently, in order to meet power constraints [SVGH<sup>+</sup>11][HRSS11]. Some dim silicon techniques include near-threshold voltage (NTV) computing [DWB<sup>+</sup>10][PSD<sup>+</sup>12], coarse-grained reconfigurable architectures (CGRAs) [PFM<sup>+</sup>08], building bigger caches, or temporal dimming techniques such as Intel's Turbo Boost [RNR<sup>+</sup>11] and computational sprinting [RLC<sup>+</sup>12].

#### "Deus Ex Machina" Silicon

In literature, *deus ex machina* refers to a solution that appears suddenly and unexpectedly. It is possible the dark silicon problem will be solved with new breakthroughs in semiconductors or device physics. Industry has a history of inventing techniques for one-time improvements to continue Moore's law scaling, for example high-k dielectrics, metal gates, FinFETs, or upcoming gate-all-around FETs [SAB+06]. However, these one-time breakthroughs are unpredictable and should not be relied upon.

#### **Specialized Silicon**

For decades, industry and computer architects have focused on general-purpose computing, relying on new process nodes to deliver more transistors, and using those transistors to build architectural improvements in order to continue performance scaling. A fourth approach to dark silicon is to instead increase the focus on *specialization* and special-purpose computing. Special-purpose accelerators can be 10-1000× faster and more energy-efficient than general-purpose processors running the same workloads [CMHM10]. As chips fill up with dark silicon, building specialized accelerators becomes an attractive option. Architects can put otherwise dark silicon to good use by building accelerators for specific, key workloads, freeing up the power and thermal budgets for additional computations. Effectively, specialization in the dark silicon regime lets architects trade a relatively "cheap" resource (silicon area) for a more valuable one (energy).

# 2.3 Specialization as a Candle in the Dark

Of the four approaches presented in the previous section, this dissertation argues that the most promising is specialized silicon. Specialized accelerators have been getting increasingly more attention lately because they let architects trade customized silicon area for performance and energy efficiency. At the heart of most accelerators' performance is the fact that architects

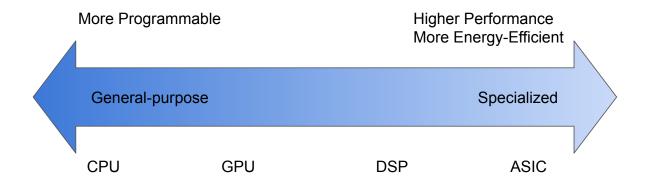

Figure 2.2. Efficiency spectrum of general-purpose versus specialized hardware Specialization presents a spectrum with tradeoffs between generality and efficiency.

have figured out how to attain parallel execution of the underlying algorithm, realized efficiently in hardware.

The challenge in creating accelerators is in reorganizing the algorithm to achieve parallel execution. Being able to do this effectively depends on the availability of exploitable parallelism in the algorithm and the ability to expose this parallelism in the form of an accelerator circuit without errors or excessive effort, complexity, or cost. In particular, creating accelerators for irregular code that's difficult to analyze or lacks parallelism is often challenging, if not impossible.

This section highlights the benefits of specialization as well as challenges, and we show that many of the challenges can be addressed with automation and layers of abstraction.

# 2.3.1 Benefits of Specialization

Specialized hardware can provide orders of magnitude better performance and energy efficiency compared to general-purpose hardware running the same workload [BVCG04]. General-purpose processors (e.g., CPUs) are flexible but relatively slow and inefficient compared to special-purpose hardware. This comes from extra overheads such as a general-purpose compute engine, complicated instruction fetch and decode logic, reorder buffers, branch predictors, and others. By reducing the scope and targeting a specific workload, specialized hardware can eliminate or reduce many of these overheads.

Specialization is not a binary design decision—rather, specialization presents a spectrum with tradeoffs between generality and efficiency (see Figure 2.2). General-purpose processors like CPUs, and to some extent GPUs, are more programmable and can handle more workloads, at a cost in energy efficiency [FKDM09]. More specialized hardware, such as DSPs, loop accelerators [CHM08] [AS01], and at the extreme end single-purpose ASICs [SAR+00], can run specific workloads with better performance and much better energy efficiency. Some approaches include [KAS+02], [VSL08], [WKMR01], and [YGBT09].

# 2.3.2 Challenges of Specialization

Specialization is not free from challenges, especially for coprocessor-dominated architectures (CoDAs) with 100s or even 1000s of accelerators [ZGHR<sup>+</sup>14]. This section describes some of the challenges of specialization and suggests ways to overcome or mitigate them.

#### **Complexity**

In general, simpler systems are easier to design, verify, use, and debug. Adding accelerators to a system introduces additional complexity. Hardware complexity comes from increased quantity and diversity of compute engines, each of which requires some form of interconnect (e.g., on-chip network or point-to-point connections) for inter-block communication and access to the memory system. To manage complexity, an accelerator system should use common communication protocols and interconnect when possible, for example ARM's AMBA protocols or Celerity's Tiered Accelerator Fabric [DXT<sup>+</sup>18].

Accelerators also introduce complexity during the chip design, verification, and manufacturing process. Each accelerator requires its own design and (maybe more importantly) verification efforts. Verification becomes especially tricky if the accelerators interact with each other. Accelerators increase the physical design effort (synthesis, place and route), and may complicate the top-level floorplan, where placement is key to good QoR. Each block also requires DFX (Design For Test and Manufacturability) structures such as scan chains and built-in

self-test (BIST) logic. Some of this increased complexity can be addressed with automation (e.g., high-level synthesis and high-level verification [KLG14]), and by using common interfaces between accelerators.

### **Programmability**

A system with heterogeneous accelerators can be difficult to program. Many accelerators support the C or C++ programming languages, but accelerators may also support more targeted languages or language subsets. For example, Nvidia GPUs can be programmed with OpenGL, OpenCL, or CUDA, while DSPs like Qualcomm's Hexagon can be programmed with domain-specific languages such as Halide [hal]. In addition to needing to learn a new language, accelerator programmers must also acquire a deep understanding of the hardware architecture in order to extract maximum performance. Help for these challenges may come from smarter, advanced compilers, and accelerators may use translation layers to hide some complexity from programmers (see Section 5.3.2 for examples).

#### **Scalability**

Dark silicon designs will some day require 100s or 1000s of accelerators [ZGHR<sup>+</sup>14], but scaling a chip to include so many coprocessors is a significant challenge [CGG<sup>+</sup>12]. The hardware for each accelerator must be designed and implemented. Part of this burden can be reduced through the use of automation and high-level synthesis tools (see Section 3.6 for an example). Each coprocessor also needs access to a general-purpose host CPU and the memory system. Section 3.1 describes how tiled architectures with replicated CPUs and a distributed memory system may help.

## **Limits on Efficiency Gains**

The benefits of any optimization are limited by Amdahl's law [Amd67], and specialized architectures are no exception. Performance and efficiency gains from accelerators are limited by the fraction of the workload that *can't* run on the accelerators, as well as overhead required to

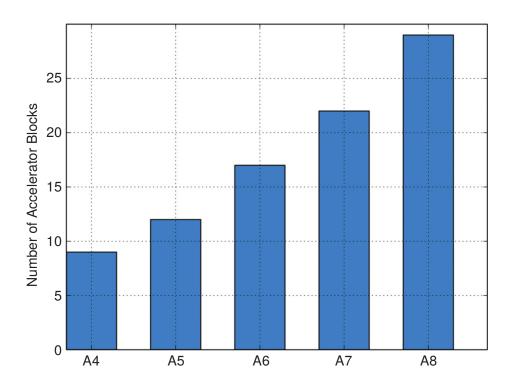

**Figure 2.3. iPhone accelerator count** The number of accelerators in Apple's iPhone SoCs has been rising exponentially. Figure from [SRWB15].

set up execution and transfer data. For example, even if 99% of a workload can be accelerated by  $1000\times$ , the remaining 1% of the workload limits the total system performance improvement to just  $91\times$ . Clearly, "nines matter," and the best way to get more nines is to target as much code as possible—not just regular, parallel code, but irregular, hard-to-parallelize code too. Chapter 3 presents one approach to do this.

### 2.3.3 Predictions Come True: Industry Trends

The author's initial research in dark silicon ([GSV+10][VSG+10][GHSV+11]) predicted a significant increase in the use of specialization and hardware accelerators. Ten years later we see that those predictions have come to pass in industry. Today, industry's mobile application processor SoCs couple multicore CPUs with GPUs and dozens of specialized accelerators. For example, Apple started building its own in-house A-Series SoCs, with more and more specialized accelerators every year. Figure 2.3 shows how this accelerator count has indeed been rising

exponentially. Today these accelerators offload a multitude of functions such as graphics, digital signal processing, multimedia encode/decode, cryptography, security, image signal processing, machine learning, I/O, and more ([Qua19][App19][Sam19][Hua19]).

In modern application processors, the vast majority of die area is now used for accelerators and specialized hardware. For example, of the Qualcomm Snapdragon 845's 95-mm<sup>2</sup> die, just 12% of the silicon area is occupied by the 8-core CPU and L3 cache [YW18], while the rest is reserved for GPU, I/O, modem, and accelerators.

## 2.4 Summary

This chapter has described the origin of dark silicon and its dark implications for chip design. We have shown how hardware specialization is a viable option for continued performance scaling in the dark silicon regime. Indeed, industry has agreed, by dedicating more and more silicon area to special-purpose accelerators in modern application processor SoCs.

The next two chapters present the author's work on an energy-saving specialized architecture called conservation cores, and then show how conservation cores can be built for Android in an application processor called GreenDroid.

## Acknowledgements

This chapter contains material from "Conservation Cores: Reducing the Energy of Mature Computations," by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, and Michael Bedford Taylor, which has appeared in the Proceedings of the 15th International Conference on Architectural Support for Programming Languages and Operating Systems, ©2010 ACM. The dissertation author is a primary contributor and third author of this paper.

This chapter also contains material from "GreenDroid: A Mobile Application Processor for a Future of Dark Silicon," by Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino

Garcia, Joe Auricchio, Jonathan Babb, Michael Bedford Taylor, and Steven Swanson, which has appeared in Hot Chips 22: A Symposium on High Performance Chips, ©2010 IEEE. The dissertation author is a primary contributor and first author of this paper.

# Chapter 3

## **Conservation Cores**

In the previous chapter we explained the dark silicon phenomenon and suggested specialized architectures as a path forward. This chapter introduces one such specialized architecture, conservation cores [VSG<sup>+</sup>10]. Conservation cores, or c-cores, are highly specialized, application-specific hardware circuits derived automatically from program source code, with a primary goal of reducing energy. Whereas traditional accelerators focus on improving performance, at a potentially worse, equal, or better energy efficiency, conservation cores focus primarily on reducing energy and energy-delay, with performance acceleration as a secondary goal.

This chapter presents an overview of c-core-based systems and then explains the c-core architecture and programming model. We describe the ability of c-cores to stay useful even as the source code evolves, through a set of generalized datapath operators and firmware-patching mechanisms. We also describe our toolchain for automatically generating c-core hardware directly from source code (nearly unrestricted C), along with simulation models and synthesized, placed, and routed netlists.

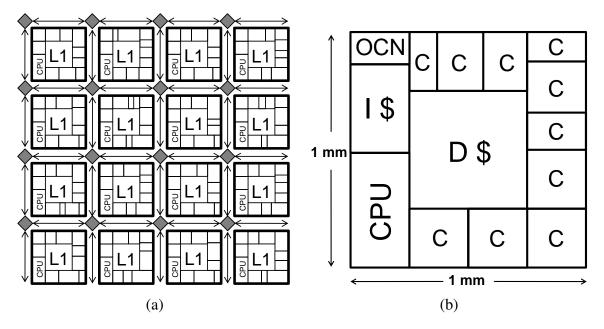

## 3.1 System Overview

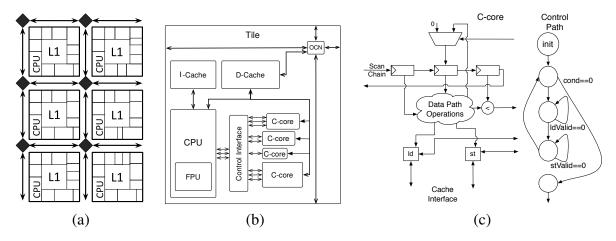

A c-core-based system includes many c-cores embedded in a multicore tiled array like the one shown in Figure 3.1(a). Each tile in the array contains a general-purpose processor (CPU), cache, on-chip network connection, and a collection of c-cores. The c-cores execute "hot"

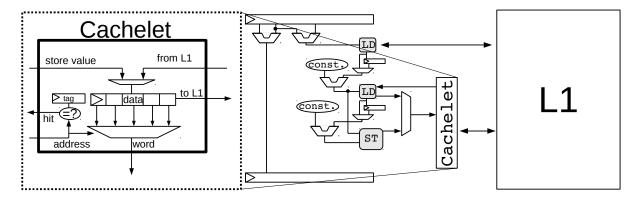

**Figure 3.1. Organization of a c-core-based system** A c-core-based system (a) comprises multiple individual tiles (b), each of which contains multiple c-cores (c). Conservation cores communicate with the rest of the system through a coherent memory system and simple scanchain-based control interface to a general-purpose CPU. Different tiles may contain different c-cores or other accelerators.

regions of specific applications that represent significant fractions of the target workload. The CPU serves as fallback for the parts of applications that are not supported by any c-cores. Using a tiled architecture ([SMSO03][TLM+04][SNH+03]) ensures each c-core is close to a host CPU, to minimize execution overheads and distribute access to the memory system.

Within a tile, the c-cores are tightly coupled to the host CPU via shared connection to the L1 data cache, and by a collection of architecturally-visible scan chains that allow the CPU to read and write all register state within each c-core (Figure 3.1(b)). Each c-core consists of a fixed compute datapath under the control of a hardware state machine (Figure 3.1(c)).

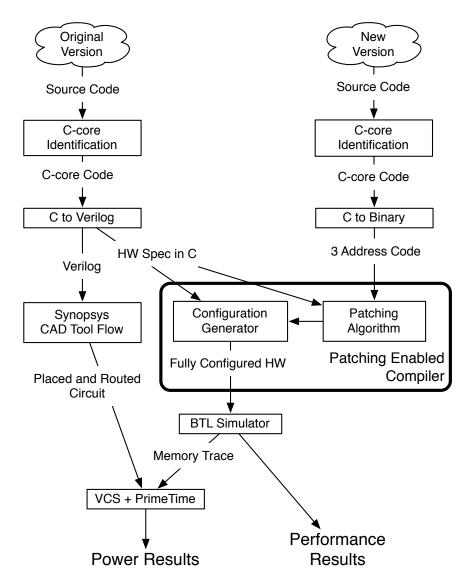

Figure 3.2 shows the life cycle of a c-core from program source code to hardware accelerator in a many-core processor: (a) The life of a c-core starts with C code from a set of relatively stable target applications. (b) The c-core toolchain is used to profile the target applications and extract the energy-intensive code regions. The toolchain converts these regions into patchable c-core specifications. (c) The specifications are used to generate synthesizable Verilog and simulation models for each c-core. (d) Sets of c-cores are placed on different tiles in a many-core tiled processor. (e) As new versions of the target applications are released over time,

**Figure 3.2. Conservation core life cycle** The life of a c-core begins with program source code and results in a patchable hardware accelerator in a many-core tiled processor.

the toolchain can analyze the differences between versions and patch the firmware of existing c-cores, extending the useful lifetime of the c-cores.

## 3.2 C-core Architecture

This section describes the conservation core architecture in more detail. First we discuss the original, baseline implementation of c-cores. Then we discuss upgrades to the baseline architecture that improve performance and generality.

#### **3.2.1** Baseline C-core Architecture

Each c-core serves as a drop-in replacement for a piece of code, specifically a leaf function in the target workload. The principle components of a c-core are a computation datapath and control unit, a cache interface, and a control interface to the CPU.

By design, the c-core datapath and control unit very closely resemble the internal representation that our toolchain extracts from the C source code. The code's data flow graph (DFG) serves as a blueprint for the c-core's datapath, which contains functional operators, such as

**Figure 3.3. C-core example translation from source code** An example c-core starting from C code (a), translated into the compiler's internal representation (b), and finally a hardware datapath controlled by state machine (c).

adders, shifters, and comparators, for each mathematical operation in the code. Muxes are used to implement control decisions, and registers are instantiated only when needed, to hold program values across basic block boundaries or between iterations of a loop.

The control unit is a hardware state machine that mimics the original program's control flow graph (CFG). It tracks branch outcomes computed in the datapath to determine which state to enter on each cycle. The control unit sets the enable and select lines on the registers and muxes in the datapath so that the correct basic block is active each cycle. The control unit's state machine also includes self-loops to wait for the results of memory operations.

The first implementation of c-cores enforces memory ordering constraints by issuing at most one memory operation per cycle to a pipelined, in-order cache interface. Both the c-core and the cache block on misses. The load/store units connect to a coherent data cache that ensures that all loads and stores are visible to the rest of the system regardless of which addresses the c-core accesses. Subsequent, improved versions of c-cores (described in Section 3.2.2) allow multiple memory operations to be in flight simultaneously.

Figure 3.3 shows an example translation from C code (a) to internal representation (b) and finally hardware datapath and control unit state machine (c). The hardware corresponds very closely to the DFG and CFG of the sample code. It has muxes for variables i and sum

corresponding to the  $\phi$ -functions in the CFG. The c-core's state machine is almost identical to the CFG, but with an additional self-loop to wait for the valid signal from the memory load operation. The valid signal is similar to the memory ordering token used in systems such as Tartan [MCC<sup>+</sup>06] and WaveScalar [SMSO03].

The close correspondence between the program's structure and the c-core is important for two reasons: First, it makes it easier to enforce the correct memory ordering from the original program. The control unit enforces an ordering that corresponds to the same order that the program counter provides in a general-purpose processor, and we use the same ordering to enforce memory dependencies. Second, by maintaining a close correspondence between the original program and the c-core hardware, it is more likely that small changes in the source code (which are the common case) will result in correspondingly small patches to the hardware.

#### 3.2.2 Improvements to C-cores

After the initial design and evaluation of c-cores in [VSG<sup>+</sup>10], we made significant changes to the c-core architecture to improve their performance, energy efficiency, and generality. Whereas the original implementation allowed at most one memory operation per basic block, upgraded c-cores can combine multiple memory operations along with dozens of datapath operations into large basic blocks called *fat operators*. We employ fat operators in *efficient complex operator cores* [SVGH<sup>+</sup>11], which extend the baseline architecture with two techniques that improve c-core efficiency: selective depipelining and cachelets. Additionally, the improvements in *quasi-specific cores* [VSGH<sup>+</sup>11] generalize the c-core datapath and patching mechanisms to support even broader ranges of applications. These techniques are fundamental to the design of c-cores but also apply to any architecture that uses fat operators, such as the "magic" instructions discussed in [HQW<sup>+</sup>10].

**Figure 3.4. Selective depipelining in c-cores** An example of selective depipelining (SDP) for one complex basic block, called a fat operator. Under SDP, non-memory datapath operators chain freely within a basic block under the control of a slow clock pulse, while memory operators and associated load registers align to fast clock boundaries.

#### **Selective Depipelining**

Selective depipelining (SDP) is a novel pipelining scheme that employs two clocks operating at different speeds: a *fast clock* allows memory requests to operate at a faster clock rate than the datapath, improving memory performance, while a *slow clock* saves power in the rest of the datapath. Figure 3.4 illustrates SDP for one example basic block.

The fast clock effectively replicates the memory interface *in time* (by exploiting pipeline parallelism), while the datapath runs at a slower clock rate, saving power and leveraging instruction-level parallelism by replicating compute resources *in space*. By driving the non-memory datapath with a slower clock, synthesis tools can use smaller and more energy-efficient operators, since these timing paths are permitted multiple fast-clock cycles to settle. SDP also saves energy by removed many registers from the datapath (see Figure 3.5), since only the final live-out values need to be captured, at fat operator basic block boundaries.

**Figure 3.5.** Using selective depipelining to remove registers The light-gray boxes highlight registers that are removed with selective depipelining. These intermediate datapath values do not need to be captured, and only the final live-out values are captured in registers by the slow clock, at fat operator basic block boundaries.

**Figure 3.6.** C-core cachelet architecture Cachelets are small, distributed L0 caches that improve memory latency in the common case. Memory operations with good locality are mapped to cachelets, while other operations continue to interface directly with the L1 cache.

#### Cachelets

In a conventional processor all loads and stores go to a single cache, since all memory instructions execute on a small set of load/store functional units. C-cores, however, can optimize load and store operations in isolation through the use of cachelets. Cachelets are small (one- to four-line), very fast, coherent, distributed L0 caches embedded in the c-core datapath to reduce load-use latency. Figure 3.6 shows the internal architecture. Cachelets enable sub-cycle load-use latency in the common case, which is  $6 \times$  faster than the L1 in our system. For more details please see [SVGH<sup>+</sup>11].

#### **Quasi-specific Cores**

Quasi-specific cores are generalized c-cores built to support multiple, similar code regions across many applications. Quasi-specific cores are based on the insight that similar code patterns exist within and across applications.

To generate these cores, the c-core toolchain analyzes the program dependence graphs (PDGs) [FOW87] of hot spots from multiple applications in the target workload. The toolchain locates similar code segments across hot spots by searching for isomorphic subgraphs across the PDGs and identifying subgraphs that are suitably similar. Next, the toolchain generates generalized datapaths that can be configured to handle each of the subgraphs. The generalized datapaths operate similarly to the c-core patching mechanisms (see Section 3.5).

Quasi-specific cores improve the scalability of c-core-based systems because they increase the total workload coverage while simultaneously decreasing the total number of accelerators needed. For more details please see [VSGH<sup>+</sup>11].

## 3.3 Integration with CPU

Traditional accelerators typically execute coarse-grained "jobs" offloaded from the CPU. As long as the jobs are large enough and can run independently, these accelerators don't require

a very tight coupling with the CPU.

In contrast, conservation cores are designed to cover much smaller, fine-grained pieces of code. Execution transfers between c-cores and the CPU much more frequently. To minimize overhead and maximize performance, c-cores are tightly integrated with a general-purpose CPU and share direct access to the CPU's L1 data cache.

#### 3.3.1 Shared L1 Data Cache