### UC Irvine UC Irvine Electronic Theses and Dissertations

**Title** Data Shepherding: Cache design for future large scale chips

Permalink https://escholarship.org/uc/item/4bq2t8q5

Author Jang, Ganghee

Publication Date 2016

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Data Shepherding: Cache design for future large scale chips

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Ganghee Jang

Dissertation Committee: Professor Jean-Luc Gaudiot, Chair Professor Alexander Veidenbaum Professor Nader Bagherzadeh

© 2016 Ganghee Jang

### DEDICATION

To my wife, Jiyoung. Her courage led me in the right direction of this journey. To my kids, Miru and Hechan. I felt re-energized whenever I saw them throughout the course of my study.

# TABLE OF CONTENTS

|          |       |        | P                                                                      | Page         |

|----------|-------|--------|------------------------------------------------------------------------|--------------|

| L]       | IST ( | OF FIG | URES                                                                   | $\mathbf{v}$ |

| L]       | IST ( | OF TA  | BLES                                                                   | vii          |

| A        | CKN   | OWLE   | EDGMENTS                                                               | viii         |

| C        | URR   | ICULU  | JM VITAE                                                               | ix           |

| A        | BST   | RACT   | OF THE DISSERTATION                                                    | x            |

| 1        | Intr  | oducti | on                                                                     | 1            |

|          | 1.1   | Backgi | cound and motivation                                                   | 1            |

|          | 1.2   |        | m definition                                                           | 2            |

|          | 1.3   | Goal o | f this work                                                            | 3            |

| <b>2</b> | Bac   | kgroun | nd Research                                                            | 5            |

|          | 2.1   | 0      | designs from the view point of design goals                            | 6            |

|          |       | 2.1.1  | Power wall problem and system design goals                             | 6            |

|          |       | 2.1.2  | System designs with dynamic change of goals                            | 12           |

|          | 2.2   |        | echnologies and system design goals                                    | 13           |

|          |       | 2.2.1  | 3D technologies and Non-Volatile Memory technologies                   | 14           |

|          |       | 2.2.2  | Reliability and design issues with other goals                         | 18           |

| 3        | Pro   | blem I | Definition                                                             | 22           |

|          | 3.1   | Logica | addressing mechanism to combine the multiple design goals              | 23           |

|          |       | 3.1.1  | System design requirements and combining different goal driven designs | 23           |

|          |       | 3.1.2  | Merging different goal driven mechanisms and explicit resource ad-     |              |

|          |       |        | dressing                                                               | 26           |

|          | 3.2   | 0      | tradeoffs                                                              | 29           |

|          |       | 3.2.1  | How extra resource indexing can handle design challenges on the last   | 26           |

|          |       | 2.2.2  | level shared cache                                                     | 29           |

|          |       | 3.2.2  | Design issues when integrating extra resource addressing on the last   | <u>م</u> ۲   |

|          |       |        | level shared cache                                                     | 35           |

| 4.1       Overall Data Shepherding cache Design       41         4.2       Detailed mechanisms for Placement and Replacement       45         4.2.1       Retrieving bank mapping information and TLB cache design       45         4.2.2       Management of a mapping between a page and a bank       47         4.2.3       Description of Replacement       51         4.3       Page flush mechanism       56         4.3.1       Estimation of performance impact due to page flush       56         4.3.2       Page flush mechanisms and cache coherence protocol       60         4.4       Physical configuration of Data Shepherding cache       65         4.4.1       Overview of physical configuration       67         4.4.2       Discussion on the bank design       72         5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2.1       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling and access timing       92 <th>4</th> <th colspan="3">Data Shepherding Cache Description 4</th>                                         | 4        | Data Shepherding Cache Description 4 |                                                                                                   |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|---------------------------------------------------------------------------------------------------|-----|

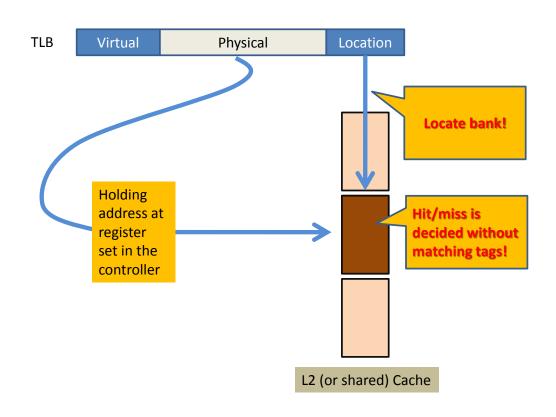

| 4.2.1       Retrieving bank mapping information and TLB cache design       45         4.2.2       Management of a mapping between a page and a bank       47         4.2.3       Description of Replacement       51         4.3       Page flush mechanism       56         4.3.1       Estimation of performance impact due to page flush       56         4.3.2       Page flush mechanisms and cache coherence protocol       60         4.4       Physical configuration of Data Shepherding cache       65         4.4.1       Overview of physical configuration       65         4.4.2       Discussion on the bank design       72         5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       <                                                                                                                                         |          | 4.1                                  | Overall Data Shepherding cache Design                                                             | 41  |

| 4.2.2       Management of a mapping between a page and a bank       47         4.2.3       Description of Replacement       51         4.3       Page flush mechanism       56         4.3.1       Estimation of performance impact due to page flush       56         4.3.2       Page flush mechanisms and cache coherence protocol       60         4.4       Physical configuration of Data Shepherding cache       65         4.4.1       Overview of physical configuration       65         4.4.2       Discussion on the bank design       69         5       Simulation Configuration       72         5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101       6.1       Analysis of physical characteristics       101                                                                                                                                              |          | 4.2                                  | Detailed mechanisms for Placement and Replacement                                                 | 45  |

| 4.2.3 Description of Replacement       51         4.3 Page flush mechanism       56         4.3.1 Estimation of performance impact due to page flush       56         4.3.2 Page flush mechanisms and cache coherence protocol       60         4.4 Physical configuration of Data Shepherding cache       65         4.4.1 Overview of physical configuration       65         4.4.2 Discussion on the bank design       69         5 Simulation Configuration       72         5.1 Overview of experiment setup       72         5.1.2 Comparison between Data Shepherding and Static NUCA cache setup       75         5.2 Implementation details on the simulator GEM5       78         5.2.1 Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2 Modeling a page flush       86         5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1.2 Comparison between the Data Shepherding and the SNUCA cache configuration       102         6.2.1 Experiment setup       105         6.2.2 Experiment results and discussion       107         6.2.2 Experiment results and discussion       117         7 Conclusion                                                                                |          |                                      | 4.2.1 Retrieving bank mapping information and TLB cache design                                    | 45  |

| 4.3 Page flush mechanism       56         4.3.1 Estimation of performance impact due to page flush       56         4.3.2 Page flush mechanisms and cache coherence protocol       60         4.4 Physical configuration of Data Shepherding cache       65         4.4.1 Overview of physical configuration       65         4.4.2 Discussion on the bank design       69         5 Simulation Configuration       72         5.1 Overview of experiment setup       72         5.1.2 Comparison between Data Shepherding and Static NUCA cache setup       75         5.2 Implementation details on the simulator GEM5       78         5.2.1 Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2 Modeling a page flush       86         5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1.1 Details of the SNUCA cache       102         6.1.2 Comparison between the Data Shepherding and the SNUCA cache       105         6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134 <td></td> <td></td> <td>4.2.2 Management of a mapping between a page and a bank</td> <td>47</td> |          |                                      | 4.2.2 Management of a mapping between a page and a bank                                           | 47  |

| 4.3.1       Estimation of performance impact due to page flush       56         4.3.2       Page flush mechanisms and cache coherence protocol       60         4.4       Physical configuration of Data Shepherding cache       65         4.4.1       Overview of physical configuration       65         4.4.2       Discussion on the bank design       69         5       Simulation Configuration       72         5.1       Overview of experiment setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       102                                                                                                                         |          |                                      | 4.2.3 Description of Replacement                                                                  | 51  |

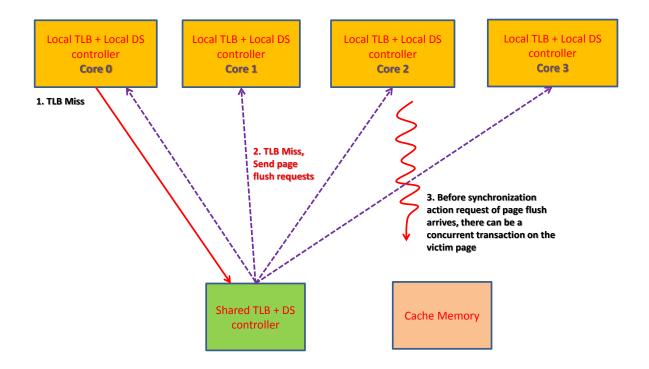

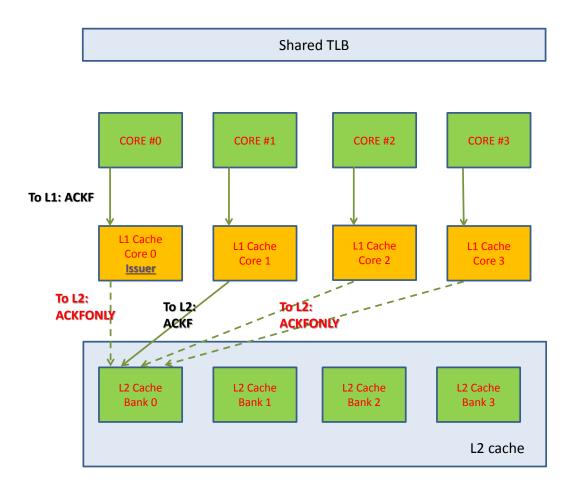

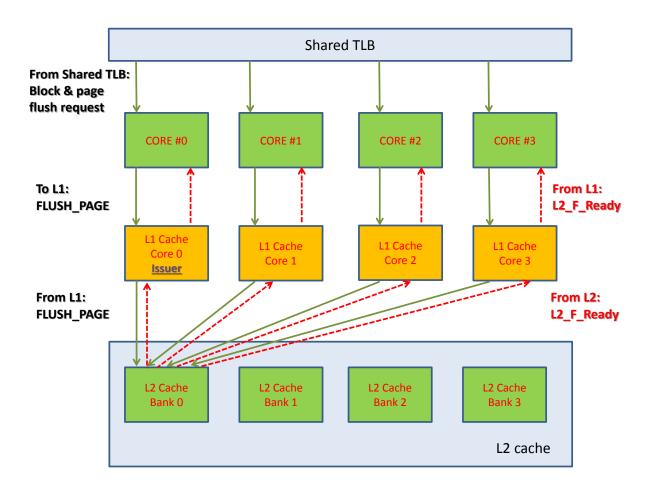

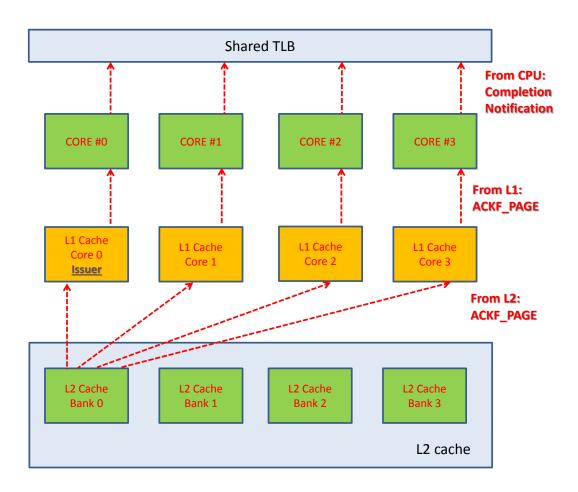

| 4.3.2       Page flush mechanisms and cache coherence protocol       60         4.4       Physical configuration of Data Shepherding cache       65         4.4.1       Overview of physical configuration       65         4.4.2       Discussion on the bank design       69         5       Simulation Configuration       72         5.1       Overview of experiment setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.2       Comparison between the Data Shepherding and the SNUCA cache configuration       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       <                                                                                                                                                  |          | 4.3                                  | Page flush mechanism                                                                              | 56  |

| 4.4 Physical configuration of Data Shepherding cache       65         4.4.1 Overview of physical configuration       65         4.4.2 Discussion on the bank design       69         5 Simulation Configuration       72         5.1 Overview of experiment setup       72         5.1.2 Comparison between Data Shepherding and Static NUCA cache setup       75         5.2 Implementation details on the simulator GEM5       78         5.2.1 Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2 Modeling a page flush       86         5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1 Analysis of physical characteristics       101         6.1.2 Comparison between the Data Shepherding and the SNUCA cache configuration       105         6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134                                                                                                                                                                                                                                                                          |          |                                      | 4.3.1 Estimation of performance impact due to page flush                                          | 56  |

| 4.1       Overview of physical configuration       65         4.4.2       Discussion on the bank design       69         5       Simulation Configuration       72         5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117                                                                                                                                                                          |          |                                      | 4.3.2 Page flush mechanisms and cache coherence protocol                                          | 60  |

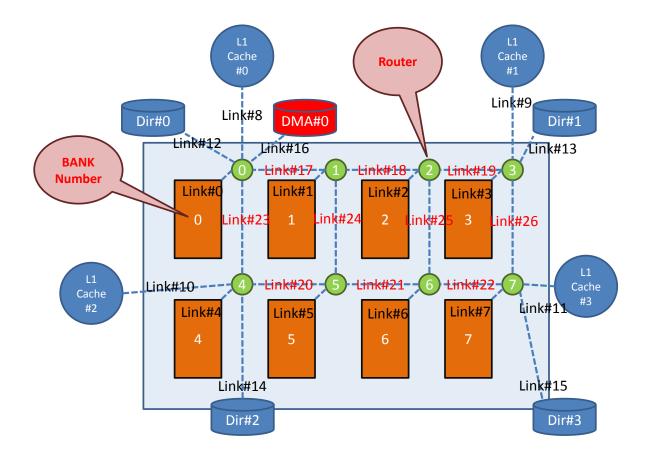

| 4.4.2 Discussion on the bank design       69         5 Simulation Configuration       72         5.1 Overview of experiment setup       72         5.1.1 Goal of simulation setup       72         5.1.2 Comparison between Data Shepherding and Static NUCA cache setup       75         5.2 Implementation details on the simulator GEM5       78         5.2.1 Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2 Modeling a page flush       86         5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1 Analysis of physical characteristics       101         6.1.1 Details of the SNUCA cache       102         6.1.2 Comparison between the Data Shepherding and the SNUCA cache       105         6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134                                                                                                                                                                                                                                                                                                                     |          | 4.4                                  | Physical configuration of Data Shepherding cache                                                  | 65  |

| 5       Simulation Configuration       72         5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                              |          |                                      | 4.4.1 Overview of physical configuration                                                          | 65  |

| 5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                |          |                                      | 4.4.2 Discussion on the bank design                                                               | 69  |

| 5.1       Overview of experiment setup       72         5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                | <b>5</b> | Simulation Configuration             |                                                                                                   | 72  |

| 5.1.1       Goal of simulation setup       72         5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       105         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                        | -        |                                      | -                                                                                                 |     |

| 5.1.2       Comparison between Data Shepherding and Static NUCA cache setup       75         5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       78         5.2.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       105         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                            |          | -                                    |                                                                                                   |     |

| 5.2       Implementation details on the simulator GEM5       78         5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                      | 1                                                                                                 | 75  |

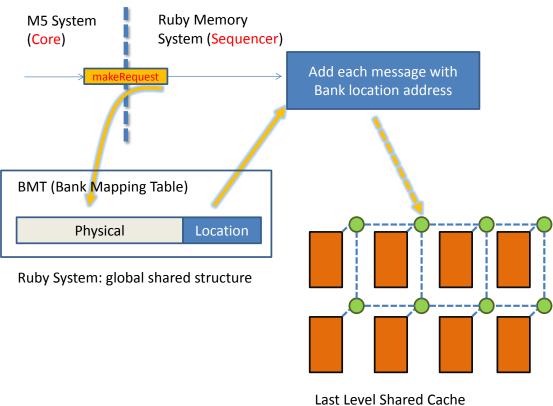

| 5.2.1       Modeling of the Data Shepherding mechanisms in the TLB       78         5.2.2       Modeling a page flush       86         5.3       Resource Conflict Modeling       92         5.3.1       Overall the Resource Conflict Modeling design       92         5.3.2       The Resource Conflict Modeling and access timing       92         5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 5.2                                  |                                                                                                   | 78  |

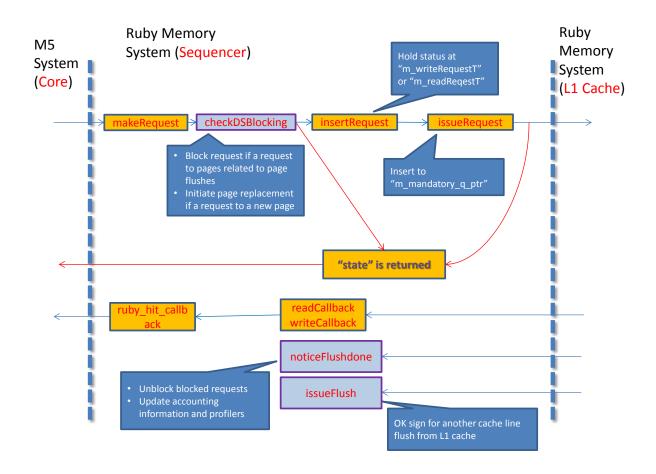

| 5.2.2 Modeling a page flush       86         5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1 Analysis of physical characteristics       101         6.1.1 Details of the SNUCA cache       102         6.1.2 Comparison between the Data Shepherding and the SNUCA cache       105         6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                      | •                                                                                                 | 78  |

| 5.3 Resource Conflict Modeling       92         5.3.1 Overall the Resource Conflict Modeling design       92         5.3.2 The Resource Conflict Modeling and access timing       97         6 Results       101         6.1 Analysis of physical characteristics       101         6.1.1 Details of the SNUCA cache       102         6.1.2 Comparison between the Data Shepherding and the SNUCA cache       105         6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                      | ů · ů                                                                                             | 86  |

| 5.3.1Overall the Resource Conflict Modeling design925.3.2The Resource Conflict Modeling and access timing976Results1016.1Analysis of physical characteristics1016.1.1Details of the SNUCA cache1026.1.2Comparison between the Data Shepherding and the SNUCA cache1026.2Performance analysis1146.2.1Experiment setup1156.2.2Experiment results and discussion1177Conclusion134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 5.3                                  | 0.1.0                                                                                             | 92  |

| 5.3.2       The Resource Conflict Modeling and access timing       97         6       Results       101         6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                      |                                                                                                   | 92  |

| 6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       105         6.2.1       Experiment setup       114         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                      | 5.3.2 The Resource Conflict Modeling and access timing                                            | 97  |

| 6.1       Analysis of physical characteristics       101         6.1.1       Details of the SNUCA cache       102         6.1.2       Comparison between the Data Shepherding and the SNUCA cache       105         6.2       Performance analysis       105         6.2.1       Experiment setup       114         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6        | 6 Besults                            |                                                                                                   | 101 |

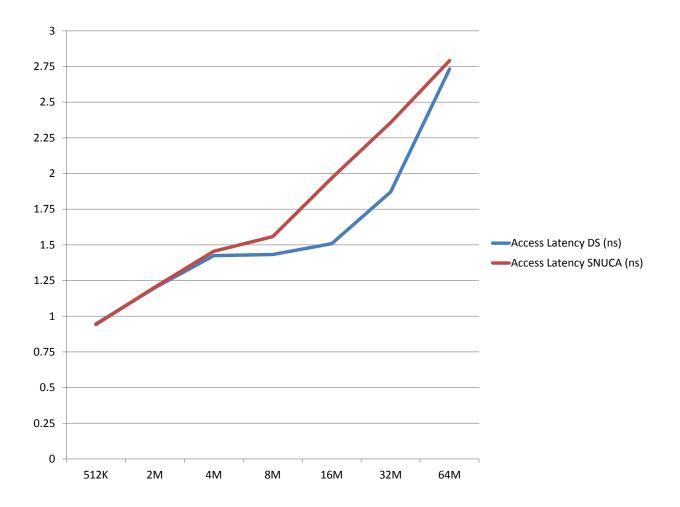

| 6.1.1 Details of the SNUCA cache1026.1.2 Comparison between the Data Shepherding and the SNUCA cache<br>configuration1056.2 Performance analysis1146.2.1 Experiment setup1156.2.2 Experiment results and discussion1177 Conclusion134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                      |                                                                                                   |     |

| 6.1.2       Comparison between the Data Shepherding and the SNUCA cache configuration       105         6.2       Performance analysis       114         6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                      |                                                                                                   | 102 |

| 6.2 Performance analysis       114         6.2.1 Experiment setup       115         6.2.2 Experiment results and discussion       117         7 Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                      |                                                                                                   |     |

| 6.2.1       Experiment setup       115         6.2.2       Experiment results and discussion       117         7       Conclusion       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                      | $\operatorname{configuration}$                                                                    | 105 |

| 6.2.2 Experiment results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 6.2                                  | Performance analysis                                                                              | 114 |

| 7 Conclusion 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                      | $6.2.1  \text{Experiment setup}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 115 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                      | 6.2.2 Experiment results and discussion                                                           | 117 |

| 8 Future Research 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7        | Cor                                  | nclusion                                                                                          | 134 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8        | Fut                                  | ure Research                                                                                      | 136 |

| Bibliography 1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                      | 140                                                                                               |     |

# LIST OF FIGURES

### Page

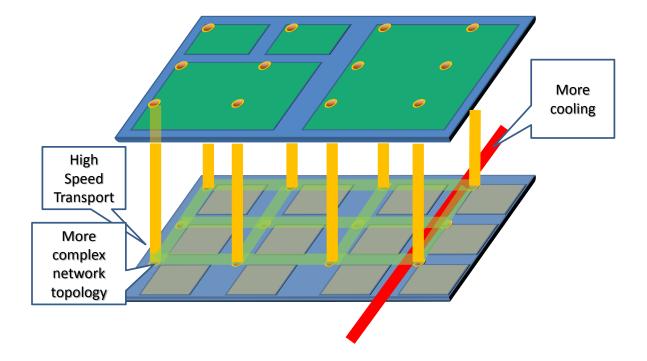

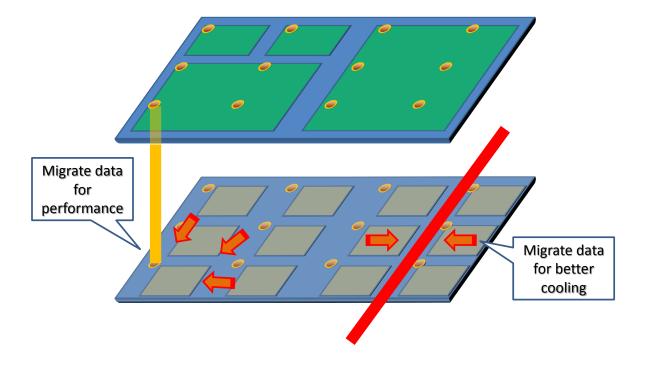

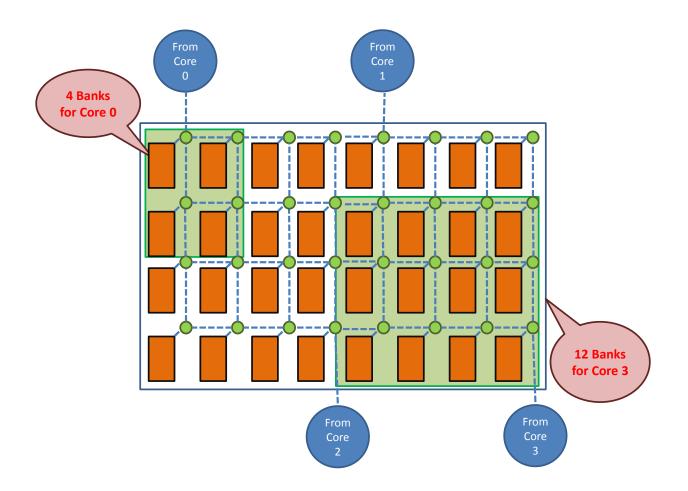

| 3.1<br>3.2<br>3.3                                                     | Example of future chip architecture                                                                                                               | 30<br>31<br>33                   |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$ | cache line placement of the Data Shepherding Cache                                                                                                | 44<br>54<br>61<br>64<br>66<br>67 |

| $5.1 \\ 5.2$                                                          | Overview of the Data Shepherding cache simulation setup                                                                                           | 80<br>84                         |

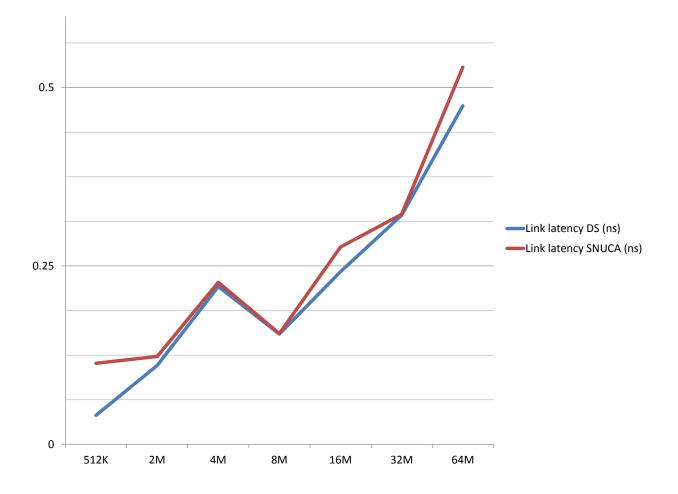

| 6.1                                                                   | Single bank access latency of the Data Shepherding cache and the SNUCA cache.                                                                     | 106                              |

| 6.2                                                                   | Latency of the longer link (between one for x-axis and the other for y-axis) of the Data Shepherding cache and the SNUCA cache.                   | 107                              |

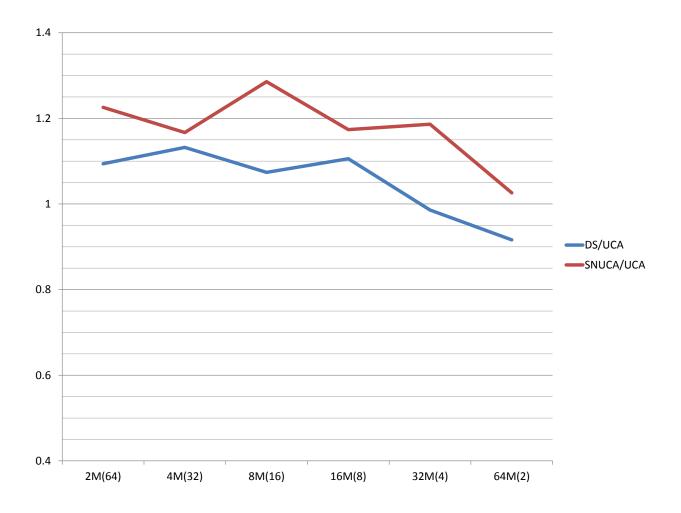

| 6.3                                                                   | Chip area comparison with ratio over the UCA cache. Each cache is sized as 128 MB.                                                                | 110                              |

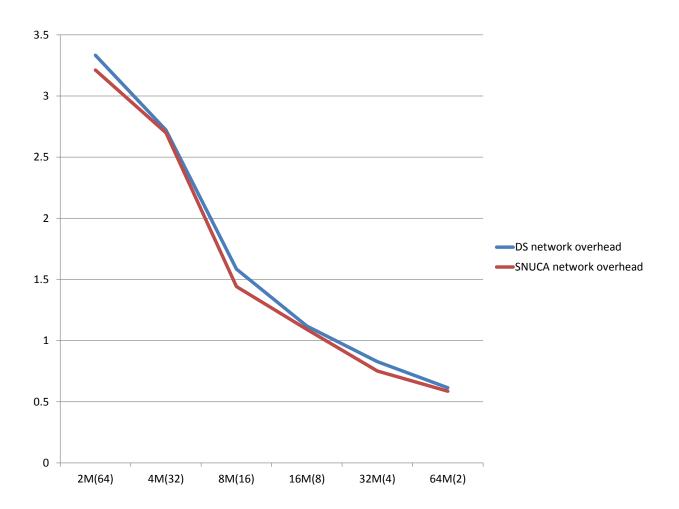

| 6.4                                                                   | Percentage of on-chip network overhead over total area                                                                                            | 110                              |

| 6.5                                                                   | Leakage power comparisons with sum of bank leakage power over the 128 MB                                                                          | ***                              |

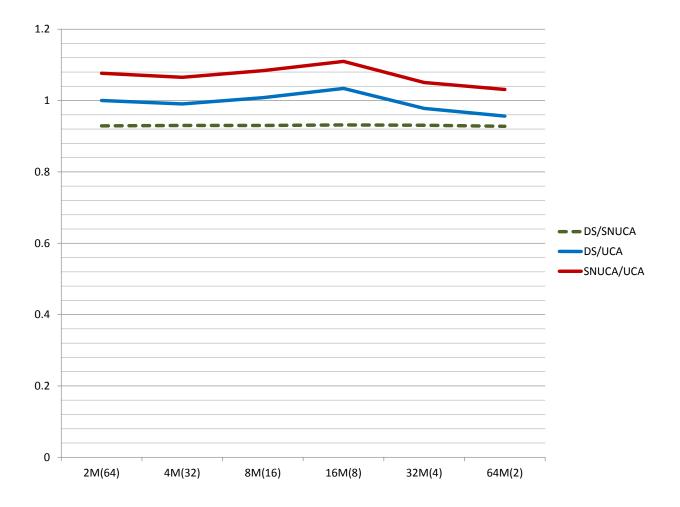

| 6.6                                                                   | UCA cache and the DS cache over the SNUCA cache                                                                                                   | 112                              |

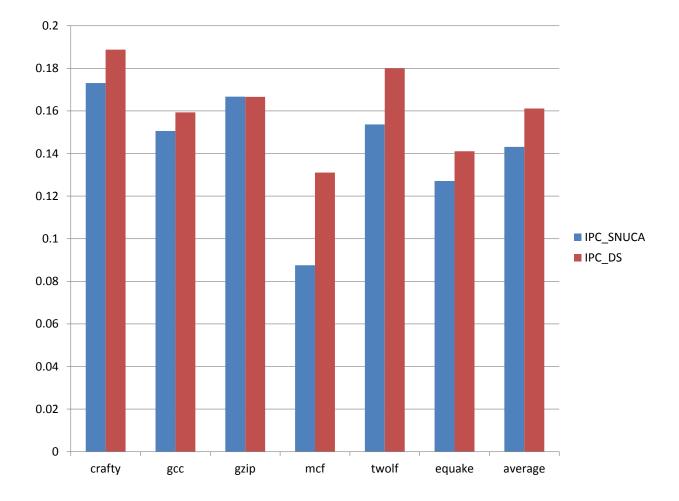

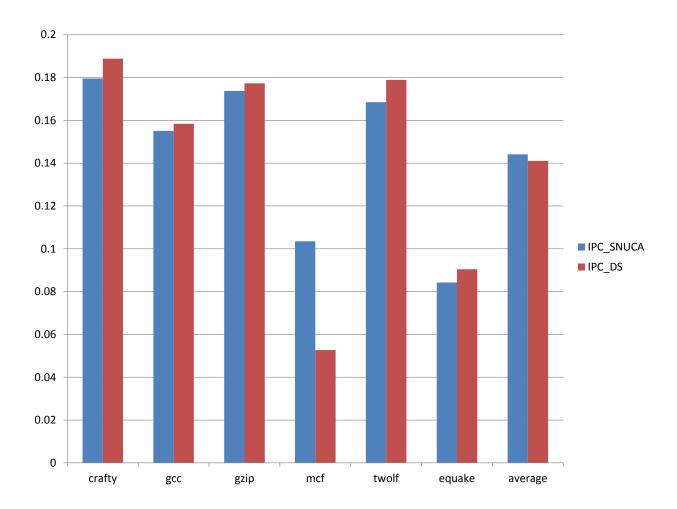

|                                                                       | size, 128 MB in total.                                                                                                                            | 118                              |

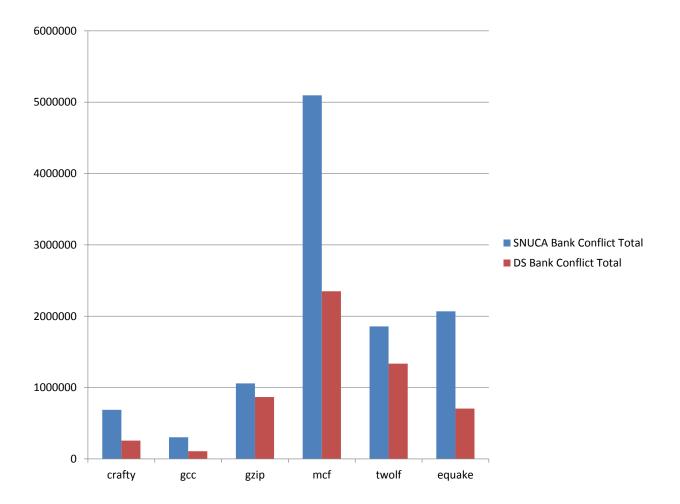

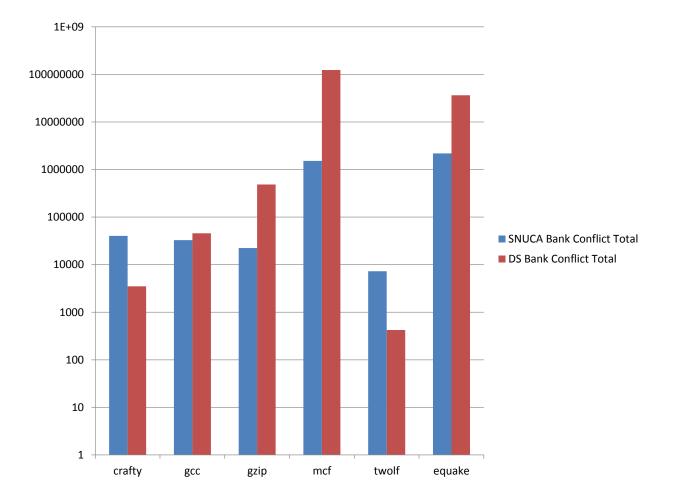

| 6.7                                                                   | The total counts of bank conflicts. 2 MB bank size, 128 MB in total                                                                               | 119                              |

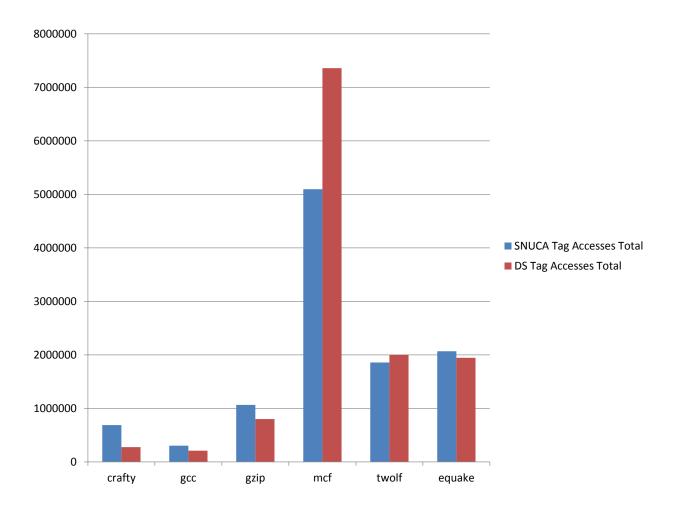

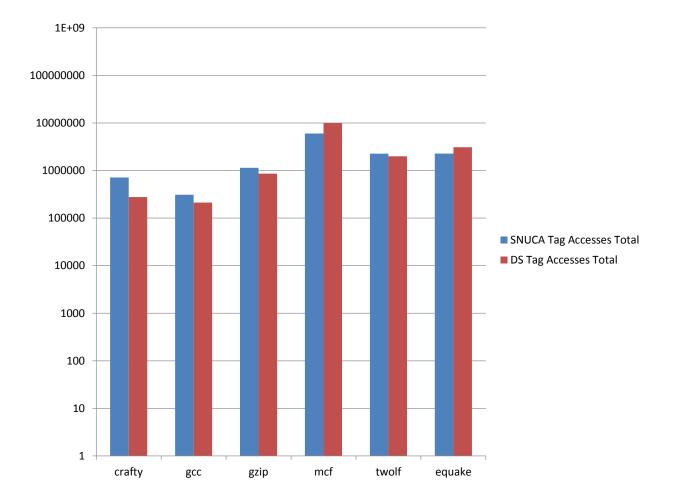

| $\begin{array}{c} 6.8 \\ 6.9 \end{array}$                             | The total counts of tag latency accesses. 2 MB bank size, 128 MB in total<br>Performance comparison between the DS and the SNUCA cache. 2 MB bank | 120                              |

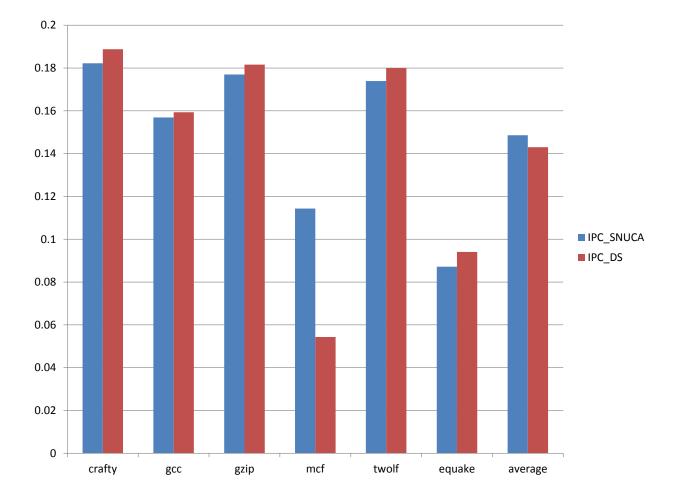

| 0.5                                                                   | size, 8 MB in total.                                                                                                                              | 122                              |

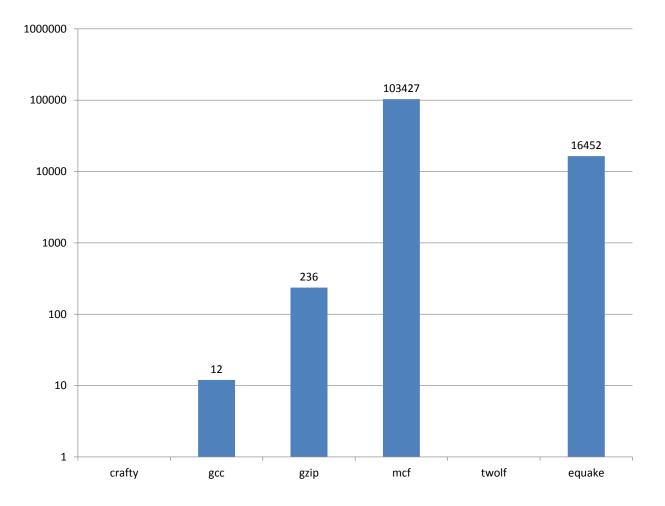

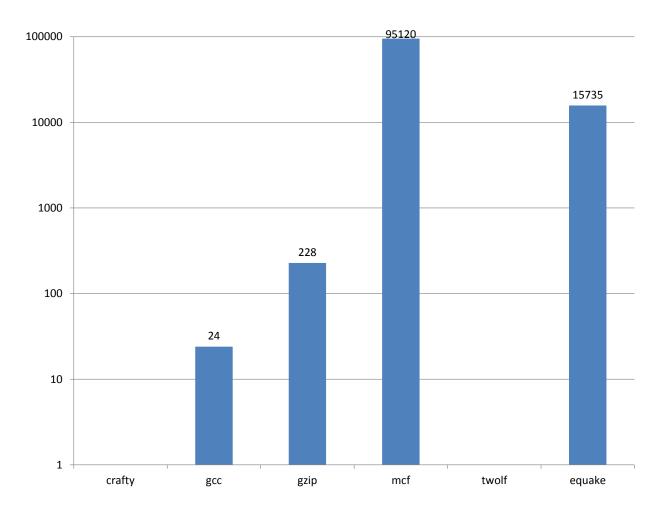

| 6.10                                                                  | The number of page flushes. 2 MB bank size, 8 MB in total                                                                                         | 123                              |

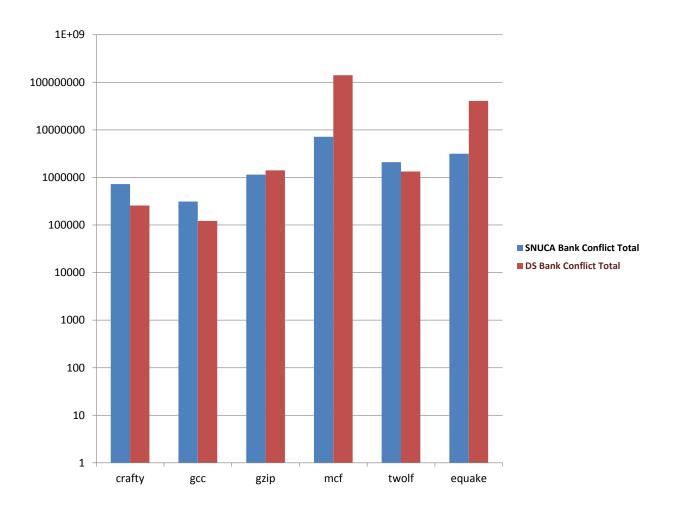

| 6.11                                                                  | The total counts of bank conflicts. 2 MB bank size, 8 MB in total                                                                                 | 124                              |

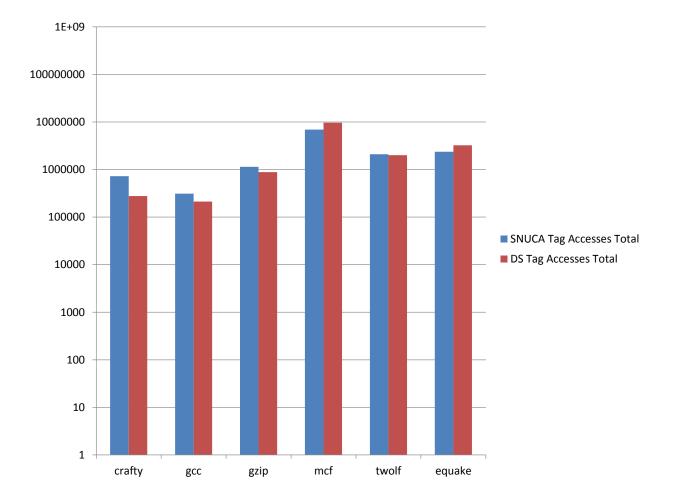

|                                                                       | The total counts of tag latency accesses. 2 MB bank size, 8 MB in total. $\ .$ .                                                                  | 125                              |

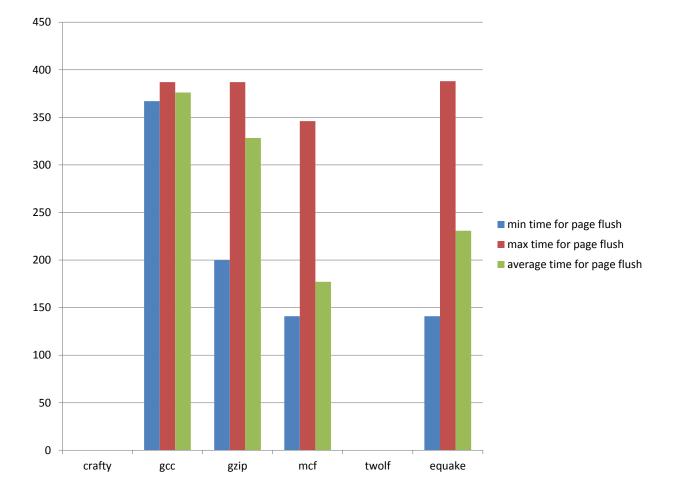

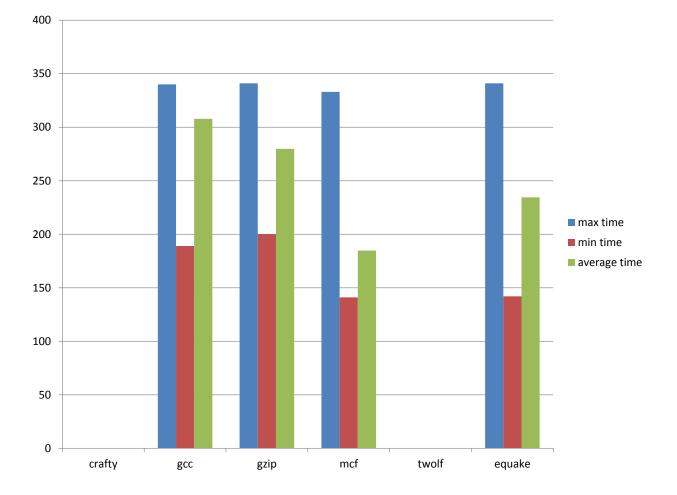

| 6.13                                                                  | Maximum, minimum and average page flush time comparison. 2 MB bank                                                                                |                                  |

|                                                                       | size, 8 MB in total.                                                                                                                              | 126                              |

| 6.14 | Performance comparison between the DS and the SNUCA cache. 512 KB                |     |

|------|----------------------------------------------------------------------------------|-----|

|      | bank size, 8 MB in total.                                                        | 128 |

| 6.15 | The total counts of bank conflicts. 512 KB bank size, 8 MB in total              | 129 |

| 6.16 | The total counts of tag latency accesses. 512 KB bank size, 8 MB in total. $\ .$ | 130 |

| 6.17 | The number of page flushes. 512 KB bank size, 8 MB in total                      | 131 |

| 6.18 | Maximum, minimum and average page flush time comparison. 512 KB bank             |     |

|      | size, 8 MB in total.                                                             | 132 |

|      |                                                                                  |     |

# LIST OF TABLES

### Page

| Extra coherence messages for the Data Shepherding simulation.             | 87                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extra coherent messages and events on the L1 cache                        | 89                                                                                                                                                                                                                                                                               |

| Extra coherent messages and events on the L2 cache                        | 91                                                                                                                                                                                                                                                                               |

| Coherent states of a L2 cache line and its access permission and location | 97                                                                                                                                                                                                                                                                               |

| CACTI settings used for experiments.                                      | 105                                                                                                                                                                                                                                                                              |

| Average hop counts on 2D mesh network with varying nodes                  | 108                                                                                                                                                                                                                                                                              |

| Selected average access time of the Data Shepherding cache and the SNUCA  |                                                                                                                                                                                                                                                                                  |

| when 4 GHz operation frequency is assumed                                 | 109                                                                                                                                                                                                                                                                              |

| GEM5 settings used for experiments                                        | 114                                                                                                                                                                                                                                                                              |

|                                                                           | Extra coherence messages for the Data Shepherding simulation Extra coherent messages and events on the L1 cache Extra coherent messages and events on the L2 cache Coherent states of a L2 cache line and its access permission and location CACTI settings used for experiments |

# ACKNOWLEDGMENTS

First of all, I would like to thank my advisor, Prof. Jean-Luc Gaudiot. He gave me opportunity and support for this great journey.

Without the love, sacrifice and support from my parents, Dongsoo Jang and Soonja Lee, I could not finish this journey. I must include my mother-in-law, Yuim Lee (my wife's mother) to this big thank-you list. Without her sacrifice and support, I could not finish my study especially after my parents' business went to bad.

During my PhD study, I met many visitors to the lab, and the conversation with them helped me a lot. Especially, I want to say special thank-you to Prof. Eui-Young Chung and Prof. Seong-Won Lee for their advices on the generic approach toward research.

I am really lucky to have good seniors and friends as being a part of the PASCAL lab. Alex Chu and Howard Wong were great office mates, and also we made many hang-outs which saved me from the research stress.

Between the people I met and become friends outside the lab, I feel really appreciated to David Keilson for all his advice on life in US. He is such a great mentor and citizen.

Also, I learned a lot from my kids, Miru and Hechan. They broadened my views on the value of education. I cannot help mentioning about my electric guitar. It gave me a new insight on what a good invention should be - a guitar has made people happy (including me) without hurting anyone.

# CURRICULUM VITAE

### Ganghee Jang

#### EDUCATION

| <b>Doctor of Philosophy in Electrical and Computer Engineering</b> | <b>2016</b>          |

|--------------------------------------------------------------------|----------------------|

| University of California, Irvine                                   | Irvine, California   |

| Master of Science in Electrical and Computer Engineering           | <b>2006</b>          |

| University of Florida                                              | Gainesville, Florida |

| Bachelor of Engineering in Electronics Engineering                 | <b>2003</b>          |

| Korea University                                                   | Seoul, South Korea   |

#### EXPERIENCE

DFM

| <b>Graduate Student Researcher</b>   | <b>2010–2015</b>          |

|--------------------------------------|---------------------------|

| University of California, Irvine     | Irvine, California        |

| <b>Teaching Experience as Grader</b> | <b>2011–2013</b>          |

| University of California, Irvine     | Irvine, California        |

| Network System Engineer              | <b>2003–2004</b>          |

| Korea Telecom                        | Seoul, South Korea        |

| SERVICIES<br>Reviewer<br>SBAC-PAD    | 2010,  2012,  2014,  2015 |

| <b>Reviewer</b><br>TPDS              | 2012                      |

| Reviewer                             | 2011,2012                 |

### ABSTRACT OF THE DISSERTATION

Data Shepherding: Cache design for future large scale chips

By

Ganghee Jang

Doctor of Philosophy in Electrical and Computer Engineering University of California, Irvine, 2016 Professor Jean-Luc Gaudiot, Chair

The issue of the power wall has had a drastic impact on many aspects of system design. Even though frequency scaling is limited because Dennard scaling stopped a few years ago, new technologies and design trends such as 3D stacking and heterogeneous multi-core architectures still offer us opportunities to integrate more logic to increase performance. However, these new trends have increased design complexity significantly, especially in terms of satisfying various system requirements and system goals: power efficiency must be handled carefully while scaled resources must be managed to improve performance. Sometimes system scaling itself conflict with system goals. Increased chip resources and core counts make fair resource sharing more notable issues, and the increased number of heterogeneous architecture makes programming more challenging by requiring more programming styles (e.g., stream programming, SPMD style programming), API, etc.

We suggest here that multiple design goal issues could be handled more efficiently via explicit resource addressing. This idea is applied to the shared last level cache design and we call this approach the Data Shepherding cache. We show how the Data Shepherding cache design solves some of the design issues of integrating mechanisms from multiple goals especially when we consider scaling in capacity and performance. The properties of the Data Shepherding cache are evaluated in two ways with open source tools. CACTI from HP.com simulates cache models to obtain cache parameters such as access time, power consumption, etc. Further analysis with the model parameters shows that the Data Shepherding cache has 10% smaller area footage, which leads to a 7% leakage power reduction over the Static NUCA cache. We analyze performance using the GEM5 simulator from gem5.org which models system architecture. The results show a 12.6% performance improvement with selected Spec2000 benchmarks with 2MB bank, 128 MB total shared cache size.

# Chapter 1

# Introduction

### 1.1 Background and motivation

Recently, we have observed a lot of challenges which lead to turns of technology trends. The issue of the power wall has had a drastic impact on many aspects of system design as we have seen the rise of multi-core design on the market. Frequency scaling also slowed down because Dennard scaling [36] is not effective any more. However, new technologies and design trends such as 3D stacking [19, 26] and Non-volatile memory technologies [62, 30] still give us room for a steady scaling in number of logics on a chip. Interestingly, new design trend such as heterogeneous architectures and Application specific Processing Units (APUs) let us transform the benefits of scaling in count into improving performance or power efficiency.

By the way, this new design trends come from utilization of extra logics. In other words, performance/power efficiency improvements are achieved at the cost of the design complexity. This induces further implications. Significant re-design may require to improve performance of the scaled version of an existing design. Mechanisms which are attached to the major components for extra functionalities also require significant change. The extra functionalities

are to meet the design requirements, or goals such as power efficiency, performance efficiency, resource sharing management, etc. For example, power control mechanisms on the shared cache design [37, 74, 41, 72, 57, 15] have suggested to control the amount of leakage power because the amount of area for the last level shared cache takes significant portion of chip area. As we will look at in Chapter 2, some of them is not easy to apply to the much larger caches than the sizes of the cache which the authors worked on. There are some which would be tough to be used together with other goal driven mechanisms. These issue of scaling and goal driven designs will be discussed in detail in Chapter 2.

### 1.2 Problem definition

A good example of goal driven designs are found in the cores of multi-core chips. The power and performance efficiency of each core can be controlled via Dynamic Voltage Frequency Scaling (DVFS) mechanism on each core. Global policy to achieve power consumption targets or performance targets can be optimized through DVFS control on each core. This is possible because each core is addressable to the global policy management. This explicit addressing is not popularly used with the last level shared cache design because explicit addressing generally had been linked with programmable cache memory. Some examples can be found in the domain of embedded system design where high degree of optimization is required.

The reason for the weak popularity is because of design approach on the cache memory. The cache memory has been considered as a buffer memory, so search has been regarded as a primary method to find a desired content in the cache memory. However, as we scale a chip size, more design concerns would be added, especially, on the last level shared cache. As discussed in [9, 92], the number of pin for data transfer might fail to catch up the required bandwidth due to the cost. 3D stacking technology and the use of heterogeneous architecture design can increase on-chip network complexity as dimensions and node counts increase. These issues require high degree of specialization on the last level shared cache [68, 47, 105].

We can find a good design example for these design issues in the domain of building architectures. Modern skyscrapers have managed similar design issues very efficiently. They absorb on and off building traffic by having multiple functional areas of living area, business area, shopping area, etc. as we can see some design approach of integrating the main memory with the CPU[105]. Traffic in the building is efficiently managed with the more complex elevator system, which is related to the performance efficiency. The solutions are possible because placement such as elevator stops and office locations can be adjusted. Actually, the adjustment can be done with the floor numbers. The floor numbers give efficient an abstraction to add multiple functionalities.

Many design issues with the cache design could be solved if similar design approach to the addressing with floor numbers of skyscrapers would be applied. We call it explicit resource addressing design strategy, and in Chapter 3, we will explore how this can solve the raised design issues. Also, in Section 3.2.2, expected challenges will be discussed when we apply the explicit resource addressing on the last level shared cache design.

### 1.3 Goal of this work

As identified challenges can be solved efficiently with explicit resource addressing on the last level shared cache design, now we have a question of whether we can make a scalable cache design with explicit resource addressing. Because adding explicit resource addressing has comparable design issues to adding logical addressing, there are design issues such as mapping table management, when and how to make mappings. By the way, as we can see 128 MB of shared last level cache on the market[5], careful consideration of mapping granularity is a key to manage implementation overhead. However, bigger granularity has its own drawbacks. Bigger granularity would increase internal fragmentation and false sharing. Also, if the granularity size is the same with the granularity of the virtual memory system, we must consider performance interference.

We selected a page size as the mapping granularity, and tried to design so that it should work for scaling in size. The purpose of explicit resource addressing is to resolve issues from the future scaled system, so it is important to imbue good features for the scalability. Detailed design of the Data Shepherding cache is discussed in Chapter 4. We assign a separate chapter (Chapter 5) to explain implementation details on the Simulator, GEM5 [25].

Because of increased granularity, the Data Shepherding cache attains less hardware overhead, but gets performance overhead of page flushes. In Chapter 6, we will evaluate the Data Shepherding cache in two ways. We will estimate the benefits from the reduced hardware overhead. The hardware parameters for the estimation is modeled from CACTI tool[78]. Then, detailed performance evaluation is made with Simulator, GEM5 to examine how the overall performance is influenced from the reduced hardware overhead and performance overhead. Observations from the results will be summarized in Chapter 7. Remained and extended works planned for the future is listed in Chapter 8.

# Chapter 2

# **Background Research**

The new technology and design trends are giving us interesting design challenges. The new technology and new design trends are not just scaled versions of previous designs, but sometimes drive into the direction of significant new designs. For example, recently we observed the very important technology turn because of "power wall" and saw the rise of multi-/many-core designs. Power wall is not the only challenge which has changed the design trend. We will look into these new design trends from a view point of design goals, and discuss the efficiency of the increased design complexity.

Actually, this chapter is to lead why the explicit resource indexing matters as a interface to implement mechanisms to achieve various design goals. So, the readers who want to read directly from the Data Shepherding cache design may skip this chapter.

### 2.1 System designs from the view point of design goals

#### 2.1.1 Power wall problem and system design goals

Embedded systems were considered more specific design goal driven as we can see many application specific designs such as realtime systems, ATM systems, etc. On the while, systems such as desktop PC systems fell on the generic system category. However, "power wall" steered huge turn in the design trend. We already saw that major performance matric for the consumer desktop system have moved to the system throughput from the system frequency because robust frequency scaling becomes impossible. One good example is that Intel canceled Tejas CPU design around 2004 [40]. The chip was originally planned to run up to 7 GHz, but power dissipation of 2.7 GHz operation was 150 watts, so failed to be scaled up.