# UCLA UCLA Electronic Theses and Dissertations

## Title

Co-optimizing High-Level Synthesis and Physical Design for Rapid Timing Closure of Large-Scale FPGA Designs

Permalink https://escholarship.org/uc/item/3xc7b89f

Author Guo, Licheng

Publication Date 2022

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Co-optimizing High-Level Synthesis and Physical Design for Rapid Timing Closure of Large-Scale FPGA Designs

> A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

> > by

Licheng Guo

2022

© Copyright by Licheng Guo 2022

#### ABSTRACT OF THE DISSERTATION

## Co-optimizing High-Level Synthesis and Physical Design for Rapid Timing Closure of Large-Scale FPGA Designs

by

Licheng Guo Doctor of Philosophy in Computer Science University of California, Los Angeles, 2022 Professor Jingsheng Jason Cong, Chair

High-level synthesis (HLS) tools simplify the FPGA design processes by allowing users to express their designs in high-level languages such as C/C++ or OpenCL. In this way, users could focus on algorithmic optimization with less concern for the cycle-by-cycle details at the register-transfer level (RTL). However, FPGA development flows still have two major limitations that hinder the adoption of FPGAs:

- Limited achievable frequency. There still exists a considerable gap between the qualityof-result (QoR) of an HLS-generated design and what is achievable by an RTL expert, especially the maximum operating frequency of the design. With the designs being scaled up in size, the final achievable frequency will be even lower. Unfortunately, a frequency degradation will directly lead to a proportional performance drop.

- Prolonged compilation time. In the current FPGA CAD flow, the RTL generated by the HLS compiler will be passed to the traditional synthesis and implementation tool. Although the C-to-RTL compilation is relatively quick, the RTL-to-bitstream implementation process will take much longer. With the designs becoming increasingly complex and the FPGA devices larger, the compile time surges from hours to days. Such an overlong process will seriously limit the working efficiency of engineers, especially when compared to software compilation that only takes seconds or minutes.

We observe that the existing FPGA CAD flows have not taken full advantage of HLS for further timing optimization and compilation reduction. Currently, the synthesis, placement, and routing tools are implemented and optimized to handle arbitrary RTL inputs. Those tools will adhere to the cycle-accurate behavior of the input design to ensure the correctness of the output. However, HLS-generated RTL is highly flexible and may tolerate additional pipeline registers without causing functional errors. Such latency-insensitive properties could significantly help the downstream compilation with timing closure. However, in the current toolchains, the HLS compilation is a standalone step, and the HLS-generated RTL will be treated in the same way as manually-written RTL by the logic synthesis tool. As a result, the information on pipeline flexibility in HLS designs will be lost, and the downstream physical implementation process cannot insert pipeline registers for timing closure.

Based on this observation, we propose methods to co-optimize the HLS compilation and the physical design process, which will enable frequency improvement and speed up the hardware accelerator development process simultaneously. Different from the conventional compilation stacks that separate the HLS compilation from the downstream physical implementation process, we propose to bridge the gap between HLS and physical design organically. By facilitating placement and routing with the latency-insensitive information of HLS, and in turn by guiding the HLS compilation with the physical layout information, we could achieve significant improvement in QoR and reduction in compile time.

Centered around this core idea, my thesis consists of three major parts. First, we explore how to improve the inherent timing quality of the RTL generated by HLS. Next, we couple HLS scheduling with coarse-grained floorplanning to improve the achievable frequency. Finally, we take one step further by partitioning the design for parallel placement and routing, then efficiently stitch them together without losing timing quality.

First, the thesis addresses the timing-closure challenge by improving the inherent timing quality of the machine-generated RTL. This chapter studies the timing issues in a diverse set of realistic and complex FPGA HLS designs, including two of my previously-published accelerator designs for genome sequencing. We observe that in almost all cases, the frequency degradation is caused by the broadcast structures generated by the HLS compiler. We classify three major types of broadcasts and propose a set of effective yet easy-to-implement approaches. Our experimental results show that our methods can improve the maximum frequency of a set of nine representative HLS benchmarks by 53% on average.

In addition to optimizing the QoR of HLS by itself, the thesis further pushes up the final frequency by coupling HLS compilation with floorplanning. We propose AutoBridge, an automated framework that couples a coarse-grained floorplanning step with pipelining during HLS compilation. Since pipelining may introduce additional latency, we further present analysis and algorithms to ensure the added latency will not compromise the overall throughput. In our experiments with a total of 43 design configurations, we improve the average frequency from 147 MHz to 297 MHz (a 102% improvement) with no loss of throughput and a negligible change in resource utilization. Notably, in 16 experiments, we make the originally unroutable designs achieve 274 MHz on average. AutoBridge was recognized with the Best Paper Award in FPGA 2021.

Finally, we take one step further to enable parallel physical implementation on top of our HLS-floorplan co-design methodology. We propose a split compilation approach based on the pipelining flexibility at the HLS level. The pipeline flexibility allows us to partition designs for parallel placement and routing without timing degradation. Our research produces RapidStream, a parallelized and physical-integrated compilation framework that takes in a latency-insensitive program in C/C++ and generates a fully placed and routed implementation. When tested on the AMD/Xilinx U280 FPGA, we observed a 5-7× compile time reduction and a  $1.3\times$  frequency increase. RapidStream was recognized with the Best Paper Award in FPGA 2022.

In conclusion, my thesis targets two of the most challenging problems for modern EDA tools: timing closure and agile compilation. We first study the fanout optimization at the HLS level. Next, we explore the co-optimization of HLS and floorplanning, which has been used by at least eight other accelerator design projects. Finally, we enable the split compilation of HLS designs to reduce the compile time significantly. At the end of the thesis, we discuss future directions, including extending the methodology to support the compilation of RTL designs, multi-FPGA designs, and ASIC designs.

The dissertation of Licheng Guo is approved.

Zhiru Zhang

George Varghese

Anthony John Nowatzki

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles

2022

This dissertation is dedicated to my family, my teachers, my friends, and all who have helped and inspired me.

### TABLE OF CONTENTS

| 1        | Intr | oducti   | on                                                                   | 1  |

|----------|------|----------|----------------------------------------------------------------------|----|

|          | 1.1  | Curren   | nt Challenges in FPGA CAD Flow                                       | 2  |

|          | 1.2  | Thesis   | Overview                                                             | 3  |

|          |      | 1.2.1    | Broadcast-Aware Optimization of HLS Code Generation                  | 5  |

|          |      | 1.2.2    | Coupling Global Floorplanning with HLS Pipelining                    | 5  |

|          |      | 1.2.3    | HLS-Based Partitioning and Stitching Methodology for Parallel Physi- |    |

|          |      |          | cal Design                                                           | 6  |

| <b>2</b> | Bac  | kgrou    | nd                                                                   | 8  |

|          | 2.1  | High-l   | Level Synthesis                                                      | 9  |

|          | 2.2  | Logic    | Synthesis                                                            | 10 |

|          | 2.3  | Placer   | nent                                                                 | 12 |

|          | 2.4  | Routin   | ng                                                                   | 12 |

|          | 2.5  | Relate   | ed Works                                                             | 13 |

|          |      | 2.5.1    | Physical-Aware HLS Timing Optimization                               | 14 |

|          |      | 2.5.2    | Physical-Independent HLS Timing Optimization                         | 15 |

|          |      | 2.5.3    | Accelerating the FPGA CAD Flow                                       | 15 |

|          |      | 2.5.4    | Latency Insensitive Design                                           | 17 |

|          |      | 2.5.5    | Other Related Works                                                  | 19 |

| 3        | Ana  | alysis a | and Optimization of the Implicitly Broadcasts by HLS                 | 21 |

|          | 3.1  | Introd   | luction                                                              | 22 |

|          | 3.2  | Classi   | fication of HLS Broadcasts                                           | 24 |

|          |      | 3.2.1    | Data Signal Broadcast                                                | 24 |

|   |                     | 3.2.2                                                         | Control Signal Broadcast - Synchronization                                                        | 26                         |

|---|---------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------|

|   |                     | 3.2.3                                                         | Control Signal Broadcast - Pipeline                                                               | 28                         |

|   | 3.3                 | Appro                                                         | aches                                                                                             | 28                         |

|   |                     | 3.3.1                                                         | Broadcast-Aware Scheduling                                                                        | 29                         |

|   |                     | 3.3.2                                                         | Synchronization Logic Pruning                                                                     | 30                         |

|   |                     | 3.3.3                                                         | Skid-Buffer-Based Pipeline Control                                                                | 31                         |

|   | 3.4                 | Exper                                                         | iments                                                                                            | 33                         |

|   |                     | 3.4.1                                                         | Benchmarks                                                                                        | 33                         |

|   |                     | 3.4.2                                                         | Case Study for Broadcast-Aware Scheduling                                                         | 33                         |

|   |                     | 3.4.3                                                         | Synchronization Logic Pruning                                                                     | 35                         |

|   |                     | 3.4.4                                                         | Skid-Buffer-Based Pipeline Control                                                                | 36                         |

|   |                     | 3.4.5                                                         | Combined Effect                                                                                   | 38                         |

|   | 3.5                 | Concl                                                         | usion                                                                                             | 39                         |

| 4 | Aut                 | oBrid                                                         | no. Counting Coores Cusingd Elegendouring and Direliging for                                      |                            |

|   | 1100                |                                                               | e: Compling Coarse-Grained Floorplanning and Pibelining for                                       |                            |

|   | igh-F               |                                                               | ge: Coupling Coarse-Grained Floorplanning and Pipelining for<br>ncy HLS Design on Multi-Die FPGAs | 40                         |

|   | <b>igh-F</b><br>4.1 | reque                                                         |                                                                                                   | <b>40</b><br>40            |

|   | 0                   | <b>reque</b><br>Introd                                        | ncy HLS Design on Multi-Die FPGAs                                                                 |                            |

|   | 4.1                 | <b>reque</b><br>Introd                                        | ncy HLS Design on Multi-Die FPGAs                                                                 | 40                         |

|   | 4.1                 | <b>reque</b><br>Introd<br>Backg                               | ncy HLS Design on Multi-Die FPGAs                                                                 | 40<br>44                   |

|   | 4.1                 | requent<br>Introd<br>Backg<br>4.2.1<br>4.2.2                  | Acy HLS Design on Multi-Die FPGAs                                                                 | 40<br>44<br>44             |

|   | 4.1<br>4.2          | requent<br>Introd<br>Backg<br>4.2.1<br>4.2.2                  | Acy HLS Design on Multi-Die FPGAs                                                                 | 40<br>44<br>44<br>45       |

|   | 4.1<br>4.2          | requer<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Coupl          | Acy HLS Design on Multi-Die FPGAs                                                                 | 40<br>44<br>44<br>45<br>46 |

|   | 4.1<br>4.2          | requer<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Coupl<br>4.3.1 | Acy HLS Design on Multi-Die FPGAs                                                                 | 40<br>44<br>45<br>46<br>46 |

|   |     | 4.4.1                                                                                                                                               | Pipelining Followed by Latency Balancing for Dataflow Designs $\ . \ .$                                                                                  | 52                                                                                                         |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   |     | 4.4.2                                                                                                                                               | Latency Balancing Algorithm                                                                                                                              | 53                                                                                                         |

|   |     | 4.4.3                                                                                                                                               | Extension to Non-Dataflow Designs                                                                                                                        | 55                                                                                                         |

|   | 4.5 | Exper                                                                                                                                               | iments                                                                                                                                                   | 57                                                                                                         |

|   |     | 4.5.1                                                                                                                                               | Implementation Details                                                                                                                                   | 57                                                                                                         |

|   |     | 4.5.2                                                                                                                                               | Benchmarks                                                                                                                                               | 59                                                                                                         |

|   |     | 4.5.3                                                                                                                                               | Frequency Improvements                                                                                                                                   | 61                                                                                                         |

|   |     | 4.5.4                                                                                                                                               | Control Experiments                                                                                                                                      | 65                                                                                                         |

|   |     | 4.5.5                                                                                                                                               | Scalability                                                                                                                                              | 66                                                                                                         |

|   | 4.6 | Concl                                                                                                                                               | usions                                                                                                                                                   | 67                                                                                                         |

| 5 | Par | allel P                                                                                                                                             | hysical Implementation of HLS Designs for Fast Timing Closure.                                                                                           | 68                                                                                                         |

| 0 |     |                                                                                                                                                     |                                                                                                                                                          |                                                                                                            |

|   | 5.1 | Introd                                                                                                                                              | luction                                                                                                                                                  | 69                                                                                                         |

|   | 5.2 | Prolin                                                                                                                                              | ninaries                                                                                                                                                 | 74                                                                                                         |

|   | 0.2 | 1 101111                                                                                                                                            |                                                                                                                                                          | 74                                                                                                         |

|   | 0.2 | 5.2.1                                                                                                                                               | Problem Scope                                                                                                                                            | 74<br>74                                                                                                   |

|   |     |                                                                                                                                                     |                                                                                                                                                          |                                                                                                            |

|   |     | 5.2.1                                                                                                                                               | Problem Scope                                                                                                                                            | 74                                                                                                         |

|   | 5.3 | 5.2.1<br>5.2.2<br>5.2.3                                                                                                                             | Problem Scope                                                                                                                                            | 74<br>74                                                                                                   |

|   |     | 5.2.1<br>5.2.2<br>5.2.3                                                                                                                             | Problem Scope                                                                                                                                            | 74<br>74<br>74                                                                                             |

|   |     | 5.2.1<br>5.2.2<br>5.2.3<br>Partit                                                                                                                   | Problem Scope                                                                                                                                            | 74<br>74<br>74<br>75                                                                                       |

|   |     | <ul> <li>5.2.1</li> <li>5.2.2</li> <li>5.2.3</li> <li>Partit</li> <li>5.3.1</li> <li>5.3.2</li> </ul>                                               | Problem Scope                                                                                                                                            | <ul> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> </ul>                                     |

|   | 5.3 | <ul> <li>5.2.1</li> <li>5.2.2</li> <li>5.2.3</li> <li>Partit</li> <li>5.3.1</li> <li>5.3.2</li> </ul>                                               | Problem Scope                                                                                                                                            | <ul> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>76</li> </ul>                         |

|   | 5.3 | <ul> <li>5.2.1</li> <li>5.2.2</li> <li>5.2.3</li> <li>Partit</li> <li>5.3.1</li> <li>5.3.2</li> <li>Parall</li> </ul>                               | Problem Scope                                                                                                                                            | <ul> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>76</li> <li>79</li> </ul>             |

|   | 5.3 | <ul> <li>5.2.1</li> <li>5.2.2</li> <li>5.2.3</li> <li>Partit</li> <li>5.3.1</li> <li>5.3.2</li> <li>Parall</li> <li>5.4.1</li> <li>5.4.2</li> </ul> | Problem Scope   Organization of the FPGA Fabric   Flow Overview   ioning   Problem Description   Approaches   Iterative Placement of Anchors and Islands | <ul> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>76</li> <li>79</li> <li>79</li> </ul> |

|      | 5.5.2   | Challenges and Previous Approaches                                                                                                                   |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 5.5.3   | Routing the Clock Trunk $(S_{10})$                                                                                                                   |

|      | 5.5.4   | Locking the Clock Buffers for Anchors $(S_{10})$                                                                                                     |

|      | 5.5.5   | Routing and Merging the Local Clocks $(S_{11})$                                                                                                      |

| 5.6  | Stitchi | ng and Inter-Island Routing                                                                                                                          |

|      | 5.6.1   | Island Merging $(S_{12}, S_{13})$                                                                                                                    |

|      | 5.6.2   | Inter-Island Routing $(S_{14})$                                                                                                                      |

| 5.7  | Accele  | rate Routing with Customized Partial Router (RapidStream $1.0$ ) 87                                                                                  |

| 5.8  | Pre-Pa  | artial-Routing of Inter-Island Nets (RapidStream 2.0) 90                                                                                             |

|      | 5.8.1   | Avoid Routing Conflicts                                                                                                                              |

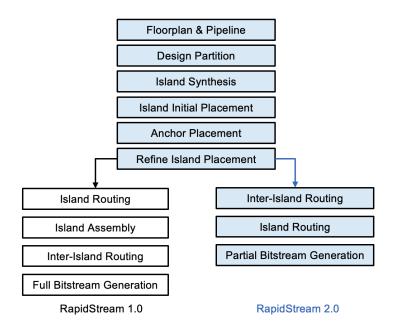

| 5.9  | Compa   | arison of RapidStream 1.0 and 2.0                                                                                                                    |

| 5.10 | Evalua  | tion of RapidStream 1.0                                                                                                                              |

|      | 5.10.1  | Implementation Details                                                                                                                               |

|      | 5.10.2  | Benchmarks                                                                                                                                           |

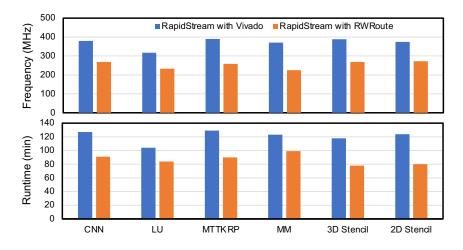

|      | 5.10.3  | Runtime Reduction                                                                                                                                    |

|      | 5.10.4  | Fast Inter-Island Routing                                                                                                                            |

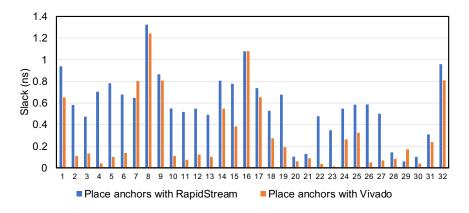

|      | 5.10.5  | Anchor Placement                                                                                                                                     |

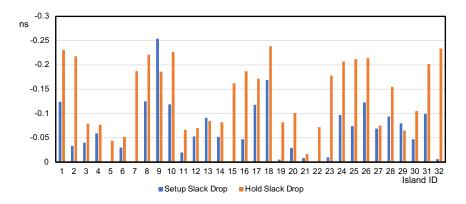

|      | 5.10.6  | Clock Management                                                                                                                                     |

| 5.11 | Evalua  | tion of RapidStream $2.0 \ldots 101$ |

|      | 5.11.1  | Implementation Details                                                                                                                               |

|      | 5.11.2  | Benchmarks                                                                                                                                           |

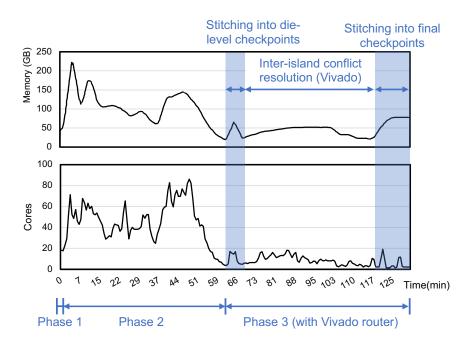

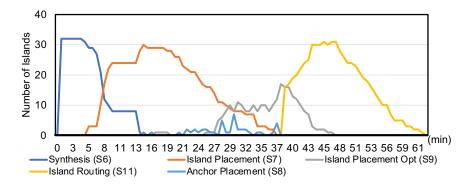

|      | 5.11.3  | Profiling of RapidStream 2.0 Compilation                                                                                                             |

| 5.12 | Conclu  | 104                                                                                                                                                  |

| Con  | clusio  | $1 \dots \dots$                                |

6

| 6.1     | Thesis | Summary and Contributions                                                                                                  |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------|

| 6.2     | Vision | and Future Work                                                                                                            |

|         | 6.2.1  | Extension to RTL designs                                                                                                   |

|         | 6.2.2  | Extension to Other FPGA Devices and ASIC                                                                                   |

|         | 6.2.3  | Efficient Emulation                                                                                                        |

|         | 6.2.4  | Multi-FPGA Programming                                                                                                     |

| 6.3     | Thesis | $Impact \dots \dots$ |

| Refere  | nces   |                                                                                                                            |

| IUCICIC |        |                                                                                                                            |

### LIST OF FIGURES

| 1.1  | A typical FPGA CAD flow.                                                        | 2  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | A motivating example showing the compile time and the achievable frequency of   |    |

|      | a set of systolic array designs                                                 | 4  |

| 2.1  | A typical FPGA design flow starting from behavior-level specifications          | 8  |

| 2.2  | A typical FPGA HLS flow. [CLN11]                                                | 9  |

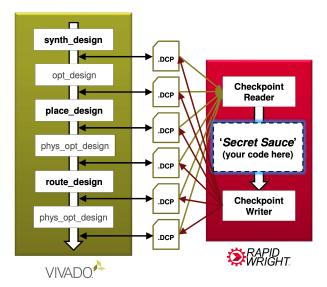

| 2.3  | Overview of how RapidWright and Vivado interacts [LK18]                         | 17 |

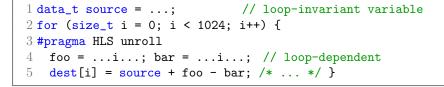

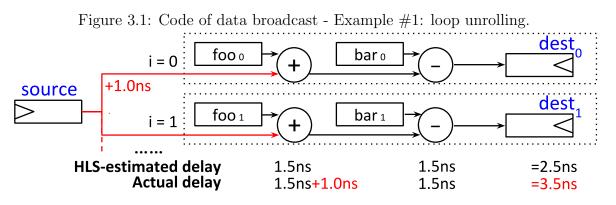

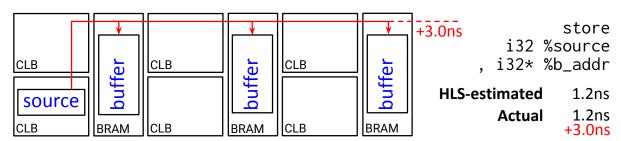

| 3.1  | Code of data broadcast - Example #1: loop unrolling                             | 25 |

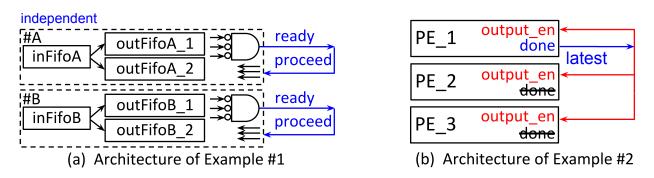

| 3.2  | HLS-generated architecture of Fig. 3.1                                          | 25 |

| 3.3  | Code of data broadcast - Example #2: large array                                | 26 |

| 3.4  | HLS-generated architecture of Fig. 3.3                                          | 26 |

| 3.5  | Code of synchronization - Example #1                                            | 27 |

| 3.6  | Code of synchronization - Example #2                                            | 27 |

| 3.7  | HLS-generated architecture of the code above.                                   | 27 |

| 3.8  | Code example of pipeline control signal broadcast                               | 28 |

| 3.9  | HLS-generated architecture of pipeline control                                  | 28 |

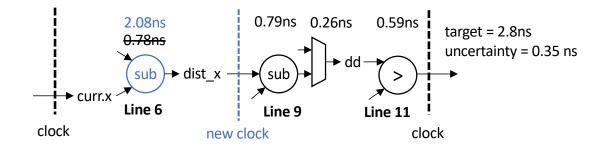

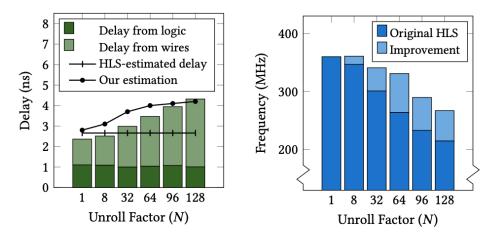

| 3.10 | Vivado HLS estimated delay, our calibrated delay, and raw experimental delay on |    |

|      | different operators                                                             | 30 |

| 3.11 | Pruned architecture corresponding to Figure 3.7.                                | 30 |

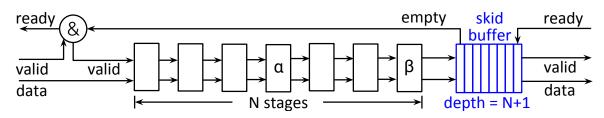

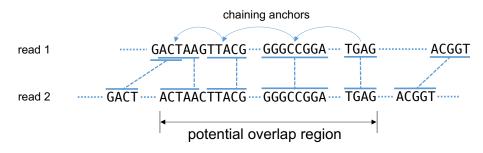

| 3.12 | Skid-buffer-based pipeline control architecture                                 | 32 |

| 3.13 | Multi-level skid-buffer-based pipeline control.                                 | 32 |

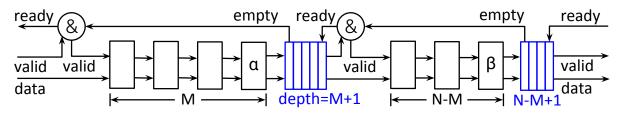

| 3.14 | Finding estimated overlap region.                                               | 34 |

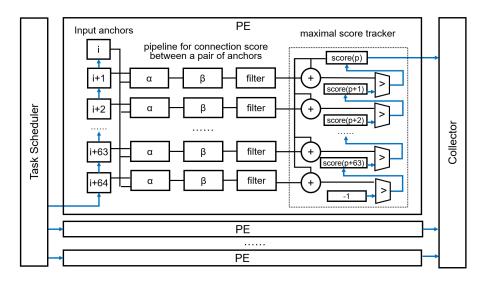

| 3.15 | Overview of a processing element array                                          | 35 |

| 3.16 | Design code snippet from [GLR19]. The loop-invariant variables (broadcast                       |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | sources) are marked blue.                                                                       | 36 |

| 3.17 | An operation chain with broadcast operators.                                                    | 36 |

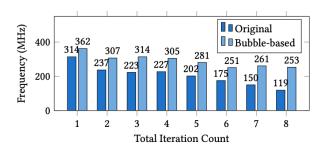

| 3.18 | Optimization of data broadcast                                                                  | 37 |

| 3.19 | The achieved frequency of the Jacobi kernels.                                                   | 37 |

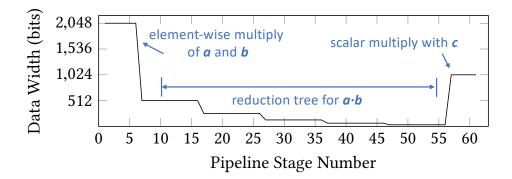

| 3.20 | Bitwidth of the passed data between stages.                                                     | 38 |

| 3.21 | Code for the large buffer access example                                                        | 38 |

| 3.22 | Achieved frequencies of the stream buffer design.                                               | 39 |

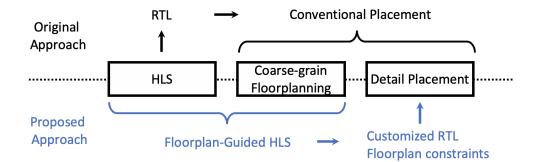

| 4.1  | Core idea of the proposed methodology.                                                          | 42 |

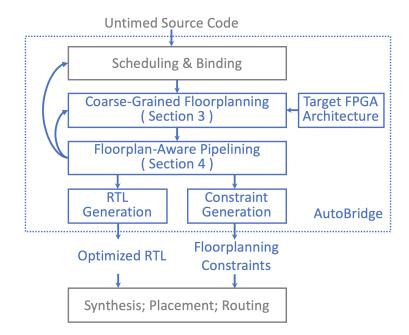

| 4.2  | Overview of the AutoBridge Framework. Grey boxes represent the original software                |    |

|      | flow and blue boxes represent components of AutoBridge                                          | 43 |

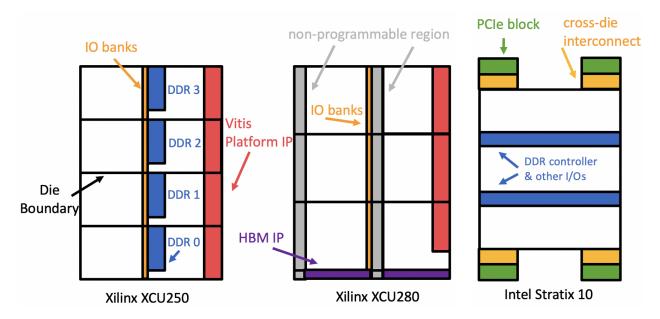

| 4.3  | Block diagrams of three representative FPGA architectures: the Xilinx Alveo                     |    |

|      | U250, U280 (based on the Xilinx UltraScale+ architecture), and the Intel Stratix 10.            | 45 |

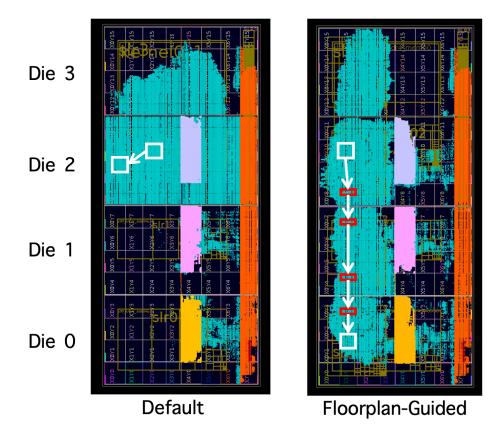

| 4.4  | Implementation results of a CNN accelerator on the Xilinx U250 FPGA. Spreading                  |    |

|      | the design across the device helps reduce local congestion, while the die-crossing              |    |

|      | wires are additionally pipelined                                                                | 46 |

| 4.5  | Implementation results of a stencil computing design on U280. Floorplanning                     |    |

|      | during HLS compilation significantly benefits the physical design tools                         | 47 |

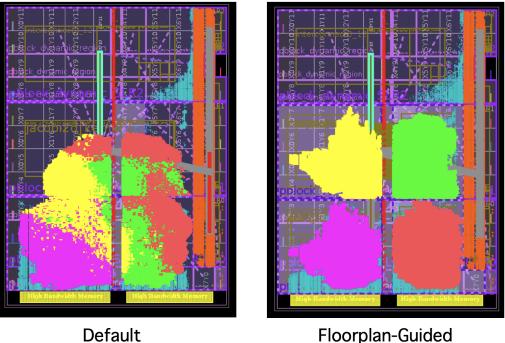

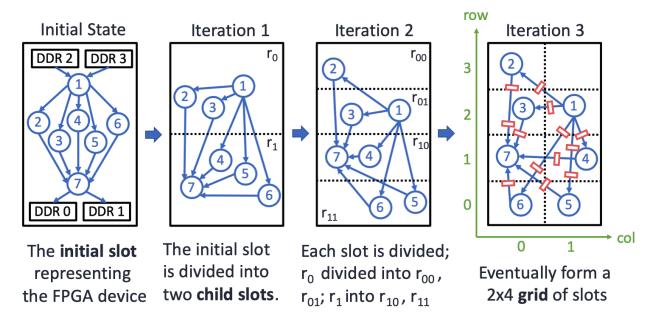

| 4.6  | Generating the floorplan for a target $2 \times 4$ grid. Based on the floorplan, all            |    |

|      | the cross-slot connections will be accordingly pipelined (marked in red) for high               |    |

|      | frequency.                                                                                      | 49 |

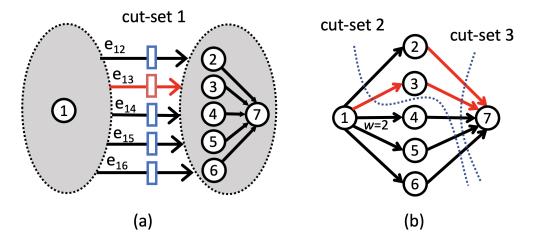

| 4.7  | Assume that the edges $e_{13}, e_{37}$ and $e_{27}$ are pipelined according to some floorplan,  |    |

|      | and each of them carries 1 unit of inserted latency. Also, assume that the bit                  |    |

|      | width of $e_{14}$ is 2 and all other edges are 1. In the latency balancing step, the            |    |

|      | optimal solution is adding 2 units of latency to each of $e_{47}, e_{57}, e_{67}$ and 1 unit of |    |

|      | latency to $e_{12}$ . Note that edge $e_{27}$ and $e_{37}$ can exist in the same cut-set        | 53 |

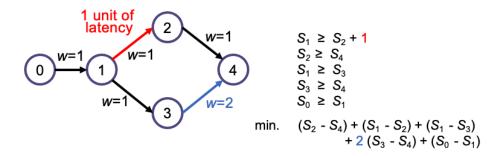

| 4.8  | Example SDC formulation for the latency balancing problem                             | 55 |

|------|---------------------------------------------------------------------------------------|----|

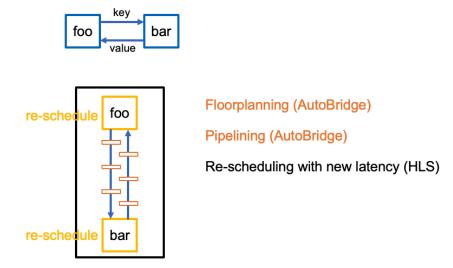

| 4.9  | Example of AutoBridge on a key-value store                                            | 57 |

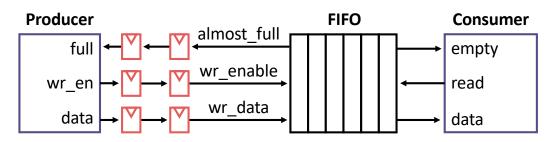

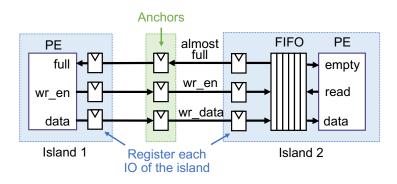

| 4.10 | Pipelining FIFO interfaces using almost-full FIFOs                                    | 58 |

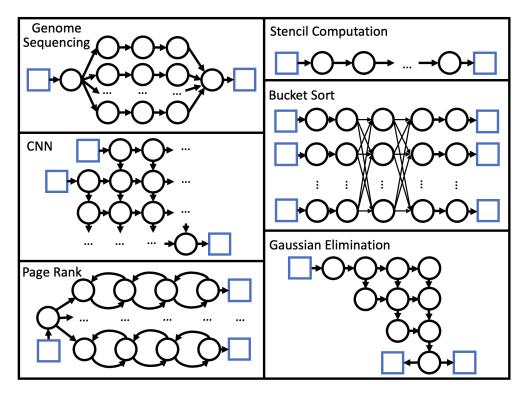

| 4.11 | Topologies of the benchmarks. Blue rectangles represent external memory ports         |    |

|      | and black circles represent the computation kernels of the design. In the genome      |    |

|      | sequencing design, the arrows represent BRAM channels; in other designs, the          |    |

|      | arrows represent FIFO channels                                                        | 60 |

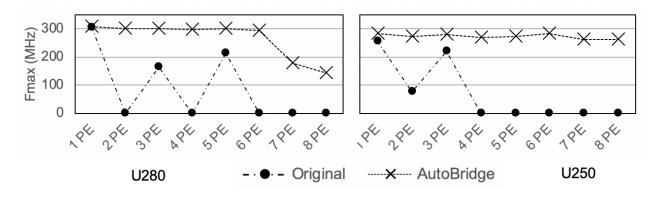

| 4.12 | Results of the stencil computation designs                                            | 62 |

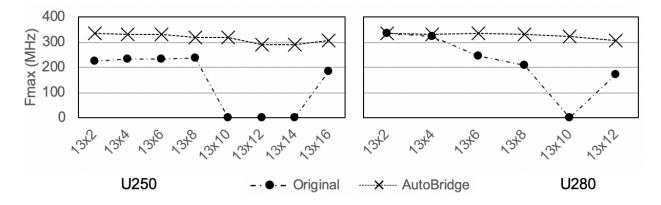

| 4.13 | Results of the CNN accelerator designs                                                | 63 |

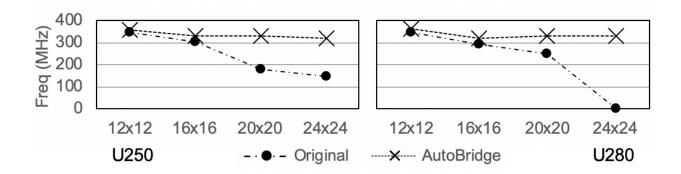

| 4.14 | Results of the Gaussian elimination designs.                                          | 64 |

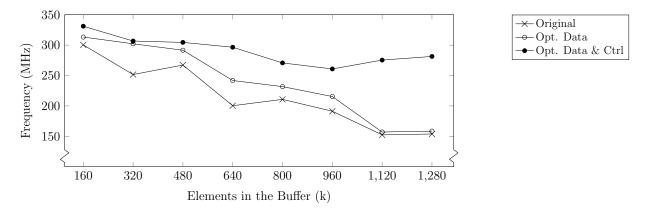

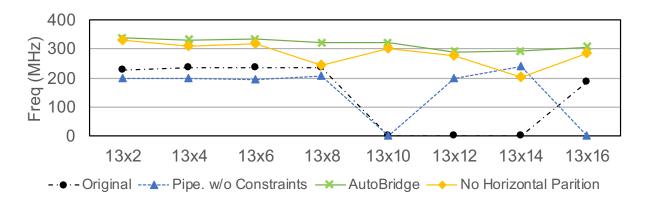

| 4.15 | Control experiments with the CNN accelerators                                         | 66 |

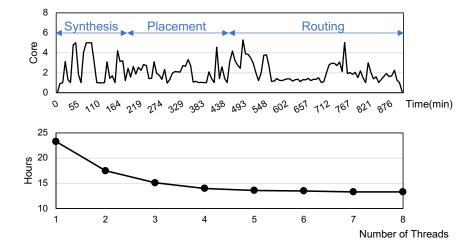

| 5.1  | The upper figure shows the number of active CPU cores when implementing a CNN         |    |

|      | benchmark by Vivado (8 threads) on a 56-core server. The total implementation         |    |

|      | process takes about 14 hours, with an average CPU utilization of 2.1 cores. The       |    |

|      | lower figure displays the runtime as we increase the number of threads                | 69 |

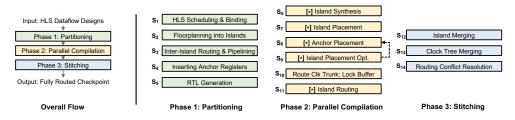

| 5.2  | An overview of our RapidStream workflow. We use [*] to denote a parallelized step.    | 70 |

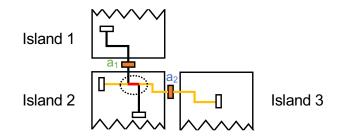

| 5.3  | Illustration of results obtained in different phases. In the final output, the orange |    |

|      | part shows the anchor registers, the cyan part shows the implemented partitions.      | 70 |

| 5.4  | Comparison of RapidStream 1.0 and 2.0.                                                | 72 |

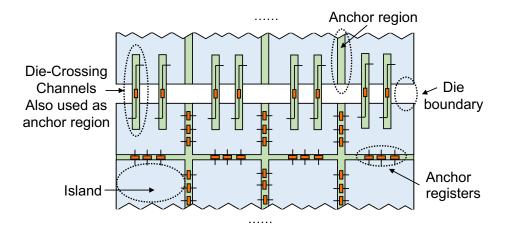

| 5.5  | Organization of the FPGA device                                                       | 75 |

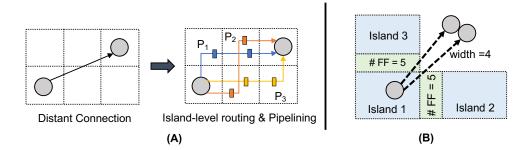

| 5.6  | (A) three potential routes for a connection. (B) Each anchor region (in green)        |    |

|      | only has 5 Flip-Flops, so the two connections (both of width 4) cannot go through     |    |

|      | the same anchor region.                                                               | 77 |

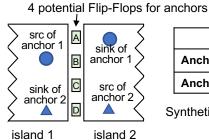

| 5.7  | Inserting anchor registers.                                                           | 78 |

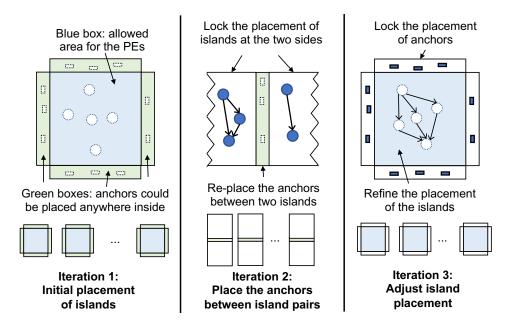

| 5.8  | Demonstration of the iterative placement.                                             | 80 |

| 5.9  | Illustration of the anchor placement formulation.                                     | 81 |

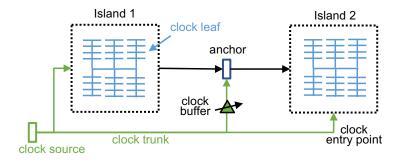

| 5.10 | Route different segments of the clock separately and maintain a stable clock skew    |    |

|------|--------------------------------------------------------------------------------------|----|

|      | in one pass. Step 1: route the clock trunk. Step 2: lock the delay level of the      |    |

|      | clock buffers for anchors. Step 3: route each island and merge with the clock trunk. | 83 |

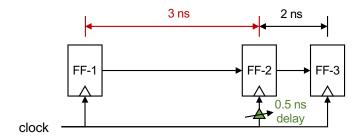

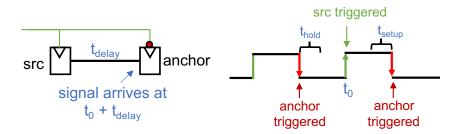

| 5.11 | By introducing an artificial clock delay of 0.5 ns to FF-2, the critical path is     |    |

|      | reduced from 3 ns to 2.5 ns                                                          | 84 |

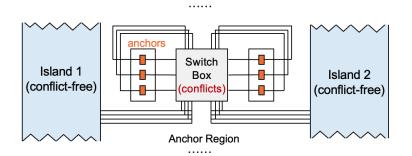

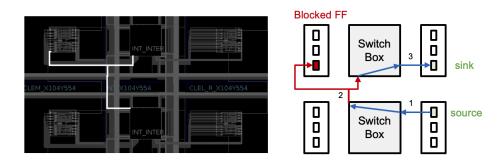

| 5.12 | Detailed view of anchor region. Only one switch box is shown                         | 86 |

| 5.13 | Pairwise inter-island routing will not work because it may cause conflicts inside    |    |

|      | the island                                                                           | 86 |

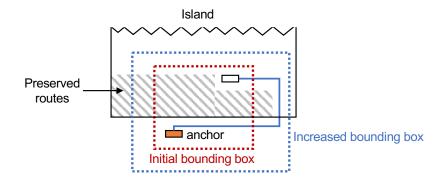

| 5.14 | Required long routing detours outside of the initial net bounding box                | 88 |

| 5.15 | Make anchors trigger on negative clock edges.                                        | 89 |

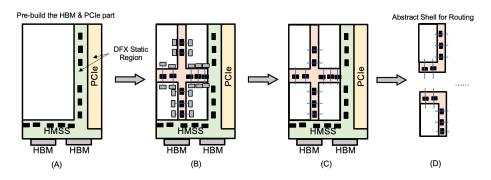

| 5.16 | Partial routing of the inter-island nets using a skeleton design. We first do a      |    |

|      | complete routing of the nets from the anchor registers to the source/sink cells      |    |

|      | inside the island, then we prune away most routing nodes inside the island and       |    |

|      | leave the net in an antenna state. The endpoints of the inter-island nets are        |    |

|      | viewed as virtual partition pins. Later when we route the island, the router will    |    |

|      | connect the island cells to those partition pins                                     | 90 |

| 5.17 | Example of a route with a multi-output node. The red FF is made unreachable          |    |

|      | by other nets since routing node 2 has been occupied                                 | 92 |

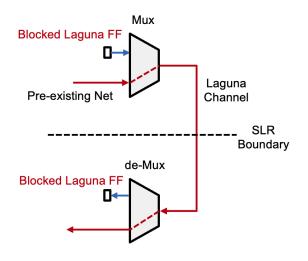

| 5.18 | Example of a route with an SLL node. The red FFs are made unreachable since          |    |

|      | the SLL node is the only input/output connection to them                             | 92 |

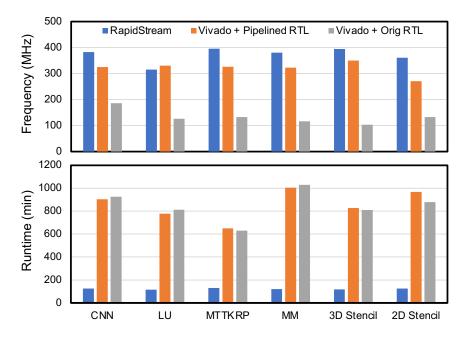

| 5.19 | Comparison of the runtime and achievable frequency between RapidStream and           |    |

|      | Vivado                                                                               | 96 |

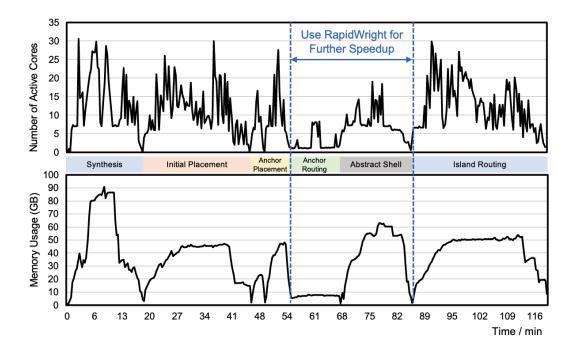

| 5.20 | CPU and memory usage of the RapidStream run on the CNN design. No re-route           |    |

|      | is needed after die-level stitching (Sec. 5.10.1)                                    | 97 |

| 5.21 | Number of active jobs in Phase 2                                                     | 98 |

| 5.22 | Runtime comparison in conflict resolution.                                           | 99 |

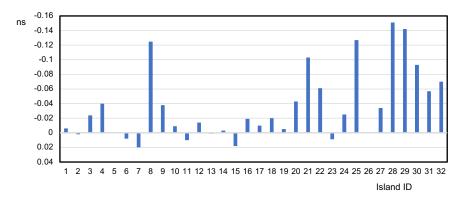

| 5.23 | Post-placement slack between using the Vivado placer or the min-cost matching                  |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | placer for anchor placement                                                                    | 100 |

| 5.24 | Timing loss after stitching w/o clock management. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 100 |

| 5.25 | Clock preservation reduces timing degradation.                                                 | 101 |

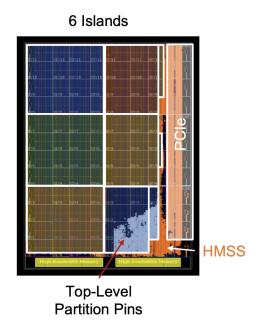

| 5.26 | An example shell for RapidStream 2.0 corresponding to Figure 5.16(C). $\ldots$                 | 102 |

| 5.27 | Profiling of the CPU and memory usage in RapidStream 2.0 for the gaussian-float                |     |

|      | benchmark.                                                                                     | 104 |

| 6.1  | Example annotation to an RTL module interface.                                                 | 108 |

## LIST OF TABLES

| 3.1 | Timing improvements and post-implementation resources on HLS designs using                            |     |

|-----|-------------------------------------------------------------------------------------------------------|-----|

|     | our proposed solutions                                                                                | 33  |

| 3.2 | Experiment results on 512-wide vector product.                                                        | 38  |

| 3.3 | Experiment results on pattern matching                                                                | 39  |

| 4.1 | Coordinates of selected vertices in Figure 4.6.                                                       | 51  |

| 4.2 | Post-placement results of the CNN designs on U250. The design point of $13 \times 12$                 |     |

|     | failed placement and $13 \times 10$ and $13 \times 14$ failed routing with the original tool flow.    | 63  |

| 4.3 | Results of Gaussian elimination designs on U250                                                       | 63  |

| 4.4 | Experiment result of genome sequencing on U250                                                        | 64  |

| 4.5 | Results of the bucket sort designs on U280                                                            | 65  |

| 4.6 | Computing time for the CNN test cases targeting the U250 FPGA. $Div-1$ and                            |     |

|     | $Div\mathchar`2$ denote the first and the second vertical decomposition, and $Div\mathchar`3$ denotes |     |

|     | the first horizontal decomposition. $Re$ -balance denotes the delay balancing                         | 67  |

| 5.1 | Benchmarks for RapidStream evaluation                                                                 | 96  |

| 5.2 | Benchmarks for RapidStream 2.0 evaluation                                                             | 102 |

| 5.3 | Detailed comparison between RapidStream 2.0 and Vivado                                                | 103 |

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the support, encouragement, advice, and help from my family, teachers, mentors, friends, and all who have inspired me and helped me along the way to get to this point both academically, professionally, and personally.

First and foremost, I would like to thank my advisor and committee chair, Prof. Jason Cong, for his advice, support, and guidance throughout the last 5 years. I am fortunate to have the opportunity to study at and grow with the VAST lab and learn a lot more than just EDA. I would like to thank Jason for allowing me to explore topics I found interesting, for trusting me with highly risky projects, for providing invaluable guidance and advice, for connecting me to domain experts outside the lab, and for his unconditional support and constant availability throughout my time at UCLA. I am grateful to Jason for my fruitful Ph.D. experience like no other.

I would also like to thank Prof. Zhiru Zhang for participating in every one of my projects and providing insightful guidance. Zhiru is always available to discuss my problems and responds quickly when I need help. In addition, Zhiru has helped with my writing significantly. I enjoy discussing with him and learning valuable lessons from him.

I appreciate the advice from Prof. George Varghese and Prof. Tony Nowatzky. I want to thank Prof. George Varghese for teaching me the engineering principles that I will always remember. I learned important lessons about computer architecture and domain-specific accelerators from Prof. Tony Nowatzki. George and Tony have brought up invaluable suggestions on extending my research projects to broader applications; I feel lucky to have them on my committee.

I want to thank Pongstorn Maidee, Chris Lavin, Eddie Hung, and Alireza Kaviani for their crucial support for the RapidStream project. The RapidStream project will never succeed without their devotion and support.

I would also like to thank all of my collaborators, without whom our projects would

never have succeeded. First, I want to thank Jason Lau, Yuze Chi, Weikang Qiao, Jie Wang, Linghao Song, Yun Zhou, Peng Wei, Zhenyuan Ruan, Tianhe Yu, and Cody Yu, for working together with me. I want to thank Prof. Zhenman Fang, Prof. Peipei Zhou, Prof. Young-Kyu Choi, Prof. Po-Tsang Huang, Prof. Luciano Lavagno, Prof. David Pan, Jianyi Cheng, Atefeh Sohrabizadeh, Karl Marrett, Danial Tan, Suhail Basalama, Stephane Pouget, Chengdi Cao, Neha Prakriya, Jason Kimko, Lorenzo Ferretti, Di Wu, DJ Wang, Gai Liu, Wuxi Li, Zhengrong Wang, Sihao Liu, Jian Weng, Yuanlong Xiao, Xingyu Tian, Alec Lu, Moazin Khatti, Shaojie Xiang, Yi-Hsiang Lai, Ecenur Ustun, Wenqi Cao, Andreas Nowatzyk, Zeyu Kuang, Yue Zhong, Guangcan Li, Haowen Chen, Wenping Wang, Sida Peng, Zixuan Jiang, Pengfei Li, Qiuxiao Chen, Feiyu Chen, Junpei Zhou and many others for their help, guidance and suggestions.

I deeply appreciate the efforts by Jason Lau and Yuze Chi to maintain our server system and voluntarily provide technical support. I want to thank Alexandra Luong and Joseph Brown for all the help on the administrative side.

I am fortunate that my Ph.D. journey turns out to be the best years of my life. Although I was half a world away from home, I have never felt lonely, and I could not be more grateful for my friends. I want to thank Bing Han, Jason Lau, Weikang Qiao, Jie Wang, Zhengrong Wang, and many others for being an irreplaceable part of my Ph.D. journey.

Besides my academic advisors, I also want to thank all my teachers and friends since I was young. Specifically, I want to thank Prof. Peiyong Zhang and Prof. Zheng Shi at Zhejiang University, who led me into the fascinating world of EDA and FPGA. I want to thank my flute teacher, Erika Andres, for helping me find great joy in music through her professional and inspiring lessons. I want to thank my middle school math teacher, Yibo Ji, who helped me build confidence and find joy in learning. I want to thank my middle school Chinese teacher, Qin Li, who played an important role in my cultivating a positive outlook on the world, life, and values. She also taught me important lessons on academic writing that I still find helpful to this day. I want to thank Wei Xie, who was always there to answer my questions and discuss tricky puzzles with me for the entire middle school and high school. I want to thank Feng Xiao, for his encouragement and support, especially in my most difficult days before and after the college entrance exam. I want to thank Ding Zhang for his support and accompany throughout the years. I want to thank Yike Li, we have worked side by side on many of the most important projects, and I have learned a lot from him; I always feel that he is like-minded, and we had much fun together. I want to thank Yifan Yuan, Yifan is one of my most visionary peers, and I appreciate all his advice and guidance. I want to thank Lijun Wang, his perseverance and optimism toward life have inspired me a lot.

I want to thank UCLA and Zhejiang University for providing a free, encouraging, tolerant, vibrant, warm, and supportive environment for their students. I want to thank the Advanced Class of Engineering Education (ACEE) at Zhejiang University, I am honored to be a part of the group, and it has broadened my perspective and connected me to so many good friends.

Most importantly, I thank my parents, Yingtong Xiong and Ling Guo, and my grandparents, Xiaojing Guo, Lamei Zhu, Zhongyin Xiong, and Aifen Ni, for all their extremely hard work that made me who I am, for always being understanding and supportive no matter the situation, and for creating an environment of love, warmth, tolerance, trust, and equality at home. I deeply thank my wife, Xinyi Li, for always being supportive and understanding and for all the love and happiness that we have shared together.

The contents of Chapter 3 is from a collaboration between Jason Lau and me. We made equal contributions to our DAC '20 paper [GLC20], which is the basis of Chapter 3. Specifically, the problem classification part (Section 3.2) is accredited to me, and the solution part (Section 3.3) is accredited to Jason Lau.

This thesis is partially supported by CRISP, one of the six centers in JUMP, a Semiconductor Research Corporation (SRC) program, member companies under the Center for Domain-Specific Computing (CDSC) Industrial Partnership Program, the Intel/NSF CAPA program, the NSF NeuroNex Award No. DBI-1707408 and the NIH Award No. U01MH117079. The authors acknowledge the valuable support of the Xilinx Adaptive Compute Clusters (XACC) Program. We thank Gurobi and GNU Parallel for their support to academia.

#### VITA

- 2014–2018 B.S., Electronic Engineering, Zhejiang University, Hangzhou, China.

- 2018–2021 Master, Computer Science, University of California, Los Angeles, U.S.A.

#### PUBLICATIONS

Licheng Guo, Pongstorn Maidee, Yun Zhou, Chris Lavin, Jie Wang, Yuze Chi, Weikang Qiao, Alireza Kaviani, Zhiru Zhang, Jason Cong, RapidStream: Parallel Physical Implementation of FPGA HLS Designs, *Proceedings of the 2022 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2022)*

Yuze Chi, <u>Licheng Guo</u>, Jason Cong, RapidStream: Accelerating SSSP for Power-Law Graphs, Proceedings of the 2022 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2022)

Linghao Song, Yuze Chi, <u>Licheng Guo</u>, Jason Cong, Serpens: a high bandwidth memory based accelerator for general-purpose sparse matrix-vector multiplication, *Proceedings of the* 59th ACM/IEEE Design Automation Conference (DAC 2022)

Licheng Guo, Yuze Chi, Jie Wang, Jason Lau, Weikang Qiao, Ecenur Ustun, Zhiru Zhang, Jason Cong, AutoBridge: Coupling Coarse-Grained Floorplanning and Pipelining for High-Frequency HLS Design on Multi-Die FPGAs, Proceedings of the 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2021) Jie Wang, <u>Licheng Guo</u>, Jason Cong, AutoSA: A Polyhedral Compiler for High-Performance Systolic Arrays on FPGA, *Proceedings of the 2021 ACM/SIGDA International Symposium* on Field-Programmable Gate Arrays (FPGA 2021)

Yuze Chi, <u>Licheng Guo</u>, Young-kyu Choi, Jie Wang, Jason Cong, Extending High-Level Synthesis for Task-Parallel Programs, *Proceedings of the IEEE 2021 Annual International* Symposium on Field-Programmable Custom Computing Machines (FCCM 2021)

Weikang Qiao, Jihun Oh, <u>Licheng Guo</u>, Mau-Chung Frank Chang, Jason Cong, FANS: FPGA Accelerated Near-Storage Sorting Solution, *Proceedings of the IEEE 2021 Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM 2021)*

Licheng Guo, Jason Lau, Yuze Chi, Jie Wang, Cody Hao Yu, Zhe Chen, Zhiru Zhang, Jason Cong, Proceedings of the 2020 Annual Design Automation Conference (DAC 2020)

Licheng Guo, Jason Lau, Zhenyuan Ruan, Peng Wei, Jason Cong, Hardware Acceleration of Long Read Pairwise Overlapping in Genome Sequencing: A Race Between GPU And FPGA, Proceedings of the IEEE 2019 Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM 2019)

Jason Cong, <u>Licheng Guo</u>, Po-Tsang Huang, Peng Wei, Tianhe Yu, SMEM++: Pipelined and Time-Mux SMEM Seeding Accelerator for Genome Sequencing, *Proceedings of the IEEE* 28th International Conference on Field Programmable Logic and Applications (FPL 2018)

## CHAPTER 1

## Introduction

The slowdown in transistor scaling and the end of Moore's law are pushing us to new computing paradigms. Compared to general computing, specialized hardware devices, such as Field Programmable Gate Arrays (FPGAs), provide a promising solution to achieve intensive computation and energy efficiency [CWA22]. FPGA is a type of reconfigurable integrated circuit designed to be configured by designers. Because of their lower non-recurring engineering costs, reconfigurability, and short time-to-market, FPGAs are becoming increasingly attractive. Beyond the success in traditional applications like fast prototyping for application-specific integrated circuits (ASIC), FPGAs have also demonstrated their applicability as hardware accelerators in modern applications, such as machine learning [FOP18, WLC19, WGC21], genome sequencing [CGH18, GLR19], compression [QDF18, QFC19] and network processing [CCP16, FSP20] and many other fields.

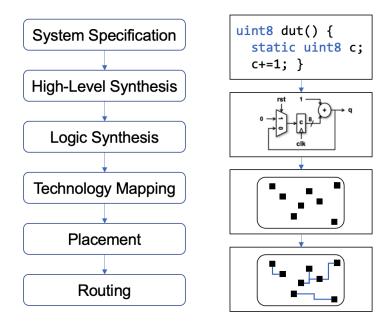

The advancement of FPGA-based design methodologies is inseparable from the support of FPGA computer-aided design (CAD). A typical modern FPGA CAD flow is illustrated in Figure 1.1. Users first describe the architecture of their designs in certain software languages (e.g., OpenCL and C/C++). After that, the high-level synthesis (HLS) tool compiles the program into a cycle-accurate representation in a hardware description language (e.g., Verilog and VHDL). The logic synthesis and the technology mapping step further translate the architectural design into a gate-level netlist. Given the results of the logic design steps, the physical design process will map these abstract logical representations onto physical function units and interconnects on the FPGA fabric. The placement step determines the physical locations of each operator, and the routing step computes the physical interconnects among the function units.

Figure 1.1: A typical FPGA CAD flow.

While RTL design methodology used to be the dominant choice, HLS has emerged as an increasingly popular and promising alternative to cope with the design productivity gap as the complexity of applications and hardware platforms continues to scale up. The key advantage of HLS is that the compiler will automatically convert the *untimed* high-level software programs into cycle-accurate RTL hardware implementations because the process of manual RTL optimization is becoming unequivocally difficult. By raising the level of abstraction from cycle-accurate hardware to untimed software, HLS reduces design effort while optimizing over a larger solution space regarding performance, area, and timing. Such benefits have led to growing development and adoption of both commercial and open-source HLS tools, including AMD/Xilinx Vitis HLS [Xil20b], LegUp HLS [HLS20a], Intel OpenCL [Exa20], Mentor Catapult HLS [HLS20b], and Cadence Stratus HLS [Cad20].

### 1.1 Current Challenges in FPGA CAD Flow

Despite the increasing adoption of HLS because of its design productivity advantage, the overall FPGA CAD flows still have unsatisfactory quality-of-results (QoR) and productivity. Such limitations continue to curb the adoption of FPGA accelerators.

- First, it is challenging to achieve a satisfactory frequency for HLS designs. The downside of a higher abstract level is the lack of control over low-level details. Regarding the frequency bottleneck, current HLS tools work like a black box when generating RTL from the user input. Unfortunately, the compiler does not provide helpful feedback or guidelines on improving the clock frequency at the source level or using additional tool options. It is also challenging for regular HLS users to reverse engineer the synthesized RTL code to identify the timing bottlenecks and optimize the corresponding critical paths in the source program.

- Second, the long end-to-end compilation still takes significant time and hinders productivity. While it only takes a few minutes for the HLS compilation, the generated RTL has to be synthesized into a physical netlist, then goes through the physical design process, including placement and routing. With the ever-increasing size of FPGA designs, the scalability issue of the physical design process becomes more serious, which results in tens of hours or even days of compilation.

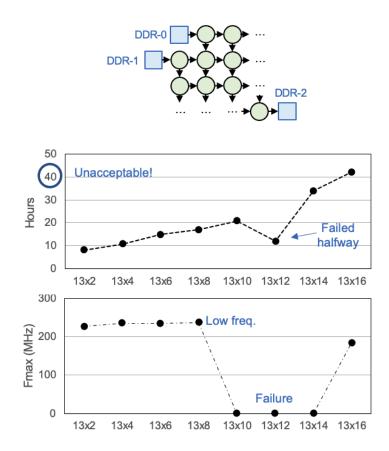

Figure 1.2 shows a motivating example that exposes the limitation of the current FPGA CAD stack. We measure the compilation time and final frequency of a set of systolic array designs of varying sizes. Each processing element of the systolic array is the same. Although this type of design is highly regular in shape, the final frequency is still relatively low. Worse, scaling up the array size leads to a significant increase in compilation time.

#### 1.2 Thesis Overview

This thesis targets two of the most challenging tasks for modern EDA tools: improving the timing quality and reducing the compile time. While these two goals are orthogonal and potentially conflicting<sup>1</sup> to some extent, we manage to address both of them using the same methodology.

The core idea throughout the thesis is to bridge the gap between physical design steps (e.g.,

<sup>&</sup>lt;sup>1</sup>Generally, spending a longer time on more optimization iterations may lead to better QoR and vice versa.

Figure 1.2: A motivating example showing the compile time and the achievable frequency of a set of systolic array designs.

global floorplanning and global routing) and the HLS compilation steps (e.g., scheduling and binding). Since HLS compiles the untimed source code into the cycle-accurate RTL code, it can introduce additional pipelining registers without breaking the overall functionality. With the help of HLS, we can rely less on manual timing optimization, where the designer must carefully adjust the surrounding logic of inserted pipeline registers, which is an error-prone and ad-hoc process.

Built on this important idea, we propose effective and scalable methods to facilitate timing closure and parallelize the physical design process. We start by optimizing the QoR of the code generation of HLS by itself. This step improves the timing quality of the generated RTL regardless of the underlying FPGA fabric. Next, we break the abstraction boundaries by coupling HLS scheduling with floorplanning. This combination significantly helps the placer determine a much better overall distribution of the logic by utilizing the high-level topology of the design; in turn, it helps HLS to identify and pipeline the global interconnects accurately instead of relying on inaccurate modeling. To further extend the idea, we partition an input design at latency-insensitive boundaries to enable parallel placement and routing, dramatically reducing the end-to-end compilation time. Specifically, we made the following contribution.

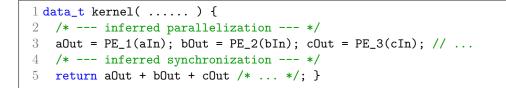

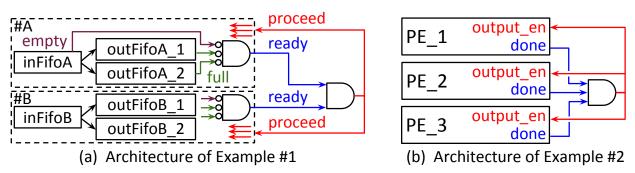

#### 1.2.1 Broadcast-Aware Optimization of HLS Code Generation.

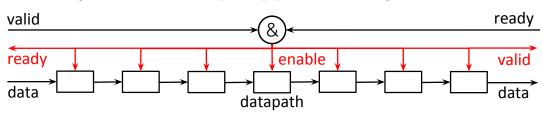

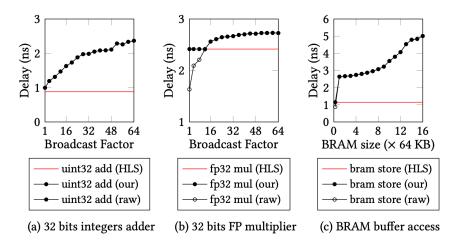

This part of the thesis improves the QoR of the HLS code generation by itself (without interaction with other steps in the FPGA CAD flow). We study the timing issues in a diverse set of realistic and complex FPGA HLS designs and observe that in almost all cases, the frequency degradation is caused by the *broadcast* structures generated by the HLS compiler. We classify three major types of broadcasts in HLS-generated designs, including high-fanout data signals, pipeline flow control signals, and synchronization signals for concurrent modules. We further reveal several limitations of the current HLS tools that result in those broadcast-related timing issues. Finally, we propose a set of effective yet easy-to-implement approaches, including broadcast-aware scheduling, synchronization pruning, and skid-buffer-based flow control. Our experimental results show that our methods can improve the maximum frequency of a set of nine representative HLS benchmarks by 53% on average. In some cases, the frequency gain is more than 100 MHz.

#### 1.2.2 Coupling Global Floorplanning with HLS Pipelining.

This part of the thesis shifts the global floorplanning step into the HLS compilation to improve the final QoR. First, our approach provides HLS with a view of the global physical layout of the design, allowing HLS to more easily identify and pipeline the long wires, especially those crossing the die boundaries. Second, by exploiting the flexibility of HLS pipelining, the floorplanner can distribute the design logic across multiple dies on the FPGA device without degrading clock frequency. This prevents the placer from aggressively packing the logic on a single die which often results in local routing congestion that eventually degrades timing. Since pipelining may introduce additional latency, we further present analysis and algorithms to ensure the added latency will not compromise the overall throughput.

Our framework, AutoBridge, can be integrated into the existing CAD flow for Xilinx FPGAs. In our experiments with a total of 43 design configurations, we improve the average frequency from 147 MHz to 297 MHz (a 102% improvement) with no loss of throughput and a negligible change in resource utilization. Notably, in 16 experiments, we make the originally unroutable designs achieve 274 MHz on average. AutoBridge was recognized with the Best Paper Award in FPGA 2022.

## 1.2.3 HLS-Based Partitioning and Stitching Methodology for Parallel Physical Design

The aforementioned idea of combining HLS compilation with global floorplanning could be further extended to support parallel placement and routing. Conventionally, a major challenge in separately implementing different design parts is achieving a good timing quality on boundary nets that span different partitions. This problem could be addressed by utilizing the pipeline flexibility of HLS to fix the critical paths on the partition boundaries while maintaining the overall functionality and the throughput. In this way, the design can be partitioned at latency-insensitive boundaries into decoupled sub-designs, which could be separately placed and routed in parallel with minimal synchronization. The partial bitstream of all sub-designs will be later stitched together, and the tool will add additional pipeline registers to boundary nets for timing closure. In the thesis, we outline a number of technical challenges of such a split compilation approach. To address the challenges, we break the conventional boundaries between different stages in a typical CAD flow, and we reorganize the steps to achieve a fast end-to-end compilation.

Our research produces RapidStream, a parallelized and physical-integrated compilation framework that takes in a latency-insensitive program in C/C++ and generates a fully placed and routed implementation. We present two approaches. The first approach (RapidStream 1.0) resolves inter-partition routing conflicts at the end when separate partitions are stitched together. When tested on the Xilinx U250 FPGA with a set of realistic HLS designs, RapidStream achieves a 5-7× reduction in compile time and up to  $1.3\times$  increase in frequency when compared to a commercial-off-the-shelf toolchain. In addition, we provide preliminary results using a customized open-source router to reduce the compile time up to an order of magnitude in cases with lower performance requirements. The second approach (RapidStream 2.0) prevents routing conflicts using virtual pins. Testing on Xilinx U280 FPGA, we observed  $5-7\times$  compile time reduction and  $1.3\times$  frequency increase. RapidStream was recognized with the Best Paper Award in FPGA 2022.

## CHAPTER 2

## Background

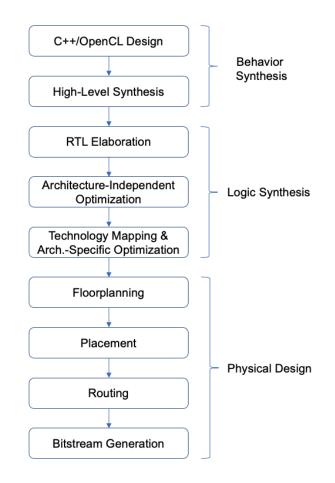

As the FPGA architecture evolves and its complexity increases, CAD software has advanced significantly as well. Nowadays, FPGA vendors provide a comprehensive set of design tools that allow automatic synthesis and compilation from design specifications in hardware specification languages all the way down to a bitstream to program FPGA chips. Fig 2.1 shows a typical FPGA design flow.

Figure 2.1: A typical FPGA design flow starting from behavior-level specifications.

#### 2.1 High-Level Synthesis

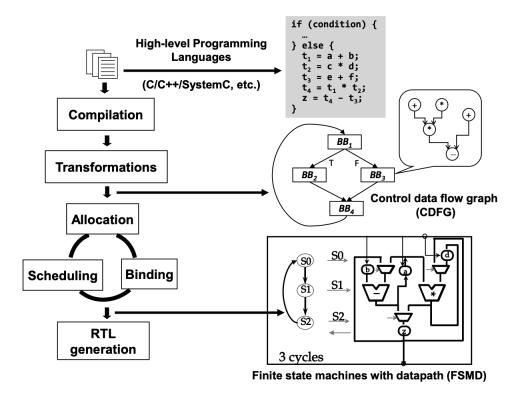

The rapid increase of complexity in FPGA design has pushed the industry and academia to raise the design abstractions with better productivity than register transfer level (RTL). High-level synthesis (HLS) plays a crucial role by enabling the automatic compilation of high-level, untimed, or partially timed specifications (e.g., C/C++ or OpenCL) to low-level cycle-accurate RTL specifications for efficient implementation in field programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs). This synthesis can be optimized considering the performance, power, and cost requirements of a particular system [CLN11]. The typical flow of modern FPGA HLS tools usually consists of three core steps: (1) scheduling, (2) binding, and (3) RTL generation, as shown in Figure 2.2.

Figure 2.2: A typical FPGA HLS flow. [CLN11]

• The *scheduling* phase inserts clock boundaries into the original untimed specification. It takes in the control data flow graph (CDFG) generated by a compiler front-end from the high-level description, for example, C/C++, and then maps the operations in the CDFG to the states and the control flow to state transitions specified by a finite-state machine (FSM). In each clock cycle, the controller will be in a state in the corresponding FSM.

- The *binding* process maps high-level operations and variables to RTL-level resources, such as functional units and registers. It maps variables to registers and links wires from registers to functional units as operands of operations. The result of a functional unit is then wired to another functional unit or a register to store the computed value.

- The *RTL generation* phase creates concrete RTL based on the results of the scheduling and the binding step. The key in this step is to properly create the control logic to orchestrate the datapath, controlling each stage to execute at its scheduled cycle.

One general limitation of today's HLS is that the HLS scheduler relies on a high-level estimation of the operation delay. This estimation is usually based on pre-characterized statistics, which include the delay of common components for computing, storage, and interconnects (e.g., adders, multipliers, registers, BRAMs, multiplexers, etc). However, such a delay model is inherently inaccurate. HLS tools lack consideration of the additional net delay in broadcast structures. The predicted delay by HLS tools for a certain operator is fixed regardless of the actual environment. Thus, the actual value for operators near broadcasts is usually larger than the predicted value. The situation is worse for global signals because HLS has no layout information on how the designs will be floorplanned and placed, thus it can hardly determine which signals will span a long distance.

### 2.2 Logic Synthesis

Logic synthesis is the process of transforming an RTL-specified design into a gate-level representation [Rud89, Sas93, DGK94]. The development and maturity of logic synthesis came before that of HLS, and RTL-based development used to be the dominant way and is still irreplaceable in many situations today. Logic synthesis is a highly automated procedure bridging the gap between high-level synthesis and the physical design process. Given an RTL digital design, logic synthesis transforms it into a gate-level or transistor-level network. This process explores different potential mappings of a logic function optimally under certain desired design constraints. After logic synthesis, the physical positions of primitive elements and the shapes and positions of the interconnections of the gate layouts are then further determined at the time of physical design.

Given an RTL design, a set of design constraints, and the target FPGA device, the overall FPGA synthesis process goes through the following steps:

- RTL elaboration. This step identifies and/or infers datapath operations (e.g. additions, multiplications, floating point arithmetic operations, register files, memory blocks, etc) and the corresponding control logic. Then they are elaborated into a set of finite-state machines or generic Boolean networks. Since most of the datapath elements have dedicated architectural support in modern FPGAs, it is important to recognize those elements such as adders with dedicated fast-carry chains and embedded DSP.

- Architecture-independent optimization. This step includes both datapath optimization (e.g., constant propagation, strength reduction, operation sharing, expression optimization, etc.) and control optimization. The control logic optimization includes sequential optimization such as finite-state machine encoding/minimization and retiming, and combinational logic optimization such as constant propagation, redundancy removal, logic network restructuring, etc.

- Technology mapping and architecture-specific optimization. This step maps the previously generated control logic and datapath to physical units of the target FPGA device. Specifically, this step maps the optimized datapath to on-chip dedicated circuit structures, such as DSPs, adders with dedicated carry-chains, embedded block RAMs, or the basic LUTs. It maps the optimized control logic to LUTs and registers.

### 2.3 Placement

The task of placement is to assign exact locations for each functional unit in the netlist to a physical component within the FPGA layout [LJG20, SM91, CCS05]. To a great extent, placement determines the overall quality of the final FPGA implementation. An inferior placement solution can hinder the downstream routing step by producing excessive wire length, which not only hampers the design performance and may even cause routing failure. Modern placement tools optimize toward various objectives, typically including wire length, routability, timing, and power. Minimizing the total wire length is often a major optimization goal because it is a reasonable approximation of routability, timing, and power. In addition to minimizing the wire length, another important factor to consider is the local routing feasibility. The placement tool must predict and distribute routing demand to avoid excessive local routing congestion. To meet a given frequency target, the placement tool has to ensure the total signal delay of the critical path is no greater than the according delay requirement.

Given the complexity of modern large-scale designs and the NP-hard nature of various algorithms involved, the FPGA placement problem is usually decomposed into several easier sub-problems, including global placement, packing, legalization, and detailed placement. Global placement targets producing a coarse-grained placement solution while globally optimizing the aforementioned placement objectives. Packing aims at grouping LUTs and FFs into architectural-legal and placement-friendly CLBs. Legalization produces a feasible placement solution by locally perturbing the result of global placement and packing. Detailed placement further conducts local refinement while maintaining the problem's feasibility.

### 2.4 Routing

Given a placed netlist where the physical location of each element in the netlist has been determined, the routing problem is to assign each net to the physical wire segments and switches such that all nets are connected while an objective function is optimized. Typical objectives for routing include total wirelength and segments [ZML21, CZ05, AR95].

Since modern FPGAs have limited and discrete interconnects and switch boxes, the routing step is a complex combinatorial optimization problem. Modern routing algorithms often abstract an FPGA as a weighted graph whose topology can represent the routing architecture of the target FPGA fabric. Each edge is associated with a weight that corresponds to the congestion level. During the routing process, the router will dynamically update the edge weights based on the available resource and applies graph-search techniques to look for desired connections.

Most FPGA routing algorithms will separate the routing task into two stages: the global routing stage and the detailed routing stage. First, global routing splits the available routing area into coarse-grained routing regions or channels to reduce the problem size. Then the router determines the coarse routing topology of each net regarding which routing regions the net is assigned to. The global routing step typically has the objectives of minimizing and balancing the overall estimated congestion and satisfying the timing constraints of critical nets. Next, the detailed routing stage produces the exact routing geometry to map every net onto each individual routing channel or region.

Due to the NP-hard nature of the routing problem, such a hierarchical approach has the advantage of being more computationally scalable. Otherwise, it will be extremely complex to determine the exact routing details directly in one step, considering that there are millions of nets and the design sizes have been increasing explosively in the last decade. However, the downside of such a two-step approach is the potential disconnection between the two stages. Since the global router relies on an estimated model for the distribution of available routing resources, the model's accuracy is critical. However, the early stage estimation often lacks consideration of the details of routing obstacles, and the final timing quality may be degraded.

### 2.5 Related Works

There are two major goals in our proposal: improving the achievable frequency and reducing the compilation time. Correspondingly, we present the previous works related to the two topics.

#### 2.5.1 Physical-Aware HLS Timing Optimization

- Co-optimize HLS and logic synthesis. Zhao *et al.* [ZTD15] and Tan *et al.* [TDG15] show that HLS typically has an over-conservative prediction of the signal delay of logic operations (e.g., AND, OR, NOT, etc). As a result, they propose methods to improve HLS scheduling by considering the technology mapping process.