# UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Optimizing Irregular Data Accesses for Cluster and Multicore Architectures

**Permalink** https://escholarship.org/uc/item/3jn6c2f6

**Author** Su, Jimmy Zhigang

Publication Date 2010

Peer reviewed|Thesis/dissertation

#### Optimizing Irregular Data Accesses for Cluster and Multicore Architectures

by

Jimmy Zhigang Su

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Katherine A. Yelick, Chair Professor Rastislav Bodik Professor Ming Gu

Fall 2010

Optimizing Irregular Data Accesses for Cluster and Multicore Architectures

Copyright 2010

by

Jimmy Zhigang Su

#### ABSTRACT

#### Optimizing Irregular Data Accesses for Cluster and Multicore Architectures

by

Jimmy Zhigang Su

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Katherine A. Yelick, Chair

Applications with irregular accesses to shared state are one of the most challenging computational patterns in parallel computing. Accesses can involve both read or write operations, with writes having the additional complexity of requiring some form of synchronization. Irregular accesses perform poorly in local cached-based memory systems and across networks in global distributed memory settings, because they have poor spatial and temporal locality. Irregular accesses arises in transaction processing, in various system level programs, in computing histograms, performing sparse matrix operations, updating meshes in particle-mesh methods, and building adaptive unstructured meshes. Writing codes with asynchronous parallel updates on clusters and multicore processors presents different sets of challenges. On clusters, the goal is to minimize the number of messages and the volume of messages between nodes. While on multicore machines, the goal is to minimize off-chip accesses since there is significant performance difference between on chip and off chip memory access.

In this dissertation, we explore various analyses, optimizations, and tools for shared accesses on both multicore and distributed memory cluster architectures. On cluster architectures, we consider both irregular reads and writes, demonstrate how Partitioned Global Address Space languages support programming irregular problems, and develop optimizations to minimize communication traffic, both in volume and number of distinct events. On multicore processors, we consider the lower level code generation and tuning problem, independent of any particular source language. We explore performance tradeoffs between various shared update implementations, such as locking, replication of state to avoid collisions, and hybrid versions. We develop an adaptive implementation that adjusts the shared update strategy based on densities that yields significant speedups. In addition, we develop a performance debugging tool to find scalability problems in large scientific applications early in the development cycle. Throughout the thesis we perform experiments demonstrating the value of our optimizations and tools in both architectural settings, use a set of benchmarks and applications that include histogram making, sparse matrix computations, and two scientific simulations involving particle-mesh methods. Our results show substantial speeds of up to 4.8X for multicore platforms and 120X for clusters. The results are a comprehensive set of techniques for improving the performance of irregular applications using advanced languages, compilers, analyses, optimizations and tools.

Professor Katherine A. Yelick Dissertation Committee Chair

#### TABLE OF CONTENTS

| 1. Introduction                                 | 1  |

|-------------------------------------------------|----|

| 2. Background                                   | 6  |

| 3. Irregular Data Access Applications           | 16 |

| 4. Optimizing Irregular Reads                   | 22 |

| 5. Optimizing Irregular Writes                  | 37 |

| 6. Multicore Optimizations for Irregular Writes | 51 |

| 7. Performance Debugging                        | 75 |

| 8. Related Work                                 |    |

| 9. Conclusion                                   | 93 |

| Bibliography                                    | 95 |

#### LIST OF FIGURES

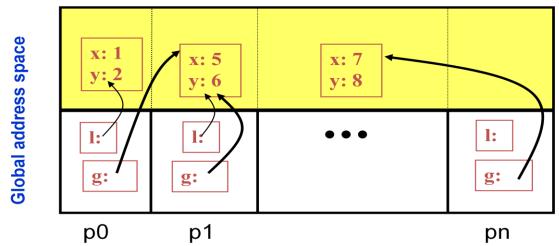

| Figure 2.1. Titanium is a Partitioned Global Address Space language7               |

|------------------------------------------------------------------------------------|

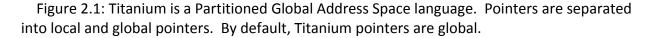

| Figure 2.2. Shared memory accesses without intervening synchronization events      |

| can be reordered under the Titanium memory consistency model10                     |

| Figure 2.3. Shared memory accesses are not allowed to reorder across barriers      |

| under the Titanium memory consistency model10                                      |

| Figure 2.4. Barriers in Titanium must be textually aligned11                       |

| Figure 2.5. Use of synchronized region for simultaneous counter update12           |

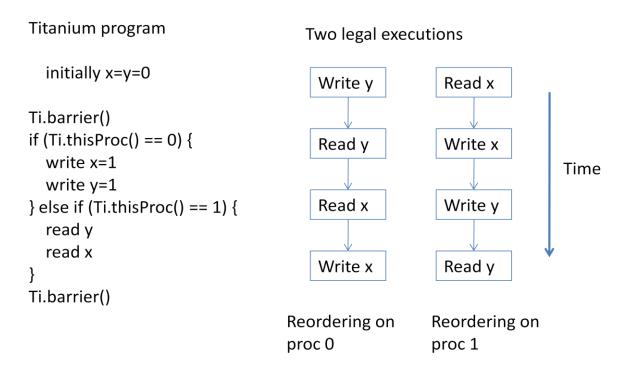

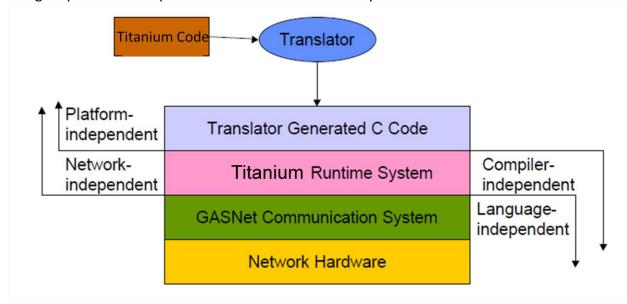

| Figure 2.6. Titanium compiler infrastructure13                                     |

| Figure 3.1. Web page language encoding distribution17                              |

| Figure 3.2. Web page out-degree distribution17                                     |

| Figure 3.3. Interactions between fine grid and coarse grid in AMR18                |

| Figure 3.4. The four phases of the immersed boundary method19                      |

| Figure 3.5. 2D Heart spread force20                                                |

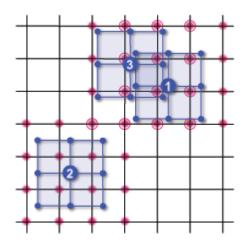

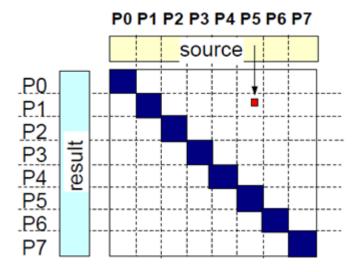

| Figure 3.6. Parallel layouts of matrix and vector21                                |

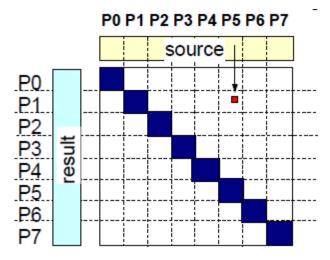

| Figure 4.1. Indirect sum benchmark on two processors23                             |

| Figure 4.2. Indirect sum benchmark on two processors with local buffers23          |

| Figure 4.3. Indirect sum benchmark on two processors using push strategy24         |

| Figure 4.4. Performance model for packing29                                        |

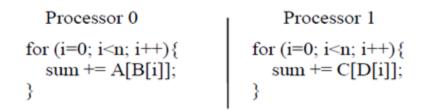

| Figure 4.5. Comparing the latency bandwidth models to actual on LAPI, GM, and      |

| Elan29                                                                             |

| Figure 4.6. SPMV matrix and vectors layouts31                                      |

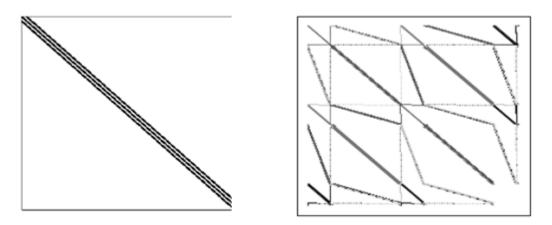

| Figure 4.7. Structure of nemeth21 (left) and garon2 (right)31                      |

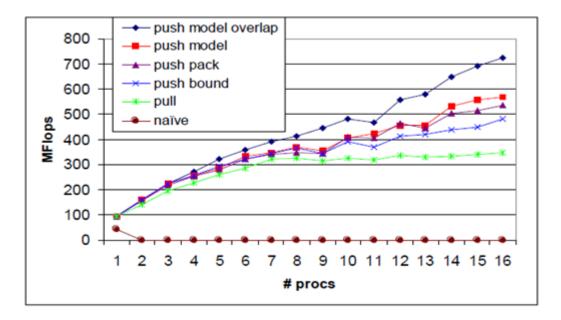

| Figure 4.8. Performance on garon2 matrix                                           |

| Figure 4.9. Performance comparison between Titanium and Aztec on Linux cluster     |

|                                                                                    |

| Figure 4.10. Performance comparison between Titanium and Aztec on Compaq           |

| Alphaserver                                                                        |

| Figure 4.11. Performance comparison between Titanium and Aztec on IBM SP36         |

| Figure 5.1. Spread force operation using a single lock for the entire fluid grid38 |

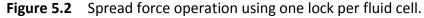

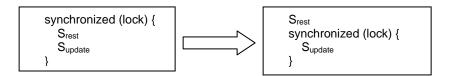

| Figure 5.2. Spread force operation using one lock per fluid cell                   |

| Figure 5.3. Manually optimized spread force code using update by owner to avoid    |

| locking40                                                                          |

| Figure 5.4. Decision procedure for deciding between including the gap in the       |

| current bounding box or start a new bounding box at the end of the gap45           |

| Figure 5.5. Speedup comparison for the spread force benchmark48                    |

| Figure 5.6. Speedup comparison for the histogram benchmark49                       |

| Figure 5.7. Speedup comparison for the particle gravitation benchmark              |

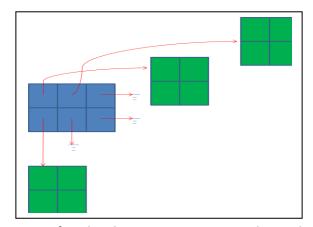

| Figure 6.1. Dynamic allocation of replica boxes57                                   |

|-------------------------------------------------------------------------------------|

| Figure 6.2. Particle partitioning in 2D with sorting57                              |

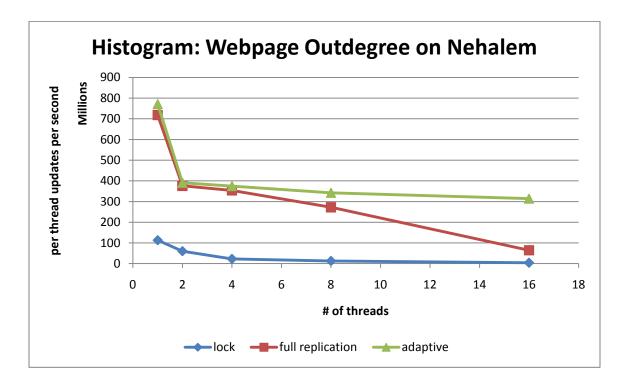

| Figure 6.3. Histogram per thread performance on Nehalem for the Web page out-       |

| degree distribution59                                                               |

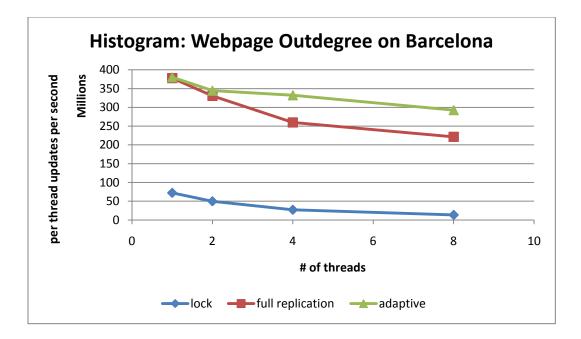

| Figure 6.4. Histogram per thread performance on Barcelona for the Web page out-     |

| degree distribution60                                                               |

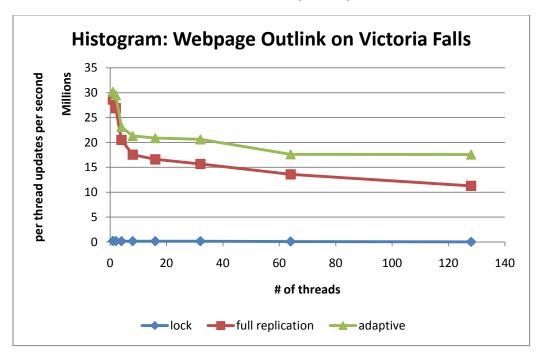

| Figure 6.5. Histogram per thread performance on Victoria Falls for the Web page     |

| out-degree distribution60                                                           |

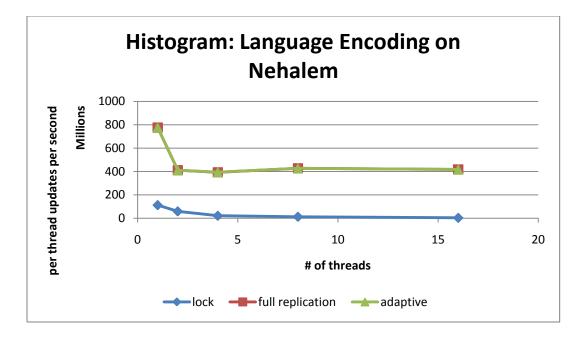

| Figure 6.6. Histogram per thread performance on Nehalem for the language            |

| encoding distribution62                                                             |

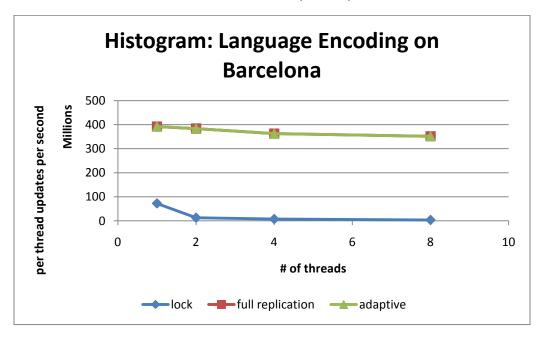

| Figure 6.7. Histogram per thread performance on Barcelona for the language          |

| encoding distribution62                                                             |

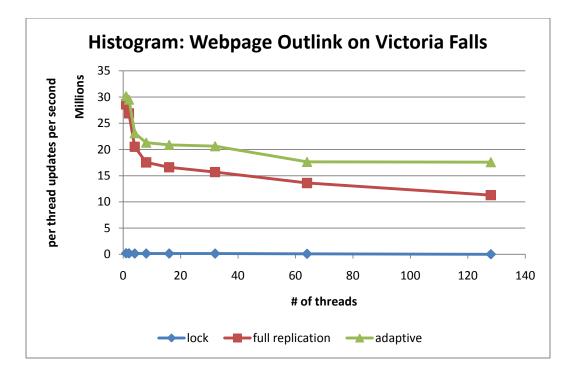

| Figure 6.8. Histogram per thread performance on Victoria Falls for the language     |

| encoding distribution63                                                             |

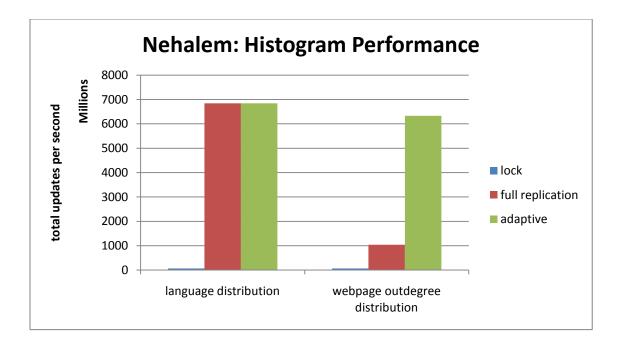

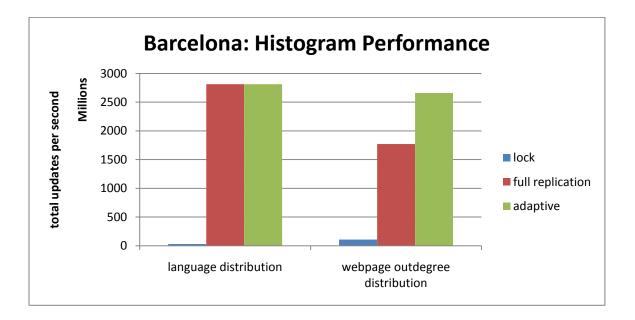

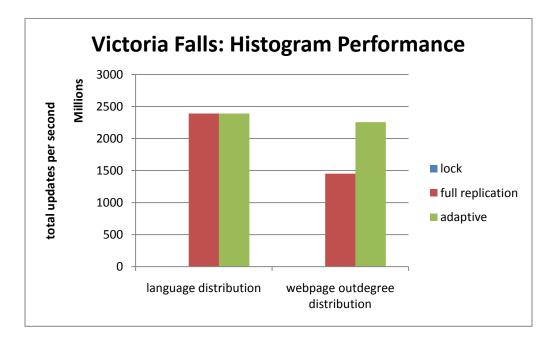

| Figure 6.9. Histogram performance summary on Nehalem for 16 threads64               |

| Figure 6.10. Histogram performance summary on Barcelona for 8 threads64             |

| Figure 6.11. Histogram performance summary on Victoria Falls for 128 threads65      |

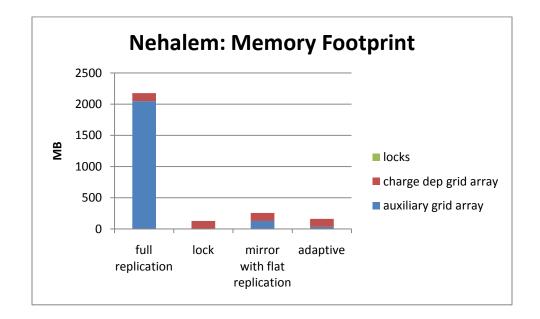

| Figure 6.12. Memory footprint of different heart spread force implementations on    |

| Nehalem using 16 threads66                                                          |

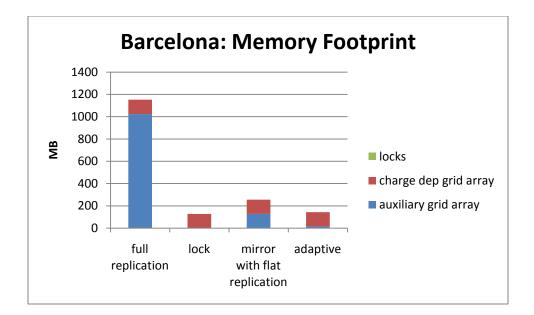

| Figure 6.13. Memory footprint of different heart spread force implementations on    |

| Barcelona using 8 threads67                                                         |

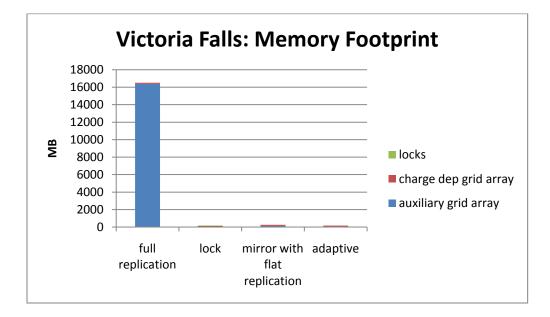

| Figure 6.14. Memory footprint of different heart spread force implementations on    |

| Victoria Falls using 128 threads67                                                  |

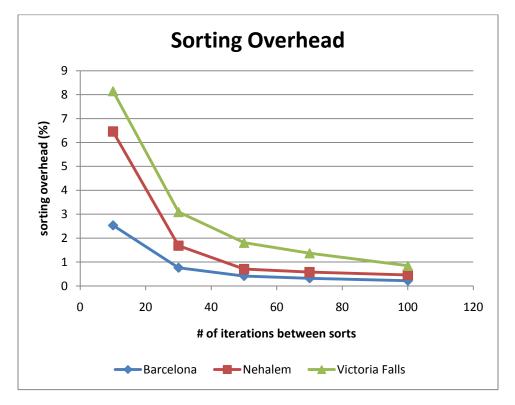

| Figure 6.15. Sorting overhead in the adaptive implementation for heart spread       |

| force computation69                                                                 |

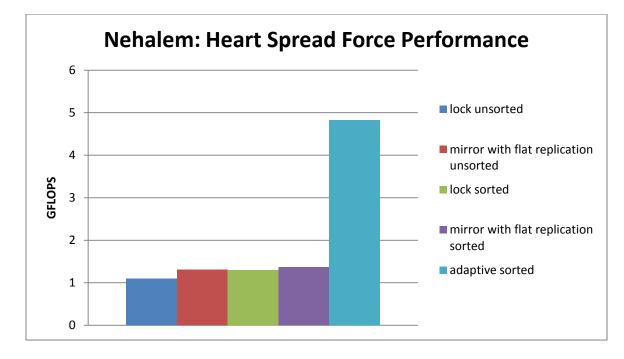

| Figure 6.16. Performance summary of different heart spread force implementations    |

| on Nehalem using 16 threads70                                                       |

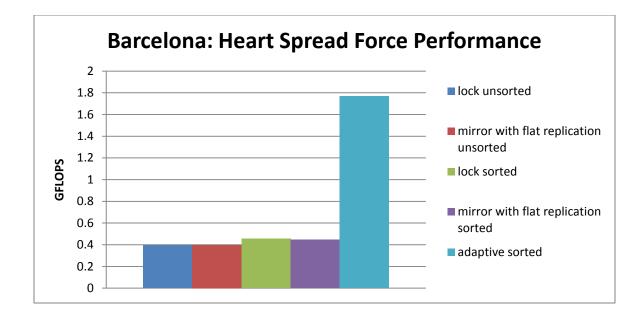

| Figure 6.17. Performance summary of different heart spread force implementations    |

| on Barcelona using 8 threads71                                                      |

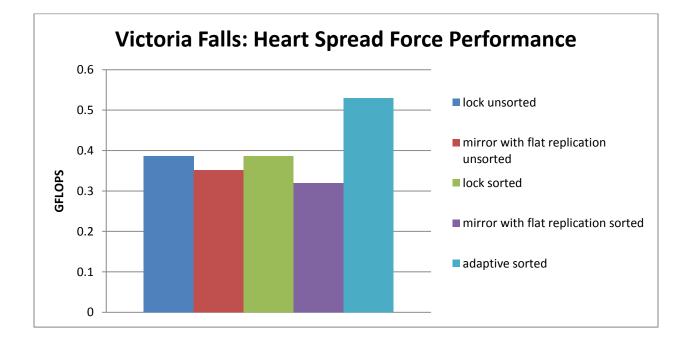

| Figure 6.18. Performance summary of different heart spread force implementations    |

| on Victoria Falls using 128 threads71                                               |

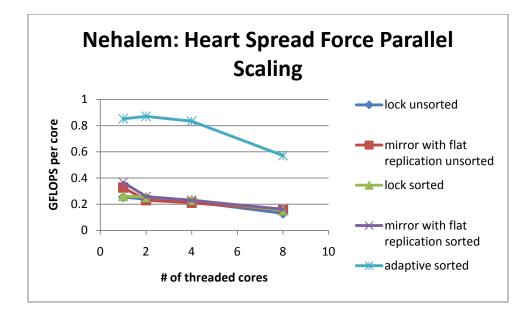

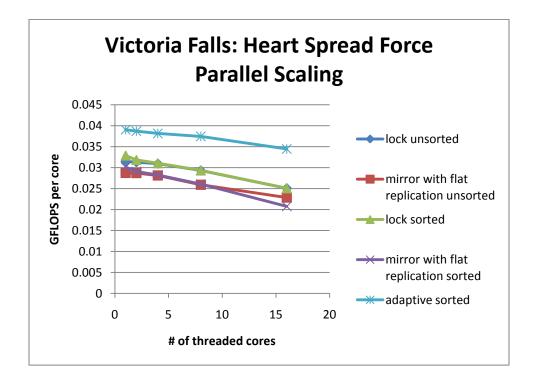

| Figure 6.19. Heart spread force per threaded core performance on Nehalem for        |

| different implementations73                                                         |

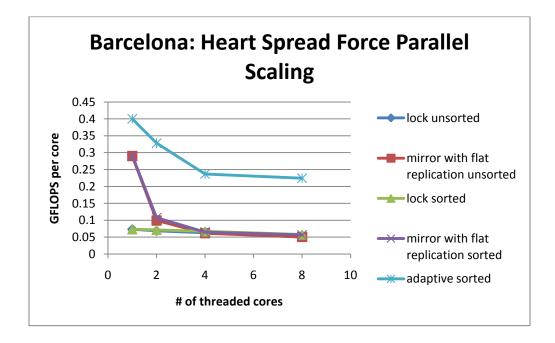

| Figure 6.20. Heart spread force per threaded core performance on Barcelona for      |

| different implementations                                                           |

| Figure 6.21. Heart spread force per threaded core performance on Victoria Falls for |

| different implementations74                                                         |

| Figure 7.1. Sum reduction example with performance bug in it76                      |

| Figure 7.2. Sum reduction example without the performance bug77                     |

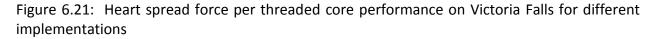

| Figure 7.3. The number of communication calls at the array dereference78            |

| Figure 7.4. Fiber distribution code containing a performance bug due to lack of |    |

|---------------------------------------------------------------------------------|----|

| immutable keyword                                                               | 81 |

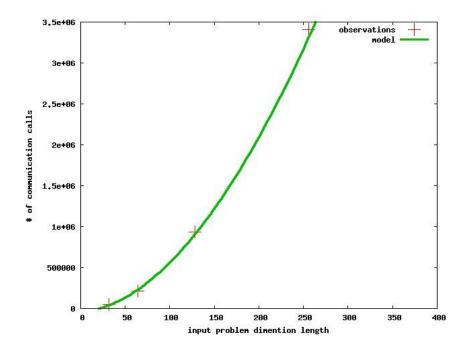

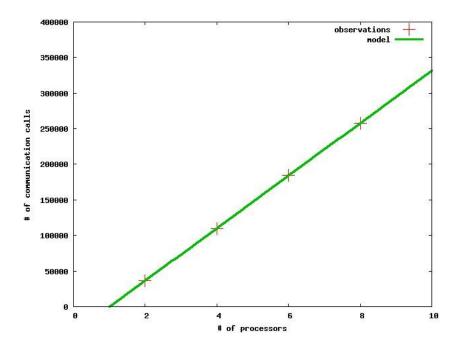

| Figure 7.5. Graph of the power law function generated by ti-trend-prof for the  |    |

| buggy line along with actual observations of communication counts while         |    |

| varying the number of processors                                                | 83 |

| Figure 7.6. Graph of the power law function generated by ti-trend-prof for the  |    |

| buggy line along with actual observations of communication counts while         |    |

| varying the input size                                                          | 84 |

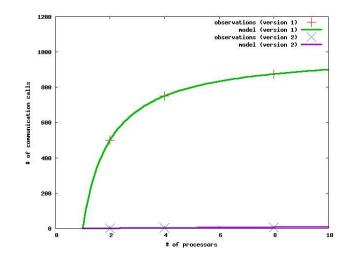

| Figure 7.7. Meta-data set up code containing a performance bug due to excessive |    |

| amount of broadcast calls                                                       | 85 |

| Figure 7.8. Graph of the power law function generated by ti-trend-prof for the  |    |

| excessive broadcast along with actual observations of communication counts      | ;  |

| -                                                                               | 86 |

|                                                                                 |    |

#### LIST OF TABLES

| Table 4.1. Machine summary                                                     | .27 |

|--------------------------------------------------------------------------------|-----|

| Table 4.2. Matrix characteristics                                              | .34 |

| Table 6.1. Architectural details of parallel platforms                         | .52 |

| Table 7.1. Trends output from ti-trend-prof for the heart simulation given the |     |

| GASNet traces for the 128^3 size problem on 4, 8, 16 and 32 processors         | .82 |

## **Chapter 1**

## Introduction

Parallel computing has long been the mainstay of high end scientific computing and has recently moved into the mainstream with multicore processors marking the end of single processor performance improvements. Single chips now have up to twelve conventional microprocessor cores, while graphics chips have hundreds of lightweight cores and the largest petascale machines available today have hundreds of thousands of cores. Despite years of effort by the research community, there is no wide-spread acceptance of a single parallel programming model, and the message passing model most popular for high end scientific computing appears unsuitable for the growing number of cores on a single chip. One of the challenges to a single common programming model is the wide spectrum of parallel programming patterns and the trade-off between generality needed to support all of them and the simplicity that is possible for a narrower domain. Data parallel languages allow programmers to write expressions that operate on aggregate data structures, such as arrays, but preserve much of the intuition behind a serial semantics. But these languages place a heavy burden on the compiler and runtime system, and the elegance of the pure data parallel language quickly breaks down when language designers try to support the breadth of parallel constructs. Message passing languages such as MPI [50] limit the interaction between parallel threads to explicit communication points, making it easier to see and therefore control the interactions. But the explicit, two-sided nature of the communication becomes awkward for some computational problems in which communication events on one thread are unexpected on another. Shared memory models (often with dynamically created threads or OpenMP [53]) offer the generality of being able to build shared data structures and access them conveniently from multiple threads, but they to not scale to large numbers of processors. Partitioned Global Address Space (PGAS) languages provide some of the best features of each of these paradigms in order to make them expressive, convenient, efficient and scalable. We will explore a particularly difficult class of applications—those involving irregular accesses—and describe analyses, optimizations and tools to support these applications.

Applications with irregular accesses to shared state are one of the most challenging computational patterns in parallel computing. The accesses may be irregular in space, accesses locations that are not contiguous, and do not follow a statically predictable pattern. They can also be irregular in time, so they occur asynchronously at times that are not predictable in advanced and are therefore difficult to coordinate if multiple threads need to be involved. Accesses can involved both read or write operations, with writes having the additional complexity of requiring some form of synchronization in case of collisions. Irregular accesses perform poorly in local cached-based memory systems and across networks in global distributed memory settings.

Irregular accesses arises in transaction processing, in various system level programs, and in algorithms that arise in HPC applications, such as computing histograms, performing sparse matrix operations, updating meshes in particle-mesh methods, and building adaptive unstructured meshes. Writing codes with asynchronous parallel updates on clusters and multicore processors presents different sets of challenges. On clusters, the goal is to minimize the number of messages and the volume of messages between nodes. Similarly, we try to minimize the memory traffic between sockets on multicore machines, since there is significant performance difference between on chip and off chip memory access.

In this dissertation, we explore various analyses, optimizations, and tools for shared updates on both multicore and distributed memory cluster architectures. On cluster architectures, we consider both irregular reads and writes, demonstrate how PGAS languages support programming some problems, and develop optimizations to minimized communication traffic, both in volume and number of distinct events. Our PGAS work is done in a Java-based language called Titanium [37, 74]. We explore optimizations for the irregular data access when it appears as a read, using sparse matrix vector multiply as the benchmark, and as a write, using histogram construction and two particle-mesh methods as benchmarks. On multicore processors, we consider the lower level code generation and tuning problem, independent of any particular source language. We explore performance tradeoffs between various shared update implementations, such as locking, replication of state to avoid collisions, and hybrid versions. The effectiveness of the optimizations is highly dependent on the frequency of updates, the distribution of the accesses across system memory, the likelihood of collisions during updates, and the relative size of the data structures involved. We develop an adaptive implementation that adjusts the shared update strategy based on densities that yields significant speedups. In addition to the difficulty of ensuring correctness on these problems with irregular accesses, there is a problem of selecting the right implementation based on the machine and usage characteristics. The space of reasonable implementation approaches is enormous, when considers all the parameter settings within each algorithm. At various points within the thesis we use performance models and automatic search-based performance tuning to select optimizations. In addition, we develop a performance debugging tool to find scalability problems in large scientific applications earlier in the development cycle.

#### 1.1 Optimizations for Irregular Read Data Access

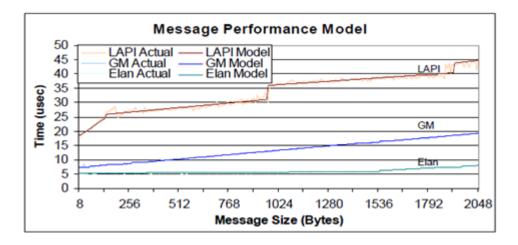

Irregular data access can appear both as a read or write. We develop new compiler and runtime extensions for the Titanium implementation to support programs with indirect read

array accesses, such as A[B[i]], where the A array may live in a remote processor's memory. The effectiveness of the optimizations is evaluated on three different cluster architectures. These computations arise in sparse iterative solvers, particle-mesh methods, and elsewhere. We add compiler support for an *inspector executor* execution model, which optimizes communication performing runtime optimization based on the dynamic pattern of indices in the indirection array, which is B in the previous example. We explore several possible transformations that can be done on the communication to minimize the number of messages and overlap communication with both computation and other communication. We use the sparse matrix vector multiply benchmark to evaluate the effectiveness of our optimizations.

#### 1.2 Asynchronous Updates Challenges on Cluster

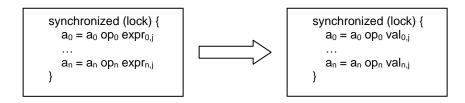

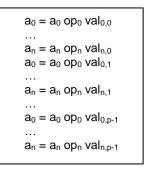

In spite of recent trends towards increased parallelism in all type of computing devices, parallel programming remains a difficult and time-consuming process. The barrier to entry for parallel programming, especially on high end machines, still deters many scientists and engineers from writing parallel programs. Parts of this dissertation were done in the context of Titanium. Titanium is a Partitioned Global Address Space (PGAS) language. Titanium offers a more convenient programming style, by permitting a thread to read and write to shared memory directly. For asynchronous updates, it can be implemented using synchronized region with fine grained accesses inside the region. Without adequate optimization by the compiler, programs written in this fashion would have very poor performance. The straightforward compilation results in four network round trips per update when the memory location is remote: lock acquisition, lock release, remote memory read and write. In practice, Titanium programmers often resort to manual optimization by rewriting their program in a coarse-grained style to aggregate the small messages together. The experience of the Titanium group and others is that performance is paramount in this domain as our experience and others shows that programmers will spend a significant amount of time and code to improve performance, and are unwilling to use languages or tools that results in significant performance penalties. In the first part of the dissertation, we developed analysis and optimizations for programs with asynchronous parallel updates in Titanium, so programmers can benefit from the high level programming language without the performance penalty.

#### **1.3 Asynchronous Update Challenges on Multicore**

The vast array of parallel computing devices offers different challenges for optimization. In contrast to cluster, shared memory is accessible by all threads on modern multicore

architectures. This allows the programmer to write parallel programs without using message passing. This is a significant gain in programmability and productivity for the programmer. But the use of shared memory does not alleviate the need for performance tuning entirely. Access from different cores to the shared memory yields different performance due to NUMA issues. This is analogous to the performance difference between local memory access and remote memory access on cluster, although the magnitude of the performance gap is less on multicore processors. The performance model of combining per update cost and overhead cost is applicable to both multicore and cluster. Overhead cost includes time spent in reduction and pre-processing of data points. In this part of the dissertation, we explore various Particle In Cell (PIC) implementations that perform tradeoffs between per update cost and overhead cost.

#### **1.4 Performance Debugging**

High performance kernels are necessary building blocks for a large parallel application, but they alone do not make the application usable for the end user on large scale machines. There are parts of the program that are less scrutinized for performance that become obstacles for running experiments on large number of processors or large inputs. As the number of cores increases for future multicore architectures, this problem will also be prevalent in the multicore domain. These include I/O, initialization, and data distribution. During application development and testing on small number of processors and small input sizes, these problems are typically hidden behind long running kernels. When the application is in production, these problems can no longer be ignored as they are not scalable with the number of processors or input size. This causes longer waiting time for the experiments to finish or not finish at all. In this part of the dissertation, we introduce a performance debugging tool for catching these problems earlier in the development cycle in the context of Titanium.

#### 1.5 Thesis Contributions

In this thesis, our primary contributions can be summarized into the following:

- 1. We develop compiler analysis and optimization for asynchronous parallel updates in the Titanium compiler.

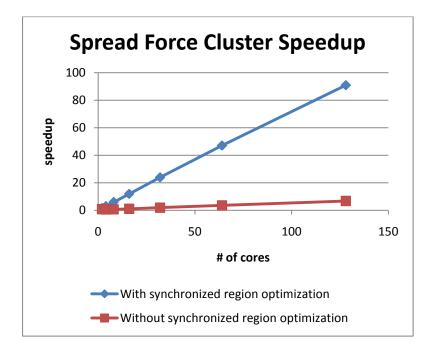

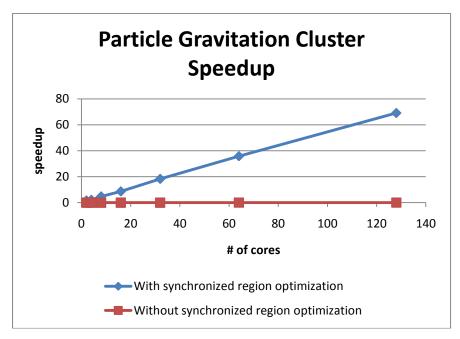

- 2. We evaluate the synchronization region optimization on the Heart code spread force, histogram, and particle gravitation benchmarks. The generated code using the

optimization achieves speedups of 90x, 120x, and 70x over the sequential code on 128 processors, while the generated code without this optimization does not get speedups above 10x on the same number of processors.

- 3. We explore the optimization space for PIC code on modern multicore processors. Our results show that optimizations to maximize the number of local updates are necessary to obtain scalable performance. Simple parallel implementations using locking or full replication yield suboptimal performance.

- 4. We develop an adaptive PIC implementation that maximizes the number of local updates. It achieves a speedup up to 4.8x over locking implementation on modern multicore processors.

- 5. We developed *inspector-executor* compiler and runtime optimizations for the Titanium implementation to support programs with indirect read array accesses.

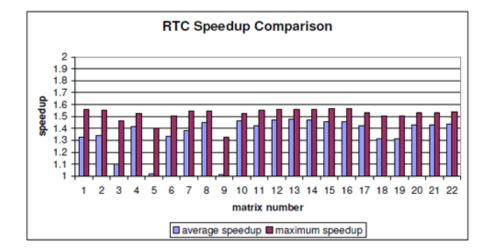

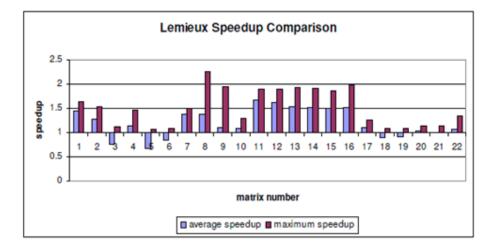

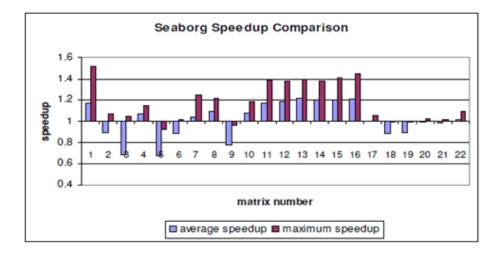

- 6. We analyze the benefits of the automated *inspector-executor* transformation using sparse matrix vector multiplication on a set of matrices from real applications. The speedup relative to MPI on a suite of over 20 matrices averages 21% on three different machines, with the maximum speedup of more than 2x.

- 7. We developed a performance debugging tool named ti-trend-prof to find scalability problems in parallel code using multiple program runtime traces. ti-trend-prof is able to predict scalability problems at high processor counts or large input sizes using traces from small number of processors or small input sizes.

- 8. For two of the largest Titanium applications, Heart code [54] and AMR [11], ti-trend-prof found multiple scalability bugs within hours instead of days for manual debugging.

# **Chapter 2**

## Background

In this chapter, we present background information on Titanium and GASNet [15]. More details on the Titanium language and GASNet can be found in the Titanium language specification [37] and GASNet specification.

#### 2.1 Titanium

Titanium is a language designed for high-performance parallel scientific computing. Titanium uses Java as its base, thereby leveraging the modern language features of Java such as object oriented programming, strong type checking, memory safety, garbage collection, and a rich library. Titanium has an optimizing compiler with both memory hierarchy optimizations [55] and communication optimizations [62, 63]. The main additions to Java in Titanium are immutable classes, multi-dimensional arrays, an explicitly parallel Single Program Multiple Data (SPMD) model of computation with a global address space, and zone-based memory management [1, 29]. High performance is always the first criterion in any parallel programming language targeting high-performance parallel scientific computing. Titanium's emphasis on programmer productivity as an equally important goal makes it unique from other parallel programming languages in this space. A recent study suggests that Titanium implementations for three of the NAS parallel benchmarks can match the performance of the standard MPI/Fortran implementations, while requiring substantially fewer lines of code [25].

Titanium is a dialect of Java, but does not use the Java Virtual Machine model. Instead, the end target is assembly code. For portability, Titanium is first translated into C and then compiled into an executable. In addition to generating C code to run on each processor, the compiler generates calls to a runtime layer based on GASNet, a lightweight communication layer that exploits hardware support for direct remote reads and writes when possible. Titanium runs on a wide range of platforms including uniprocessors, shared memory machines (SMPs), distributed-memory clusters of uniprocessors or SMPs (CLUMPS), and a number of specific supercomputer architectures (Cray X1, Cray T3E, SGI Altix, IBM SP, Origin 2000, and NEC SX6).

Titanium is a Single Program, Multiple Data (SPMD) language, so all threads execute the same code image. Each thread has its own thread ID, which can be obtained through a call to Ti.thisProc. A call to Ti.barrier causes a thread to wait until all other threads reach the same barrier. Titanium is part of the Partitioned Global Address Space (PGAS) programming language family. The global address space provides a shared memory view of the combined memory of

the processors since that thread running on one processor can directly read or write the memory associated with another. This feature significantly increases programmer productivity, since the programmer can build large shared data structures and does not need to write explicit communication with matching send and receive calls as in message passing programs. The address space is logically partitioned to provide a scalable performance abstraction for the global address space in which some data is considered nearby each processor. The Titanium type system distinguishes between references to data that is nearby (local) vs data that can possibly be remote (global). Figure 2.1 demonstrates the difference between local pointers and global pointers. Local pointers can only point to a memory address that is on the local processor. Global pointers can point to either local memory or remote memory on a remote processor. By default, Titanium pointers are global. Each processor p0 to pn has a section of memory that is viewed as nearby. Data in that memory can further be divided into local and global. Execution of I.x on processor 0 does not require communication, since the object pointed to by I is in the nearby memory. In contrast, execution of g.x on processor 0 would require communication between processor 0 and processor 1, because the object pointed to by g lives on processor 1. A global pointer can point to both local and global objects. On processor 1, the global pointer g points to an object in nearby memory, so the execution of g.x. on processor 1 would not require any communication.

Through programmer type annotation and compiler inference [45], some Titanium pointers can be inferred as local at compile time. This can significantly improve serial performance and reduce memory footprint. Global pointers contain a field for node ID in addition to the pointer address.

Titanium extends sequential Java with the following key features:

Titanium arrays – Titanium provides a powerful multidimensional array abstraction defined on a global index space along with the same kinds of sub-array operations available in Fortran 90.

2. Domain calculus – The built-in multidimensional domain calculus provides syntactical support for sub-arrays. In Titanium, the location of an array element is represented by an integer vector called a *point*, and a *domain* is a set of points which can be either rectangular or not. Points (Point) and domains (RectDomain, Domain) are first-class types and literals.

3. Foreach loops – The iteration over any multidimensional Titanium array is expressed concisely in one loop, using the unordered looping construct *foreach*. Unlike for loops, the Titanium compiler has the freedom to execute the loop iterations in any order. The compiler currently does not exploit this as an optimization opportunity.

4. Distributed data structures – Global data structures are built in Titanium through its general pointer-based distribution mechanism. It is each process's responsibility to construct its local share of a global data structure and have the references available to others. After that each process can access the entire data structure in the same way as on a shared-memory machine by dereferencing pointers.

5. Non-blocking array copy – The bulk communication between two processes is realized through a copy method of Titanium arrays. The support for non-blocking array copy enables the overlap of computation and communication. Some of the optimizations presented in this dissertation automatically generate non-blocking array copy calls.

6. The *local* keyword and locality qualification – Titanium expresses the affinity between data and its owning process explicitly using the local type qualifier. The default type for a Titanium pointer is *global*, meaning that the pointer can point to data residing in the local memory or remote memory. Locality information is automatically propagated by the Titanium optimizer using a constraint-based inference. This performance feature helps especially when running computations on distributed-memory platforms. Global pointer contains information on node ID and the actual memory address on that node. Pointer dereferencing using global pointers in a loop often causes the native C compiler to give up on loop optimizations such as loop unrolling, even when the global pointer is pointing to data in local memory.

7. Immutable classes – All Java objects are accessed through references. This adds a constant overhead including extra level of indirection and object creation and destruction to programs with heavy use of small objects. To address this problem in Titanium, application-specific primitive types can be defined as immutable classes. Immutable classes are not extensions of any class including Object. All fields in an immutable class are final. Objects of an immutable class (lightweight objects) are unboxed, analogous to C structs. They are manipulated and passed by value.

#### 2.2 Memory Consistency Model

Optimizations presented in this dissertation require the ability to reorder remote writes in a program through aggregation and non-blocking communication. In a uniprocessor environment, such compiler transformations must adhere to a simple data dependency constraint: the orders of all pairs of conflicting accesses (accesses to the same memory location, with at least one a write) must be preserved. The execution model for parallel programs is considerably more complicated, since each thread executes its own portion of the program asynchronously, and there is no predetermined ordering among accesses issued by different threads to shared memory locations. A memory consistency model defines the memory semantics and restricts the possible execution orders of memory operations. Titanium has a relaxed memory consistency model. Between synchronization events, accesses from one thread may be observed to happen out of order by another thread, and such reordering is allowed under the Titanium memory consistency model. Here are some informal properties of the Titanium model.

· Locally sequentially consistent: All reads and writes issued by a given processor must appear to that processor to occur in exactly the order specified. Thus, dependencies within a processor stream must be observed.

• Globally consistent at synchronization events: At a global synchronization event, such as a barrier, all processors must agree on the values of all the variables. At a non-global synchronization event, such as entry into a critical section, the processor must see all previous updates made using that synchronization event.

The first property implies that a processor must be able to read its own writes. If a processor writes to array elements that have been prefetched from a remote location into a local buffer, subsequent reads by that processor must return the new value. The second property makes data prefetched prior to a synchronization point unusable after that synchronization point. The prefetched data may have been changed by other processors, and reads after the synchronization point must reflect those changes. This property prevents code motion past synchronization points.

Figure 2.2: Shared memory accesses without intervening synchronization events can be reordered under the Titanium memory consistency model.

Titanium program Two illegal executions initially x=y=0Write y Read x if (Ti.thisProc() == 0) { write x=1 Write x Read y } else if (Ti.thisProc() == 1) { Time read y Read x Write y } Ti.barrier() if (Ti.thisProc() == 0) { Write x Read y write y=1} else if (Ti.thisProc() == 1) { read x Reordering on Reordering on } proc 0 proc 1

Figure 2.3: Shared memory accesses are not allowed to reorder across barriers under the Titanium memory consistency model.

Figure 2.2 shows a Titanium program where reads and writes can be reordered between a pair of barriers. It is possible for Processor 1 to observe the reordering of writes on Processor 0. The (x,y) pair read by Processor 1 can read any combination of 0's and 1's, including (0,1) as shown by the two reordered executions in Figure 2.2. This is allowed under the Titanium memory consistency model, since there is no synchronization event between those shared memory accesses. In contrast, Figure 2.3 shows a Titanium program where the same reordering of memory accesses across the barrier is not allowed. In this case, the only allowed values read for the (x, y) pair on processor 1 is (1, 0).

#### 2.3 Textually Aligned Barriers

A *barrier* causes a thread to wait until all other threads reach a barrier. Titanium has the unique feature that requires all threads to reach the same textual sequence of barriers during the execution of the program. This property is called textually aligned barriers: a call to a barrier in Titanium causes the calling thread to wait until all other threads have executed the same textual instance of the barrier call. The code in the example below is not allowed because not all the threads will hit the same textual barrier. The Titanium compiler checks statically that all the barriers are lined up correctly.

if (Ti.thisProc() % 2 == 0) Ti.barrier(); // even ID threads else Ti.barrier(); // odd ID threads

Figure 2.4: Barriers in Titanium must be textually aligned. Only the even ID threads can hit the first barrier. The Titanium compiler emits a compilation error for this code.

In contrast, if we change the conditional to Ti.numProcs() % 2 == 0, then it would satisfy the textually aligned property, since all threads would hit the first barrier if the total number of threads is even, and hit the second barrier if the total number of threads is odd.

Textually aligned barrier enables the Titanium compiler to eliminate deadlock bugs due to misaligned barriers at compiler time. Gay and Aiken developed the single inference technique to detect such errors statically [2].

Textually aligned barrier also enables many optimizations in the Titanium compiler, since the set of barriers effectively divides the Titanium program into phases. Analysis such as data race detection can be applied to each phase independently due to the memory consistency model of Titanium. This enables n^2 running time analysis to be scalable in practice, since the number of statements in a phase is typically small. Data prefetch and delayed write optimizations can also be applied to each phase independently of each other, since prefetched reads can not initiate

before the beginning barrier of a phase, and delayed writes must be finished prior to the ending barrier of a phase.

#### 2.4 Single Valued Expressions

Titanium's textually aligned barriers require all threads to execute the same sequence of barriers during program execution. If a barrier appears inside of a branch of a conditional statement, the compiler needs to statically determine that all threads would take the same branch at runtime. This would require the conditional expression to evaluate to the same value on all threads. To aid such analysis at compile time, *single valued expressions* are introduced in Titanium. A single-valued expression evaluates to the same value for all threads. Examples of single valued expressions include constants and Ti.numProcs(), which returns the number of threads running the program. With programmer annotation and compiler inference, the Titanium compiler statically determines which expressions are single-valued. Single valued expressions are used to ensure that barriers line up: a conditional may only contain a barrier if it is guarded by a single-valued expression. The code in Figure 2.4 is erroneous since Ti.thisProc() % 2 == 0 is not single-valued.

### 2.5 Synchronized Region

Titanium inherits the synchronized region feature from Java. A block of code that is inside of a synchronized region only allows one thread to execute code in the region at a time. Figure 2.5 shows an example use of synchronized region to handle simultaneous updates to a counter.

```

public class Counter {

private int count = 0;

public void increment() {

synchronized (this) {

count++;

}

}

public int getCount() {

synchronized (this) {

return count;

}

}

Figure 2.5: Use of synchronized region for simultaneous counter update

```

In this example, the counter needs to be incremented simultaneously by different threads. Ordinarily, there would be a risk that two threads could simultaneously try and update the counter at the same time, or one thread is doing an update while another thread is doing a read at the same time. By wrapping the update code in a synchronized region, we avoid this risk since both the update and the read for the counter require the acquisition of the same lock. Every Java object created has an associated lock or monitor. Putting code inside a synchronized block makes the compiler append instructions to acquire the lock on the specified object before executing the code, and release it afterwards. In Figure 2.5, it is using the lock of the Counter object to guard the synchronized regions for both increment and getCount.

#### 2.6 Titanium Implementation

Figure 2.6 shows the overall structure of the Titanium compiler, which is divided into three components: the Titanium-to-C translator, the Titanium runtime system, and the GASNet communication system. During the first phase of compilation, the Titanium compiler translates Titanium programs into C code in a platform-independent manner, with calls to Titanium-related parallel features such as synchronization, memory access through global pointers, and array copies converted into runtime library calls. The translated C code is next compiled using the target system's C compiler and linked to the runtime system.

Figure 2.6: Titanium compiler infrastructure

The Titanium runtime delegates communication operations such as remote memory accesses to the GASNet communication layer, which provides a uniform interface for low level communication primitives on all networks. GASNet provides native implementations for several high performance networks including Infiniband, Myrinet, and IBM's LAPI. This threelayer design has several advantages. Because of the choice of C as our intermediate representation, our compiler will be available on most commonly used hardware platforms that have an ISO-compliant C compiler. In addition to the portability benefits, the layered design also has the goal that each component can be implemented and performance tuned individually. The backend C compiler is free to aggressively optimize the intermediate C output, and the Titanium compiler can utilize its Titanium-specific knowledge to perform communication optimizations. In practice, we have found significant impact on the backend C compiler's ability to do serial optimizations due to the way the Titanium compiler generates C code. For typical serial optimizations applied by the backend C compiler, we have found that the backend C compilers are very sensitive to the way the Titanium compiler generates C code. Substantial efforts we put into the Titanium compiler to allow the backend C compiler to apply serial optimizations. This process is done for each backend C compiler individually. For example, the gcc compiler is more likely to unroll a *for* loop with a constant increment than a *do while* loop with a constant increment. The icc compiler was able to unroll both types of loops. This remains a challenge to Titanium compiler developers on future releases, since the backend C compiler's ability to optimize the generated C code will change over time.

#### 2.7 GASNet

For most Titanium distributed memory backends, the Titanium runtime system delegates communication operations such as remote memory accesses and synchronization to the GASNet communication layer, which provides a uniform interface for low level communication primitives on all networks. GASNet is the communication target for several PGAS languages including Titanum, UPC [67], Co-Array Fortran [52], and Chapel [17]. Unlike MPI, GASNet is designed as a compiler target, rather than an end-user library. It provides Active Messages, one-sided point-to-point messaging, a set of collective operations, and many other features.

The GASNet implementation is designed for both portability and performance. A small set of core functions constitute the basis for portability, and GASNet provides a reference implementation of the full API in terms of this core. In addition, the implementation for a given network can be tuned by implementing any appropriate subset of the general functionality directly upon the hardware-specific primitives, bypassing the reference implementation. The hardware-specific primitives provide higher bandwidth and lower latency primitives.

#### 2.8 GASNet Trace

Titanium's GASNet backends include features that can be used to trace communication using the GASNet trace tool. When a Titanium program is compiled with GASNet trace enabled, a

communication log is kept for each run of the program. In this communication log, each communication event along with the source code line number is recorded. The communication event includes information such as the type of communication (put/get), message size, and the thread ID. GASNet trace is useful in gathering statistics regarding the number of communication calls and the volume of communication. This helps the performance debugging process, but it is not recommended to be used for production runs, since it adds significant overhead on the application performance.

# **Chapter 3**

# **Irregular Data Access Applications**

Irregular data access patterns appear in many scientific applications, including sparse matrix vector multiply, Particle In Cell (PIC) method, histogram, and Giga UPdates per Second (GUPS) [47]. The irregular data access typically contains a data array and an index array, appearing as A[B[i]], where A is the data array and B is the index array. The irregular data access can appear as a read or a write. This dissertation covers both the read and write cases. Irregular write is a harder problem due to the need for synchronization on memory locations that receive updates. This computational pattern is challenging due to the following:

- 1. The memory locations of the updates are not known until runtime.

- 2. Updates to the same memory location from different threads must be synchronized.

In this chapter, we present background information on the irregular data access applications that are used throughout this dissertation.

#### 3.1 Histogram

Histogram is a simple benchmark that exemplifies the irregular write data access pattern. In our histogram benchmark, an array of integers are taken as input, each element is mapped to a bucket and counted. The bucket to be incremented is determined based on the value of the integer. The number of dimensions of the target array and the set of elements in the target array receiving updates for a single data point are important characteristics for describing any irregular write algorithm. For the histogram benchmark, the target array is one dimensional, and the update affects a single element of the target array.

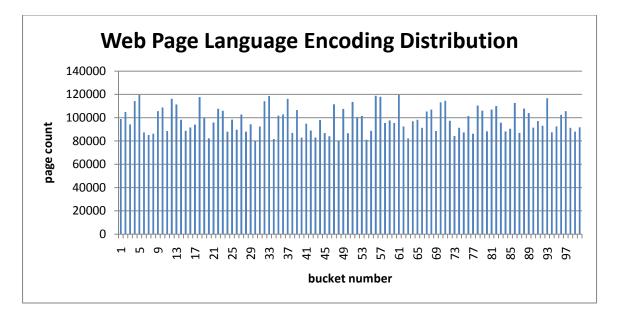

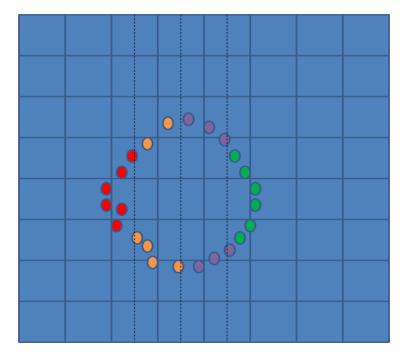

We use two different index distributions in our experiments: Web page out-degrees and language encodings. The two index distributions differ in the number of buckets and the clustering of the data points. In the language encodings distribution, there are around 100 language encodings widely in used in the World Wide Web. Each bucket represents one language encoding, therefore making about 100 buckets in the histogram. Figure 3.1 shows the language encoding distribution.

Figure 3.1: Web page language encoding distribution

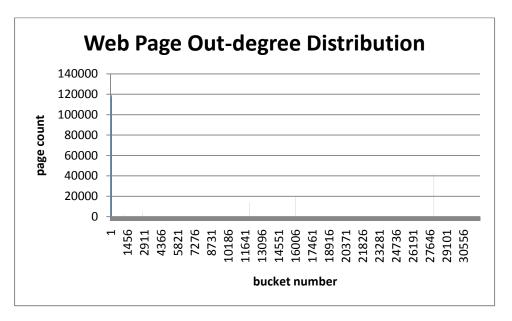

In comparison, there are many more buckets in the Web page out-degree distribution, where each out-degree count represents one bucket. The range of out-degrees in the dataset ranges from 0 to 40000. Most human written Web pages have fewer than 100 outlinks. This characteristic causes clustering for buckets in the range of 0 to 100. The chances of collision in the two distributions are similar, since they have roughly 100 buckets that receive updates. The difference is the Web page out-degree distribution has many more buckets, where most of them receive zero updates. Figure 3.2 shows the Web page out-degree distribution.

Figure 3.2: Web page out-degree distribution

### 3.2 Particle Gravitation

In the particle gravitation benchmark, particles are spread around in 3D space. Each particle exerts a gravitational force on every other particle. Particles are partitioned evenly among processors. As processors work on its set of particles, two processors may update the force field of a particle simultaneously. Synchronization is required to ensure atomic update to the force field. Particles are represented as objects, so that an update to its force field requires a level of indirection.

## 3.3 Adaptive Mesh Refinement

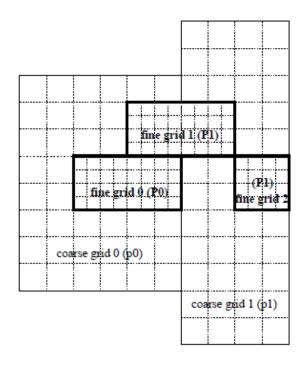

Adaptive Mesh Refinement is one of the largest Titanium applications. It is used in the performance debugging chapter of this dissertation. The AMR methodology has been successfully applied to numerical modeling of various physical problems that exhibit multiscale behavior, such as those mentioned in. The idea of AMR is quite straightforward, that is, to apply finer discretization only at places where higher resolution is needed. However, the simplicity of finite difference calculation on a uniform grid is traded in AMR, where the irregularity comes from the boundaries between grids introduced by local mesh refinement. Figure 3.3 illustrates the interaction between the fine grids and their corresponding coarse grids. Irregular computations arise in updating boundary values, for example, the location-dependent quadratic interpolation of ghost values at the coarse-fine grid interface.

Figure 3.3: Interactions between fine grid and coarse grid in AMR

#### 3.4 Immersed Boundary Method

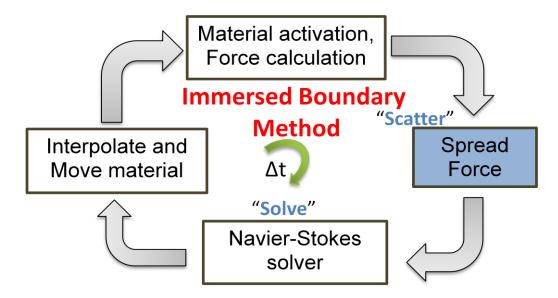

One of the benchmarks used throughout this dissertation is the spread force operation in the Heart simulation code. The Heart simulation code uses the immersed boundary method [51] to simulate blood flow through the heart. The immersed boundary method is a general technique for modeling elastic boundaries immersed within a viscous, incompressible fluid. The method has been applied to several biological and engineering systems, including the simulation of blood flow in the heart, sound waves in the cochlea, and clotting of blood. These simulations have the potential to improve our basic understanding of the biological systems they model and aid in the development of surgical treatments and prosthetic devices. Despite the popularity of the immersed boundary method and the desire to scale the problems to accurately capture the details of the physical systems, parallelization for large scale distributed memory machine has proven challenging. Figure 3.4 shows the four phases of the Heart simulation.

Figure 3.4: The four phases of the immersed boundary method

One of the most challenging operations in the heart simulation is spread force, where the forces from the heart fiber point are spread to the neighboring fluid cells. The target array is 3D, and the particle spreads force to its nearest 4x4x4 cube of fluid cells. In this dissertation, we explore optimizations that are applicable to the spread force operation on both multicore processors and clusters.

Figure 3.5: 2D Heart spread force. Each particle affects its nearby 4x4 neighbor patch

In Figure 3.5, we visualize a 2D particle-to-grid spread force operation of the Heart Code. As the patch is interpolated into the grid, 16 point must be updated (the 3D Heart Code updates 64 points in a 4x4x4 cube). Enlarged circles represent grid points that receive updates from multiple patches. Proper synchronization must be used to avoid data races on those grid points. For example, there are two grid points in the upper right corner of patch 2 that overlap with patch 1 and patch 3. Between patch 1 and patch 3, there are 12 grid points that overlap.

The density of heart fiber points is not uniform throughout the fluid grid. In the beginning of the simulation, the heart fiber points are grouped together in a heart shape at the center of the fluid cell. As the simulation progresses, the fiber points slowly drift away from the center. High density of fiber points are found at the center of the fluid grid. Regions away from the center have sparse population of fiber points. For the experiments in this chapter, we use a sphere instead of the actual heart for simulation. The source code is the same, only the initial positions of the fiber points differ to make up a different shape. It is much easier to generate inputs for different size problems for the sphere. For the heart, we only have inputs for a single configuration from clinical data. The sizes of the fluid grid used in our experiments are 128^3, 192^3, and 256^3.

There are two input parameters in the heart code to describe the test simulation. They are the grid size and number of particles. We vary the number of particles and the grid size in our experiments. The particles form a sphere centered in the fluid grid. Particles are evenly distributed on the surface of the sphere. By varying the number of particles, we change the particle density on the surface of the sphere. By varying the grid size, we change the memory footprint of the problem instance, which is analogous to increasing the number of buckets in a histogram.

### 3.5 Sparse Matrix Vector Multiply

Indirect array accesses and the irregular memory access patterns that result are common in sparse matrix code. In this dissertation, we use a sparse matrix kernel, matrix vector multiplication, to evaluate our compiler and runtime techniques for optimizing irregular read data access patterns. In this case, the matrix is sparse while both the source and result vectors are dense. The parallel algorithm partitions the matrix by rows, with each processor getting a contiguous block of complete rows. Each processor also holds the corresponding piece of the result vector, so the only communication that is required is on the source vector. Because the source vector is often computed from an earlier result, it is partitioned in the same manner as the result vector. Figure 3.6 illustrates the layout of the matrix in the case with eight processors. Communication is only required for the source vector, and only for those elements in which a processor holds a nonzero outside of the processor's diagonal block. The off-diagonal nonzero shown will result in communication from P5 to P1, for example.

Figure 3.6: Parallel layouts of matrix and vector

# **Chapter 4**

## **Optimizing Irregular Reads**

In this chapter, we present compiler and runtime extensions for the Titanium implementation to support programs with indirect read array accesses, such as A[B[i]], where some elements of the A array may live in a remote processor's memory. The effectiveness of the optimizations is evaluated on three different cluster architectures. These computations arise in sparse iterative solvers, particle-mesh methods, and elsewhere. We add compiler support for an inspector executor execution model, which optimizes communication performing runtime optimization based on the dynamic pattern of indices in the indirection array, which is B in the previous example. There are several possible transformations that can be done on the communication, and we consider three in this chapter: sending the entire remote array, sending exactly those elements that are needed, and sending a bounding box of the required values. While packing is guaranteed to send the minimal number of actual values, it has a higher metadata overhead and is therefore not necessarily optimal. One of the challenges is to select the best communication transformation, because it depends on properties of the application and the machine. We introduce a simple analytical performance model into the compiler, which selects optimizations automatically. We analyze the benefits of the automated inspector-executor transformation using sparse matrix vector multiplication on a set of matrices from real applications. Our results show that although the program is significantly simpler when written in Titanium, because it avoids the explicit communication code and the pack and unpack code, the performance is almost always superior to a popular MPI message passing code. The speedup relative to MPI on a suite of over 20 matrices averages 21% on three different machines, with the maximum speedup of more than 2x.

The model-based optimization selection is critical to both programmability and performance. Not only does the model select optimizations that differ by matrix and machine, but also differ between processors within a single matrix-vector multiplication. This runtime complexity is entirely hidden from the programmer, making the application both cleaner and faster.

#### 4.1 Source Code Transformation

In this section, we give motivations for the optimizations later in the chapter using source code transformation on a simple example. The simple example is the indirect sum benchmark in Figure 4.1.

Figure 4.1: Indirect sum benchmark on two processors

The example illustrates the case for two processors, but can easily be extended for more processors. A is an array that resides on processor 1, and B is an index array owned by processor 0 for accessing array A. When processor 0 reads A[B[i]], it requires communication, because A resides on processor 1. Analogously, C is an array on processor 0, and D is an index array owned by processor 1 for accessing array C.

In Figure 4.2, we introduce buffers into the indirect sum benchmark. The buffers are local to each processor. The values of each indirect array access are stored in the buffer, and subsequently used in the second loop. This transformation is legal because neither A or B appear in the left-hand side of an assignment statement in the code on either processor, so it changes neither the local dependence order nor the order of any conflicting accesses across processors.

```

Processor 0

for (i=0; i<n; i++){

buffer0[i] = A[B[i]];

for (i=0; i<n; i++){

sum += buffer0[i];

}

for (i=0; i<n; i++){

sum += buffer0[i];

}

}

```

Figure 4.2: Indirect sum benchmark on two processors with local buffers

In Figure 4.1 and Figure 4.2, the communication uses a pull strategy. Each processor gets the data it needs from the remote processor that owns the data. The next source code transformation in Figure 4.3 uses a push strategy instead. This code does not show the entire transformation, which includes recording information about which values each processor will need from the other and the location of remote buffers in which to store the data. This data is computed in a separate preprocessing phase and is performed only once, whereas the code in

Figure 4.3 will be executed many times, e.g., one per iteration of a solver. In the push strategy, data is put to the processor that needs it.

```

Processor 0

for (i=0; i<n; i++){

buffer1[i] = C[D[i]];

for (i=0; i<n; i++){

sum += buffer0[i];

}

for (i=0; i<n; i++){

sum += buffer0[i];

}

}

```

Figure 4.3: Indirect sum benchmark on two processors using push strategy

Two questions arise from these source code transformations. The first question is when is it legal to apply these transformations. The second question is how do these transformations give us the desired speedup. These questions will be addressed later in this chapter.

### 4.2 Compile Time Transformations

#### 4.2.1 Identify Inspector Executor Candidates

The first step is to identify *inspector executor* candidates for indirect array accesses A[B[i]]. Below is the list of the conditions that the compiler checks for:

• A, B, and all of the elements A[i] and B[i] are not modified either directly or through aliases by the processor reading them. This ensures local dependencies are preserved.

• There are no synchronization points inside of the foreach loop, since the memory model requires memory to be globally consistent at a synchronization point.

The memory consistency model in Titanium does not require a check for conflicting accesses across threads, so the program behavior could be surprising if A and B were modified by another thread. After identifying the candidates, the compiler performs the *inspector executor* transformation. In the inspector phase, the array address for each A[B[i]] is computed. The computed values are stored in an index array. After the inspector phase, a communication method is chosen to retrieve the remote data into a local buffer. More details on the choice of the communication method are presented in Section 4.4. The set of array addresses together with the communication method are stored in a communication schedule. In the executor loop, values for each A[B[i]] are read out of the local buffer.

In some applications, the same pattern of indirect array accesses happens over multiple iterations. One example is an iterative solver. In this case, we would like to store the communication schedule computed during the inspector phase of the first iteration, and reuse the communication schedule on other iterations. A communication schedule may contain information for one or more sets of indirect array accesses to remote arrays. For each set of array accesses, the computed array addresses and the choice of communication method are stored in the schedule. Schedule reuse has been used in prior work, but our schedules contain additional information about the communication method to be employed.

The three properties are sufficient for ensuring the soundness of the *inspector executor* transformation. First we show that the values read for B[i] are the same for both versions of the program. If B and B[i] do not change during the execution of the loop, then the values read for B[i] in the inspector are the same as the ones in the original loop. B can only change locally, because it is a pointer on the local processor. The changes to B[i] can either come locally or remotely. We know that there are no local changes, because we check that B and B[i] are loop invariant using defuse information. Remote changes to B[i] are possible, since any of the remote processors can be executing code that modifies B[i] while the local processor is inside the loop. If we take a snap shot of memory where the B[i]'s reside before the local processor enters the loop, we can use the values from the snap shot for B[i]'s inside the loop regardless of whether there are changes to B[i] remotely. The reason is that there are no synchronization events inside the loop, so any remote changes to B[i] during the execution of the loop do not need to be reflected under the Titanium memory consistency model. Any remote writes to B[i] are allowed to be reordered relative to local reads and writes, so they may all appear to happen after the loop completes.

Now we know the index sets for both versions are the same. We would like to show that the values read from A using this index set are the same for both versions of the program. The argument is similar to the previous step. We know that there are no local changes to A or A[i] using defuse information. Changes to A[i] caused by remote processors during the loop do not need to be reflected, because there is no synchronization event inside the loop.

The requirement that A[i] is not modified by the processor executing the loop can be relaxed. The processor executing the loop has access to the buffer that contains the prefetched values of A[B[i]]. The runtime can conceivably intercept all writes to A[i] from this processor in the loop, and reflect the changes to the values in the buffer. Our experiments show that this relaxation is not worthwhile.

#### 4.2.2 Pull to Push Transformation

Now we know the requirements for applying the *inspector executor* transformation. In this section, we turn our attention to the issue of using the push strategy instead of the pull strategy for communication. Extra coordination between processors is needed to use the push strategy. In the case where the schedule can be reused, we would like to communicate the index set and the choice of communication method during the first iteration, and have the processor that owns the data to send the needed data in the subsequent iterations independently. The push strategy uses about half as many messages as the pull strategy. The pull strategy also suffers when the remote processor is not attentive to the network. The communication is not entirely one-sided, because remote packing is required, so if the remote processor is in a computation intensive loop, other processors may be delayed waiting for it.

The extra coordination means that the communication calls need to be placed in the right place so that the data will be coming when it is expected. It is the job of the compiler to find the right place in the code to insert these communication calls, since we are applying the optimizations automatically without hints from the application programmer.

The communication calls need to be placed in such a way that when a processor is about to enter the loop that contains the *inspector executor* array access, the expected data is on its way from the remote processor. The processor can simply poll on a flag for the arrival of the data.

In Titanium, a barrier statement is executed by all the processors at the same time for the same number of times. Unlike other languages and libraries, the simultaneous barriers must be the same textual instance in the program, so a barrier in one branch of conditional cannot match a barrier in another. This prevents barrier deadlocks in which a barrier is executed by only a subset of the processors and therefore deadlocks. The Titanium compiler provides a static analysis called *single analysis* that eliminates this type of bugs. It conservatively rejects all programs that might run into deadlocks due to misplaced barriers at compile time.

We use *single analysis* to help us in finding the right place to insert the communication calls. The property that we are looking for is that whenever a processor is about to enter the loop containing the *inspector executor* array access, the processor that owns the needed data would execute the communication calls to send the data over. In the top of the loop that contains the *inspector executor* array access, we insert a barrier node in the control flow graph. Then we run single analysis on this modified control flow graph. Single analysis tells us if it is safe to place the barrier in the top of the loop. If it is not safe, then it is not safe to place the communication calls there, because the processor that needs the data and the processor that owns the data may come to the top of the loop at different times or for different number of times. If single analysis tells us that it is safe to place a barrier in the top of the loop, then we can place the communication calls there, because we are certain that all processors would come to the top of

the loop around the same time for the same number of times. After running single analysis, we remove the barrier node from the control flow graph.

#### 4.2.3 Overlap

Our generated code utilizes two types of overlap: communication with communication, and communication with computation. When a processor owns data that is needed by multiple remote processors, non-blocking puts are used to push the needed data to the remote processors. While waiting for the remote data to arrive, we can overlap the computation that only involves local elements or computation with elements that have already arrived.

### 4.3 Experimental Platforms

We performed experiments on three parallel machines and developed a performance model for the communication on each of them. This includes a cluster of Itanium processors connected by a Myrinet network, an IBM Power3 system, and an HP system with a Quandrics interconnect. Table 4.1 contains a summary of their key features.

| Name    | System           | Network   | CPU       |

|---------|------------------|-----------|-----------|

| RTC     | Linux cluster    | Myrinet   | 900 MHz   |

|         |                  | 2000      | Itanium 2 |

| Seaborg | IBM RS/6000 SP   | SP Colony | 375 MHz   |

|         |                  | Switch 2  | Power 3+  |

| Lemieux | Compaq           | Quadrics  | 1 GHz     |

|         | Alphaserver ES45 | Elan3     | Alpha     |

Table 4.1: machine summary

### 4.4 Runtime Selection of Communication

With a set of indirect array accesses to a remote array, there are several options for performing the data communication. The options are listed below:

• *Pack method*: only communicates the needed elements without duplicates. The needed elements are packed into a buffer before sending them to the processor that needs the data.

- *Bound method*: use a bulk put operation to send a bounding box that contains the needed elements.

- *Bulk method*: use a bulk put operation to send the entire array.

The three methods require different amount of set up work. The pack method needs to run the inspector phase to translate all the indirect array accesses into remote addresses and the bound method needs to run the inspector phase to compute the bounding box that contains all the needed elements. The bulk method does not require an inspector phase.

In this chapter, we focus on the case where the communication pattern is repeated several times, in which case the cost of the inspector is amortized, so we always run the inspector in the first iteration. In this scenario the bulk method becomes a special case of the bounding box method, so we only discuss the pack and bound methods in the remainder of this chapter.

Our experiments show that the choice of communication is both application and machine specific. The application determines the size of the array, number of accesses to that array, and the size of the bounding box. The machine gives different memory and communication costs. Our compiler generates code that can choose the best communication method at runtime based on a performance model.

The total time of a communication method consists of three parts:

- 1. the time spent on getting the data ready for communication in the remote processor

- 2. the communication time for sending the data

- 3. the time for reading the data out of local buffer in the executor loop

Both 1 and 3 are local processor costs, which are dominated by memory access times. We use cache and memory latency numbers provided by the vendor in a performance model. In the pack method, the needed elements are gathered into a buffer by the remote processor. The gathering from the source array is random access, while the storing of the elements into the buffer and the reading of indices are sequential access. In the bound method, no packing of the data is needed, since the entire bounding box is sent. Figure 4.4 shows the model components. N is the number of distinct elements being packed, L1<sub>line</sub> and L2<sub>line</sub> are cache line sizes, and  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_{mem}$  are latencies for L1, L2, and memory, respectively. Cache line sizes are adjusted to match the word size in each formula.

buffer gather:  $N\alpha_1 + N / (L1_{line})(\alpha_2 - \alpha_1) + N / (L2_{line})^*(\alpha_{mem} - \alpha_2)$ index read:  $N\alpha_1 + N / (L1_{line})(\alpha_2 - \alpha_1) + N / (L2_{line})^*(\alpha_{mem} - \alpha_2)$ source: if (source fits in L1) then  $N\alpha_1$ else if (source fits in L2) then  $N\alpha_2$ else  $N\alpha_{mem}$

Figure 4.4: Performance model for packing

To estimate the communication cost, we use a piecewise linear model. For large messages, the cost is a fixed per message latency plus a per Byte bandwidth cost. We found that using this simple linear model for small messages was not accurate enough, and instead use different latency and bandwidth terms in different size ranges. For example, in the GM network, the steps are due to the 4KB MTU size of the packets. Figure 4.5 shows how well our models fit the actual. The average error comparing our models with the actual on all three machines is less than 1%. These latency and bandwidth numbers are computed empirically for each machine.

Figure 4.5: Comparing the latency bandwidth models to actual on LAPI, GM, and Elan

In practice, each processor may communicate with multiple other processors, while our model is for a single pair of processors and does not account for network contention. The number of simultaneous communication events depends on the application characteristics. While our point to point model does not capture this more complex communication behavior, we find it is sufficient for selecting a good communication method, as we will show in the performance section.

After the data arrives at the destination processor, the data is read out of the buffer during the executor phase in a random access pattern. In our model, we assume the costs for both methods are the same, although the bound method may suffer more cache misses in practice, because it is a larger data buffer than in the pack case.

We pick the communication method that gives the lowest estimated cost by adding the packing and communication cost estimates. A choice is made separately for each processor pair. A schedule may contain several pairs, since each processor may need to communicate with several remote processors. The communication method selection automatically trades off network bandwidth and cache misses. By packing the needed elements into a buffer, the pack method uses a smaller message than the bounding box, but it incurs more memory traffic for the packing process.

# 4.5 Optimizing a Sparse Matrix Kernel

Indirect array accesses and the irregular memory and network access patterns that result are common in sparse matrix code. In this section we use a sparse matrix kernel, matrix vector multiplication, to evaluate our compiler and runtime techniques, which are entirely automatic. In this case, the matrix is sparse while both the source and result vectors are dense.

The parallel algorithm partitions the matrix by rows, with each processor getting a contiguous block of complete rows. Each processor also holds the corresponding piece of the result vector, so the only communication that is required is on the source vector. Because the source vector is often computed from an earlier result, it is partitioned in the same manner as the result vector. Figure 4.6 illustrates the layout of the matrix in the case with eight processors. Communication is only required for the source vector, and only for those elements in which a processor holds a nonzero outside of the processor's diagonal block. The off-diagonal nonzero shown will result in communication from P5 to P1, for example.

Figure 4.6: Parallel layouts of matrix and vectors

Due to the different nonzero structures of the matrices, the communication requirements vary widely across matrices. We therefore use a set of benchmark matrices from real applications to evaluate our optimizations. Figure 4.7 gives two examples to illustrate the differences. On the left we have the nemeth21 from Matrix Market [49]. It is a 9506x9506 matrix with 1173746 nonzeros. Because the nonzero occur only near the diagonal, each processor needs to communicate with at most two of its neighbors. The garon2 matrix on the right is taken from the UF Sparse Matrix Collection and is a 2D finite element method matrix [66]. The size is 13535x13535 and there are 390607 nonzeros. There is more data communication for this matrix than the previous one, because nonzero are spread throughout the matrix, albeit in a regular pattern. Every processor will need some data from every other processor.

Figure 4.7: Structure of nemeth21 (left) and garon2 (right)

### 4.6 Evaluating Each Optimization

We begin by analyzing the performance of several different Titanium implementations using the garon2 matrix, which will highlight the differences in communication costs between the versions. The Titanium source code is the same across the versions, but the compiler and runtime support differ. Figure 4.8 shows the performance on the Itanium/Myrinet cluster using the GASNet implementation for Myrinet's GM1 communication layer.

Figure 4.8: Performance on the garon2 matrix

Naïve: With the naïve version, the generated code uses a remote read for each indirect array access when the array is remote. As expected, the performance does not scale.

Pull: The next line shows the benefit of an initial inspector executor optimization on this code. This significantly improves on the naïve version, because data is packed into larger messages. Remote gets are used in this case to pull data from the remote parts of the source vector.