## **UC Davis**

## **UC Davis Electronic Theses and Dissertations**

#### **Title**

Photonic integrated circuits for optical sensing and communication

#### **Permalink**

https://escholarship.org/uc/item/3cz8z09n

#### **Author**

Zhang, Yichi

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

Ву

## YICHI ZHANG DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

**DOCTOR OF PHILOSOPHY**

in

**Electrical and Computer Engineering**

in the

OFFICE OF GRADUATE STUDIES

of the

**UNIVERSITY OF CALIFORNIA**

**DAVIS**

Approved:

S. J. Ben Yoo, Chair

Juan Sebastian Gomez Diaz

Weijian Yang

Committee in Charge

2023

To my family members and my friends

## **ACKNOWLEDGEMENTS**

Pursuing a Ph.D. has been a long, unforgettable, and fruitful experience. I want to thank my advisor, Distinguished Professor S. J. Ben Yoo, who has provided me with constant support and inspiring guidance since 2016. His knowledge and insight in the integrated photonics area guided my research. More importantly, his hardworking attitude and well-organized habits set a standard for an excellent researcher.

I want to thank my dissertation committee members, Prof. J. Sebastian Gomez-Diaz and Prof. Weijian Yang, for providing guidance and advice on my dissertation.

I want to thank everyone in the Next Generation Networking and Computing Systems (NGNCS) group. Kuanping Shang was my mentor in my first year. His careful training in photonic device design and fabrication built my foundation in photonics research. I want to thank Yu Zhang for giving me enlightening guidance. His comments and advice helped me accomplish many research tests, and he shows an excellent example of teamwork. I want to thank Mathias Prost and Tiehui Su for their photonic device characterization training, Siwei Li for the development of the flip-chip bonding process, Yi-chun Lin for his help on photonic integrated chips characterization, and Hongbo Lu for his research work in the ERON project. I also want to thank Chuan Qin, Shaoqi Feng, Guangyao Liu, Gengchen Liu, Kaiqi Zhang, Mingye Fu, Hang Su, Yujia Zhang, Jingwei Wan, Zhennan Wu, Zhixing Lin, Rijuta Ravichandran, and Yiting Jin for their help and encouragements.

I also want to thank my friends who helped me in the nanolabs, including Xiaoer Hu, Zeying Ren, Qianyi Xie, and Hanbin Song, for their advice and accompanying. I want to thank all my

friends who helped me through the seven years, including Qiutong Jin, Xuan Ding, Xiaoyu Yang, and Wenjin Pei.

I want to appreciate all staff in UC Berkeley Marvell Nanofabrication Laboratory and Center for Nano-MicroManufacturing, including Dave Taosaka, Allison Dove, Richelieu Hemphill, Ryan Rivers, Sam Tsitrin, Jay Morford, Jason Chukes, Joanna Bettinger, Daniel Martinez, Ryan Anderson, Chan Kim, Vishal Narang, and Paula Lee.

Finally, I want to thank my family for their love and support. My parents and grandparents supported me unconditionally during my Ph.D. study. I want to thank Kaiyi Wu, Hong Yang, and Ziyao Guo for their encouragement.

## **ABSTRACT**

Photonic integrated circuits (PICs) are widely used in various applications, such as optical sensing, computing, and communication, thanks to the development of multiple photonic components, including light sources, waveguides, couplers, splitters, combiners, multiplexers, detectors, and modulators. Many material platforms can be employed for PICs. Silicon photonics taking advantage of the mature complementary metal-oxide-semiconductor (CMOS) fabrication technology stands out as a good choice. Silicon-on-insulator (SOI) platform is attracting more interest since it is CMOS compatible, cheap, and scalable. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) platform is also CMOS compatible and can be a supplementary and substitution of the Si platform in some cases, especially when low propagation and high scalability are required. Complex integrated photonics systems usually require the integration of many platforms.

The explosive growth of the demands for sensing and data transferring drives the development of integrated photonics. For example, future autonomous vehicles require low-cost, high-performance light detection and ranging (LIDAR) systems. Optical interconnects are proposed and being explored for modern high-performance computing (HPC) systems. Modern astronomy needs a small size, weight, and power consumption optical sensing system to significantly reduce the cost. Integrated photonics are continuously being explored and developed for higher performance and lower cost.

This dissertation presents the development of PICs for optical imaging and communication. Chapter 1 introduces integrated photonics and briefly introduces all the works in this dissertation. Chapter 2 presents our multi-layer Si<sub>3</sub>N<sub>4</sub> platform, including the device design, simulation, fabrication, and measurement. This chapter experimentally demonstrates our multi-layer Si<sub>3</sub>N<sub>4</sub>

platform. Chapter 3 proposed and demonstrated a low-loss and broadband optical interposer for large-scale integration. The interposer includes low-loss inter-chip couplers and can be extended to a wafer scale, which shows great potential for large-scale heterogeneous integration for modern sensing and communication systems.

Chapters 4 and 5 discuss the segmented planar imaging detector for electro-optic reconnaissance (SPIDER) realized by PICs for astronomy. The SPIDER uses interferometric imaging based on PICs and can significantly reduce the size, weight, and power consumption compared to traditional bulk optical devices. Chapter 4 presents a SPIDER imager formed by many chips and a high-resolution SPIDER imaging achieved using a wafer-scale fabrication technique. Chapter 5 presents a surface-coupled SPIDER imager based on a broadband surface coupler.

Chapter 6 investigates the PICs for an elastic RF-optical network. The PICs are based on our multi-layer Si<sub>3</sub>N<sub>4</sub> platform and include arrayed waveguide grating (AWG), multi-mode interferometer (MMI), and thermal phase shifters. The PICs show the capability of generating optical signals for RF-beam forming.

Chapter 7 summarizes the dissertation.

## **Table of Contents**

| ACKN   | NOWLEDGEMENTS                                                                          | iii  |

|--------|----------------------------------------------------------------------------------------|------|

| ABST   | RACT                                                                                   | v    |

| LIST ( | OF FIGURES                                                                             | ix   |

| LIST ( | OF TABLES                                                                              | xvii |

| Chapte | er 1 Introduction                                                                      | 1    |

| 1.1    | Overview of photonic integrated circuits                                               | 1    |

| 1.2    | Large-scale heterogeneous photonic integrated systems                                  | 4    |

| 1.3    | Low-loss and broadband wafer-scale optical interposer                                  | 6    |

| 1.4    | Large-scale PICs for optical interferometric imaging                                   | 7    |

| 1.5    | Surface-coupled SPIDER imager                                                          | 8    |

| 1.6    | PICs for an elastic RF-optical network                                                 | 9    |

| 1.7    | Organization of the dissertation                                                       | 9    |

| Chapte | er 2 Design, Fabrication, and Characterization of Multi-Layer Silicon Photonic Devices | 15   |

| 2.1    | Silicon nitride platform overview                                                      | 15   |

| 2.2    | Silicon nitride devices simulation and layout                                          | 20   |

| 2.3    | Multi-layer silicon nitride platform                                                   | 22   |

| 2.     | .3.a Multi-layer silicon nitride platform                                              | 22   |

| 2.     | .3.b Low-loss inter-layer coupler                                                      | 25   |

| 2.     | .3.c Multi-layer silicon nitride platform fabrication                                  | 31   |

| Chapte | er 3 Low-loss and broadband optical interposer for large-scale integration             | 42   |

| 3.1    | Diagram of the low-loss electrical and optical interposers                             | 42   |

| 3.2    | Low-loss and broadband optical interposer for large-scale integration                  | 51   |

| 3.3    | Large-scale integration using optical and electrical interposer                        | 59   |

| Chapte | er 4 PICs for Optical Interferometric Imaging                                          | 68   |

| 4.1    | Overview of the interferometric imaging                                                | 68   |

| 4.2    | Platform and devices for SPIDER                                                        | 70   |

| 4.3    | Optical interferometric imaging using a multi-chip system                              | 75   |

| 4.4    | Large-scale Si3N4 Integrated Circuit for High-resolution Interferometric Imaging       | 87   |

| Chapte | er 5 Surface-coupled SPIDER Imager                                                     | 101  |

| 5 1    | 1st version of the surface coupler                                                     | 101  |

| 5.2 2 <sup>nd</sup> version of the surface coupler | 114 |

|----------------------------------------------------|-----|

| 5.3 Surface-coupled SPIDER Imager                  | 124 |

| Chapter 6 PICs for an elastic RF-optical network   | 136 |

| 6.1 Overview of the elastic RF-optical network     | 136 |

| 6.2 Elements design of the PICs                    | 138 |

| 6.3 1 <sup>st</sup> generation ERON PPU            | 149 |

| 6.4 2 <sup>nd</sup> generation ERON PPU            | 156 |

| Chapter 7 SUMMARY                                  | 167 |

| APPENDIX A: LIST OF PUBLICATIONS                   | 170 |

# **LIST OF FIGURES**

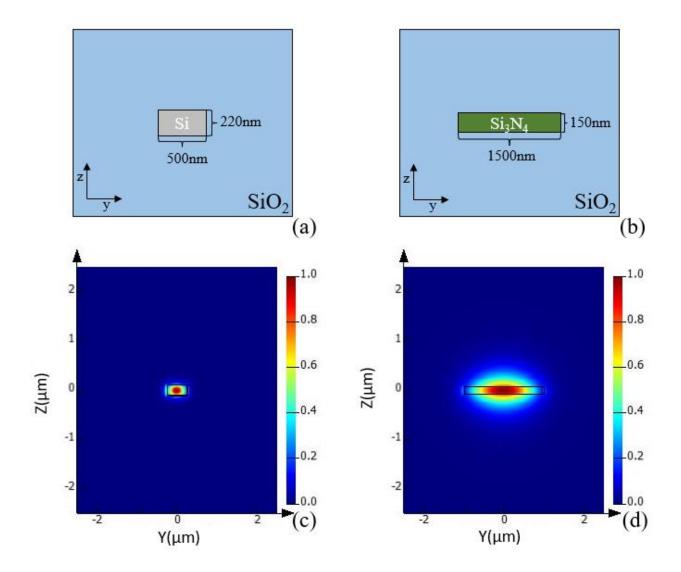

| Figure 1 (a) The schematic of a typical silicon waveguide embedded in silicon dioxide at cross-section                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| view. The thickness of silicon is 220nm, and the width of the silicon is 500nm. (b) The schematic of a                                                                                                      |

| typical silicon nitride waveguide embedded in silicon dioxide, at cross-section view. The thickness of                                                                                                      |

| silicon is 150nm, and the width of the silicon is 1500nm. (c) and (d) the simulated fundamental TE mode                                                                                                     |

| in (a) and (b), respectively. The simulation area is $5\mu m$ by $5\mu m$                                                                                                                                   |

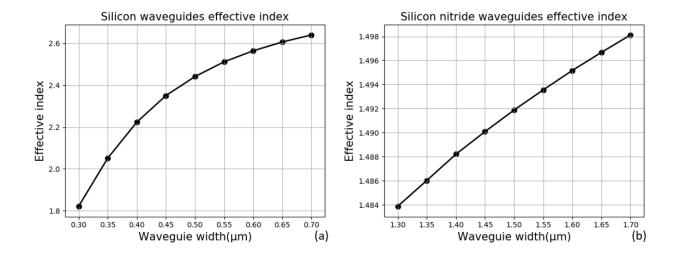

| Figure 2 (a) Effective index of a silicon waveguide with 220nm core thickness with varying waveguide width (around 0.5µm). (b) The effective index of a silicon nitride waveguide with 150nm core thickness |

| with varying waveguide width (around 1.5μm). Lumerical FDE simulates the effective index20                                                                                                                  |

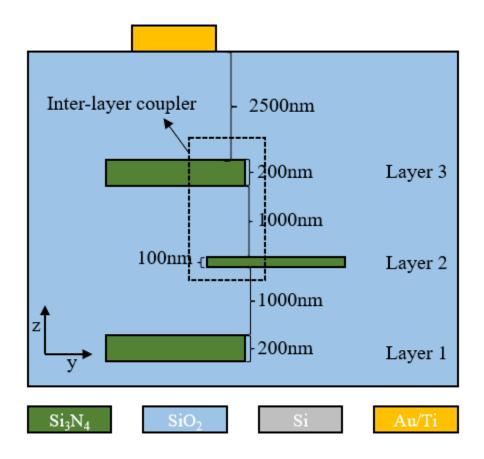

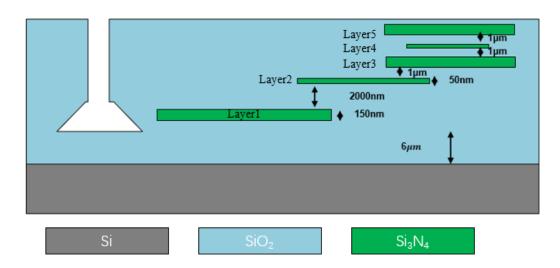

| Figure 3 Diagram of the multi-layer silicon nitride platform. The silicon nitride platform consists of 3                                                                                                    |

| layers and one metal layer for thermal tuning. Layer 1 and 3 are function layers, while layer 2 is a                                                                                                        |

|                                                                                                                                                                                                             |

| transition layer                                                                                                                                                                                            |

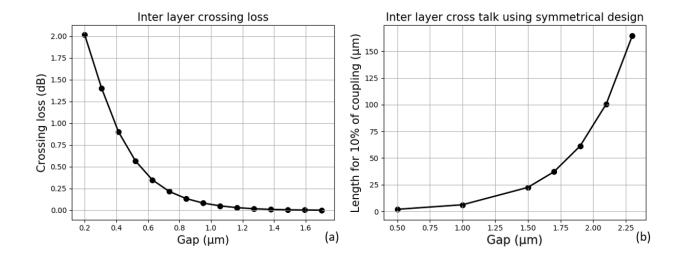

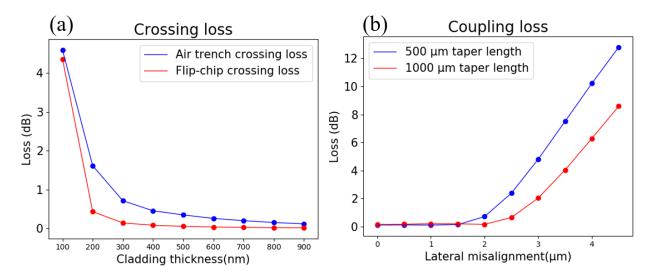

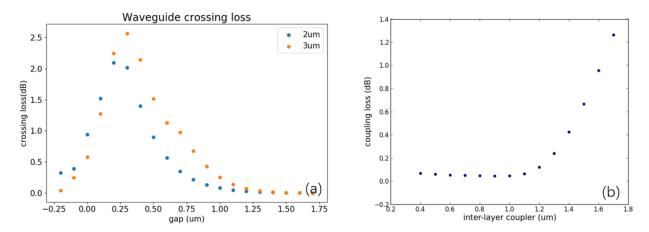

| Figure 4 (a) Inter-layer crossing loss with varying gap thickness. The waveguides at the 2 layers have                                                                                                      |

| 200nm waveguide thickness and 2µm width. (b) Inter-layer crosstalk with varying gap thickness. The                                                                                                          |

| waveguides at the 2 layers have 200nm waveguide thickness and 2μm width and overlap with each other.                                                                                                        |

| The y-axis shows the length of 10% of crosstalk between the two layers.                                                                                                                                     |

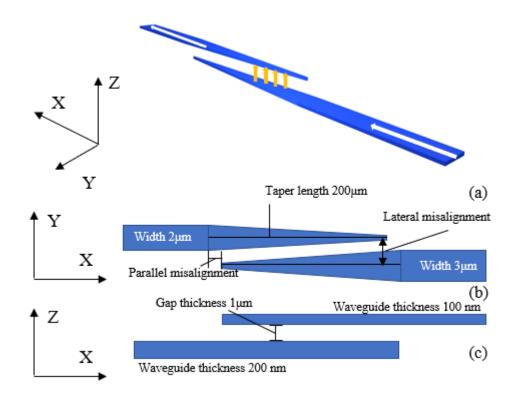

| Figure 5 (a) 3D diagram of the inter-layer coupler. The white arrows indicate the light transmission                                                                                                        |

| through the waveguides, and the yellow arrows indicate the light transmission through the two                                                                                                               |

| waveguides evanescently. (b) Top view of the interlayer coupler. (c) Cross-section view of the inter-layer                                                                                                  |

| coupler [39]25                                                                                                                                                                                              |

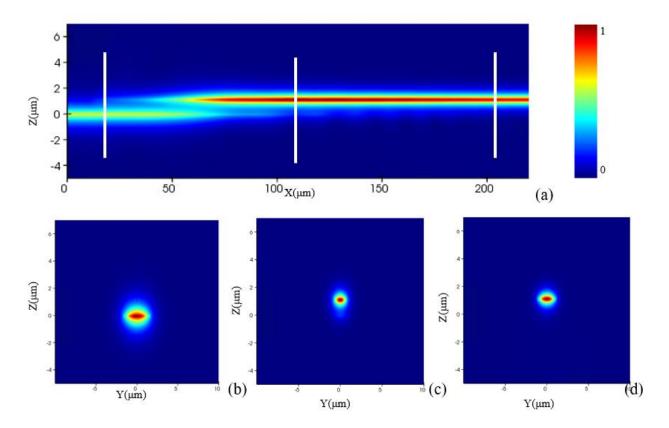

| Figure 6 (a) Simulated inter-layer coupler at the XoZ plane. The input waveguide has a 100nm thickness                                                                                                      |

| and $3\mu m$ width. The output waveguide has a 200nm thickness and $2\mu m$ width. The inter-layer coupler has                                                                                              |

| a $1\mu m$ gap. The three whit lines denote the beginning of the output taper, the middle of the tapers, and the                                                                                            |

| end of the output taper, whose cross-section view of the E-field at YoZ plane (in Figure 5) is shown in (b)                                                                                                 |

| (c), and (d), respectively27                                                                                                                                                                                |

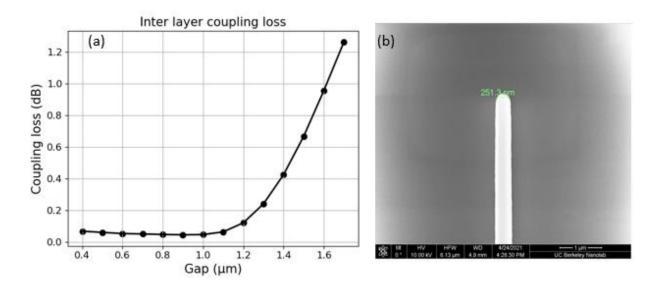

| Figure 7 (a) Simulated inter-layer coupling loss with varying gap thickness. The input waveguide has a                                                                                                      |

| $100$ nm thickness and $3\mu m$ width. The output waveguide has $200$ nm thickness and $2\mu m$ width. (b) An                                                                                               |

| SEM photo of the inter-layer coupler at the end of the taper                                                                                                                                                |

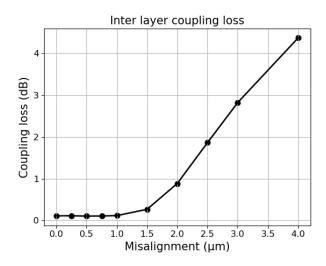

| Figure 8 (a) Simulated inter-layer coupling loss with varying lateral misalignment. The input waveguide                                                                                                     |

| has a 100nm thickness and 3µm width. The output waveguide has 200nm thickness and 2µm width. The                                                                                                            |

| inter-layer coupler has a 1µm gap and 200µm taper length.                                                                                                                                                   |

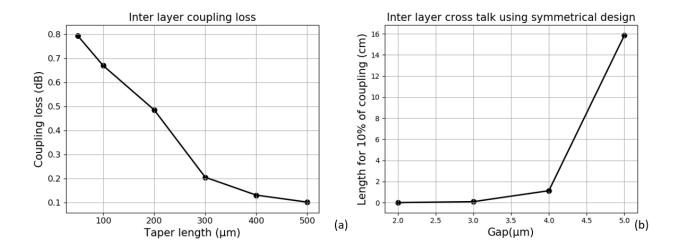

| Figure 9 (a) Simulated inter-layer coupling loss with varying taper length. The input waveguide has a                                                                                                       |

| 100nm thickness and 3μm width. The output waveguide has 200nm thickness and 2μm width. The inter-                                                                                                           |

| layer coupler has a 1.4µm gap. (b) Simulated inter-layer crosstalk using the same waveguide as (a) 30                                                                                                       |

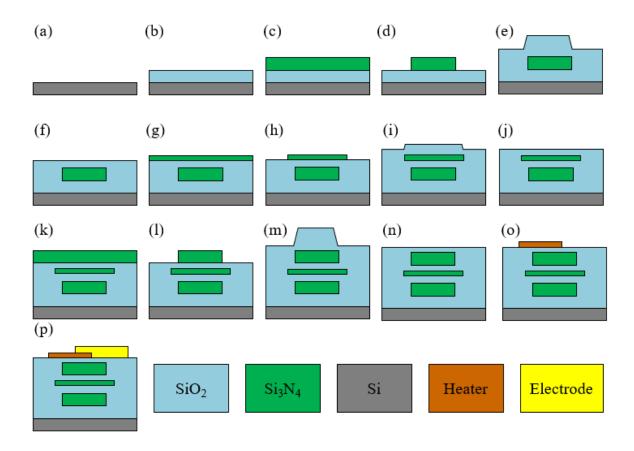

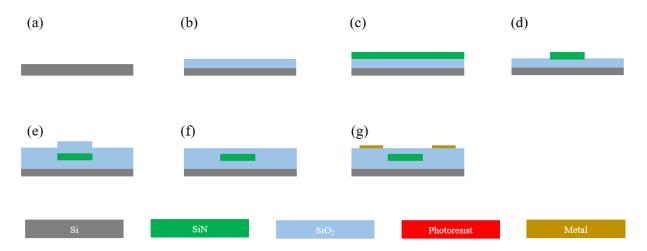

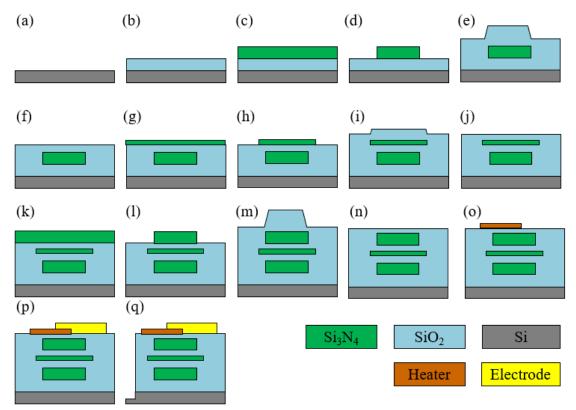

| Figure 10 Fabrication process flow of the multi-layer silicon nitride platform. (a) Initial wafer cleaning for                                                                                              |

| 6-inch wafers. (b) Thermal oxidation. (c) The bottom layer is 200 nm Si3N4 deposition. (d) 500 nm                                                                                                           |

| Si3N4 patterning by lithography and etching. (e) First inter-layer SiO2 deposition. (f) CMP. (g) The                                                                                                        |

| transition layer 100 nm Si3N4 deposition (h) 100 nm Si3N4 patterning by lithography and etching. (i)                                                                                                        |

| Second inter-layer SiO2 deposition. (j) CMP. (k) The top layer 200nm Si3N4 deposition. (l) 200 nm                                                                                                           |

| Si3N4 patterning by lithography and etching. (m) Top cladding SiO2 deposition. (n) CMP. (o) 20nm Ti /                                                                                                       |

| 100 nm Au metal heaters fabrication using metal lift-off. (p) 20 nm Ti / 800 nm Au metal electrodes                                                                                                         |

| fabrication using metal lift-off.                                                                                                                                                                           |

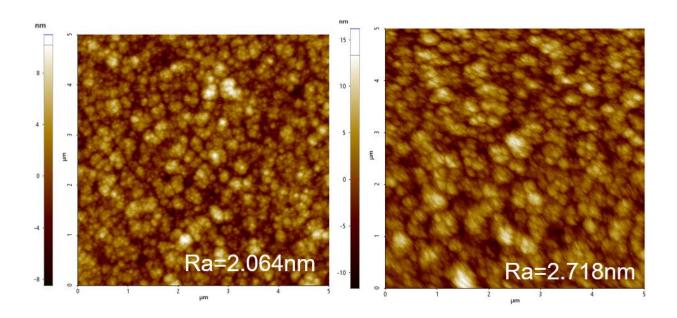

| Figure 11 Surface roughness measured by atomic force microscope (AFM) (a) thermal oxide. (b) LTO             |

|--------------------------------------------------------------------------------------------------------------|

| after deposition, (c) LTO after deposition, and (c) LTO after CMP32                                          |

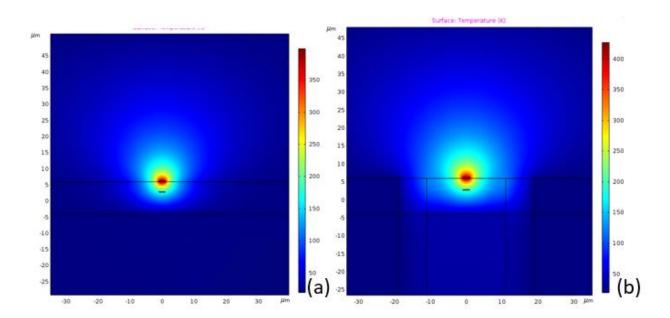

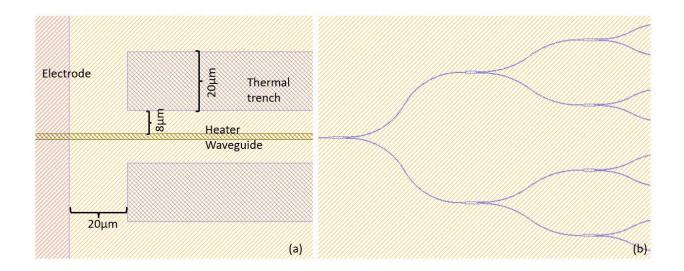

| Figure 12 Thermal simulations of the single-layer silicon nitride waveguide using the same input thermal     |

| power. The room temperature is 20°C. (a) No thermal trench. The center of the silicon nitride has 176°C      |

| temperature. The temperature at 30 µm away from the waveguide is 23 °C. (b) Two thermal trenches at the      |

| left and right of the waveguide by 8μm. The center of the silicon nitride has 200°C temperature. The         |

| temperature at 30µm away from the waveguide is 20.4°C                                                        |

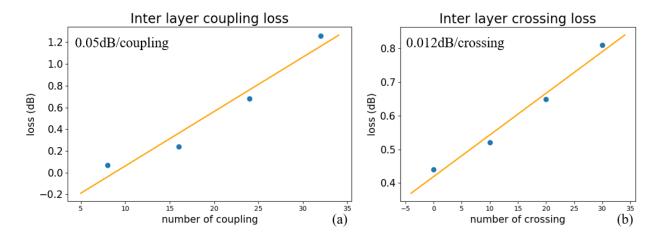

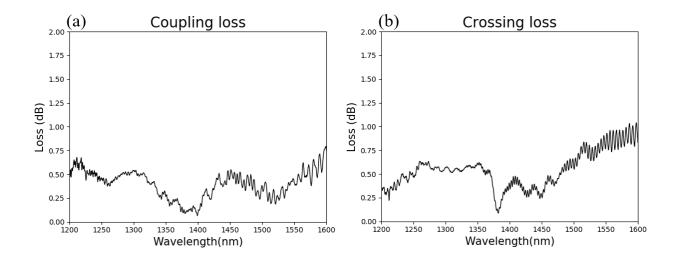

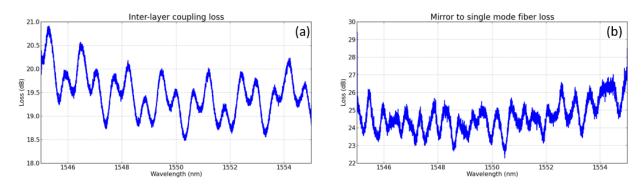

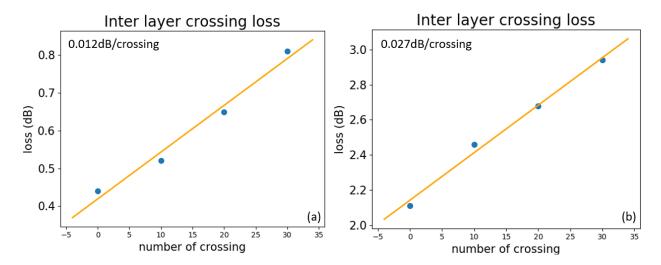

| Figure 13 (a) Measured inter-layer coupling loss. (b) Measured inter-layer crossing loss35                   |

| Figure 14 SEM photo of the silicon nitride waveguides on one layer                                           |

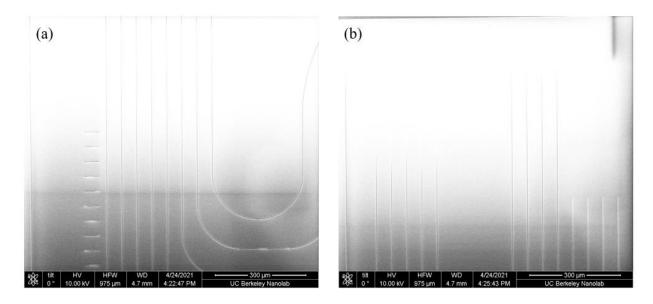

| Figure 15 (a) Layout of the 8×8 200GHz channel spacing AWG and (b) SEM photo of the 8×8 200GHz               |

| channel spacing AWG after waveguide patterning                                                               |

| Figure 16 Measured 8×8 200GHz channel spacing AWGR transmission spectrum38                                   |

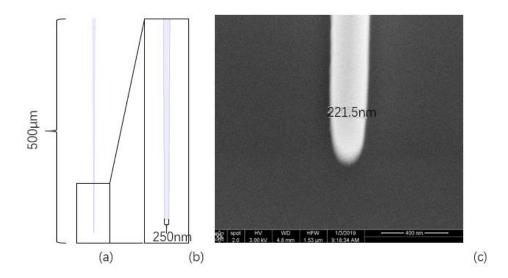

| Figure 17 (a) A layout for an inverse taper coupler with 500µm taper length. (b) An SEM photo of the         |

| inverse taper coupler with 250nm taper end width and 100nm thickness                                         |

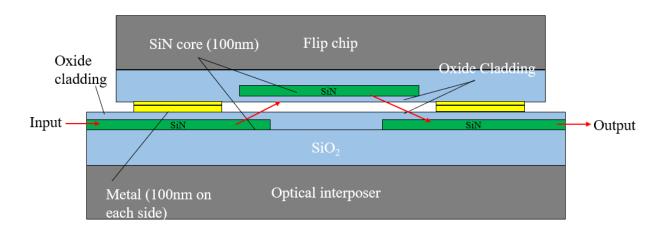

| Figure 18 Diagram of the optical interposer. Red arrows indicate the light propagation directions 44         |

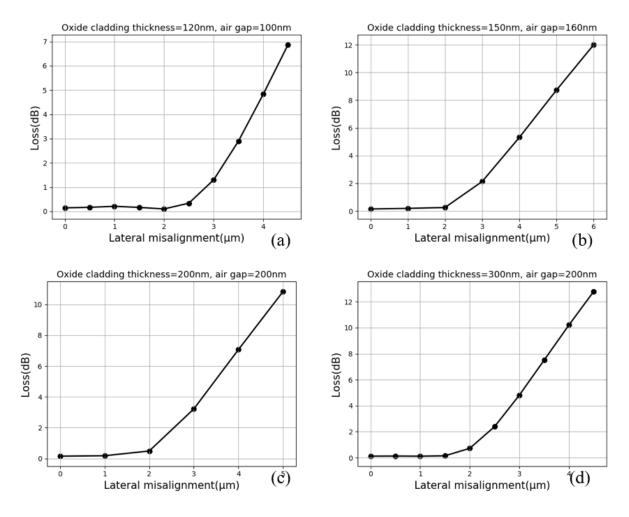

| Figure 19 Coupling loss of the chip-to-chip coupler with 500µm taper length with a varying lateral           |

| misalignment at TE mode and 1550nm wavelength. (a) The oxide cladding is 120nm on each side, and             |

| the air gap is 100nm. (b) The oxide cladding is 150nm on each side, and the air gap is 160nm. (c) The        |

| oxide cladding is 200nm on each side, and the air gap is 200nm. (d) The oxide cladding is 300nm on each      |

| side, and the air gap is 200nm                                                                               |

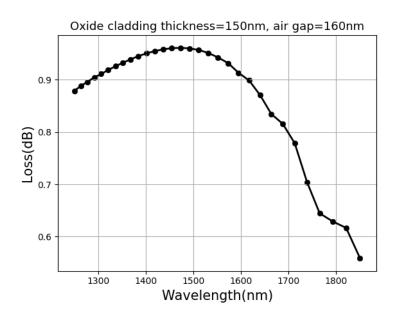

| Figure 20 Bandwidth of the chip-to-chip coupler with 500µm taper length at TE mode46                         |

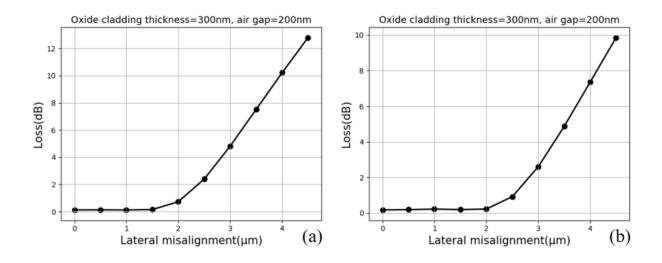

| Figure 21 Coupling loss of the chip-to-chip coupler with a varying lateral misalignment at TE mode and       |

| $1550 nm$ wavelength, with (a) $500 \mu m$ taper length and (b) $1000 \mu m$ taper length                    |

| Figure 22 Fabrication process of the optical interposer. (a) Initial wafer cleaning. (b) LTO deposition or   |

| thermal oxidation. (c) Silicon nitride LPCVD. (d) Waveguide patterning using lithography and etching. (e)    |

| LTO deposition. (f) CMP. (g) Metal patterning using metal lift-off                                           |

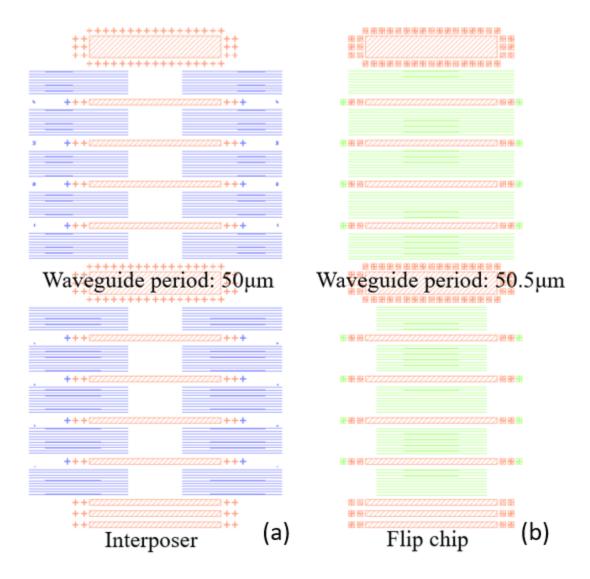

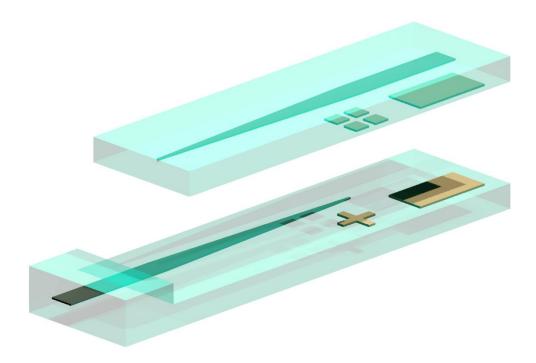

| Figure 23 (a) Layout of the interposer. The blue structures are on the silicon nitride layer. (b) Layout of  |

| the flip-chip. The green structures are on the silicon nitride layer. Orange structures on both layouts show |

| the metal layer49                                                                                            |

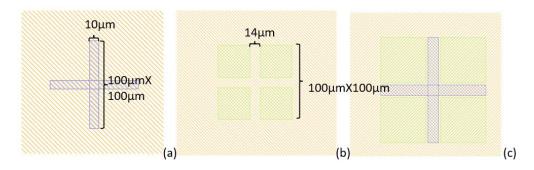

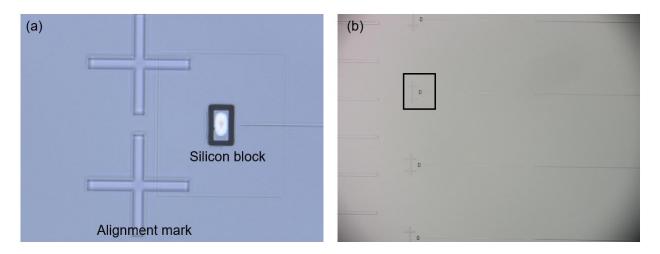

| Figure 24 Alignment marks on the (a) interposer and (b) flip chips. (c) Overlay of the alignment marks on    |

| both chips50                                                                                                 |

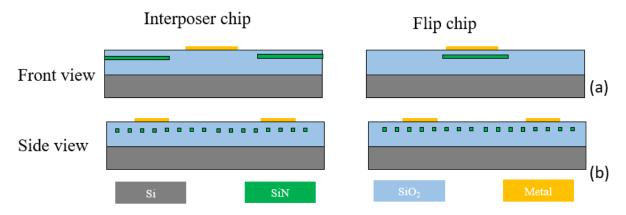

| Figure 25 Diagram of the interposer chip and the flip chip. (a) Front view. (b) Side view50                  |

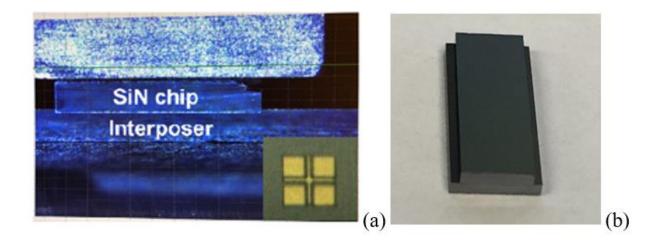

| Figure 26 (a) Photo of flip chip bonding. The small figure at the bottom right illustrates the alignment of  |

| flip-chip bonding. (b) Photo of the bonded chips                                                             |

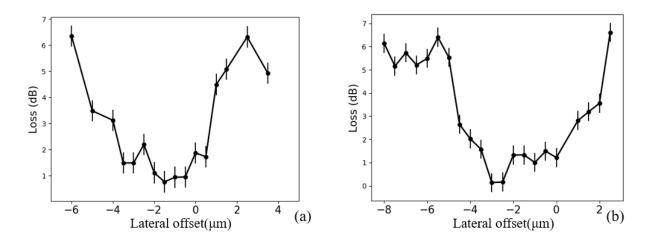

| Figure 27 Measured chip-to-chip coupling loss (a) with 500μm taper length and (b) with 1000μm taper          |

| length                                                                                                       |

| Figure 28 Schematic of the inter-chip coupler. Alignment marks and bonding pads are on the surface of        |

| the two chips. The Orange arrows denote the beam propagation direction. The black arrow denotes the          |

| chip movement direction during flip-chip bonding                                                             |

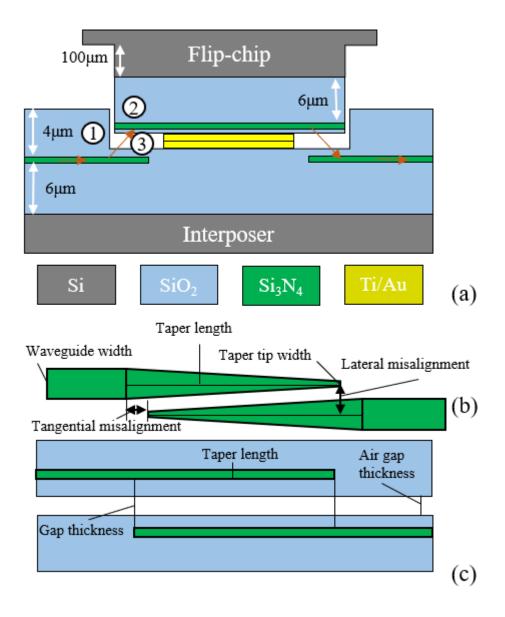

| Figure 29 (a) Diagram of the flip-chip and Interposer packaging. The numbers denote:1. Air trench            |

| crossing loss, 2. flip-chip crossing loss, and 3. coupling loss. (b) Top view and (c) side view diagram of   |

| the inter-chip coupler53                                                                                     |

| Figure 30 (a)Simulated crossing loss, (b) Simulated coupling loss                                            |

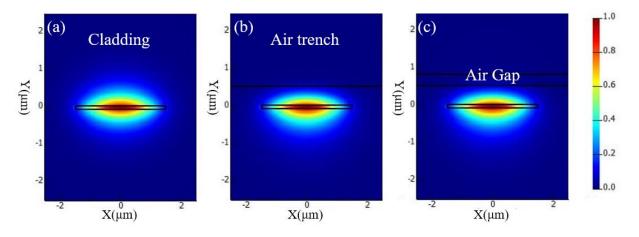

| Figure 31 (a), (b), and (c) are simulated mode profiles with full cladding, with 500nm silicon dioxide cladding, and with a 200nm air gap, respectively |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

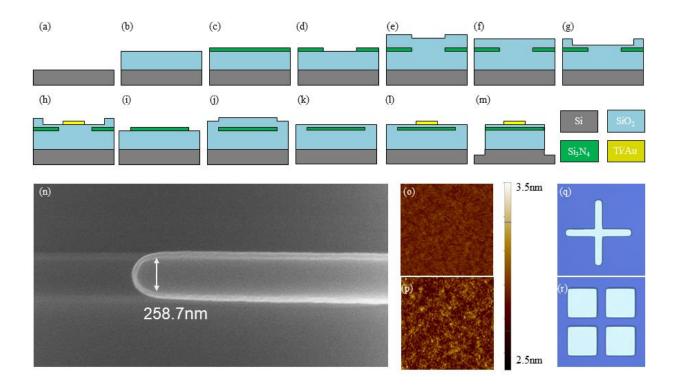

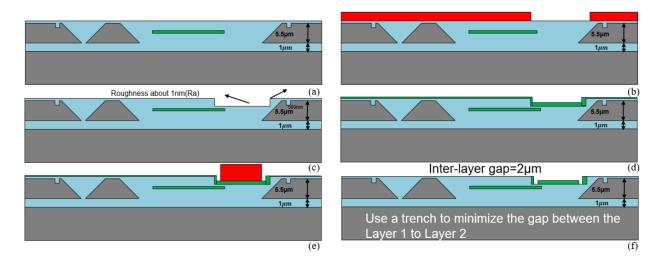

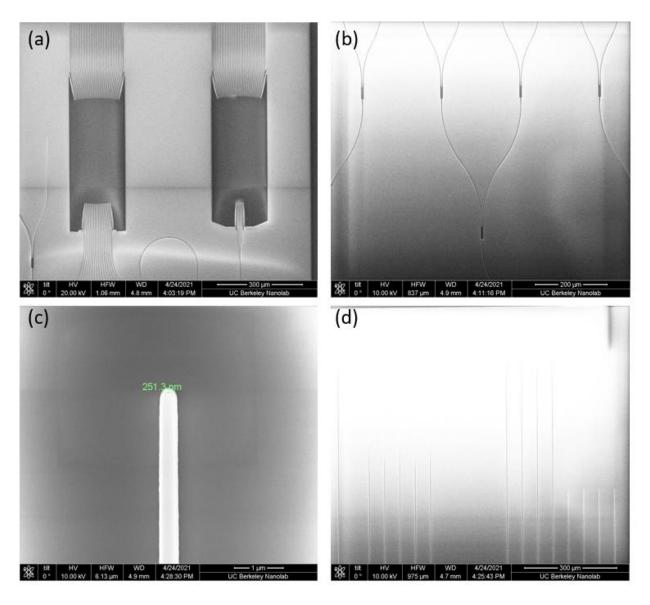

| Figure 32 Fabrication flow chart of (a) initial wafer cleaning; (b) thermal oxidation; (c) Si <sub>3</sub> N <sub>4</sub> deposition;                   |

| (d) interposer Si3N4 lithography and etching; (e) interposer LTO deposition; (f) interposer CMP; (g)                                                    |

| interposer LTO lithography and etching; (h) interposer Ti/Au lift-off; (i) flip-chip Si3N4 lithography and                                              |

| etching; (j) flip-chip LTO deposition; (k) flip-chip CMP; (l) flip-chip Ti/Au lift-off; (m) deep                                                        |

| LTO/Silicon etching, (n) SEM photo of a patterned Si3N4 taper, at the tip, (o) AFM measurement of the                                                   |

| SiO2 surface after CMP, (p) AFM measurement of the SiO2 surface inside the LTO trench after step (g),                                                   |

| (q) and (r) microscope photo of the alignment marks on the interposer and the flip-chip, respectively 56                                                |

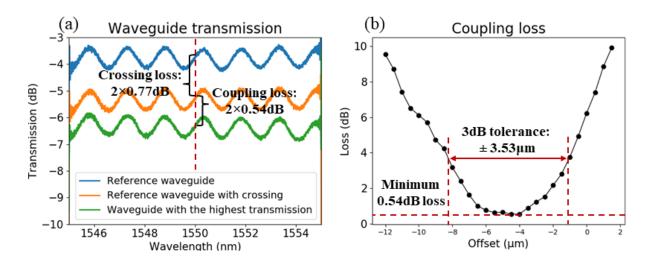

| Figure 33 (a)Measured transmission of the reference waveguides and the inter-chip coupler with the                                                      |

| highest transmission around 1550nm wavelength and (b) measured inter-chip coupling loss as a function                                                   |

| of the offset at 1550nm wavelength57                                                                                                                    |

| Figure 34 (a)Measured broadband coupling loss and (b) measured broadband crossing loss58                                                                |

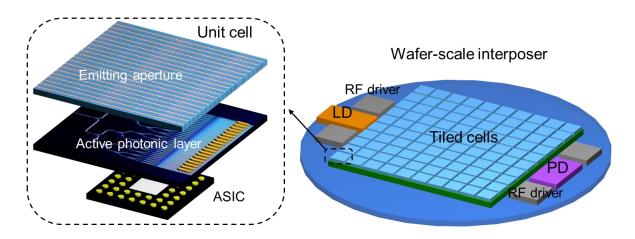

| Figure 35 Schematic of a wafer-scale LIDAR system consisting of unit cell-based 3D silicon photonic                                                     |

| chips tiling on an interposer                                                                                                                           |

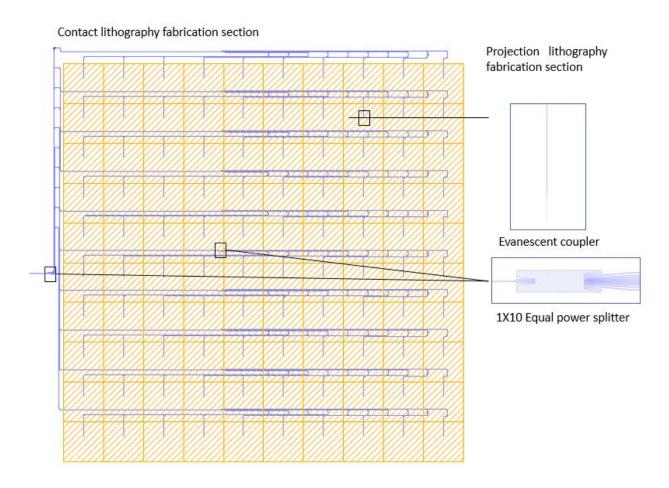

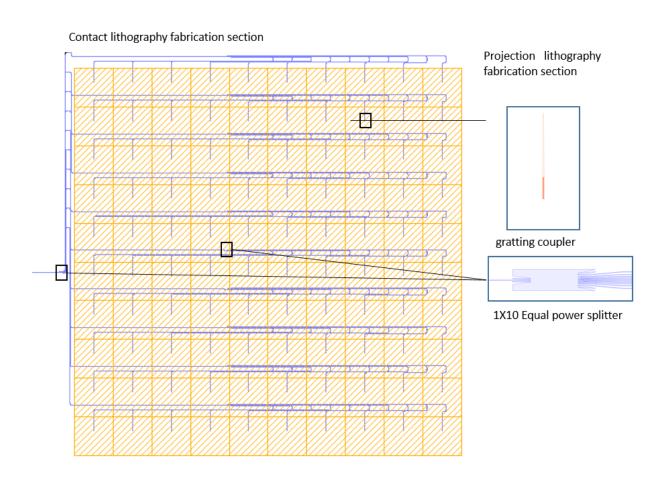

| Figure 36 The layout of a wafer-scale interposer. The size of the tiles is 10 cm x 10 cm. The Waveguide                                                 |

| section is patterned by contact lithography. An equal power splitter and inverse taper coupler are stitched                                             |

| onto the wafer by projection lithography with high resolution (<250nm)60                                                                                |

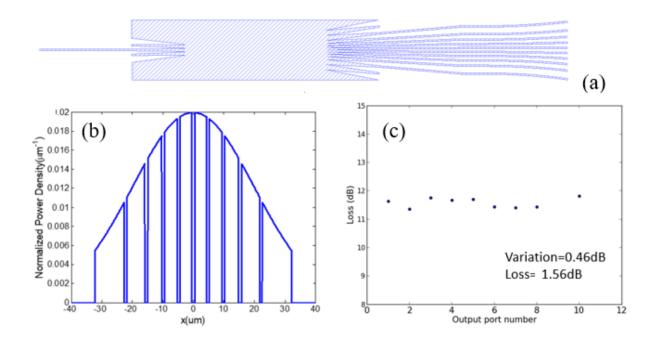

| Figure 37 (a) Layout of the equal power splitter. (b) The simulated output width and power. (c) The                                                     |

| measured output power61                                                                                                                                 |

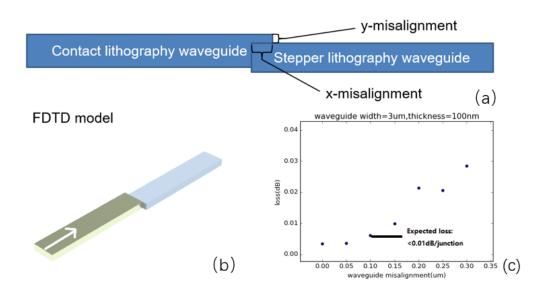

| Figure 38 (a) Diagram of waveguide stitching. (b) FDTD modal of waveguide stitch. (c) The extra loss                                                    |

| brought by waveguide mismatching62                                                                                                                      |

| Figure 39 The layout of a wafer-scale grating array64                                                                                                   |

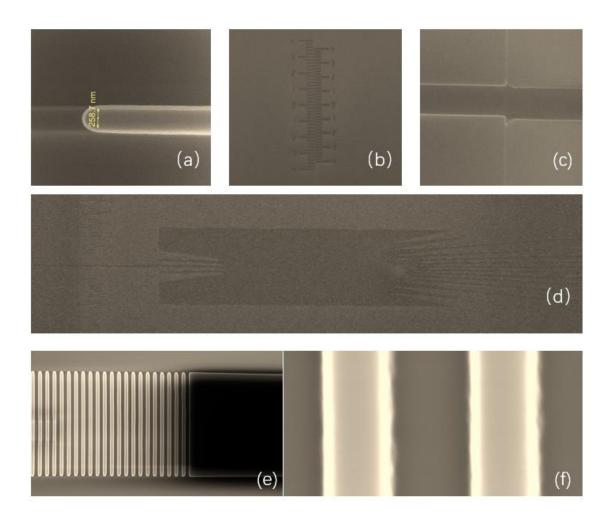

| Figure 40 SEM photo on the wafer-scale grating array. (a) Inverse taper coupler tip end. (b) Vernier ruler                                              |

| for measuring stitching misalignment. Smaller than 100nm is observed on the ruler. (c) Waveguide                                                        |

| stitching section. The waveguide width is 3µm. The left part is patterned by projection lithography, while                                              |

| the right part is patterned by contact lithography. (d) Equal power splitter. (e) Grating and bus waveguide.                                            |

| The width of the bus waveguide. The grating has a pitch of 1.2µm and a 50% duty cycle. (f) Zoom in a                                                    |

| photo of the grating. About 50% of the duty cycle is achieved by adjusting lithography energy65                                                         |

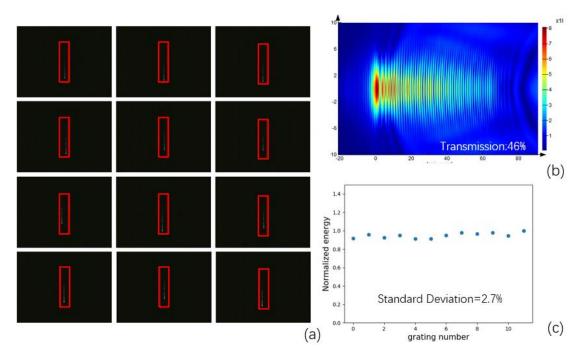

| Figure 41 (a) Wafer-scale grating array measurement results sampled at the center of a 150mm wafer. (b)                                                 |

| Simulated grating pattern. (c) Normalized output power in (a). Only energy in the red box is calculated to                                              |

| minimize noise                                                                                                                                          |

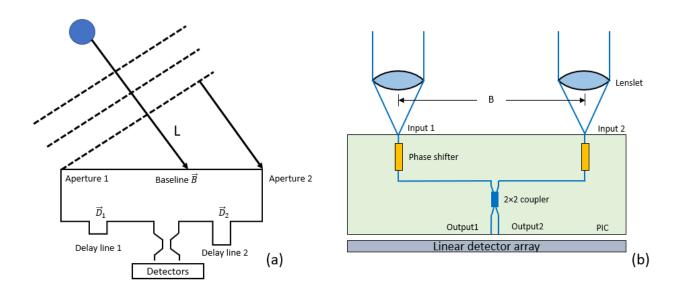

| Figure 42. (a) Interferometric imaging diagram. (b) PICs diagram in SPIDER system                                                                       |

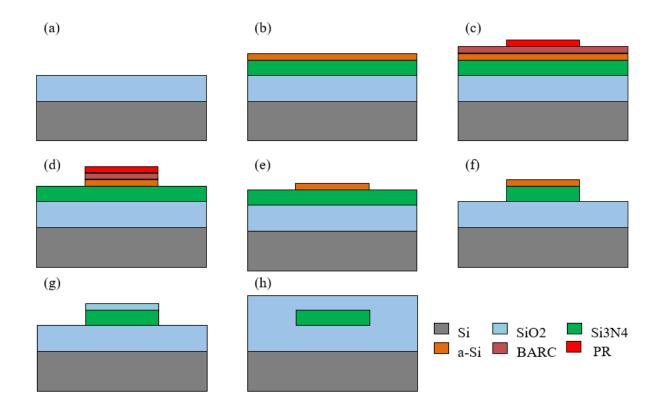

| Figure 43 Fabrication process of the low-loss silicon nitride waveguide (a) Wet oxidation. (b) Silicon                                                  |

| nitride and a-Si deposition. (c) Lithography. (d) BARC and a-Si hard mask etching. (e) Photoresist                                                      |

| removal. (f) Silicon nitride etching. (g) Wet oxidation. (h) LTO deposition                                                                             |

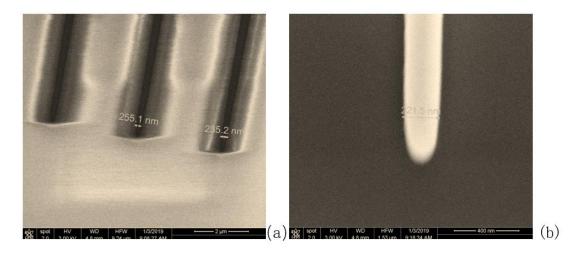

| Figure 44. SEM photo of the patterned photoresist using a 15mJ/cm <sup>2</sup> (a) at the AWG and (b) at the tip of                                     |

| the inversed taper                                                                                                                                      |

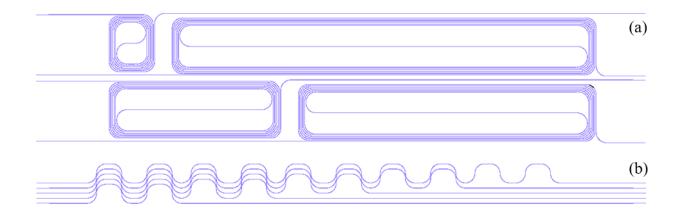

| Figure 45 Layout of the silicon nitride test structures. (a) Propagation loss testing structures. (b) Bending                                           |

| loss testing structure                                                                                                                                  |

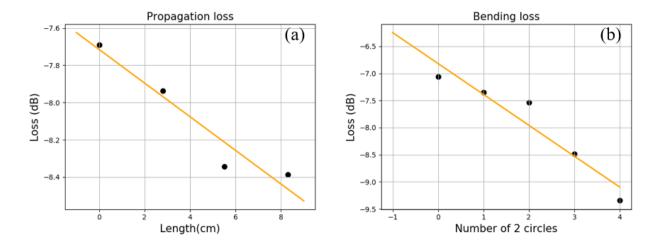

| Figure 46 (a) Measured propagation loss. (b) Measured bending loss. One circle means the waveguide                                                      |

| bend with 90° for four times                                                                                                                            |

| Figure 47 SEM photo of the patterned AWGs (a) gap between 2 inputs and (b) input region74                                                               |

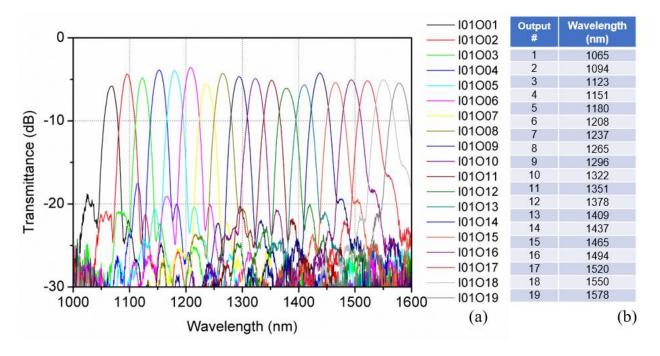

| Figure 48 (a) Transmission spectrum of the AWG (b) Channel center wavelength                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

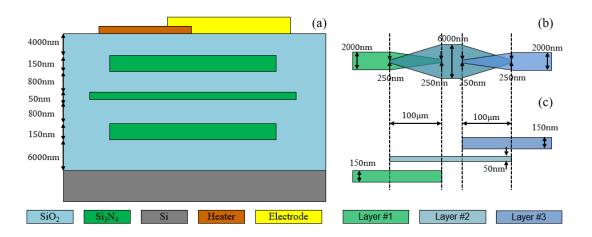

| Figure 49 (a) Cross-section view of the 3-layer Si <sub>3</sub> N <sub>4</sub> waveguide structure. (b) and (c) Top-down and                        |

| cross-section view of the inter-layer coupler in the 3-layer $Si_3N_4$ waveguide structure                                                          |

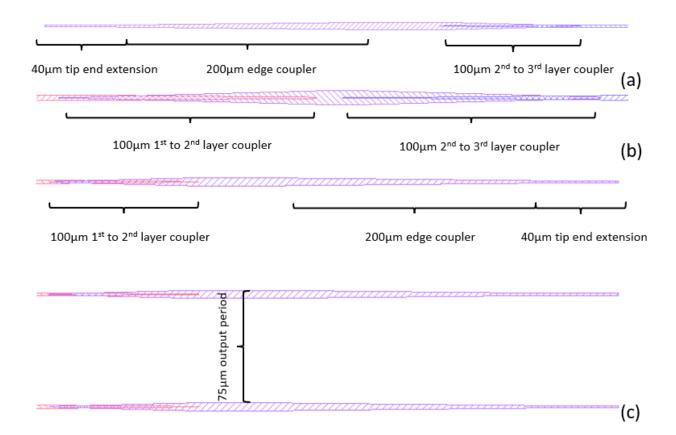

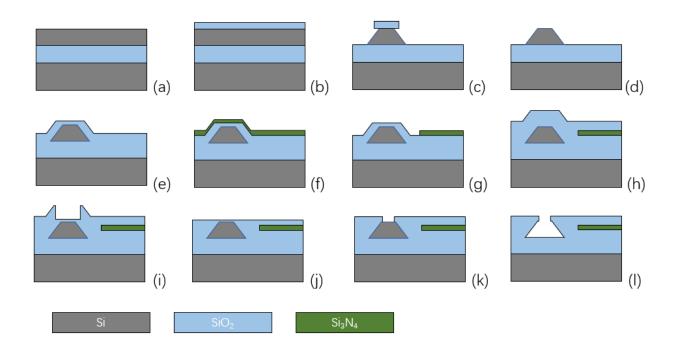

| Figure 50 Fabrication process flow of the SPIDER PICs. (a) Initial wafer cleaning for 6-inch wafers. (b)                                            |

| Thermal oxidation. (c) The bottom layer 150 nm Si <sub>3</sub> N <sub>4</sub> deposition. (d) 150 nm Si <sub>3</sub> N <sub>4</sub> patterning by   |

| lithography and etching. (e) First inter-layer $SiO_2$ deposition. (f) CMP. (g) The middle layer $50 \text{ nm } Si_3N_4$                           |

| deposition (h) 50 nm Si <sub>3</sub> N <sub>4</sub> patterning by lithography and etching. (i) Second inter-layer SiO <sub>2</sub> deposition.      |

| (j) CMP. (k) The top layer 150nm Si <sub>3</sub> N <sub>4</sub> deposition. (l) 150 nm Si <sub>3</sub> N <sub>4</sub> patterning by lithography and |

| etching. (m) Top cladding SiO <sub>2</sub> deposition. (n) CMP. (o) 20nm Ti / 100 nm Au metal heaters fabrication                                   |

| using metal lift-off. (p) 20 nm Ti / 800 nm Au metal electrodes fabrication using metal lift-off. (q) silicon                                       |

| dioxide and silicon deep etching76                                                                                                                  |

| Figure 51 Baseline configuration in the SPIDER PICs designed by Lockheed Martin77                                                                   |

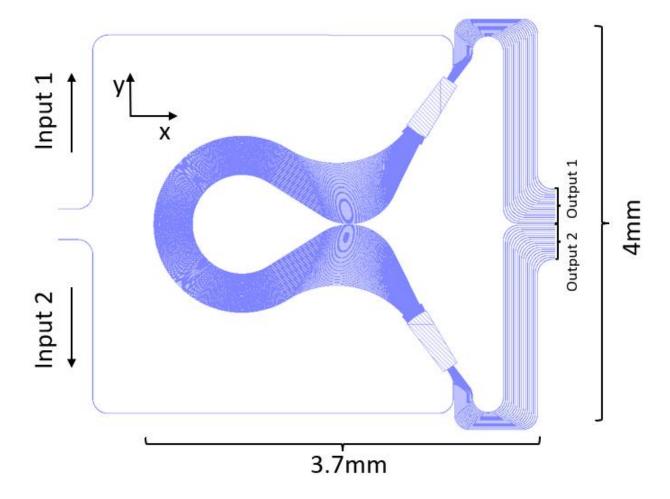

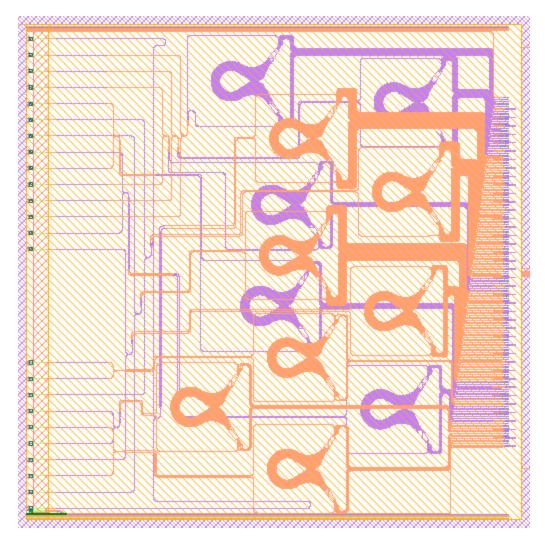

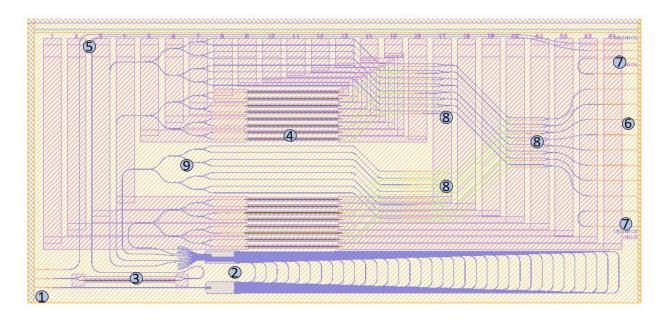

| Figure 52 (a) Layout of the SPIDER PICs. Elements are denoted with numbers: 1. AWGs at the first                                                    |

| waveguide layer. 2. AWGs at the third waveguide layer. 3. MMI. 4. Thermal phase shifter. 5. Metal ruler                                             |

| for polishing. 6. Electrode I/O. 7. Optical inputs. 8. Optical outputs. 9. Test waveguides. (b) Colors for                                          |

| different layers. (c) Metal ruler for polishing in the black box at the top right corner of (a)78                                                   |

| Figure 53 Layout of the SPIDER PICs. (a) Optical input, (b) inter-layer coupler, and (c) output array79                                             |

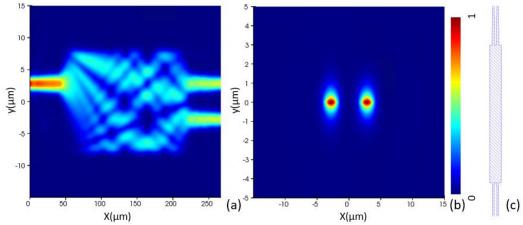

| Figure 54 Simulated E field plot of the MMI at 1500nm wavelength. (a) Top view and (b) Cross section                                                |

| view at the end of the outputs. (c) Layout for the MMI80                                                                                            |

| Figure 55 Layout of the broadband AWG                                                                                                               |

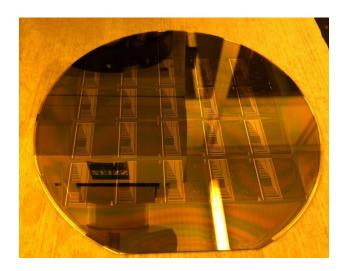

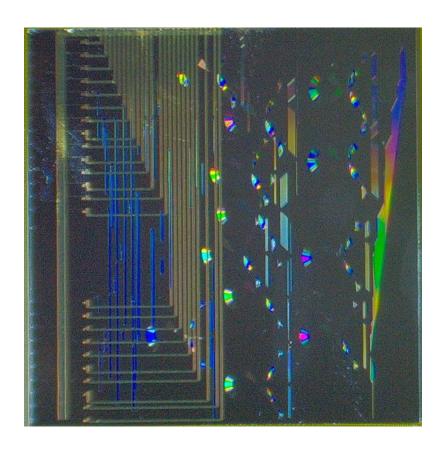

| Figure 56 Photo of the fabricated SPIDER PICs wafer                                                                                                 |

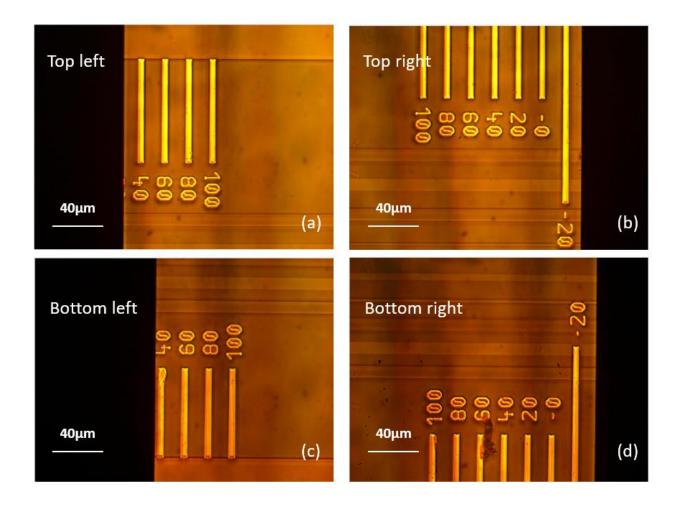

| Figure 57 Microscope photo of the PICs corners after polishing. (a) Top left corner, (b) top right corner,                                          |

| (c) bottom left corner, and (d) bottom right corner83                                                                                               |

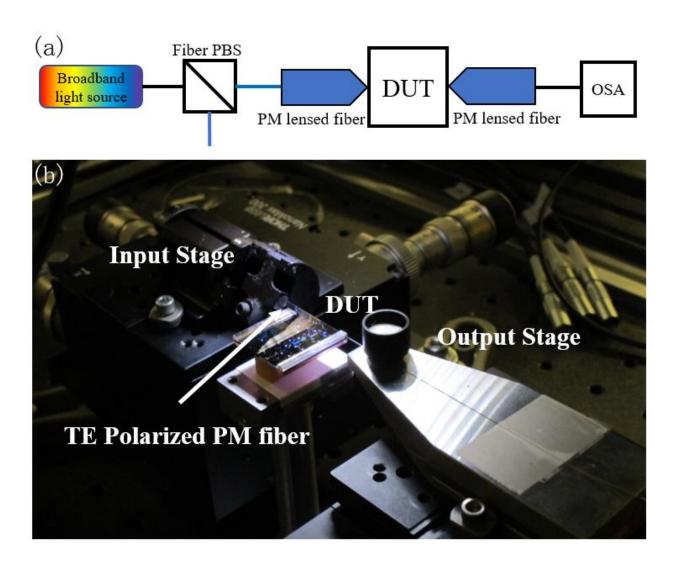

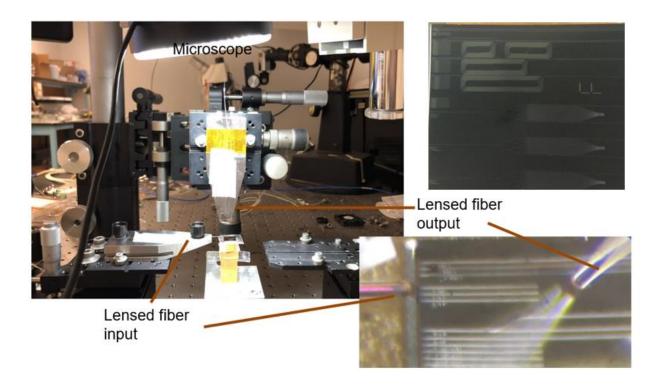

| Figure 58 (a) Diagram of the PICs measurement setup. (b) Photo of the measurement setup with a device                                               |

| under testing (DUT)84                                                                                                                               |

| Figure 59 Transmission spectrum of 6 AWGs at six chips, calibrated to the straight waveguide at the same                                            |

| layer                                                                                                                                               |

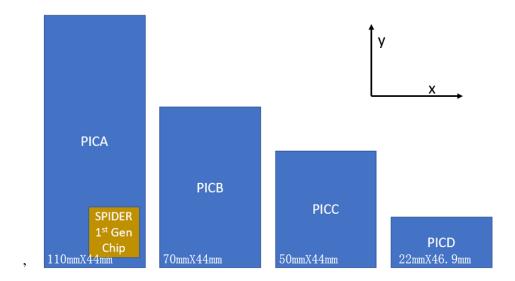

| Figure 60 Relative size of the SuperPIC PICs. The yellow square shows the size of the first-generation                                              |

| chip with a 22mm-by-22mm size                                                                                                                       |

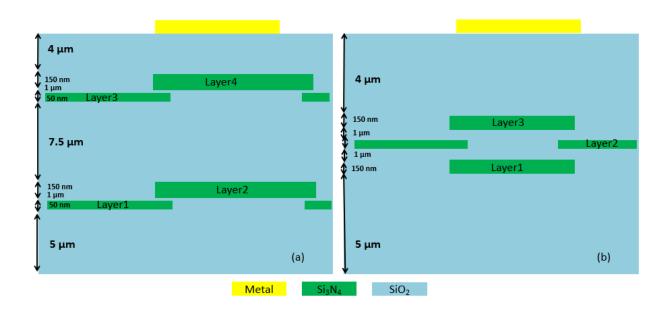

| Figure 61 Cross-section view diagram of the SuperPIC PICs. (a) PICA, B, and C. (b) PICD88                                                           |

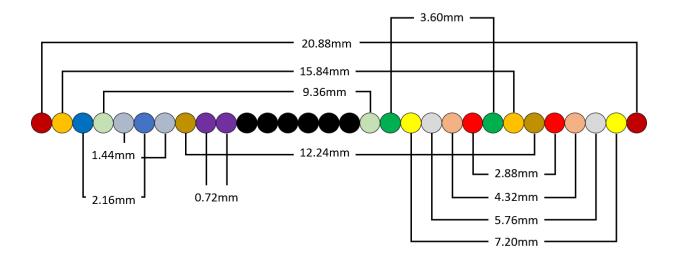

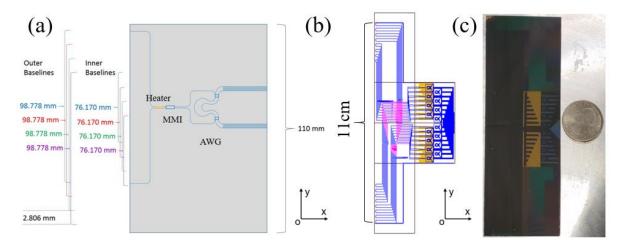

| Figure 62 (a)Top view of the Si3N4 PICs with baseline length and locations. (b) The layout of the Si3N4                                             |

| PICs. (c) A photo of the PIC.                                                                                                                       |

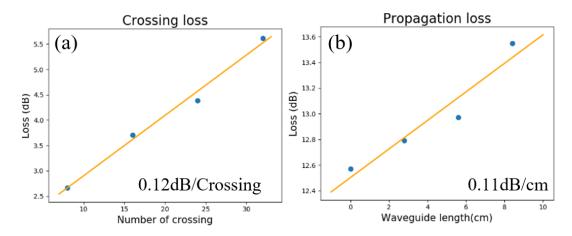

| Figure 63 (a)Measured waveguide crossing loss on 50nm Si3N4 layers. (b) Measure waveguide                                                           |

| propagation loss on 150nm Si3N4 layers90                                                                                                            |

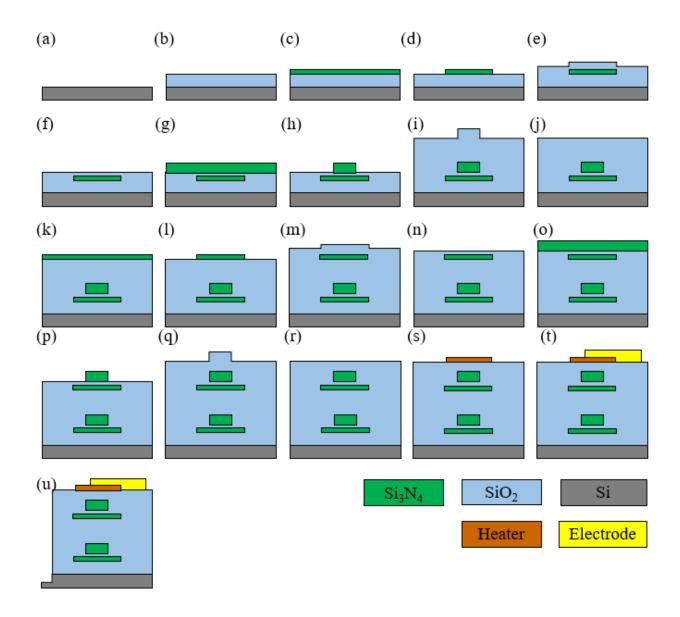

| Figure 64 Fabrication process of the SPIDER SuperPIC PICA, B and C. (a) Initial wafer cleaning for 6-                                               |

| inch wafers. (b) Thermal oxidation. (c) The 1st layer is 50 nm Si3N4 deposition. (d) 50 nm Si3N4                                                    |

| patterning by lithography and etching. (e) First inter-layer $SiO_2$ deposition. (f) CMP. (g) The $2^{nd}$ layer $150$                              |

| nm Si3N4 deposition (h) 150 nm Si3N4 patterning by lithography and etching. (i) Second inter-layer $SiO_2$                                          |

| deposition. (j) CMP. (k) The 3 <sup>rd</sup> layer 50nm Si3N4 deposition. (l) 50 nm Si3N4 patterning by lithography                                 |

| and etching. (m) Inter-layer $SiO_2$ deposition. (n) CMP. (o) The $4^{th}$ layer 150nm $Si3N4$ deposition. (p) 150                                  |

| nm Si3N4 patterning by lithography and etching. (q) Top cladding SiO <sub>2</sub> deposition. (r) CMP. (s) 20nm Ti                                  |

| / 100 nm Au metal heaters fabrication using metal lift-off. (t) 20 nm Ti / 800 nm Au metal electrodes                                               |

| fabrication using metal lift-off. (u) silicon dioxide and silicon deep etching                                                                      |

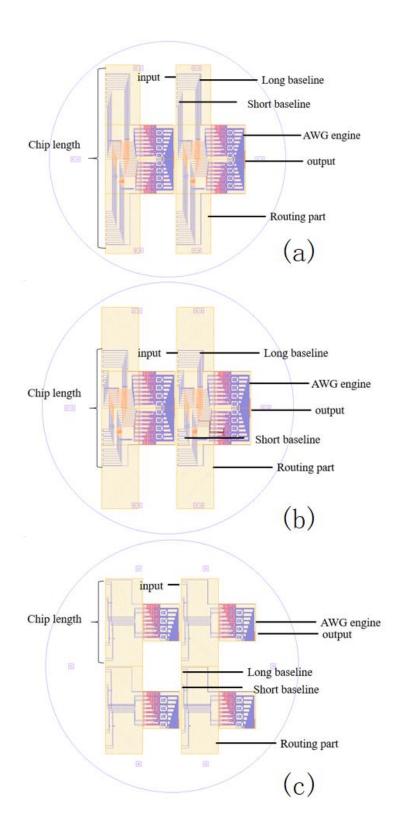

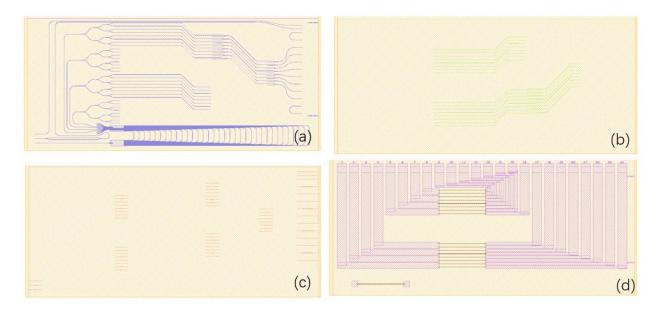

| Figure 65 Layout of the SuperPIC PICs. (a) PICA, (b) PICB and (c) PICC. The blue circles show the size                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| and location of 6-inch wafers. Yellow boxes show the size and location of the dies. Purple boxes around                                          |

| the edge of the dies are alignment marks region94                                                                                                |

| Figure 66 Layout of the PICD95                                                                                                                   |

| Figure 67 Layout of the Super PICs PICA at the bottom set. (a) Vernier ruler for alignment between tiles.                                        |

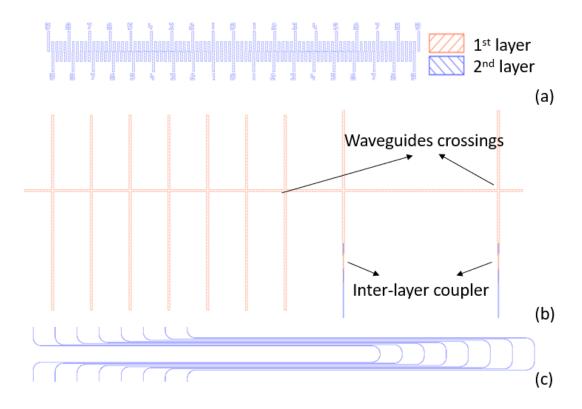

| (b) Waveguide crossings and inter-layer couplers. (c) Waveguides for path length matching96                                                      |

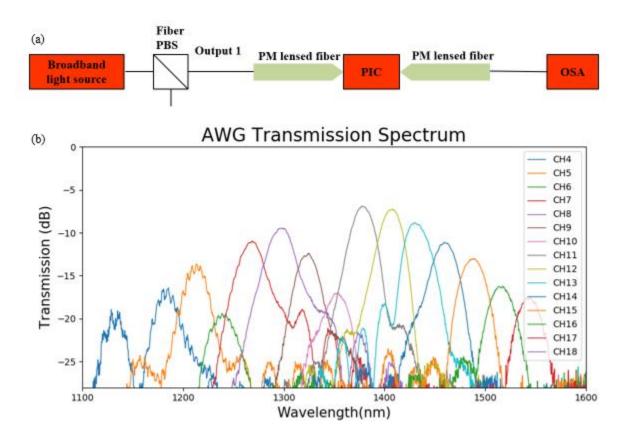

| Figure 68 (a)Diagram of the PICs measurement setup. (b)Measured waveguide crossing loss on 50nm                                                  |

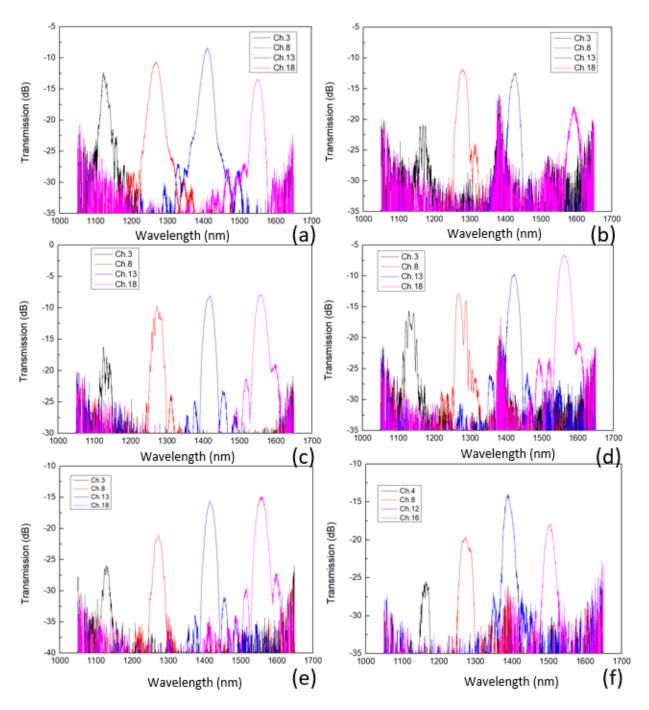

| Si <sub>3</sub> N <sub>4</sub> layers. (c) Measure waveguide propagation loss on 150nm Si <sub>3</sub> N <sub>4</sub> layers. (d)Measured 3.3THz |

| AWG transmission spectrum97                                                                                                                      |

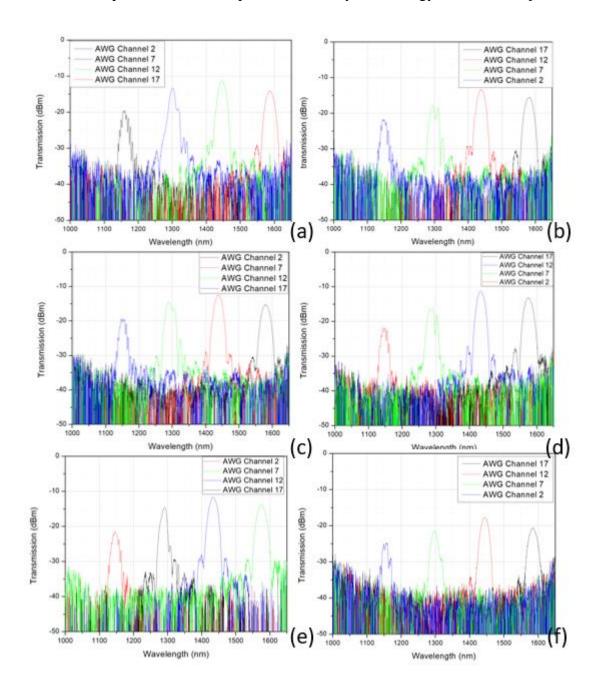

| Figure 69 Transmission spectrum of the SuperPIC PICs (a) PICB bottom set, (b) PICB top set, (c) PICC                                             |

| bottom set, (d) PICC top set, (e) PICD bottom set and (f) PICD top set                                                                           |

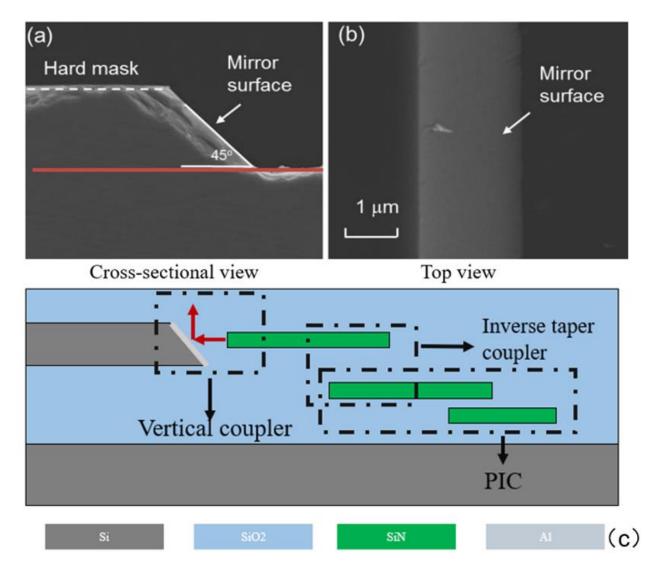

| Figure 70 Diagram of the surface coupler based on a 45° mirror. The surface coupler is fabricated on                                             |

| (a)Side view of silicon 45° wet etching. (b) Top view of silicon 45° wet etching. (c) Diagram of the                                             |

| surface coupler based on a 45° mirror. The surface coupler is fabricated on top of a PIC. Light transmits                                        |

| in and out through the surface coupler and is coupled into the PIC by the inverse taper coupler 102                                              |

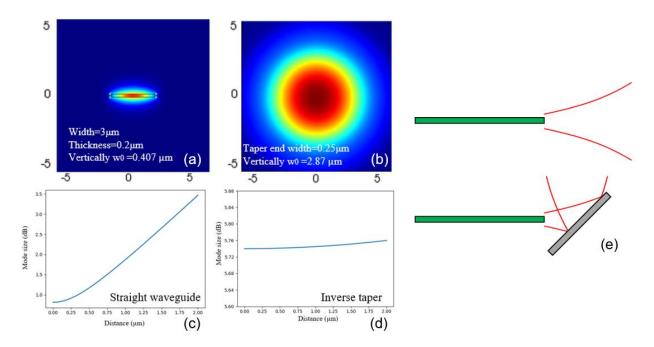

| Figure 71 (a) Mode profile of a silicon nitride waveguide without taper. (b) Mode profile of a silicon                                           |

| nitride waveguide with taper. (c) and (d) Output mode size in vertical direction with the variation of the                                       |

| distance. (d) Diagram of the surface coupler with the silicon nitride waveguide103                                                               |

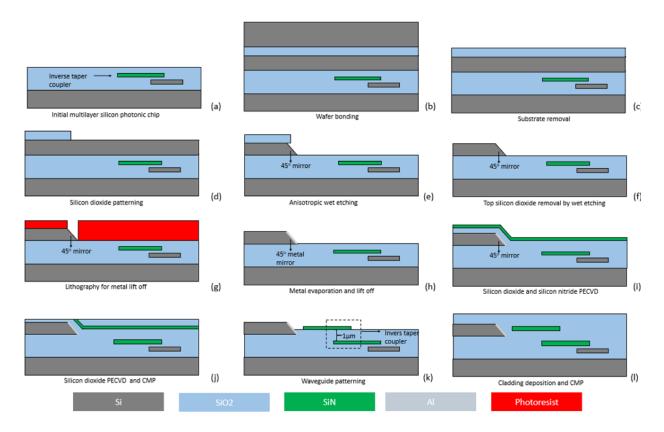

| Figure 72 (a) Substrate silicon photonics integrated chip top surface planarization. (b) SOI wafer bonding.                                      |

| (c) Substrate removal by grinding. (d) silicon dioxide patterning. (e) 45° anisotropic wet etching. (f) Top                                      |

| silicon dioxide removal by wet etching. (g) Lithography for the metal mirror. (h) Metal evaporation and                                          |

| lift-off. (i) Silicon dioxide and silicon nitride PECVD. (j) Silicon dioxide PECVD and CMP. (k)                                                  |

| Waveguide patterning. (1) Cladding deposition and CMP                                                                                            |

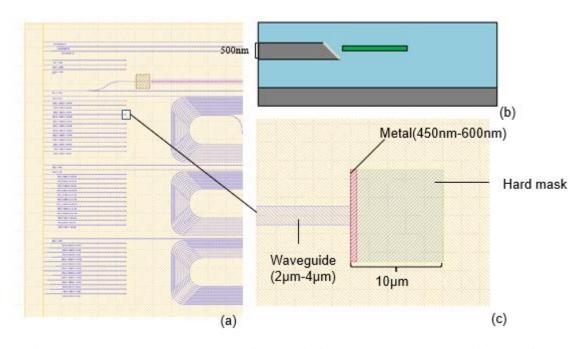

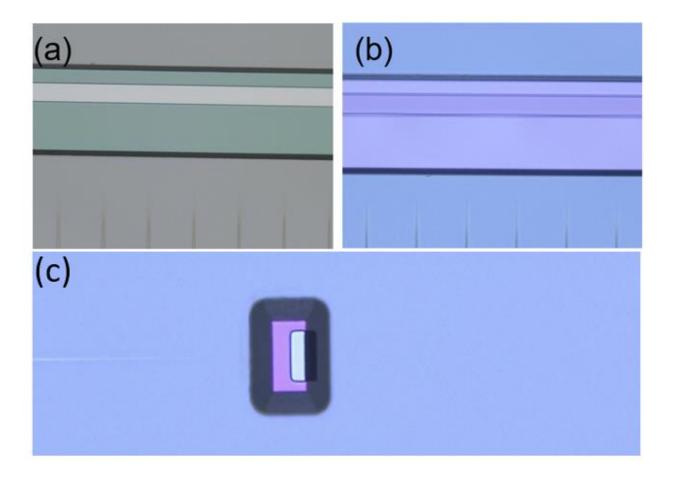

| Figure 73 (a) and (c) Mask layout of a proof-of-concept demonstration of the surface coupler. (b)                                                |

| Diagram of the surface coupler proof-of-concept demonstration                                                                                    |

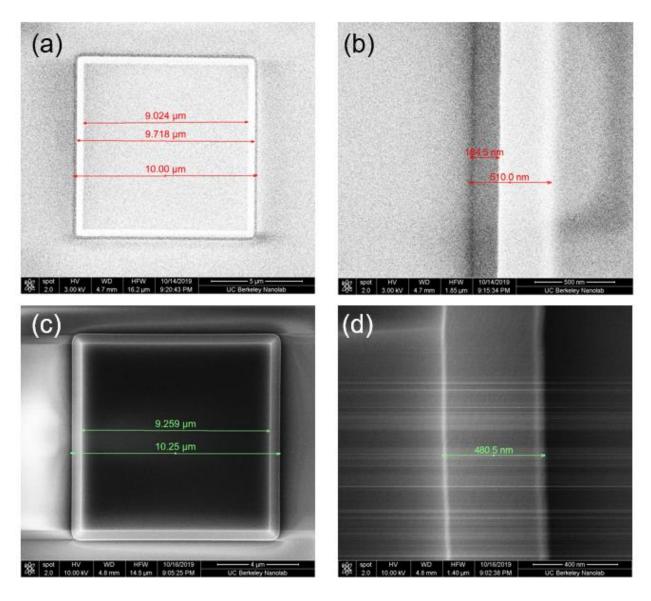

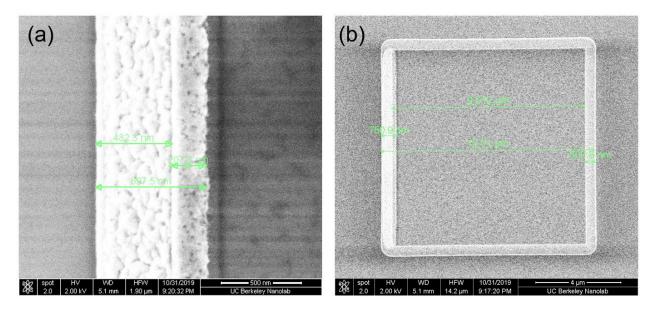

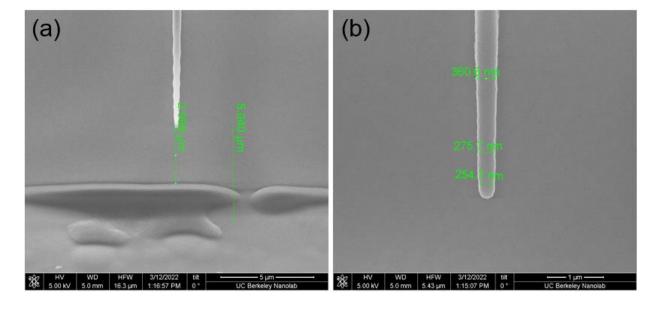

| Figure 74 (a) and (b) SEM photos of the silicon block after Si anisotropic etching. (c) and (d) SEM photos                                       |

| of the silicon block after the hard mask removal                                                                                                 |

| Figure 75 SEM photos of the silicon block after metal deposition. (a) A Zoom-in photo, and (b) A Zoom-                                           |

| out photo                                                                                                                                        |

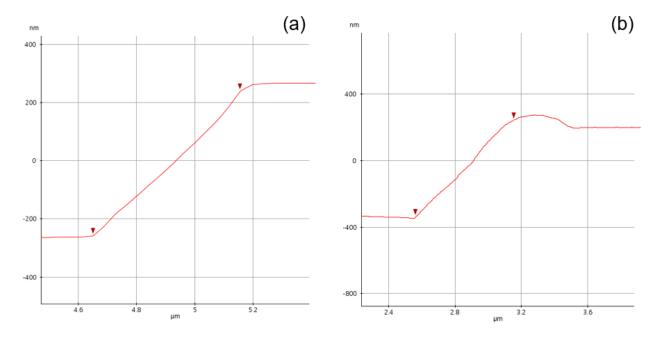

| Figure 76 AFM photo of the 45° slope (a) after hard mask removal and (b) after deposition. The angles                                            |

| between the two cursors in (a) and (b) are 44.4 and 44.6 degrees, respectively                                                                   |

| Figure 77 (a) AFM photos of the deposited Al, with 1.619nm surface roughness. (b) AFM photo of the                                               |

| SiO <sub>2</sub> bottom cladding after hard mask removal, with a 0.145nm surface roughness                                                       |

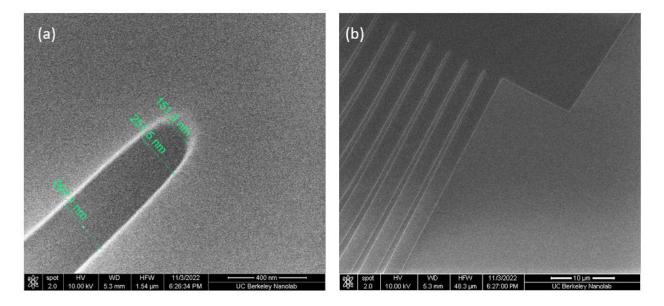

| Figure 78 SEM photo of the silicon nitride waveguide at the mirror (a) zoom in and (b) zoom out 111                                              |

| Figure 79 Measurement setup of the surface coupler. The photo of the chip is shown at the top right                                              |

| corner                                                                                                                                           |

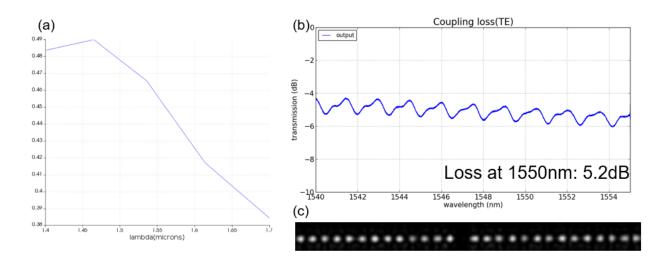

| Figure 80 (a) Simulated transmission of the surface coupler. (b) measured coupling loss of the surface                                           |

| coupler to a lensed fiber. (c) Photo of the reflector arrays                                                                                     |

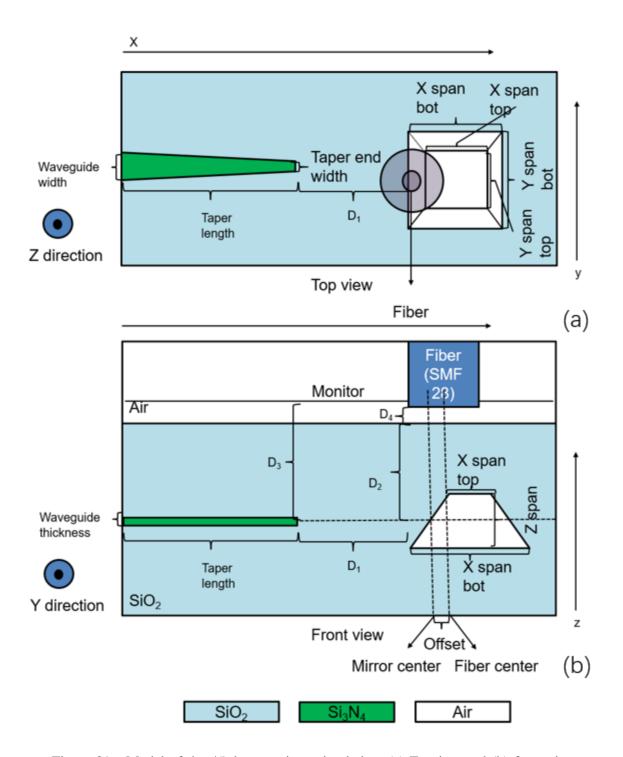

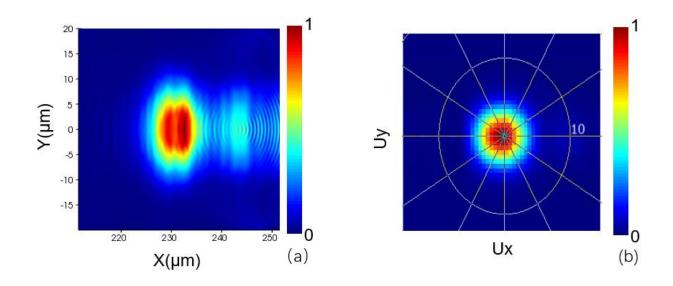

| Figure 81 Modal of the 45-degree mirror simulation. (a) To view and (b) front view, respectively. Light                                          |

| comes from the left side in the silicon nitride waveguide, which is transmitted and expanded through a                                           |

| tapered waveguide and is reflected by a 45-degree mirror                                                                                         |

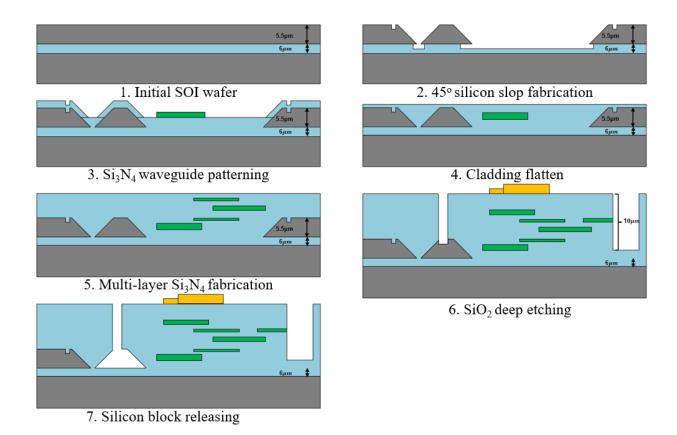

| Figure 82 Fabrication process of the surface coupler. (a) SOI wafer cleaning. (b) SiO2 hard mask                                                 |

| deposition. (c) 45-degree anisotropic wet etching. (d) SiO2 hard mask removal using BOE wet etching. (e)                                         |

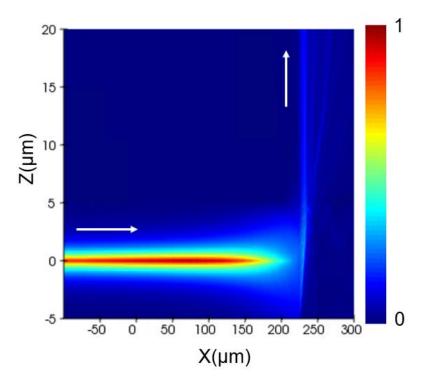

| SiO2 bottom cladding deposition. (f) Si3N4 deposition. (g) Si3N4 waveguide patterning using lithography and dry etching. (h) SiO2 top cladding deposition. (i) Inverse etching for CMP. (j) CMP. ((k) Silicon dioxide window opening using lithography and dry etching. (l) $XeF_2$ etching |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -3.82dB. The 3dB tolerance is around 7μm. 118                                                                                                                                                                                                                                               |

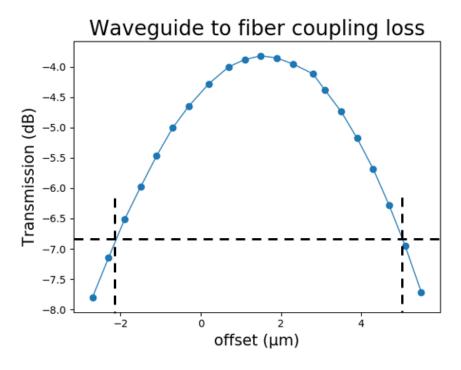

| Figure 86 (a) Microscope photo of the Si pyramid blocks. (b) and (c) SEM photos of the Si pyramid                                                                                                                                                                                           |

| blocks                                                                                                                                                                                                                                                                                      |

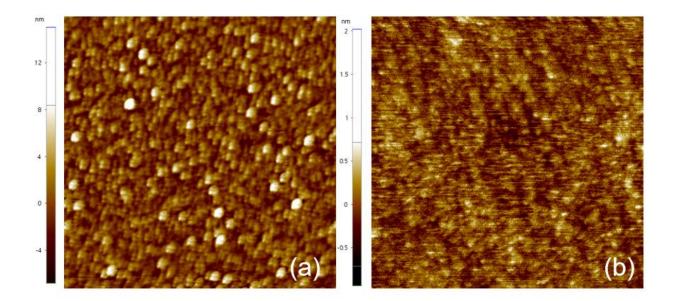

| Figure 87 (a) AFM photos of a $5\mu m$ HTO. (b) AFM photo of a $5\mu m$ LTO                                                                                                                                                                                                                 |

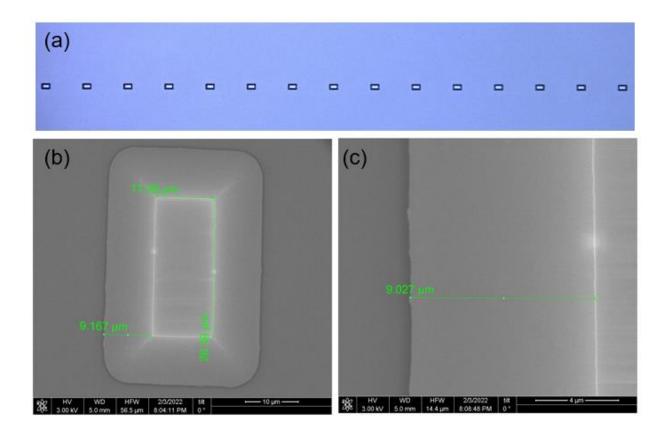

| Figure 88 (a) and (b) SEM photo of the inversed taper after waveguide lithography                                                                                                                                                                                                           |

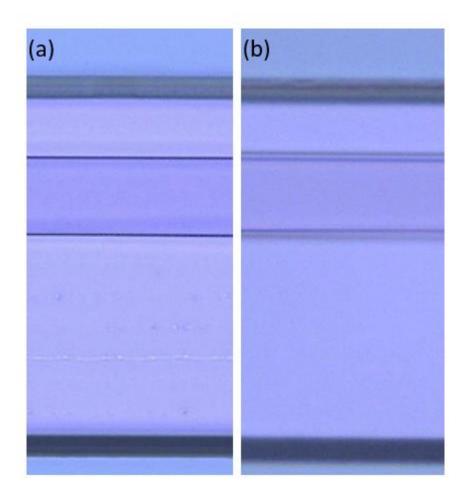

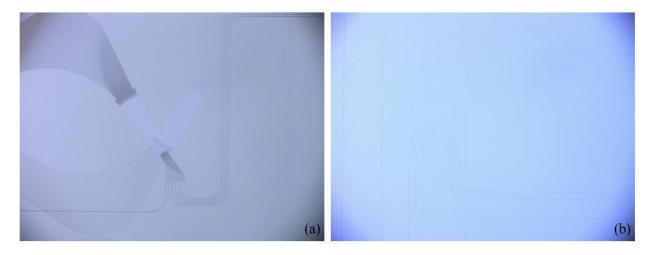

| Figure 89 (a) Microscope photo before the Si removal. (b) Microscope photo after the Si removal. (c)                                                                                                                                                                                        |

| Microscope photo of the pyramid voided with $Si_3N_4$ taper                                                                                                                                                                                                                                 |

| Figure 90 Microscope photo of the SiO <sub>2</sub> membrane (a) before HF cleaning and (b) after HF cleaning 123                                                                                                                                                                            |

| Figure 91. Diagram of the SPIDER imaging PICs using the surface coupler based on 45° mirrors 125                                                                                                                                                                                            |

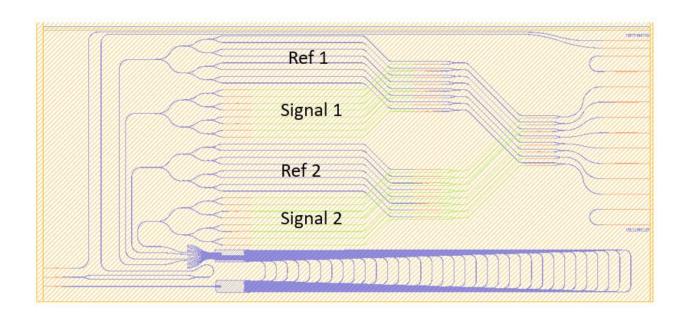

| Figure 92. The layout of the PICs for interferometric imaging                                                                                                                                                                                                                               |

| Figure 93. Simulated coupling loss of a pair of inter-layer couplers with (a) 300µm taper length and (b)                                                                                                                                                                                    |

| 500µm taper length. The waveguides on the two layers have 150nm and 50nm thicknesses, respectively.                                                                                                                                                                                         |

| Figure 94. The fabrication process of the SPIDER imaging PICs using the surface coupler129                                                                                                                                                                                                  |

| Figure 95. Fabrication process for the 2nd silicon nitride layer                                                                                                                                                                                                                            |

| Figure 96. Microscope photo of the (a) Zoom in and (b) Zoom out photo of the silicon block with waveguides                                                                                                                                                                                  |

| Figure 97. Microscope photo of the (a) AWGs and (b) routing regions                                                                                                                                                                                                                         |

| Figure 98. Photo of the SPIDER imager using a surface coupler                                                                                                                                                                                                                               |

| Figure 99. (a) Measured inter-layer coupling loss and (b) measured coupling loss of the surface coupler to                                                                                                                                                                                  |

| a cleaved single-mode fiber                                                                                                                                                                                                                                                                 |

| Figure 100. Measured AWG transmission spectrum.                                                                                                                                                                                                                                             |

| Figure 101. Photo and schematic of the fringe measurement setup                                                                                                                                                                                                                             |

| • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                     |

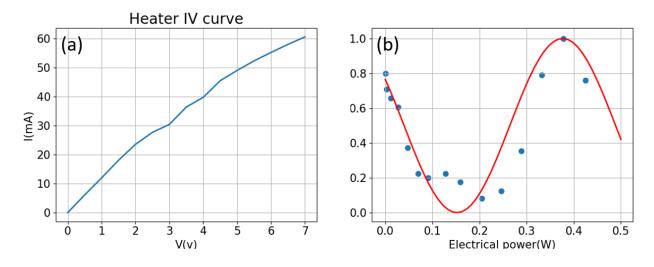

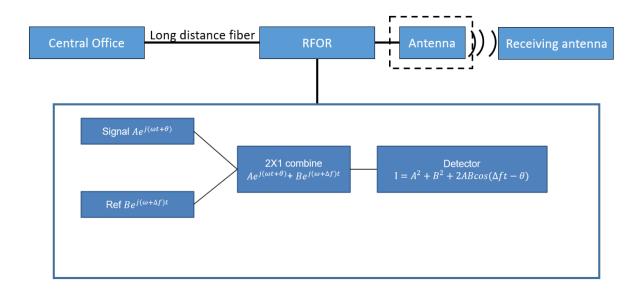

| Figure 102. (a) Measured IV curve of the heater and (b) measured fringe at 1550nm wavelength 133 Figure 103 Diagram of ROF and ERON PPU. Signals are generated and modulated in the central office                                                                                          |

| and propagate along a long fiber, like any long-distance fiber communication system. RFOR receives an                                                                                                                                                                                       |

| input signal, combines it with a local signal, and turns it into an RF signal. The function of an antenna can                                                                                                                                                                               |

| be integrated into the RFOR.                                                                                                                                                                                                                                                                |

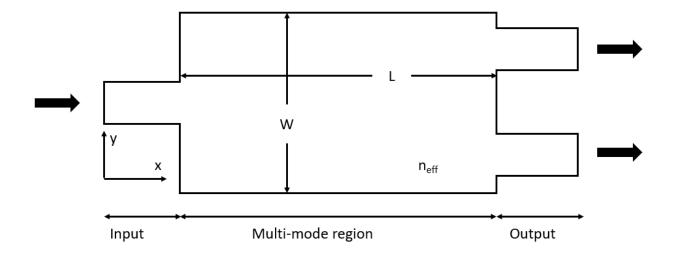

| Figure 104 2D schematic of a 1×2 MMI. Black arrows denote the beam transmission                                                                                                                                                                                                             |

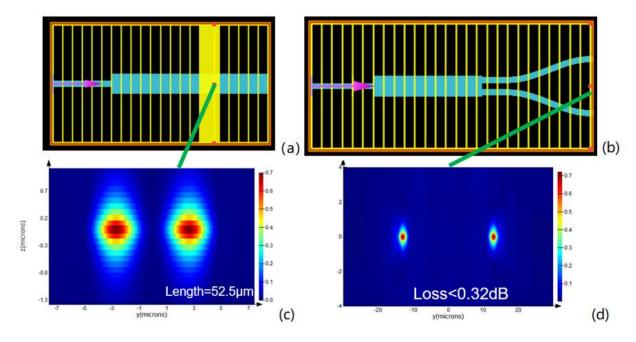

| Figure 104 2D schemate of a 1×2 MMI. Black arrows denote the beam transmission                                                                                                                                                                                                              |

| respectively. The green line denotes the position of the field monitor. The focal length in (b) and (d) is                                                                                                                                                                                  |

| 52.5μm. The width of the multimode region is 10μm. All simulation is at 1.55 μm wavelength139                                                                                                                                                                                               |

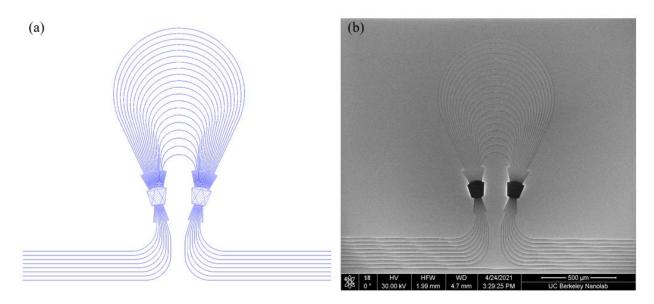

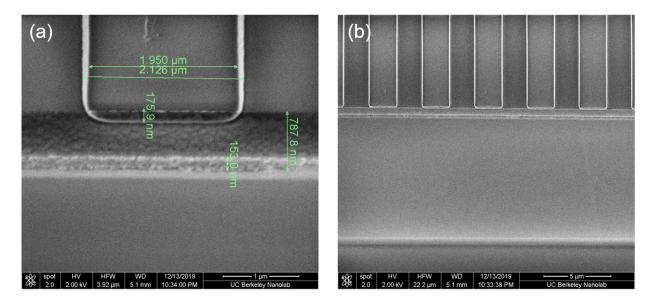

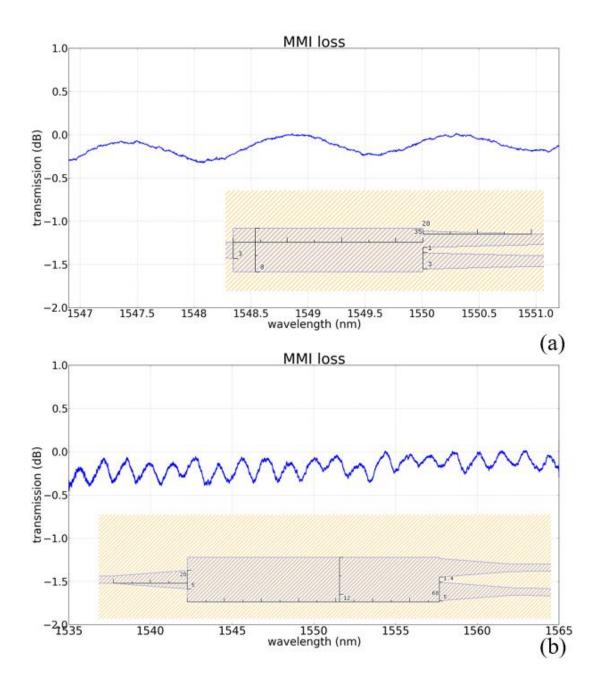

| Figure 106 (a) Layout of an MMI tree with 3 MMIs. (b) SEM photo of an MMI after device patterning. (c)                                                                                                                                                                                      |

| Zoom in SEM photo of an MMI after device patterning                                                                                                                                                                                                                                         |

| Figure 107 Measured MMI insertion loss with the layout. (a) Small size design and (b) large size design  141                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

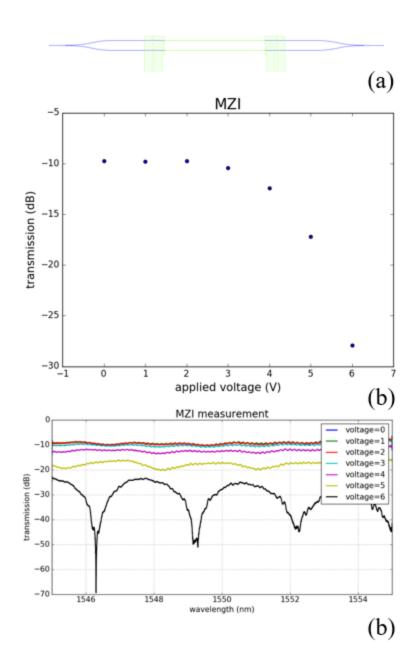

| Figure 108 (a) Layout of an MZI. Blue structures are waveguides, and green structures are metal for heating and controlling. (b) Measured MZI transmission with a variable applied voltage at 1550nm wavelength, calibrated to a fiber-to-fiber loss. (c) Measured MZI transmission spectrum with a variable applied voltage around 1550nm wavelength, a fiber-to-fiber loss                                                                        |

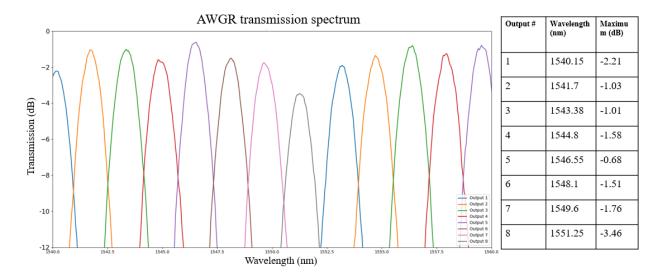

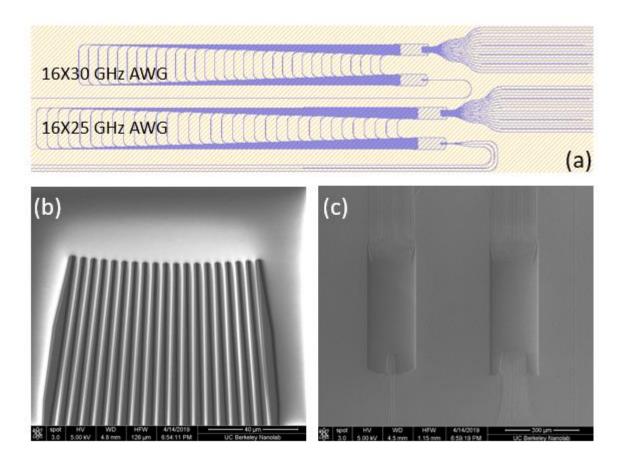

| Figure 109 (a) Layout of a 16-channel, 25GHz channel spacing AWG and layout of a 16-channel, 30GHz channel spacing AWG. (b) SEM photo of the AWG after photoresist patterning. (c) SEM photo of the AWG after device patterning                                                                                                                                                                                                                     |

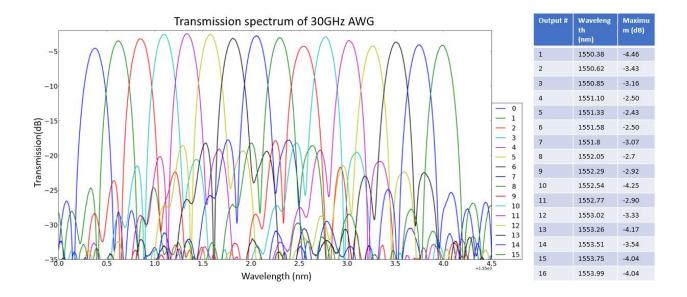

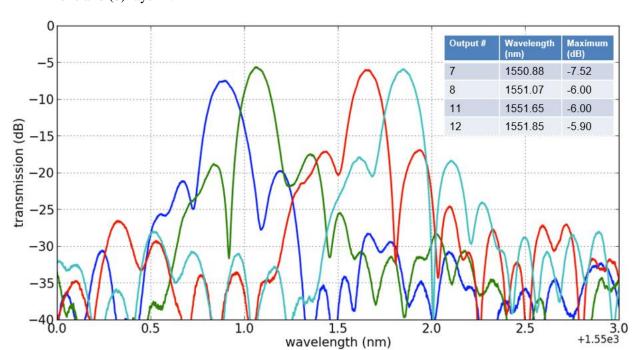

| Figure 110 Transmission spectrum of the 16 channel, 25GHz channel spacing AWG calibrated to a straight waveguide, with center wavelength and insertion loss of each channel shown on the right side.146 Figure 111 Transmission spectrum of the 16 channel, 30GHz channel spacing AWG calibrated to a                                                                                                                                               |

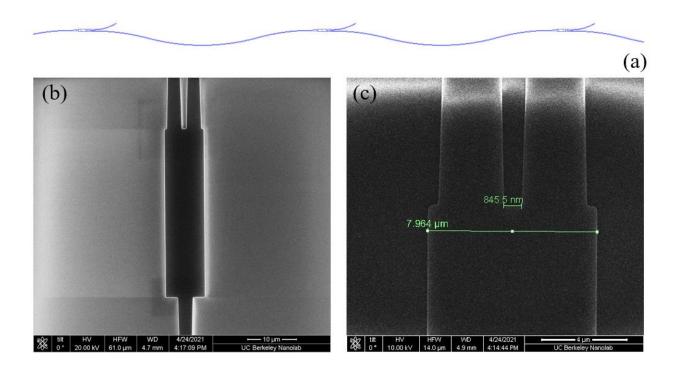

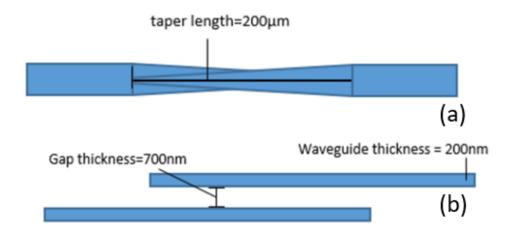

| straight waveguide, with center wavelength and insertion loss of each channel shown on the right side.147 Figure 112 Diagram of the inter-layer coupler (a) top view and (b) cross-section view                                                                                                                                                                                                                                                     |

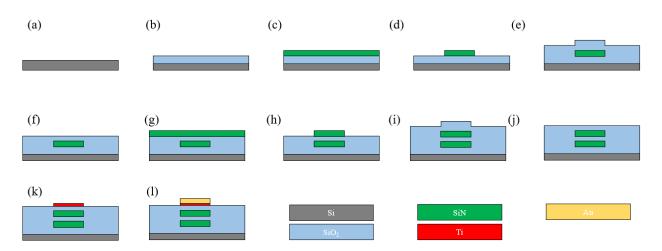

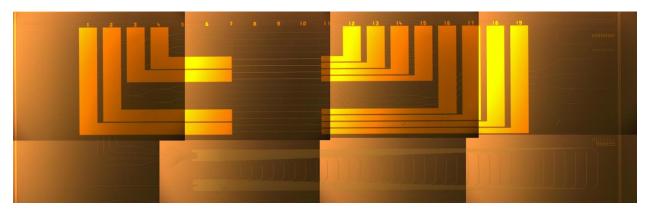

| Figure 114 Fabrication flow chart of ERON device. (a) Starting 6 in silicon wafer. (b) Wet thermal oxidation. (c) 200nm thick Si3N4 first layer LPCVD. (d) Si3N4 first layer lithography and etching. (e) LTO inter-layer deposition. (f) CMP. (g) 200nm thick Si3N4 second layer LPCVD. (h) Si3N4 second layer lithography and etching. (i) LTO top cladding deposition. (j) CMP. (k) Ti evaporation and lift-off. (l) Au evaporation and lift-off |

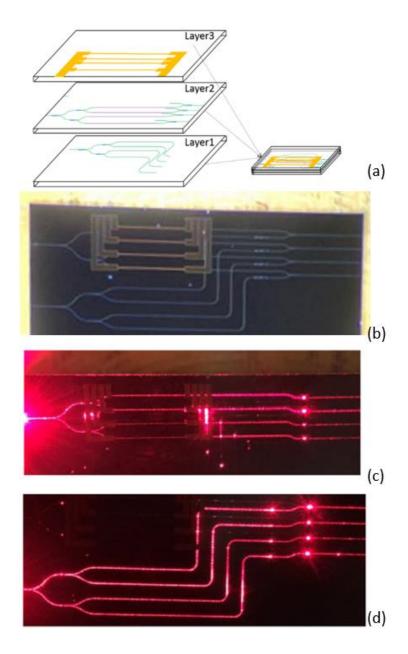

| Figure 115 (a) Each layer design layout of the SiN PIC for ERON PPU. Yellow: Metal wire and pad. Purple: Optical phase shifter. Blue: MMI optical coupler. Green: SiN optical waveguide. (b) Photo of the fabricated chip (c) and (d) photo of PIC with red light coupled into, at signal and reference layer, respectively                                                                                                                         |

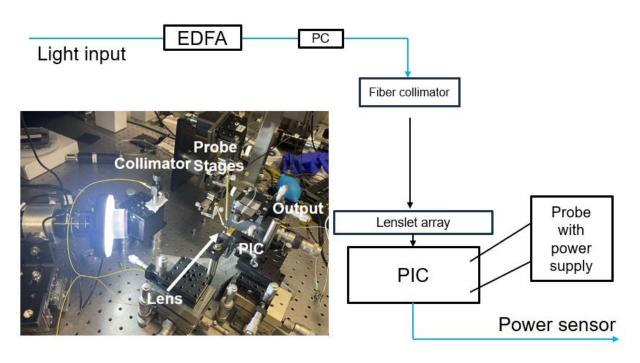

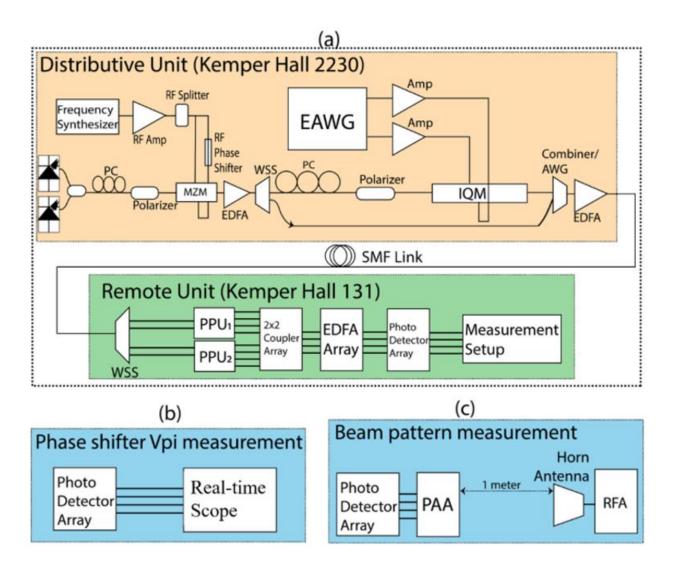

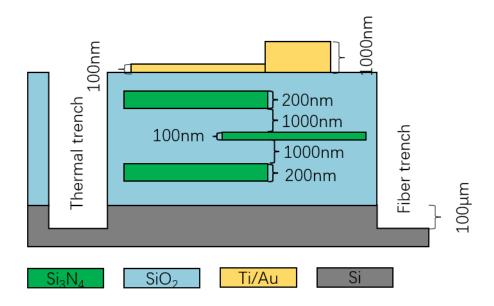

| Figure 116 (a) The ERON DU-RU experimental setup. (b) The phase shifter measurement setup. (c) The far-field beam pattern measurement setup                                                                                                                                                                                                                                                                                                         |

| Figure 117 (a) Measured phase change as a function of the applied voltage of the phase shifter. (b) Measured far-field beam pattern from a single PCB phased array antenna at 24 GHz. (c) Measured optical front-end BER as a function of the OSNR for 1-GHz QPSK and 16-QAM signal                                                                                                                                                                 |

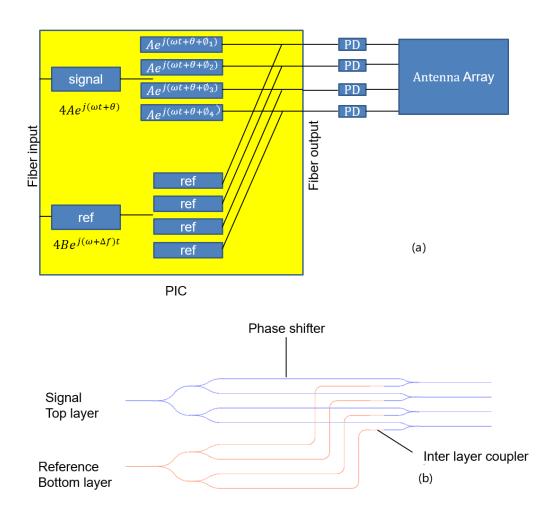

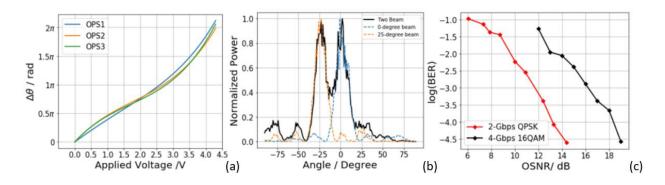

| then each signal is split into eight waveguides for both signal channel and reference channel. A tunable phase shift is added onto each signal waveguide. Then, each signal is combined with its corresponding reference channel. Then the 2 signal channels will be combined into eight waveguides and connected to                                                                                                                                |

| PDs using a fiber array. The optical signal is converted to an electrical signal at the PD and fed into a         | n      |

|-------------------------------------------------------------------------------------------------------------------|--------|

| antenna array to realize beamforming                                                                              | . 156  |

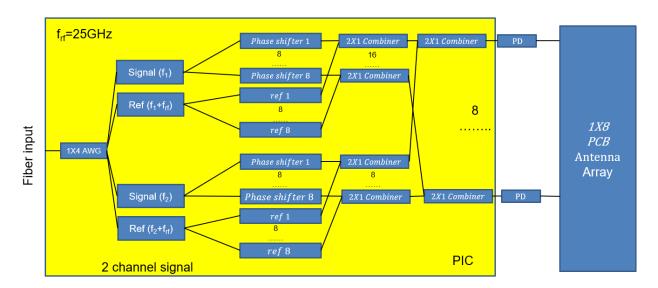

| Figure 119 Diagram of the 2 <sup>nd</sup> generation ERON PPU platform. The silicon nitride platform consists of  | of 3   |

| silicon nitride layers and two metal layers for thermal tuning. Layer 1 and 3 are function layers, while          | ;      |

| layer 2 is a transition layer. Trenches for accommodating fibers and thermal isolation are fabricated or          | n the  |

| wafer using a silicon deep etching.                                                                               | . 158  |

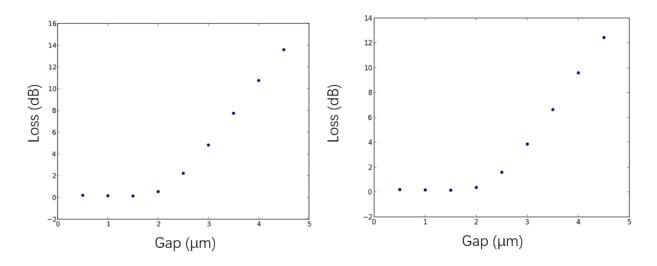

| Figure 120 (a) Simulated waveguide crossing loss as a function of gap thickness with different waveg              | uide   |

| widths. (b) Inter-layer coupling loss as a function of gap thickness.                                             | . 158  |

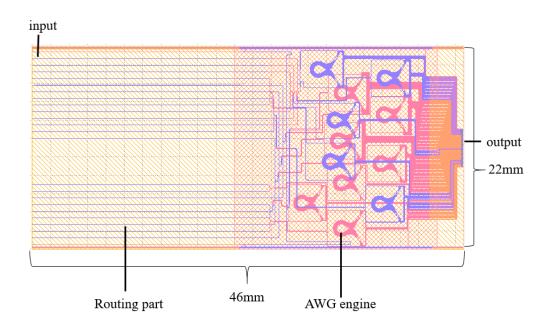

| Figure 121 Layout of the 2 <sup>nd</sup> generation ERON PPU. Elements are denoted with numbers: 1. Optical       | input  |

| 2.25GHz channel spacing AWG, 3. test MZI, 4. thermal phase shifters, 5. electrodes, 6. optical output             | ts, 7. |

| reference loops, 8. 2×1 combiner, and 9. MMI tree.                                                                | . 159  |

| Figure 122 Layout of the 2 <sup>nd</sup> generation ERON PPU at waveguides layers                                 | . 160  |

| Figure 123 Layout of the 2 <sup>nd</sup> generation ERON PPU (a) layer 1, (b) layer 2, (c) layer3, and (d) 2 meta | 1      |

| layers                                                                                                            | . 160  |

| Figure 124 Layout of the 2 <sup>nd</sup> generation ERON PPU (a) thermal trenches and heaters. (b) MMI tree       | . 161  |

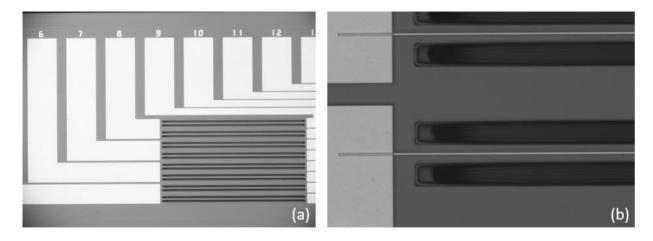

| Figure 125 SEM photos of the 2 <sup>nd</sup> generation ERON PPU after device patterning. (a) AWG, (b) MMI        | I tree |

| (c) inter-layer coupler, and (d) waveguides.                                                                      | . 162  |

| Figure 126 Assembled microscope photo of the 2 <sup>nd</sup> generation ERON PPU                                  | . 163  |

| Figure 127 Microscope photo of the 2 <sup>nd</sup> generation ERON PPU. (a) Metals and thermal trenches and (     | (b)    |

| zoom-in photo of the thermal trenches.                                                                            | . 163  |

| Figure 128 Transmission spectrum of an MMI tree with seven cascaded MMIs calibrated to a straight                 |        |

| waveguide                                                                                                         | . 163  |

| Figure 129 Inter-layer waveguide crossing loss when the bus waveguide is at (a) layer one and (b) lay             | er 2.  |

|                                                                                                                   |        |

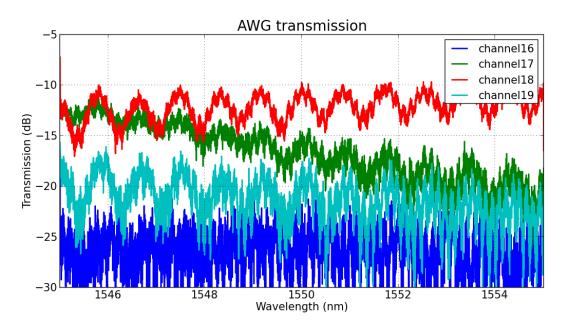

| Figure 130 Transmission spectrum of the 2 <sup>nd</sup> generation ERON PPU at four outputs                       | .164   |

# LIST OF TABLES

| Table 1 Comparison between different couplers for chip-to-chip coupling                        | 44             |

|------------------------------------------------------------------------------------------------|----------------|

| Table 2 Simulated inter-layer coupling loss between a device layer and the transition layer, w | vith different |

| taper lengths and gap thickness                                                                | 80             |

| Table 3 The designed parameters and testing results of the fabricated 1×2 MMIs                 | 95             |

| Table 4 Comparison of the 45° mirror and the grating coupler.                                  | 105            |

| Table 5 Interlayer coupling loss from a pair of inverse taper couplers. The waveguides on the  | e two layers   |

| have 150nm and 50nm thicknesses, respectively                                                  | 128            |

## **Chapter 1 Introduction**

## 1.1 Overview of photonic integrated circuits

The invention of fiber optics communication in the 1970s [1]-[3] and integrated circuits (IC) in the 1950s built the foundations of integrated photonics. By integrating photonic devices (including lasers [4]-[6], modulators [7], Error! Reference source not found., amplifiers [9], light-emitting diodes [10], waveguides [11]-[14], multiplexers [15], splitters [16], combiners, and detectors [17] on chips, the optical signal can be generated, transmitted, processed, and detected using photonic integrated circuits (PICs). Compared to traditional bulk optical devices, the PICs significantly improve the cost and performance of the optical systems by minimizing the size, weight, power consumption, and device fabrication cost, thus offering excellent solutions for modern sensing, communication, and computing systems.

An electron is a fermion with electron spin 1/2, while a photon is a boson with spin one, so photons do not obey the Pauli exclusion principle. During transmission, the photons move at the speed of light with almost no interference between photons, which allows dense wavelength division multiplexing (DWDM) [18], while electrons move at a low speed, and the electrons will repel each other. As a result, signals that carry information transmit lower loss and higher bandwidth in PICs than in ICs. Besides, natural and manual light sources exist everywhere, providing an excellent sensing and imaging stage.

Waveguides are one of the most essential elements in integrated photonics. Waveguides in integrated photonics usually consist of a core material with a higher refractive index and a cladding material with a lower refractive index. The waveguide platform can decide the index contrast, material loss, fabrication difficulties, and capability to generate or modulate optical

signals of all its devices. PICs can be fabricated on many platforms, here are the leading platforms in integrated photonics:

- III/V material: InP-based platforms are excellent in fabricating active devices, including lasers [19] and detectors [20], for their direct band. GaAs's high electron mobility enables high-speed devices such as modulators [21]. The platform is challenging to scale up due to its high propagation loss and fabrication difficulties.

- Silica: The Silica platform [22] uses doped Silica as the waveguide core material. Silica waveguides have a low refractive index that supports a low-loss transmission while suffering from a large device footprint since the bending radius in the silica platform is large. The silica platform can achieve high-performance passive devices such as filters and AWGs [23]-[24]. Meanwhile, it is not suitable for active devices.

- Lithium niobate: The thin film lithium niobate (TFLN) platform [25]-[30] is used for fabricating high-performance modulators [31],[33] and is suitable for nonlinear optical devices [34]. However, it is hard to fabricate thin-film lithium niobate on top of CMOS chips since the TFLN fabrication technology is not as mature as silicon. The stress and thermal budget limit the fabrication of TFLN devices. Besides, the TFLN also suffers from the absence of photo generation capability, so it requires an external light source.

- Silicon-on-insulator (SOI): Silicon photonics are built on the SOI platform [35], which has high core-to-cladding refractive index contrast. The high confinement of the Si/SiO<sub>2</sub> waveguide allows the Si platform to achieve passible optical devices in a small footprint. The carrier injection/depletion in Si enables modulators on the Si platform [36],[37]. Silicon photonics can utilize the mature CMOS fabrication technology and can be directly integrated with CMOS devices. Meanwhile, Ge can be epitaxially grown on Si

- for fabricating photodetectors and modulators [38]. However, the indirect band of Si makes it challenging to fabricate light sources such as lasers.

- Silicon nitride: Silicon nitride platform [39] is also CMOS-compatible and can utilize CMOS fabrication technology. The refractive index contrast in the SiN/SiO<sub>2</sub> platform is between the Si and silica platforms, so its device footprint is also between the two platforms. The Silicon nitride platform can support passive devices but is not suitable for active devices since it is a dielectric. Besides, silicon nitride is widely used in nonlinear optics.

- Germanium. Germanium is a group IV material heavily used in silicon photonics for multiple reasons [40]-[42]. High-quality crystalized germanium can be epitaxially grown on top of a single crystallized silicon layer using an ultrahigh-vacuum chemical vapor deposition (UHV-CVD), and this growth can be a selective growth in which Ge is only grown in a designed trench [43]-[45]. Rapid-melting growth is also used for Ge deposition. Germanium is widely used in silicon photonics foundries for photodetectors [46]-[49] and electro-absorption modulators (EAM) [50],[51]. Ge laser is developed since the band structure of Ge can be engineered using proper doping and tensile strain engineering [52],[53]. Furthermore, Ge is transparent in medium wavelength infrared (MWIR) to enable long-wavelength applications [54],[55].

- Polymer: The polymer platform includes many materials, such as PMMA [56]. The

polymer platform usually has a low fabrication cost and high flexibility but cannot stand

processes, including annealing, O<sub>2</sub> plasma cleaning, and wet chemical cleaning. Besides,

the polymer devices will degrade during aging.

The above information shows that none of the platforms can cover all the applications of integrated photonics, so complex optical systems may require the integration or packaging of many platforms.

## 1.2 Large-scale heterogeneous photonic integrated systems

The growing demand for high throughput communication and sensing requires large-scale heterogeneous photonic integrated systems [57]. Compared to most of the electronic integrated circuits built on the Si platform, complex electrical and optical systems may not be achieved on a single platform. For example, a modern communication system requires optical signal generation, modulation, routing, multiplexing/demultiplexing, amplification, and transmission on the transmitter side. Besides, electrical signals for controlling and monitoring are also necessary. The systems must use the packaging or integration of many platforms since none of the platforms can support all the building blocks individually. Besides, the heavy data traffic in data centers requires communication in many channels simultaneously. Co-packaged optics (CPO), which contains the heterogeneous integrations of multiple chips onto one substrate, is explored to increase bandwidth and energy efficiency.

Another approach for increasing the integration density is using multi-layer structures, which stack multiple devices vertically to increase the device density several times. The multi-layer devices require inter-layer coupling and isolation so the layers can work independently with connections.

Optical sensing is another area that requires large-scale heterogeneous optical systems. Light for detection and ranging (LIDAR) [58] provides 3D sensing for many applications, such as autonomous cars. The performance of the LIDAR usually improves with increasing the aperture size to support higher optical throughput. In optical imaging, the imaging system's resolution is

usually decided by the size of the aperture, so a large scale is required to achieve high imaging quality.

Si and silicon nitride platform plays an essential role in the large-scale heterogeneous photonic integrated system for the following reasons:

- Low propagation loss: The low propagation loss in Si and silicon nitride platforms allows signal routing on a large scale. Especially, the Si<sub>3</sub>N<sub>4</sub> waveguide can achieve a down to 0.1dB/m loss, which is negligible when routing on 6-inch wafers.

- Low coupling loss: Si and silicon nitride platforms can support many surface/edge couplers, such as inversed taper, sub-wavelength grating edge couplers, and grating couplers.

- Capability of supporting optical devices: Si and silicon nitride platforms can achieve almost all optical devices except for high-performance light sources.

- CMOS compatibility. The Si and silicon nitride platform can be fabricated using the mature CMOS foundry, which can support 12-inch wafers. Besides, the electrical ICs are directly fabricated on the same wafer.

- Germanium epitaxial growth: Germanium can be epitaxially grown or deposited onto the

Si for realizing high-speed electron absorption modulators and photodetectors.

- Flexibility on multi-layer fabrication: The silicon and silicon nitride can support interlayer couplers. Utilizing wafer bonding and smart cut technology, multiple Si layers can be transferred to the top of another wafer. Silicon nitride can be directly deposited on top of a wafer. Si and silicon nitride layers can be integrated into one wafer using CMOScompatible fabrication technology.

• III/V compatibility: III-V materials can be heterogeneously integrated into silicon photonics chips using direct wafer bonding or adhesive wafer bonding to realize lasers, modulators, and detectors. Due to the lattice constant mismatch between silicon and III-V materials, the epitaxial growth of high-quality III-V materials on silicon is complex and can introduce defects such as threading dislocations, micro-cracks, and anti-phase domains. Progress on quantum dots offers solutions for high-performance lasers on Si substrate.

The dissertation first introduces our multi-layer silicon nitride platform and its application. Design methodology, fabrication techniques, and measurement techniques are discussed and verified.

#### 1.3 Low-loss and broadband wafer-scale optical interposer

Optical interposer to support many function blocks with electrical and optical connection brings a solution for complex electro-optics integrated systems [59], such as large-scale light detection and ranging (LIDAR) [60] with large emitting aperture area occupation, and high-performance computing (HPC) systems assisted by optical interconnect. Such systems require the optical interposer to have large-scale, high integration density, high throughput, high energy efficiency, and low packaging difficulty.

A critical component in the optical interposer is the inter-chip coupler, which couples light between the interposer and packaged chips for supporting a high-efficiency signal transfer between elements under achievable packaging quality, with enough bandwidth to support applications. Inter-chip couplers based on gratings typically suffer from a high coupling loss and narrow bandwidth. Polymer waveguides offer a low-loss and broadband inter-chip coupler

solution at the cost of low reliability and temperature tolerance. In this chapter, we use evanescent coupling between chips, which uses the same principle as the inter-layer coupler presented in Chapter 2. A low-loss compact silicon nitride platform enables low-loss and broadband transition for inter-chip coupling due to the low index contrasts between the core and cladding material, which brings excellent potential to the optical interposer. Another concern of the interposer is to enlarge the interposer to a large scale with acceptable cost and yield. Die size in traditional CMOS fabrication using projection lithography is limited by the exposure region. On the other hand, contact lithography can expose the whole wafer in one shot, but it has limited quality, uniformity, and minimum feature size.

This dissertation will present a low-loss broadband inter-chip coupler with high packaging tolerance to support applications from 1200nm to 1600nm wavelength and a wafer-scale energy distribution for large-scale integration.

## 1.4 Large-scale PICs for optical interferometric imaging

Interferometry retrieves images from the interference of superimposed waves and is widely used in fiber optics, astronomy, and spectroscopy. Interferometers for interferometry require sampling from input signals and reconstructing images from the interference visibility [62]. The recent development of the Segmented Planar Imaging Detector for Electro-optical Reconnaissance (SPIDER) imager utilizes multi-layer Si<sub>3</sub>N<sub>4</sub> photonics integrated circuits (PICs) to reconstruct images with a smaller size, weight, and power compared to traditional optical telescopes with a similar resolution. The SPIDER system has multiple baselines to sample the image of objects in the Fourier domain and reconstruct the image based on the measured interference fringes. The length and number of the baseline set a hardware limitation on the image quality of a SPIDER imager. Thus, large-scale integration is required for high-resolution SPIDERs.

Our 1<sup>st</sup> demonstrated SPIDER systems use a single PIC with a 22mm×22mm chip size, which can only get and process information from one dimension at a time. For imaging, we need to rotate the PIC to extract data from a two-dimensional plane, which limits the imager's latency and stability. Our new SPIDER system uses a 21 PICs system to achieve real-time imaging by placing the PICs in a radian shape. Besides, we explore the route to extend our imager to a wafer scale for high-resolution imaging.

This dissertation presents a SPIDER imaging system with multiple chips for achieving imaging in real time. Furthermore, we present an ultra-large SPIDER imager for high-resolution interferometric imaging.

## 1.5 Surface-coupled SPIDER imager

The 1<sup>st</sup> generation of the SPIDER imager uses edge coupling, which significantly limits the position of all the optical inputs since all of them must be arranged along almost one axis. Surface couplers provide great potential for the SPIDER since the baselines can be arranged in a 2D plane and collect singles in many directions using a single wafer at one time. However, traditional surface couplers based on gratings have limited bandwidth, so they cannot lead to broadband detection. We propose and design the 1<sup>st</sup> and 2<sup>nd</sup> version of the broadband surface coupler based on a 45° mirror for the broadband imaging applications. The mirrors are fabricated by a Si anisotropic wet etching and can achieve wafer-scale uniformity. As a proof-of concept demonstration, we design surface-coupled SPIDER PICs by replacing the optical inputs of the 1<sup>st</sup> generation SPIDER PICs with surface couplers. By integrating the surface coupler with the SPIDER imager, we can achieve a surface-coupled SPIDER imager, which significantly extends the flexibility and capabilities of the SPIDER imager.