### UC Irvine UC Irvine Electronic Theses and Dissertations

#### Title

A Multiple Compiler Approach for Improved Performance and Efficiency

Permalink https://escholarship.org/uc/item/3c00m7d6

**Author** Shivam, Aniket

Publication Date 2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

A Multiple Compiler Approach for Improved Performance and Efficiency

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Aniket Shivam

Dissertation Committee: Professor Alexander V. Veidenbaum, Chair Professor Alexandru Nicolau Professor Tony Givargis

Portion of Chapter 4 © Springer Nature Switzerland AG 2019 All other materials © 2021 Aniket Shivam

# DEDICATION

To my parents.

# TABLE OF CONTENTS

| Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ge                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vi                                                                       |

| LIST OF TABLES vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ii                                                                       |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ix                                                                       |

| VITA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x                                                                        |

| ABSTRACT OF THE DISSERTATION x                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ii                                                                       |

| Introduction1.1Loop Nest Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>1</b><br>2<br>4<br>5<br>6<br>7<br>8                                   |

| 2.3       Motivation       1         2.3.1       Example 1: Intel's icc performs the best       1         2.3.2       Example 2: GNU's gcc performs the best       1         2.3.3       Example 3: LLVM clang performs the best       1         2.4       Overall Framework Architecture       1         2.5       Loop Extraction Phase       1         2.6       Optimization Phase       1         2.7       Exploratory Search Phase       2         2.8       Synthesis Phase       2 | 9<br>9<br>10<br>14<br>15<br>16<br>16<br>17<br>19<br>23<br>24<br>24<br>25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27<br>27<br>29                                                           |

|          | 3.3                                                                          | MCompiler with Exploratory Search                                             | 31 |  |  |

|----------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----|--|--|

|          |                                                                              |                                                                               | 32 |  |  |

|          |                                                                              | 3.3.2 Auto-Parallelized Code                                                  | 34 |  |  |

|          |                                                                              | 3.3.3 OpenMP Code                                                             | 36 |  |  |

|          |                                                                              | 3.3.4 Analysis of Results                                                     | 36 |  |  |

|          | 3.4                                                                          |                                                                               | 37 |  |  |

| 4        | Pro                                                                          | dicting the Best Code Optimizer for the Loop Nests                            | 39 |  |  |

| т        | 4.1                                                                          |                                                                               | 39 |  |  |

|          | 4.2                                                                          | 1                                                                             | 42 |  |  |

|          | 1.2                                                                          |                                                                               | 43 |  |  |

|          |                                                                              | 0 0                                                                           | 43 |  |  |

|          |                                                                              | 1                                                                             | 45 |  |  |

|          |                                                                              |                                                                               | 46 |  |  |

|          |                                                                              | 8 8                                                                           | 47 |  |  |

|          |                                                                              |                                                                               | 48 |  |  |

|          | 4.3                                                                          | 1                                                                             | 49 |  |  |

|          | 1.0                                                                          |                                                                               | 50 |  |  |

|          |                                                                              |                                                                               | 51 |  |  |

|          |                                                                              | · · · · · · · · · · · · · · · · · · ·                                         | 52 |  |  |

|          | 4.4                                                                          |                                                                               | 53 |  |  |

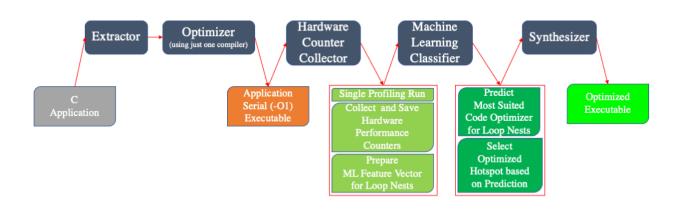

|          | 4.5 A Framework for Improving Performance using Machine Learning Predictions |                                                                               |    |  |  |

|          |                                                                              |                                                                               | 59 |  |  |

|          | 4.6                                                                          | Evaluation of the <i>MCompiler</i> with Machine Learning Prediction           | 60 |  |  |

|          |                                                                              | 4.6.1 Serial Code                                                             | 62 |  |  |

|          |                                                                              | 4.6.2 Auto-Parallelized Code                                                  | 63 |  |  |

|          | 4.7                                                                          | Summary                                                                       | 63 |  |  |

| <b>5</b> | Apr                                                                          | plying the Multiple Compiler Approach to Improve Energy Efficiency            | 65 |  |  |

|          | 5.1                                                                          |                                                                               | 65 |  |  |

|          | 5.2                                                                          | Impact of Performance-Oriented Loop Nest Optimizations on Energy Efficiency 6 | 67 |  |  |

|          | 5.3                                                                          | Evaluation of Different Compilers in Terms of Energy Efficiency               | 71 |  |  |

|          |                                                                              |                                                                               | 72 |  |  |

|          |                                                                              | 5.3.2 Reduction in EDP when Selecting the Most Energy Efficient Version       | 73 |  |  |

|          | 5.4                                                                          | Performance and Energy Consumption Implications of using Different Vector     |    |  |  |

|          |                                                                              | Extensions                                                                    | 76 |  |  |

|          |                                                                              | 5.4.1 Compiler's Ability to Auto-Vectorize and Impact of Selecting the Best   |    |  |  |

|          |                                                                              | Vector Length                                                                 | 76 |  |  |

|          |                                                                              | 5.4.2 Impact on Performance and Energy Consumption when Increasing the        |    |  |  |

|          |                                                                              | Number of Active Cores                                                        | 78 |  |  |

|          | 5.5                                                                          | A Framework for Improving Energy Efficiency                                   | 80 |  |  |

|          | 5.6                                                                          | Evaluation of the <i>MCompiler</i> for Improving Energy Efficiency            | 82 |  |  |

|          |                                                                              |                                                                               | 85 |  |  |

|          |                                                                              |                                                                               | 85 |  |  |

|          | 5.7                                                                          | Summary 8                                                                     | 86 |  |  |

| 6  | Prior Art                         | 87 |

|----|-----------------------------------|----|

| 7  | Conclusions and Future Directions | 91 |

| Bi | bliography                        | 95 |

## LIST OF FIGURES

Page

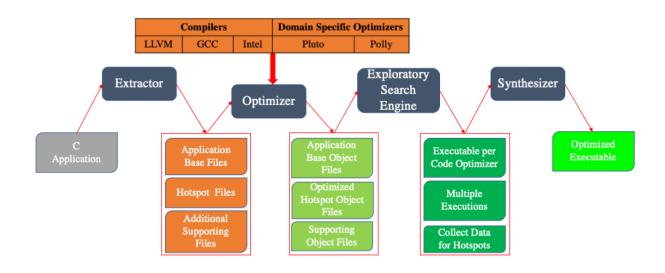

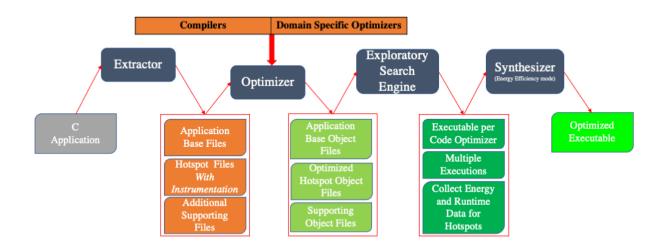

| 2.1          | MCompiler Framework                                                                                                                                                                                                                           | 18              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.2          | MCompiler Command Line Options                                                                                                                                                                                                                | 25              |

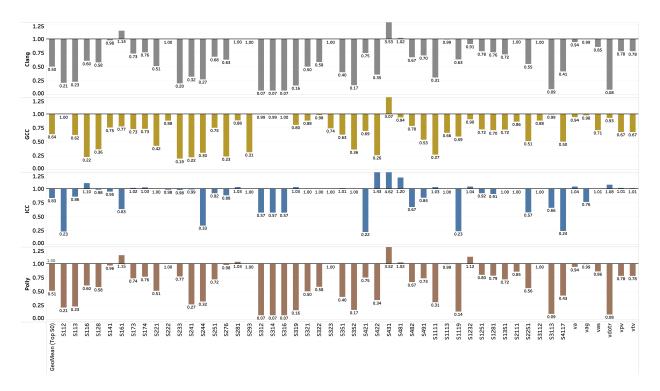

| 3.1          | Performance of individual Code Optimizers vs <i>MCompiler</i> on TSVC benchmark (top 50 loop nests). A value of 1 indicates the same performance as the <i>MCompiler</i> , less than 1 means a slower performance than the <i>MCompiler</i> . | 29              |

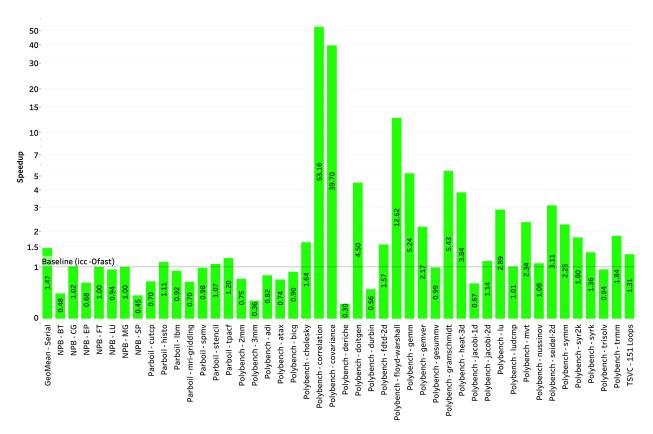

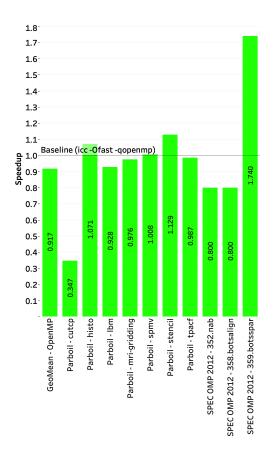

| 3.2          | <i>MCompiler</i> Speedup for Serial Benchmarks                                                                                                                                                                                                | $\overline{32}$ |

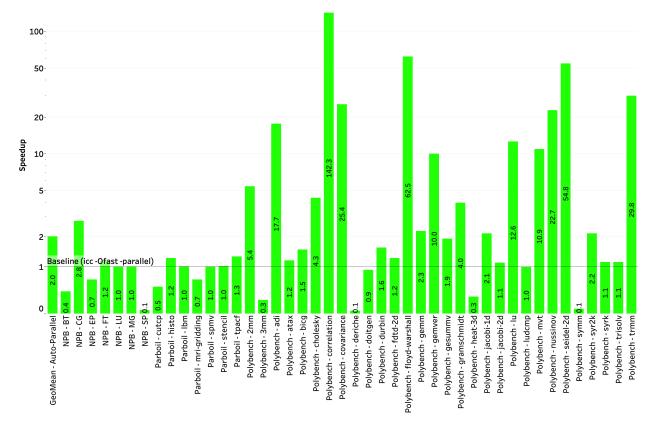

| $3.3 \\ 3.4$ | <i>MCompiler</i> Speedup for Auto-Parallelized Benchmarks Distribution of best performing code per Code Optimizer. Breakdowns per                                                                                                             | 33              |

| -            | benchmarks suite showcase benefits of specialized code optimizers                                                                                                                                                                             | 34              |

| 3.5          | MCompiler Speedup for OpenMP Benchmarks                                                                                                                                                                                                       | 35              |

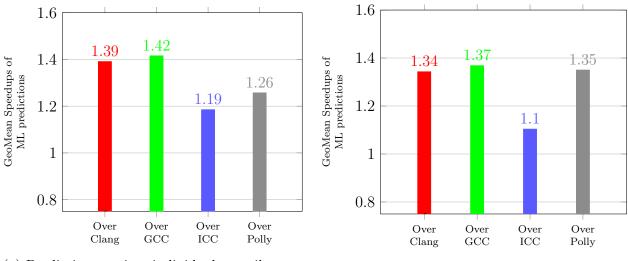

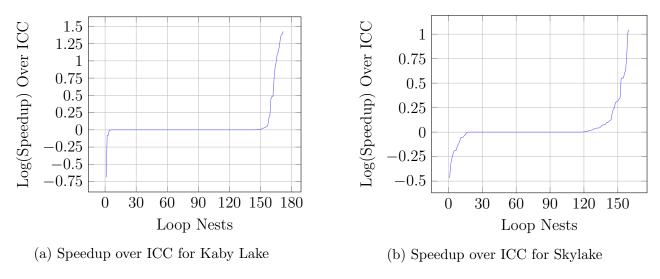

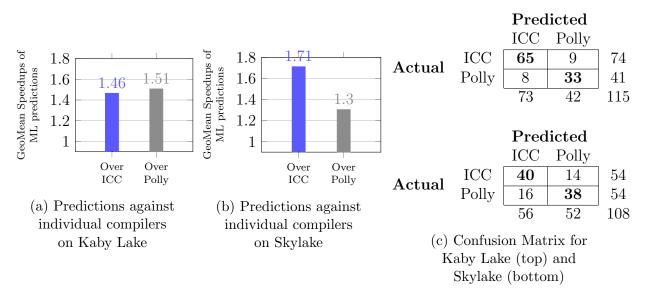

| 4.1          | Speedup of Predictions for Serial Code                                                                                                                                                                                                        | 49              |

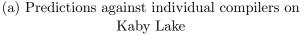

| 4.2          | Confusion Matrix for Serial Code Predictions                                                                                                                                                                                                  | 50              |

| 4.3          | Distribution of Predictions for Serial Code                                                                                                                                                                                                   | 51              |

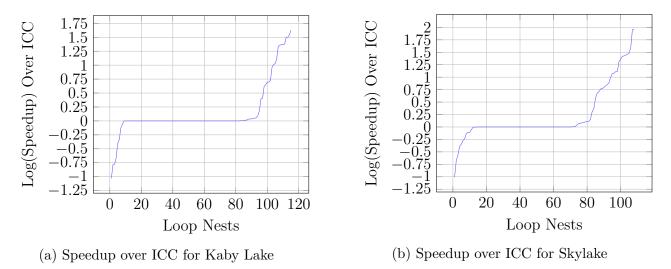

| 4.4          | Speedup and Confusion Matrix of Predictions for Auto-Parallelized Code                                                                                                                                                                        | 52              |

| 4.5          | Distribution of Predictions for Auto-Parallelized Code                                                                                                                                                                                        | 52              |

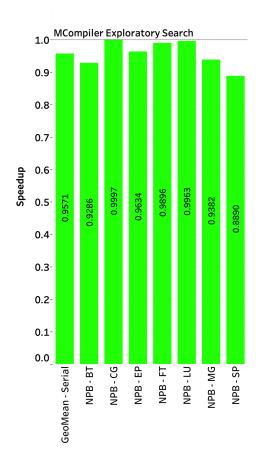

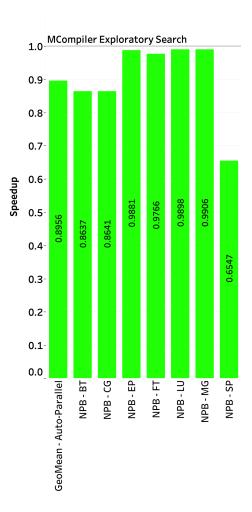

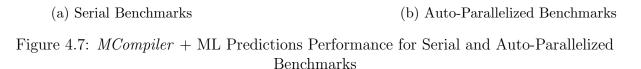

| $4.6 \\ 4.7$ | MCompiler Framework with Machine Learning Predictions                                                                                                                                                                                         | 57              |

|              | Benchmarks                                                                                                                                                                                                                                    | 62              |

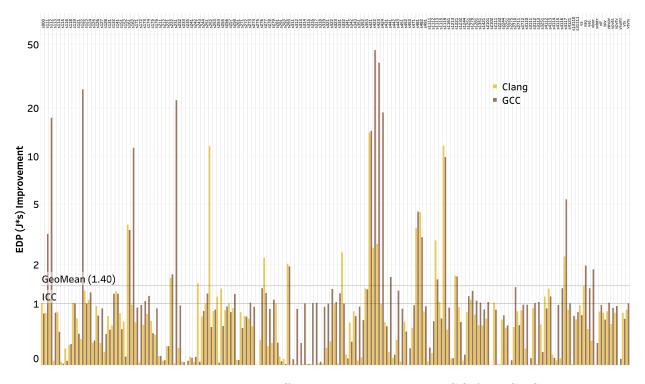

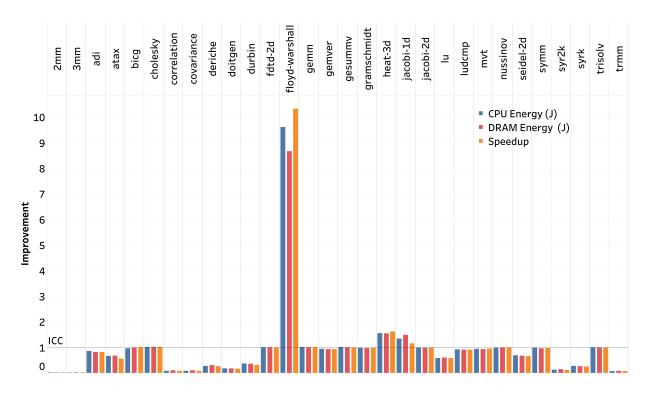

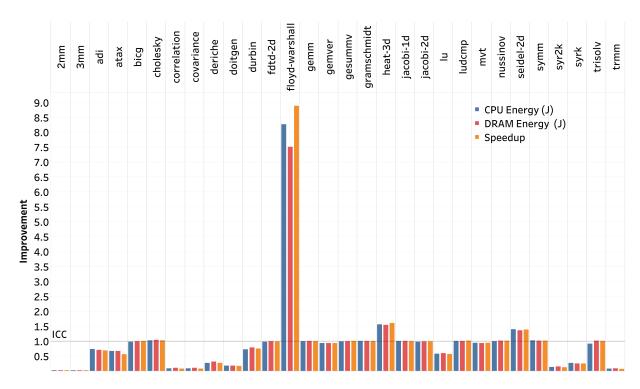

| 5.1          | EDP comparison between different compilers w.r.t. ICC for TSVC. Y-axis is log scaled. Improvement in EDP means the factor of reduction in EDP compared to the EDP of ICC generated code.                                                      | 70              |

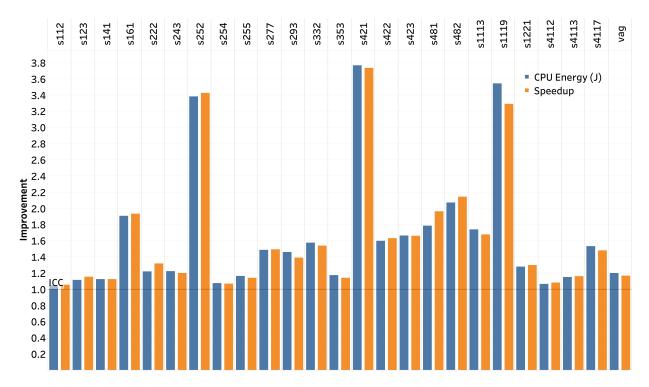

| 5.2          | Comparison of CPU Energy and Speedup between different Clang and ICC for TSVC loop nests. Only cases with more than 10% EDP improvement are shown.                                                                                            | 71              |

| 5.3          | Comparison of CPU Energy and Speedup between different GCC and ICC                                                                                                                                                                            | 11              |

|              | for TSVC loop nests. Only cases with more than 10% EDP improvement are shown.                                                                                                                                                                 | 72              |

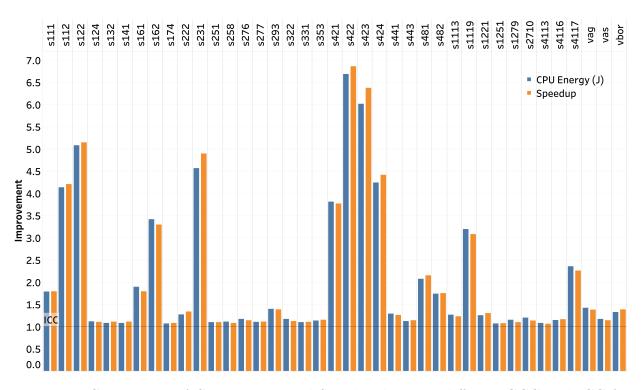

| 5.4          | EDP comparison between different compilers w.r.t. ICC for Polybench. Y-axis is log scaled.                                                                                                                                                    | 73              |

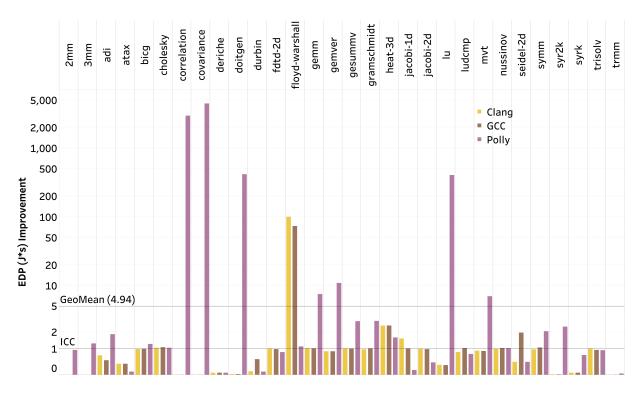

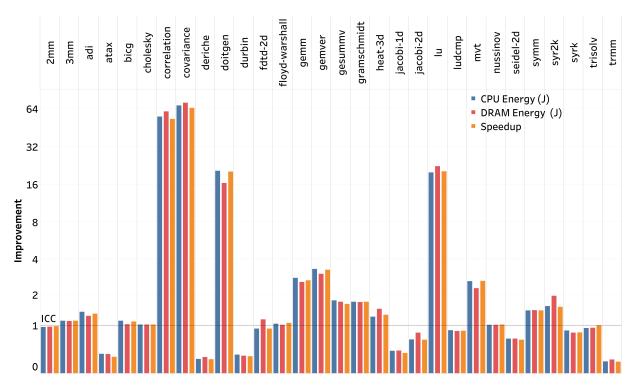

| 5.5          | Comparison of CPU Energy, DRAM Energy and Speedup between Clang and ICC for Polybench loop nests.                                                                                                                                             | 74              |

|              |                                                                                                                                                                                                                                               |                 |

| 5.6  | Comparison of CPU Energy, DRAM Energy and Speedup between GCC and          |    |

|------|----------------------------------------------------------------------------|----|

|      | ICC for Polybench loop nests.                                              | 75 |

| 5.7  | Comparison of CPU Energy, DRAM Energy and Speedup between Polly and        |    |

|      | ICC for Polybench loop nests. Y-axis is log scaled.                        | 76 |

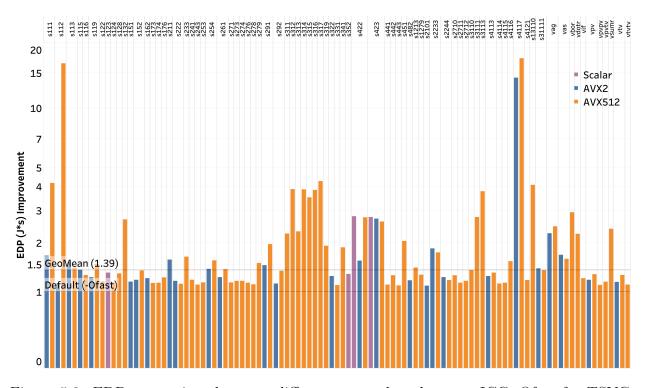

| 5.8  | EDP comparison between different vector length w.r.t. ICC -Ofast for TSVC. |    |

|      | Y-axis is log scaled. Only cases that showed more than 10% EDP improvement |    |

|      | are shown.                                                                 | 77 |

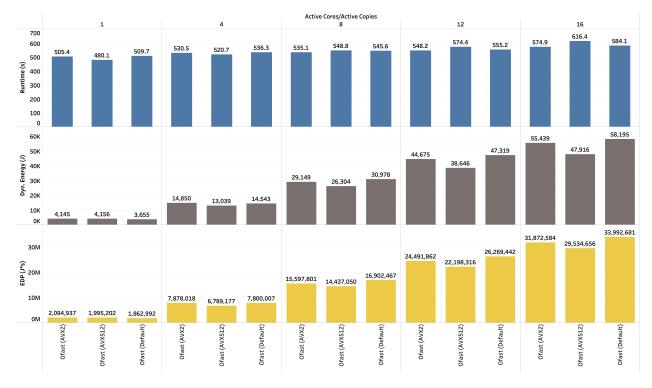

| 5.9  | Variation in Average Runtime, Total Dynamic Energy Consumption and EDP     |    |

|      | when running multiple copies of TSVC with different Vectorized versions    | 79 |

| 5.10 | <i>MCompiler</i> Framework for Improving Energy Efficiency                 | 81 |

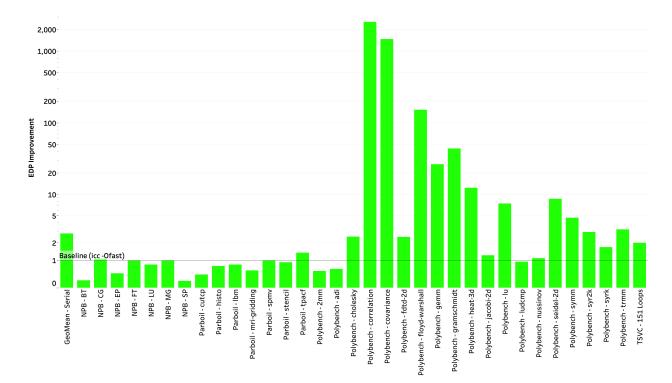

| 5.11 | MCompiler EDP Improvement for Serial Benchmarks                            | 82 |

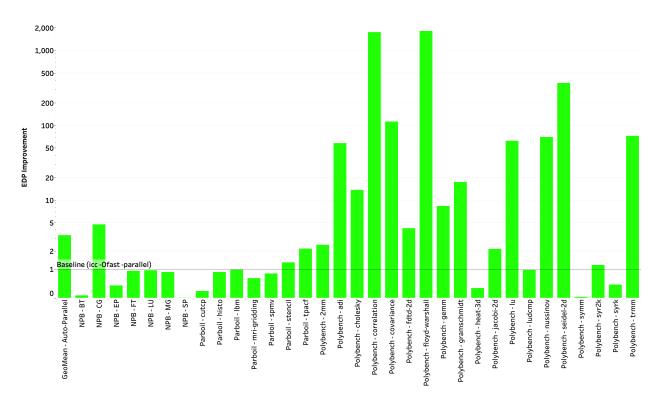

| 5.12 | <i>MCompiler</i> EDP Improvement for Auto-Parallelized Benchmarks          | 83 |

| 5.13 | Distribution of most energy efficient code per Code Optimizer. Breakdowns  |    |

|      | per benchmarks suite showcase benefits of specialized code optimizers      | 84 |

### LIST OF TABLES

### Page

| 2.1 | Sequence of LLVM's Loop Transformation Passes at the highest optimization                                    |    |

|-----|--------------------------------------------------------------------------------------------------------------|----|

|     | setting                                                                                                      | 11 |

| 2.2 | Compilers and Domain Specific Optimizers integrated in the <i>MCompiler</i> Frame-                           |    |

|     | work                                                                                                         | 23 |

| 4.1 | Candidate Code Optimizers used for the ML Experiments                                                        | 44 |

| 4.2 | Top Ranking ML Features for Serial Code Predictions.                                                         | 55 |

| 4.3 | Top Ranking ML Features for Auto-Parallelized Code Predictions                                               | 56 |

| 5.1 | Change in Maximum Core Frequency with different Vector Extensions for a                                      |    |

|     | sixteen-core Intel <sup>®</sup> Xeon <sup>®</sup> Skylake Gold 6142 processor. $\ldots \ldots \ldots \ldots$ | 69 |

### ACKNOWLEDGMENTS

I would like to thank my advisor Professor Alex Veidenbaum for his mentorship and for many interesting discussions we had over the last few years. I would also like to thank Professor Alex Nicolau for his guidance and support. Also, thanks to Professor Tony Givargis for serving on the Advancement Committee and the Defense Committee.

I feel fortunate that I get to work with some great researchers and engineers over the course of my graduate studies. I have high appreciation for Rosario Cammarota for being a mentor and a friend, and also motivating me during the first few crucial years of my graduate studies. I learned a lot from Michael Wolfe (NVIDIA) about being a good researcher and an even better engineer. Seeing his passion for work, the ability to share his knowledge and his career advice for me have been really helpful. Another source of inspiration has been David Kuck (Intel) and seeing his continuous passion for research and a great career spanning more than five decades. I would like to thank David Wong (Intel) for guidance over the course of the internship. Finally, I would like to thank my mentors and managers at the Portland Group (now NVIDIA HPC SDK) at NVIDIA, the Fast Kernels team at NVIDIA, the Performance Tools group at Intel and the team at Advanced Processor Lab, Samsung Research America for giving me valuable experience as part of my internships.

I consider myself fortunate to meet some really good people and forge some great friendships over the last few years. Juan Besa, Hirak Kashyap and Neftali Watkinson have been wonderful friends who enriched my life with their support, kindness and knowledge. Additionally, I would like to thank my lab colleagues over the years for their support, collaboration and valuable feedback.

Last but not least, I have great appreciation for my family and friends who gave me strength throughout the course of my studies.

### VITA

### Aniket Shivam

### EDUCATION

| <b>Doctor of Philosophy in Computer Science</b>            | <b>2021</b>               |

|------------------------------------------------------------|---------------------------|

| University of California, Irvine                           | <i>Irvine</i> , <i>CA</i> |

| Master of Science in Computer Science                      | <b>2016</b>               |

| University of California, Irvine                           | Irvine, CA                |

| Bachelor of Technology in Computer Science and Engineering | g 2014                    |

| National Institute of Technology, Uttarakhand              | Uttarakhand, India        |

| WORK EXPERIENCE                                            |                           |

| <b>Deep Learning Performance Library Intern</b>            | June–Sept 2020            |

| NVIDIA Corporation                                         | Santa Clara, CA           |

| Performance Tools Pathfinding Intern                       | June–Sept 2019            |

| Intel Corporation                                          | Austin, TX                |

| Compiler Engineer (PGI OpenACC/GPGPU team) Intern          | June–Sept 2017            |

| NVIDIA Corporation                                         | Hillsboro, OR             |

| Compiler Engineer (PGI OpenACC/GPGPU team) Intern          | July–Sept 2016            |

| NVIDIA Corporation                                         | Hillsboro, OR             |

| Compiler Engineer (GPU Compiler team) Intern               | June–Sept 2015            |

| Samsung Research America (SRA)                             | Mountain View, CA         |

| <b>Teaching Assistant</b>                                  | <b>2015–2021</b>          |

| University of California, Irvine                           | <i>Irvine, CA</i>         |

#### SELECTED PUBLICATIONS

| A Multiple Compiler Framework for Improved Perfor-                                                                                                           | 2021 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Using Performance-Oriented Loop Nest Optimizations<br>to achieve Energy Efficiency<br>In submission.                                                         | 2021 |

| <b>OpenACC Routine Directive Propagation using Inter-</b><br><b>procedural Analysis</b><br>Workshop on Accelerator Programming Using Directives (WACCPD), SC | 2018 |

| Towards an Achievable Performance for the Loop Nests2Languages and Compilers for Parallel Computing (LCPC)                                                   | 2018 |

| Load Balancing with Polygonal Partitions<br>International Workshop on Polyhedral Compilation Techniques (IMPACT), HiPEAC                                     | 2018 |

| Using Hardware Counters To Predict Vectorization<br>Languages and Compilers for Parallel Computing (LCPC)                                                    | 2017 |

| Polygonal Iteration Space Partitioning<br>Languages and Compilers for Parallel Computing (LCPC)                                                              | 2016 |

#### SOFTWARE

**MCompiler** A Synergistic Compilation Framework

### ABSTRACT OF THE DISSERTATION

A Multiple Compiler Approach for Improved Performance and Efficiency

By

Aniket Shivam

Doctor of Philosophy in Computer Science University of California, Irvine, 2021 Professor Alexander V. Veidenbaum, Chair

Production compilers have achieved a high level of maturity in terms of generating efficient code. Compilers are embedded with numerous code optimization techniques, with special focus on loop nest optimizations, that have been developed over the last four decades. The code generated by any two production compilers can turn out to be very different based on pros and cons of their respective Intermediate Representation (IR), implemented loop transformations and their ordering, cost models used and even instruction selection (such as vector instructions) and scheduling. The compilers also need to predict the behavior of a multi-core processor which has complex pipelines, multiple functional units, complex memory hierarchy, etc. on the overall performance. Hence, the performance of produced code for a program segment by a given compiler may not necessarily be matched by other compilers. Additionally, there is no way of knowing how close a compiler gets to optimal performance or if there is any headroom for improvement.

The complexity and rigidity of the compilation process makes it very difficult to modify a given compiler to improve the performance of generated code for every case where it couldn't produce the best possible code. Therefore, this thesis presents a compilation approach that turns the differences between compilation processes and performance optimizations in each compiler from a weakness to a strength. This approach is implemented as a novel compila-

tion framework, the *MCompiler*. This meta-compilation framework allows different segments of a program to be compiled using an ensemble of compilers/optimizers and combined into a single executable. Utilizing the highest performing code for each segment, identified via Exploratory Search, can lead to a significant overall improvement in performance. The framework is shown to produce performance improvements for serial (including auto-vectorized code), auto-parallelized and hand-optimized (using OpenMP) parallel code.

Next, this thesis explores the possibility of learning which compiler will produce the best code for a segment. This is accomplished using Machine Learning. The Machine Learning models learn about inherent characteristics of loop nests and then predict which code optimizer is the most suited for each loop nest in an application. These Machine Learning models are then incorporated into the *MCompiler* to predict the best code optimizer, during compilation, for each code segment of the application. This feature allows the *MCompiler* to replace the expensive Exploratory Search with Machine Learning predictions and still keep performance very close to the Exploratory Search.

Finally, this thesis expands the compilation approach to achieve energy efficiency on modern architectures. Prior research has advocated both for and against the hypothesis that optimizing for performance translates into optimizing for energy efficiency. No production compiler optimizes for energy efficiency directly, expecting optimizing for performance to translate into higher energy efficiency. Optimizing for performance is complex for recent generations of processors and, with automatic DVFS management in these processors, optimizing for energy efficiency would add another level of complexity for compilers with no guarantee of success. Using the *MCompiler*, this thesis shows how the performance-oriented compiler optimizations can be used to achieve energy efficiency.

# Chapter 1

# Introduction

State-of-the-art compilers optimize applications for better performance on target architectures. The developers and the users of applications trust the compilers to be able to generate the most efficient code for the architecture of choice. Specially in the domain of High-Performance Computing, and recently in other domains such as Computer Vision and Deep Learning, a lot of attention is paid to getting the best out of target architecture. Application developers are responsible to come up with efficient algorithms and source code. Once this step is done, writing hand-optimized code or libraries for a target system is a possible option, but the complexities are such that even these approaches cannot guarantee the absolute best results. In addition to that, this requires massive efforts from developers to understand and optimize for each applicable system and later to port these applications to newer architectures and systems. Hence, more often than not, applications are written using the best known algorithm and language features, but the rest is left to the compilers to optimize for different architectures and systems.

Compiler optimizations are essential to reach an achievable performance for many applications. The means to reach the goal of producing high performance code may, and in most cases, do differ between any two production compilers. Each may have their own flavor of Intermediate Representation (IR), vary in implemented loop transformations and their ordering, and even differ in instruction selection (such as vector instructions) and scheduling. Each compiler uses a specific, ordered set of optimization techniques and different profitability models and can, therefore, generate code significantly different from other compilers. For program segments, such as loop nests, the performance of generated code from a compiler may either turn out to be better or worse compared to other compilers. And given the complexity of the entire compilation/optimization process it is very difficult to modify a given compiler so as to produce the best performing code for every case where it couldn't match a different compiler. Discrepancies in performance between compilers are not merely engineering shortcomings that can be fixed in the next update. They are the unavoidable result of many NP-Hard or NP-Complete problems encountered in the compilation/optimization process[80, 129]. Compilers try to approximately solve NP-Hard problems efficiently and effectively by using profitability models that are based on many assumptions. Compiler writers try to find the optimal solutions, based on experimentation, that work well for a large portion of target applications for their compiler, but not all. Therefore, it is quite apparent why different compilers produce different results for a given program segment. This calls for a strategy to harness the strengths of multiple compilers, while substituting the weakness of individual compilers. Hence, this thesis presents a compilation approach that will provide both the users of compilers and compiler writers a means to find best possible solution for their target applications.

### **1.1** Loop Nest Optimizations

Optimizing loop nests, in particular, contributes significantly towards achieving better performance. State-of-the-art architectures have multiple cores on a chip, where each core has Single Instruction Multiple Data (SIMD), or vector, capabilities. These architectural features provide opportunities for a compiler to expose parallelism in applications on multiple levels, but with a caveat of additional complexity in the decision making for the compiler. The code optimization techniques to *auto-vectorize* the loop nests [106, 4, 146], so as to generate SIMD instructions, require careful analysis of data dependences, memory access patterns, etc. Several auto-parallelization techniques [105, 90, 8, 92, 91, 93, 88, 21, 39, 100] and directive based parallel programming models, such as OpenMP [104], have been developed to take advantage of multiple cores. In fact, most auto-parallelization implementations in modern compilers, which take serial code as input, generate OpenMP code [68, 111, 113].

Key loop transformation techniques [15, 12, 146, 143, 16, 77] include Distribution, Fusion, Interchange, Skewing, Tiling and Unrolling. Code optimizers apply a semantic-preserving sequence of transformations to generate a better performing code, either serial or parallel. But evaluating if a sequence of transformations is optimal is NP-Hard and the search for the best sequence of transformations and their profitability is guided by heuristics and/or approximate analytical models. Thus, a code optimizer may end up with a sub-optimal result and different code optimizers may, for the same source code segment, generate code with significant performance differences on the same architecture.

A major challenge in developing the heuristics and profitability models is predicting the behavior of a multi-core processor which has complex pipelines, multiple functional units, complex memory hierarchy, hardware data prefetching, etc. Parallelization of loop nests involves further challenges for the code optimizers, since communication costs based on the temporal and spatial data locality among iterations have an impact on the overall performance. Evaluation studies [102, 134, 94, 54] have shown that state-of-the-art code optimizers may miss out on opportunities to auto-vectorize and auto-parallelize the loop nests for modern architectures. For optimizing applications written in C, there are several compilers and domain specific loop optimizers that perform auto-vectorization and, in some cases, auto-

parallelization of code. From a given code optimizer's point of view, the sequence it used is the best it could do but there is no way of knowing how close it gets to optimal performance or if there is any headroom for improvement.

### **1.2** A Synergistic Compilation Approach

In this thesis a compiler framework, called the *MCompiler*, is presented and its design is discussed in Chapter 2. The design allows each loop nest in the application to be optimized by the best optimizer available for it. The *MCompiler* identifies loop nests in C applications, optimizes the loop nests using different code optimizers, times each optimized code version in execution of its complete application, and links the best performing code to generate the complete application binary. This is referred to as the Exploratory Search method of the *MCompiler*. The *MCompiler* currently incorporates code optimizers from Intel's C compiler, GNU GCC and LLVM Clang. In addition to these, two Polyhedral Model based loop optimizers, Polly [56, 113] and Pluto [22, 111] are used, if applicable. The best loop nest code selection allows the *MCompiler* to produce higher-performing code than the best of the code optimizers in the framework. The *MCompiler* benefits from the entire compilation process (loop transformations and optimizations, and code generation) implemented in each of the code optimizers. The framework allows for easy integration of newer versions and newer configurations of the available code optimizers as well as the addition of new code optimizers.

The framework can be used to optimize applications, first, for serial execution with autovectorization of loop nests. This optimizes loop nests for SIMD or vector code generation, in addition to optimizing loop nests for data locality, memory hierarchy, etc. Second, the framework can also target multi-core processors, by taking serial loop nest code as input and auto-parallelizing those loop nests using the available code optimizers to generate multithreaded code. Auto-parallelized code is also optimized for SIMD execution within each thread. In this case, the original loop nests are transformed such that loop iterations can be reordered and scheduled for parallel execution across the multiple cores. Third, the framework can target OpenMP applications, i.e., applications with OpenMP directives inserted across sections of the code meant for parallel execution.

The framework extracts loop nests from the applications' source files into separate source files as a function, together with any additional information needed. It then replaces loop nests with a function call in the original source files. This allows for separate code optimizers to focus on just the loop nests and also allows the framework to insert the best performing code, i.e., linking object files to generate the executable.

Chapter 3 presents a study of the potential of the proposed approach. It optimizes each extracted loop nest, or a consecutive set of loop nests, separately with all available code optimization *candidates*. The performance of each optimized loop nest is measured as part of the complete application execution. The best performing code for a loop nest is selected for linking into the final executable. This step, referred to as Exploratory Search, shows that the framework can indeed improve the resulting code's performance.

# 1.3 *Learning* about the Impact of Optimizations on Performance

The benefits of the proposed approach comes from the fact that different optimizers try to solve a certain problem differently, i.e., optimizing a certain type of loop nest(s) in a unique manner. Loop nests have different inherent characteristics based on memory access patterns, types and counts of operations, presence of branches, etc. This leads to a research question: can we get an insight into these inherent characteristics of the loop nest? If so, can this learning be useful in predicting which optimizer will produce the best code for a loop nest?

The thesis presents Machine Learning (ML) based techniques to learn such inherent characteristics and predict the most suited code optimizer for a given loop nest in Chapter 4. The approach used in this thesis relies on the hardware performance counters collected for a loop nest to learn about its inherent characteristics. Hardware performance counters capture intricate details about data movement across levels of caches, memory footprint, and count and types of instructions retired that determine the performance of loop nests on an architecture. These hardware performance counters are used as features/input to the ML algorithms to predict the most suited code optimizer for the loop nests.

These ML models are then incorporated into the *MCompiler* and provides a substitute for the expensive Exploratory Search step of the framework. The hardware performance counters are collected from a single profile of the applications, i.e., the applications are compiled with just one code optimizer and then executed ones. However, as with any prediction, it can lead to a potential performance loss compared to search-based selection due prediction errors, i.e., when the ML model or classifier does not choose the best code optimizer. The results show that by using well-trained ML models this potential loss in performance can be quite small.

# 1.4 Using Performance-Oriented Optimizations to Achieve Energy Efficiency

Energy efficiency is a major issue for domains from embedded systems to Exascale computing [71]. The goals for optimizing applications, in terms of energy or power, differ from domain to domain and may even differ from user to user. Energy consumption for different processors (even from the same architecture) is driven by dynamic parameters, such as Dynamic Voltage Frequency Scaling (DVFS). These parameters cannot be modeled while doing static compilation, hence implementing energy efficiency driven compiler optimization may provide no guaranteed results. In general, production compilers optimize for performance, with various optimization levels with increasing aggressiveness towards generating better performance, but no such optimization levels for better energy efficiency, and understandably so.

Prior works [44, 149, 73, 75, 109, 137, 76, 151, 152, 53, 120, 138, 107, 55, 89, 52, 70] have explored the impact of compilers and their optimizations on performance and energy consumption for the CPU and memory, some focusing on loop nest transformations. However, Chapter 5 of this thesis shows the overall impact of the sequence of loop nest transformations implemented in *several* compilers on energy efficiency.

Then, the Exploratory Search method of the *MCompiler* is expanded to optimize applications for better energy efficiency by choosing the most energy efficient version possible for each loop nest. The results show that optimizations oriented towards performance improvement may not have the same impact on energy consumption improvement and these differences vary from loop nest to loop nest. Also, by using the Exploratory Search method, the *MCompiler* is able to measure the impact of dynamic parameters before generating the optimized binary.

### **1.5** Tool for Compiler Researchers

The *MCompiler* framework can also serve as an important tool for compiler researchers who regularly implement and test their optimization techniques and/or tweak analytical or heuristic models to improve performance and/or efficiency for applications. The framework design allows for adding new code optimizers and monitoring their performance on entire application or just on particular hotspots.

The framework also allows for training new Machine Learning models and using them for

making predictions. Various flags are available for choosing the target architecture and choosing particular optimizations such as auto-parallelization optimizations or enabling particular passes such as data prefetching pass. The framework also allows for running Hardware Counter Collector independently, i.e., collect hardware performance counters for all the hotspots in an application while disabling the ML predictions.

### **1.6** Contributions

Overall, this thesis makes the following contributions:

- It presents a meta-compilation framework that improves performance for C applications for serial as well as parallel execution, including OpenMP applications.

- It shows that using the framework can achieve better performance over state-of-the-art compilers.

- It demonstrates that prediction for the most suited code optimizer (serial as well as parallel) for a loop nest can be accurately made using Machine Learning classifiers.

- It explores the impact of performance-oriented optimizations on energy efficiency and then uses the framework to generate energy efficient version for applications.

- It provides an open source framework for researchers and compiler developers to analyze and compare their code optimization techniques.

# Chapter 2

# MCompiler - A Synergistic Compilation Framework

This chapter primarily presents the design of the framework that implements the multiple compiler approach for improving performance. The chapter starts with an overview of the prior art in the field of compilation and optimization frameworks. Then, it presents interesting cases that justify the need for a multiple compiler approach. Finally, the details of the *MCompiler* framework are presented and its benefits and flexibility are explained.

### 2.1 Loop Nest Optimizations

In the field of compilers, loop nest optimizations have been a focus for decades. The reason being that the majority of the application execution time is spent in executing a set of instructions repeatedly, i.e., the loop nests. Improvements in performance may come from various avenues. These may include Loop Nest (or Iteration Space) Transformations [82, 106, 4, 45, 46, 15, 12, 146, 143, 16, 77, 117] such as Distribution, Fusion, In-

terchange, Skewing, Tiling [144, 145] and Unrolling. These transformations are performed at the Intermediate Representation (IR) level. They try to optimize the code for data locality and memory management. The order of these transformations and the correctness of the profitability models for directing these transformations have significant impact on the performance. Next step includes taking advantage of the architecture specific components such as Vector/SIMD units and multi-core processors (with multi-level caches and shared memory). This is accomplished using auto-vectorization techniques [105, 106, 4, 3, 146, 83, 77, 94], so as to generate SIMD instructions, that require careful analysis of data dependences [118, 16], memory access patterns, etc. For improving performance for multi-core processors several auto-parallelization techniques [105, 90, 95, 6, 8, 59, 92, 91, 148, 74, 93, 88, 22, 21, 39, 100] have been proposed. But due to the complexity of the applications and their source code, compilers are not able to model the definite behavior of the loop nests/hotspots during compilation. For such cases, hand-optimized code using directive based parallel programming models, such as OpenMP [104], aid compilers in generating the high-performance machine code and are allow for code portability. Other available options for hand-optimizing code that are restrictive to specific architectures and compilers are using assembly-coded functions [66] and specialized libraries [67].

### 2.2 Compilation and Optimization Frameworks

To solve the NP-Hard or NP-Complete problems encountered during the optimization process, several compilation frameworks have been proposed. These include compilation frameworks for program analysis and transformation such as LLVM [84], similar to GNU GCC and Intel C/C++ compilers. LLVM uses a static sequence of loop transformations for optimizing code for performance. Table 2.1 shows the sequence of loop transformations at the highest optimization setting (-O3). Few of these transformations are optional and need to be switched on explicitly by the users. Many other compiler optimization passes are executed in and around these loop transformations.

| Loop Transformations       | Include<br>Profitability<br>Models | Optional<br>Pass | Link-Time<br>Optimization<br>Pass |

|----------------------------|------------------------------------|------------------|-----------------------------------|

| Rotate Loops               |                                    |                  |                                   |

| Loop Invariant Code Motion |                                    |                  |                                   |

| Unswitch Loops             |                                    |                  |                                   |

| Loop Flatten               |                                    | Y                | Y                                 |

| Recognize Loop Idioms      |                                    |                  |                                   |

| Delete Dead Loops          |                                    |                  | Y                                 |

| Loop Interchange           | Y                                  | Y                | Y                                 |

| Unroll Loops               | Y                                  |                  | Y                                 |

| Loop Invariant Code Motion |                                    |                  |                                   |

| Reroll Loops               |                                    | Y                |                                   |

| Loop Versioning LICM       |                                    | Y                |                                   |

| Loop Invariant Code Motion |                                    |                  |                                   |

| Rotate Loops               |                                    |                  |                                   |

| Loop Distribution          |                                    |                  | Y                                 |

| Loop Vectorization         | Y                                  |                  | Y                                 |

| Loop Load Elimination      |                                    |                  |                                   |

| Loop Invariant Code Motion | Y                                  |                  |                                   |

| Unswitch Loop              |                                    |                  |                                   |

| SLP Vectorizer             | Y                                  |                  |                                   |

| Loop Unroll-And-Jam        | Y                                  | Y                |                                   |

| Unroll Loops               | Y                                  |                  | Y                                 |

| Loop Invariant Code Motion |                                    |                  |                                   |

| Loop Sink                  |                                    |                  |                                   |

| Loop Fusion                |                                    | Y                |                                   |

Table 2.1: Sequence of LLVM's Loop Transformation Passes at the highest optimization setting.

These order of transformations and their profitability models differ from one compiler to the other. Compiler writers try to find the optimal solutions that work well for a large portion of target applications for their compiler. That is why, different compilers produce different results for a loop nest and hence, the entire application.

Several classes of code optimizers have been proposed in the past. Polaris [20] operated

on Fortran 77 programs and it's IR is Fortran-oriented. SUIF [59] was a source-to-source parallelizing compiler framework. PIPS [78] is a tool to implement and evaluate various interprocedural compilation, parallelization, analysis and optimization techniques. Cetus [88] is a source-to-source parallelizing compiler for C. Whereas, ROSE [119] provide tools for static analysis, program optimization, arbitrary program transformation, domain-specific optimizations, complex loop optimizations, performance analysis, and cyber-security analysis.

There are several domain-specific compilation frameworks that have been proposed and show significant performance improvement over traditional compilers and techniques. One such domain is Polyhedral Model based optimizations [7, 47, 48]. Compilation frameworks built on the concepts of the Polyhedral Model are Pluto [22, 111], Polly [56, 113], PoCC [115, 116, 112], CHiLL [33, 133], AlphaZ [150] and Tiramisu [13].

Recently, compilation frameworks for Deep Learning and Machine Learning, such as TensorFlow XLA [1] and Apache TVM [35], and for Tensor Algebra, such as TACO [79], have been shown to improve performance of applications in their respective domains. MLIR [85] is an extensible compiler infrastructure (based on LLVM) that aims to address software fragmentation, improve compilation for heterogeneous hardware, significantly reduce the cost of building domain specific compilers.

Several programming models, such as OpenMP [104], aim to provide better performance by allowing users to explicitly expose parallelism in the applications. For example, OmpSs [49] extends OpenMP with new directives to support asynchronous parallelism and heterogeneity. Whereas, Tapir/LLVM [124] compiles and optimizes Cilk programs to allow for efficient parallel execution on shared-memory multicore machines.

Compilers provide several options and configurations that let users explore various configurations that may suit their application the best, rather than the default setting embedded into the compilers. In order to take advantage of these options and configurations, several iterative compilation [136, 5, 2, 115, 116, 36] and auto-tuning frameworks have been proposed in the past that explore, search or predict good combinations of compiler flags to improve performance. MilepostGCC [51] presents an auto-tuning framework that explores GCC and its flags, and uses ML techniques to predict good combinations of compiler flags. Another similar work, the OpenTuner framework [9], searches for the best performing compiler flag combinations. There are few options [81, 132] available to control transformation orders at finer granularity but require user assistance.

Production compilers also provide option for Interprocedural optimizations (IPO) [38, 24, 60], sometimes also known as Whole Program Optimizations (WPO) or Link-Time Optimizations (LTO), and Profile-guided Optimization (PGO) [34, 108]. IPO and LTO passes perform several optimizations based on whole program analysis or interprocedural analysis and may re-address loop nests' optimization based on the new information. In case of LLVM, few loop nest transformations are repeated in the Link-Time Optimization (LTO) phase, as mentioned in Table 2.1, after analyzing the entire program and may help optimize the code further. Whereas, PGO, for example, in the Intel compilers improves performance by reducing code size, reducing branch mispredictions and reorganizing code layout to reduce instruction-cache problems. Also, determine profitability of loop nests with small iteration counts [66].

#### Why a synergistic compilation framework could be helpful?

To take advantage of these several compilers and code optimizers, a unified and extensible compilation framework that can incorporate these tools is one approach. The *MCompiler* framework presented in this chapter targets different classes of compilers, code optimizers and programming models in a single framework. *MCompiler* starts with using ROSE to transform the application source code in a desired manner so as to facilitate an infrastructure that can combine optimized code from several optimizers in one single executable. Next, it applies traditional compilers such as Intel's icc, GNU's gcc and LLVM clang to optimize

loop nests. It also applies two domain specific optimizers: Polly and Pluto (wherever applicable). Polly is an extension to LLVM optimizer, that transforms LLVM IR to Polyhedral representation to do transformations, and finally generates machine code using LLVM code generator. Whereas, Pluto is a source-to-source optimizer that lowers the loop nests in a Polyhedral representation and uses Polyhedral Model based code generators to generate optimized C code. Using these compilers/optimizers, the *MCompiler* can generate serial (with SIMD/vector code) code and auto-parallelized code. Finally, *MCompiler* can also optimize hand-parallelized programs written using OpenMP programming model and generate multithreaded programs. But, *MCompiler* can be extended to other domain specific optimizers and auto-tuning frameworks.

### 2.3 Motivation

Let us start with three motivating examples that highlight the fact that different compilers do perform different loop nest optimizations at highest optimization levels. This leads to a difference in performance on the same architecture. The presented framework exploits this fact to improve performance of applications. These examples also highlight that performance improvements can be attributed to complex loop transformation techniques. In these cases, even phase-ordering or changing flag combinations on a compiler may not help. The performance improvement comes from specific loop transformation and auto-vectorization techniques. The following three examples compare and analyze auto-vectorized code from three compilers that produce the best performance in terms of execution time. Their performance is compared on Intel Xeon Scalable Gold Skylake processor with AVX-512 vector extensions. The three compilers are Intel's icc, GNU's gcc and LLVM clang. The three loop nests are taken from Test Suite for Vectorizing Compilers (TSVC) by Callahan et al. [25] and Maleki et al. [94].

#### 2.3.1 Example 1: Intel's icc performs the best

Listing 2.1: Example 1

```

for (int nl = 0; nl < 100*(ntimes/LEN2); nl++) {</pre>

// Loop 1

1

2

for (int i = 1; i < LEN2; i++) {

// Loop 2

for (int j = 1; j < LEN2; j++) {</pre>

// Loop 3

3

4

aa[j][i] = aa[j-1][i] + cc[j][i];

}

5

// Loop 4

for (int j = 1; j < LEN2; j++) {</pre>

6

bb[i][j] = bb[i-1][j] + cc[i][j];

7

8

}

}

9

}

10

```

Here icc performs 14.5x better than gcc and 12.9x better than clang. Listing 2.1 is loop nest s2233 from the TSVC benchmark. icc distributes Loop 2, over Loop 3 and Loop 4, into two separate loop nests. The first loop nest, Loop Nest 1, then consists of Loop 1 { Loop 2 { Loop 3 } }. Second loop nest, Loop Nest 2, is Loop 1 { Loop 2 { Loop 4 } }. Next, in Loop Nest 1, Loop 2 and Loop 3 were interchanged to provide sequential memory accesses. In Loop Nest 2, the memory accesses are sequential already inside innermost loop. Therefore, innermost loops in both loop nests were auto-vectorized. Finally, Loop 2 and Loop 4 were completely unrolled as they were left with only 15 iteration after vectorization. Interestingly, icc chose to use AVX and AVX-2 registers only and skip AVX-512 based on the cost model. gcc on the other hand, did not distribute or interchange loops. It simply vectorized for AVX-512 and then completely unrolled Loop 4 only. Lastly, clang followed gcc's transformation and added one more transformation on Loop 3, i.e., unroll by factor of 5. This one last transformation from clang improved code performance over gcc. This example clearly shows why different compilers perform so differently. The application and order of loop transformations are primarily responsible for this contrast. These transformation and their

order may also be tightly embedded and fixed in most compilers, therefore they can't be controlled by flags or hints.

#### 2.3.2 Example 2: GNU's gcc performs the best

Listing 2.2: Example 2

In this example, gcc performs 6.1x better than icc and 5.3x better than clang. Listing 2.2 is loop nest s112 from the TSVC benchmark. gcc vectorized the innermost loop with the factor of 16, array a is type float, therefore using AVX-512 registers. Followed by unrolling the innermost loop by a factor of 16. The innermost loop can indeed be vectorized since the only dependence present is an anti-dependence or write-after-read on a[i]. On the other hand, icc decided against vectorization (vector width = 2, unrolled factor = 4) of the innermost loop based on the cost model. Hence, it simply unrolled the innermost loop by a factor of 2. This resulted in 6.1x performance loss compared to gcc. clang also decided against vectorization and unrolled innermost loop by a factor of 4, hence lost an opportunity for performance gain. This example showcases the importance of cost models for decision making process for loop transformations and optimizations. The cost models used here were the default ones at the highest optimization level. There are compiler flags available to the users that can override these default cost models.

#### 2.3.3 Example 3: LLVM clang performs the best

Listing 2.3: Example 3

```

1 for (int nl = 0; nl < ntimes; nl++) {

2     for (int i = 0; i < LEN; i++) {

3         a[i * inc] += b[i];

4     }

5 }</pre>

```

Here, clang performs 4.4x better than gcc and 3.8x better than icc. Listing 2.3 is loop nest s171 from the TSVC benchmark. In this example, the innermost loop nest can only be vectorized if variable inc has value 1. Otherwise, there could be flow-dependence and anti-dependence on a[i \* inc]. This variable comes in as a function argument, hence compilers cannot resolve its value at compile-time. gcc decided to do no transformations or optimizations for this loop, it just used AVX and AVX2 registers for scalar computations. icc unrolled the innermost loop with a factor of 2. Interestingly, clang analyzed the peculiarity here and added an additional branch inside the outermost loop to check the value of variable inc. This branch checked if inc had value 1 at runtime, if so, the code executed is vectorized for AVX-512 with vector width of 16, array a is type float. Also, clang unrolled, or interleaved as they call it, this loop by a factor of 4. If the above mentioned branch fails then the code executed is a loop unrolled by a factor of 4 with scalar operations. The value of inc was indeed 1 in the benchmark, and hence clang produced higher performance than the other two compilers. This example highlights the importance of handling edge or special cases by the compiler to gain performance. Again, these details are not possible for users to control by either flags or annotating code with hints. These are simply optimizations embedded into the compiler.

#### 2.4 Overall Framework Architecture

The overall architecture of the *MCompiler* framework and the technical details about the individual phases of the framework are discussed in this section. Fig. 2.1 shows the structure

Figure 2.1: *MCompiler* Framework

of the *MCompiler* framework.

The first phase is *Loop Extraction* from C applications. The *Extractor* parses the source files to find loop nests, extract those loop nests as **functions** into separate, independently compilable files and replaces the loop nests with the corresponding function call in the *base* source file. Base files are similar to the original source files but with loop nests replaced with function calls. Whereas hotspot files are newly generated files which define the function containing the loop body and supporting components to make them compile successfully.

The second phase is the *Optimization* phase. The *Optimizer* compiles each hotspot file with the available code optimizers. Also, it compiles the base files and additional *MCompiler* files, i.e., files added to support the functioning of the framework. For source-to-source code optimizers, a *default compiler* is used to compile optimized hotspot files, the base files and additional files.

The third phase is the Exploratory Search phase, where an application is executed to record

the execution times of the extracted loop nests. Executables generated for each code optimizer are executed and reported execution times for the loop nests are collected.

The final phase is the *Synthesis* phase. Here, for each extracted loop nest, the collected loop execution times from every code optimizer are compared and the best performing code/optimizer is selected, i.e., the optimized code that executes the loop body in the shortest time. Finally, the default compiler links the selected object files for every loop nest file, plus the object files generated by the default compiler for the base files. This step also requires linking libraries that code optimizers may have used or taken support of for generating code for the hotspot files.

For large applications, if -c flag is provided, i.e., compile to object files only, then just the Extractor and the Optimizer are enabled. In such cases, the Exploratory Search Engine and the Synthesizer are enabled only at link-time. The *MCompiler* framework handles flags for macro definitions, paths to header files and libraries for linking, etc. similar to other compilers.

#### 2.5 Loop Extraction Phase

The loop extractor is implemented using ROSE, a source-to-source compiler infrastructure [119], and is inspired by the loop extractor described in the work by Chen et. al. [37] that encapsulate loop nests into standalone executables.

The Extractor works in three phases. First, it traverses the abstract syntax tree (AST) and locates the **for** loop nests that are eligible for extraction. Second, the extractor creates a new file for this loop, adds necessary headers and macro definitions in the hotspot file, and also adds **extern** declarations for global variables and global functions, as well as for functions called in the scope of the loop body. It encloses the loop body in a function definition with parameters being the variables and pointers to the data structures required by the loop body in order to compile and run correctly. Third, in the base file's AST it replaces the loop body with a function call (with required arguments) and adds an **extern** declaration to this function. Finally, it generates the modified base source file and the new hotspot files.

A sample hotspot file for the main kernel from Polybench's Matrix Multiplication benchmark is shown in listing 2.4.

Listing 2.4: Loop Nest extracted from Polybench's Matrix Multiplication Benchmark

```

1 void gemm_kernel_gemm_line89(int* ni_primitive, int* nj_primitive, int*

nk_primitive, double* alpha_primitive, double* beta_primitive, double C

[2000][2300], double A[2000][2600], double B[2600][2300]){

2

int ni = *ni_primitive;

3

int nj = *nj_primitive;

int nk = *nk_primitive;

4

double alpha = *alpha_primitive;

5

6

double beta = *beta_primitive;

#pragma scop

7

for(int i = 0; i < ni; i++) {</pre>

8

for(int j = 0; j < nj; j++) {</pre>

9

10

C[i][j] *= beta;

}

11

for(int k = 0; k < nk; k++) {

12

13

for(int j = 0; j < nj; j++) {</pre>

C[i][j] += alpha * A[i][k] * B[k][j];

14

}

15

}

16

17

}

#pragma endscop

18

19

*ni_primitive = ni;

20

*nj_primitive = nj;

*nk_primitive = nk;

21

```

```

22 *alpha_primitive = alpha;

23 *beta_primitive = beta;

24 }

```

A function of the base file from which this kernel was extracted is shown in listing 2.5.

Listing 2.5: Loop Nest replaced by a Function Call for Polybench's Matrix Multiplication Benchmark

```

1 static void kernel_gemm(int ni, int nj, int nk, double alpha, double beta,

double C[2000][2300], double A[2000][2600], double B[2600][2300])

{

2

3

int i;

4

int j;

5

int k;

6

// BLAS PARAMS TRANSA = 'N' TRANSB = 'N'

// A is NIxNK, B is NKxNJ, C is NIxNJ

7

8

// C := alpha * A * B + beta * C,

9

extern void gemm_kernel_gemm_line89(int *ni,int *nj,int *nk,double *

alpha, double *beta, double C[2000][2300], double A[2000][2600], double

B[2600][2300]);

10

gemm_kernel_gemm_line89(&ni,&nj,&nk,&alpha,&beta,C,A,B);

11 }

```

While traversing the AST for eligible loop nests, the extractor skips loop nests with irregular control flow that hinders extraction, i.e., contains **return** and **goto** statements. Also, it skips loop nests with calls to static functions and static variables since those properties hinder their usage in the new hotspot files.

The extractor generates two versions for each hotspot file, where one version is instrumented to collect the execution time for the loop nest. This version is used during the Exploratory Search phase. The other version does not contain any instrumentation code and is used to generate the final executable for the applications.

#### Function Definition enclosing the Loop Nests

The extractor generates the list of variables, with their data types, used inside the scope of the loop body. All primitive data types (int, float, etc.) are passed by reference, as well as the user-defined types such as arrays, structs and typedefs. The extractor also does an optimization to maintain properties of the loop from the point of view of the code optimizers. This optimization copies the function parameters of primitive types (passed by reference) into local variables (with same names as original variables) before the loop body and correspondingly copies the local variables into the function parameters at the end of the loop body. This optimization prevents any change to loop body and is also critical to performance since usage of pointers can prevent some code optimizations.

The extractor also annotates loop nests with pragma scop/endscop so as to aid sourceto-source Polyhedral optimizers, such as Pluto, in locating Static Control Parts (SCoP)[47, 48]. If the loop nest was indeed not a SCoP, then Polyhedral optimizers can't optimize them. The framework will recognize that in the Optimization Phase and discard Polyhedral optimizers as a candidate for those loop nests. For loop nests with OpenMP directives, the extractor moves the directives with loop body and sanitizes the clauses of variables that are not present in the scope of the loop nest. For OpenMP for loops that are enclosed in a omp parallel region, extracting the loop body with omp for directive doesn't change the behavior of the program. One issue with extracting OpenMP for loops that are enclosed in a parallel region in such manner is that in the presence of threadprivate variables, synthesizer encounters a link-time error because compilers may generate different symbols for the same threadprivate variable.

## 2.6 Optimization Phase

The framework currently uses five candidate code optimizers: Intel's icc, GNU's gcc, LLVM clang, LLVM based polyhedral loop optimizer Polly and source-to-source polyhedral loop optimizer Pluto. icc is chosen as the default compiler because its performance is, on average, the best of the compilers included, as the results show in Chapter 3. It is also used to compile source files generated by a source-to-source loop optimizer, i.e., Pluto. Table 2.2 shows the flags used for optimizing loop nests for serial execution and parallel execution. These flags also include target architecture specific flags to enable optimizations that can generate better performing code on the specific architecture. For OpenMP applications, flags from serial configuration are used in addition to the OpenMP flags. The optimizer can

| Compiler                             | Version | Optimization Flags                       | Auto-<br>Parallelization |  |

|--------------------------------------|---------|------------------------------------------|--------------------------|--|

| clang (LLVM)                         | 10.0.0  | -O3 -march=native                        | No                       |  |

| gcc (GNU)                            | 10.1.0  | -Ofast -march=native                     | No                       |  |

| icc (Intel)                          | 19.1.0  | -Ofast -xHost                            | Yes (-parallel)          |  |

| Domain<br>Specific<br>Optimizer      | Version | Optimization Flags                       | Auto-<br>Parallelization |  |

| pluto<br>(source-to-source)<br>+ icc | 0.11.4  | tile                                     | Yes (parallel)           |  |

| polly (LLVM)                         | 10.0.0  | -polly-tiling<br>-polly-vectorizer=polly | Yes (-polly-parallel)    |  |

Table 2.2: Compilers and Domain Specific Optimizers integrated in the *MCompiler* Framework.

compile hotspot files and base files in parallel. This is similar to -j option of Makefiles, but here all candidate code optimizers are invoked in parallel to compile the source files. This reduces the overall compilation time for the *MCompiler* framework. The optimizer generates multiple executables of the application (with instrumentation code) where each executable is completely compiled and linked by a candidate code optimizer.

## 2.7 Exploratory Search Phase

The Exploratory Search Engine invokes executables generated by the code optimizers oneby-one and performs multiple runs for stable data, if requested. Exploratory Search Engine at the end of each execution collects the information for each of the loop nests and forwards it to the Synthesizer. For applications that need input through command line, the Exploratory Search Engine runs the application with the input given to the *MCompiler* framework using a --input flag.

## 2.8 Synthesis Phase

The synthesizer compares the collected execution times for each loop nest from different code optimizers and chooses the code optimizer that performed the best as the most suited code optimizer. For loop nests with no information, i.e., the code that was not executed during Exploratory Search phase, the default compiler is used. The synthesizer then generates the final executable that contains no instrumentation code. For an OpenMP application, the synthesizer links OpenMP runtime libraries that are used by different compilers, e.g., icc and clang use compatible OpenMP runtime libraries whereas gcc doesn't. Therefore, for example, if for an application *MCompiler* chooses a omp parallel for region from icc and another from gcc, then the parallel regions will be executed by different OpenMP runtime libraries. Static libraries specific to compilers are also linked to successfully generate the final executable.

| <pre>\$ MCompiler<br/>Usage: MCompiler [options]<br/>Options:<br/>h,help<br/>[no]extract<br/>[no]profile<br/>[no]synthesize<br/>adv-profile<br/>predict<br/>energy<br/>test<br/>parallel</pre> | <pre>file1 [file2] Print usage Extract hotspots Profile extracted hotspots Combine best performing hotspots to generate binary Advanced Profiling Predict candidate using ML Choose most energy efficient candidate Test performance compared to other compilers optimized code Generate multi-threaded code based on OpenMP directives</pre> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|