# UCLA UCLA Electronic Theses and Dissertations

### Title

A Multi-Accelerator Architecture for Photon Mapping

**Permalink** https://escholarship.org/uc/item/3bc9k638

Author Pan, Seung hyun

Publication Date 2014

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# A Multi-Accelerator Architecture for Photon Mapping

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

## Seung hyun Pan

2014

© Copyright by Seung hyun Pan 2014

### Abstract of the Dissertation

# A Multi-Accelerator Architecture for Photon Mapping

by

### Seung hyun Pan

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2014 Professor Miloš D. Ercegovac, Chair

Real-time rendering of photorealistic images has always been an important goal in Computer Graphics. The most computationally expensive part of this process is obtaining the effects of global illumination. Photon mapping is a well-known technique for calculation of realistic global illumination, and also shows characteristics which we believe make it favorable for dedicated hardware acceleration.

Online arithmetic is a digit-serial form of arithmetic, where input vectors are processed from the most significant digit down to the least, and the result is also produced one digit at each step. Pipelined online arithmetic circuits are extremely regular while only requiring simple calculations between registers, which allows for high clock speeds and low power dissipation with a huge potential for parallel execution.

Combining these two concepts, we design and evaluate MAPM (Multi-Accelerator for Photon Mapping), a multi-accelerator architecture that employs pipelined online arithmetic to accelerate the two most time consuming operations in photon mapping: the tree search and shader operation. On a VHDL implementation, we perform behavioral verification using ModelSim, examine hardware cost with Synopsys tools and evaluate throughput gain and scalability of the architecture using a custom built cycle-accurate simulator based on the Intel Pin tool.

By employing two MAPMs set to a configuration of 16 Tree Search Modules, 16 Shader Operation Modules and 2 Shader Operation Accelerators per Shader Operation Module, we observed a throughput increase of  $1384 \times$  over an optimized software setup, and an increase of  $4.78 \times$  over a recent MPSoC implementation. This is achieved using an acceptable hardware cost of 28.8% of the bandwidth, 22.2% of the area, and 5.6% of the power consumption of the low-end Intel Celeron G1820T.

The MAPM also shows a significant reduction in power dissipation. Compared to a conventional parallel circuit with equivalent functionality, the MAPM showed a synthesizable clock speed at about  $3.5\times$ , dynamic power consumption of  $0.104\times$ , and area cost of  $1.799\times$ .

The dissertation of Seung hyun Pan is approved.

Yuval Tamir

Glenn Reinman

Behzad Razavi

Miloš D. Ercegovac, Committee Chair

University of California, Los Angeles 2014

To my father and mother, who have nurtured me with unending love into the person I am today. For that, I am eternally grateful.

## TABLE OF CONTENTS

| 1        | Intr | roducti | $\operatorname{ion}$                                          | 1         |

|----------|------|---------|---------------------------------------------------------------|-----------|

|          | 1.1  | Main    | research problem                                              | 2         |

|          | 1.2  | Contr   | ibutions of this dissertation                                 | 4         |

|          |      | 1.2.1   | Collaborator contribution                                     | 6         |

|          | 1.3  | Organ   | nization of dissertation                                      | 7         |

| <b>2</b> | Bac  | kgrou   | nd and related work                                           | 8         |

|          | 2.1  | Rende   | ering algorithms                                              | 8         |

|          |      | 2.1.1   | Rasterization                                                 | 9         |

|          |      | 2.1.2   | Ray tracing                                                   | 10        |

|          |      | 2.1.3   | Photon mapping                                                | 11        |

|          | 2.2  | Hardw   | vare acceleration for photon mapping                          | 14        |

|          | 2.3  | Previo  | bus work on photon mapping using online arithmetic $\ldots$ . | 15        |

|          | 2.4  | Online  | e arithmetic                                                  | 17        |

|          |      | 2.4.1   | Timing of online arithmetic circuits                          | 17        |

|          |      | 2.4.2   | Online arithmetic applications                                | 20        |

| 3        | The  | e Mult  | i-Accelerator architecture                                    | <b>21</b> |

|          | 3.1  | Photo   | on mapping algorithm overview                                 | 21        |

|          |      | 3.1.1   | Goal of the algorithm                                         | 21        |

|          |      | 3.1.2   | Input data                                                    | 22        |

|          |      | 3.1.3   | The KD-tree                                                   | 24        |

|          |      | 3.1.4   | Building the photon KD-tree                                   | 25        |

|     | 3.1.5  | Final gathering and query points                                           | 30 |

|-----|--------|----------------------------------------------------------------------------|----|

|     | 3.1.6  | Tree Search and Shader Operation                                           | 31 |

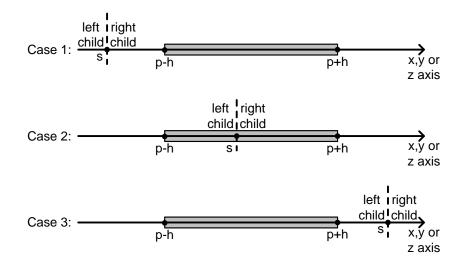

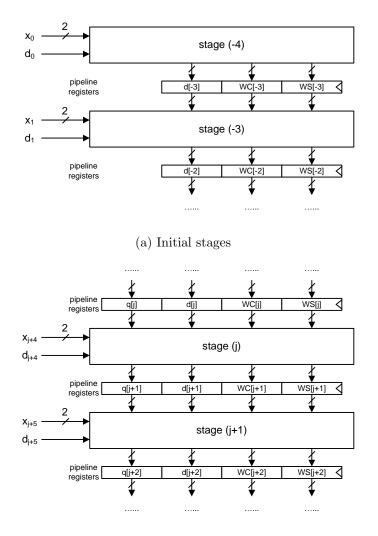

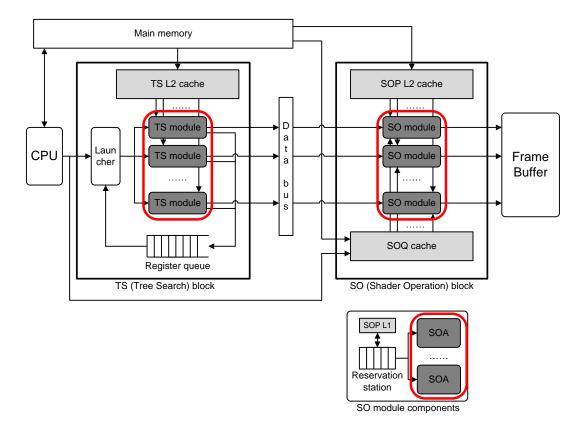

| 3.2 | Archit | cecture overview                                                           | 38 |

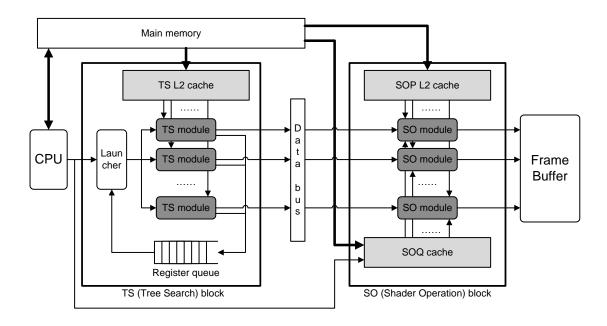

| 3.3 | The T  | ree Search block                                                           | 42 |

|     | 3.3.1  | Overview                                                                   | 42 |

| 3.4 | The T  | ree Search Accelerator (TSA)                                               | 54 |

|     | 3.4.1  | Problem outline                                                            | 54 |

|     | 3.4.2  | Overall structure                                                          | 55 |

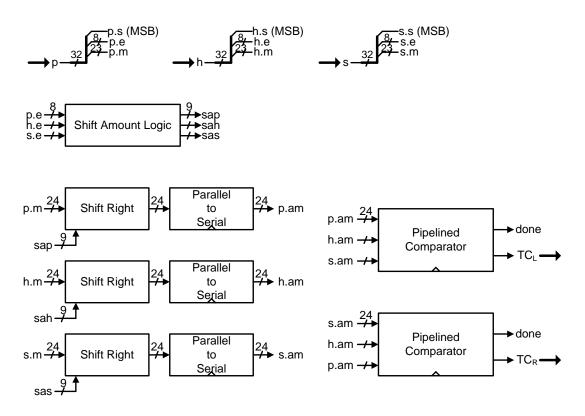

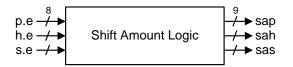

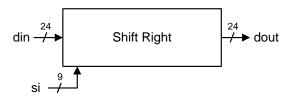

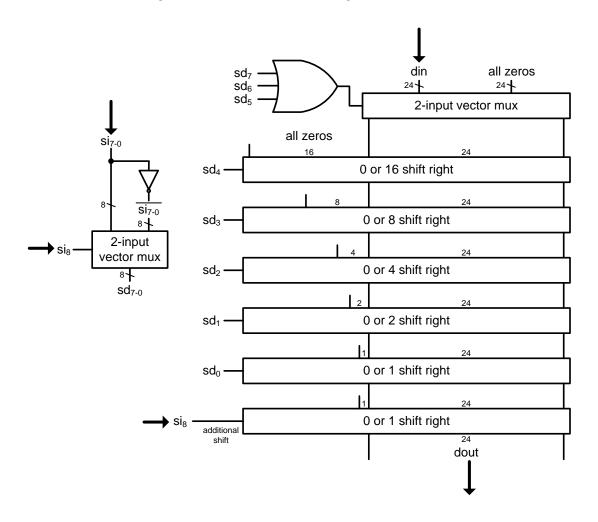

|     | 3.4.3  | Submodule : Shift Amount Logic                                             | 57 |

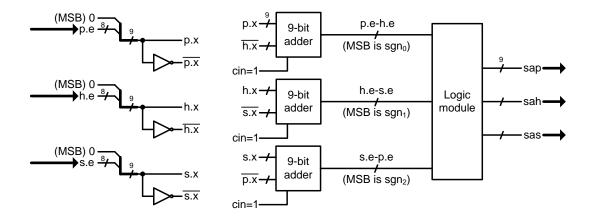

|     | 3.4.4  | Submodule : Shift Right                                                    | 63 |

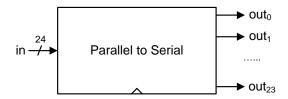

|     | 3.4.5  | Submodule : P2S (Parallel to Serial)                                       | 66 |

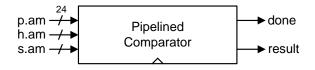

|     | 3.4.6  | Submodule : Pipelined Comparator                                           | 68 |

| 3.5 | The S  | hader Operation block                                                      | 77 |

|     | 3.5.1  | Overview                                                                   | 77 |

|     | 3.5.2  | The two caches of the SO block $\ldots \ldots \ldots \ldots \ldots \ldots$ | 79 |

| 3.6 | The S  | hader Operation Accelerator (SOA)                                          | 82 |

|     | 3.6.1  | Problem definition                                                         | 82 |

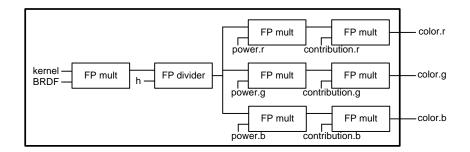

|     | 3.6.2  | Calculation trees                                                          | 83 |

|     | 3.6.3  | Overall structure                                                          | 87 |

|     | 3.6.4  | Submodule : P2S (Parallel to Serial)                                       | 87 |

|     | 3.6.5  | Submodule : ADD8 (Parallel Adder)                                          | 87 |

|     | 3.6.6  | Submodule : MUL24 (Pipelined Online Multiplier) $\ldots$                   | 88 |

|     | 3.6.7  | Submodule : DIV24 (Pipelined Online Divider) $\ldots$                      | 93 |

|     | 3.6.8  | Critial path delay                                                         | 99 |

|              | 3.7          | Cycle stalls                                                                                                        |  |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------|--|

| 4            | 4 Evaluation |                                                                                                                     |  |

|              | 4.1          | Tools used in the evaluation and design                                                                             |  |

|              |              | 4.1.1 Software environment                                                                                          |  |

|              |              | 4.1.2 Cycle accurate simulation                                                                                     |  |

|              |              | 4.1.3 Cache sizes                                                                                                   |  |

|              |              | 4.1.4 Benchmark images                                                                                              |  |

|              | 4.2          | ASIC synthesis and hardware cost                                                                                    |  |

|              | 4.3          | Performance evaluation and scalability 116                                                                          |  |

|              |              | 4.3.1 Target performance numbers                                                                                    |  |

|              |              | 4.3.2 Design space exploration                                                                                      |  |

|              |              | 4.3.3 Throughput evaluation                                                                                         |  |

| 5            | Sun          | mary and future work                                                                                                |  |

|              | 5.1          | Summary                                                                                                             |  |

|              | 5.2          | Future work                                                                                                         |  |

| 6            | List         | of abbreviations and commonly used terms                                                                            |  |

|              | 6.1          | Abbreviations                                                                                                       |  |

|              | 6.2          | Mathematical expressions                                                                                            |  |

| $\mathbf{R}$ | efere        | $nces \ldots 140$ |  |

# LIST OF FIGURES

| 19 |

|----|

|    |

| 19 |

| 23 |

| 25 |

| 33 |

| 33 |

| 39 |

| 42 |

| 44 |

| 47 |

| 48 |

| 52 |

| 56 |

| 57 |

| 58 |

| 60 |

| 63 |

| 65 |

| 66 |

| 67 |

| 68 |

|    |

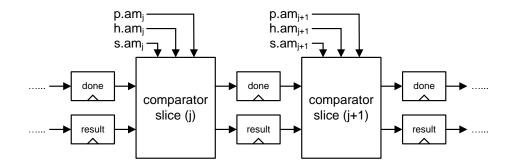

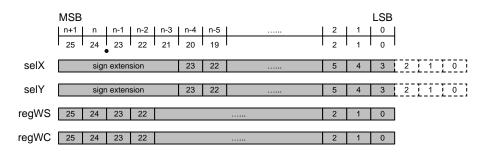

| 3.20 | Partial view of pipelined slices                                                                       | 69  |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 3.21 | Components for Comparator slice (adapted from [47])                                                    | 76  |

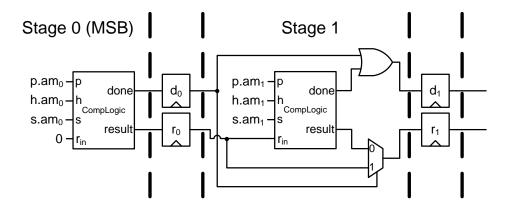

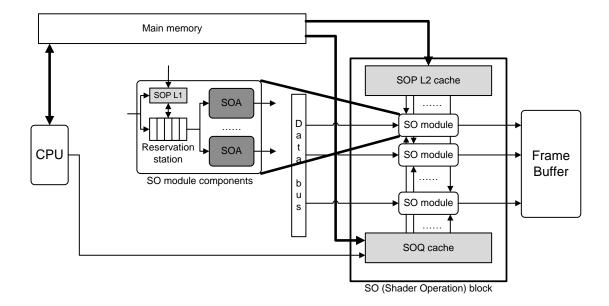

| 3.22 | The SO block                                                                                           | 77  |

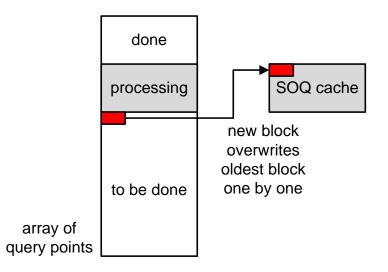

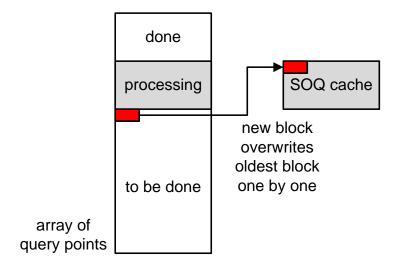

| 3.23 | Cache operation for the SOQ cache                                                                      | 81  |

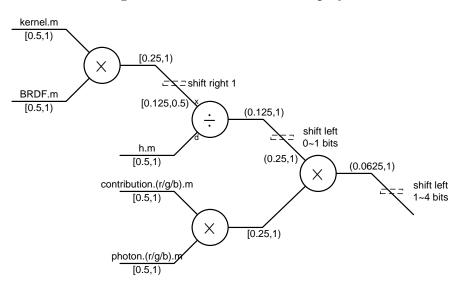

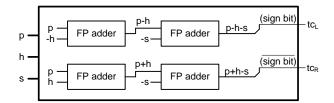

| 3.24 | Calculation tree for mantissa                                                                          | 83  |

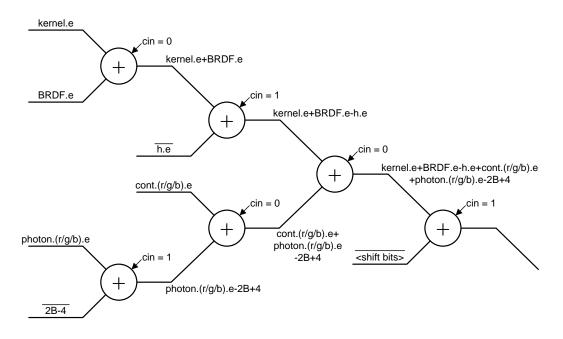

| 3.25 | Calculation tree for exponent                                                                          | 85  |

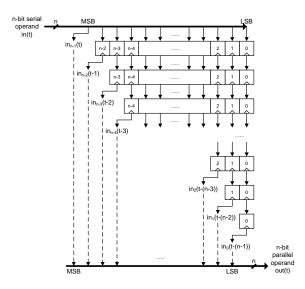

| 3.26 | Components of Parallel to Serial                                                                       | 87  |

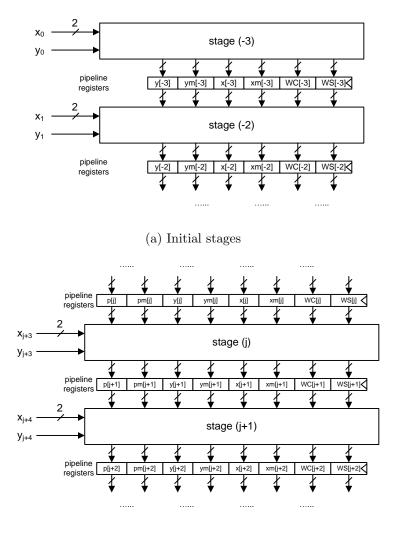

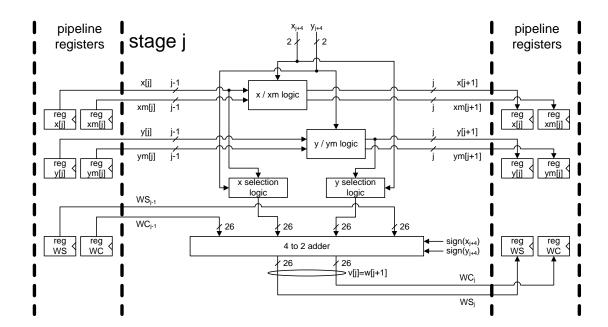

| 3.27 | Online multiplier pipeline stages overview                                                             | 90  |

| 3.28 | Initialize stage details of a pipelined online multiplier (adapted from                                |     |

|      | $[16])  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                               | 91  |

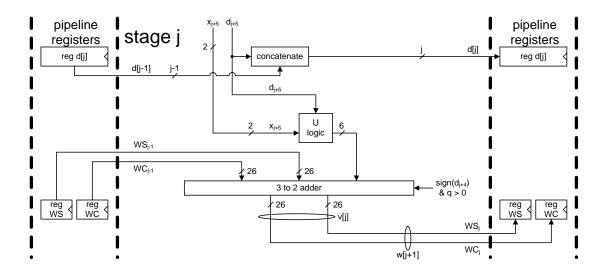

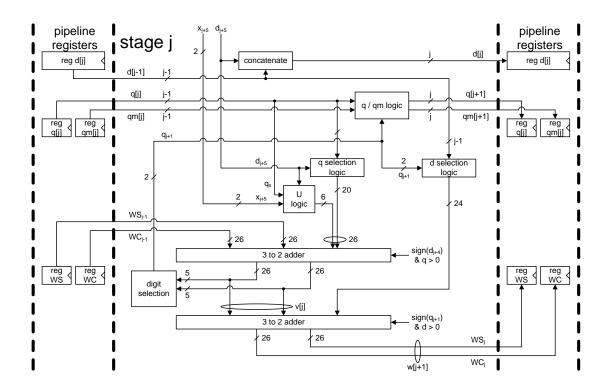

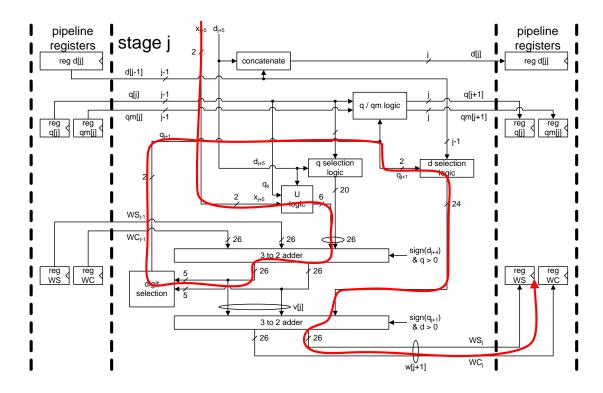

| 3.29 | Recurrence stage details of a pipelined online multiplier (adapted                                     |     |

|      | from [16])                                                                                             | 92  |

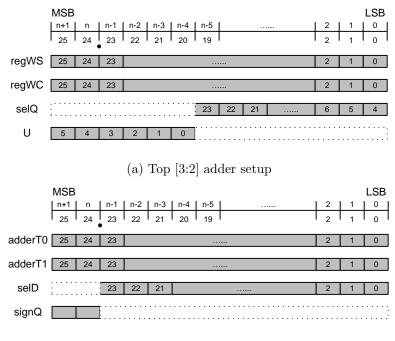

| 3.30 | $\left[4{:}2\right]$ adder setup for a 24-bit online multiplier (adapted from $\left[16\right]\right)$ | 92  |

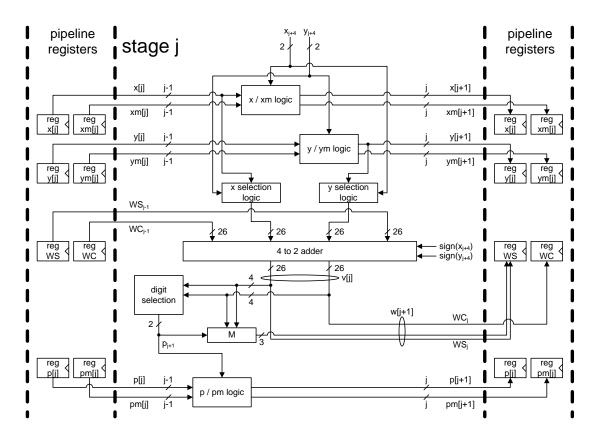

| 3.31 | Online divider pipeline stages overview                                                                | 96  |

| 3.32 | Initialize stage details of a pipelined online divider (adapted from $[16]$ )                          | 97  |

| 3.33 | Recurrence stage details of a pipelined online divider (adapted from                                   |     |

|      | $[16])  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                               | 97  |

| 3.34 | [3:2] adder setup for a 24-bit online divider (adapted from $[16])$                                    | 98  |

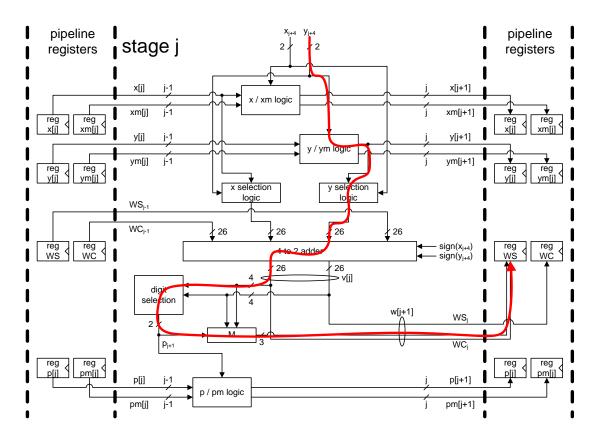

| 3.35 | Critical path for the online multiplier                                                                | 100 |

| 3.36 | Critical path for the online divider                                                                   | 101 |

| 4.1  | Operation of the SOQ cache                                                                             | 107 |

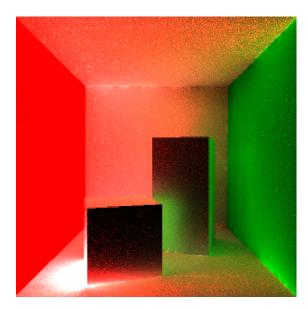

| 4.2  | Benchmark 1 - Cornell box (adapted from [19])                                                          | 110 |

| 4.3  | Benchmark 2 - Sponza corridor (model by Marko Davrovic)                                                | 111 |

| 4.4  | Benchmark 3 - Sponza atrium (model by Marko Davrovic)                                                  | 112 |

| 4.5  | FloPoCo implementation of the TSA                                       | 114 |

|------|-------------------------------------------------------------------------|-----|

| 4.6  | FloPoCo implementation of the SOA                                       | 114 |

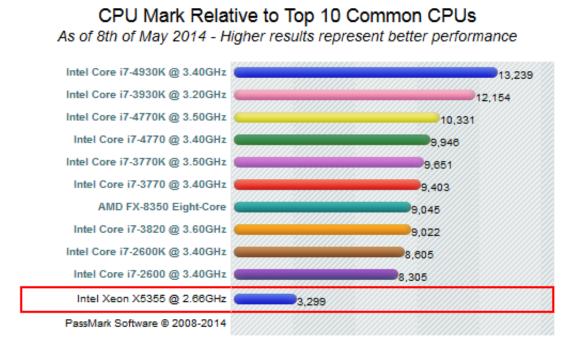

| 4.7  | CPU performance benchmark number comparison                             | 119 |

| 4.8  | Replicable modules in the MAPM                                          | 120 |

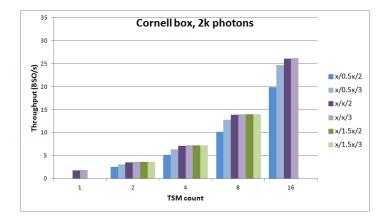

| 4.9  | Throughput for Cornell box, 2k photons (BSO/sec) $\ldots \ldots \ldots$ | 121 |

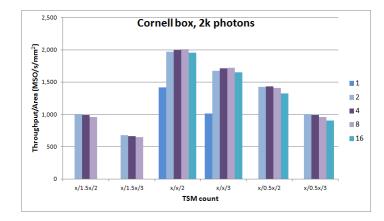

| 4.10 | Throughput/area for Cornell box, 2k photons (MSO/sec/ $mm^2$ ) .        | 123 |

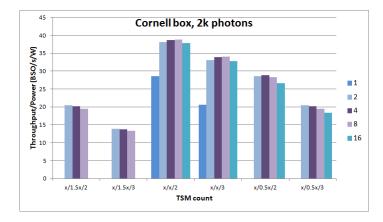

| 4.11 | Throughput/power for Cornell box, 2k photons (BSO/sec/W) $$ .           | 123 |

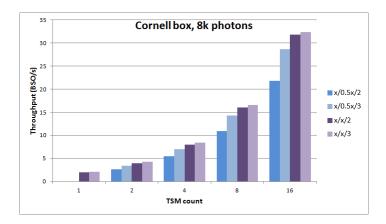

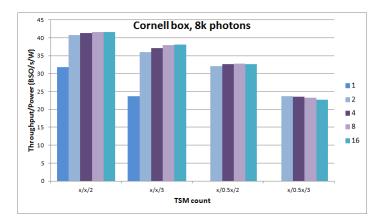

| 4.12 | Throughput for Cornell box, 8k photons (BSO/sec) $\ . \ . \ . \ .$      | 127 |

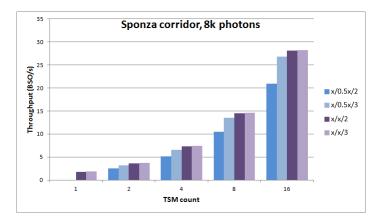

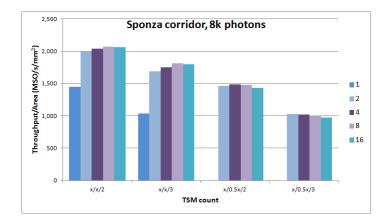

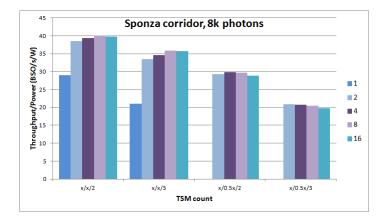

| 4.13 | Throughput for Sponza corridor, 8k photons (BSO/sec)                    | 127 |

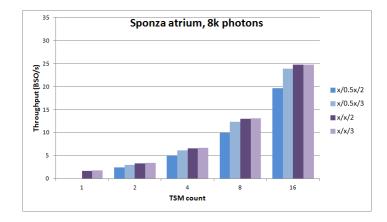

| 4.14 | Throughput for Sponza atrium, 8k photons (BSO/sec) $\ . \ . \ .$ .      | 127 |

| 4.15 | Throughput/area for Cornell box, 8k photons $({\rm MSO/sec}/mm^2)~$ .   | 128 |

| 4.16 | Throughput/power for Cornell box, $8k$ photons (BSO/sec/W) $$           | 128 |

| 4.17 | Throughput/area for Sponza corridor, 8k photons (MSO/sec/ $mm^2$ )      | 129 |

| 4.18 | Throughput/power for Sponza corridor, 8k photons (BSO/sec/W)            | 129 |

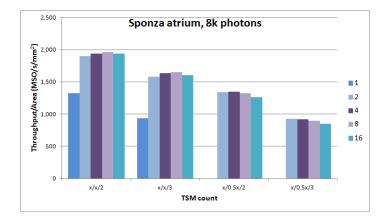

| 4.19 | Throughput/area for Sponza atrium, 8k photons (MSO/sec/ $mm^2)$         | 129 |

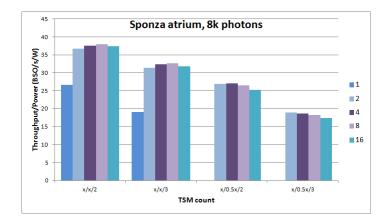

| 4.20 | Throughput/power for Sponza atrium, $8k\ photons\ (BSO/sec/W)$ .        | 130 |

# LIST OF TABLES

| 3.1        | Tree contents for the example photon tree                             | 30         |

|------------|-----------------------------------------------------------------------|------------|

| 3.2        | Inequality for each sign bit                                          | 60         |

| 3.3        | Determining largest exponent                                          | 62         |

| 3.4        | Output logic according to largest exponent                            | 63         |

| 3.5        | Possible output combinations of the comparator $\ldots \ldots \ldots$ | 69         |

| 3.6        | Logic table for comparator slice (adapted from $[47]$ )               | 74         |

| 3.7        | Truth table of comparator slice circuit (adapted from [47]) $\ldots$  | 75         |

| 3.8        | Required parameters for a single SO                                   | 80         |

| 3.9        | Digit selection table for online multiplier (adapted from $[16]$ )    | 93         |

| 3.10       | U module output for redundant $x$ and non-redundant $d$ (adapted      |            |

|            | from [16])                                                            | 99         |

| 4.1        | Required inputs for a single SO                                       | 106        |

| 4.2        | Cache setup for simulations                                           | 109        |

| 4.3        | Synthesis results for a single SOA                                    | 113        |

| 4.4        | Synthesis results for a single TSA                                    | 113        |

| 4.5        | FloPoCo components for Tree Search and Shader Operation               | 115        |

| 4.6        | Comparison of synthesis results                                       | 115        |

|            |                                                                       |            |

| 4.7        | Comparison with normalized numbers                                    | 116        |

| 4.7<br>4.8 | Comparison with normalized numbers                                    | 116        |

|            |                                                                       | 116<br>122 |

|            | Total cycles and throughput for different TSM/SOM/SOA config-         |            |

| 4.11 | Total cycles and throughput for different benchmark scenes | 126 |

|------|------------------------------------------------------------|-----|

| 4.12 | Specifications of select Intel Haswell CPUs                | 131 |

| 4.13 | Cache simulation results for bandwidth evaluation          | 132 |

#### Acknowledgments

First and foremost, I am sincerely grateful and forever indebted to my advisor, Professor Miloš D. Ercegovac, for without him none of this work would have been possible. Ever patient and focused, with a sparkling sense of humor, he was an inspiration and role model throughout my grad school years. The years of learning from him has indeed been an awe-inspiring experience which I shall never forget all my life.

I also wish to thank my committee Professors. I have learned so much from all my classes with Professors Yuval Tamir and Glenn Reinman, both attending and working as a TA. Thanks to Professors Bezhad Razavi and Dejan Marković, who were kind enough to attend my oral exams and offer their insights and moral support. Their feedback was crucial in raising the scientific integrity of my dissertation.

A huge thank you goes to Shawn Singh, whose joint work with me has been the firm basis of my dissertation work. On top of that, his friendship and hours of work and discussion that we shared was an essential part of this project. I also extend thanks to my labmates and fellow CS students past and present, wonderful people who would always help me with anything and everything without question; in no particular order, Suk-bok Lee, Seung Hoon Lee, Sung Chul Choi, Pouya Dormiani, Hojat Parta, Seok Won Heo and Young-kyu Choi.

Special thanks to my family also, whose unending love is always a warm haven even in the gloomiest of times. My dear mother and father who are always worrying over and praying for me from afar, and my only brother who I know always has my back. And my profound gratitude to my fiancée, who has stood beside me during all the dark hours, even through the burden of her own inspiring research work. Without her support, there is no doubt that this would have been a much harder and less successful journey for me.

There are countless people that have helped and supported me throughout my grad school years, so many that I do not have enough space here to thank individually. Also for anyone that I may have carelessly overlooked, please know that you all have my most sincere word of thanks, and no one was left out on purpose. This dissertation is not a mere token of my personal accomplishment; it is truly a monument that represents how fortunate I am to have all the great people that are around me.

### VITA

2006 B. S., Electrical Engineering, Seoul National University Seoul, Republic of Korea.

## PUBLICATIONS

S. Singh, S. h. Pan, and M. Ercegovac, "Accelerating the Photon Mapping Algorithm and its Hardware Implementation," in *Application-Specific Systems*, *Architectures and Processors (ASAP)*, 2011 IEEE International Conference on, September 2011, pp. 149–157.

## CHAPTER 1

## Introduction

Rendering photorealistic high-quality images in real-time has long been an important and classic goal in Computer Graphics. Due to a rising demand on applications such as interactive entertainment, virtual reality, and 3D displays, the need for fast high-quality image rendering is rapidly on the rise.

In general, the mechanism of how light travels through the physical environment and reaches the optic nerves in the retina of human eyes is well known. To achieve photorealistic rendering, it is necessary to calculate the effects of light transmission to emulate the physics of light, by a precise yet feasible method. The main obstacle is the massive amount of calculation that is required in order to obtain high-quality rendering. The main bulk of the calculation load is the process required for obtaining the effects of global illumination. To calculate this, one needs to consider light reflections from all parts of the scene that end up at points visible in the final image.

Current solutions usually fall in one of the two groups; one, they offer highquality imagery but is too slow for real-time, or two, their throughput is good enough for real-time but the light emulation is approximated and thus produce images that are not photorealistic. The two most common rendering algorithm classes are rasterization-based approaches and ray tracing-based approaches [59]. The rasterization-based approach is a very fast but physically approximated method, where it goes through each polygon in the scene one by one to determine the color of each pixel in the final image. By making use of the inherent parallelism in this operation, rasterization has seen a lot of success by running on graphics processing units (GPUs) for massively parallel execution. On the other hand, ray tracing-based methods emulate physical light rays more accurately, and can produce extremely realistic light effects. This makes ray tracing a better candidate for the goal of high-quality global illumination. The main drawback of ray tracing algorithms is that it is comparatively slower than rasterization methods, where even with all the algorithmic advances and improved hardware support, current performance of ray tracing is still a few magnitudes away from our ultimate goal of real-time photorealistic rendering.

Photon mapping [28] is a ray tracing-based approach which we believe to be an efficient method for global illumination calculation, and also shows promise of showing real time performance [52]. The focus of this dissertation will be on the design and verification of an application-specific accelerator for obtaining massively parallel execution of the photon mapping rendering algorithm. By using digit-serial online arithmetic, we can process a large amount of pipelined concurrent operations, in addition to parallel execution using multiple instances of execution modules. Additionally, the simple and structurally regular circuits of online arithmetic allows for a fast clock speed and low power consumption.

### 1.1 Main research problem

Regarding our final goal, let us examine some numbers regarding actual performance for current systems. Full HD, which is also referred to as the 1080p, is a widely used mode for screen resolutions. This uses a widescreen aspect ratio of 16:9, with a resolution of 1,920 pixels wide by 1,080 high, which is 2,073,600 pixels total. Full HD is a commonly used standard for various multimedia applications, including digital films, HDTV, and the most recent generation of video game consoles. For photon mapping in general, the number of final gather rays (FGRs) that need to be calculated for each pixel is around 600 to 4,255 as noted in [24]. From these numbers, we can calculate the maximum number of total rays for Full HD to be 2,073,600  $\times$  4,255 = 8,823,168,000, which is almost 9 billion rays. If we can get a throughput capable of calculating around 10 billion rays per frame at around 20-30 frames per second, this would be enough performance to achieve real-time rendering for this resolution. We can consider this as the minimum performance required for real-time photorealistic image rendering in Full HD.

As a side note, future applications will need to consider 2160p (4K UHD) and 4320p (8K UHD). 2160p has a resolution of 3,840 pixels wide by 2,160 high, which is 8,294,400 pixels total, which is 4 times the count of 1080p. And 4320p has a resolution of 7,680 pixels wide by 4,320 high, which is 33,177,600 pixels total, which is 16 times the count of 1080p. These will obviously have a higher ray process requirement compared to those of the 1080p.

Regarding the goal of 10 billion rays per frame, let us consider the following points:

- As can be seen in the International Technology Roadmap for Semiconductors annual report [27], speedup obtained from the advancement of CMOS technology is subtly but surely slowing down. This trend is evident as a lot of recent processors do not obtain speedup from increased clock time but through an increased number of cores or processing units, and increasing the amount of parallel work that the processor can efficiently handle at the same time. Simply waiting for the hardware to improve to the necessary performance point is not a viable solution, even before we consider the amount of time it will take to get there.

- Looking at [59], we can see that a wide range of algorithmic improvements have been thoroughly explored for ray tracing. However, the amount of re-

quired processing is still too much to overcome by purely algorithmic methods. As mentioned in [63], performances of up to several hundred million rays per second is expected to be reachable in a few years, but this still falls a few magnitudes short of the performance goal for real-time photorealistic rendering in Full HD.

- There have been attempts to implement photorealistic photon mapping in real time as we shall examine in more detail in 2.2, but the current methods still come short of our performance goal.

- While parallelism will definitely be one of the techniques that we will need to utilize, the work necessary for the handling of each individual thread is far too complex and slow that this performance goal cannot be achieved by simply employing a large number of duplicate execution modules that are avaliable.

Considering these points, to move closer to realizing the goal of real-time photorealistic image rendering, one of the the main issues that we need to tackle is improving the efficiency of resource usage overall, including power, area, and memory bandwidth.

In order to achieve this goal, we propose an accelerator architecture with application-specific modules which can speed up each individual thread, and can be run in parallel to get high throughput. The main goal of this dissertation is to design and evaluate an application specific Multi-Accelerator for Photon Mapping (MAPM) architecture.

### 1.2 Contributions of this dissertation

In this dissertation, we develop and analyze a hardware design for accelerating the 3D rendering algorithm of photon mapping. For the realization of this end target, we worked on the following tasks.

1. Novel architecture and design The MAPM focuses on the back-end part of the photon mapping process, where all data structures are complete and processing them is all that remains. The MAPM is a co-processor like structure; it shares data paths to the main memory with the CPU, receives new instructions from the CPU, and outputs the results to the frame buffer or the main memory. For the detailed design, we need to consider where the actual calculation is processed, which data is utilized at that point, and all required data paths needed to supply this information.

The Tree Search logic module design is adapted from [47], and online multiplier and divider designs are adapted from [16].

2. HDL implementation After the details of the design are finalized, it is vital to make sure the design functions as intended. To do this, the MAPM design is implemented using VHDL. Key components have gone through rigorous behavioral verification with ModelSim using test benches with Python generated inputs.

After making sure that the functionality of the design is valid, we obtained ASIC hardware cost numbers by synthesizing the VHDL designs using Synopsys Design Compiler.

3. Cycle-accurate simulation To examine how well the MAPM scales, and to obtain more detailed performance numbers from cycle count, we built a cycle-accurate simulator. The simulator was created using Intel Pin libraries [44], an instrumentation tool that allows insertion of arbitrary C++ code in an executable. The Pin tool inserts calls to the simulator into a software photon mapping executable code created in [49], and the simulator returns exact cycle count and cache simulation results.

- 4. Putting it all together With all the information from the tasks listed above, we have enough information to evaluate the MAPM by making detailed comparisons with other recent systems and photon mapping implementations. We compared hardware cost to recent CPUs to verify whether the MAPM's hardware cost is affordable. Also, we evaluated the performance of the MAPM by looking at throughput numbers and comparing it to other recent photon mapping implementations.

- 5. The results In brief, using two MAPMs with a configuration having 16 Tree Search Modules, 16 Shader Operation Modules and 2 Shader Operation Accelerators per Shader Operation Module demonstrated a throughput increase of 1384× over the optimized software implementation of [48], and a throughput increase of 4.78× compared to the MPSoC setup in [17]. This is achieved while only using 28.8% of the bandwidth, 22.2% of the area, and 5.6% of the power consumption of the low-end Intel Celeron G1820T. These results represent the fastest throughput of all photon mapping architectures known to us.

The MAPM also shows a significant reduction in power dissipation. Compared to a conventional parallel circuit with equivalent functionality, the MAPM showed a synthesizable clock speed at about  $3.5\times$ , dynamic power consumption of  $0.104\times$ , and area cost of  $1.799\times$ .

#### 1.2.1 Collaborator contribution

This work is based on research in photon mapping architectures investigated jointly with Shawn Singh in [49]. Ideas and results from his doctoral dissertation [47] have been used in the design of the MAPM. In particular, we used his photon mapping C++ code for the software executable used in the cycle accurate simulation, and his Pin code written for [49] served as a great learning example for writing the cycle-accurate simulator.

### 1.3 Organization of dissertation

The organization of the dissertation is as follows. Chapter 2 examines some background and related work. Chapter 3 briefly introduces the photon mapping algorithm and presents the details of the MAPM architecture. Chapter 4 looks at evaluation methods and results, and Chapter 5 provides a summary and future work.

## CHAPTER 2

## Background and related work

The problem of rendering a 3D scene can be described as follows. Given a description of a scene, where we are given the objects in the scene, light sources, and a camera, we wish to output an image. This image is an array of color information which reflects what the scene will look like as viewed from the camera location.

For this rendering problem, there are two standards we need to consider, which are the quality of the final image, and the time required to produce the image. In general, higher photorealism would require more complex calculations which leads to more time required for processing. Leaving out part of the required processing, or approximating it to reduce time would lead to a drop in the quality of the final image. There already exist algorithms which are oriented to enhancing one of the criteria, but at the cost of a high quality drop in the other criterion.

With this in mind, we examine some of the algorithmic approaches to rendering and offer some justification on our selection of photon mapping.

### 2.1 Rendering algorithms

There are various classes of algorithms which try to solve this rendering problem. Each has its own strengths and weaknesses, and here we shall examine the positive and negative aspects of photon mapping and why we think photon mapping is a great candidate for real-time photorealistic rendering.

#### 2.1.1 Rasterization

Rasterization is a widely used method of rendering due to its high speed. Most of the GPU architectures on the market are based on this.

For each pixel, the rasterization pipeline [18, 39] goes through each polygon in turn and determines whether the polygon intersects a straight line from the camera, and if it does, which one is the closest to the camera point. Once this is determined, the color of the closest point is calculated using shader functions, and the result becomes the pixel color for the final image. A large part of this can be performed independently of each other. For example, comparing the distance to each polygon with the smallest value found so far does not require data from other polygons.

The GPU architecture takes advantage of this instruction independence by having a huge number of simple cores where each instruction is passed through in parallel. Each instruction is assigned to a core on the GPU, leading to massively parallel execution. This leads to a very high throughput performance, to the point where it is possible to get real-time frame rates.

However, rasterization is not a good solution for photorealistic rendering due to a few drawbacks:

1. When using only rasterization, it is difficult to account for secondary rays and physically correct global illumination. The main reason is that rasterization is optimized to calculate visibility of the entire scene from a single camera point, and to obtain illumination from secondary rays, a large number of multiple passes through the pipeline is necessary. This would weaken the timing performance of rasterization, and still likely not yield physically accurate global illumination.

Another way to obtain global illumination using rasterization would be to have some approximation at the shader phase, but again, this would result in a physically inaccurate rendering and would yield lower quality images.

2. The workload does not scale well due to the fact that rasterization needs to go through all polygons to determine visibility from each pixel, therefore having a linear dependency on the number of polygons in the scene. There has been some previous work that tries to deal with this issue such as the irregular z-buffer [29], but a lot of the calculation still ends up not being used in the final image. This affects the scalability of rasterization in terms of the the number of polygons in the scene.

In short, rasterization offers many speed benefits, but for the goal of rendering physically correct photorealistic images, is not a well-suited class of algorithm.

#### 2.1.2 Ray tracing

This brings us to ray tracing, which is a method much more appropriate for physically based rendering than rasterization.

Ray tracing is a rendering method where the actual light paths are traced through the scene using a general ray path calculation. Compared to other rendering methods, ray tracing has the benefit of being able to account for all possible light paths, and this is done with a generalized and unified algorithm, i. e. tracing rays. Ray tracing closely emulates how light physically operates in the real world, which makes it easy to account for various illumination effects such as reflection, refraction, scattering and dispersion. This allows ray tracing to achieve levels of realism not possible in rasterization, making it the most suitable method for photorealistic rendering.

Ray tracing can also reduce the amount of wasted calculation, due to being able to pinpoint parts of the scenery that is directly visible from the camera. From this, ray tracing can eliminate unnecessary processing for areas not used in the final image. This is a weak point for rasterization, where it is difficult to identify which calculations will be used for the final image, and the workload increases linearly with the number of polygons in the scene.

However, the higher quality of rendering comes at the cost of a much larger computation load compared to rasterization. Looking at some recent work, RPU (Ray Processing Unit) by Woop et al. [64] shows a hardware design for an architecture with programmable shaders. On a 66 MHz FPGA, the RPU shows a performance of up to 20 FPS (frames per second) for an image resolution of  $512 \times 384$  pixels using primary rays only. This is around 100 million rays/s for simple scenes with no lighting and shading, and 15 million rays/s for moderately complex scenes with simple lighting. OptiX, a general purpose ray tracing engine by Parker et al. [40] that utilizes GPUs for ray tracing, shows performance of 1.5 FPS on the GTX480 for path tracing, and 4.5 FPS for the less-accurate Whitted-style tracing. While this is quite an advancement, for the goal of photorealistic real-time rendering for Full HD, the state of the art still comes a bit short.

#### 2.1.3 Photon mapping

Photon mapping is a ray tracing based method that is effective for calculating global illumination. It was originally proposed by Jensen [28] as an algorithm for offline rendering. Since then, various research has been carried out, including exploration of algorithmic improvements such as reverse photon mapping [24] and SIMD (Single Instruction, Multiple Data) packets with data reordering [48], and analysis on required cache bandwidth as in [51]. Recently, Singh has shown in his dissertation [47] that compared to other ray tracing methods, photon mapping can produce better quality images from a much smaller number of rays, and it has great potential for a speedup similar to rasterization, as the main workload can be divided up into fine-grain operations. This speedup was explored in the collaborative work [49] where the simulation of an online hardware accelerator shows a potential speedup of  $100 \times$  throughput compared to the software performance.

Instead of treating particles as virtual light sources, photon mapping uses density estimation [46] to compute contribution to a camera point more effectively. By actually creating and bouncing photons around the scene to emulate light transport, photon mapping is also capable of producing a wide range of complex illumination effects. Some examples of light effects that can be captured efficiently using photon mapping are caustics (concentrated patches of light of nearby surfaces), diffuse interreflection (light reflection from diffuse surfaces, example: color bleeding), and subsurface scattering (light enters material and is scattered before being absorbed or reflected).

Photon mapping has the following strong points:

- Compared to other ray tracing algorithms, photon mapping requires a smaller number of rays. As explored in detail in [47], photon mapping can produce a similar or better quality image from processing an order of magnitude smaller number of rays. By using an efficient search data structure such as KD-trees (k-Dimensional trees) [9] to sort through the photons, photon mapping can calculate global illumination by processing a fewer number of rays compared to that of a ray traced image of similar quality.

- 2. The main bulk of photon mapping can be divided into fine-grain operations. The biggest reason for the fast processing speed of rasterization is that each polygon and shader process can be divided up into small independent sections that can be run in a massively parallel manner. Photon mapping is similar in that each search into the data structure and each shader operation can be processed independent of each other. By utilizing this parallelism, photon mapping can be efficiently mapped to separate many-core accelerators to achieve high throughput.

- 3. The number of photons is unlikely to be intractable. Each photon carries information that is highly likely to be used in the final image, and due to

density estimation, processing photons is much more efficient than processing light rays of the same effect [47], allowing us to render higher quality images from a smaller number of samples.

These characteristics all combine to allow a smaller workload, and can be mostly achieved without having to sacrifice the quality of the final image. Therefore, we assert that development of an accelerator to take full advantage of the fine-grain characteristic of photon mapping would be an important step towards real-time photorealistic rendering.

However, there are still a number of obstacles that prevent us from having real-time Full HD photon mapping. For one, processing each ray in photon mapping is more complex compared to other ray tracing methods. Each separate shader operation needs to process a handful of floating-point multiplications and divisions, and simply using conventional floating-point units will not be enough to yield the massive throughput necessary for real-time rendering. Also, photon mapping relies on the KD-tree data structure to accelerate the photon search process and reduce the time spent in searching for shader operations. Unfortunately, building the tree is relatively slow and updates are costly, compared to other data structures used in rendering such as grid accelerators or bounding volume hierarchies [59]. In general, with more time spent in building the data structure, a better search performance can be obtained. The tree build is not a focus of this dissertation, however a lot of research is being done to speed up the KD-tree build, such as speeding up the surface area heuristic used in the tree build [26, 42], utilizing multi-threading and multi-core parallelism [45], adaptive fast rebuilding from the scene graph [11], or motion decomposition [21].

### 2.2 Hardware acceleration for photon mapping

Here we examine some previous work on using hardware to accelerate photon mapping.

In [43] by Purcell et al., photon mapping was implemented on the GPU architecture. Unfortunately, as it was difficult to fit the main search data structure on the old, less programmable GPU architecture, a different search method had to be used, and this affected the overall quality of the image.

Work by Larsen and Christensen in [32] implements photon mapping on a combination of a CPU and GPU. This work uses textures to store global illumination information, and they reduce the number of necessary samples by tracking coherence for frame to frame photon tracing. This works in 35+ FPS for the images in the paper at  $512 \times 512$ , but the need to have multiple passes for each global illumination texture may limit the scalability to larger resolution images.

McGuire and Luebke has an interesting paper in [36], where an algorithm named Image Space Photon Mapping was implemented on an 8-core CPU and a GPU. Rasterization methods are used to produce photons and query points very quickly. The rendering rate is very impressive at up to 26 FPS for Full HD images. However, this is only an estimation of physically based rendering, and no secondary rays are traced, resulting in a low quality image and limiting the method's scalability to photorealism.

T-ReX by Kim et al. [30] also uses a heterogeneous setup of a CPU and a GPU to implement photon mapping. Using decoupled data for each, and progressive photon mapping methods [22], they were able to reduce required data transfer between the CPU and GPU and obtain performance numbers of 3-20 million rays/s with response time at 15-67 ms.

Work by Fallahpour et al. [17] presents a homogeneous MPSoC implementation for photon mapping, which includes the full process including all data structure builds. The maximum performance obtained here is about 639 million cycles to render a  $320 \times 240$  resolution image using an 8x8 ARMv4 core network.

As far as we know, there has not been another approach for accelerating photon mapping using application-specific hardware that utilizes fine-grain parallelism, without heavy approximations which affect the quality of the rendering. In this work, the MAPM approaches this problem using online arithmetic.

# 2.3 Previous work on photon mapping using online arithmetic

Here we look at previous work on accelerating photon mapping using online application-specific hardware.

In the collaborative work [49], we built on the main idea of focusing on the fine-granularity of photon mapping using online arithmetic. We drew the large picture of the co-processor accelerator architecture and implemented the Tree Search Accelerator (TSA) and Shader Operation Accelerator (SOA) modules in detail using VHDL. Using Synopsys tools, hardware cost comparison was done with conventional circuits generated using FloPoCo [10]. Software simulation was done using Pin [5] to obtain instruction count.

The hardware cost comparison at 200 MHz showed a power cost of about 20% and area cost of about 130% compared to conventional circuits. Also, the online implementation synthesis could be synthesized up to 1.5 GHz, while the parallel conventional implementation showed a much slower clock speed. Perfomancewise, simulation results showed a 100× factor throughput improvement over a pure software implementation in [48] while needing an estimated power cost of less than 200 mW, and area cost of around 1% of 150  $mm^2$ .

In Singh's dissertation [47], in addition to the above collaborative work, he

evaluates how photon mapping compares to other ray tracing algorithms in terms of rays traced and output quality, and also shows mathematical proof of the fine-granularity of photon mapping. Also covered in this work is his methods of optimizing the photon mapping algorithm using SIMD data packets with data reordering to enhance cache behavior.

This dissertation expands and elaborates on these previous works by:

- 1. Detailed architecture design In previous work, no details of the architecture surrounding the TSA and SOA were implemented; power and area cost did not take these circuits into account. In this work, all data paths to memory and between modules, and the instruction flow of input parameters through the accelerators are figured out in detail. The arithmetic inside the SOA is implemented in detail, including calculation trees and all bit shifts needed to match the input data range of online operators. All necessary modules are shown with working details so that the TSA and SOA modules created in [49] are supplied with the necessary information and can process the tree search and shader operations.

- 2. HDL implementation With the detailed design for the MAPM figured out, we can now better evaluate the hardware cost. All key modules with any updated design details are implemented in VHDL and their functionality is verified using ModelSim. The SOA especially needs meticulous evaluation, using a large amount of test benches generated with the help of Python [6]. Again, we enlist the help of FloPoCo to implement a conventional parallel circuit with the same functionality, and Synopsys tools to obtain hardware cost numbers.

- 3. Cycle-accurate simulation Cycle-accurate simulation is necessary to evaluate scalability of the MAPM, along with obtaining cycle count and cache bandwidth. The simulator was created in C++ using Intel Pin libraries [44],

carefully taking into account how the internal data would flow through each module in the detailed design.

4. Evaluation With the information we obtain from HDL implementation and cycle-accurate simulation, we have enough information to evaluate the scalability of the MAPM architecture, and compare the performance and hardware cost of the MAPM with other recent solutions.

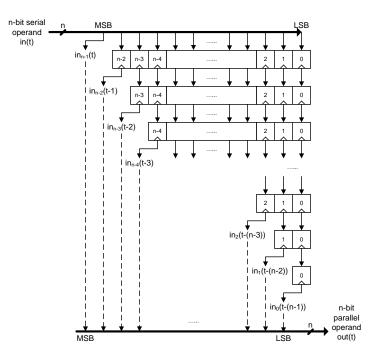

### 2.4 Online arithmetic

Online arithmetic [16] is a digit-serial form of arithmetic, where input vectors are processed digit by digit from the most significant digit down to the least, with the results also being produced one digit at a time. Due to the the digit-serial characteristic of online arithmetic, by using a pipelined form, it is possible to issue one application specific operation every clock cycle. This gives us a large concurrency potential at the operator level even before we consider parallelism by using duplicate accelerators.

#### 2.4.1 Timing of online arithmetic circuits

There are two components to the delay of a single online arithmetic operation [16].

- 1. Initial delay: The initial delay  $\delta$  is also called the online delay. This is the number of additional digits required to determine the value of the first result digit. The first output digit is delivered after  $\delta + 1$  cycles.

- 2. Time to deliver n output digits: After the initial delay, one output digit is delivered every cycle. For the circuit to output n output digits, n cycles is required.

Therefore the cycle delay of a single online operand is  $T_n = \delta + 1 + n$ . These numbers may seem to suggest that the timing characteristics of online arithmetic is worse than traditional arithmetic circuits. However, the main benefit of online arithmetic is that we can easily pipeline the architecture in a digit-serial manner. Combined with the fact that pipelined online arithmetic consists of a very regular structure, with simpler circuits between registers allowing a faster clock speed compared to traditional circuits, this allows for a very high throughput overall.

Also, at first glance, online arithmetic may seem to be adding cycle latency for a single operation. However, the faster clock speed that is possible with online arithemetic more than makes up for the added cycles, and as a result it is possible to actually reduce the latency of a single operation in terms of time, depending on the synthesized clock speed.

Another way that throughput of online circuits can be enhanced is by replication of online modules for calculations with no operation-level feedback loops. For iterations such as y(i) = f(y(i-1)), it is possible to push the throughput rate up to

$$\frac{1}{\text{cycle time}}$$

at the cost of more replicated online modules. This is highly useful as the designer can choose any point between the two extremes for a tradeoff between throughput and hardware cost.

For a compound network of operators, more cycles can be saved for a single operation by starting the next operation before the previous one is finished. Online arithmetic works in a digit-serial method where the inputs are fed into the circuit one digit at a time, and the outputs are also produced digit by digit.

Given the following compound network,

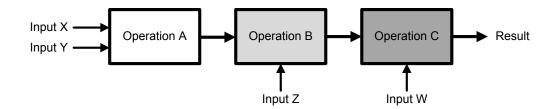

Figure 2.1: An example compound operation

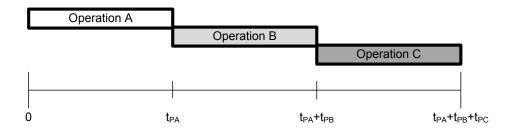

with a conventional parallel arithmetic architecture, we need to wait until the result of Operation A is available. Only then can we start the next operation, which is Operation B. Therefore, the timing diagram for a parallel circuit would look like something shown in figure 2.2. Here,  $t_{PA}$  is the time it takes for Operation A to finish in the parallel operator.

Figure 2.2: Timing diagram of conventional parallel arithmetic

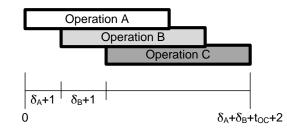

On the other hand, if we use online arithmetic, the second Operation B will be able to start as soon as the most significant result digit is obtained from the previous operation. The delay for this is the preprocessing delay  $\delta$ . So the timing diagram will look similar to this.

Figure 2.3: Timing diagram of online arithmetic

It is easy to see that with online arithmetic, the more operators we have in the compound operator, the more cycles we can save from this digit-serial form of execution.

#### 2.4.2 Online arithmetic applications

Online arithmetic has been implemented for a large number of applications.

Online algorithms for fixed-point division and multiplication were initially proposed in [55], with proof of correctness and expansion to a radix-4 scheme in [56]. The square root operation was implemented in [38]. Floating-point algorithms for addition, subtraction and multiplication, along with the notion of quasi-normalization is presented in works such as [60–62]. Multiplicative normalization of fractions for evaluation of elementary functions was implemented in online form in [20]. An algorithm and VLSI implementation of a radix-2 evaluation of the function Y = AX + B can be found in [58]. Computation of rotation factors for matrix transformations in online form is shown in [14]. Online arithmetic was used in implementing a general hardware oriented algorithm that can be used for a wide application domain, including evaluation of polynomials, certain rational functions and arithmetic expressions, solving linear equation systems, and basic arithmetic operations [13].

Details on established online arithmetic algorithms for basic fundamental operations including addition, multiplication, division and square root can be found in [16]. More complex operations such as the sum of three squares used for vector normalization [25] or primitives used in Fast Fourier Transform and Discrete Cosine Transform operations [33] are also implemented in online arithmetic. The advantages of online arithmetic for high throughput operations has been explored in gene sequence profiling [37], and motion estimation for video encoding standards such as H.26x and MPEG-1, -2 or -4 [53].

# CHAPTER 3

# The Multi-Accelerator architecture

# 3.1 Photon mapping algorithm overview

Before examining the details of the MAPM architecture, we first need a brief understanding of how the photon mapping algorithm works. The discussion in this section is based on implementation details from [41] and the actual implementation code from [49]. The following explains the details of the photon mapping algorithm that is the basis of the MAPM architecture implementation, with some examples where applicable. Note that the algorithm here is for calculating indirect illumination only. Direct illumination is usually calculated separately from indirect illumination and are added together for the final image. As direct illumination does not account for secondary rays, the workload is smaller than indirect illumination by many orders of magnitude, and it will not be considered for acceleration here.

#### 3.1.1 Goal of the algorithm

The end goal of the PM (Photon Mapping) algorithm is to produce a 2D image of the given scene. The image has a preset aspect ratio and resolution, given as the number of pixels on the x and y axis. Each pixel is a square block that displays a single unified color, specified by three floating-point values. Each of these stands for the color intensity of red, green and blue light components, and combined together, determines the single color of each pixel that make up the image. In short, the process of rendering a 3D image using PM is determining the color of each pixel of the image, so that it faithfully represents what the given scene would look like. The color components are calculated in floating-point values, and are converted into the data format that fits the display's color palette data format (usually integers) if necessary.

#### 3.1.2 Input data

For the image, we are given information on the 3D scene, along with light sources and camera information.

- 1. **3D** scene Information of the 3D scene is given as a set of triangles, along with color and texture information of its surface. For flat surfaces with straight edges, it is trivial to divide it up into triangular parts, and curved surfaces or edges are divided up into a sufficiently large number of small triangles, so that they look curved from a distance.

- 2. Light sources Light sources are the origin points of illumination in the scene. Light travels in straight lines from the sources and bounce from the surfaces to project direct and indirect illumination into the scene. Without any illumination, nothing would be visible.

Information on the light sources include the (x, y, z) coordinates of the location, and the intensity of the light's RGB (Red, Green, Blue) components.

3. Camera The camera is the viewpoint into the scene. Basically, objects in front of it will be visible in the image, and objects not in the direction that the camera is facing or obscured by another object will not be shown in the final image. The location of the camera is given in (x, y, z) coordinates, and a direction vector indicates where the camera is pointing.

For the example, the scene used is a variation of the Cornell box, a well known 3D test model that is widely used for various image rendering techniques and first introduced in [19].

Figure 3.1: Cornell box (adapted from [19])

Our example model consists of two cuboid blocks placed inside five outer walls (left, right, ceiling, floor and rear wall). The left wall is colored red, the right wall is colored green, and all other walls of the room and the two blocks are white. The colored walls will create a similarly colored hue on the white walls with proper global illumination.

The scene file cornell-box bj holds information on the x, y, z coordinates of all vertices in the scene, and each triangle is defined by its material and the three indices of the vertices that make up the triangle. This information is parsed and built into a polygon map, which is the KD-tree where all triangle information is stored in order to speed up the ray intersection process.

The camera of our example is located at (278.0, 273.0, -530). This is parallel to the center of the overall bounds on the xy plane, with a negative z coordinate to distance the camera from the objects in the scene. The camera's direction vector is pointing straight in the direction of the scene, parallel to the z axis.

For the sake of our example, a single light source is placed at (1.0, 25.0, 1.0). Seen from the camera point, this is at the corner closer to the camera of the two lower-left ones of the scene. Looking at the image, we can see a circle of intense light on the floor due to it being very close to the light. The light itself is not visible as this image is indirect illumination only.

## 3.1.3 The KD-tree

A KD-tree is a binary space partitioning tree that subdivides a k-dimensional space into irregularly sized regions [9]. In computer graphics, it is used to store and efficiently search for objects inside the 3D space, and is generally considered to be the best data structure for accelerating the tracing of rays [23] (from this point on, we shall assume that all KD-trees are set to a 3D space unless stated otherwise). This is an essential part of the PM algorithm, since the process requires a large number of searches to find query point and photon pairs.

Every node in the KD-tree represents a cuboid region inside the 3D space. Each non-leaf node divides the current cell in two with a splitting hyperplane that is perpendicular to the coordinate axes. The splitting hyperplane can be plotted using one of the following equations: x = a, y = b, or z = c.

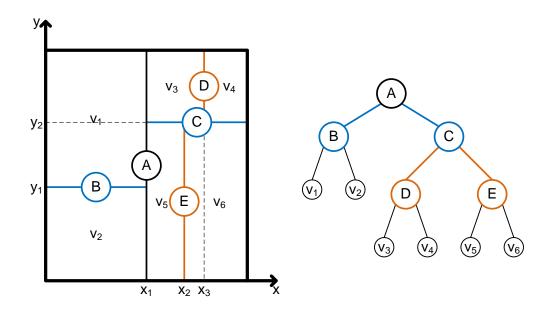

Figure 3.2 shows a simplified example of a KD-tree in 2D space.

Figure 3.2: KD-tree example on a 2-dimensional space

From the 2D example, if we are looking for points that have an x coordinate larger than  $x_1$ , we can easily determine that it will not exist under node B, since all points under B have  $x < x_1$ . As each node has at most 2 children, the average search time is O(log n), with n being the number of total search points in the scene.

## 3.1.4 Building the photon KD-tree

Parsing the scene file The .obj file holding the polygon information is parsed, and all triangle information is loaded into memory. All triangles are sorted and built into the polygon map, which is the KD-tree where all triangle information is stored in order to speed up the ray intersection process. To build the polygon map, a well known heuristic called the surface area heuristic (SAH) [35] is used. At each division of the triangles into children nodes, the SAH selects the division that minimizes the total surface area for the two children. This is based on the idea that the relative probability of

a ray passing through a subspace is linear to its surface area.

Since this is not a part of the PM process that is accelerated in the MAPM, we shall not delve into the details any further here.

2. Photon tracing With the polygon tree finished, rays are recursively traced from the light source into the scene to create photons. In essence, the photons represent a sampling of light at various locations in the scene.

The initial ray starts from the light source into a random direction. If an intersection is found, a photon is created at the intersection point. Related information is stored in an array, which includes the x, y, z coordinates, incoming direction of the light, and RGB intensity values. Once this is done, a reflected bounce ray is created with RGB intensity values adjusted in accordance to the surface material, and the ray intersection process is repeated using the new bounce ray.

This process ends if it reaches a preset hard depth limit. Also, it is beneficial to make use of the Monte Carlo method [12] Russian Roulette, by randomly selecting photons to terminate early after a smaller depth limit. This is due to the photon mapping process inherently being a random sampling problem.

The photon tracing is repeated by creating a new sample ray from the light source, until the number of total photons created reaches a preset number count.

3. Photon KD-tree build Once all photons are found, the photons are sorted by location to form the photon map, which is a KD-tree that holds all the photon information. At each tree node, all contained photons are sorted along the longest axis and divided into two children at the median, with the one photon at the median being saved to the current node. This goes on until a node has only one photon, whereas that node now is a leaf node without any further children. We can see that a photon map containing n photons will result in a balanced and dense binary tree, with n total nodes and  $\lceil log(n) \rceil$  levels.

Below we see a small example of a 7 photon tree build process. The initial bounding box is the bounding box for the whole scene, and it starts at x(0, 555.036), y(0, 548.8), z(0.769442, 559.2).

(a) Node 0 (root node)

Initial photons are:

| slot | x       | y       | z       |

|------|---------|---------|---------|

| 0    | 312.808 | 548.8   | 8.8027  |

| 1    | 264.63  | 428.347 | 559.2   |

| 2    | 0       | 44.8259 | 495.07  |

| 3    | 28.2439 | 0       | 7.08738 |

| 4    | 72.7003 | 548.8   | 191.099 |

| 5    | 0       | 509.39  | 171.588 |

| 6    | 114.27  | 84.3132 | 117.435 |

Length of bounding box axes are x(555.036 - 0 = 555.036), y(548.8 - 0 = 548.8), z(559.2 - 0.769442 = 558.431), and longest is z. Sorting through z gives us:

| slot | x       | y       | z       |

|------|---------|---------|---------|

| 0    | 28.2439 | 0       | 7.08738 |

| 1    | 312.808 | 548.8   | 8.8027  |

| 2    | 114.27  | 84.3132 | 117.435 |

| 3    | 0       | 509.39  | 171.588 |

| 4    | 72.7003 | 548.8   | 191.099 |

| 5    | 0       | 44.8259 | 495.07  |

| 6    | 264.63  | 428.347 | 559.2   |

Median is 171.588 at slot 3 with split axis z, photon at slot 3 is placed at current node 0, left child contains photons at slots 0-2 and right child contains photons at slots 4-6.

(b) Node 1 (left child of node 0)

Initial photons are:

| slot | x       | y       | z       |

|------|---------|---------|---------|

| 0    | 28.2439 | 0       | 7.08738 |

| 1    | 312.808 | 548.8   | 8.8027  |

| 2    | 114.27  | 84.3132 | 117.435 |

Length of bounding box axes are x(555.036 - 0 = 555.036), y(548.8 - 0 = 548.8), z(171.588 - 0.769442 = 170.819), and longest is x. Sorting through x gives us:

i.

| slot | x       | y       | z       |

|------|---------|---------|---------|

| 0    | 28.2439 | 0       | 7.08738 |

| 1    | 114.27  | 84.3132 | 117.435 |

| 2    | 312.808 | 548.8   | 8.8027  |

Median is 114.27 at slot 1 with split axis x, photon at slot 1 is placed at current node 1, left child contains photon at slot 0 and right child contains photon at slot 2.

(c) Node 2 (left child of node 1)

As there is only 1 photon given, node 2 becomes a leaf node that contains the photon at (28.2439, 0, 7.08738).

(d) Node 3 (right child of node 1)

As there is only 1 photon given, node 3 becomes a leaf node that contains the photon at (312.808, 548.8, 8.8027).

(e) Node 4 (right child of node 0)

Initial photons are:

| slot | x       | y       | z       |

|------|---------|---------|---------|

| 0    | 72.7003 | 548.8   | 191.099 |

| 1    | 0       | 44.8259 | 495.07  |

| 2    | 264.63  | 428.347 | 559.2   |

Length of bounding box axes are x(555.036 - 0 = 555.036), y(548.8 - 0 = 548.8), z(559.2 - 171.588 = 387.612), and longest is x. Sorting through x gives us:

| slot | x       | y       | z       |  |

|------|---------|---------|---------|--|

| 0    | 0       | 44.8259 | 495.07  |  |

| 1    | 72.7003 | 548.8   | 191.099 |  |

| 2    | 264.63  | 428.347 | 559.2   |  |

Median is 72.7003 at slot 1 with split axis x, photon at slot 1 is placed at current node 4, left child contains photon at slot 0 and right child contains photon at slot 2.

(f) Node 5 (left child of node 4)

As there is only 1 photon given, node 5 becomes a leaf node that contains the photon at (0, 44.8259, 495.07).

(g) Node 6 (right child of node 4)

As there is only 1 photon given, node 6 becomes a leaf node that contains the photon at (264.63, 428.347, 559.2).

Now all photons are accounted for, and the final tree looks like Table 3.1.

| Index | LC | RC | Photon coordinates       |

|-------|----|----|--------------------------|

| 0     | 1  | 4  | 0,509.39,171.588         |

| 1     | 2  | 3  | 114.27, 84.3132, 117.435 |

| 2     | _  | —  | 28.2439, 0, 7.08738      |

| 3     | _  | _  | 312.808, 548.8, 8.8027   |

| 4     | 5  | 6  | 72.7003, 548.8, 191.099  |

| 5     | _  | _  | 0, 44.8259, 495.07       |

| 6     | _  | _  | 264.63, 428.347, 559.2   |

Table 3.1: Tree contents for the example photon tree

# 3.1.5 Final gathering and query points

1. Tracing primary rays As mentioned in the previous section, we are given the location of the camera and the direction it is pointing at. From this information, we create a plane in front of the camera that is perpendicular to the camera direction vector. A rectangle with the same aspect ratio of the final image is drawn on this plane, which is then divided up into the same number of pixels as the image. This rectangle acts as a virtual frame of the final image, and by calculating the color of each pixel on the image plane, we can determine the color of the pixel on the final image.

To do this, rays that originate from the camera are created. Each ray is directed to pass a single pixel on the rectangular frame. These rays are called primary rays.

Each primary ray is traced into the scene to find an intersection point with the 3D scene. Again, the polygon map is utilized for faster search through the scene. The color of this intersection point then becomes the final color of the image pixel that corresponds to this primary ray. The process of determining this value is final gathering.

2. Final gathering and query points Final gathering starts from the intersection points of primary rays. From each intersection point, a number of sampling rays are shot into the scene in random directions. Intersections with these rays become query points, where we need to find nearby photons in order to calculate the indirect lighting that is sent towards the intersection point of the primary ray, and provides global illumination. In preparation of this search and shade process, the query points are stored in an array.

#### 3.1.6 Tree Search and Shader Operation

With the above processes finished and the photon KD-tree and query point array complete, we are now ready to run tree search and find shader operations. This is the main part of the PM algorithm that is accelerated by the MAPM architecture.

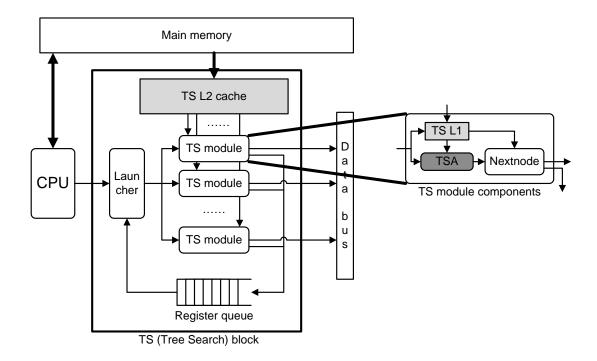

1. Tree search For each query point in the array, we would like to find all photons that are close enough to affect the illumination at the query point. We determine this by checking the distance from the query point to the photon. In relation to the location of the query point, we wish to find all photons that have a distance equal to or smaller than a fixed distance h, which is the radius of the kernel. This is done in an efficient method by starting from the root node of the photon KD-tree and moving down the tree node by node, excluding any branches that contain spaces that are further than h from the query point. Any photons that are found during and at the end the search are paired up with the query point to form shader operations.

Each step through the KD-tree processes a single node. Every node represents a subset of the 3D space containing photons. As we examined in Section 3.1.3, each node divides the space in two via its splitting plane, and

all photons inside the 3D space fall into one of 3 distinct sets, the left child, right child, or on the splitting plane.

At each node, we wish to determine which of the 3 sets hold the photons that we seek for this given query point. With this information, we can determine whether or not we need to search further into the children, or if we need to assign any shader operations from this node. In order to determine this in an efficient manner, we calculate the distance between the query point and the split position of each cell along a single axis, and derive a pair of simple comparisons.

For each query point and photon KD-tree node pair, we work with the following floating-point values:

- p : query point position

- h : radius of the kernel

- s : split position of the KD-tree node

The query point position p is the x, y or z coordinate of the query point. This is selected depending on the orientation of the splitting plane of the current tree node, for instance, if the splitting plane is x = a, p is equal to the x coordinate of the query point.

The radius of the kernel h is a pre-computed value which affects the overall image quality. Discussion on calculation of this value can be found in [47]. In terms of the tree search operation, h is the maximum distance between a photon and a query point for the photon to affect the color at the query point. Any photon that lies outside this distance can be ignored, without any effect on the final image.

And lastly, the split position s is the coordinate of the splitting plane that divides the space of the current node between the two children. For example, if the splitting plane crosses the x axis, its plot equation would be x = s. Put simply, we wish to exclude all photons that lie outside the area marked by the dark rectangle in Figure 3.3. The distance to any photon that lies outside this range will be greater than h and do not need to be considered for a shader operation.

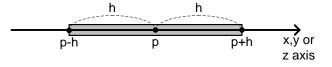

Figure 3.3: Photon search range

With this in mind, there are only 3 possible cases regarding the split position s of the KD-tree node:

Figure 3.4: Scenarios for the split position location

- (a) Case 1 The rectangle lies completely to the right of the split position.We can safely exclude any photons that are in the left child, meaning that we continue searching the right child.

- (b) Case 2 The rectangle lies on both sides of the split position. No photons can be safely excluded, meaning that we continue searching both the left and right child.

(c) Case 3 The rectangle lies completely to the left of the split position. We can safely exclude any photons that are in the right child, meaning that we continue searching the left child.

To determine which one of these cases we have, we evaluate two inequalities, p-h < s and p+h > s. From Figure 3.3, p-h is the left end of the rectangle, and p+h is the right end of the rectangle. From the two values, we can determine which case this search belongs to:

- (a) p h < s is true and p + h > s is false. Which means that the left end of the rectangle is on the left side of s, and the right end of the rectangle is NOT on the right side of s. This indicates that the whole rectangle is on the left side of s, which would be Case 3 of Figure 3.4. We would need to traverse the left child for this case.

- (b) p h < s is false and p + h > s is true. Which means that the left end of the rectangle is NOT on the left side of s, and the right end of the rectangle is on the right side of s. This indicates that the whole rectangle is on the right side of s, which would be Case 1 of Figure 3.4. We would need to traverse the right child for this case.

- (c) p-h < s is true and p+h > s is true. Which means that the left end of the rectangle is on the left side of s, and the right end of the rectangle is on the right side of s. This indicates that the whole rectangle is on both sides of s, which would be Case 2 of Figure 3.4. We would need to traverse both the left and right child for this case.

- (d) p-h < s is false and p+h > s is false. Which means that the left end of the rectangle is NOT on the left side of s, and the right end of the rectangle is NOT on the right side of s. This cannot possibly be true unless h is a negative number, but since h > 0, we will never have this condition.

For reasons that are obvious, we shall call the inequality p - h < s as  $TC_L$ (Traverse Child Left) and the inequality p + h > s as  $TC_R$  (Traverse Child Right).

Some example tree search queries into our minimal photon KD-tree at Table 3.1 is shown below.

- (a) Tree Search with query point at (0, 358.739, 280.736)

- Examining node 0: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis z.

We have p = 280.736, h = 100, s = 171.588, p - h = 180.736, p + h = 380.736.

$TC_L$  = false and  $TC_R$  = true, traverse right child (4) only.

• Examining node 4: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis x.

We have p = 0, h = 100, s = 72.7003, p - h = -100, p + h = 100.  $TC_L$  =true and  $TC_R$  =true, traverse both children (5,6).

Also, create Shader Operation for photon in node 4.

- Examining node 5: leaf, create Shader Operation for photon in node 5.

- Examining node 6: leaf, create Shader Operation for photon in node 6.

- End of query

- (b) Tree Search with query point at (0, 473.547, 255.165)

- Examining node 0: not a leaf, calculate TC<sub>L</sub> and TC<sub>R</sub> using split axis z.

We have p = 255.165, h = 100, s = 171.588, p h = 155.165, p + h = 355.165.

TC<sub>L</sub> =true and TC<sub>R</sub> =true, traverse both children (1,4).

Also, create Shader Operation for photon in node 0.

• Examining node 1: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis x.

We have p = 0, h = 100, s = 114.27, p - h = -100, p + h = 100.  $TC_L$  =true and  $TC_R$  =false, traverse left child (2) only.

• Examining node 4: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis x.

We have p = 0, h = 100, s = 72.7003, p - h = -100, p + h = 100.  $TC_L$  =true and  $TC_R$  =true, traverse both children (5,6). Also, create Shader Operation for photon in node 4.

- Examining node 2: leaf, create Shader Operation for photon in node 2.

- Examining node 5: leaf, create Shader Operation for photon in node 5.

- Examining node 6: leaf, create Shader Operation for photon in node 6.

- End of query

- (c) Tree Search with query point at (213.296, 0, 26.6906)

- Examining node 0: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis z.

We have p = 26.6906, h = 100, s = 171.588, p - h = -73.3094, p + h = 126.691.

$TC_L$  =true and  $TC_R$  =false, traverse left child (1) only.

• Examining node 1: not a leaf, calculate  $TC_L$  and  $TC_R$  using split axis x.

We have p = 213.296, h = 100, s = 114.27, p - h = 113.296, p + h = 313.296.

$TC_L$  =true and  $TC_R$  =true, traverse both children (2,3).

- Examining node 2: leaf, create Shader Operation for photon in node 2.

- Examining node 3: leaf, create Shader Operation for photon in node 3.

- End of query

The pseudo code for Tree Search can be written as shown:

```

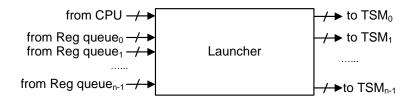

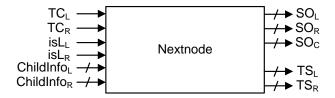

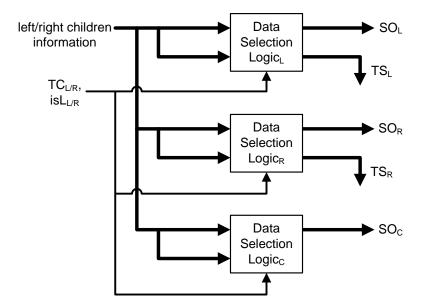

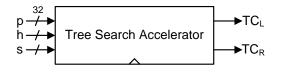

obtain p from query point, s from current node