# **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Scalable Scientific Computation Acceleration Using Hardware-Accelerated Compression

#### **Permalink**

https://escholarship.org/uc/item/2tk163fh

#### **Author**

Sun, Gongjin

### **Publication Date**

2022

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Scalable Scientific Computation Acceleration Using Hardware-Accelerated Compression ${\color{blue} {\rm DISSERTATION}}$

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Gongjin Sun

Dissertation Committee: Professor Sang Woo Jun, Chair Professor Nikil Dutt Professor Elaheh Bozorgzadeh

# **DEDICATION**

To my parents, my sister, my fiancée and those who support and help my pursuing my  ${\rm Ph.D.}$

# TABLE OF CONTENTS

|                        |       | F                                                            | Page |

|------------------------|-------|--------------------------------------------------------------|------|

| $\mathbf{L}\mathbf{I}$ | IST ( | OF FIGURES                                                   | vi   |

| LI                     | IST ( | OF TABLES                                                    | viii |

| $\mathbf{A}$           | CKN   | NOWLEDGMENTS                                                 | ix   |

| <b>1</b> 7             | ITA   |                                                              | xi   |

| ν.                     | IIA   |                                                              | ΛI   |

| $\mathbf{A}$           | BST   | RACT OF THE DISSERTATION                                     | xiii |

| 1                      | Intr  | roduction                                                    | 1    |

|                        | 1.1   | Case Study: Lossy Floating-Point Compression                 | 4    |

|                        |       | 1.1.1 Optimizing ZFP For Hardware Implementation             | 5    |

|                        | 1.2   | Grid-Based Scientific Computing with Compression             | 7    |

|                        | 1.3   | Case Study: Integer Stream Compression                       | 9    |

|                        | 1.4   | Dissertation Contributions and Organization                  | 11   |

| 2                      | ZFI   | P-V: Hardware-Optimized Lossy Floating Point Compression     | 13   |

|                        | 2.1   | Introduction to Compression                                  | 13   |

|                        |       | 2.1.1 Lossless Compression and Lossy Compression             | 14   |

|                        |       | 2.1.2 Floating Point Compression                             | 15   |

|                        |       | 2.1.3 Why Accelerate Floating-Point Compression Algorithms?  | 16   |

|                        |       | 2.1.4 Straightforward Hardware Implementation is not Enough! | 17   |

|                        | 2.2   | ZFP Compression Algorithm                                    | 17   |

|                        |       | 2.2.1 Fixed-Point Conversion                                 | 18   |

|                        |       | 2.2.2 Block Transform                                        | 19   |

|                        |       | 2.2.3 Sequency Ordering                                      | 19   |

|                        |       | 2.2.4 Embedded Coding                                        | 19   |

|                        |       | 2.2.5 Inefficiency of Group Testing For Hardware             | 21   |

|                        | 2.3   | ZFP-V Design and Implementation                              | 22   |

|                        |       | 2.3.1 Fixed-Length Header-Based Encoding                     | 23   |

|                        |       | 2.3.2 Variable Length Header (VLH) for ZFP-V2                | 25   |

|                        |       | 2.3.3 2-Layer Header for ZFP-V2                              | 26   |

|                        |       | 2.3.4 Coarse-Grained VLH for ZFP-V1                          | 27   |

|                        |       | 2.3.5 Bitstream Structure                                    | 29   |

|   |      | 2.3.6 Independent Aligned Chunks                             | 30        |

|---|------|--------------------------------------------------------------|-----------|

|   | 2.4  | ZFP-V Accelerator Architecture                               | 30        |

|   |      | 2.4.1 ZFP-V1 Decompression Accelerator                       | 31        |

|   |      | 2.4.2 ZFP-V1 Compression Accelerator                         | 32        |

|   |      |                                                              | 32        |

|   |      |                                                              | 33        |

|   | 2.5  |                                                              | 34        |

|   |      |                                                              | 34        |

|   |      |                                                              | 35        |

|   |      |                                                              | 37        |

|   | 2.6  | v v                                                          | 37        |

|   |      |                                                              | 38        |

|   |      |                                                              | 43        |

|   |      | 1                                                            | $45^{-3}$ |

|   |      | 1                                                            | 47        |

|   | 2.7  |                                                              | 17<br>17  |

|   | 2.,  | Summary                                                      |           |

| 3 | Bur  | rstZ+: Scientific Computing Acceleration with ZFP-V          | 19        |

|   | 3.1  | Introduction                                                 | 49        |

|   |      | 3.1.1 The BurstZ+ Platform                                   | 50        |

|   |      | 3.1.2 Applications: Stencil Computation on a Structured Grid | 51        |

|   |      | 3.1.3 Prototype Implementation and Evaluation                | 53        |

|   | 3.2  | Background and Related Work                                  | 55        |

|   |      | 3.2.1 Stencil Computing and its Acceleration                 | 55        |

|   |      |                                                              | 59        |

|   | 3.3  | Performance Analysis of Stencil Acceleration                 | 31        |

|   | 3.4  | BurstZ+ Architecture                                         | 33        |

|   |      |                                                              | 34        |

|   |      |                                                              | 35        |

|   |      | 3.4.3 Implementation Details                                 | 70        |

|   | 3.5  | Performance Evaluation                                       | 72        |

|   |      |                                                              | 73        |

|   |      |                                                              | 73        |

|   |      | 3.5.3 End-to-End Application Performance                     | 75        |

|   |      | 3.5.4 Scalability Analysis                                   | 31        |

|   | 3.6  | Summary                                                      | 32        |

|   |      | ·                                                            |           |

| 4 | Zip] | v i                                                          | 34        |

|   | 4.1  |                                                              | 34        |

|   | 4.2  | 8                                                            | 39        |

|   |      | v                                                            | 39        |

|   |      | 1 0                                                          | 90        |

|   |      |                                                              | 91        |

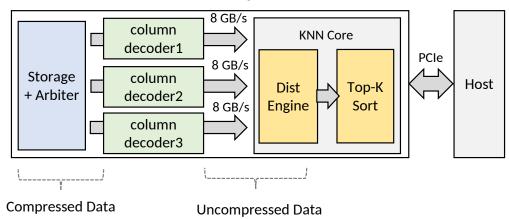

|   | 4.3  | ZipNN Accelerator Architecture                               | 91        |

|   |      | 4.3.1 Column Decoder Architecture                            | 92        |

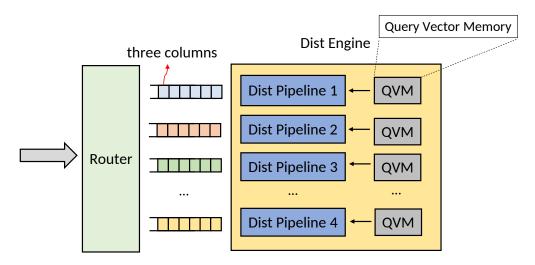

|        | 4.3.2   | K-NN Accelerator Architecture                      | . 93  |

|--------|---------|----------------------------------------------------|-------|

| 4.4    | Hardy   | vare-Efficient Integer Stream Compression          | 96    |

|        | 4.4.1   | Choice of Compression Algorithms                   | . 96  |

|        | 4.4.2   | Optimizing Heterogeneous Decoders to Data Patterns | . 97  |

|        | 4.4.3   | Limitations of a Hardware Group Varint Decoder     | . 99  |

|        | 4.4.4   | Pipelined Group Varint                             | . 99  |

|        | 4.4.5   | Fully Pipelining Hardware Group Varint             | 101   |

| 4.5    | Perfor  | mance Evaluation                                   | 102   |

|        | 4.5.1   | Implementation Details                             | 102   |

|        | 4.5.2   | Benchmark And Configuration Details                | 103   |

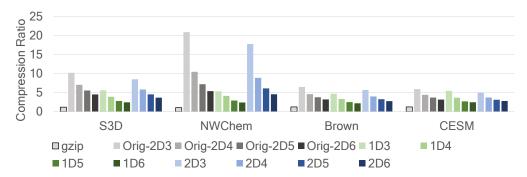

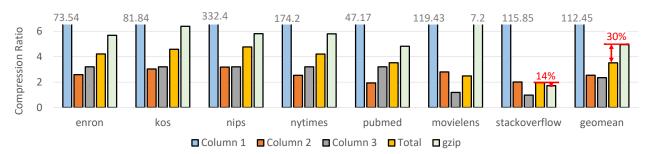

|        | 4.5.3   | Compression Effectiveness                          | 104   |

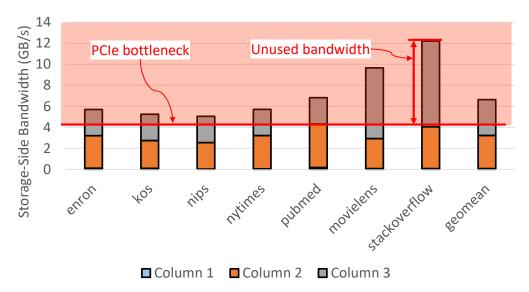

|        | 4.5.4   | K-NN Accelerator Performance                       | 106   |

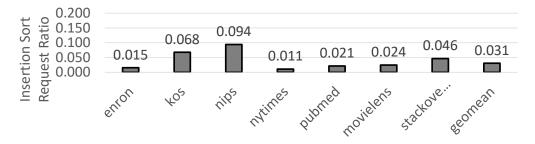

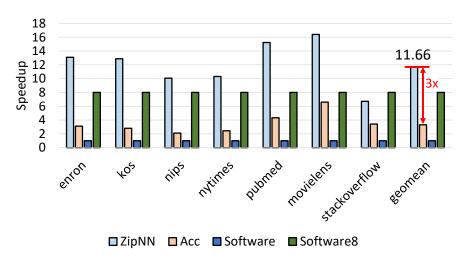

|        | 4.5.5   | End-To-End Application Performance                 | 106   |

| 4.6    | Summ    | nary                                               | 109   |

| 5 Co   | nclusio | n and Future Work                                  | 110   |

| 5.1    | Concl   | usion                                              | 110   |

| 5.2    | Futur   | e Work                                             | . 111 |

| D:bl:a | graphy  |                                                    | 113   |

# LIST OF FIGURES

|                    | I                                                                                                                                                                                          | Page             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.1<br>1.2<br>1.3  | PCIe bandwidth becomes the bottleneck between Host and Accelerator One example of Group Testing Encoding                                                                                   | 2<br>6<br>10     |

| 2.1<br>2.2<br>2.3  | The bits distribution of a 2D block with double type The MSB distribution of the binary string in a bit plane Three different encoding schemes are used for three different regions (Blue, | 21<br>26         |

| 2.4<br>2.5         | green, red)                                                                                                                                                                                | 28<br>30<br>31   |

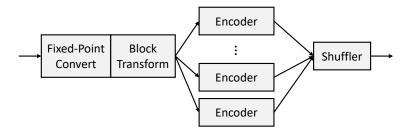

| 2.6<br>2.7         | A multi-pipeline ZFP-V compressor accelerator                                                                                                                                              | 32               |

| 2.8<br>2.9<br>2.10 | wire-speed output                                                                                                                                                                          | 33<br>35<br>s 36 |

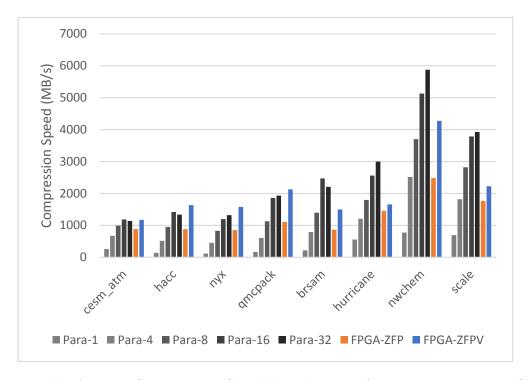

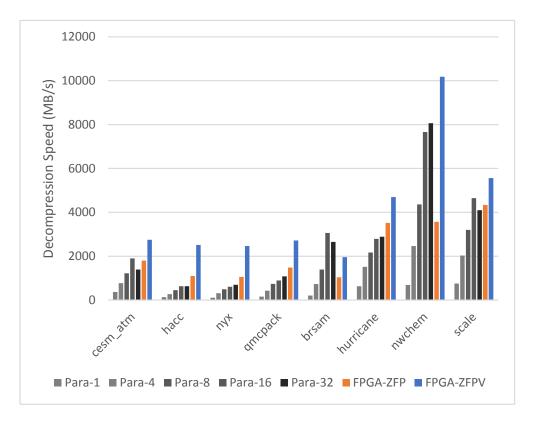

| 2.11               | ZFPV                                                                                                                                                                                       | 40               |

| 9 19               | ZFPV                                                                                                                                                                                       | 41<br>42         |

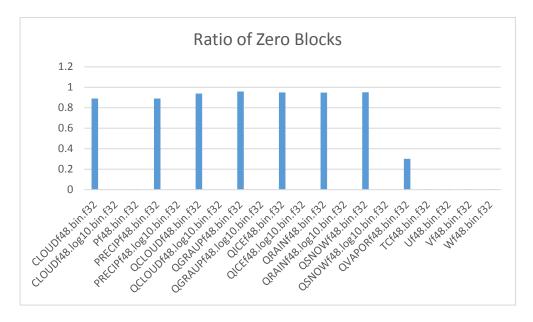

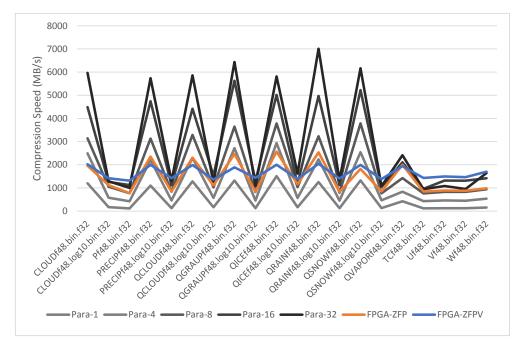

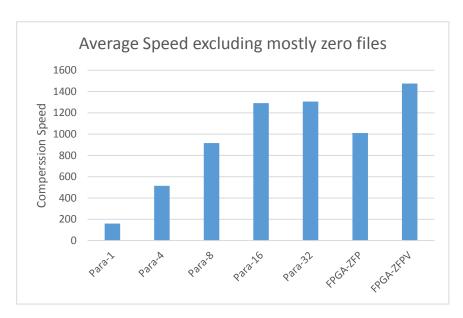

| 2.13               | The Compression Speed of all data files in the benchmark Hurricane                                                                                                                         | 43               |

|                    | Hurricane                                                                                                                                                                                  | 44               |

|                    | bounds                                                                                                                                                                                     | 45               |

|                    | bounds                                                                                                                                                                                     | 47               |

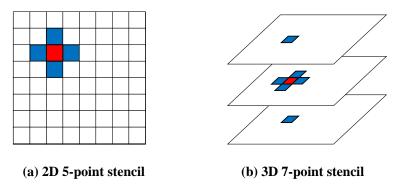

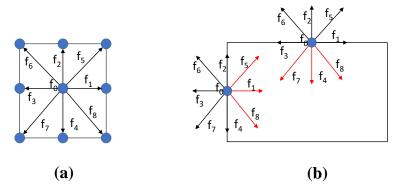

| 3.1 3.2            | Example 2D and 3D stencils                                                                                                                                                                 | 55<br>57         |

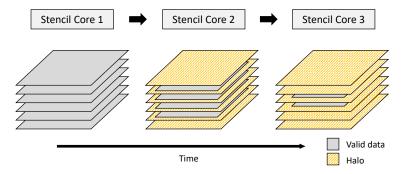

| 3.3                | Deep temporal blocking increases the size of the <i>Halo</i> , reducing the amount of valid data                                                                                           | 58               |

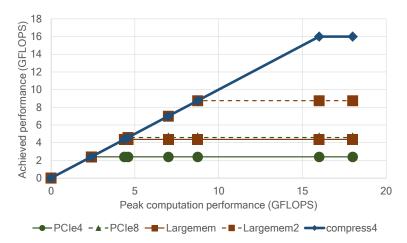

| 0.4                | bandwidth                                                                                                                                                                                  | 62               |

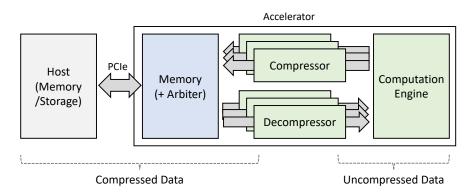

| 3.5  | The overall architecture of BurstZ+. Data is stored compressed until it is used by the computation engine                               | 63  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

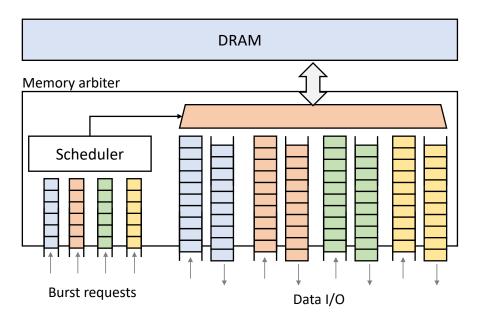

| 3.6  | The memory arbiter provides high-performance multiplexing to multiple end-                                                              | 00  |

| 0.0  | points                                                                                                                                  | 66  |

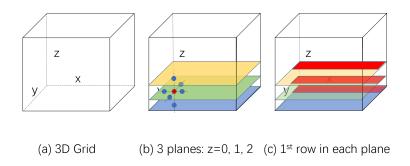

| 3.7  | The basic principle of 3D stencil computation                                                                                           | 68  |

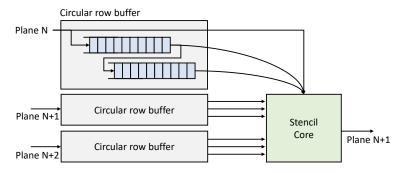

| 3.8  | Three sets of two on-chip BRAM row buffers are used by the stencil core                                                                 | 69  |

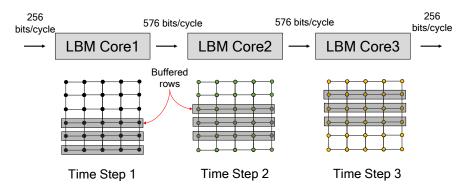

| 3.9  | The Architecture of a 3-stage LBM pipeline                                                                                              | 70  |

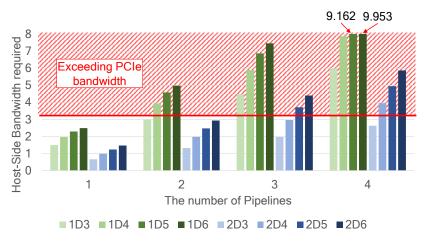

| 3.10 | The communication bandwidth required for the full performance operation of                                                              | 70  |

| 5.10 | multiple decompressor pipelines, for various fault tolerance settings of ZFP-V1                                                         |     |

|      | and ZFP-V2                                                                                                                              | 74  |

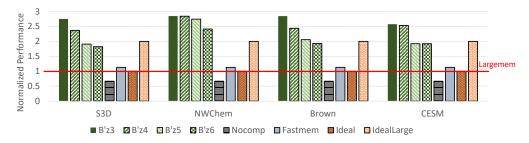

| 3 11 | 3D stencil evaluation: BurstZ+ outperforms even in-memory systems with                                                                  | 14  |

| 0.11 | ideal caching                                                                                                                           | 77  |

| 3.12 | LBM evaluation: BurstZ+ outperforms an accelerator with no compression                                                                  | ' ' |

| J.12 | by over $2\times$ , and often outperforms even in-memory accelerators                                                                   | 79  |

| 3.13 | SRAD evaluation: BurstZ+ outperforms an accelerator with no compression                                                                 |     |

| 0.10 | by over $2\times$ , and often outperforms even in-memory accelerators                                                                   | 80  |

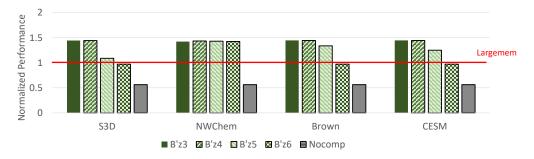

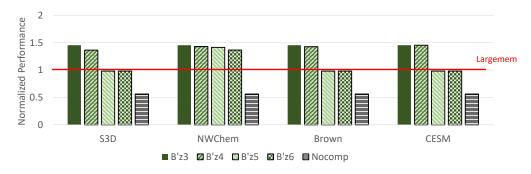

| 3.14 | The performance of the computing engine when the original ZFP is used in                                                                |     |

|      | BurstZ+                                                                                                                                 | 81  |

| 3.15 | More efficient compression using ZFP-V2 allows good performance scaling                                                                 |     |

|      | within a strict bandwidth budget                                                                                                        | 82  |

|      |                                                                                                                                         | 0.0 |

| 4.1  | The Overall Architecture of ZipNN                                                                                                       | 92  |

| 4.2  | The architecture of cosine similarity calculation engine                                                                                | 94  |

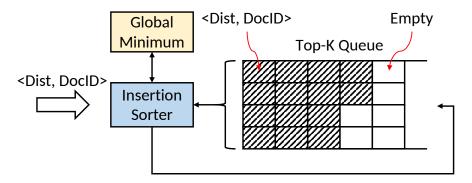

| 4.3  | Internal architecture of the top-k sorting engine                                                                                       | 95  |

| 4.4  | FIFO walking to insert a new data element into the top-k buffer                                                                         | 96  |

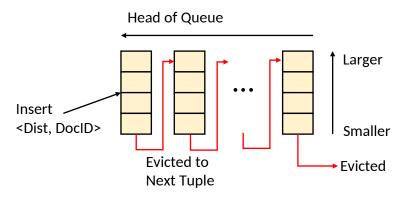

| 4.5  | Pipelined Group Varint decoding across sections                                                                                         | 100 |

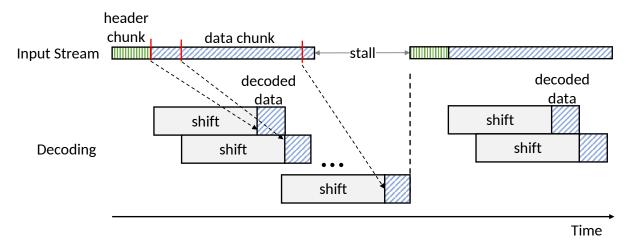

| 4.6  | Optimally pipelined Group Varint using a lookahead buffer                                                                               | 101 |

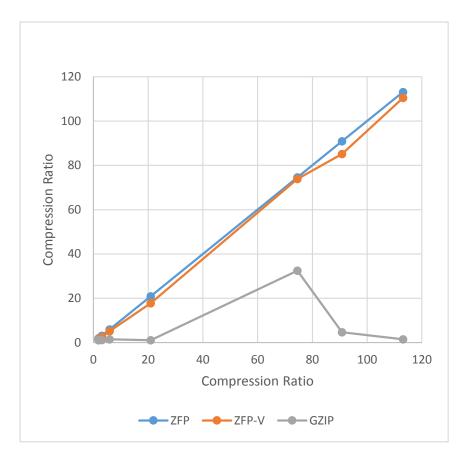

| 4.7  | Per-column and total compression ratios                                                                                                 | 104 |

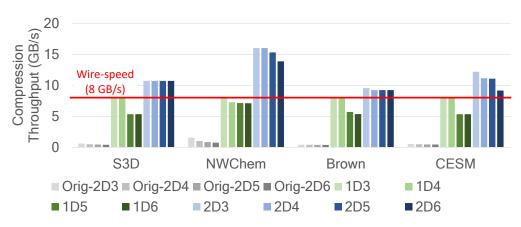

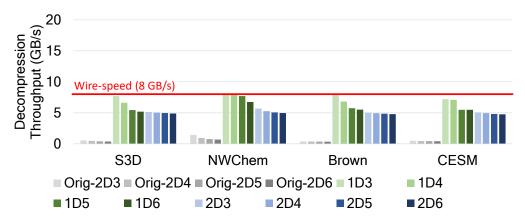

| 4.8  | Storage bandwidth required to support wire-speed decompression exceeds the PCIe bandwidth                                               | 105 |

| 4.0  |                                                                                                                                         | 105 |

| 4.9  | Ratio of data elements requiring insertion sort. Note the range of Y is 0 to 0.2 Normalized performance of ZipNN, using BlueDBM storage | 100 |

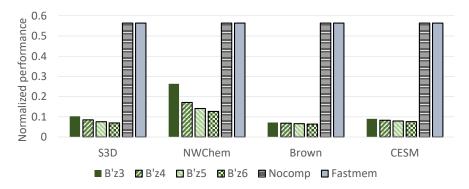

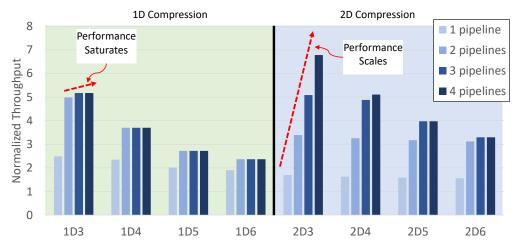

|      | 1 , , , ,                                                                                                                               | 101 |

| 4.11 |                                                                                                                                         | 107 |

|      | ideany scaled software performance is also minued by PCIe                                                                               | TOI |

# LIST OF TABLES

|     |                                                                           | Page |

|-----|---------------------------------------------------------------------------|------|

| 2.1 | Header Coding of the bit plane                                            | 26   |

| 2.2 | Number of bit planes encoded on average                                   | 37   |

| 2.3 | FPGA Resource Utilization of ZFP and ZFP-V                                | 39   |

| 3.1 | Different configurations for roofline analysis                            | 62   |

|     | Various characteristics of the benchmark stencils                         |      |

| 3.3 | FPGA LUTs usage breakdown of the BurstZ+ platform for stencil computation | n 72 |

| 3.4 | Evaluated accelerator configurations                                      | 76   |

| 4.1 | Datasets used to evaluate ZipNN                                           | 103  |

| 4.2 | System configurations evaluated                                           | 108  |

### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Sang-Woo Jun. You give me a chance to explore the world of FPGA with a totally new and amazing experience. Your brilliant insights, extreme patient guidance, and rich experience and strong expertise make me grow quickly in this area. I feel so honored to become your first student in your professor career and am so grateful to you for all that you have done including writing and polishing code, papers, presentations, a lot of research suggestions, job hunting, and many more.

I also would like to thank Professor Alex Veidenbaum. Your advising makes me get deep understanding in the area of processor microarchitecture, especially in hardware prefetcher. I appreciate so many talks with you and a lot of useful research advice you gave me.

Next, I would like to thank Professor Anton Burtsev for discussing OS knowledge with me, and, thank Professor Alex Nicolau, Professor Nikil Dutt, Professor Elaheh Bozorgzadeh, Professor Ahmed Eltawil for your service, your valuable comments and suggestions in my advancement, defense and dissertation.

I also would like to thank many staff in Computer Science department, Donald Bren School of Information and Computer Sciences, Center for Embedded Cyber-Physical Systems (CECS), International Center, UCI housing office, Verano Place housing office, and other UCI departments. Thank you so much for your assistance during my PhD program.

Then, I thank Jinpyo Kim for your mentoring in my internship in the vmware and your help in my job hunting.

I also thank my friends and colleagues during my PhD life: Zhi Chen, thank you for giving me many useful suggestions in my first few PhD years; Junjie Shen, we've been labmate for a long time and it is so nice to work and discuss with you, and you give me so much help, so many useful suggestions, thank you!; Wentao Zhu, you always give me support, help and encouragement, especially when I was depressed. I value a lot of talk between us. Sajjad Taheri, Aniket Shivam, Biswadip Maity, Tongsheng Geng and others. Thank you all for your friendship, support, suggestions and collaboration!

I thank YoungBong Kim. As a visiting member in our ARDA group, you taught us a lot of useful storage knowledge.

I would like to thank the ARDA group members: Jeffrey Chen, I miss the time we went to the scary farm for fun at Halloween, went to the comic book store and hung out on the streets in San Diego; Seongyoung Kang, I value and miss the time you, me and Sang-Woo work together to complete a lot of meaningful research work! Se-Min Lim, JiyoungAn, Esmerald Aliaj. I'm very impressed by your work and your progress. I believe all of you will make our group better and better in the future!

I sincerely thank the support from Intel's Academic Compute Environment for the HLS part of our ZFP-V work; BurstZ+ was partially funded by NSF (CNS-1908507), as well as with

generous donations from VMware Research. Thank NSF and VMware Research!

My PhD program is financially supported by Computer Science department, Professor Alex Veidenbaum, and Professor Sang-Woo Jun. I really appreciate your support!

Last but not least, I appreciate a lot the support from my parents, my sister, my fiancée and friends during my PhD career.

Thank you to everyone who have helped me during my PhD career!

# VITA

# Gongjin Sun

### **EDUCATION**

| Doctor of Philosophy in Computer Science                                               | 2022                        |

|----------------------------------------------------------------------------------------|-----------------------------|

| University of California, Irvine                                                       | Irvine, CA                  |

| Master of Science in Computer Science<br>University of Science and Technology of China | <b>2013</b><br>Hefei, China |

| Bachelor of Science in Computer Sciences Northwestern Polytechnical University         | <b>2006</b><br>Xi'an, China |

#### RESEARCH EXPERIENCE

| Graduate Research Assistant      | 2015 – 2022        |

|----------------------------------|--------------------|

| University of California, Irvine | Irvine, California |

# Visiting Research Assistant State Key Laboratory of Computer System and Architecture, ICT, CAS Beijing, China

#### TEACHING EXPERIENCE

| Reader                           | 2015 – 2018 |

|----------------------------------|-------------|

| University of California, Irvine | Irvine, CA  |

#### REFEREED JOURNAL PUBLICATIONS

### BurstZ+: Eliminating The Communication Bottleneck 2022 of Scientific Computing Accelerators via Accelerated Compression ACM Transactions on Reconfigurable Technology and Systems (TRETS) REFEREED CONFERENCE PUBLICATIONS Bandwidth Efficient Near-Storage Accelerator for High-Dec 2020 **Dimensional Similarity Search** International Conference on Field-Programmable Technology (FPT) August 2020 ColumnBurst: a near-storage accelerator for memoryefficient database join queries ACM SIGOPS Asia-Pacific Workshop on Systems (APSys) BurstZ: A Bandwidth-Efficient Scientific Computing June 2020 Accelerator Platform for Large-Scale Data ACM International Conference on Supercomputing (ICS) ZFP-V: Hardware-Optimized Lossy Floating Point Dec 2019 Compression International Conference on Field-Programmable Technology (FPT)

May 2019

Combining Prefetch Control and Cache Partitioning to

International Parallel and Distributed Processing Symposium (IPDPS)

Improve Multicore Performance

### ABSTRACT OF THE DISSERTATION

Scalable Scientific Computation Acceleration Using Hardware-Accelerated Compression

By

Gongjin Sun

Doctor of Philosophy in Computer Science

University of California, Irvine, 2022

Professor Sang Woo Jun, Chair

Hardware accelerators such as GPUs and FPGAs can often provide enormous computing capabilities and power efficiency, as long as the working set fits in the on-board memory capacity of the accelerator. But if the working set does not fit, data must be streamed from the larger host memory or storage, causing performance to be limited by the slow communication bandwidth between the accelerator and the host. While compression is an effective method to reduce data storage and movement overhead, it has not been very useful in solving this issue due to efficiency and performance limitations. This is especially true for scientific computing accelerators with heavy floating-point arithmetic, because efficiently compressing floating-point numbers requires complex, floating-point specific algorithms.

This dissertation addresses the host-side bandwidth issue of accelerators, specifically FPGA accelerators, using a series of hardware-optimized compression algorithms. Since typical compression algorithms are not designed with efficient hardware implementation in mind, we explore and implement variants of existing algorithms for high performance and efficiency. We demonstrate the impact of our ideas using two classes of applications: Grid-based scientific computing, and high-dimensional nearest neighbor search. We have implemented a scientific computing accelerator platform (BurstZ+), which uses a class of novel error-controlled lossy floating-point compression algorithms (ZFP-V Series). We demonstrate that BurstZ+ can

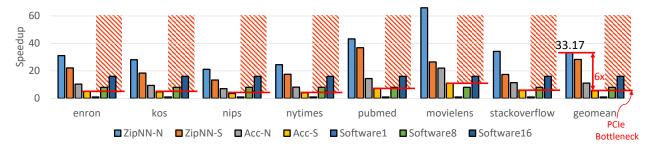

completely remove the host-accelerator communication bottleneck for accelerators. Evaluated against hand-optimized kernel accelerator implementations without compression, our single-pipeline BurstZ+ prototype outperforms an accelerator without compression by almost  $4\times$ , and even an accelerator with enough memory for the entire dataset by over  $2\times$ . We have also developed a near-storage high-dimensional nearest neighbor search accelerator (ZipNN) which uses a hardware-optimized Group Varint compression algorithm to remove the host-side communication bottleneck. Our ZipNN prototype outperforms an accelerator without compression by  $6\times$ , and even much costlier in-memory multithreaded software implementations by over  $2\times$ .

# Chapter 1

# Introduction

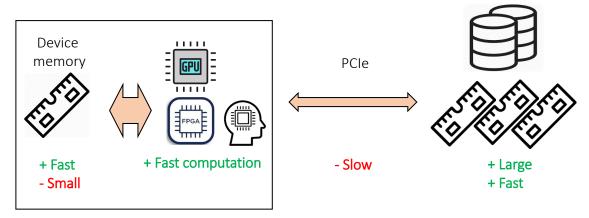

While heterogeneous computing systems equipped with application-specific hardware accelerators are becoming staples in datacenters due to their high performance and power efficiency, their performance is often limited not by computation capacity, but by host-side communication bandwidth. For ease of deployment, accelerators such as General-Purpose Graphics Processing Units (GPGPU), Field-Programmable Gate Arrays (FPGA), Tensor Processing Units (TPU), and others, are often packaged as a PCIe-attached expansion card, equipped with fast on-board memory. Such accelerators deliver extremely high performance if the working set fits on their on-board memory resources, but once the working set exceeds their memory resources so that data needs to be dynamically transferred over PCIe, the limited bandwidth of the PCIe link often becomes the critical performance bottleneck [118, 27, 19, 5, 41, 117]. Due to this reason, many existing research on scientific computing accelerators have focused on problem sizes which can fit on the on-board memory resources [39, 129, 23, 26, 143, 111].

Figure 1.1 shows this issue. On the host side, we have large volume and fast memory devices. On the device side, the computation engine can work very fast and the engine may be equipped with fast memory device as well. However, PCIe communication bandwidth

becomes the performance bottleneck between them due to its low bandwidth.

Figure 1.1: PCIe bandwidth becomes the bottleneck between Host and Accelerator

Data Compression is a commonly used technique that can effectively save storage space and the overhead of data movement. If the data movement over the communication channel can be in compressed form, and if the compression and decompression can be done fast enough to keep up with the computation and memory performances, the accelerator can enjoy a sufficiently high effective bandwidth over the communication channel. This brings us to an important challenge regarding compression design and implementation: How can we achieve high enough performance to remove the communication bottleneck, while maintaining efficient compression, and also while minimizing accelerator resources utilization? During the exploration, we face several key questions:

- Which algorithm can achieve the necessary compression efficiency?

- Can this algorithm achieve high performance on the accelerator?

- Can this algorithm be implemented efficiently on the accelerator, leaving enough resources for the actual computation?

- If the algorithm cannot achieve high performance with low resources in its original form, how can it be modified for better performance and resource utilization?

In this dissertation, we explore the use of high-efficiency compression schemes to solve the above-mentioned issue by integrating one or multiple compression components into the accelerator platform. We focus mainly on FPGAs as the target accelerator due to their extremely high power efficiency and performance [104, 51], which not only makes them popular as stand-alone accelerators, but also opens up many new venues for systems architectural exploration, such as near-storage [67, 38, 68] and near-network [45, 137] accelerators. As a result, our compression algorithm explorations also focus on efficient implementation as application-specific hardware accelerators.

We demonstrate our approach using two important application case studies: Grid-based scientific computing, and high-dimensional nearest-neighbor search. The grid-based scientific computing application predominantly involves floating point data and operations, and we explore the use of highly efficient, error-controlled lossy compression algorithms for faster data movement of intermediate state. Algorithmic exploration was especially important for this application as general-purpose dictionary-based copression algorithms such as the LZ series of algorithms are notoriously ineffective at compression floating point data [82]. The nearest neighbor search application involves quickly scanning a database of sparsely encoded data elements, and we explore the use of column-wise Varint compression for faster access into the database.

For both approaches, we notice that the original compression algorithms are designed for efficient software implementation, and are not well-suited for effective hardware accelerator implementation. We noticed that in many cases, only a minimal amount of changes to the algorithm are necessary for more efficient hardware implementation. This dissertation presents the approaches we took to improve the hardware implementation efficiency of these algorithms, and demonstrate the benefits they have on the end-to-end application performance.

Given the same resources, the introduction of efficient compression results in impressive

performance improvement which goes beyond merely removing the communication bandwidth limitations. Not only does our compression-enabled accelerators vastly outperform accelerators that suffer from communication bandwidth limitations, they often significantly outperform even much costlier systems configurations with sufficient memory capacity for the entire working set of the application.

# 1.1 Case Study: Lossy Floating-Point Compression

The use of compression for scientific computing acceleration has traditionally been limited because of the high performance overhead of floating-point compression algorithms. General-purpose lossless compression schemes such as DEFLATE [33] and LZW [133] are typically not very efficient with floating point data, which often make up a large part of scientific datasets [82, 34]. On the other hand, floating-point specific lossy compression algorithms such as ZFP [82, 36] and SZ [34] are widely used to compress scientific data, due to their very efficient compression as well as their capability to limit the error bound of each data element.

Previous research have shown that use of these error-bound lossy compression schemes do not cause meaningful quality degradation of computation [10, 65], even for iterative algorithms compressing intermediate data [46]. However, these complex algorithms also have high performance overhead compared to lightweight data-oblivious compression algorithms like LZ4 or LZO, making their demonstrated performance insufficient to keep up with the internal computation capabilities of scientific computing accelerators.

One natural solution to this problem is to re-implement them on hardware. We choose ZFP as our target algorithm because most of the algorithm is easily parallelizable. This is in contrast to SZ [34], the other prominent lossy floating point compression algorithm, which

is organized around individual data prediction.

However, our evaluation on FPGA implementations of ZFP showed that a straightforward FPGA implementation of ZFP cannot bring significant compression/decompression throughput improvement over its software version due to the inherently serial characteristic of a single stage ("embedded coding") in the algorithm. To address this problem, we made minor, hardware-aware changes to the algorithm for easier parallelization, resulting in higher-efficiency hardware implementations. We have created a family of hardware-optimized ZFP variant, which we call the ZFP-V family, and it includes ZFP-V1 (1D) and ZFP-V2 (2D) targeting 1D ZFP and 2D ZFP, respectively. The two designs solve the serial aspect of the original algorithm in different ways.

As a result, both ZFP-V implementations are capable of providing wire-speed compression and decompression of floating point data while using only a small fraction of on-chip resources. The new coding schemes do trade a small amount of compression while obtaining an order of magnitude performance improvement. However, this proved not to be an issue for us, as the goal of our hardware compressors is removing the host-accelerator communication bottleneck, which the compression efficiency of both ZFP-V designs more than achieve.

A high-level overview of the algorithmic modifications are provided below, and more details about the ZFP-V algorithm design, as well as the accelerator implementation and performance evaluations are given in Chapter 2.

## 1.1.1 Optimizing ZFP For Hardware Implementation

ZFP is a block-based algorithm, which processes input in d-dimensional (d = 1/2/3) blocks of size  $4^d$ . During compression, the input floating-point data go through multiple stages of preprocessing and transformation and are turned into a list of decorrelated fixed-point numbers

where earlier values in the list have statistically larger values. This list is compactly encoded taking advantage of the statistically large number of zero bits near the most significant bits. The algorithm also takes advantage of the relaxed, *lossy*, compression requirement, only encoding a subset of the upper bits of the data until the required error control is satisfied.

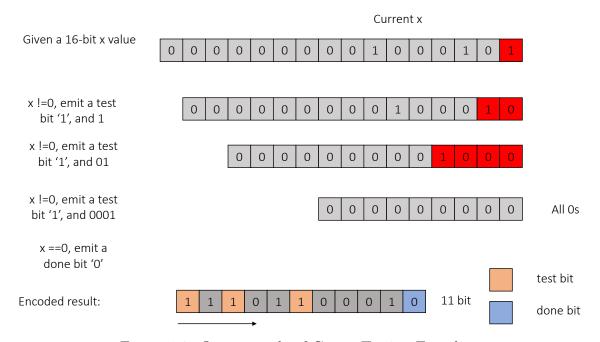

During data encoding, the original ZFP algorithm adopts a technique called "group testing" to encode the transformed block, and this is the stage which is the most difficult to parallelize as-is. This approach repeats a simple process of emitting individual nonzero bits and then checking if the remainder of the value being encoded is now zero. Figure 1.2 uses a simple example to show how group testing is used to compress a bit plane that has 16 bits. For a given n-bit bit plane value, the algorithm scans bits one by one from the LSB (least significant bit) position until the remaining bits become all zeros. If the remaining bits are not all zero, a test bit "1" is emitted, then the LSB bits until a nonzero bit are emitted. This process is repeated until all remaining bits are emitted, after which the done bit "0" is emitted.

Figure 1.2: One example of Group Testing Encoding

Since the algorithm cannot know the remaining bits before the current sequence of nonzero bits are emitted, this portion of the algorithm is inherently sequential. As a result, in the

worst case only 1 bit can be processed per cycle when it is implemented on hardware, which gives a 31.25 MB/s speed based on a 250 MHz FPGA design. On the other hand, our scientific computing engine (e.g., stencil computing engine) can handle data ingestion at wire-speed, which is 8 GB/s on a 256-bit datapath clocked at 250 MHz. As a result, a single pipeline of the unmodified ZFP algorithm is insufficient to match the data ingestion speed of the computing engine.

We modify the embedded coding stage to use a header to specify the position of the most significant nonzero bit, instead of a sequence of test bits interleaved with data. This way, there is no internal dependency when processing a single data element, and a single data element can be either encoded or decoded within a single clock cycle. By doing so, we can achieve a processing speed of 16 bits/cycle (500 MB/s) on a 250 MHz design, which is a significant improvement over the original approach.

However, allocating a fixed-size header for each data element results in a significant degradation of compression efficiency. We address this problem using a variable-length header scheme, which is described in more detail in Chapter 2.

This design not only improves the performance of a single pipeline implementation, but also drastically reduces the chip resource utilization per unit bandwidth. As a result, we can afford to implement a multi-pipeline design to eventually achieve wire-speed processing, matching the data ingestion and emission bandwidth requirements of the computation engine.

# 1.2 Grid-Based Scientific Computing with Compression

With these high-efficiency hardware compressors, we are able to design and implement BurstZ+, a scientific computing accelerator platform that integrates one or multiple hardware compressors/decompressors and a high-speed scientific computation engine. It ad-

dresses the communication bandwidth issue of scientific computing accelerators by providing the computation engine with highly efficient compression engines.

BurstZ+ is able to sustain high performance regardless of the size of the working set relative to the on-board fast random access memory. If the intermediate data size exceeds the memory capacity, the overflow data is exported to either the memory or storage of the host server, in a compressed and randomly accessible format. The compressed data is fetched and decompressed piecemeal at the accelerator side only when required.

We evaluate the performance of BurstZ+ using three realistic grid-based scientific computing applications with widely differing characteristics. Grid-based scientific computing applications process data organized into a grid of cells, where the data type of each cell may be widely different for each application. A kernel or stencil is run on each cell, where the kernel can read values of neighboring cells within a fixed distance. Many important and difficult non-linear systems can be decomposed into kernels and stencils, which supports effective parallelization. Each kernel can have high or low operational intensity based on the amount of computation required by the algorithm per every byte of data I/O. We use the three following applications for evaluation:

- 3D Heat Dissipation: 3D stencil kernel with high memory bandwidth requirements but relatively low operational intensity.

- 2D Speckle Reducing Anisotropic Diffusion (SRAD): 2D stencil kernel with high operational intensity.

- 2D Fluid Dynamics via Lattice Boltzmann Method (LBM): 2D stencil kernel with high operational intensity, and also large cell sizes in bytes.

Using these applications, we demonstrate that the ZFP-V accelerators have both high performance enough to supply the accelerator cores with enough bandwidth, as well as achieves high enough compression efficiency to close the bandwidth gap between the PCIe and on-board DRAM bandwidth. As a result, our compressor is efficient enough to remove not only the PCIe performance bottleneck, but also improve the effective performance of the on-board DRAM by storing compressed data even on the fast on-board DRAM, and decompressing on the fly. Evaluated against hand-optimized implementations of kernel accelerators without compression, our single-pipeline BurstZ+ prototype outperforms an accelerator without compression by almost  $4\times$ , and even an accelerator with enough memory for the entire dataset by over  $2\times$ .

# 1.3 Case Study: Integer Stream Compression

We also explore the difficult problem of high-dimensional nearest-neighbor search, and apply the approach of hardware-optimized compression algorithms to the application. High-dimensional nearest neighbor search suffers from the so-called *curse of dimensionality*, where the effectiveness of indexing algorithms quickly degrades for data types with high dimensions. As a result, search into such datasets cannot take advantage of efficient indexing, devolving into linear search. In such a situation, the performance of the search system depends on how fast the database to search can be streamed from storage to the processing engine.

For this application, we encode the high-dimensional data using typical sparse multi-column encoding, and apply integer stream compression to the individual columns. Data is stored in a compressed format, and decompressed on-the-fly and entered into the comparator engine. Each decompressor contains a configurable sequence of integer stream compression algorithm implementations, including a Delta Encoder, Run-Length Encoder (RLE) [103], and Group Varint Encoder [29]. Since each column shows different statistical distributions, the decompressor can be configured with a subset of provided compression algorithms to achieve maximum compression efficiency. For example, Delta encoding calculates and stores

the difference between two consecutive integers in a given integer list instead of the original integers. So it is beneficial for an ascending and small difference list.

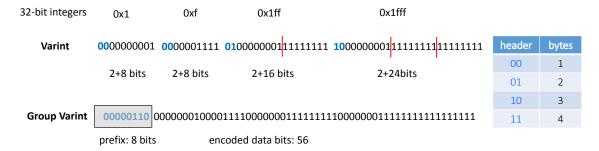

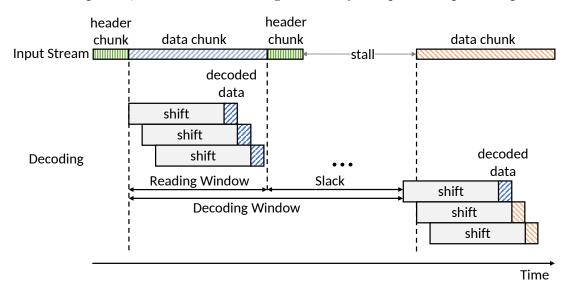

Varint encodes an integer by just storing the bytes that contain non zero bytes instead of the fixed number of bytes, coupled with a small header describing the actual number of encoded bytes. So each 32-bit integer needs 2-bit header that denotes the number of bytes stored. Obviously, it is only useful if the data being compressed is composed of typically small integers. Group Varint is an optimized variant of Varint that groups headers of 4 32-bit integers together (called a prefix). As a result, the 4 headers in the prefix occupy one byte and can be read at once, which provides higher decoding speed than Varint by reducing the amount of dependencies between each encoded value. Figure 1.3 shows the encoding process.

Figure 1.3: Varint and Group Varint Encoding

These three encoders can be combined as a chained structure to achieve excellent compression effect, such as a Delta-RLE-GroupVarint encoder or Delta-GroupVarint encoder depending on the needs and available hardware resources.

While the run-length compression and the delta compression algorithms can be effectively implemented for a necessary wide datapath in a straightforward manner, the Varint compression algorithm involves dependencies between data elements, limiting the performance and efficiency of the hardware implementation. For example, even with the Group Varint algorithm, at most 4 integers can be decoded at once, after which a multi-cycle shifting process is required to find the beginning of the next encoded set.

In order to achieve higher decoding speed we introduce a wider Group Varint algorithm where we group more encoded data into each header, allowing the algorithm to pre-calculate and shift the input stream while the data decompression process is still ongoing. With this minor adjustment, we demonstrate that the decompression engine can achieve wire-speed performance at a very low chip resource utilization.

We use this algorithm implementation to construct an accelerator for high-dimensional nearest neighbor search, ZipNN. Another characteristics of ZipNN is that it is implemented as a near-storage accelerator, enjoying the relatively higher internal bandwidth of the storage device, which is often  $2\times$  faster than the under-provisioned host-side PCIe bandwidth. Our system demonstrates using three column decompressors, that the near-storage accelerator is capable of supporting high enough decompressed bandwidth to saturate the comparator engine, achieving over  $6\times$  the performance compared to the same accelerator without compression, and over  $2\times$  the performance of multi-threaded software running on much costlier systems with enough fast random-access memory capacity to store the entire dataset.

## 1.4 Dissertation Contributions and Organization

This dissertation explores the use of hardware-optimized compression to solve the host-accelerator communication performance issue. The claimed contributions are listed as follows:

- 1. Design and implementation of high-efficiency hardware accelerated floating point compression algorithms (ZFP-V series).

- 2. Demonstrate a bandwidth-efficient scientific computation platform BurstZ+ that completely removes the host-accelerator communication bottleneck using ZFP-V.

3. Demonstrate ZipNN, which designs and implements a hardware-optimized library of heterogeneous integer compressors/decompressors to accelerate high-dimensional similarity search.

The rest of this dissertation is organized as follows:

Chapter 2 and 3 present how our ZFP-V algorithms solve the performance issue of hardware ZFP implementations using hardware-optimized design changes, and its application to grid-based scientific computation. Chapter 2 presents a detailed breakdown of inefficiencies of the original ZFP algorithm and how it can be improved with a minor algorithmic change, as well as the performance and resource utilization analysis of the hardware implementation. Detailed evaluation against software ZFP and unmodified hardware ZFP are conducted. Chapter 3 presents the BurstZ+ framework and evaluates its performance by three scientific computing accelerators.

Chapter 4 explores hardware-optimizing a high-throughput integer stream compression algorithm, and applies it to the high-dimensional similarity search application. The resulting system is called ZipNN, which uses a near-storage accelerator configuration of a heterogeneous library of hardware-optimized compression algorithms for integer streams, in order to accelerate high-dimensional similarity search.

Chapter 5 concludes this dissertation and discusses some potential future research work.

# Chapter 2

# **ZFP-V**: Hardware-Optimized Lossy

# Floating Point Compression

# 2.1 Introduction to Compression

Traditionally, compression is an effective method to reduce the storage cost and the overhead of data movement. As the amount of data processed by many important applications exceed the DRAM capacity of reasonable single-node machines, the limiting factor of processing capacity has become the data transfer speed between machines in a cluster, as well as the capacity and transfer speed of secondary storage devices.

Compression reduces cost and improves performance of computing by reducing the amount of data that must be stored and transported. Therefore, high-performance data compression algorithms are some of the critical components of high-performance computing.

### 2.1.1 Lossless Compression and Lossy Compression

Generally, compression algorithms can be categorized into two types: lossless compression that allows the original data to be reconstructed without any loss from the compressed data, and lossy compression that implements the compression by discarding partial original data. With lossy compression, there always exist an error between the decompressed data and the original one.

Common lossless algorithms include dictionary-based algorithms including the LZ series (e.g., LZ77/78, LZW, LZO, LZ4, etc.) and others, such as huffman coding, deflate, snappy, gzip, and so on. These algorithms find repetitions in the data stream and encode them using a shorter code. These algorithms are typically data-agnostic, and can provide high compression efficiency in a wide range of data types spanning from text to binary data. There are data type-specific algorithms as well, such as delta encoding, run-length encoding (RLE), Varint and Group Varint encoding, which can effectively compress integer numbers with specific distribution patterns. These algorithms typically do not provide as high compression ratios as the more complex dictionary methods, but are typically much simpler to implement, and provide very high performance.

On the other hand, lossy compression tolerates a certain amount of noise during the compression and decompression process, and are used for data types that can tolerate such noice, such as images, video, and sound. There are a lot of related industry standards, such as JPEG, MPEG, H.264/265, Xvid, and VP8. These algorithms can either be configured to achieve a certain compression ratio regardless of the introduced error, or to maintain noise below a certain level. If noise can be maintained below a user-defined level, the algorithm is considered error-controlled.

Another interesting area for lossy compression is floating point compression. Due to the high entropy involved in the floating point representation, they are notoriously difficult to compress. For example, gzip and other lossless compression methods typically achieve no compression on floating point data [121]. Floating point numbers are often used in the scientific computing and hence their compression is the focus of this dissertation.

### 2.1.2 Floating Point Compression

Traditional data-oblivious compression algorithms (based on Huffman coding, LZ77/78, and other methods) are typically unable to achieve high compression ratios on scientific data, which are often composed mainly of floating point (FP) values. Floating point data introduces a large amount of variation in the byte-stream which makes it difficult for data-oblivious algorithms to compress efficiently.

Recently proposed lossy floating-point compression algorithms take advantage of how a small amount of error is tolerable with floating-point operations, and provide very high compression ratios while ensuring data retrieval with errors within a user-specified margin.

Many lossy floating-point compression schemes have been researched, including ZFP [83, 37], SZ [35, 124, 81], FPZIP [84], ISABELLA [75], SSEM [115], and others, each with strengths and weaknesses.

These algorithms specifically targeting multi-dimensional floating point data, and allow the user to make a trade-off between compression ratio and error margin. They typically achieve an order of magnitude better compression ratios compared to data-oblivious algorithms like gzip, while controlling error below an acceptable margin for many scientific computing applications. Such highly efficient compression algorithms have improved the performance of high-performance computing while lowering the cost, by reducing storage and network requirements [11, 101, 57].

Of the many proposed algorithms, ZFP, proposed by Lindstrom et al. [83], and SZ, pro-

posed by Di et al.[35] are two most commonly used algorithms in the scientific computing community [1, 88, 123, 101], with different strengths and weaknesses on different data types.

These two are based on different principles: the former is based on block transformation and the latter is based on value prediction. For diverse scientific datasets, they play a complementary role. Tao et al. [125] points out that for some dataset ZFP is better, for others SZ is better.

### 2.1.3 Why Accelerate Floating-Point Compression Algorithms?

While these floating-point compression algorithms have been designed with performance in mind, running them on general-purpose processors does impose a limitation in performance. Our profiling of ZFP shows that neither a single thread compressor or decompressor on a highend Intel Xeon processor can achieve 1 GB/s of throughput even for favorably compressed data, often processing 200 MB or less per second. With SZ, according to benchmarks, a single-thread software version of SZ on a high-end Intel Xeon was able to process data at less than 100 MB/s [136]. Considering the multi-GB/s bandwidth of modern network and storage devices, software implementations of these algorithms will not be able to sustain the high throughput of modern system infrastructure.

Naturally, hardware-accelerated implementations would be desirable. There are not many prior work on floating-point compression algorithms for scientific data. GhostSZ [136] is a state-of-the-art FPGA implementation of SZ on the Arria-10 FPGA platform, and has demonstrated single-pipeline throughput of over 800 MB/s. To the best of our knowledge, there does not yet exist an FPGA implementation of ZFP. One system, TerseCades [101], uses ZFP in some of its pipelines, but it does not use a hardware version of the algorithm.

In this dissertation, We select ZFP due to its high efficiency on the datasets of our interest. In addition, most components of ZFP were readily parallelizable numerical operations.

### 2.1.4 Straightforward Hardware Implementation is not Enough!

While a hardware accelerator is a natural way to achieve high throughput while freeing up the CPU cores for useful work, a straightforward implementation of the ZFP algorithm is unable to achieve very high performance due to the inherently serial nature of some of its sub-components. Specifically, the "group testing" step is a completely serial process which, in the worst case, can emit a single bit per cycle.

To overcome the above-mentioned weaknesses, this paper presents ZFP-V, a hardware-optimized error-controlled lossy floating-point algorithm which modifies the ZFP algorithm to achieve higher performance on hardware accelerators. ZFP-V replaces the serial group testing step with a new algorithm using variable-length headers, which allows the accelerator to invariably handle a bit plane per cycle.

In the following sections, we will first introduce the basic principle of ZFP algorithm, then introduce the design and implementation of ZFP-V, and finally evaluate the performance of ZFP-V.

## 2.2 ZFP Compression Algorithm

ZFP is a lossy floating-point (both single- and double-precision) data compression scheme and was designed specifically for the high-precision numerical data used in scientific computing. It provides multiple compression modes including bit rate, error tolerance or precision control, making it very flexible. In our work, we use the most recent version 0.5.4 as the starting

point of our development.

ZFP applies compression/decompression on a block level, where it divides a 1D, 2D or 3D array into a series of small, fixed-size blocks which are processed independently. Each block consists of  $4^d$  values, where d is the dimension of the block. For example, a 3D block contains 4x4x4 values and a 2D block contains 4x4 values. The choice of block dimensions is up to the user, trading performance for better compression with higher dimensions. Block processing allows efficient compression at an arbitrary point in data, and also can achieve a very high throughput because multiple blocks can be processed in parallel.

For each block, compression is performed in four steps: (1) **Fixed-point conversion** via block-floating point representation [92], (2) **Block transform** to de-correlate the integers, (3) **Sequency ordering** to roughly order the transformed values according to their magnitude, and (4) **Embedded coding** to compactly encode data in the order of significance.

The rest of this section describes each step in more detail, and describes how the embedded coding step design causes a performance bottleneck in a hardware implementation.

#### 2.2.1 Fixed-Point Conversion

In this step, each floating-point value in a block is converted to a block-floating point (BFP)[132] representation, which is a floating-point representation where all values share the same exponent. By calculating the largest exponent in the block and expressing all values with respect to it, each value in the block is represented with a signed integer.

#### 2.2.2 Block Transform

ZFP uses a  $4^d$  orthogonal linear transformation that is similar to the discrete cosine transform (DCT) used in JPEG and other algorithms, to decorrelate the values in a block. Decorrelation results in many near-zero coefficients, which can be compressed efficiently. The unique structure of the linear transformation used by ZFP allows it to use the "lifting scheme", which factorizes the transformation into a series of simple filters, greatly simplifying its computation.

### 2.2.3 Sequency Ordering

Next, the values in the block are reordered by its "sequency", which is the sum of the indices of each value in each of its dimensions, i.e., by x + y + z for a 3D matrix. The ZFP authors show that after the block transform, the sequency ordering roughly corresponds to the magnitude ordering of the data, without having to perform a costly sort. The nearly sorted characteristic of sequency ordered data makes the embedded coding scheme highly efficient in terms of compression ratio.

### 2.2.4 Embedded Coding

In this step, ZFP applies embedded coding to compactly encode the current block and write the compressed bits to the output bit stream. There are many embedded coding techniques, such as zero-tree coding [24], set partitioning [109], etc. ZFP adopts a modified version of a technique called "group testing" to encode multiple bit planes.

#### Embedded Coding Using Group Testing

Put simply, group testing efficiently encodes a word by repeatedly testing if the remainder

of the word is zero, and only encoding it if there are nonzero bits present. As a result, group compression generally demonstrates good compression performance when there are enough zeros in the data. The group testing algorithm encoding a word x can be described via the following pseudocode:

The algorithm repeatedly checks if x is zero, and terminates with a done bit **0** if so. If not, it emits a *test bit* **1**, and emits bits one-by-one until a **1** is emitted, and repeats the process.

Given a 16-bit x value of "00000000001000101" in binary, x can be encoded as  $\underline{11101100010}$ , which requires only 11 bits. The underlined bits are test bits. It should be noted that this particular value of x can be efficiently compressed because it contains many leading zeros. As a counter example, if x is, say, "00001000001000101", which has a small number of leading zeros, the encoded result would be  $\underline{111011000110000010}$ . The encoding requires 18 bits, which is more than the uncompressed bit width of 16.

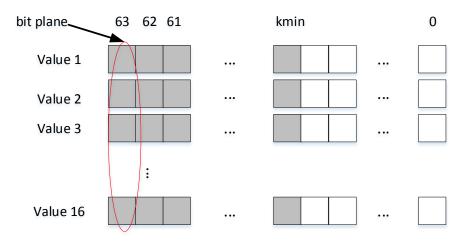

#### Bit Plane Encoding Using Group Testing

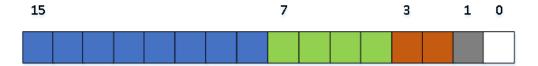

We use a simple example to show how group testing is used to compress a block of data. Fig. 2.1 shows the layout of a 2D block after the sequency ordering step. Here we use the double data type, so each value has a 64 bit width. The  $k^{th}$  bit of all values form a **bit plane** (0<sup>th</sup> bit plane is marked by a red ellipse). With a 4x4 block, we have 16 values. So each bit planes contains 16 bits, and we have 64 bit planes. ZFP encodes bit planes one by one from the most significant bit plane to the least significant.

Recall that ZFP allows users to specify the error tolerance and precision control, not all bit planes are encoded here. According to the parameters provided by users, ZFP first calculates a bit plane lower bound called "kmin", which means only the bit planes from 63 to kmin will be encoded. The greyed bits in Fig. 2.1 represents the bits to be encoded. The rest are simply ignored.

Figure 2.1: The bits distribution of a 2D block with double type

ZFP takes advantage of the data distribution of sequency ordering to further reduce data size. ZFP encodes parts of each bit plane verbatim before applying group testing, and the number of bits emitted verbatim is the MSB index of the previous bitplane. Because the sequency ordered data is roughly ordered by size, this scheme prevents group testing from being inefficiently applied to data with many nonzero bits. In other words, having roughly sorted numbers thanks to sequency ordering can result in an early exit per bit plane, after emitting all the nonzero least significant bits.

# 2.2.5 Inefficiency of Group Testing For Hardware

While group testing can result in efficient encoding, it has a high performance overhead in a hardware implementation, especially on a reconfigurable platform such as an FPGA with lower clock speed compared to ASICs. Because each loop iteration in Algorithm 1 depends on the results of its previous iteration, and because each iteration emits only one bit of data, a straightforward hardware implementation can only emit one bit per cycle and in the worst case may require  $4^d$  cycles to emit a single bit-plane.

While this problem can be somewhat mitigated during compression by parallelizing each bit-plane encoding, such an approach is less feasible for decompression. Because the offset of the next encoded bit plane depends on the encoding results of the current plane, we cannot start decoding the next bit plane until the current one is completely decoded.

In this dissertation, we have designed and implemented multiple algorithms based on ZFP, which result in more efficient hardware implementations on reconfigurable fabric. They not only improve a single bit plane's compression and decompression performance, but also achieve parallelism across multiple bit planes by replacing the group testing-based encoding algorithm with a header-based encoding scheme. The collection of our proposed algorithms is called ZFP-V. ZFP-V consists of 1D and 2D variants of ZFP-V, which we will denote as ZFP-V1 and ZFP-V2. Different optimization methods were employed for the two variants due to the differences in data distribution.

We describe these optimizations and their effects in the next sections.

# 2.3 ZFP-V Design and Implementation

In this section we describe the design and optimizations of our ZFP-V compression step by step. The first three steps in ZFP can be easily parallelized to support deterministic wire-speed operation without major design changes when implementing it on FPGA. For the last step "group testing" which is hard to parallelize, we introduce a novel and high-efficient algorithm to accelerate it.

We first describe a simple algorithm that uses a fixed-length header to improve performance, but loses compression efficiency. Then we provide a sequence of further optimization approaches we employed to both reclaim compression efficiency and also improve performance. Our optimizations include the variable-length header as well as the multi-level header approach for the 2D algorithm, and the coarse-grained header for the 1D algorithm. We also describe and compare the actual compressed bitstreams generated by these algorithms, as well as describe coarser-grained parallelism approaches using padded chunks of compressed data.

### 2.3.1 Fixed-Length Header-Based Encoding

As can be seen from last section, group testing can only process one bit at a time in the worst case, and therefore is often a completely serial process. As a result, the group testing step was usually the biggest performance bottleneck of our optimized ZFP implementation efforts.

By analyzing group testing encoding, we found that the low efficiency is from the fact that the test bits are mixed with the data bits. And because of the dependency relation, each bit plane has to be scanned serially bit-by-bit until a "1" is seen.

To expose more parallelism, we decided to use a header to store the number of data bits to be written for each bit plane. Algorithm 2 describes the encoding algorithm using headers. Because encoding each bit plane no longer requires an irregular loop, each bit plane can now be processed at once.

One weakness of a fixed-length header-based algorithm is that it could increase the size of compressed bit stream due to **the fixed overhead of the header bits**, reducing the compression ratio. Given a favorable example word "0000000001000101", we can write a

```

for k = 64 to kmin do

bitplane = extract_bitplane(block, k);

msb = msb_index(bitplane);

emit_bits(msb, sizeof(header));

emit_bits(bitplane, msb+1);

end

```

**Algorithm 2:** Encoding a block using a header-based algorithm

header "7" and "1000101" to the bit stream. Since a bit plane contains 16 bits for a 2D block, a naive header needs at most 4 bits. As a result, we need 4 + 7 = 11 bits, which is equal to the number of the result generated by the group testing. However, if the bit plane is a string with many leading zeros, e.g., "0000000000001001", group testing just needs 6 bits to encode it, but the new algorithm needs 4 + 4 = 8 bits. The header consumes 4 bits which are too much for this string.

As an improvement, we can partition this string into 8 substrings with each one containing 2 bits, like "00|00|00|00|00|00|00|00|00". In this scheme, we just need 3 bit to store the number of nonzero substrings. In this case, we store the data bits in substring units. As a result, we need 3 + 4 = 7 bits and the compressed bits are "0101001". The underlined bits are the header and represent 2 2-bit substrings that followed. Similarly, we can partition the string into 4 4-bit substrings, then we just need 2 bits to store the header. However, our experiments show it is not better than the 3-bit substring. If a substring is "0001", for example, we will waste 3 more bits than the 4-bit header scheme, and 2 more bits than the 3-bit scheme.

We call these schemes with fixed header width fixed length header (FLH) algorithms. Though they can simplify the original group testing algorithm and increase the parallelism, they cause the compression ratio to drop significantly. In next section, we will introduce a variable length header (VLH) algorithm that can achieve as much bit-level parallelism as the FLH algorithms while causing negligible compression ratio loss.

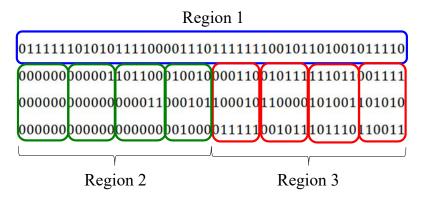

#### 2.3.2 Variable Length Header (VLH) for ZFP-V2

We showed that fixed-length headers can cause much extra bit overhead by using a header for each bit plane. The biggest problem in this is mostly from adding a fixed overhead to bitplanes that consist entirely of zeros, which are not only very common, but also can be very efficiently compressed in the original algorithm. Actually, we observed that for many benchmarks, both real-world and synthetic, the distribution of MSB indices were skewed towards either lower or higher indices, without many values in the middle<sup>1</sup>. In order to solve the issue caused by FLH, based on this observation, we partition the binary string of a bit plane into 5 sets of exponentially increasing width, and assign each of them a unique code word as its header. As a result, different sets can have different header lengths. This is called variable length header (VLH) scheme. Fig. 2.2 shows the 5 sets with different colors, and Table 2.1 shows the variable length header coding scheme. For example, if the word has no nonzero bits, we use "0" to represent the header and write only one header bit and one data bit to the stream; if msb is 1, we use "100" to represent the header and write three header bits and two data bits to the stream; if the msb is 2 or 3, we use "101" to encode the header and write three header bits and 4 data bits to the stream. The reason encoding is skewed in this way is because we wanted to improve the common case where a bit plane has zero or only one nonzero bit.

This encoding efficiently handles bit planes with one or less nonzero bits using two bits, and also requires only a three-bit header in all other cases. Though VLH needs a little bit more logic to encode or decode the header before processing the data bits than FLH, both of them can process one bit plane at a time, which provides much better performance than the original group testing algorithm.

<sup>&</sup>lt;sup>1</sup>For the eight real-world datasets we evaluated in Section 2.5, 80% of all encoded bitplanes had MSB indices that were either less than 1, or more than 11. (46% less than 1, 34% more than 11)

Figure 2.2: The MSB distribution of the binary string in a bit plane

Table 2.1: Header Coding of the bit plane

| MSB    | Code word | #header_bits | $\# data\_bits$ |

|--------|-----------|--------------|-----------------|

| 0      | 0         | 1            | 1               |

| 1      | 100       | 3            | 2               |

| 2 - 3  | 101       | 3            | 4               |

| 4 - 7  | 110       | 3            | 8               |

| 8 - 15 | 111       | 3            | 16              |

#### 2.3.3 2-Layer Header for ZFP-V2

Though VLH effectively improves 2D ZFP's encoding/decoding performance, the introduction of a variable-length header introduces dependency between the offsets of each encoded bit-plane, limiting parallelization and potentially harming performance. For example, while each bit plane can be invariably decoded in a single clock cycle, we cannot start working on the next bit plane at the same time because we cannot start decoding the next header before we know the encoded length of the header and data bits in the previous bit plane. Since a bit plane is only 16 bits for 2D, this approach as-is cannot achieve our performance goals.

In order to overcome this limitation caused by inter-bit plane dependency while maintaining high compression efficiency, we implement a 2-layer header structure. This is a new algorithmic improvement over the originally published 2D ZFP-V algorithm [121].

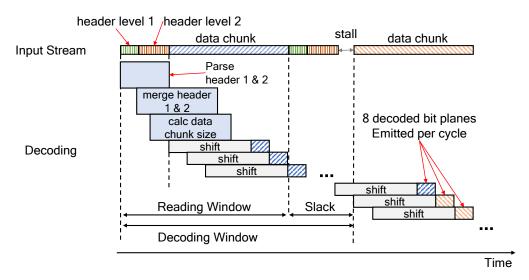

We observe from Table 2.1, only the bit planes whose MSB is 0 need a 1-bit header and all others need a 3-bit header. So we extract the first bit of all original headers to group them to a "header-of-headers" called "header level 1", and then group the rest of the original headers to a "header level 2". Since at most 64 bit planes need to be encoded or decoded, header level 1 encodes at most 64 bits, and header level 2 encodes at most 192 bits. The number

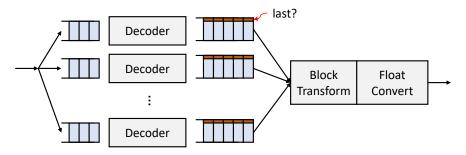

of encoded bit planes are also encoded in the compressed format. This is described in more detail in Section 2.3.5. When decompressing, we can conduct completely parallel bit-level operations on header level 1 to get each bit plane's header size, and hence the size of all headers. We can then immediately read all header level 2 headers to reconstruct the headers of all bit planes, within one cycle. With the decoded headers, we can calculate the size of each compressed bit plane in the next cycle, and decide how many bit planes to decompress in parallel. While theoretically this approach can decode all 64 bit planes in parallel in a single cycle, we have decided on a narrower datapath to avoid the high resource utilization and routing difficulty of very wide datapaths. Our current implementation decompresses 8 bit planes (128 bits) per cycle. On our prototype running at 250 MHz clock speed, this guarantees a 4 GB/s of decompression bandwidth lower bound per pipeline.

#### 2.3.4 Coarse-Grained VLH for ZFP-V1

VLH is used in ZFP-V2 and effectively improves its throughput. However, this approach would not be very efficient for the 1-dimensional algorithm ZFP-V1 because of the following observations: First, putting a header per bit plane is too expensive, because each block in the 1D ZFP only has four values, resulting in only four bits per bit plane. Second, after block transform and sequency ordering, the first 64-bit element of the four has a very high index of the first nonzero MSB bit.

In order to address the first issue of header overhead, ZFP-V1 uses a coarse unit of encoding, and attaches a 2-bit header per 6 bit-planes instead of attaching a header per each bit-plane. The six bit-planes are simply concatenated, to keep the nonzero bits in the lower bits as much as possible.

However, the second issue of a high MSB in the first element harms the compression effectiveness of this scheme, because almost all sub-groups described below would have nonzero bits

in upper bits because of the first element. To solve this second issue, ZFP-V1 treats the first element specially, and encodes it first before encoding other elements. Only the remaining three elements, which often have many leading zeros, are encoded using the coarse-grained header.

Figure 2.3: Three different encoding schemes are used for three different regions (Blue, green, red)

Figure 2.3 shows the resulting different regions of the four-element unit with different encoding methods, using an example block after sequency ordering. The first, top-most element is first encoded separately. The number of bits from the first element that is encoded depends on the requested error margin. The remaining three elements are divided into two groups (region 2 and 3), which are in turn divided into four sub-groups. Each group is assigned a two-bit header, representing how many sub-groups need to be encoded. If the desired error margin is achieved within the first group (region 2), encoding can stop after encoding the first element (region 1) and valid sub-groups of the green group. If the error margin requires more bit planes to be encoded, region 3 is encoded as well.

In most cases, we only encode up to the first 48 bit-planes in order to ensure efficient compression, as seen in Figure 2.3. In extremely rare cases when more than 48 bit-planes need to be encoded, we simply encode the whole block uncompressed, in order to simplify the compression accelerator.

The design of ZFP-V1 encoding ensures that one block of four elements can be encoded in

at most three cycles, where one cycle is spent for each of the blue, green, and red regions. This fact, coupled with pipelining, allows ZFP-V1 to achieve very high throughput with very small on-chip resources.

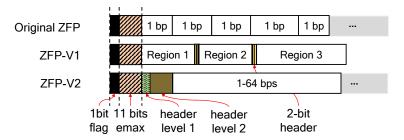

#### 2.3.5 Bitstream Structure

Figure 2.4 shows what the encoded block looks like for the original ZFP, ZFP-V1 and ZFP-V2, respectively. For all methods, the first two encoded elements are a 1-bit zero-block flag bit, and an 8 or 11 bit *emax* field. The zero-block flag denotes whether all elements in this block are zeros or not. If this block is a zero block, ZFP just simply writes a '0' to the bitstream and processes the next block without any more action. If it is not a zero block, it stores an 8 bit (single precision floating point) or 11 bit (double precision floating point) *emax* value that represents the maximum exponents among all the floating point values in this block, encoded with an offset similarly to the floating point encoding. This *emax* value is used to recover the number of bit planes encoded, by comparing it against the error margin requested during compression.

The encoding scheme for the three approaches begin to differ after this point. For the original ZFP, it then proceeds to encode bit planes one by one, where each bit plane is encoded in a 1 to 31-bit variable-length format with mixed flag and data bits. On the other hand, ZFP-V1 first encodes the first element of the 4-element block (region 1), and then one or both of regions 2 and 3, each coupled with a 2-bit header. ZFP-V2 encodes the level 1 and 2 headers, and then the 1 to 64 encoded bit planes in sequence.

Figure 2.4: The encoded block layout of the original ZFP, ZFP-V1 and ZFP-V2

## 2.3.6 Independent Aligned Chunks