## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Advanced Architectures for Efficient mm-Wave CMOS Wireless Transmitters

#### **Permalink**

https://escholarship.org/uc/item/2bj7g90f

#### **Author**

CHEN, JIASHU

### **Publication Date**

2013

Peer reviewed|Thesis/dissertation

#### Advanced Architectures for Efficient mm-Wave CMOS Wireless Transmitters

by

Jiashu Chen

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineeing - Electrical Engineeing and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Robert G. Meyer Professor Paul K. Wright

Fall 2013

Advanced Architectures for Efficient mm-Wave CMOS Wireless Transmitters

Copyright © 2013

by

Jiashu Chen

#### Abstract

Advanced Architectures for Efficient mm-Wave CMOS Wireless Transmitters

by

#### Jiashu Chen

Doctor of Philosophy in Engineeing - Electrical Engineeing and Computer Sciences

University of California, Berkeley Professor Ali M. Niknejad, Chair

With fast growing consumer demand for high speed mobile data capacity, wireless spectrum has become increasingly precious. This drives the evolution of the personal wireless communication, with new standards developed to improve the spectral efficiency. However, the available spectrum below 10GHz is very limited and packing more bits per second into the same bandwidth requires larger energy consumption as well as more stringent radio and MODEM performance. As a result, such an approach is not sustainable for meeting the future demand. A natural path is to move into higher frequency bands which have larger spectrum bandwidth but less commercial usage. Recent years have witnessed vast technology development on V-band (60GHz) Wireless Personal Area Networks (WPAN) and E-band (80GHz) point-to-point cellular backhauls. Meanwhile, the advancement of low-cost CMOS technologies enables researchers to significantly improve the integration level of high speed mm-wave radios with traditional analog and digital circuitry. However, current mmwave radio transmitters suffer from short communication distance and low energy efficiency. This is mainly caused by the reduced performance of the CMOS transmitters employing traditional Power Amplifiers (PAs) that suffer from low transistor breakdown voltage, low power gain and poor back-off characteristics. This dissertation investigates the challenges of designing efficient mm-wave transmitters for both long range and short range applications, and proposes concepts and techniques that can potentially break the barriers imposed by the low cost digital CMOS process. The scope of investigation and proposal extends from the architecture level down to the transistor level. Specifically, on-chip and spatial power combining techniques are analyzed and implemented to achieve larger transmitter Equivalent Isotropically Radiated Power (EIRP). To enhance the average efficiency for modulated signals with high Peak-to-Average-Power-Ratio (PAPR), a direct digital-to-RF conversion architecture is proposed and implemented, enabling dynamic DC power scaling. Finally, a Quadrature Spatial Combining concept is introduced to eliminate the tradeoff between low insertion loss and high isolation present in a traditional Cartesian architecture with on-chip signal combiners. Prototype chips are fabricated and tested in 65nm CMOS technology to verify the proposed architectures and techniques.

| Dedicated to my<br>this far | v parents and grand | lparents, without | whom I would nev | er have reached |

|-----------------------------|---------------------|-------------------|------------------|-----------------|

|                             |                     |                   |                  |                 |

|                             |                     |                   |                  |                 |

|                             |                     |                   |                  |                 |

# Contents

| $\mathbf{C}$ | onter                  | nts                                      | ii |

|--------------|------------------------|------------------------------------------|----|

| Li           | $\operatorname{st}$ of | Figures                                  | v  |

| Li           | $\operatorname{st}$ of | Tables                                   | X  |

| $\mathbf{A}$ | ckno                   | wledgements                              | xi |

| 1            | Intr                   | roduction                                | 1  |

| <b>2</b>     | Wir                    | reless Transmitter Basics                | 6  |

|              | 2.1                    | Link Budget Analysis                     | 6  |

|              | 2.2                    | Wireless Transmitter Architectures       | 10 |

|              | 2.3                    | Power Amplifiers (The ABCDEFs)           | 12 |

|              |                        | 2.3.1 Linear Classes (Class-A/B/AB)      | 13 |

|              |                        | 2.3.2 Non-Linear Classes (Class-C/D/E/F) | 16 |

|              | 2.4                    | The Extended Class-E/F Family            | 21 |

|              | 2.5                    | High Frequency Challenges                | 27 |

| 3            | Line                   | ear Transmitter                          | 29 |

|              | 3.1                    | Power Combining Techniques               | 29 |

|              | 3.2                    | DAT Combiners                            | 32 |

|              | 3.3                    | A 60GHz DAT Power Amplifier              | 35 |

|              |                        | 3.3.1 Design Procedure                   | 37 |

|              |                        | 3.3.2 CW Measurement Results             | 41 |

|              |                        | 3 3 3 Modulation Measurement Results     | 41 |

| 4 | Bea | mforming Transmitter                           | 49  |

|---|-----|------------------------------------------------|-----|

|   | 4.1 | Antenna Basics                                 | 49  |

|   | 4.2 | Beamforming through Antenna Array              | 52  |

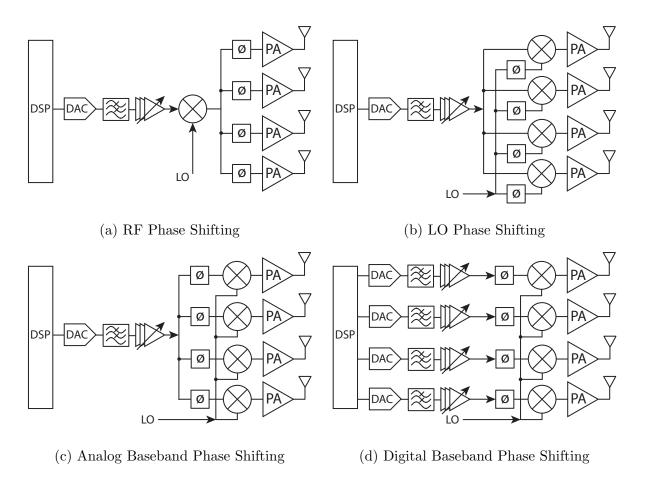

|   | 4.3 | Phased Array Architectures                     | 55  |

|   |     | 4.3.1 RF Phase Shifting                        | 55  |

|   |     | 4.3.2 LO Phase Shifting                        | 58  |

|   |     | 4.3.3 Analog Baseband Phase Shifting           | 58  |

|   |     | 4.3.4 Digital Baseband Phase Shifting          | 60  |

|   | 4.4 | Architecture Power Comparison                  | 60  |

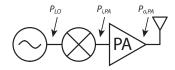

|   |     | 4.4.1 RF Phase Shifting                        | 62  |

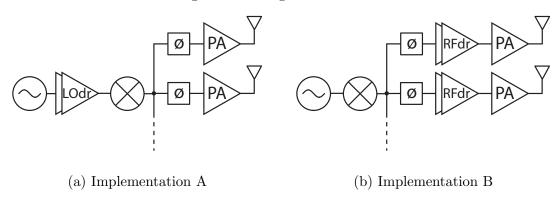

|   |     | 4.4.2 LO Phase Shifting                        | 64  |

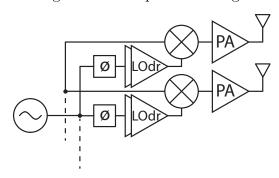

|   |     | 4.4.3 Analog Baseband Phase Shifting           | 64  |

|   |     | 4.4.4 Generalized Comparison                   | 66  |

|   | 4.5 | Phase Shifters                                 | 66  |

|   |     | 4.5.1 Resolution                               | 66  |

|   |     | 4.5.2 Implementation                           | 72  |

|   | 4.6 | Low Power 4-Element Phased Array               | 74  |

|   |     | 4.6.1 Phase Rotating Quadrature Mixer          | 75  |

|   |     | 4.6.2 ZVS PA                                   | 79  |

|   |     | 4.6.3 Experimental Results                     | 81  |

| 5 | Dir | ect Digital-to-RF Transmitter                  | 85  |

|   | 5.1 | Traditional Efficiency Enhancing Architectures | 86  |

|   | 5.2 | Direct Digital-to-RF Conversion                | 88  |

|   | 5.3 | Quadrature Spatial Combining                   | 89  |

|   |     | 5.3.1 Transmitter EVM                          | 91  |

|   |     | 5.3.2 Radiation Pattern                        | 93  |

|   | 5.4 | Circuit Implementation                         | 98  |

|   |     | 5.4.1 mm-Wave Switching PA-DAC                 | 99  |

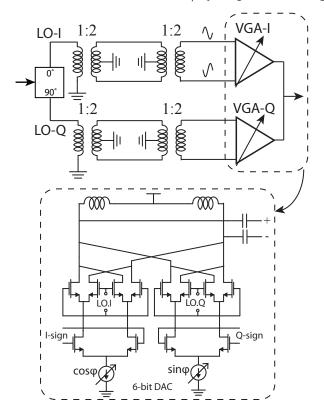

|   |     | 5.4.2 Phase Shifters                           | 103 |

|   |     | 5.4.3 LO Generation and Distribution           | 105 |

|   |     | 5.4.4 Mixed-Signal Baseband Signal Processing  | 106 |

| Bi | bliog | raphy   |                                | 127 |

|----|-------|---------|--------------------------------|-----|

| 6  | Con   | clusion | ıs                             | 125 |

|    | 5.6   | Digital | Calibration and Pre-distortion | 123 |

|    |       | 5.5.2   | Package Measurement Results    | 112 |

|    |       | 5.5.1   | CW Mode Measurement Results    | 112 |

|    | 5.5   | Experi  | mental Results                 | 110 |

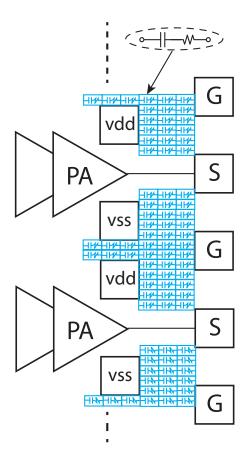

|    |       | 5.4.5   | Supply Bypass Network          | 108 |

# List of Figures

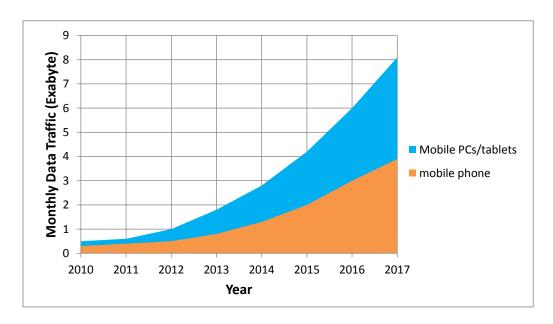

| 1.1  | Predicted mobile traffic growth                                                        | 2  |

|------|----------------------------------------------------------------------------------------|----|

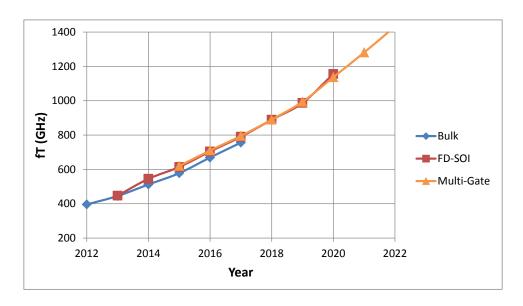

| 1.2  | ITRS roadmap for RF CMOS                                                               | 3  |

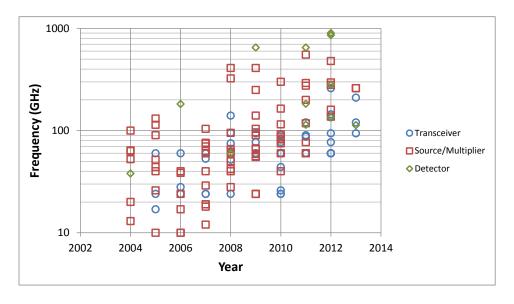

| 1.3  | Operating frequency of CMOS circuits and systems                                       | 3  |

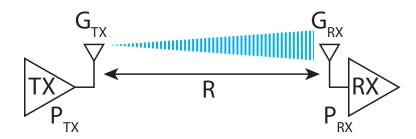

| 2.1  | Wireless link budget analysis                                                          | 6  |

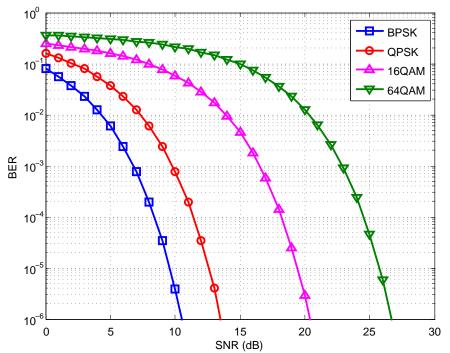

| 2.2  | BER as a function of SNR                                                               | 8  |

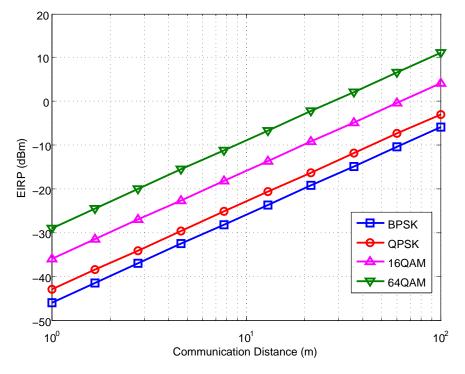

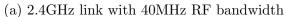

| 2.3  | Required EIRP as a function of communication distance                                  | 9  |

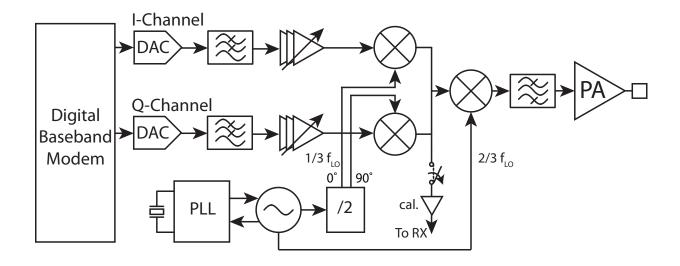

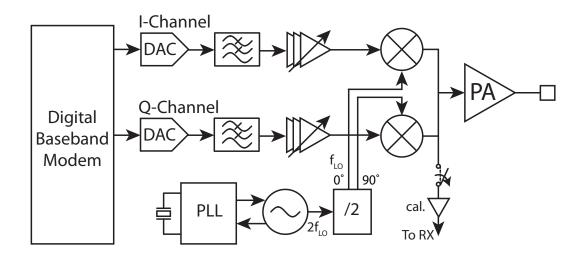

| 2.4  | A sliding-IF superheterodyne transmitter                                               | 11 |

| 2.5  | A direct conversion transmitter                                                        | 11 |

| 2.6  | Schematics and V-I waveforms of Class-A amplifiers                                     | 15 |

| 2.7  | Schematics and V-I waveforms of Class-B amplifiers                                     | 15 |

| 2.8  | Schematics and V-I waveforms of Class-C amplifiers                                     | 18 |

| 2.9  | Schematics and V-I waveforms of Class-D amplifiers                                     | 18 |

| 2.10 | Schematics and V-I waveforms of Class-E amplifiers                                     | 20 |

| 2.11 | Schematics and V-I waveforms of Class-F amplifiers                                     | 20 |

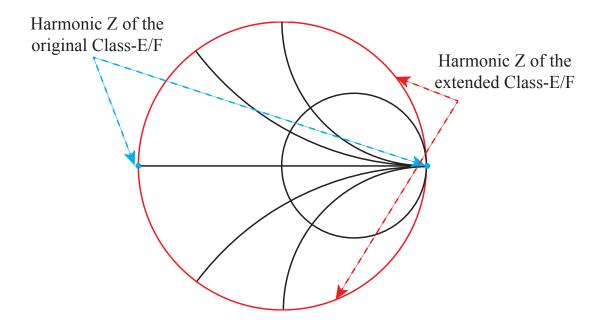

| 2.12 | Harmonic impedance region of the extended Class-E/F family on the Smith Chart          | 23 |

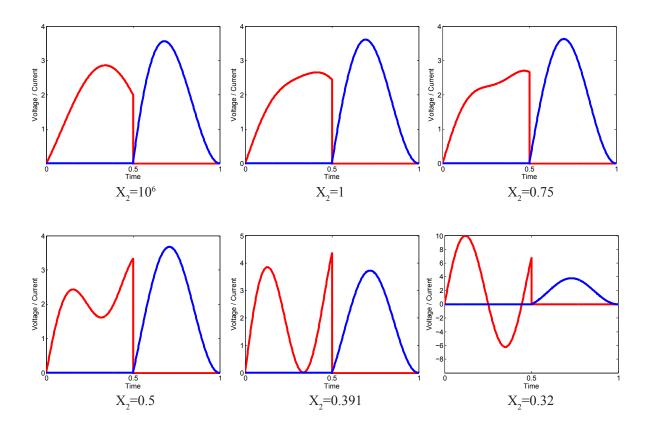

| 2.13 | V-I waveforms of the Class-E/F $_{X2}$ tunings with various $X_2$ values               | 24 |

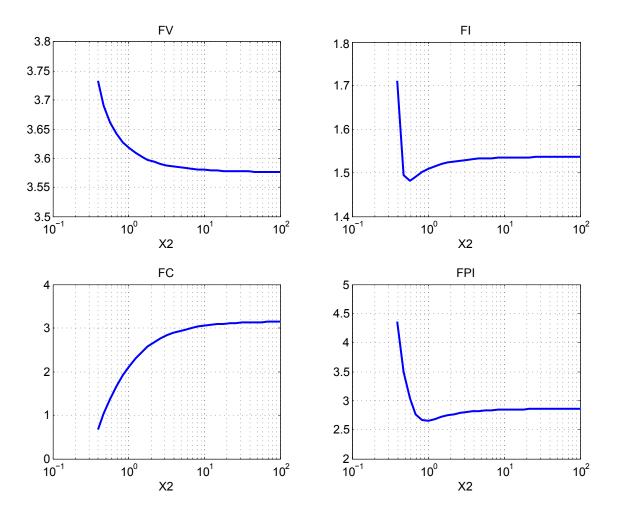

| 2.14 | Waveform FoM of Class-E/F $_{X2}$ tunings as a function of $X_2$                       | 25 |

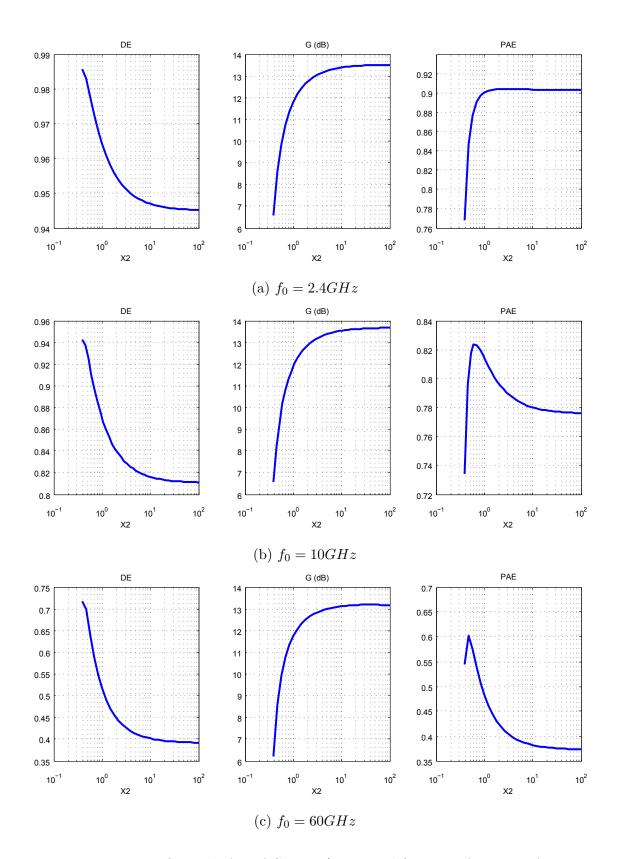

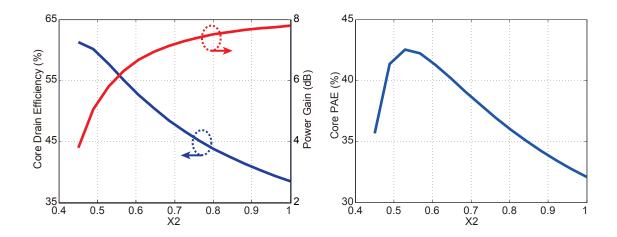

| 2.15 | $\eta_D,G_p$ and PAE of Class-E/F <sub>X2</sub> amplifiers as a function of $X_2$      | 26 |

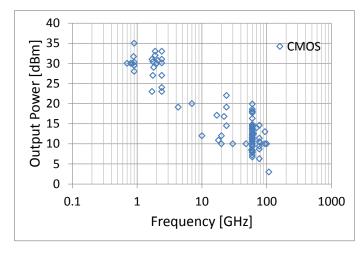

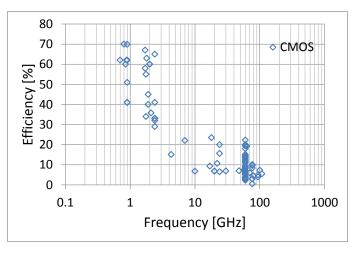

| 2.16 | A survey of CMOS PA performance                                                        | 28 |

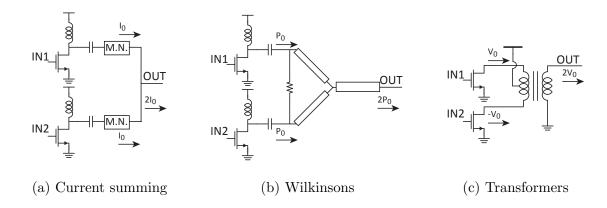

| 3.1  | On-chip power combining techniques                                                     | 30 |

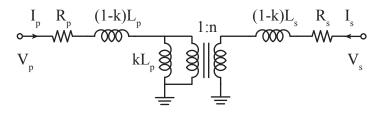

| 3.2  | Equivalent circuit model of a transformer                                              | 30 |

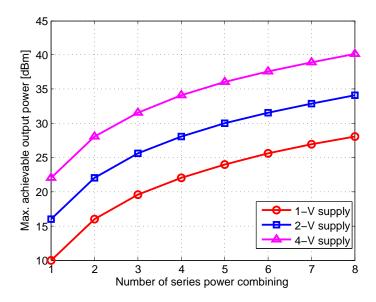

| 3.3  | Theoretical output power of a DAT based PA as a function of number of combined inputs. | 32 |

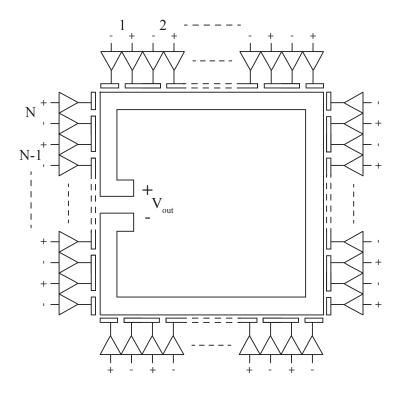

| 3.4  | Increase the number of DAT inputs to the limit                                                     | 33 |

|------|----------------------------------------------------------------------------------------------------|----|

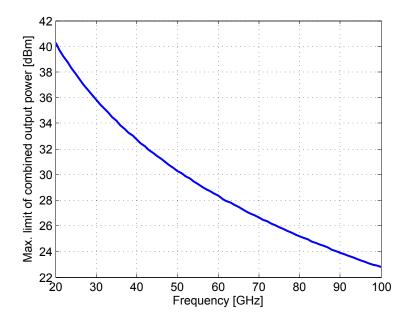

| 3.5  | Maximum total combined output power                                                                | 35 |

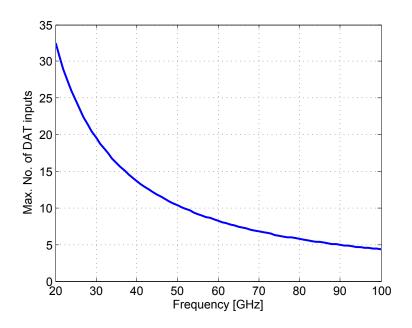

| 3.6  | Maximum number of DAT inputs                                                                       | 36 |

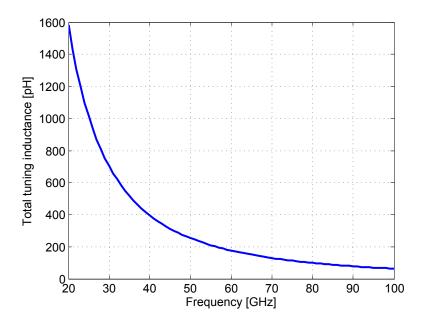

| 3.7  | Total tuning inductance of the transformer                                                         | 36 |

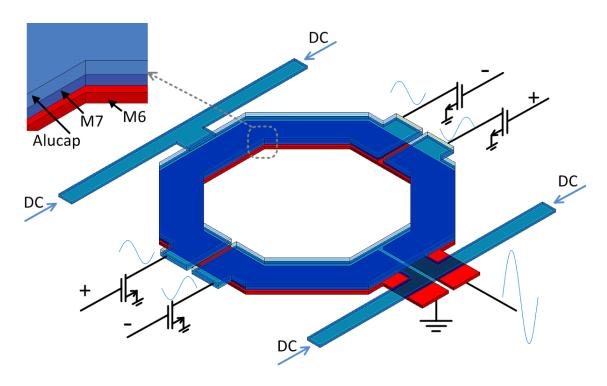

| 3.8  | Quad-input 60GHz DAT combiner                                                                      | 38 |

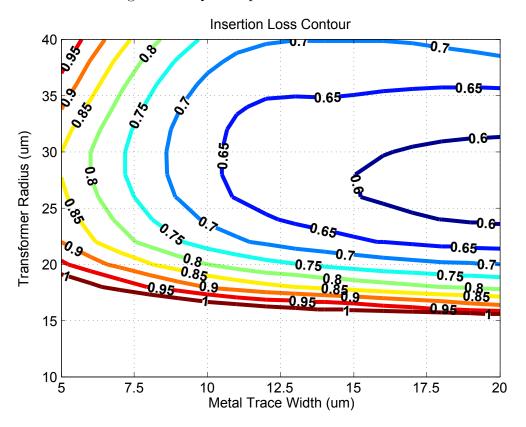

| 3.9  | Insertion loss of the quad-input DAT combiner                                                      | 38 |

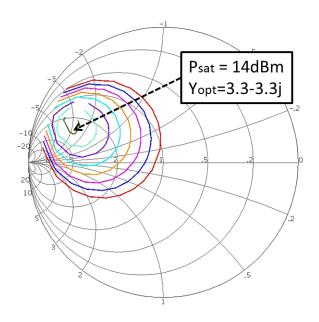

| 3.10 | Load-pull of a $140\mu m$ transistor                                                               | 36 |

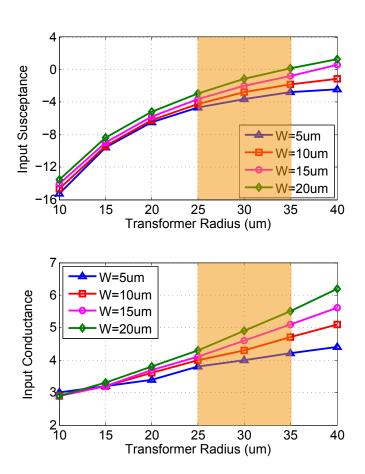

| 3.11 | Input susceptance and conductance of the quad-input DAT combiner $$                                | 36 |

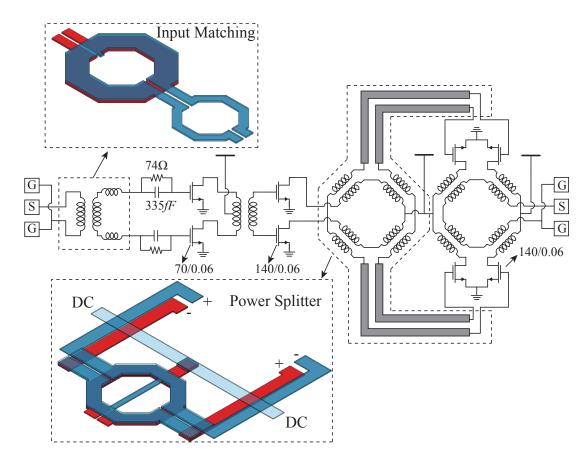

| 3.12 | Schematic of the three stage 60GHz PA                                                              | 40 |

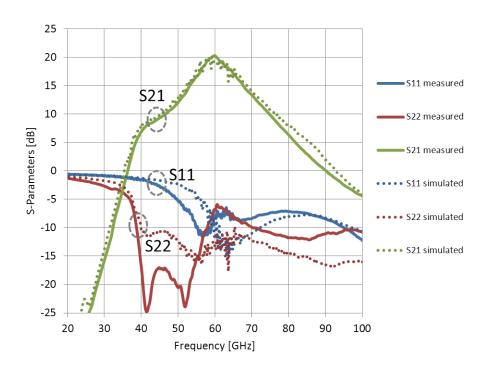

| 3.13 | S-Parameters of the 60GHz PA                                                                       | 42 |

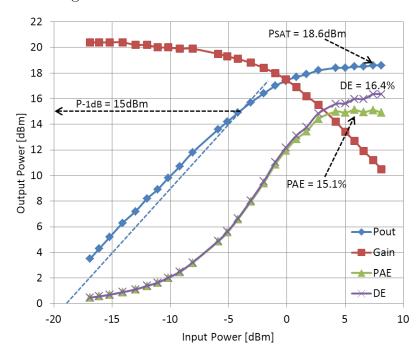

| 3.14 | Output power, efficiency and gain of the 60GHz PA                                                  | 42 |

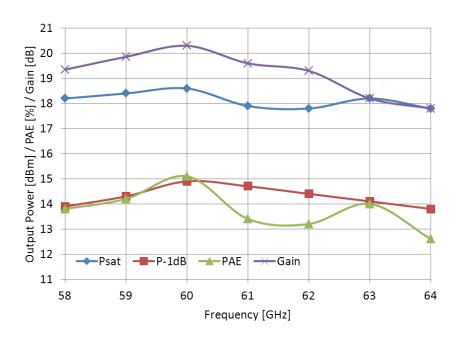

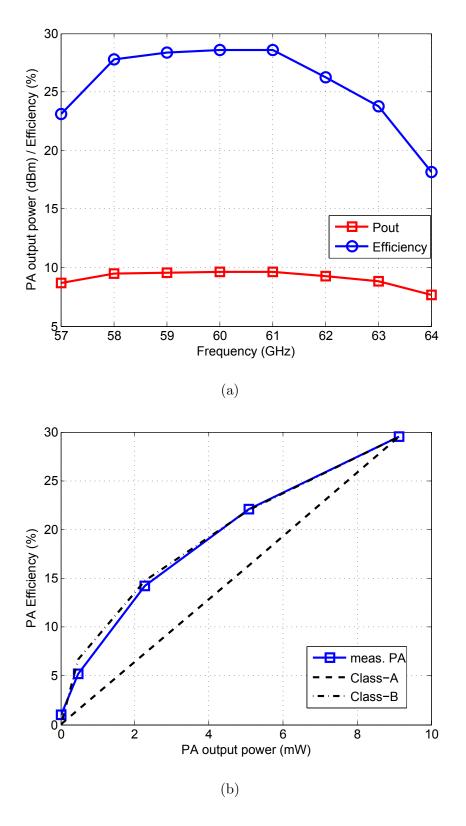

| 3.15 | $60\mathrm{GHz}$ PA large signal performance across the IEEE 802.15.3c band. $$                    | 43 |

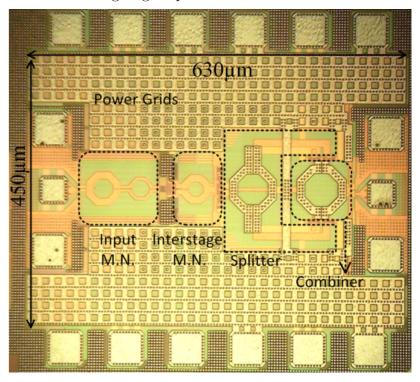

| 3.16 | Chip micrograph of the 60GHz PA                                                                    | 43 |

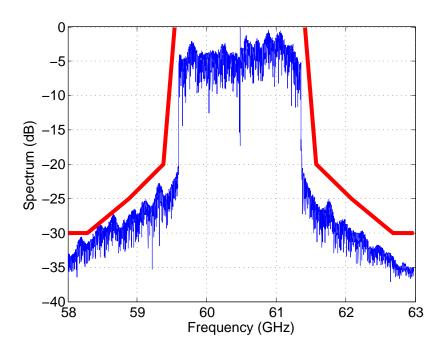

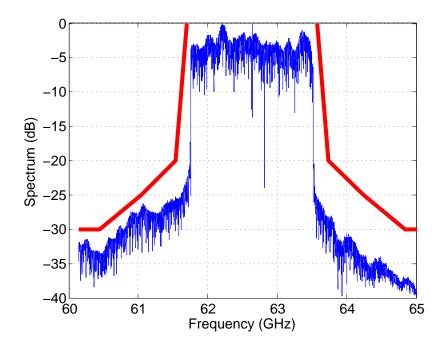

| 3.17 | PA output spectrum and 802.15.3c spectral mask for Channel 2                                       | 44 |

| 3.18 | PA output spectrum and 802.15.3c spectral mask for Channel 3 $\dots \dots$                         | 44 |

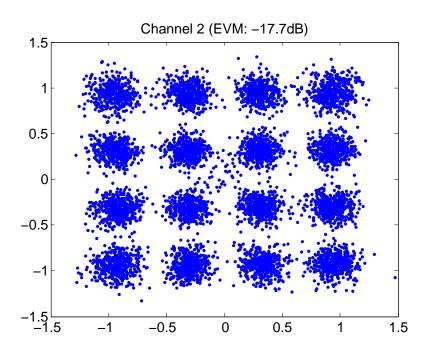

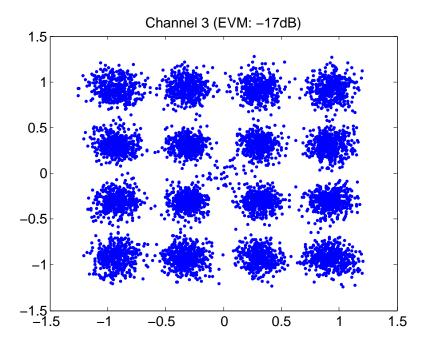

| 3.19 | Received constellation of the 3.8Gb/s 512 sub-carrier 16-QAM OFDM signal for Channel 2             | 45 |

| 3.20 | Received constellation of the $3.8 \mathrm{Gb/s}$ 512 sub-carrier 16-QAM OFDM signal for Channel 3 | 45 |

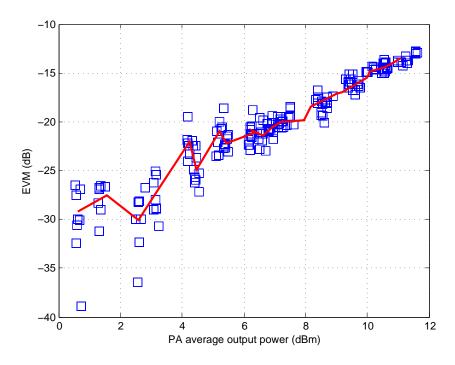

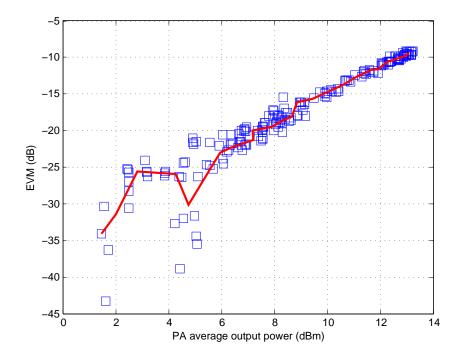

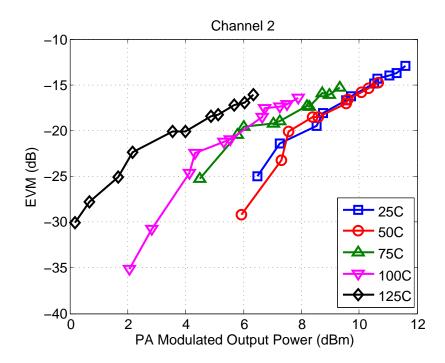

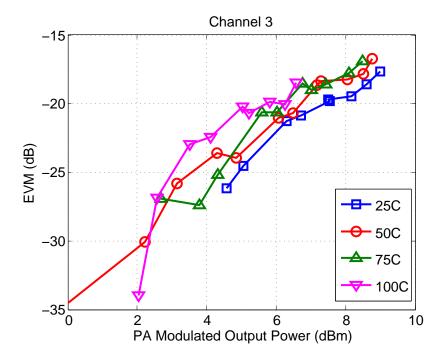

| 3.21 | Measured PA EVM for channel 2 as a function of average output power                                | 47 |

| 3.22 | Measured PA EVM for channel 3 as a function of average output power                                | 47 |

| 3.23 | Measured PA EVM characteristic for channel 2 at different ambient temperatures                     | 48 |

| 3.24 | Measured PA EVM characteristic for channel 3 at different ambient temperatures                     | 48 |

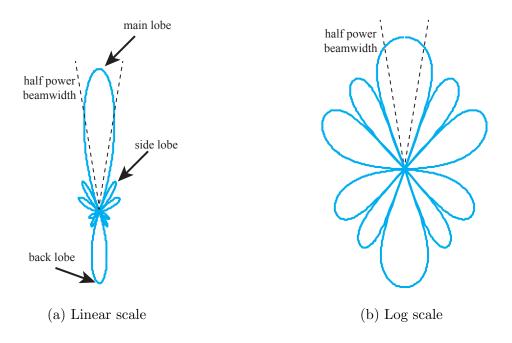

| 4.1  | Antenna radiation pattern in a polar plot                                                          | 50 |

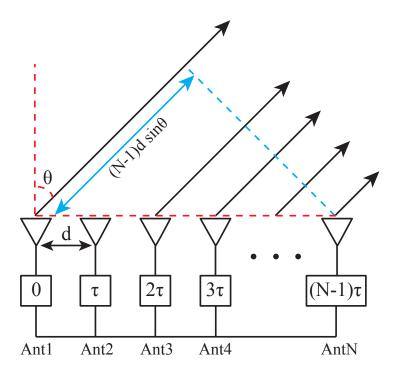

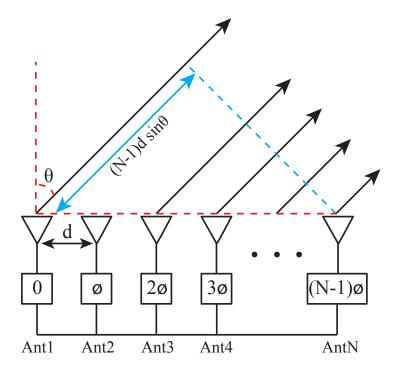

| 4.2  | N-element timed array                                                                              | 53 |

| 4.3  | N-element phased array                                                                             | 54 |

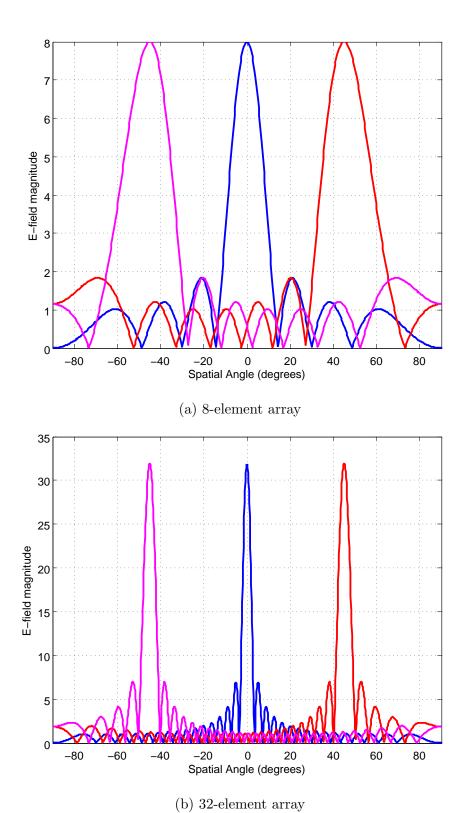

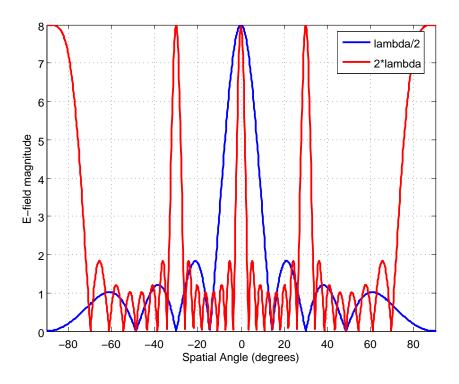

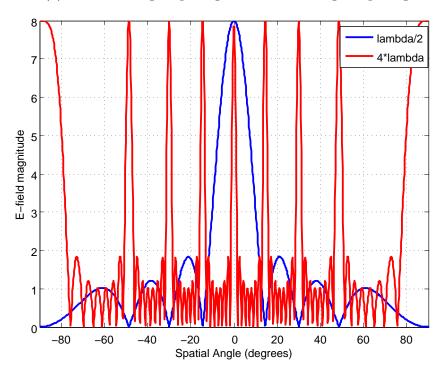

| 4.4  | Phased array E-field magnitude patterns                                                            | 56 |

| 4.5  | Phased array E-field magnitude patterns with various element spacings                              | 57 |

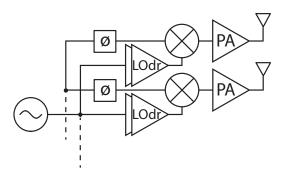

| 4.6  | Phased array architecutres (Transmitter)                                                           | 59 |

| 4.7  | Single element transmitter                                                                         | 61 |

| 4.8  | RF phase shifting                                                                                                             | 61 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | LO phase shifting                                                                                                             | 61 |

| 4.10 | Analog baseband phase shifting                                                                                                | 61 |

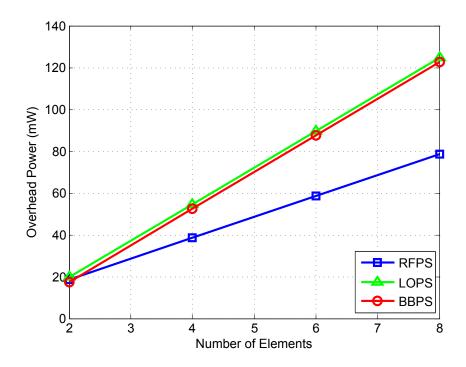

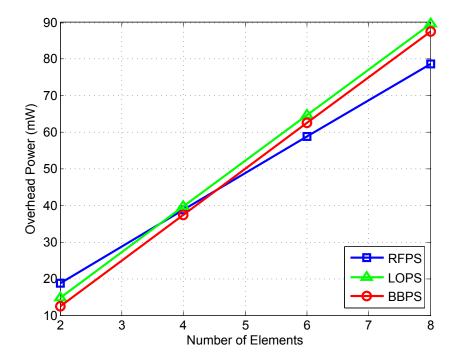

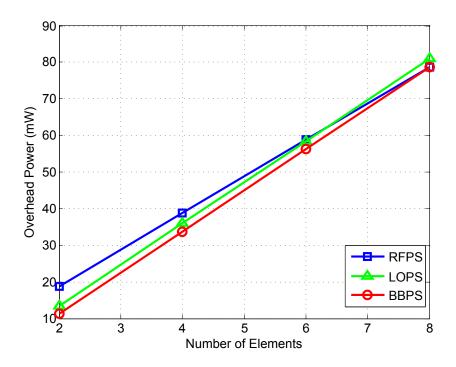

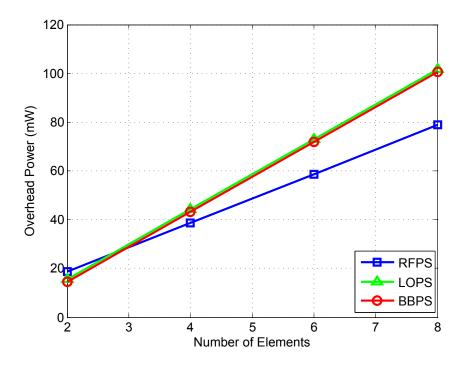

| 4.11 | Overhead power $(G_{mix} = 2, \frac{PAE_{amp,lin}}{PAE_{mix}} = 3, \frac{PAE_{amp,lin}}{PAE_{amp,non}} = 2, G_{PS} = 1/8)$    | 67 |

| 4.12 | Overhead power $(G_{mix} = 2, \frac{PAE_{amp,lin}}{PAE_{mix}} = 2, \frac{PAE_{amp,lin}}{PAE_{amp,non}} = 2, G_{PS} = 1/8)$    | 67 |

| 4.13 | Overhead power $(G_{mix}=2, \frac{PAE_{amp,lin}}{PAE_{mix}}=1.75, \frac{PAE_{amp,lin}}{PAE_{amp,non}}=2, G_{PS}=1/8)$         | 68 |

| 4.14 | Overhead power $(G_{mix} = 4, \frac{PAE_{amp,lin}}{PAE_{mix}} = 1.75, \frac{PAE_{amp,lin}}{PAE_{amp,non}} = 2, G_{PS} = 1/8)$ | 68 |

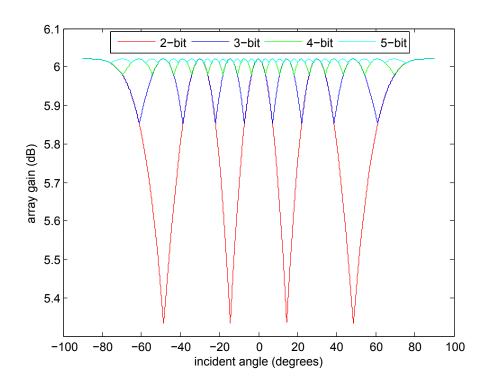

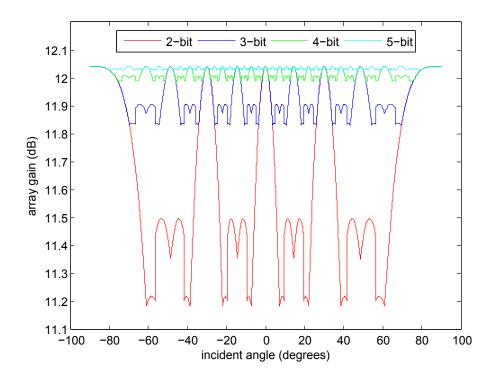

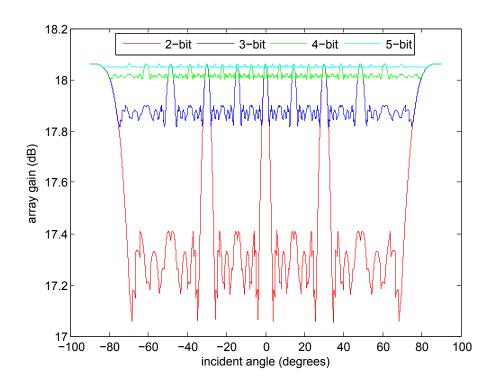

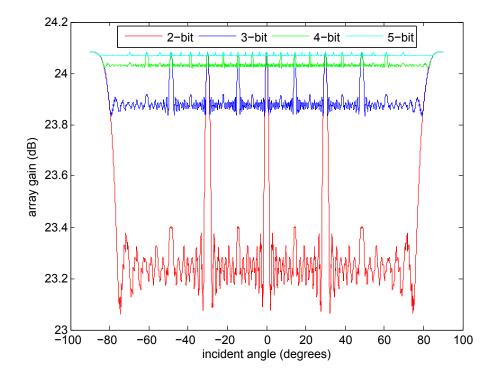

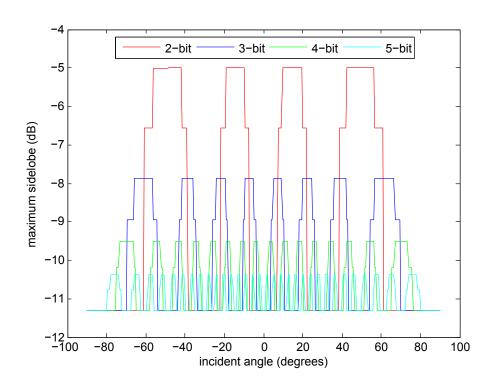

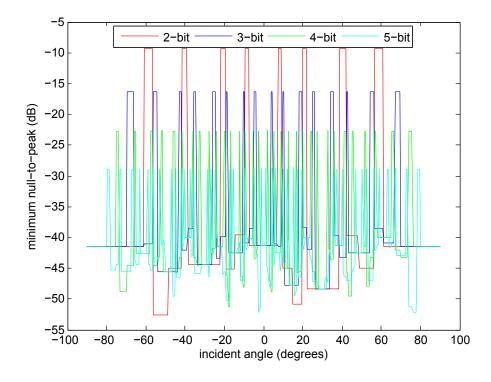

| 4.15 | Array gain as a function of beamforming angle (2 elements)                                                                    | 69 |

| 4.16 | Array gain as a function of beamforming angle (4 elements)                                                                    | 69 |

| 4.17 | Array gain as a function of beamforming angle (8 elements)                                                                    | 70 |

| 4.18 | Array gain as a function of beamforming angle (16 elements)                                                                   | 70 |

| 4.19 | Maximum sidelode as a function of beamforming angle (4 elements) $\dots$                                                      | 71 |

| 4.20 | Minimum peak-to-null ratio as a function of beamforming angle (4 elements)                                                    | 71 |

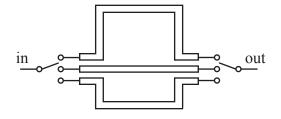

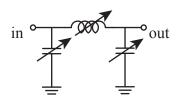

| 4.21 | Through type phase shifters                                                                                                   | 73 |

| 4.22 | Reflection type phase shifters                                                                                                | 73 |

| 4.23 | I/Q interpolating phase shifters                                                                                              | 74 |

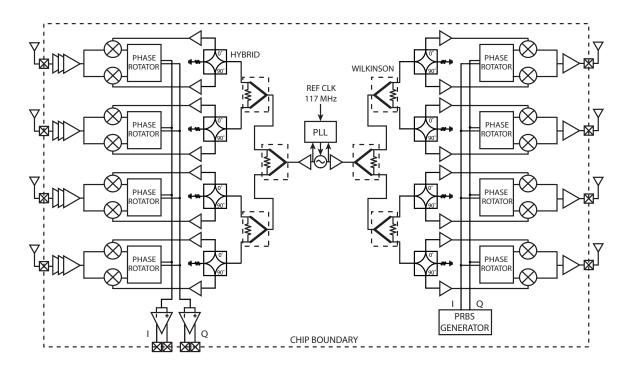

| 4.24 | Block diagram of the 60<br>GHz four-element phased array transceiver                                                          | 76 |

| 4.25 | Schematic of the transmitter element                                                                                          | 76 |

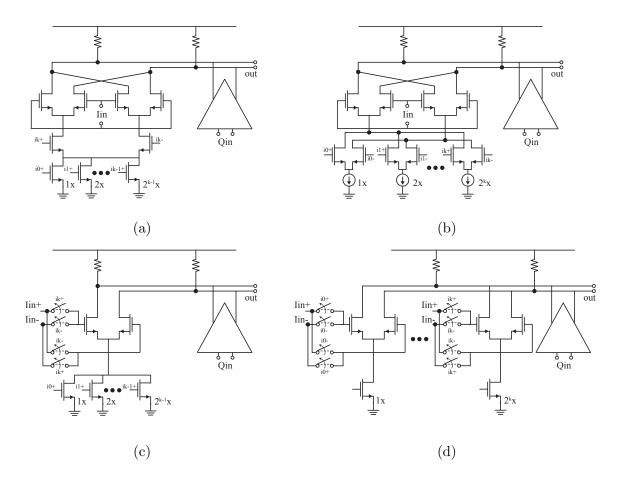

| 4.26 | Conventional BB phase shifter architecture                                                                                    | 78 |

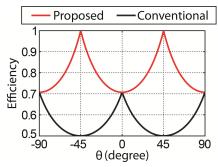

| 4.27 | Proposed BB phase shifter architecture                                                                                        | 78 |

| 4.28 | Efficiency comparison of the conventional and proposed phase shifters                                                         | 78 |

| 4.29 | Predicted PA drain efficiency, power gain and PAE                                                                             | 80 |

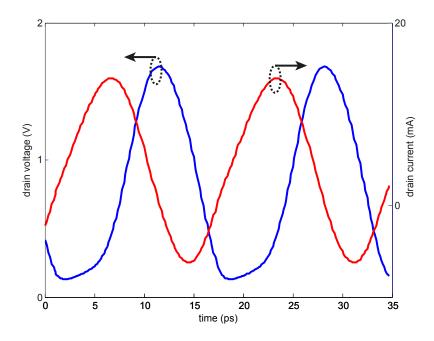

| 4.30 | Simulated V-I waveforms of the PA                                                                                             | 80 |

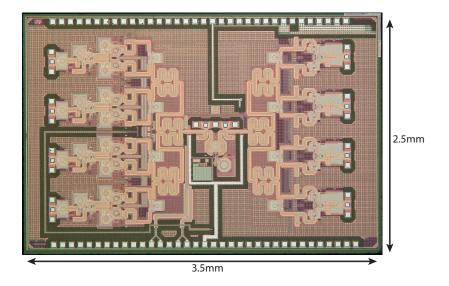

| 4.31 | Chip micrograph of the 60GHz 4-element phased array transceiver                                                               | 82 |

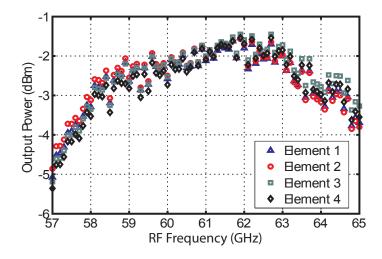

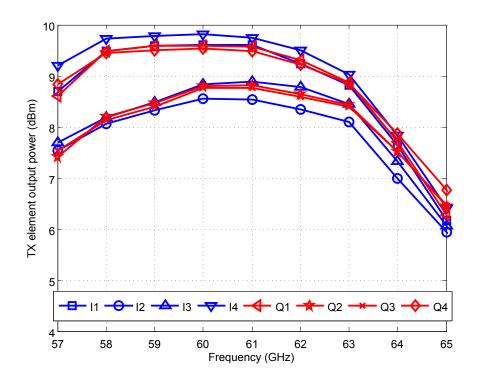

| 4.32 | Measured transmitter output power                                                                                             | 82 |

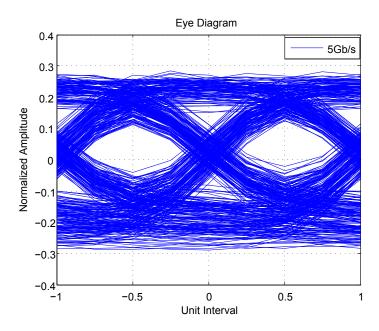

| 4.33 | Measured eye-diagram of the I-channel while transmitting 5<br>Gb/s QPSK data.                                                 | 83 |

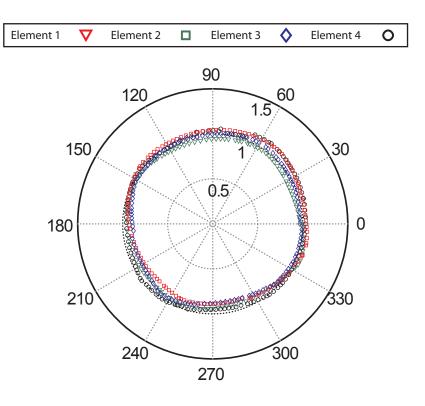

| 4.34 | Measured phase constellations for four TX elements                                                                            | 84 |

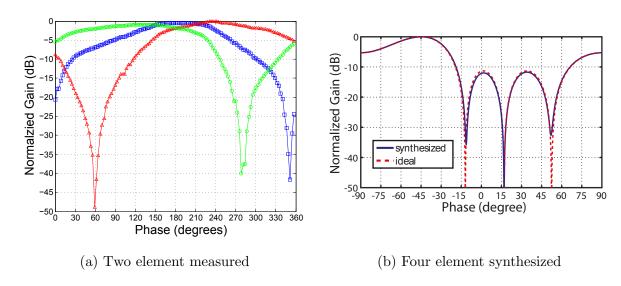

| 4.35 | Transmitter beamforming pattern                                                                                               | 84 |

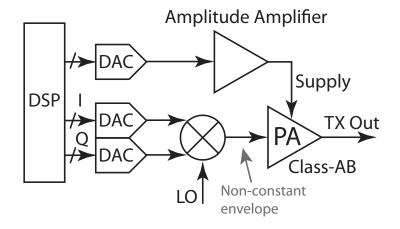

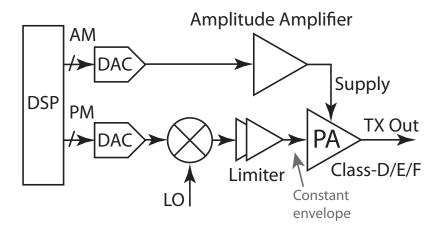

| 5.1  | Envelope tracking through supply path                                                                                         | 87 |

| 5.2  | Envelope elimination and resotoration (Polar)                                                                                 | 87 |

| 5.3  | Outphasing                                                                                                                              | 87  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

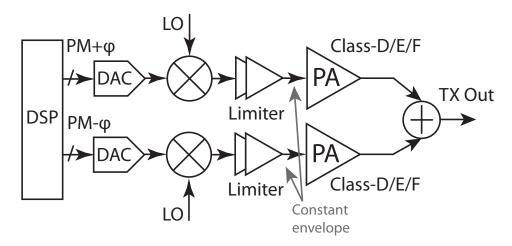

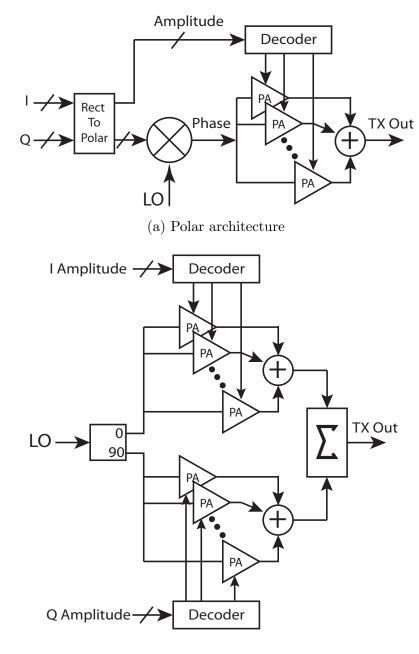

| 5.4  | Direct digital-to-RF conversion transmitters                                                                                            | 90  |

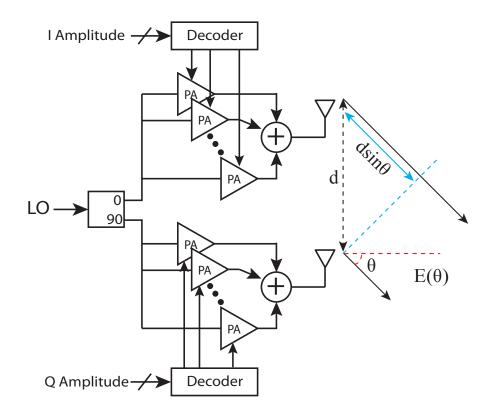

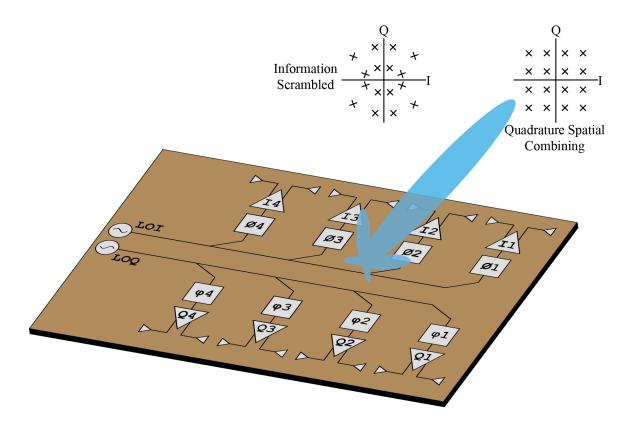

| 5.5  | Cartesian transmitter with quadrature spatial combining                                                                                 | 91  |

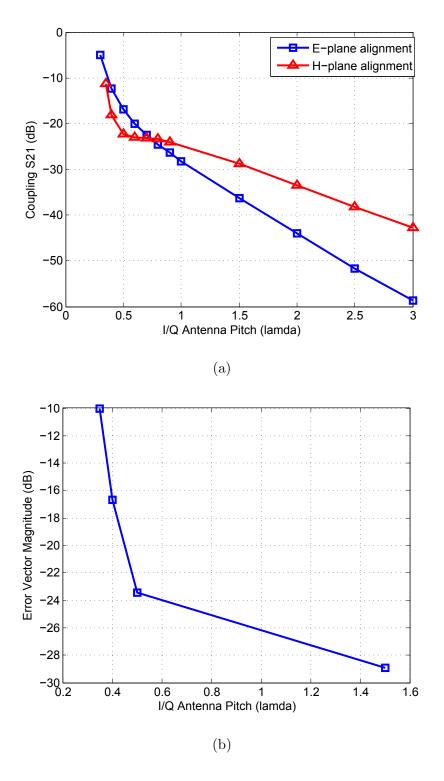

| 5.6  | Antenna mutual coupling (a) coupling factor S21. (b) EVM                                                                                | 92  |

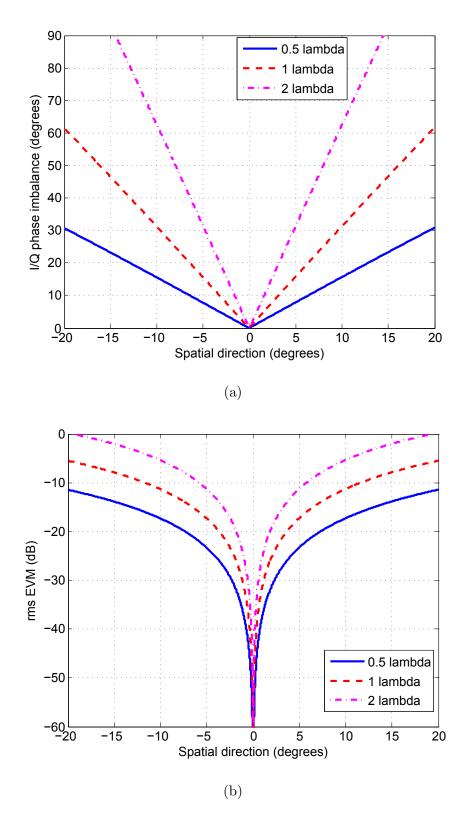

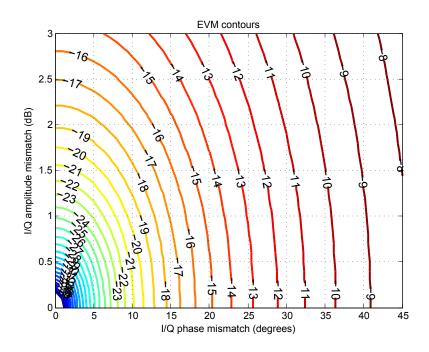

| 5.7  | Quadrature spatial combining output (a) I/Q phase imbalance. (b) EVM                                                                    | 94  |

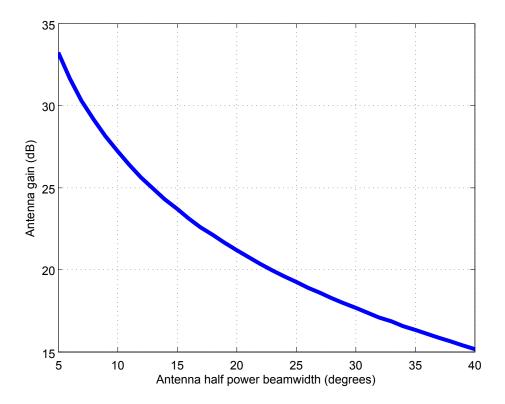

| 5.8  | Antenna half power beamwidth as a function of antenna gain                                                                              | 95  |

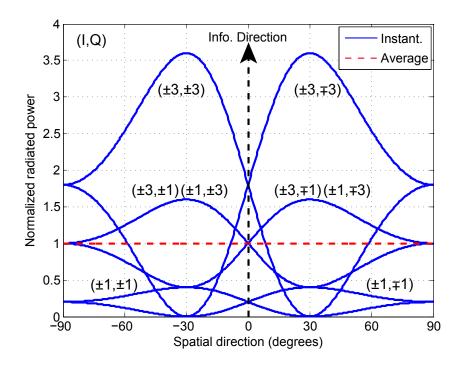

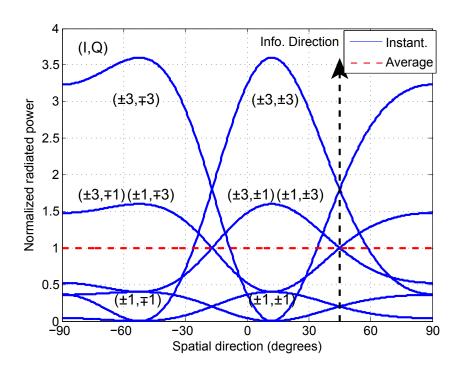

| 5.9  | Instantaneous and time averaged radiation power pattern of a quadrature spatial combined transmitter with two antennas for 16QAM signal | 96  |

| 5.10 | Multi-element beamforming transmitter with quadrature spatial combining. $\!$                                                           | 97  |

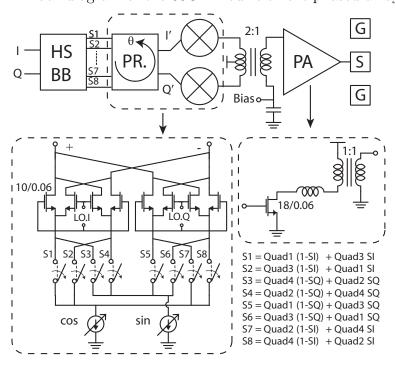

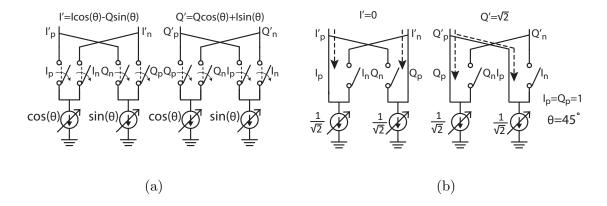

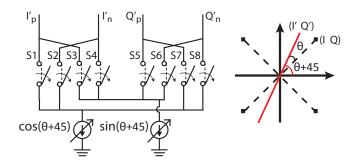

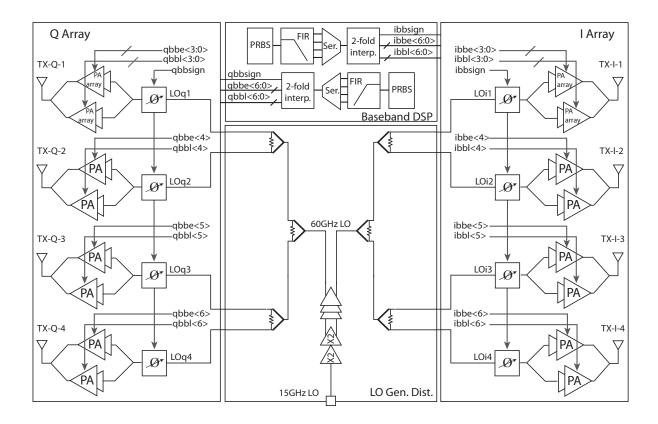

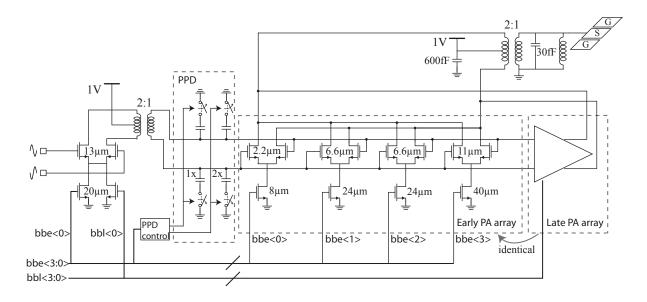

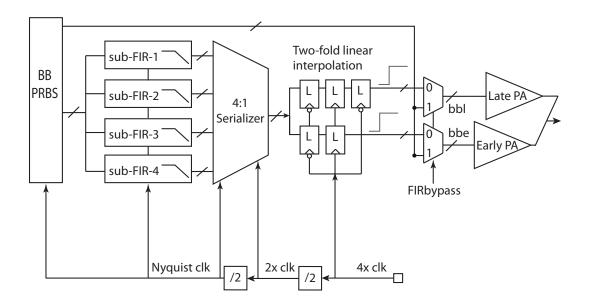

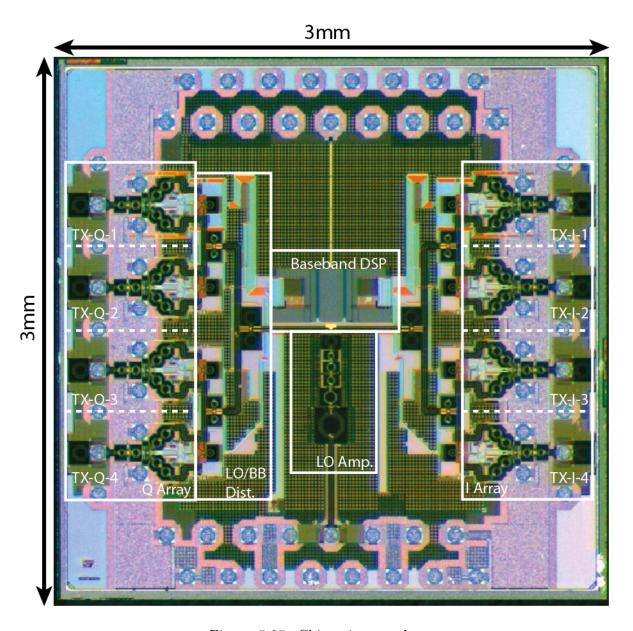

| 5.11 | System block diagram of the 60GHz beamforming transmitter with quadrature spatial combining                                             | 98  |

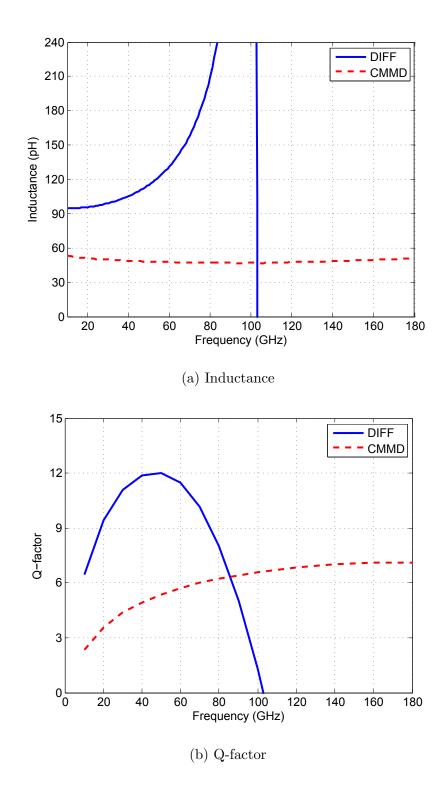

| 5.12 | Inductance and Q-factor of a two turn inductor $(25\mu m \text{ inner diameter and } 2.5\mu m \text{ spacing})$                         | 100 |

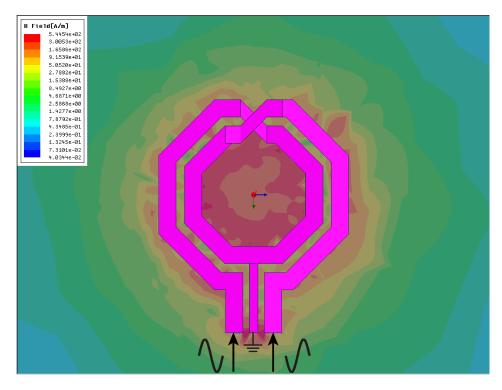

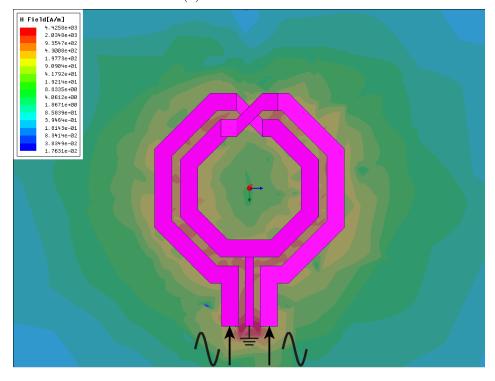

| 5.13 | Magnetic field of a two-turn inductor when exited by differential signals and common-mode signals                                       | 101 |

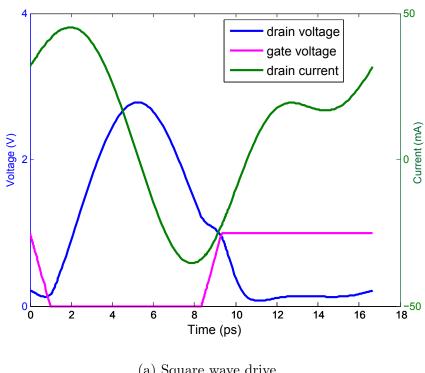

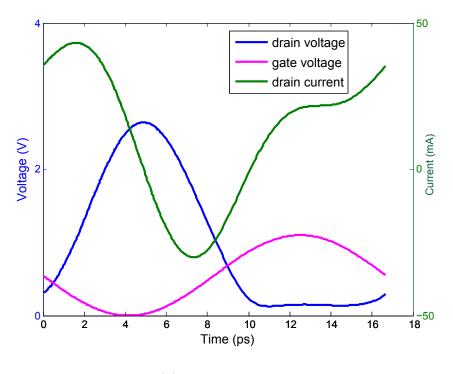

| 5.14 | V-I waveforms of the Class-E/F $_2$ PA using 2:1 transformer                                                                            | 102 |

| 5.15 | Schematic of the PA-DAC in the first transmitter element                                                                                | 103 |

| 5.16 | EVM contour as a function of I/Q amplitude and phase imbalance                                                                          | 104 |

| 5.17 | Schematic of the LO phase shifter                                                                                                       | 104 |

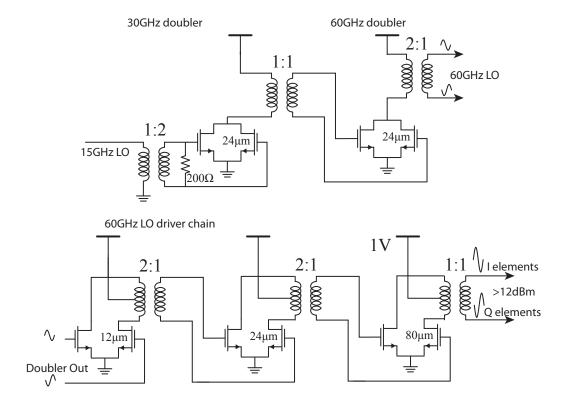

| 5.18 | Schematic of the LO frequency doublers and the driver chain                                                                             | 105 |

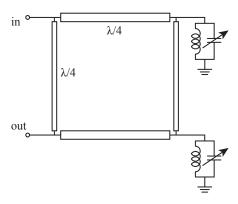

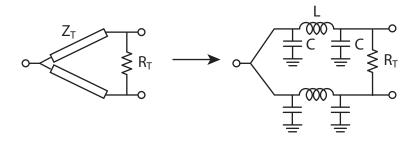

| 5.19 | Lumped Wilkinson power dividers                                                                                                         | 106 |

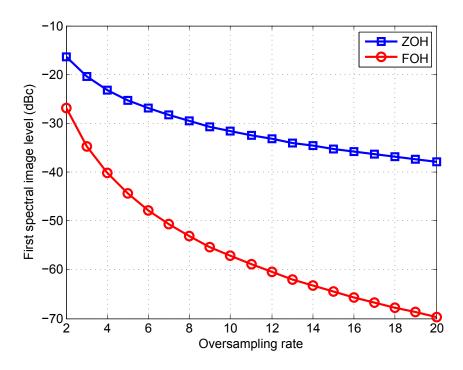

| 5.20 | First spectral image level as a function of the oversampling rate                                                                       | 107 |

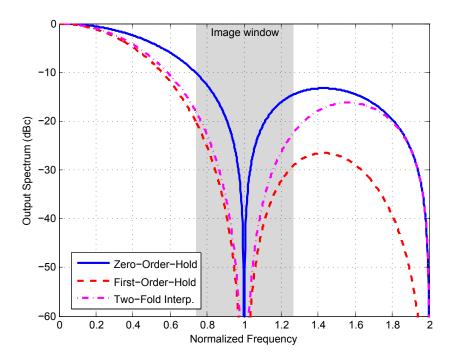

| 5.21 | Output spectrum of different types of digital to analog conversion                                                                      | 107 |

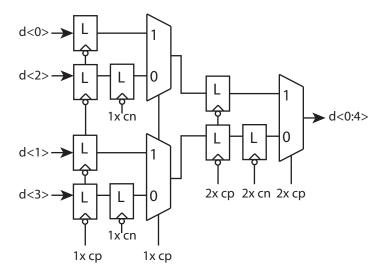

| 5.22 | Mixed-signal baseband signal processing for spectrum filtering                                                                          | 109 |

| 5.23 | Schematic of the 4-to-1 serializer                                                                                                      | 109 |

| 5.24 | Supply bypass network floorplan                                                                                                         | 110 |

| 5.25 | Chip micrograph                                                                                                                         | 111 |

| 5.26 | Measured transmitter output power and drain efficiency                                                                                  | 113 |

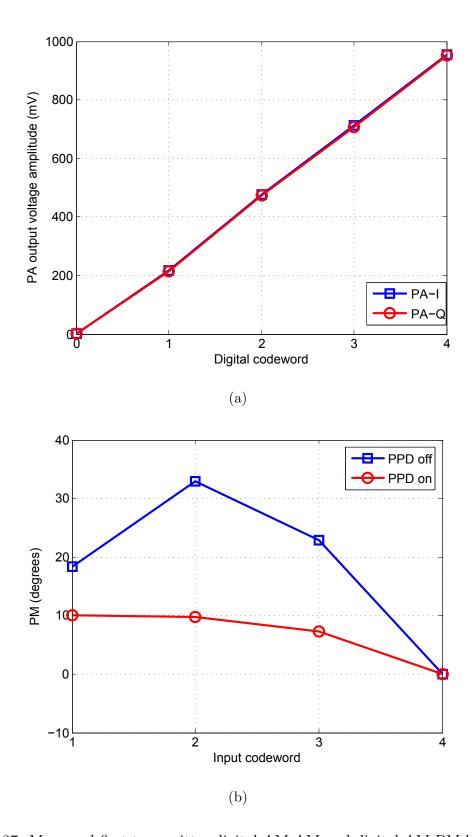

| 5.27 | Measured first transmitter digital AM-AM and digital AM-PM behaviors                                                                    | 114 |

| 5.28 | Measured output power of 8 transmitter elements                                                                                         | 115 |

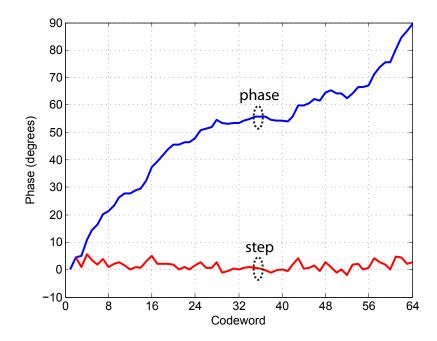

| 5.29 | Measured LO phase shifter codeword to phase transfer curve and the corresponding phase step                                             | 115 |

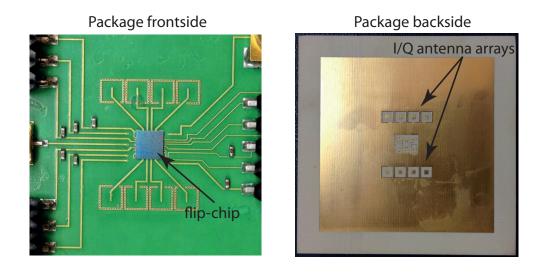

| 5.30 | Flip-chip packaged module with antenna arrays                                                                                           | 116 |

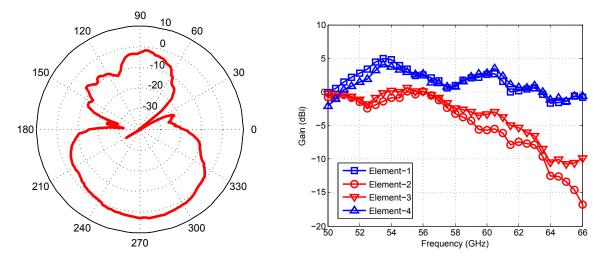

| 5.31 | Measured antenna radiation pattern and frequency response                        | 16 |

|------|----------------------------------------------------------------------------------|----|

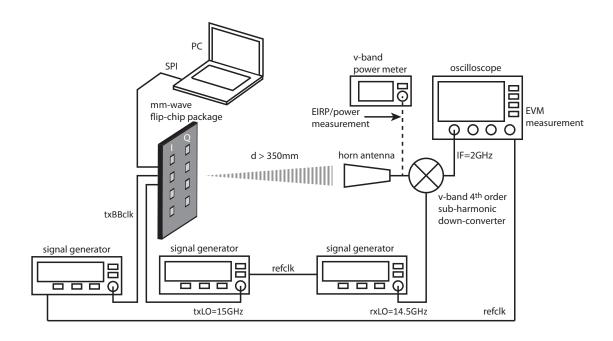

| 5.32 | Measurement setup for wireless transmission using the mm-wave module $1$         | 17 |

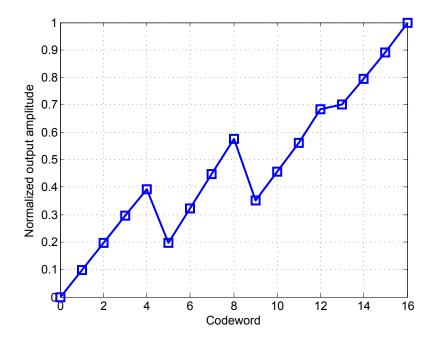

| 5.33 | Measured radiated transmitter amplitude as a function of amplitude codeword. $1$ | 17 |

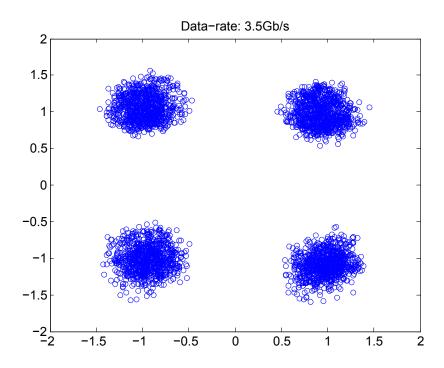

| 5.34 | Received signal constellation of QPSK modulation at 3.5Gb/s                      | 18 |

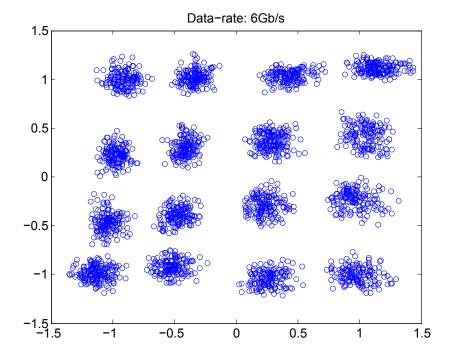

| 5.35 | Received signal constellation of 16QAM modulation at 6Gb/s                       | 18 |

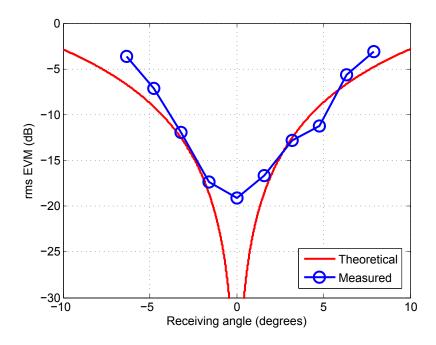

| 5.36 | Transmitter output EVM as a function of spatial angle                            | 19 |

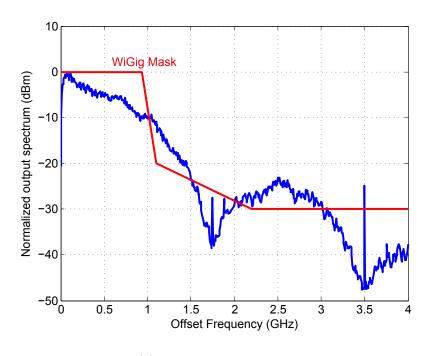

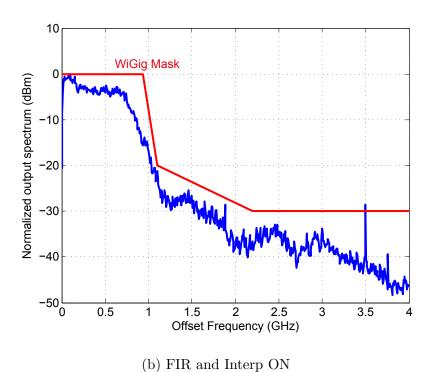

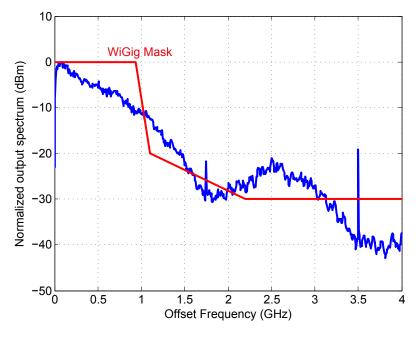

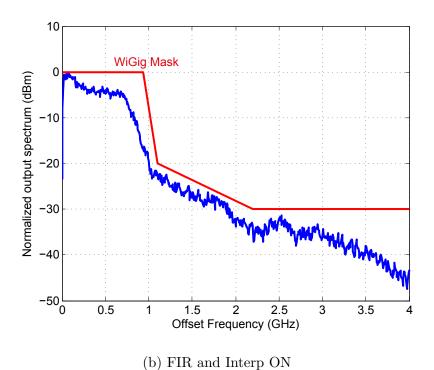

| 5.37 | Measured QPSK transmitter output spectrum                                        | 20 |

| 5.38 | Measured 16QAM transmitter output spectrum                                       | 21 |

# List of Tables

| 2.1 | FSPL for different distances and frequencies                                | 7   |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | The harmonic impedance specifications of several original Class-E/F tunings | 22  |

| 2.3 | Technology dependent parameters                                             | 23  |

| 2.4 | The harmonic impedance specifications of several extended Class-E/F tunings | 24  |

| 4.1 | Link budget analysis for a 10Gb/s 60GHz QPSK link over 2 meters             | 75  |

| 4.2 | Truth table of the quadrant signals                                         | 79  |

| 4.3 | Phase shift region and its corresponding control sign bits                  | 79  |

| 5.1 | Chip power breakdown                                                        | 122 |

| 5.2 | Chip performance summary                                                    | 122 |

| 5.3 | Comparison to efficiency enhancing 60GHz transmitters                       | 123 |

### Acknowledgements

Time flies. Six years passed since I came to the United States to embark on this journey that I will always remember throughout my life. Like most journeys, this is a colorful one full of stories, during which I've encountered excitement and anxieties, obstacles and accomplishments, praises and criticisms. Yet, I could never confidently reach the finish line without generous help and insightful guidance from many important people during these years.

The best part of this journey was meeting my advisor Prof. Ali M. Niknejad and working in his group. From a microwave background, I was initially lost in the sea of transistors. However, Ali was patient to share his exceptional knowledge in both fields and helped me to bridge the gap. Through his encouragements, I gradually gained confidence. Being a knowledgeable and humble person, Ali taught me not only technical skills but also readiness to learn new things and adapt to changes, a mentality shared by many successful people in this rapidly evolving world. I also greatly appreciate him for giving me the freedom to practice in the industry throughout the graduate study, which turns out to be tremendously rewarding.

I am also very grateful to Prof. Elad Alon who has taught me three IC design courses and advised me on a number of research projects. Elad is an excellent instructor and his courses introduced me to a variety of topics and helped me develop insights for analyzing circuits. Although I am not his student, he is always ready to mentor, and I enjoyed discussing with him. I would also like to thank Prof. Robert Meyer and Prof. Paul Wright for serving as my qualification exam committee. I had an opportunity to work with Prof. Meyer during one of my internships, and I was very grateful to him not only for his advice but also for what he had shown to me as a true scientist.

I was never alone during this journey. I was so happy to meet my fellow classmates who came in the same year as me: Lingkai Kong, Wenting Zhou, Paul Liu, Yida Duan, Lu Ye, Hanh-Phuc Le, Chintan Takkar, Maryam Tabesh, Jung-Dong Park, Rikky Muller, Mervin John, Ping-Chen Huang, Namseog Kim, Kyoohyun Noh. We've been through all the challenges together and I wish you all the best. My life at Berkeley Wireless Research Center was enriched by the company of many other graduate students: Yue Lu, Wen Li, Jun-Chau Chien, Siva Thyagarajan, Charles Wu, Shingwon Kang, Kuangmo Jung, John Crossley, Steven Callendar, Jaehwa Kwak, Zhiming Deng, Amin Arbabian, Debo Chowdhury, Bagher Afshar and Ehsan Adabi.

Studying at BWRC has brought me the precious access to the semiconductor industry. Throughout the last two years, I've been largely involved in the R&D at Tensorcom, a WiGig start-up company. I was exposed to various aspect of a fabless start-up, from chip design to customer presentation. The technical experience brought many practical elements into my research projects and helped me to reflect deeper on issues that are typically overlooked in an academic work. The wide exposure at the startup was also extremely valuable to my career objectives. I would like thank co-founders Hock Law and Ismail Lakkis for inviting me to participate. Besides, I was lucky to get to know Sohrab Emami and I would like to thank

him for allowing me to test my 60GHz PA at SiBEAM, where I was truly impressed by the remarkable technological achievement of the start-up founded by former BWRC graduates.

Now that I am close to finishing my PhD study, I cannot resist of thinking about my undergraduate advisor Prof. C.H. Chan, who brought me onto this road. I still clearly remember the first day when I arrived at City University of Hong Kong and was lost in the gigantic academic building when I bumped into him. He showed me around the EE department and encouraged me to take full advantage of the school resources. Three years later, I became his FYP student and he recommended me to take the RF integrated circuit topic. He also showed tremendous support for my graduate school application, and without him I could've not come to my dream school.

My graduate study was also made possible by the Fulbright foundation, and I am so proud to be one of the 27 worldwide recipients of the International Fulbright Science and Technology Fellowship in its inaugural year. My thank goes to Kate Leiva and Tom Koerber at the Institute of International Education and Lance Sung at the Hong Kong US Consulate for their support.

Finally and as always, I want to give a special acknowledgement to my parents and grandparents. Nothing can be even compared to the love and support from you, and no words can ever express my gratitude and love to you.

# Chapter 1

## Introduction

Since the global smartphone revolution, the consumer demand for wireless data capacity has been skyrocketing. The percentage of Internet traffic coming from mobile devices has increased dramatically from less than 1% in 2009 to more than 20% in 2012, and it's predicted that the mobile data traffic volume will grow 15 times within the next five years (Fig. 1.1) [1]. This increasing data demand constantly drives the evolution of the wireless communications, with new standards being developed to provide higher speed and larger capacity. In less than a decade, the data rate of both WiFi and cellular networks have increased from less than 1Mbps to more than 100Mb/s today. This is mainly achieved by using larger radio bandwidth and obtaining higher spectral efficiency. For example, the 802.11g standard utilizes 20MHz bandwidth with 64QAM modulation scheme whereas the draft 802.11ac standard utilizes 160MHz bandwidth with highest modulation scheme of 256QAM, which results in 16 times data rate improvement. However, the available spectrum below 10GHz is very limited and packing more bits per second into the same bandwidth requires larger energy consumption as well as much more stringent radio and modem performance. As a result, current approaches may not be sustainable for meeting the future demands.

In contrast, the mm-wave frequency band has much larger spectrum bandwidth but very minimum commercial usage. In recent years, much effort has been made to utilize the advantages of the mm-wave frequency band. One example is the development of the 60GHz Wireless Personal Area Networks (WPAN). The 7GHz unlicensed bandwidth provides 10 times speed improvement compared to the current 802.11n standard, and therefore enables various new applications such as wireless HD video streaming, instant data synchronization. Another example is the E-band (71-76GHz, 81-86GHz) cellular backhaul. Compared to current wireless backhaul systems which use congested frequency bands below 38GHz, the E-band backhaul not only improves the data rate by at least 4 times, but also enables spectrum reuse due to the narrow beam feature of the long distance mm-wave transmission.

The ubiquitous deployment of mm-wave wireless communications is made possible by the low cost integrated Complementary Metal Oxide Semiconductor (CMOS) solution. Tra-

Figure 1.1: Predicted mobile traffic growth

ditionally all the mm-wave radios are implemented by discrete components or compound semiconductor based Monolithic Microwave Integrated Circuits (MMICs), which are not only expensive but also limited in capabilities. Due to process scaling, CMOS technology which was mainly used for digital computations and certain low frequency analog circuits, is now capable of operating at speeds in excess of 100GHz. According to ITRS roadmap for RF CMOS technology as shown in Fig. 1.2, the maximum transit frequency ( $f_T$ ) will reach 1THz by the end of this decade [2]. Taking full advantages of the increasing transistor speed, researchers are now able to design circuit blocks and complete transceivers in the mm-wave frequency domain using bulk CMOS. In the past decade, a clear trend is seen that engineers have been aggressively pushing the envelope of mm-wave CMOS design, demonstrating sources and detectors beyond 500GHz and fully integrated transceivers close to 300GHz (Fig. 1.3).

In spite of the glory that the circuit frequency world record is being set every year, the mm-wave CMOS radios today have fairly short communication range. The reasons are two fold. First, the path loss increases with the frequency and therefore larger Equivalent Isotropically Radiated Power (EIRP) is needed at higher frequency to cover the same amount of transmission distance. Second, due to low transistor breakdown voltage and parasitic loss, CMOS transmitters have much inferior power delivery capability at higher frequencies, limiting the achievable output power and EIRP. In addition to short link distance, current CMOS mm-wave radios also have very poor energy efficiency, particularly on the transmitter side. The efficiency of current mm-wave transmitters is only about 20% to 30% of WiFi and celluar transmitters in the sub-10GHz frequency range. Among many factors that cause this phenomenon, low transistor breakdown voltage, low power gain and large passive loss are the major contributors.

What's worse? To obtain better spectrum efficiency and immunity to multipath effect,

Figure 1.2: ITRS roadmap for RF CMOS

Figure 1.3: Operating frequency of CMOS circuits and systems

modern communication modulation schemes use high order QAM and Orthogonal Frequency Division Multiplexing (OFDM). As a result, the modulated radio signal usually has fairly high Peak-to-Average-Power-Ratio (PAPR), which means the transmitter has to back-off from its peak output power level. For a linear transmitter, which has been the default choice for almost all mm-wave radios, the power efficiency decreases linearly with output power level, therefore the average efficiency diminishes very quickly when the transmitter backs off from its peak momentum. As an example, a typical linear mm-wave transmitter with 10% peak efficiency will only have 2.5% average efficiency at 6 dB back-off when delivering modulated signals. This means for every 100W of power consumed, 97.5W are being wasted.

The same back-off characteristic exist for WiFi and cellular counterparts, however since the peak efficiency is much higher, the average efficiency is also proportionally better. In addition, various average efficiency enhancing techniques have been introduced at both the architecture level and the circuit level for WiFi and cellular transmitters, demonstrating remarkable improvement. In contrast, there is much less similar endeavor at the mm-wave domain, mainly due to the difficulty of adopting existing architectures and techniques.

This dissertation investigates the challenges of designing efficient mm-wave transmitters for both long range and short range applications, and proposes concepts and techniques that can potentially break the barriers imposed by the low cost digital CMOS process. The scope of investigation and proposal extends from the architecture level down to the transistor level. Indeed it's shown that the holistic optimization for a particular application at different design hierarchies is the key to achieving overall energy efficiency. The important contribution of this dissertation is summarized below.

- 1. The fundamentals of the CMOS process are analyzed from mm-wave radio designers' perspective. Bottlenecks have been identified that prevent the implementation of high performance mm-wave transmitters.

- 2. The traditional Class-E/F switching amplifier family has been extended with the potential benefits explained.

- 3. mm-Wave on-chip power combining techniques are analyzed. A compact and low-loss solution is proposed to enhance the output power of single-element transmitters. An optimization procedure is outlined and the theoretical limits are predicted.

- 4. The general design procedure for mm-wave linear Power Amplifiers (PAs) is documented.

- 5. The pros and cons of various beamforming transmitter architectures are analyzed. The optimal architecture choice is predicted based on array size, operating frequency and process.

- 6. An analog baseband phase shifting beamforming transceiver is implemented for short range high data rate links.

- 7. The direct digital-to-RF conversion architecture is analyzed and compared to traditional efficiency-enhancing architectures. Optimal mm-Wave CMOS implementation is proposed.

- 8. The concept of Quadrature Spatial Combing is proposed to solve the dilemma between minimizing insertion loss and minimizing undesired load-pull.

The remainder of the dissertation is organized as follows. Chapter 2 discusses the basic features of wireless transmitters, including various architectures and link budget analysis. It also introduces the most important block inside the transmitter: the power amplifier. Different classes of power amplifier topologies are presented, with insights on the design difficulty at mm-wave frequencies. Chapter 3 presents the design procedure for linear transmitters,

with focus on techniques that improve the PA output power. Various on-chip power combiners are discussed, and a compact solution is used to realize a 19dBm 60GHz PA. Chapter 4 focuses on using beamforming techniques to improve the transmitter EIRP. The tradeoff among several different beamforming architectures is presented. An optimal analog baseband phase shifting topology is chosen for an ultra-low power 4-element 60GHz phased-array transmitter covering 2 meters of communication range. In Chapter 5, the main focus shifts to the average efficiency enhancement. It first discusses the existing techniques including envelope tracking, Envelope Elimination and Restoration (EER), and outphasing, as well as the reasons why current architectures are not suitable for mm-wave applications. It then introduces the concept of direct digital to RF conversion as an effective approach for enhancing back-off efficiency of mm-wave transmitters. Optimal circuit level implementation is also presented. In particular, the concept of quadrature spatial combining is introduced as an effective signal combiner for Cartesian transmitters. A WiGig prototype is built based on the proposed transmitter architecture and measurement results are presented. Finally, Chapter 6 summarizes the important findings of the research.

# Chapter 2

# Wireless Transmitter Basics

## 2.1 Link Budget Analysis

Figure 2.1: Wireless link budget analysis

The wireless radio design usually starts from the link budget analysis, which determines the specifications for individual blocks based on the application requirements such as distance and data rate. Fig. 2.1 shows a wireless link with a transmit to receive antenna distance of R. The transmitter delivers an output power of  $P_{TX}$ , and the antenna gains are  $G_{TX}$  and  $G_{RX}$  for the transmit and receive side respectively. According to the Friis transmission equation, the received signal power at the receiver input is,

$$P_{RX} = P_{TX} \times G_{TX} \times G_{RX} \times (\frac{\lambda}{4\pi R})^2$$

(2.1)

|                 |      | FSPL (dl | 3)     |

|-----------------|------|----------|--------|

| Frequency (GHz) | R=2m | R=10m    | R=100m |

| 0.9             | 38   | 52       | 72     |

| 5               | 52   | 66       | 86     |

| 60              | 74   | 88       | 108    |

Table 2.1: FSPL for different distances and frequencies

or in dB units,

$$P_{RX} = P_{TX} + G_{TX} + G_{RX} - 20\log(\frac{4\pi R}{\lambda})$$

(2.2)

$$= EIRP + G_{RX} - FSPL \tag{2.3}$$

$$EIRP = P_{TX} + G_{TX} (2.4)$$

$$FSPL = 20\log(\frac{4\pi R}{\lambda})\tag{2.5}$$

where EIRP is the transmitter output power plus the transmitter antenna gain and the last term is the Free Space Path Loss (FSPL). FSPL describes the loss in signal power level due to line-of-sight propagation through free space. It assumes isotropic antennas on both the transmit and receive side. Table. 2.1 lists the FSPL for various link distances at three different carrier frequencies. One can already observe the challenge for mm-wave transmitter design here. The FSPL increase with the carrier frequency, e.g the FSPL at 900MHz for 10 meters is around 52dB, but it increases by 36dB when the carrier frequency goes up to 60GHz. To maintain the same transmission distance, the transmitter EIRP must be increased correspondingly.

The link specs are ultimately set by the receiver Signal to Noise Ratio (SNR) requirement. The SNR at the receiver output can be expressed as follows,

$$SNR_{RXo} = P_{TX} + G_{TX} + G_{RX} - FSPL - 10\log(kT) - 10\log(BW_{RX}) - NF_{RX}$$

(2.6)

where  $BW_{RX}$  is the receiver bandwidth and  $NF_{RX}$  is the receiver noise figure. From Eq. 2.6 one can see the second challenge for mm-wave transmitters. For the same received SNR, larger data rate links require larger receiver bandwidth and therefore require larger EIRP. Current mm-wave standards demand a radio bandwidth significantly larger than any existing WiFi or cellular standard. For example, the WiGig standard utilizes a RF bandwidth of 1.76GHz, which is 44 times bigger than the 40MHz bandwidth utilized by the 802.11n standard. As a result, mm-wave transmitters need to deliver larger EIRP for the same SNR level.

The minimum SNR requirement depends on the modulation scheme and Bit Error Rate (BER). The BER can be expressed as a function of the energy per bit to noise power spectral

Figure 2.2: BER as a function of SNR

density ratio  $(E_b/N_0)$ ,

$$BER_{BPSK} = Q(\sqrt{\frac{2E_b}{N_0}}) \tag{2.7}$$

$$BER_{QPSK} = Q(\sqrt{\frac{2E_b}{N_0}}) \tag{2.8}$$

$$BER_{M-aray-QAM} = \frac{4}{k} (1 - \frac{1}{\sqrt{M}}) Q(\sqrt{\frac{3k}{M-1}} \frac{E_b}{N_0})$$

(2.9)

where M is the number of constellation points and k is the number of bits per symbol.  $E_b/N_0$  can be further expressed in terms of SNR,

$$\frac{E_b}{N_0} = \frac{1}{k} \frac{E_s}{N_0} = \frac{1}{k} \frac{BW_{RX}}{f_s} SNR \tag{2.10}$$

The receiver RF bandwidth is usually designed to be roughly equal to the Nyquist symbol frequency and therefore Eq. 2.10 can be simplified to,

$$\frac{E_b}{N_0} = \frac{1}{k}SNR\tag{2.11}$$

Using this relation, the BERs in Eqn. 2.7-2.9 can be expressed in terms of SNR directly,

$$BER_{BPSK} = Q(\sqrt{2SNR}) \tag{2.12}$$

$$BER_{QPSK} = Q(\sqrt{SNR}) \tag{2.13}$$

$$BER_{M-aray-QAM} = \frac{4}{k} (1 - \frac{1}{\sqrt{M}}) Q(\sqrt{\frac{3}{M-1}} SNR)$$

(2.14)

(b) 60GHz link with 5GHz RF bandwidth

Figure 2.3: Required EIRP as a function of communication distance

Fig. 2.2 plots the BER as a function of SNR for BPSK, QPSK, 16QAM and 64QAM modulation schemes. In modern wireless systems, expected BER at the radio front-end output is around  $10^{-3}$  to  $10^{-4}$  <sup>1</sup>, and therefore the minimum received SNR needs to be greater than 7dB for BPSK, 10dB for QPSK, 17dB for 16QAM and 23dB for 64QAM. As a result, with the same receiver, higher order modulation schemes require higher transmitter EIRP. Fig. 2.3 plots the required EIRP as a function of communication distance to achieve a BER of  $10^{-3}$ , and compares a 2.4GHz link with 40MHz RF bandwidth and a 60GHz link with 5GHz bandwidth. In both cases, the receiver has an isotropic antenna ( $G_{RX} = 0$ dBi) and 5dB noise figure. Clearly, the 60GHz link requires much larger EIRP for covering the same distance, illustrating the aforementioned challenges. Note that the EIRPs shown in Fig. 2.3 represent the average values, which means transmitters need to handle peak EIRPs several dBs higher, depending on the PAPR of the modulation scheme.

### 2.2 Wireless Transmitter Architectures

Most modern wireless transmitters can be classified into two different categories <sup>2</sup>: the superheterodyne<sup>3</sup> architecture and the direction conversion architecture. Common in both architectures, there are four major sub-systems in the RF front-end: analog baseband, frequency generation, modulation and frequency conversion, and power amplification. The analog baseband first converts the coded baseband I/Q digital bits into continuous time analog signals through Digital-to-Analog-Converters (DACs), and subsequently filters the analog signals to reject unwanted high frequency spectral contents. The filtered I/Q signals are used to modulate a high frequency carrier signal known as the Local Oscillator (LO) signal. The modulated signal is amplified to achieve required power level by the PA. The high frequency LO signal is usually generated by a Phase-Lock-Loop (PLL) taking highly accurate frequency reference from a quartz crystal. In a superheterodyne transmitter (Fig. 2.4), the modulation takes place at an Intermediate Frequency (IF) which is lower than the final RF carrier frequency. Then the modulated signal is up-converted by a mixer. There are two major advantages: first, since the frequency generation block only needs to synthesize a lower frequency, it can achieve lower power consumption and better phase noise performance; second, modulation at IF is more power efficient and linear, and it also reduces the operating frequency of the calibration circuits<sup>4</sup>. However, superheterodyne transmitters need a band-pass filter after the up-conversion mixer since the mixer produces undesired spectral contents 2×IF frequency away from the RF carrier, which is known as the image. Image leaking through the transmitter not only reduces the desired signal power, but also potentially interferes with other communication links operating at the image frequency band.

<sup>&</sup>lt;sup>1</sup>The errors are being corrected by equalizers and error decoders in the digital MODEM

<sup>&</sup>lt;sup>2</sup>Except for non-coherence detection based modulation schemes such On-Off Keying (OOK) or Frequency Modulation (FM). These modulation schemes are less spectral efficient and the corresponding transmitter architecture is much simpler. In fact, they existed long before the CMOS radios.

<sup>&</sup>lt;sup>3</sup>Sometimes simply referred to as hererodyne

<sup>&</sup>lt;sup>4</sup>This is especially true for mm-wave transmitters where high frequency blocks need proper impedance matching and careful layout.

Figure 2.4: A sliding-IF superheterodyne transmitter

Figure 2.5: A direct conversion transmitter

To eliminate the image problem, direction conversion architecture can be used, in which the modulation happens at the final RF carrier frequency. This means the image is actual the signal itself, and therefore no filtering is required. However, one practical problem of the direction conversion transmitter is the VCO pulling. Since the PA output contains a wideband signal around the carrier and the amplitude level is usually very large (e.g. 20dBm output power with  $50\Omega$  load corresponds to 3.3V of swing), the VCO oscillation frequency may be dragged around by the parasitic feedback from the PA. A good layout that isolates the PA from the VCO reduces the pulling effect, however, it's almost impossible to completely block the feedback paths from the PA since they exist everywhere: supply coupling, substrate coupling and even reflection from the package! Pulling at close-in frequencies can be corrected by the PLL, but unfortunately the PLL usually has a much lower bandwidth compared to the data bandwidth, and therefore is not effective in reducing pulling at higher frequencies. A common solution is to synthesize a clock that is multiples of the desired LO frequency, as shown in Fig. 2.5. It's generally much more difficult to pull a VCO running at the multiples of the pulling signal frequency.

## 2.3 Power Amplifiers (The ABCDEFs)

The most power consuming block in a wireless transmitter is the power amplifier. In a WLAN transmitter, the PA usually contributes over 60% of the total power consumption [3]. As a result, the power efficiency of the PA is directly related to the battery life of mobile devices. To quantify the PA efficiency, several efficiency measures are used. The most widely used measures are the drain efficiency ( $\eta_D$ )<sup>5</sup> and the Power Added Efficiency (PAE). The drain efficiency is defined as the ratio between the useful output power  $P_{out}$  and the DC power supplied to the drain of the PA device  $P_{DC}$ ,

$$\eta_D = \frac{P_{out}}{P_{DC}} \tag{2.15}$$

The drain efficiency tells how much power is being dissipated during the DC to AC power conversion. The losses include power dissipation in the transistor as well as in the passive matching network. On the other hand, PAE takes into account of the additional power used to drive the PA device and is defined as the ratio between the added power  $P_{out} - P_{in}$  and the DC power  $P_{DC}$ ,

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2.16}$$

The PAE is related to  $\eta_D$  by the power gain of the PA  $G_P$ ,

$$PAE = \eta_D (1 - \frac{1}{G_P}) \tag{2.17}$$

The significance of the PAE measure can be understood when analyzing a cascaded chain of similar amplifiers. Assume each amplifier has a drain efficiency of  $\eta_D$  and a power gain of

<sup>&</sup>lt;sup>5</sup>It's also referred to as collector efficiency in bipolar PAs

$G_P$ , the output power and the DC power of the  $n^{th}$  stage are,

$$P_{out}(n) = \frac{P_{out}}{G_p^{N-n}} \tag{2.18}$$

$$P_{DC}(n) = \frac{1}{\eta_D} \frac{P_{out}}{G_p^{N-n}}$$

(2.19)

Summing the DC power of each stage, the total DC power is,

$$P_{DC} = \sum_{n=1}^{N} P_{DC}(n) = \frac{P_{out}}{\eta_D} \frac{1 - \frac{1}{G_P^N}}{1 - \frac{1}{G_P}}$$

(2.20)

The cascaded PAE is,

$$PAE_{cascaded} = \frac{P_{out}(1 - \frac{1}{G_P^N})}{\frac{P_{out}}{\eta_D} \frac{1 - \frac{1}{G_P^N}}{1 - \frac{1}{G_P}}} = \eta_D(1 - \frac{1}{G_P}) = PAE$$

(2.21)

Therefore, the cascaded PAE is identical to the single-stage PAE. When N approaches a sufficiently large number, the input power becomes negligible and the PAE represents the total power efficiency of the amplifier chain.

Depending on the input-output relation, power amplifiers are usually categorized as linear amplifiers and non-linear amplifiers. Within each category, multiple classes are defined according to the voltage and current waveforms. The following subsections will describe these different classes.

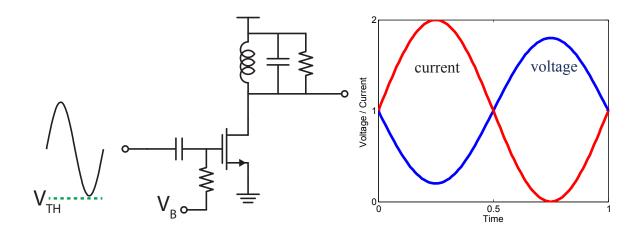

## 2.3.1 Linear Classes (Class-A/B/AB)

Linear amplifiers produce an output signal that is an exactly scaled version of the input signal. In other words, the gain of a linear amplifier is constant, independent of the input signal level. All linear amplifiers are transconductance amplifiers, meaning the device operates as a current source with a transconductance gain of  $g_m$ . The simplest class that produces a linear behavior is Class-A. In Class-A amplifiers, the transistor is biased at a sufficiently large overdrive voltage so that it's conducting current all the time. The voltage and current waveforms at the drain node are shown in Fig. 2.6. The largest voltage swing obtainable is  $V_{dd} - V_{ov}$  and the largest current swing obtainable is the DC bias current  $I_{dbias}$ , which is usually set to half of the maximum current  $I_{max}$  that the transistor can sink in order to maximize the linear current swing. As a result, the largest power obtainable is,

$$P_{out}^{A} = \frac{1}{2} V_{sw} I_{sw} = \frac{1}{4} (V_{dd} - V_{ov}) I_{max}$$

(2.22)

Note that in order to achieve this maximum obtainable output power, an appropriate load impedance is needed to simultaneously maximize the voltage and current swings. This

optimal load impedance can be expressed as a ratio of the voltage swing and the current swing,

$$R_{opt}^{A} = 2\frac{V_{dd} - V_{ov}}{I_{max}} (2.23)$$

When the load impedance is smaller than  $R_{opt}^A$ , the amplifier becomes current limited, meaning that there isn't enough current swing to generate the maximum voltage swing. Likewise, if the load impedance is larger than  $R_{opt}^A$ , the amplifier becomes voltage limited, meaning that only a fraction of the current swing is sufficient to saturate the voltage swing. In both cases, the output power decreases from  $P_{out}^A$ . The peak drain efficiency of Class-A amplifiers is obtained when  $R_{opt}^A$  is presented,

$$\eta_D^A = \frac{P_{out}^A}{P_{DC}} = \frac{\frac{(V_{dd} - V_{ov})I_{max}}{4}}{\frac{V_{dd}I_{max}}{2}} = \frac{V_{dd} - V_{ov}}{2V_{dd}} \approx 50\%$$

(2.24)

Class-A amplifiers have all the attractiveness except for the efficiency. 50% of the DC power is dissipated on the transistor when the product of drain voltage and current is non-zero. In other words, the transistor dissipates power whenever there's overlap between non-zero voltage and current waveforms. Therefore, it's obvious that in order to improve the efficiency, the overlapping period needs to be reduced.

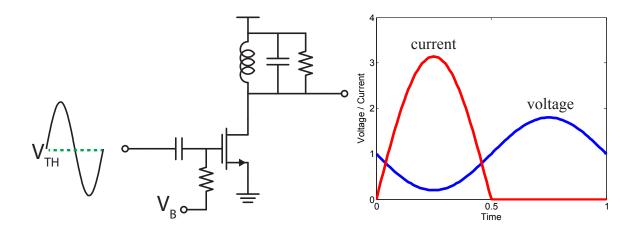

A simple way to achieve this goal is to bias the transistor at the threshould voltage such that the transistor is conducting current during half of the cycle. Such amplifiers are known as Class-B amplifiers, and the drain node voltage and current waveforms are shown in Fig. 2.7. Since the transistor is only conducting current 50% of the time, the amount of V-I overlap is greatly reduced. The current going into the transistor drain becomes a half-wave rectified sine, with a fundamental component of  $\frac{I_{max}}{2}$  and a DC value of  $\frac{I_{max}}{\pi}$ . The output power, optimal load impedance and the drain efficiency of Class-B amplifiers can be found in a similar way,

$$P_{out}^{B} = \frac{1}{2} V_{sw} I_{sw} = \frac{1}{4} (V_{dd} - V_{ov}) I_{max}$$

(2.25)

$$R_{opt}^{B} = 2\frac{V_{dd} - V_{ov}}{I_{max}} \tag{2.26}$$

$$\eta_D^B = \frac{P_{out}^B}{P_{DC}} = \frac{\frac{(V_{dd} - V_{ov})I_{max}}{4}}{\frac{\pi}{V_{dd}I_{max}}} = \frac{\pi(V_{dd} - V_{ov})}{4V_{dd}} \approx 79\%$$

(2.27)

Compared to Class-A amplifiers, Class-B amplifier has much better peak drain efficiency, but maintains the same peak output power. The disadvantage is that the amplifier becomes slightly nonlinear, due to the varying effective bias condition at the input. However, the amplifier is fundamentally considered as a linear class due to the transconductance behavior of the device.

To improve the linearity of Class-B amplifiers, the gate bias of the transistor can be set slightly higher than the threshold voltage so that the transistor is conducting current more than half of the cycle, but still much less than the entire cycle. This sub-category is called Class-AB amplifiers. As a result, the efficiency will lie between Class-A and Class-B

Figure 2.6: Schematics and V-I waveforms of Class-A amplifiers

Figure 2.7: Schematics and V-I waveforms of Class-B amplifiers

amplifiers. To find the power and efficiency of Class-AB amplifiers, the current swing and DC current are first expressed as a function of the conduction angle  $\alpha$ , defined as the total number of radians in one cycle during which the transistor is conducting current,

$$I_{sw} = \frac{1}{2\pi} \left[ \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \right] I_{max}$$

(2.28)

$$I_{DC} = \frac{1}{2\pi} \left[ \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)} \right]$$

(2.29)

Next, the output power, optimal load impedance and the drain efficiency of Class-AB amplifiers can be found,

$$P_{out}^{AB} = \frac{1}{4\pi} \left[ \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \right] (V_{dd} - V_{ov}) I_{max}$$

(2.30)

$$R_{opt}^{AB} = 2\pi \left[\frac{1 - \cos(\alpha/2)}{\alpha - \sin\alpha}\right] \frac{V_{dd} - V_{ov}}{I_{max}}$$

(2.31)

$$\eta_D^{AB} = \frac{P_{out}^{AB}}{P_{DC}} = \frac{1}{2} \frac{V_{dd} - V_{ov}}{V_{dd}} \frac{\alpha - \sin \alpha}{2 \sin(\alpha/2) - \alpha \cos(\alpha/2)}$$

(2.32)

$$\alpha \subset [\pi, 2\pi] \tag{2.33}$$

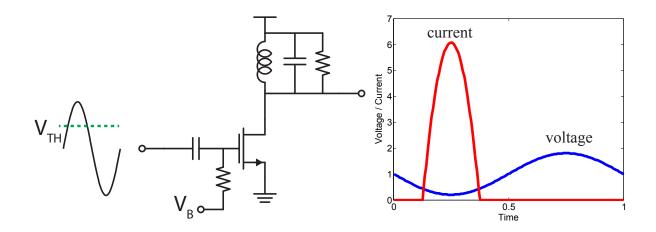

## 2.3.2 Non-Linear Classes (Class-C/D/E/F)

Unlike linear amplifiers, non-linear amplifiers lack of amplitude linearity. They usually produce significant amplitude-to-amplitude (AM-AM) and amplitude-to-phase (AM-PM) distortions. As a result, they cannot be directly used for convey amplitude modulated signals. However, most non-linear amplifiers are still linear in phase, and have no phase-to-phase (PM-PM) distortions. Therefore, they are often used for amplifying phase modulated signals such as GMSK signals. The biggest advantage of most non-linear amplifiers is the high drain efficiency. A linear transconductance amplifier can be turned into a non-linear amplifier by biasing the transistor below threshold voltage. Such amplifiers are known as Class-C amplifiers (Fig. 2.8). Class-C amplifiers conduct current less than half of the cycle, and have smaller window of V-I overlap. Therefore, the efficiency of Class-C amplifiers is even higher than that of Class-B amplifiers. The expression for output power, optimal load impedance and efficiency of Class-C amplifiers is the same as Class-AB amplifiers, but the conduction angle is smaller than  $\pi$ .

$$P_{out}^{C} = \frac{1}{4\pi} \left[ \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \right] (V_{dd} - V_{ov}) I_{max}$$

(2.34)

$$R_{opt}^{C} = 2\pi \left[\frac{1 - \cos(\alpha/2)}{\alpha - \sin\alpha}\right] \frac{V_{dd} - V_{ov}}{I_{max}}$$

(2.35)

$$\eta_D^C = \frac{P_{out}^{AB}}{P_{DC}} = \frac{1}{2} \frac{V_{dd} - V_{ov}}{V_{dd}} \frac{\alpha - \sin \alpha}{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}$$

(2.36)

$$\alpha \subset [0, \pi] \tag{2.37}$$

In theory, Class-C amplifiers can have drain efficiency as high as 100%. However, this is achieved at zero conduction angel, which means the output power also drops to zero according to Eq. 2.34. Unlike Class-AB amplifiers, Class-C amplifier has a clear tradeoff between output power and drain efficiency.

Due to the low output power level, Class-C amplifiers are seldom used as a stand-alone amplifier unit<sup>6</sup>. More widely used non-linear amplifiers are switching amplifiers. In switching amplifiers, transistors behave like switches, and it's either in triode region or in cut-off region. This is in contrast with transconductance amplifiers in which transistors remain in saturation region.

A switching amplifier can be constructed with an inverter which produces a square voltage waveform. In order to extract the fundamental component, a series LC band-pass filter can be added at the output. Such amplifiers are known as Class-D amplifiers (Fig. 2.9). Since only fundamental frequency current can flow through the filter, each of the two transistors contribute half cycle of the sine current waveform. Since there's no V-I overlap, the theoretical peak drain efficiency is 100%. The maximum voltage and current swings are,

$$V_{sw} = \frac{2}{\pi} V_{dd} \tag{2.38}$$

$$I_{sw} = I_{max} (2.39)$$

Therefore the output power, optimal load impedance and the drain efficiency can be found,

$$P_{out}^D = \frac{1}{\pi} V_{dd} I_{max} \tag{2.40}$$

$$R_{opt}^{D} = \frac{\pi}{I_{sw}} = \frac{2}{\pi} \frac{V_{dd}}{I_{max}}$$

(2.41)

$$\eta_D^D = \frac{V_{sw} I_{sw}}{2V_{DC} I_{DC}} \approx \frac{\frac{1}{\pi} V_{dd} I_{max}}{V_{dd} \frac{1}{\pi} I_{max}} = 100\%$$

(2.42)

Note that the peak drain efficiency can only be achieved at very low frequency, where the transistor capacitance is negligible. Unfortunately, the power spent charging the transistor drain node parasitic capacitance increases linearly with frequency. Besides this charging power loss, the parasitic capacitor also smooths the edges of the square waveform, and thereby introduces finite V-I overlap. As a consequence, Class-D amplifiers are seldom used for high frequency designs due to dramatically reduced efficiency.

Class-E amplifiers can absorb the transistor parasitic capacitance into an impedance tuning network while ensure non-overlapping V-I waveforms (Fig. 2.10)[4, 5]. When the switch is off, the current flowing into the drain is zero while the drain voltage is non-zero. The voltage waveform reaches zero right before the switch is turned on, after which the drain voltage remains zero when the transistor sinks current. Such transition behavior is called Zero Voltage Switching (ZVS). ZVS not only ensures non-overlapping V-I waveforms, but also avoids charge loss when the switch turns on. In fact, Class-E amplifiers satisfy not only ZVS but also Zero derivative Voltage Switching (ZdVS), meaning the derivative of the

<sup>&</sup>lt;sup>6</sup>It's often used in conjunction with other amplifiers for efficiency enhancement, such as Doherty amplifiers

Figure 2.8: Schematics and V-I waveforms of Class-C amplifiers

Figure 2.9: Schematics and V-I waveforms of Class-D amplifiers

voltage waveform at the time instant when the switch turns on is also zero. This property significantly reduces the efficiency sensitivity due to the passive component variations. The typical Class-E implementation is shown in Fig. 2.10. A series LC filter is used so that the load impedance is only seen at the fundamental frequency. As a result, the transistor sees inductive load impedance at the fundamental frequency while it only sees the parasitic drain capacitor at all harmonics. An inductor choke is used to provide the DC current path. The derivation for the required tuning impedances is skipped here, since it's given in multiple literatures [6, 7, 8].

$$P_{out}^{E} \approx V_{DC}I_{DC} = \frac{1}{F_{PJ}}V_{dd}I_{max} = \frac{1}{2.86}V_{dd}I_{max}$$

(2.43)

$$Z_{C,opt}^{E} = F_{PI}F_{C}\frac{V_{dd}}{I_{max}} = 8.985\frac{V_{dd}}{I_{max}}$$

(2.44)

$$R_{opt}^{E} = 0.1836 Z_{C,opt}^{E} = 1.65 \frac{V_{dd}}{I_{max}}$$

(2.45)

$$X_{opt}^{E} = 1.152R_{opt}^{E} = 1.9\frac{V_{dd}}{I_{max}}$$

(2.46)

$$F_{PI} = 2.86$$

(2.47)

$$F_C = \pi \tag{2.48}$$

$$\eta_D^E \approx 100\% \tag{2.49}$$

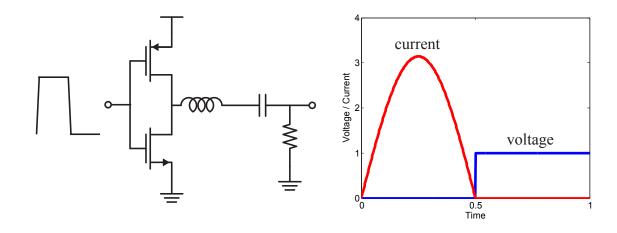

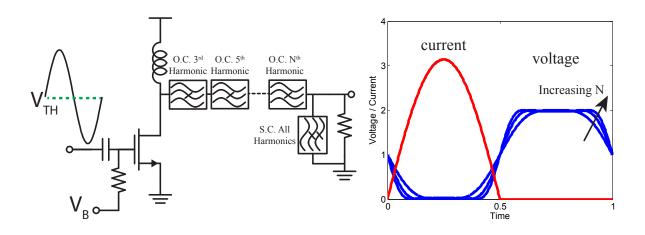

The final amplifier class in alphabetical order is Class-F. Class-F amplifiers are constructed based on Class-B amplifiers. In order to further improve the efficiency of Class-B amplifiers beyond 79% while not sacrificing the output power, odd harmonics can be added to the voltage waveform. The addition of the odd harmonics shapes the voltage waveform from a sine to a square, and thus reducing the V-I overlap. By increasing the number of harmonics, the efficiency can approach 100% eventually. To implement this idea, a bank of filters need to be inserted in series at the amplifier output to present Open Circuit (O.C.) impedance to the transistor at odd harmonics to enrich the odd harmonic content in the drain voltage waveform while a low-pass filter is needed at the output to eliminate all the even order harmonics (Fig. 2.11). When sufficient harmonics are added, the waveform resembles that of Class-D amplifiers. The output power, optimal impedance and efficiency of Class-F amplifiers are,

$$P_{out}^{F} = \frac{1}{2} \frac{4}{\pi} V_{dd} \frac{1}{2} I_{max} = \frac{1}{\pi} V_{dd} I_{max}$$

(2.50)

$$R_{opt}^{F} = \frac{V_{sw}}{I_{sw}} = \frac{8}{\pi} \frac{V_{dd}}{I_{max}}$$

(2.51)

$$\eta_D^F = \frac{V_{sw} I_{sw}}{2V_{DC} I_{DC}} \approx \frac{\frac{1}{\pi} V_{dd} I_{max}}{V_{dd} \frac{1}{\pi} I_{max}} = 100\%$$

(2.52)

Similar to Class-D amplifiers, the efficiency of Class-F amplifiers is also degraded by the parasitic capacitance at the transistor drain node. In addition, it requires large number of filters for harmonic generation which introduces insertion loss. As a result, the beauty of Class-F amplifiers is usually lost in implementation.

Figure 2.10: Schematics and V-I waveforms of Class-E amplifiers

Figure 2.11: Schematics and V-I waveforms of Class-F amplifiers

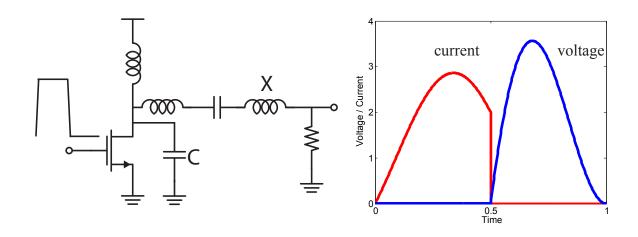

## 2.4 The Extended Class-E/F Family

As discussed in the previous section, Class-E amplifiers have ZVS waveform characteristic. In fact, there are numerous impedance tuning networks which can produce the ZVS waveform. It was not until recently that the relation between different impedance tuning networks was well discovered. In [8], it's summarized that many of the ZVS tuning networks belong to the Class-E/F family. Different members of the family correspond to different harmonic impedances, with Class-E and Class-F<sup>-1</sup> being the two extremes: Class-E has no harmonic impedance tuning while Class-F<sup>-1</sup> has impedance tuning at all harmonics. The essential rule of the Class-E/F harmonic tunings in [8] is as follows: the effective load impedance needs to be open circuit at even harmonics but short circuit at odd harmonics. Table. 2.2 shows examples of some Class-E/F tunings in terms of harmonic impedance.

It's also shown in [8] that the power, efficiency and gain of a Class-E/F amplifier can be expressed in terms of a set of technology dependent parameters such as transistor resistance and capacitance, defined in Table. 2.3, and also a set of technology independent parameters called the waveform figures of merit. The waveform figures of merit are determined by the combination of the harmonic load impedances and are unique to each tuning class. They are defined as follows,

$$F_V = \frac{V_{pk}}{V_{DC}} \tag{2.53}$$

$$F_I = \frac{I_{RMS}}{I_{DC}} \tag{2.54}$$

$$F_{PI} = \frac{I_{pk}}{I_{DC}} \tag{2.55}$$

$$F_C = \frac{V_{DC} I_{DC}}{V_{DC}^2 / Z_C} \tag{2.56}$$

$F_V$  is the ratio between the peak and DC voltages.  $F_I$  is the ratio between the RMS and DC current.  $F_{PI}$  is the ratio between the peak and DC current.  $F_C$  is the ration between the DC power and the reactive power stored on the drain capacitor. Under the condition that the transistor is sized to be largest possible given the capacitance constraint, the drain efficiency, power gain and PAE can be expressed as follows,

$$\eta_D^{EF} = 1 - (F_I^2 F_C) 2\pi f_0(\overline{r_{on} c_{out}})$$

(2.57)

$$G^{EF} = \eta_D^{EF} \left(\frac{\overline{c_{out}}V_{bk}^2}{\overline{p_{in}}}\right) \left(\frac{F_C}{F_V^2}\right) 2\pi f_0 \tag{2.58}$$

$$PAE^{EF} = (1 - \frac{1}{G^{EF}})\eta_D^{EF} \tag{2.59}$$

Note that here the loss due to the transistor finite on-resistance is taken into account.

The original Class-E/F family in [8] only considers open or short load for harmonic terminations, however, it turns out ZVS waveform can be achieved using arbitrary harmonic

| Tuning            | $f_0$                                                      | $2f_0$         | $3f_0$ | $4f_0$      | $5f_0$         | $6f_0$        | $7f_0$         |

|-------------------|------------------------------------------------------------|----------------|--------|-------------|----------------|---------------|----------------|

|                   | $\bigcap_{C} X_{\text{opt}} \ge R_{\text{opt}}$            |                |        |             |                |               |                |

| E                 |                                                            |                |        |             |                |               |                |

|                   | $\bigcap_{C} X_{\text{opt}} \not \geqslant R_{\text{opt}}$ |                |        |             |                |               |                |

| $E/F_2$           | 🛓 🗼                                                        | Open           |        | <u>C</u>    | C              |               |                |

|                   |                                                            | <u> </u>       |        | <u> </u>    | <u> </u>       | <u> </u>      | <u> </u>       |

| $\mathrm{E/F_3}$  | $\bigcap_{C} X_{\text{opt}} \ge R_{\text{opt}}$            | $C\overline{}$ | Short  | C           | $C\overline{}$ | C             | $C\overline{}$ |

| E/F3              | • <del>-</del>                                             | _              | 511016 | <u>-</u>    | <u> </u>       | <u>-</u>      | <u> </u>       |

|                   | $\bigcap_{C} X_{\text{opt}} \geqslant R_{\text{opt}}$      |                |        | $C^{\perp}$ | $C^{\perp}$    | $C^{\perp}$   | $C^{\perp}$    |

| $E/F_{2,3}$       | <u>+</u> +                                                 | Open           | Short  | <u></u>     | =              | <u></u> =     | =              |

|                   | $\bigcap_{C} X_{\text{opt}} = R_{\text{opt}}$              |                |        |             |                |               |                |

|                   |                                                            |                |        |             |                | $C^{\dagger}$ | $C^{\dagger}$  |

| $E/F_{2,3,4,5}$   | <u></u> + +                                                | Open           | Short  | Open        | Short          | <u></u>       | ᆂ              |

|                   | °                                                          |                |        |             |                |               |                |

| $\mathrm{F}^{-1}$ | <u></u>                                                    | Open           | Short  | Open        | Short          | Open          | Short          |

Table 2.2: The harmonic impedance specifications of several original Class- $\mathrm{E}/\mathrm{F}$  tunings

| $V_{bk}$             | Breakdown voltage $(V)$                          |

|----------------------|--------------------------------------------------|

| $\overline{r_{on}}$  | normalized transistor on-resistance $(\Omega m)$ |

| $\overline{c_{out}}$ | normalized transistor output capacitance $(F/m)$ |

| $\overline{c_{in}}$  | normalized transistor input capacitance $(F/m)$  |

| $\overline{p_{in}}$  | normalized input driving power $(W/m)$           |

Table 2.3: Technology dependent parameters

Figure 2.12: Harmonic impedance region of the extended Class-E/F family on the Smith Chart

terminations. Resistive termination at harmonics is undesired since it introduces additional harmonic resistance loss, therefore only purely reactive harmonic impedance is considered. In other words, the harmonic impedance of the extended Class-E/F family includes not only the O.C. and S.C. points on the Smith Chart, but also the entire perimeter, as shown in Fig. 2.12. Table. 2.4 shows several examples of the extended Class-E/F tunings with their corresponding naming conventions.

The extended Class-E/F tunings provide much larger design flexibility for performance optimization, especially when making tradeoffs between gain and drain efficiency. In order to see the impact of harmonic impedance on the amplifier performance, consider the Class-E/F<sub>X2</sub> tuning with inductive second harmonic termination of  $X_2$ .  $X_2$  is the second harmonic load reactance (in parallel with the transistor drain capacitor, as shown in Table. 2.4) normalized to the fundamental impedance of the drain capacitor ( $\frac{1}{\omega_0 C}$ ). Fig. 2.13 plots the V-I waveform of the Class-E/F<sub>X2</sub> with various  $X_2$  values. The amplifier starts as a Class-E am-

| Tuning                       | $f_0$                             | $2f_0$ | $3f_0$ | $4f_0$ | $5f_0$ | $6f_0$ | $7f_0$ |

|------------------------------|-----------------------------------|--------|--------|--------|--------|--------|--------|

| E                            | $\bigcap_{C} X_{opt} \ge R_{opt}$ | C      | C      | C      |        | C      | C      |

| $\mathrm{E}/\mathrm{F}_{X2}$ | $\bigcap_{C} X_{opt} \ge R_{opt}$ |        | C      | C      |        | C      | C      |

| $E/F_{X2,X3}$                | $\bigcap_{C} X_{opt} \ge R_{opt}$ |        |        | C =    | C =    | C =    | C =    |

Table 2.4: The harmonic impedance specifications of several extended Class-E/F tunings

Figure 2.13: V-I waveforms of the Class-E/F  $_{X2}$  tunings with various  $X_2$  values

Figure 2.14: Waveform FoM of Class-E/F<sub>X2</sub> tunings as a function of  $X_2$

plifier when  $X_2$  is infinity. When  $X_2$  decreases, stronger second harmonic content is present in the current waveform. When  $X_2$  reaches 0.5, the amplifier becomes Class-E/F<sub>2</sub>, since the load reactance cancels out the reactance of the drain capacitor, presenting an overall O.C. at the second harmonic. Further decreasing  $X_2$  keeps enriching the second harmonic content until the minimum instantaneous current reaches zero. Since it's undesired to have reverse direction current through the transistor, there's a lower limit on the  $X_2$  value. For Class-E/F<sub>X2</sub>, the minimum  $X_2$  is 0.391. Based on V-I waveforms, the four waveform figures of merit can be calculated. Fig. 2.14 plots  $F_V$ ,  $F_I$ ,  $F_C$  and  $F_{PI}$  as a function of  $X_2$ . When  $X_2$  decreases from infinity (no second harmonic tuning),  $F_V$  increases while  $F_C$  decreases, meaning larger peak to average voltage ratio and larger drain capacitance tolerance. Low  $F_C$  is desired from drain efficiency point of view since larger transistor size can be used to reduce the on resistance loss. On the other hand, the behavior of both  $F_I$  and  $F_{PI}$  is nonmonotonic. Both  $F_I$  and  $F_{PI}$  decreases initially until it reaches the minimum value and they start to climb back up. The minimum is obtained when  $X_2$  is 0.5. Since low  $F_I$  is desired for

Figure 2.15:  $\eta_D,\,G_p$  and PAE of Class-E/F  $_{X2}$  amplifiers as a function of  $X_2$

efficiency,  $X_2 = 0.5$  gives the best  $F_I$  value. Note that with  $X_2 = 0.5$ , the tuning becomes Class-E/F<sub>2</sub>.

Based on a typical 65nm CMOS technology, the drain efficiency, power gain and PAE of Class-E/F<sub>X2</sub> amplifiers can be plotted as a function of  $X_2$  for different operating frequencies, as shown in Fig. 2.15. There's a clear tradeoff between drain efficiency and power gain: decreasing  $X_2$  decreases the product  $F_I^2F_C$  and therefore improves the drain efficiency; but due to decreased  $F_C$ , or equivalently increased transistor size, larger input power is needed which leads to reduced power gain. The optimal PAE point depends on not only technology parameters, but also the operating frequency. At 2.4GHz, the optimal PAE is obtained when  $X_2$  is around 0.6. Finally at 60GHz, the optimal PAE is obtained when  $X_2$  is around 0.45. Intuitively, the decreasing optimal  $X_2$  value is caused by the fact that  $\eta_D$  drops with increasing frequency, and therefore larger transistor sizes are needed to reduce the on resistance loss, which means lower  $F_C$  value is desired.

## 2.5 High Frequency Challenges

CMOS technology scaling has dramatically improved the transistor speed, as a result, significant progress has been achieved in integrating many of the mm-wave circuit blocks. However, mm-wave power amplifiers still face many design challenges. Fig. 2.16 shows a performance survey of the state-of-the-art CMOS PA over a wide frequency range. A clear trend can be observed here: both output power and efficiency drop with increasing operating frequency. This trend can be explained by multiple reasons. Since the product of transistor  $f_t$  and breakdown voltage is kept roughly constant during technology scaling, the breakdown voltage reduces as  $f_t$  improves. The thin oxide breakdown voltage is around 15MV/cm, and with oxide thickness in the order of 1nm, the breakdown voltage is usually around 1V. This means all the mm-wave devices need to operate from a very low supply voltage, which directly affect the PA output power since power is proportional to the voltage square. To deliver more power with the same supply voltage, the transistor need to deliver more current and therefore it needs to see a smaller load impedance. This means an impedance transformation network is needed at the PA output. However, the insertion loss of the matching network is inversely proportional to the impedance transformation ratio, and larger desired output power translates into larger insertion loss in the matching network. The result is that with a simple LC impedance transformation network, there is a limit on the obtainable output power [9]. To make things worse, technology scaling not only shrinks the copper metal thickness but also reduce the distance between top metal layer and the silicon substrate, thus reducing the Quality factor (Q factor) of on-chip passives. It's also shown in [9] that the maximum obtainable output power is proportional to the square of the Q factor.