### **Lawrence Berkeley National Laboratory**

#### **Recent Work**

#### **Title**

Characterization of Wafer Charging Mechanisms and Oxide Survival Prediction Methodology

#### **Permalink**

https://escholarship.org/uc/item/29b63894

#### **Authors**

Lukaszek, W. Dixon, W. Vella, M. <u>et al.</u>

#### **Publication Date**

1994-04-11

# L

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

# Accelerator & Fusion Research Division

Invited paper presented at the Reliability Physics Symposium, San Jose, CA, April 11–14, 1994, and to be published in the Proceedings

**Characterization of Wafer Charging Mechanisms** and Oxide Survival Prediction Methodology

W. Lukaszek, W. Dixon, M. Vella, C. Messick, S. Reno, and J. Shideler

**April** 1994

Does Not | Copy irculate | Bldg. 50 Library

Prepared for the U.S. Department of Energy under Contract Number DE-AC03-76SF00098

#### DISCLAIMER

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

## Characterization of Wafer Charging Mechanisms and Oxide Survival Prediction Methodology

Wes Lukaszek and William Dixon

Center for Integrated Systems Stanford University, Stanford, CA 09305

Michael Vella

Accelerator and Fusion Research Division Lawrence Berkeley Laboratory University of California Berkeley, California 94720

Cleston Messick, Steve Reno, and Jay Shideler

National Semiconductor 3333 West 9000 South West Jordan, UT 84088-8838

April 1994

# Characterization of Wafer Charging Mechanisms and Oxide Survival Prediction Methodology

Wes Lukaszek and William Dixon Center for Integrated Systems Stanford University, Stanford, CA 09305 (415) 725-3641, Fax: (415) 725-6278

Michael Vella

Lawrence Berkeley Labsor a tory

Berkeley, CA

Cleston Messick, Steve Reno, and Jay Shideler National Semiconductor 3333 West 9000 South West Jordan, UT 84088-8838 Invited pages

Reliability Phypies Sym

San Dee SA

AREN 11-14 1994

#### **ABSTRACT**

Unipolar, EEPROM-based peak potential sensors and current sensors have been used to characterize the I-V relationship of charging transients which devices normally experience during the course of ion implantation. The results indicate that the charging sources may appear to behave like current-sources or voltage-sources, depending on the impedance of the load. This behavior may be understood in terms of plasma concepts. The ability to empirically characterize the I-V characteristics of charging sources using the CHARM-2 monitor wafers opens the way for prediction of failure rates of oxides subjected to specific processes, if the oxide  $Q_{bd}$  distributions are known.

#### INTRODUCTION

Good morning. My talk today is about characterization of wafer charging in process equipment. Before I get into the technical details, I'd like you to recognize that I am not going to talk about measurements made on a product. Instead, we are using pre-fabricated test wafers which are populated with sensors specifically designed to characterize the charging properties of the process medium.

I will begin by briefly reviewing the CHARM measurement technique. I will not go into details - if you are interested in the CHARM device design details you may refer to last year's talk.[1] This time, I will describe how the CHARM sensors are calibrated, and how measurements are performed. I will spend most of my time discussing the results of an ion implant experiment conducted at National Semiconductor. I will show you how the data which we have obtained with the help of the CHARM monitors has helped us develop a model of wafer charging in ion implanters that appears to fit the observations quite well. Finally, I will make some comments about the methodology for predicting oxide wear-out.

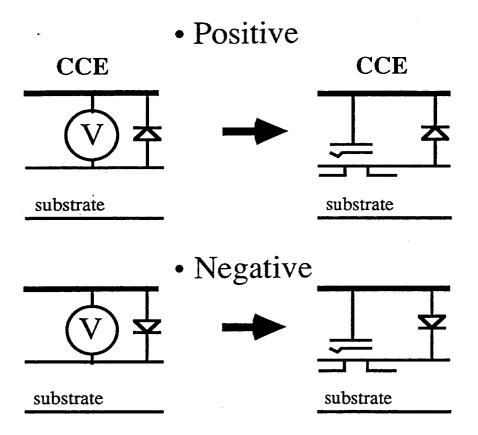

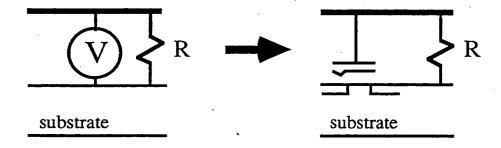

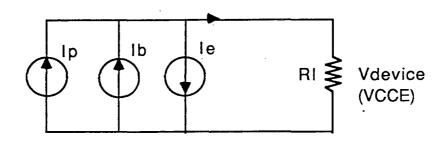

When it comes to wafer charging in process equipment, we want to look at the driving forces behind the damage: the potential build up on the surface of the wafer, relative to the substrate, which enables current conduction through oxides, and the charge flux delivered to the wafer, which ultimately does the damage. (Figure 1) In principle, to measure surface potential of a given polarity, we would employ a charge collec-

tion electrode (CCE) on the surface of the wafer, connected to a high input impedance voltmeter, shunted by a diode of opposite polarity. However, because it is difficult to implement a voltmeter on a wafer and to supply power to it inside process equipment, our sensors employ EEPROM transistors as high input impedance voltmeters. Due to limited dynamic range of the EEPROM transistors, most of the effort involved in implementing the sensors is devoted to overcoming this limitation. It is important to use unipolar potential sensors of both polarities because ion implantation, in particular, continually subjects the wafers to alternating positive and negative transients [2], both of which need to be monitored. Charge flux sensors, in turn, are implemented by adding resistors from CCEs to the substrate, and measuring the voltage drop across the resistors with EEPROM transistors.

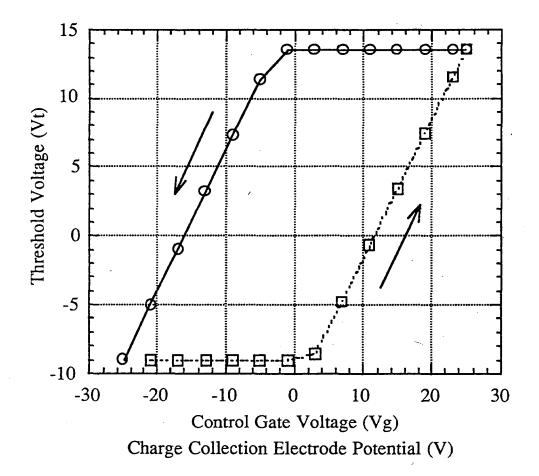

(Figure 2) To perform the desired measurements using the CHARM2 monitors, we pre-program the threshold voltages (Vt's) of the EEPROM transistors, place the wafers in process equipment (in this case, ion implanter), perform the process, and measure the resulting Vt's. Because the EEPROM transistors are re-programmable, this cycle may be repeated many times using the same wafer. The conversion of the post-process EEPROM Vt's to surface potentials is performed using the Vt-Vg calibration curve. Knowing the pre-programmed Vt and the post-experiment Vt tells us which of the Vg-Vt curves to use: if the final Vt is higher than the initial Vt, the right-side curve is used and, conversely, if the final Vt is lower than the initial Vt, the left-side curve is used to determine the value of Vg, i. e. surface-substrate potential which caused the final Vt.

#### **EXPERIMENTAL RESULTS**

From here on, I will concentrate on the experiment that we have performed at National Semiconductor. (Figure 3) It employed three CHARM-2 wafers with resist on field oxide, and exposed charge collection electrodes. The wafers were implanted with Arsenic at 80 KeV to a dose of 5e15, using a beam current of 6 mA, on an NV10-80 high current ion implanter. The variable was the flood gun current used to neutralize the beam, monitored by measuring the disc current. Three different flood gun settings were employed: flood gun off, corresponding to a disc current of +6 mA; slight over-

flood, corresponding to a disc current of -1 mA; and substantial overflood, corresponding to a disc current of -8 mA.

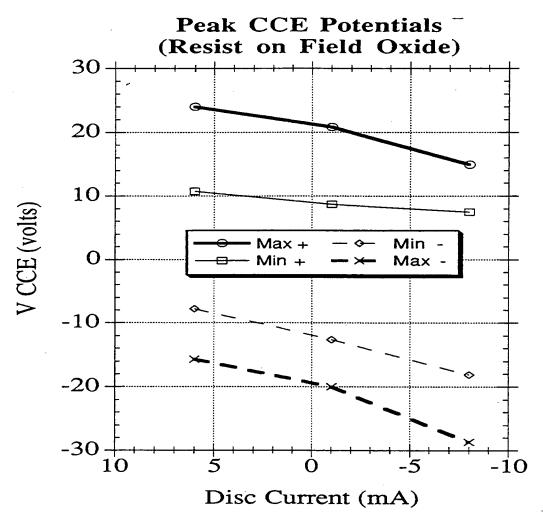

Figure 3 shows the maximum and minimum values of positive potential and maximum and minimum values of negative potential recorded with the CHARM-2 sensors. The observations are entirely consistent with past knowledge [2]. Increasing the number of flood electrons in the beam lowers the excursions in positive potential and increases the excursions in negative potential. It is interesting to note that at a disc current of -1 mA, the maximum positive and negative excursion are almost symmetrical at +/- 20 V. This should minimize possible damage to CMOS wafers since it symmetrically minimizes the stress for both n-channel and p-channel devices. Indeed, this is the nominal production setting for this implant, determined on a large volume of product wafers[3].

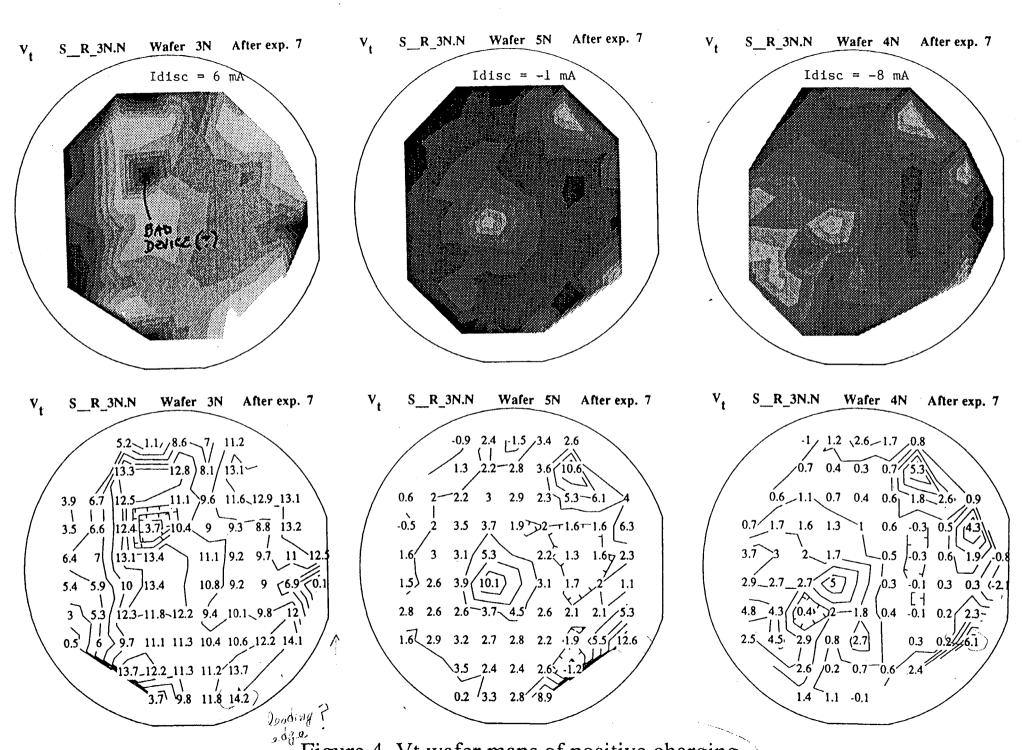

The large spread between maximum and minimum values of both positive and negative potentials indicates non-uniform charging, illustrated in more detail on the wafer maps of Figure 4, which shows the distribution of Vt's associated with positive charging on the three wafers. (The higher the Vt, the more positive the surface-substrate potential.) Is interesting to note that similar patterns are observed on all three wafers, suggesting that the non-uniformity may be a signature of the equipment, perhaps related to its design.

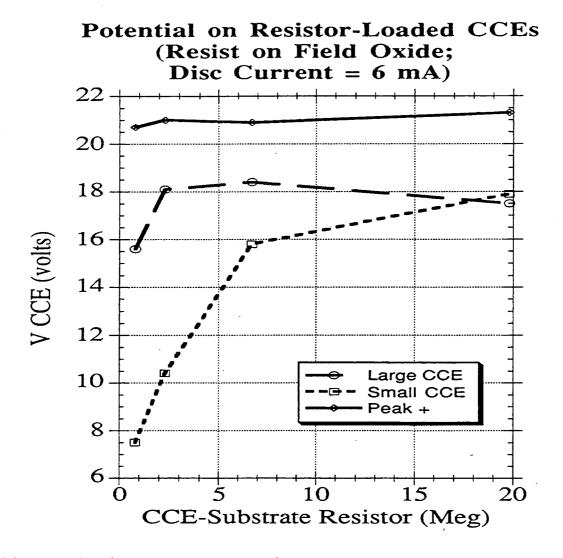

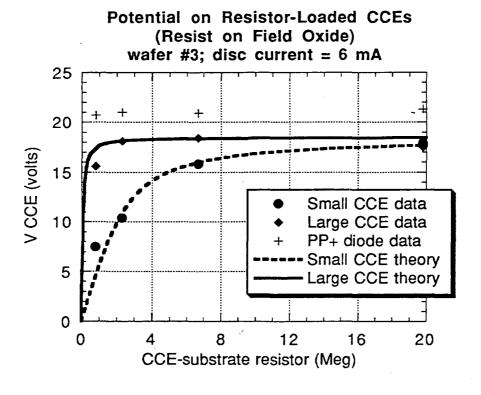

Let's now examine in more detail the positive charging data obtained on the wafer whose implant beam was not neutralized with flood electrons (disc current = 6 mA), resulting in the largest positive charging. The graph in Figure 5 shows the median CCE potential recorded by the peak potential monitor (Peak +) and two charge flux monitors, one having a small CCE and one having a large CCE, as function of the value of the resistor connected between the CCE and substrate. For low values of VCCE, the small CCE flux sensor shows a linear increase of VCCE vs. resistance, indicating a currentsource behavior. However, as VCCE increases, the curve bends over, saturating at ~18 V for both small and large CCE sensors. At first glance, this suggests a voltage-source behavior, and helps explain past debate in the ion implant community regarding the current-source vs. voltage-source nature of the charging phenomena. Our data clearly indicates that the charging source may appear as a current-source or a voltagesource, depending on the value of the load impedance. For low values of load impedance (or small CCEs, which collect little current) the beam behaves like a current-source, but for high values of load impedance (or large CCEs) the beam imposes a fixed maximum potential.

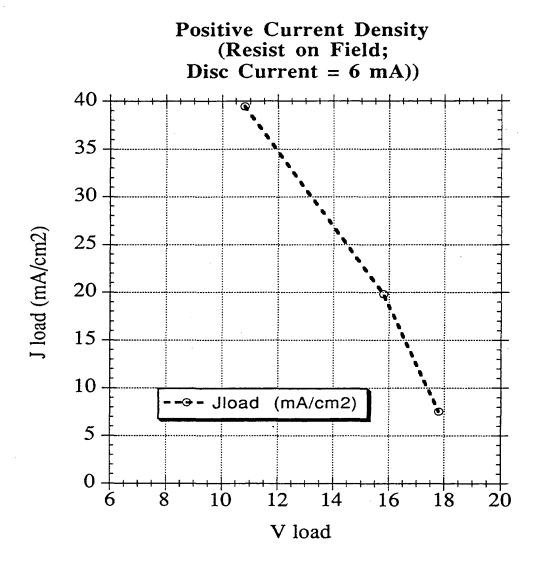

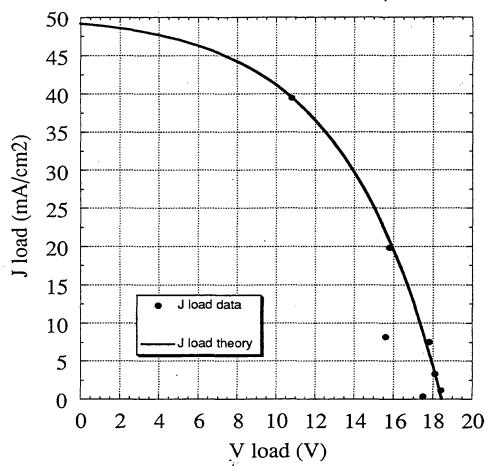

This data may also be displayed in the form of a J-V plot, shown in Figure 6 for the small CCE sensor, which completely characterizes the charging source. Once the J-V characteristics of a charging source are determined, the charging behavior of any CCE connected to any load may be predicted by superimposing the load J-V curve on the J-V characteristics of the charging source. The intersection of the two curves determines the value of current density which the charging source can deliver to the CCE sourcing the load. For example, in the case of this implant, a CCE connected to a 200 Å gate oxide capacitor (which would turn on strongly at ~ 20 V) would not cause damage to the oxide since our ion beam is not capable of delivering much current at 20 V. However, the

same CCE connected to a 100 Å capacitor (which would turn on strongly at ~ 10 V) would be much more likely to cause damage, since our implant beam is capable of sourcing a very large positive current density at 10 V.

#### THEORY

To explain the curious transition from current-source charging behavior at low VCCE to a voltage clamp at high VCCE, we turn to a suggestion by Michael Vella [4], that the ion beam and its charging behavior should be treated as a plasma composed of the beam ions, slow ions resulting from background 7 = 63gases, and plasma electrons. In our model, each of these quantities is represented by a current source, as shown in Figure 7. The positive charging by the beam is represented by  $j_{ib}(1+\gamma_s)$ , where  $j_{ib}$  represents the beam flux and  $\gamma_s$  represents the secondary electron emission coefficient. The positive charging by the slow ions is represented by jip, and the negative charging by the plasma electrons is represented by j<sub>ip</sub>(exp(eV/kT<sub>e</sub>)), where T<sub>e</sub> is the electron temperature. It is the strongly non-linear behavior of the plasma electrons which clamps the CCE potential at high voltages: as the CCE potential rises, electrons attracted from the plasma neutralize the positive charging by the beam and the slow ions. This clamps the CCE potential, and reduces the net charging current density for high VCCE, as previously observed.

The graph in Figure 7 shows a comparison between the experimental data, the theoretical curve-fit to the small CCE data, and the prediction of the large CCE results based on the small CCE data fitting parameters. It is interesting to note that the secondary electron emission coefficient obtained in this case of resist-covered wafers is very high, although to determine its value with precision we need to know the exact area of the ion beam. If beam area of 6 cm<sup>2</sup> is assumed, the secondary electron emission coefficient is about 50, which explains why implant wafer charging in the presence of photoresist is much greater than in the absence of photoresist [5].

A comparison between the theoretically predicted J-V characteristics of the charging source, and the small and large CCE data is shown in Figure 8. The theory predicts a peak charging current dominated by the beam ions and their secondary electrons, which should remain fixed even in the presence of flood electrons. Consequently, flood electrons can reduce Jload only for Vload > 0, resulting in a steeper J-V curve but the same Jload-axis intercept. This appears to be supported by implant charging data obtained at different flood gun settings. Regrettably, this will require improved implant process uniformity for thinner oxides devices, where the net charging current will need to remain low at low VCCE, over the entire wafer.

#### PREDICTION OF OXIDE WEAR-OUT

In principle, by knowing the J-V charging characteristics of process equipment, which may be obtained using the CHARM-2 wafers, the J-V characteristics of the oxide, the duration of the charging portion of the process (t), the CCE area (Acce), and the gate oxide area (Aox), we can calculate the charge passed through the oxide as Q = JtAcce/Aox. If the Qbd distribution of the oxide is known before processing,

it will be reduced by Q after processing, giving rise to a new  $Q_{bd}$  distribution, translated by Q along the  $Q_{bd}$  axis. Devices whose  $Q_{bd} < Q$  will fail. A similar analysis may be performed to determine if existing process equipment will be able to meet the needs of a newer, scaled technology. These simplified analyses assume, of course, that the  $Q_{bd}$  of the oxide was characterized using waveforms similar to those encountered in the given process equipment, and that the temperature experienced by the processed wafers was not sufficient to cause any annealing effects. It should also be recognized that any predicted reduction in  $Q_{bd}$  resulting from a given process may not be fully expressed at end-of-line due to subsequent high temperature steps and attendant annealing effects.

#### SUMMARY

The above results show that the CHARM-2 monitor wafers are an effective tool for studying many aspects of wafer charging in process equipment. They can be used to directly measure the peak positive and peak negative charging potentials and charging currents, and provide wafer maps of these quantities and the total integrated UV dose. This "fingerprint" of the driving forces behind charging damage may be used, for example, to ensure reproducible process conditions after equipment maintenance. The monitors are fast and easy to test (only a threshold voltage measurement is needed); they can be calibrated at every point on a wafer to ensure validity of "strange" data; and they are re-usable (hence, more cost effective than existing techniques using product or test wafers). Due to their inherent ability to characterize individual equipment and processes, the CHARM-2 monitors make it easy to isolate offending hardware and processes, thus expediting process and yield improvement. They may also be used to optimize processes to minimize charging damage, or to study the fundamental mechanisms of wafer charging in process equipment. We have used them to obtain the data needed for empirically-based modeling of wafer charging in high current ion implanters. We also envision using these models and measurements as a starting point for prediction of oxide wear out based on measurements of the basic parameters associated with the fundamental mechanisms governing the operation of process equipment.

#### REFERENCES

- [1] W. Lukaszek, "Monitoring Plasma and Ion Implant Charging Damage Using EEPROM-Based Monitor Wafers", Final Report 1992 International Wafer Level Reliability Workshop, Lake Tahoe, CA, Oct. 25-28, 1992, pp. 101-105.

- [2] B J. Doherty and D. J. McCarron, "Ion Induced Wafer Charging", Nuclear Instruments and Methods, B37/38, 1989, pp. 559-562.

- [3] S. Reno, National Semiconductor, Private communication.

- [4] M. Vella, "Role of the Beam/Plasma Potential in Charging Damage", UC Berkeley Extension Short Course on Wafer Charging Effects in Ion Implantation Processing, June 10-11, 1993, Dallas, TX

[5] W. Lukaszek, et. al., "Charging Studies Using the CHARM2 Wafer Surface Charging Monitor", Nuclear Instruments and Methods in Physics Research, B74, 1993, pp. 301-305.

#### **QUESTIONS AND ANSWERS**

- Q: Have you correlated the locations of maximum charging on your CHARM wafers with reduced Q<sub>bd</sub> on product wafers at the end of the process?

- A: No, we haven't so far. That's the next step.

- Q: Can you comment on any limits on reusability due to actual damage to the CHARM devices themselves?

- A. As far as longevity of the CHARM-2 monitors is concerned, the first thing to wear out are the pads, due to repeated probing. The EEPROM transistors themselves are capable of about 1e7 cycles, which corresponds to about 1e3 implants. The EEPROM transistors are also quite rugged, using oxide thicknesses capable of withstanding about 100 V.

- Q: Do you have any case study results like this for equipment other than implanters, such as etching equipment or anything else?

- A: Yes, we have also used the CHARM-2 monitors to look at resist stripping and metal etching. But more work needs to be done, especially in plasma etching.

## CHARM2 measurement technique ...

• Surface potential

• Charge flux

Figure 1. CHARM2 Measurement Technique

## Measurement procedure and calibration ...

Program & Measure Vt (on a parametric tester)

Implant

Measure Vt (on a parametric tester)

Repeat (CHARM2 wafers are re-usable)

### Calibration

Figure 2. Measurement procedure and EEPROM calibration

### Implant process optimization ...

• Implanter: NV10-80

Implant: Arsenic; 5e15; 80KeV

Beam current = 6 mA

Flood gun current = variable

Figure 3. Optimization of Arsenic implant conditions

Figure 4. Vt wafer maps of positive charging

# Characterization of positive charging source...

• Implanter: NV10-80 Implant: Arsenic; 5e15; 80KeV Beam current = 6 mA Disc current = 6 mA

Figure 5. Characteristics of positive charging source

# J-V characteristics of positive charging source...

• Implanter: NV10-80 Implant: Arsenic; 5e15; 80KeV Beam current = 6 mA Disc current = 6 mA

Figure 6. J-V Characteristics of positive charging source.

## Implant charging model ...

$$V_{\text{device}} = RA \left[ j_{ip} (1 - \exp\left[\frac{eV_{\text{device}}}{kT_e}\right]) + j_{ib} (1 + \gamma_s) \right]$$

$$j_{ip} = 1.26 \text{ mA/cm}^2$$

;  $T_e = 5 \text{ eV}$ ;  $j_{ib}(1+\gamma_s) = 49.2 \text{ mA/cm}^2$

Figure 7. Implant charging model and comparison with positive charging data

15 & No Man Ken J-V characteristics of positive charging source: theory vs experiment

Theory:

$$j_{\text{device}} = j_{ip} (1 - \exp[\frac{eV_{\text{device}}}{kT_e}]) + j_{ib} (1 + \gamma_s)$$

$j_{\text{ip}} = 1.26 \text{ mA/cm}^2$ ;  $T_e = 5 \text{ eV}$ ;  $j_{\text{ib}} (1 + \gamma_s) = 49.2 \text{ mA/cm}^2$

Positive Current Density (Resist on Field; Disc Current = 6 mA)

Figure 8. Experimental vs. predicted J-V characteristics of positive charging source

LAWRENCE BERKELEY LABORATORY UNIVERSITY OF CALIFORNIA TECHNICAL AND ELECTRONIC INFORMATION DEPARTMENT BERKELEY, CALIFORNIA 94720