# UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Fault-susceptibility Mitigation and Efficient Use of Resources in Programmable Hardware Accelerators

**Permalink** https://escholarship.org/uc/item/1ww3k3b8

**Author** Lotfi, Atieh

Publication Date 2018

\_\_\_\_

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

### Fault-susceptibility Mitigation and Efficient Use of Resources in Programmable Hardware Accelerators

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

#### Atieh Lotfi

Committee in charge:

Professor Rajesh K. Gupta, Chair Professor Ryan Kastner Professor Sorin Lerner Professor Patrick Mercier Professor Dean Tullsen

Copyright Atieh Lotfi, 2018 All rights reserved. The dissertation of Atieh Lotfi is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2018

### DEDICATION

To my parents with everlasting gratitude

### TABLE OF CONTENTS

| Signature Page  | iii                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication      | iv                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table of Conte  | nts                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| List of Figures | viii                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| List of Tables  |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Acknowledge     | nents                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vita            | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Abstract of the | Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 1       | Introduction11.1Dissertation Organization and Contributions6                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 2       | Background112.1Background on FPGA and Synthesis Process112.2Isolating faulty primitives in FPGA132.3OpenCL Execution Model on GPU and FPGA142.4GPU Architecture162.4.1AMD GCN architecture16                                                                                                                                                                                                                                                |

| Chapter 3       | Enabling Task Migration to Isolate Corrupted Cores in GPUs183.1Introduction193.2Detecting and locating faulty cores203.3Proposed methodology to quarantine faulty cores213.3.1Stream core isolation223.4Experimental Setup and Results253.4.1Performance and Energy Overhead253.5Mitigation of Effects Caused by Aging in Microelectronics323.5.2Improvement in $\Delta V_{th}$ 353.6Related Work363.7Chapter Summary373.8Acknowledgments37 |

| Chapter 4 | Case Stu     | udy: Reducing Redundant Hardware Overheads                       | 38  |

|-----------|--------------|------------------------------------------------------------------|-----|

|           | 4.1 Int      | troduction                                                       | 39  |

|           | 4.2 Ta       | rget GPU Architecture                                            | 41  |

|           |              | w overhead tag checking                                          | 42  |

|           | 4.4 Si       | mulation Methodology and Evaluation Metrics                      | 45  |

|           | 4.5 Ex       | xperimental Results                                              | 47  |

|           | 4.5          | Instruction Cache Tag SRAM Structure Evaluation                  | 47  |

|           | 4.5          | 5.2 Data Cache Tag SRAM Structure Evaluation                     | 50  |

|           | 4.5          | 5.3 Hash Function Area and Timing Analysis                       | 52  |

|           | 4.5          | 5.4 Address Stride Distribution Analysis                         | 53  |

|           | 4.6 Ar       | nalytical and Monte-Carlo Simulation for Estimation of False Hit |     |

|           |              | ites                                                             | 55  |

|           | 4.7 Re       | elated Work                                                      | 57  |

|           | 4.7          |                                                                  | 57  |

|           |              | 7.2 Exploiting Hash Functions for Addressing Memory Structures   | 57  |

|           |              | hapter Summary                                                   | 59  |

|           |              | cknowledgments                                                   | 60  |

|           |              |                                                                  | 00  |

| Chapter 5 | Automa       | ted Source-code Optimization for Efficient Use of Hardware Re-   |     |

| -         | sources      | -<br>                                                            | 61  |

|           | 5.1 Int      | troduction                                                       | 61  |

|           | 5.2 Ba       | ackground and Motivating Example                                 | 63  |

|           |              | RATER: Design Optimization Workflow                              | 64  |

|           | 5.3          |                                                                  | 67  |

|           | 5.3          | 3.2 Genetic-based Design Space Exploration Algorithm             | 68  |

|           | 5.3          |                                                                  | 72  |

|           |              | aperimental Results                                              | 73  |

|           | 5.4          |                                                                  | 73  |

|           |              | 4.2 Improvements for FPGA                                        | 73  |

|           | 5.4<br>5.4   | I I I I I I I I I I I I I I I I I I I                            | 76  |

|           |              | 4.4 Quality                                                      | 77  |

|           | 5.4<br>5.4   |                                                                  | 78  |

|           |              | elated Work                                                      | 79  |

|           |              | hapter Summary                                                   | 80  |

|           |              |                                                                  | 81  |

|           | <i>J.1</i> 1 |                                                                  | 01  |

| Chapter 6 | Resourc      | e-aware Task Migration in HLS-based FPGA Design                  | 82  |

| <b>I</b>  |              | troduction                                                       | 83  |

|           |              | otivating Example                                                | 85  |

|           |              | esource-Aware Regularity Extraction and Task Migration Workflow  | 89  |

|           |              | perimental Results                                               | 97  |

|           | 6.4          | •                                                                | 97  |

|           |              | 4.2 Results                                                      | 98  |

|           |              |                                                                  | 102 |

|           | 5.           |                                                                  |     |

|              | 6.5 Related   | Work                                                      | 103 |

|--------------|---------------|-----------------------------------------------------------|-----|

|              | 6.6 Chapter   | Summary                                                   | 105 |

|              | 6.7 Acknow    | vledgements                                               | 106 |

| Chapter 7    | Case Study: I | mpact of Algorithmic Optimization on Resource Utilization | 107 |

|              | 7.1 Introduc  | ction                                                     | 108 |

|              | 7.2 Backgro   | ound                                                      | 109 |

|              | 7.2.1         | Convolutional Neural Networks                             | 109 |

|              | 7.2.2         | Local Binary Pattern Network                              | 110 |

|              | 7.3 FPGA A    | Accelerator Design                                        | 112 |

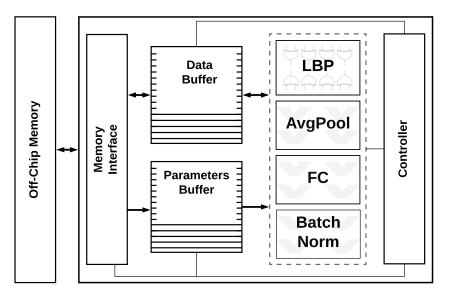

|              | 7.3.1         | Accelerator Architecture                                  | 112 |

|              | 7.3.2         | Execution Flow of the Accelerator                         | 114 |

|              | 7.3.3         | Compute Units Architecture                                | 114 |

|              |               | nental Results                                            |     |

|              | -             | Experiment Setup                                          |     |

|              |               | Results                                                   |     |

|              |               | Work                                                      |     |

|              |               | Summary                                                   |     |

|              |               | vledgement                                                |     |

| Chapter 8    | Concluding R  | Remarks                                                   | 120 |

| Bibliography |               |                                                           | 123 |

### LIST OF FIGURES

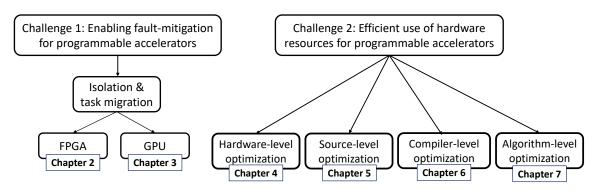

| Figure 1.1:                               | Dissertation organization.                                                                                                                                                                                                   | 7              |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

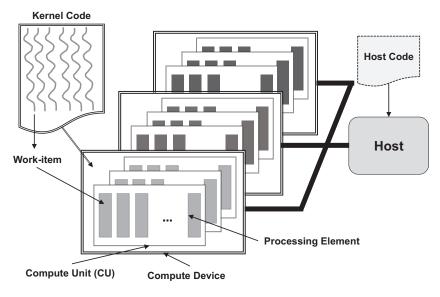

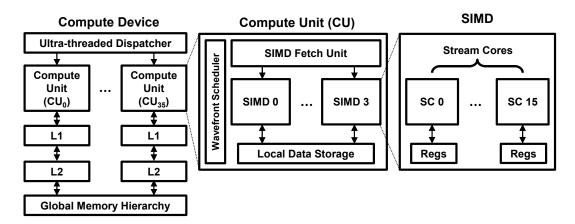

| Figure 2.1:<br>Figure 2.2:                | OpenCL platform model                                                                                                                                                                                                        | 15<br>17       |

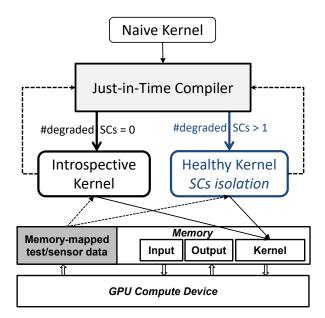

| Figure 3.1:<br>Figure 3.2:<br>Figure 3.3: | Kernel adaptation flow                                                                                                                                                                                                       | 22<br>23<br>24 |

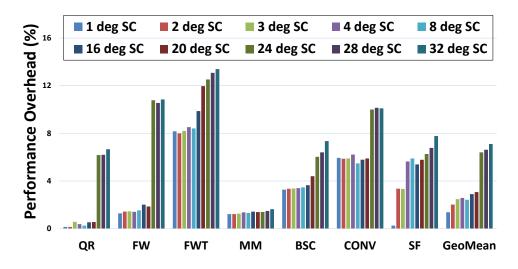

| Figure 3.4:                               | Performance overhead of using healthy kernel on Radeon RX 580 compared to the naive kernel when the number of degraded SCs (deg SC) are increased from 1 to 32 (all in a single CU) for different kernels and their average  | 27             |

| Figure 3.5:                               | Energy overhead of using healthy kernel on Radeon RX 580 compared to<br>the naive kernel when the number of degraded SCs (deg SC) are increased<br>from 1 to 32 (all in a single CU) for different kernels and their average | 27             |

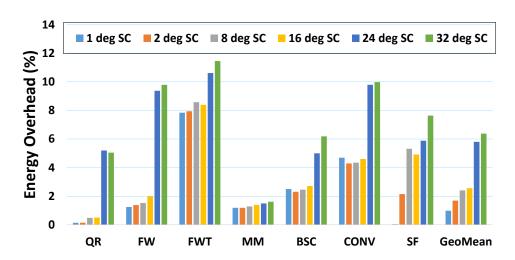

| Figure 3.6:                               | Performance overhead of using healthy kernel compared to the naive kernel<br>when the number of degraded CUs is increased from 1 to 10 (one degraded                                                                         |                |

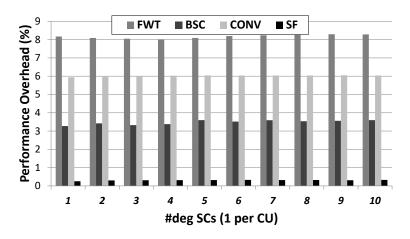

| Figure 3.7:                               | SC per each CU) for four kernels<br>Effect of changing number of work-groups (input size) on Radeon RX 580<br>for (a) Blackscholes (b) SimpleConvolution as the number of degraded SCs                                       | 28             |

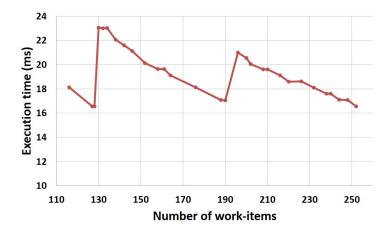

| Figure 3.8:                               | is changed from 1 to 32 in a CU Effect of changing work-item count in the naive kernel for SobelFilter                                                                                                                       | 29<br>30       |

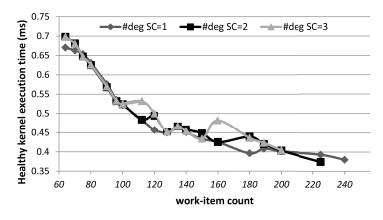

| Figure 3.9:                               | Performance tuning for healthy kernels                                                                                                                                                                                       | 30             |

| Figure 3.10:                              | Effect of changing (#WI, #WG) on the execution time of healthy kernel for                                                                                                                                                    | 50             |

| 11guie 5.10.                              |                                                                                                                                                                                                                              | 31             |

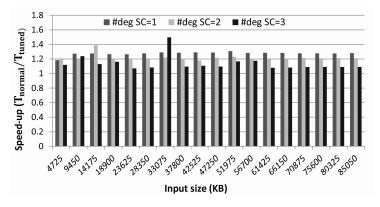

| Figure 3.11:                              | Performance benefit of using a tuned healthy kernel over a healthy kernel                                                                                                                                                    | 51             |

| <b>T</b> ' <b>2.12</b>                    | which is unaware of tuning (The benchmark is the same as Figure 3.10)                                                                                                                                                        | 32             |

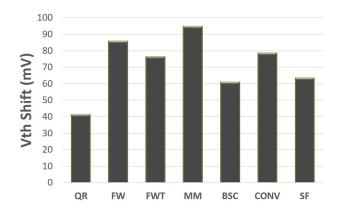

| Figure 3.12:                              | $V_{th}$ shift for different kernels at the end of 360 hours on HD 5870 with one                                                                                                                                             | 25             |

| Eigung 2 12.                              | degraded SC.                                                                                                                                                                                                                 | 35             |

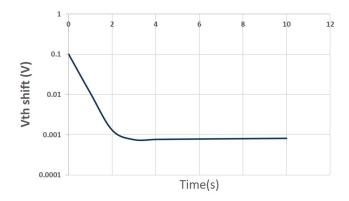

| Figure 5.15:                              | $V_{th}$ shift behaviour during recovery phase based on the NBTI model in [14].                                                                                                                                              | 36             |

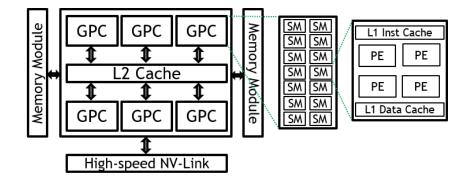

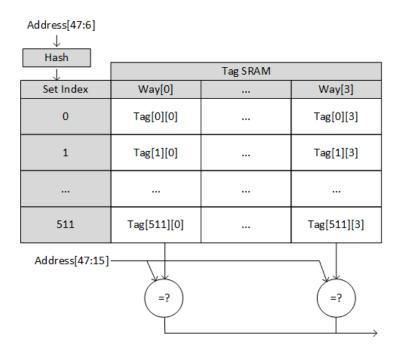

| Figure 4.1:                               | Volta GPU block diagram                                                                                                                                                                                                      | 42             |

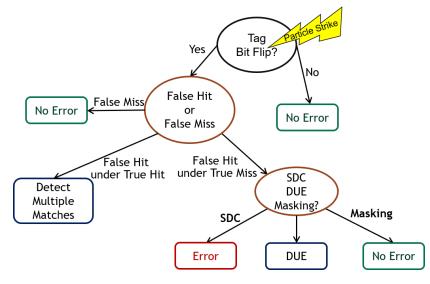

| Figure 4.2:                               | Tag error event space                                                                                                                                                                                                        | 43             |

| Figure 4.3:                               | No explicit tag error checking                                                                                                                                                                                               | 44             |

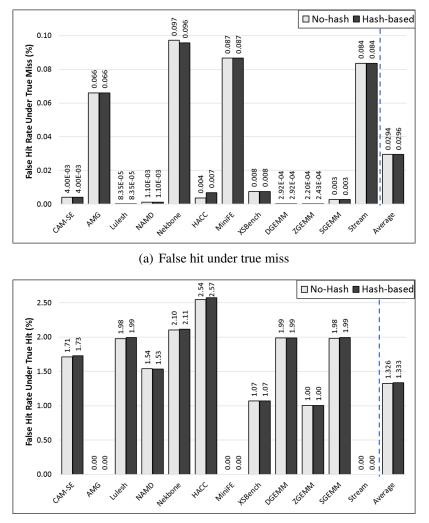

| Figure 4.4:                               | False hit for a 3-way12KB set-associative instruction cache: Hash-based vs                                                                                                                                                   |                |

|                                           | No-Hash Schemes                                                                                                                                                                                                              | 49             |

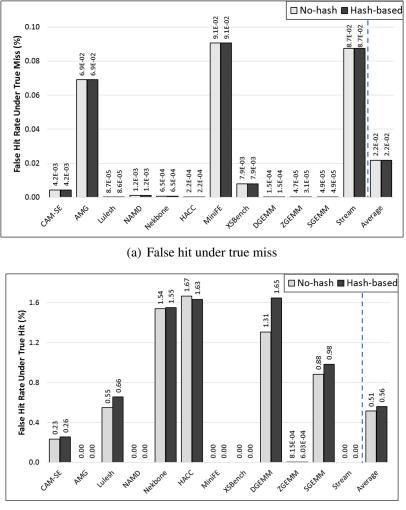

| Figure 4.5:                               | False hit for a 3-Way 24KB set-associative instruction cache: Hash-based vs                                                                                                                                                  |                |

|                                           | No-Hash Schemes                                                                                                                                                                                                              | 50             |

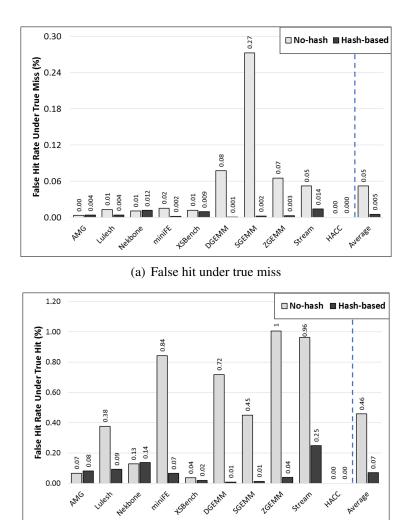

| Figure 4.6:                               | False hit for a 4-way 128KB data cache: Hash-based vs No-Hash Schemes                                                                                                                                                        | 52             |

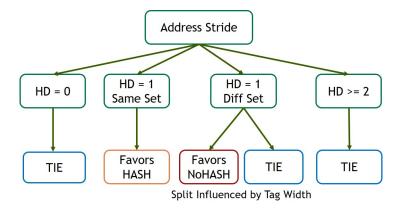

| Figure 4.7:                               | Address stride distribution analysis, based on Hamming distance (HD)                                                                                                                                                         | 50             |

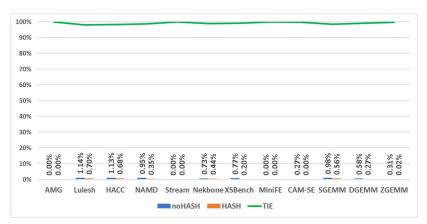

| Figure 4.8:                               | between tag portions of consecutive addresses                                                                                                                                                                                | 53<br>54       |

| 1 iguie 4.0.                              |                                                                                                                                                                                                                              | 54             |

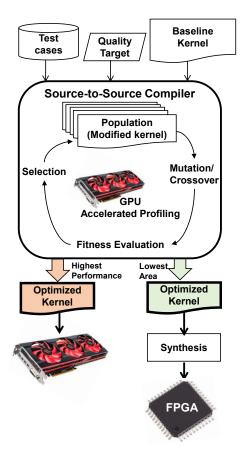

| Figure 5.1: | Overview of GRATER, our design optimization workflow.                             | 66  |

|-------------|-----------------------------------------------------------------------------------|-----|

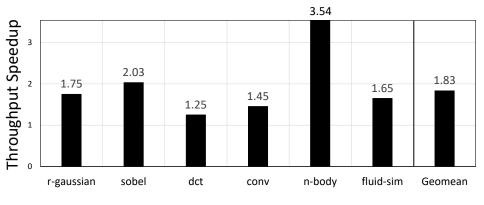

| Figure 5.2: | Throughput speedup with GRATER on FPGA                                            | 75  |

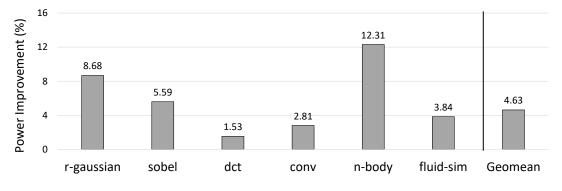

| Figure 5.3: | Power improvement with GRATER on FPGA.                                            | 76  |

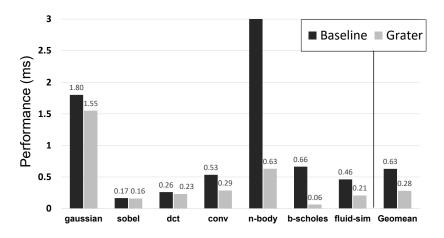

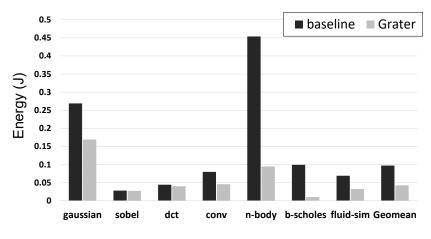

| Figure 5.4: | Performance speedup with GRATER on GPU                                            | 77  |

| Figure 5.5: | Energy improvement with GRATER on GPU.                                            | 77  |

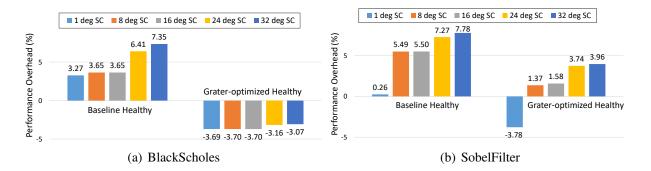

| Figure 5.6: | Performance overhead comparison for GPU core isolation on Radeon 580rx            |     |

|             | for the baseline healthy kernel and grater-optimized healthy kernel ((a) b-       |     |

|             | scholes and (b) sobel) when number of degraded SCs are changed from 1 to          |     |

|             | 32                                                                                | 79  |

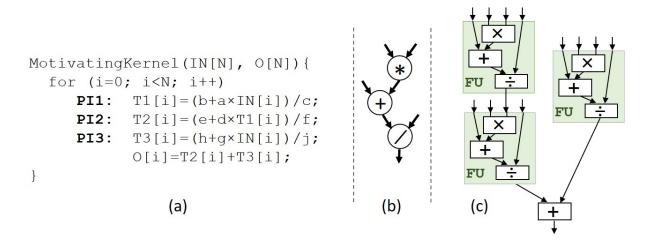

| Figure 6.1: | (a) example code, (b) its pattern, (c) the design generated for this program .    | 87  |

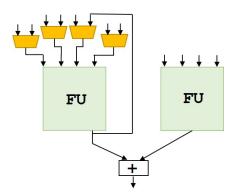

| Figure 6.2: | Design 1. Timing-aware resource sharing for baseline design of Fig 6.1            | 87  |

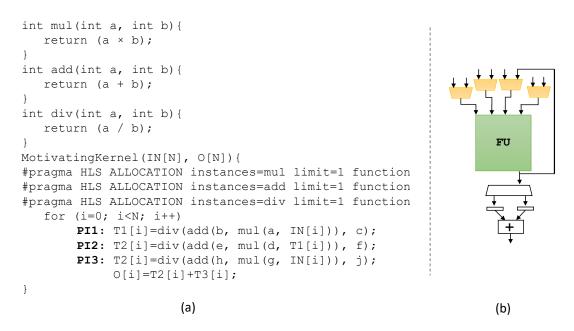

| Figure 6.3: | (a) Code for <i>Design 2</i> . Aggressive resource sharing for baseline design of |     |

|             | Fig 6.1, (b) the design generated for this program                                | 88  |

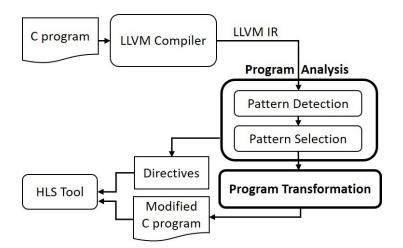

| Figure 6.4: | Overview of REHLS, our resource-aware regularity extraction tool                  | 91  |

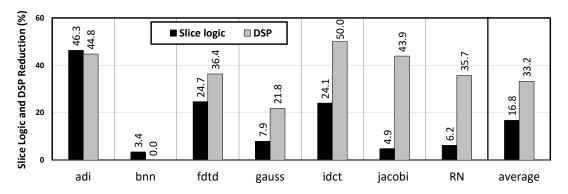

| Figure 6.5: | Relative reduction in the number of slice logics and DSP elements on Virtex       |     |

|             | 7. Numbers are in percentage                                                      | 99  |

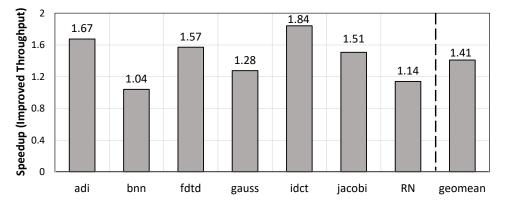

| Figure 6.6: | Throughput speedup of REHLS-optimized design (Normalized to baseline)             | 101 |

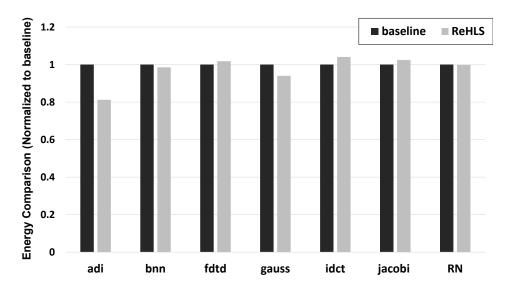

| Figure 6.7: | Energy comparison of REHLS-optimized design (Normalized to baseline)              | 102 |

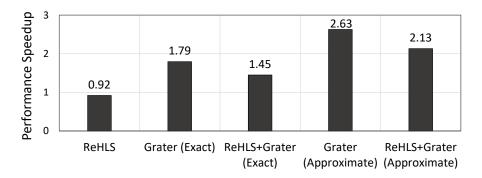

| Figure 6.8: | Impact of both REHLS and GRATER on Performance                                    | 103 |

| Figure 7.1: | The typical convolutional neural network model structure                          | 110 |

| Figure 7.2: | The structure of the LBPNet for MNIST.                                            | 111 |

| Figure 7.3: | System-level architecture for LBPNet accelerator.                                 | 113 |

### LIST OF TABLES

| Table 3.1:                                                          | Parameters for the Naive Kernels                                                                                                                                                                             | 25                     |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Table 4.1:         Table 4.2:         Table 4.3:         Table 4.4: | Benchmark DescriptionHit rate comparison for No-hash and Hash-based schemesFalse Hit Probability Sensitivity to Tag Width (Associativity=3)False Hit Probability Sensitivity to Associativity (Tag Width=20) | 48<br>51<br>56<br>56   |

| Table 5.1:                                                          | Resource utilization of multiply operation for different types/bitwidth on Virtex7 FPGA                                                                                                                      | 63                     |

| Table 5.2:                                                          | Resource utilization for <i>Baseline</i> and GRATER-optimized kernels on StratixV<br>FPGA                                                                                                                    | 74                     |

| Table 6.1:<br>Table 6.2:<br>Table 6.3:<br>Table 6.4:                | Resource utilization and timing comparison for Fig 6.1, 6.2 & 6.3 Benchmark Descriptions                                                                                                                     | 88<br>98<br>100<br>104 |

| Table 7.1:<br>Table 7.2:                                            | The structure of LBPNet for MNIST.                                                                                                                                                                           | 112                    |

| Table 7.2:<br>Table 7.3:                                            | Latency (number of clock cycles) break-down for different layers and total<br>run time for MNIST dataset. The runtime is in millisecond                                                                      | 117<br>118             |

| Table 8.1:                                                          | Impact on Resource saving Vs. Labor time Vs. Scope for different proposed methods targeting hardware resource optimization                                                                                   | 122                    |

#### ACKNOWLEDGEMENTS

This long venture of my PhD journey is a combined effort of many characters, including the scholars whom I had the privilege to meet and work with, family members who constantly supported me, and friends who were always accessible and guided me through this journey. All of them played a crucial role in one or another step of this journey and helped me to achieve my goals. None of my achievements, if any, would have been possible without the unconditional support and help from them. This thesis would therefore be incomplete without expressing my gratitude to all of them.

First and foremost, I owe immense gratitude to my advisor Professor Rajesh Gupta, who gave me the opportunity to conduct the research in an extremely free environment. I dedicate my deepest gratitude for his support, guidance, and encouragements.

I would also like to thank my committee members, Professor Ryan Kastner, Professor Sorin Lerner, Professor Dean Tullsen, and Professor Patrick Mercier for their advice and comments in my dissertation. I would also like to give special thanks to Dr. Nirmal Saxena and Dr. Philip Shirvani, who have given me tremendous advice and support while I was at NVIDIA.

I am blessed to be surrounded by so many good friends and colleagues during my Ph.D. time. I would like to thank many research colleagues who have made this dissertation possible. I would like to thank Abbas Rahimi for his mentorship during my first year. I dedicate especial thanks to Moein Khazraee for our brainstorming discussions, helps, and his encouragements. I thank my colleagues and friends Vahideh Akhlaghi, Jeng-Hau Lin, Manish Gupta, Dhiman Sengupta, Alex Forencich, Nishant Bhaskar, Jason Koh, Omid Assare, Armita Ardeshiricham, Alireza Khodamoradi, Quentin Gautier, Bahram Kherandmand, Shelby Thomas, Michael Barrow, Mohsen Imani, and Xun Jiao for their helps, feedbacks, and our discussions.

Finally, I would like to thank my parents, Homa Rahimi and Kazem Lotfi, for being strong pillars of support throughout my life. They have always encouraged me to explore and pursue opportunities, go above and beyond my potential, think big, and never give up. This dissertation has all been made possible by their infinite patience. I dedicate special thanks to my lovely sister and brother, Atefeh Lotfi and Ali Lotfi, for their endless kindness and encouragements.

The material in this dissertation is based on the following publications.

Chapter 3 contains reprints of Atieh Lotfi, Abbas Rahimi, Luca Benini, and Rajesh Gupta, "Aging-Aware Compilation for GPGPUs", *ACM Transactions on Architecture and Code Optimization (TACO)*, 2015. The dissertation author is the primary author of this paper.

Chapter 4 contains reprints of Atieh Lotfi, Nirmal Saxena, Richard Bramley, Paul Racunas, Philip Shirvani, "Low Overhead Tag Error Mitigation for GPU Architectures", *International Conference on Dependable Systems and Networks (DSN)*, 2018. The dissertation author is the primary author of this paper.

Chapter 5 contains reprints of Atieh Lotfi, Abbas Rahimi, Amir Yazdanbakhsh, Hadi Esmaeilzadeh, Rajesh Gupta, "GRATER: An Approximation Workflow for Exploiting Data-Level Parallelism in FPGA Acceleration", *Proc. IEEE/ACM Design, Automation, and Test in Europe (DATE)*, 2016. The dissertation author is the primary author of this paper.

Chapter 6 contains reprints of Atieh Lotfi, and Rajesh Gupta, "ReHLS: Resource-Aware Program Transformation Workflow for High-Level Synthesis", *IEEE International Conference on Computer Design (ICCD)*, 2017. The dissertation author is the primary author of this paper.

Chapter 7, contains reprints of Jen-Hau Lin, Atieh Lotfi, Vahideh Akhlaghi, Zhuowen Tu, and Rajesh Gupta, "Accelerating Local Binary Pattern Networks with Software-Programmable FPGAs", *Proc. IEEE/ACM Design, Automation, and Test in Europe (DATE)*, 2019. The dissertation author is the primary co-author of this paper.

VITA

| 2008 | Bachelor in Computer Engineering,<br>University of Tehran                                              |

|------|--------------------------------------------------------------------------------------------------------|

| 2012 | Masters in Computer Engineering,<br>University of Tehran                                               |

| 2017 | Intern, NVIDIA Corporation,<br>Santa Clara, California                                                 |

| 2018 | Doctor of Philosophy in Computer Science (Computer Engineering),<br>University of California San Diego |

- Jeng-Hau Lin, Atieh Lotfi, Vahideh Akhlaghi, Zhuowen Tu, and Rajesh K. Gupta, "Accelerating Local Binary Pattern Networks with Software Programmable FPGAs", *Design, Automation & Test in Europe (DATE)*, 2019.

- Atieh Lotfi, Nirmal Saxena, Richard Bramley, Paul Racunas, Philip Shirvani, "Low Overhead Tag Error Mitigation for GPU Architectures", *Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN)*, 2018.

- Atieh Lotfi, and Rajesh K Gupta, "ReHLS: Resource-Aware Program Transformation Workflow for High-Level Synthesis", *IEEE International Conference on Computer Design* (*ICCD*), 2017.

- Atieh Lotfi, and Rajesh K Gupta, "RxRE: Throughput Optimization for High-Level Synthesis using Resource-Aware Regularity Extraction (Abstract)", *Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays(FPGA)*, 2017.

- Tutu Ajayi, Khalid Al-Hawaj, Aporva Amarnath, Steve Dai, Scott Davidson, Paul Gao, Gai Liu, Atieh Lotfi, Julian Puscar, Anuj Rao, Austin Rovinski, Loai Salem, Ningxiao Sun, Christopher Torng, Luis Vega, Bandhav Veluri, Xiaoyang Wang, Shaolin Xie, Chun Zhao, Ritchie Zhao, Christopher Batten, Ronald G Dreslinski, Ian Galton, Rajesh K Gupta, Patrick P Mercier, Mani Srivastava, Michael B Taylor, Zhiru Zhang, "Celerity: An

Open-Source RISC-V Tiered Accelerator Fabric", Symp. on High Performance Chips (Hot Chips), 2017.

- Atieh Lotfi, Abbas Rahimi, Amir Yazdanbakhsh, Hadi Esmaeilzadeh, and Rajesh K. Gupta, "Grater: an approximation workflow for exploiting data-level parallelism in FPGA acceleration", *Design, Automation & Test in Europe (DATE)*, 2016.

- Atieh Lotfi, Abbas Rahimi, Luca Benini, and Rajesh K. Gupta, "Aging-Aware Compilation for GPGPUs", ACM Transactions on Architecture and Code Optimization (TACO), 2015.

- Atieh Lotfi, Abbas Rahimi, Hadi Esmaeilzadeh, Rajesh K. Gupta, "SqueezCL Squeezing OpenCL Kernels for Approximate Computing on Contemporary GPUs", Approximate Computing Workshop, 2015.

- Mehdi Semsarzadeh, Atieh Lotfi, Mahmoud Reza Hashemi, Shervin Shirmohammadi, "A fine-grain distortion and complexity aware parameter tuning model for the H. 264/AVC encoder", Signal Processing: Image Communication, 2013.

- Atieh Lotfi, Arash Bayat, Saeed Safari, "Architectural vulnerability aware checkpoint placement in a multicore processor", IEEE 18th International On-Line Testing Symposium (IOLTS), 2012.

#### ABSTRACT OF THE DISSERTATION

### Fault-susceptibility Mitigation and Efficient Use of Resources in Programmable Hardware Accelerators

by

### Atieh Lotfi

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2018

Professor Rajesh K. Gupta, Chair

Faced with the exponential growth in computing requirements, programmable hardware accelerators, such as GPUs and FPGAs, are becoming increasingly popular in high performance computing systems. In deference to energy efficiency and scalability challenges in these systems, it is crucial to efficiently use hardware resources while maintaining their reliability requirements. To meet system reliability requirements, traditional methods add redundancy in hardware or software. However, these redundancy-based error mitigation techniques suffer from inefficient use of hardware resources. The goal in this dissertation is to devise low-overhead approaches to mitigate the fault-susceptibility of hardware accelerators, and use their available resources efficiently.

For fault-susceptibility mitigation in GPU accelerators, this dissertation proposes a software-based approach that enables isolation of faulty components through task migration. Due to lack of configurable scheduler for GPUs, the proposed solution makes use of *introspective kernels* to enable effective task migration for isolating faulty components. This technique has very low overhead in terms of performance and energy and improves the accelerator lifetime and overall system cost. For FPGA accelerators, faulty component isolation is handled with a directive-based method through the synthesis tool.

This dissertation presents practical optimization methods to efficiently use the available resources on programmable hardware accelerators. These optimizations are performed at different levels of abstractions that are useful for GPUs and FPGAs, and the trade-offs among them are elaborated. For GPUs, optimization opportunities are explored in hardware-level and source-level. For FPGAs, optimizations are studied at the compiler-level, source-level, and algorithm-level. These optimization methods seek to remove unnecessary redundancies from program or hardware. This dissertation demonstrates *practical* and *efficient* approaches for utilizing fault-susceptible programmable hardware accelerators and improving their efficiency in terms of both cost per performance and energy.

# Chapter 1

# Introduction

With the end of the classical Dennard scaling, the benefits from continued transistor scaling are diminishing due to energy and power constraints, leading to prevalence of "dark silicon", that is, chips portions that must remain dark or unused due to limits of energy use or thermal limits [47] [40]. The dark silicon phenomenon documents diminishing returns in per-transistor speed and energy efficiency with increases in chip sizes. Further, the demand of compute and power intensive tasks are rapidly growing while the general-purpose CPU platforms are not able to keep pace with this increasing demand due to slowdown in scaling. Faced with the large growth in computing requirements and the dark silicon problem, chip designers have started using hardware accelerators to improve performance, cost, and energy efficiency. Among these, programmable hardware accelerators such as graphic processing units (GPUs) or field programmable gate arrays (FPGAs) have been gaining popularity.

For a long time GPUs were used for graphics and gaming purposes, and FPGAs were used for ASIC prototyping and base stations. However, these programmable accelerators are now being used in new systems ranging from embedded systems and IoT to high-performance computing (HPC) and data centers. These new systems create new challenges for these accelerators. The first challenge is that the penalty of inefficient use of their resources becomes more severe, and it becomes more important to efficiently use hardware resources. The second challenge is that the probability of fault occurrence is increased due to their use at a large scale while there are no error mitigation methods for handling permanent faults in these accelerators.

Regarding the first challenge, these accelerators have complicated programming model. Developing a parallel program for GPUs that considers regular memory access patterns and suitable memory managements is complicated. Moreover, writing a program for FPGAs either by hardware description languages or through the use of high-level synthesis tools requires hardware-aware programming. If our programs are not hardware-friendly, we lose the benefits of using hardware accelerators. In addition, we have seen fast-paced development of code by software developers, e.g. in cloud applications, resulting in codes that are not optimized and tuned for the target platform. Executing an un-optimized code on these accelerators might result in inefficient use of their resources. Therefore, there is a need for automatic tools to further optimize the code and avoid inefficiencies that they may cause.

Regarding the second challenge, these accelerators have no error mitigation method for addressing permanent faults. This means that these accelerators are no longer usable if they become partially defective. This results in disposal of partially defective accelerators which is costly. Various factors such as variation in manufacturing, aging effects and wearout mechanisms, and dynamic variation such as temperature fluctuation and voltage drops may initiate and accelerate the frequency of faults and system failure [11] [53]. As we go towards smaller transistor technologies making a perfectly working die becomes even harder which results in increasing costs of chips by a large factor [62]. In fact, hardware resource failures and down times is a critical concern for large scale high-performance computing platforms, as they adversely affect the performance and quality of service in a system [104].

Since reliability is an important factor in hardware design, different approaches exist to detect and recover from failure. Several approaches add redundancy to perform recovery from failures. These methods incorporate extra components, instructions, or data in the design of a system so that the functionality is not impaired in the event of a failure. Possible ways to build a redundantly reliable system include:

2

- 1. Hardware redundancy: These methods replicate all or some part of the hardware device. For example, triple modular redundancy (TMR) [78] is one technique in which the critical components are replicated three times and the results are voted to produce the output. The redundant component can be active at all time and a voter decides the correct output (static hardware redundancy), or the spare components become activated upon the failure of a currently active component (dynamic hardware redundancy). Even though hardware-based redundancy approaches can detect and correct errors fast, they are very expensive in terms of their impact on circuit area, energy, and cost of the system. In addition, for memory elements, redundancy is augmented into data bits so that an error in the data can be detected or corrected. Example of these techniques are using parity bits [54] or error correction codes [34].

- 2. Software redundancy: These methods perform redundant code execution. For example, SWIFT [98] executes each instruction twice on replicated inputs and compares their outputs. In N-Version programming [36], *N* independently designed versions of a software is executed either sequentially or in parallel and their results are compared by a decision algorithm. While software-based techniques can be more flexible than hardware-based approaches, they have considerable cost in terms of performance and energy efficiency [58].

Hardware and software redundancy add significant overhead on cost, performance, and energy. These approaches repeat a part of computation and this increases the overall system energy consumption. Applying redundancy-based methods are necessary for safety critical applications such as autonomous driving and avionics, but they are not desirable in most other systems. For example, energy efficiency in embedded systems or performance and scalability requirements in high performance computing data centers can not afford these overheads [72].

An alternative approach is core isolation and task migration. This approach works for systems that have a number of components that can work in parallel. Here, the faulty core is isolated, and the tasks running on a faulty core are migrated to another non-faulty one as soon as a failure is predicted or detected [72]. This approach isolates the faulty component and makes use of other available functional resources in the system to perform its task. For example, [91] [90] [108] [56] propose dynamic workload allocation policies to mitigate core failures in multicore architectures. In these works, the operating system effectively changes workload scheduling method to isolate a faulty core and distribute its tasks to other available cores in the system. In general, this approach has lower overhead than redundancy-based approach, since it does not have expensive redundancies, there is no task duplication that needs to be run at all time, and the fault-affected hardware is still being used. Naturally, this approach is only possible if adequate hardware resources are still available.

In fact, both GPUs and FPGAs are great targets for implementing isolation due to their architectures. GPU architecture contains many parallel cores that run in the Single Instruction Multiple Data (SIMD) fashion. FPGA provides a customizable architecture containing many primitive cells that can be configured through placement and routing. For FPGA accelerators, the synthesis tool allows isolation of faulty components with fine-grained granularity. However, due to lack of operating systems and configurable scheduler for GPUs, core isolation and task migration is not possible for this platform. This result in disposal of partially defective accelerators, which is expensive in terms of cost and replacement time especially in data centers and IoT devices. Enabling error mitigation on accelerators can open up opportunities to use hardware which were considered unusable due to their conditions for a longer time; leading to reducing waste of available hardware resources, increasing the lifetime of defective hardware, as well as reducing the manufacturing cost by accepting more range of defective hardware. Reducing cost while keeping a system energy efficient can significantly help with today's exponentially growing computational requirements.

In this dissertation, we address the aforementioned two challenges. First, we add the missing fault mitigation and isolation support for these accelerators. We develop automatic software-level and directive-based methods to implement isolation and task migration with very low overhead in terms of performance and energy. By isolating faulty components, we can make

use of other available components in the hardware accelerator, and improve the cost and lifetime of hardware. Moreover, efficient use of hardware resources becomes more advantageous in the new use cases of these accelerators. To improve efficiency of using GPU and FPGA accelerators, we perform optimizations in different levels of abstractions that are useful for each of them. For GPUs, we seek opportunities to perform optimization in hardware-level and source-level, to remove unnecessary overheads in hardware or optimize the program running on GPU. For FPGAs, we target optimizations in compiler-level, source-level, and algorithm-level. These optimizations either improve efficiency of high-level synthesis design process, tune the program for hardware, or use a hardware-friendly algorithm and implementation.

To improve efficiency of using GPU accelerators, we seek methods to remove unnecessary redundancy in hardware and software. For removing unnecessary hardware redundancy, we perform a case study to seek opportunities to remove some reliability-related redundancy and replace them with a more efficient design choice. Traditionally, memory structures are augmented with reliability-related redundancy in order to become resilient to errors, which results in area and energy overhead. We study the necessity of these redundancies and the resiliency of unprotected caches in GPU. We further study the usefulness of a very low overhead error mitigation to replace parity bits in some structures. For removing unnecessary redundancy in software, we perform automated optimization of programs that are developed for GPUs. Especially, with the growth in the number of software developers who are not familiar with low-level hardware details, there exists unnecessary computations in these programs. We develop a source-to-source compiler that selectively tunes the bitwidth of variables and operations in a program, and results in efficient use of hardware resources. This optimization is also useful for FPGA accelerators, in which the automatic transformation is done on the high-level design specification. In addition to this optimization, we present two more optimization methods for efficient use of FPGA resources. For improving the efficiency of synthesis results through high-level synthesis (HLS) process, we perform automated transformation in the design specification through compiler and enable task migration and resource sharing without any modification in the HLS tool. This

transformation results in more efficient use of FPGA resources. We also present a case study that uses algorithmic modification to increase efficiency of using FPGA hardware accelerators. All presented approaches can be used to improve efficiency in either a fully functional or faulty hardware accelerator.

# **1.1** Dissertation Organization and Contributions

In this dissertation, we focus on addressing the two important challenges that are caused by the new use cases of programmable accelerators. We present methods that enable fault mitigation through isolation for GPUs and FPGAs. We further present optimization techniques that result in more efficient use of hardware resources for these commodity programmable accelerators. This dissertation has two main parts. In the first part, we focus on presenting fault mitigation and optimization methods for efficient use of resources in GPU accelerators. First, we propose an efficient method to enable isolation and task migration on GPU accelerators, with very low overhead in terms of performance and energy. Then, we study and propose techniques for more efficient utilization of resources using hardware and software optimizations. The second part, focuses on optimization for FPGA accelerators. We target two optimization approaches that automatically modifies the FPGA design specification. The first approach removes unnecessary computations in the design, and the second one exploits resource sharing opportunities by regularity extraction. We also study the effect of algorithmic optimization on the efficiency of FPGA accelerators. Figure 1.1 illustrates the scope and organization of this dissertation.

The contributions of this dissertation are:

- 1. Introducing primitive cell isolation for defective FPGAs by a directive-based approach,

- 2. Enabling component isolation and task migration for faulty GPUs through compiler,

- 3. Automatic source-level optimization and program transformation for programmable accelerators that results in better resource utilization in hardware,

Figure 1.1: Dissertation organization.

- Enabling automatic task migration to improve resource efficiency and throughput of HLS-based FPGA design,

- 5. Presenting and evaluating optimizations in different levels, from hardware to algorithm, for efficient use of hardware resources, and analyzing their trade-off and impact.

The organization of this dissertation is as follows:

First, we start by providing background information on GPU and FPGA architecture and design flow in Chapter 2. We also discuss how we can guide the synthesis tool to enable isolation of faulty primitives in FPGAs through a directive-based approach.

For GPU platforms with faulty components, we enable faulty components isolation and task migration in the granularity of stream cores using a just-in-time compilation method. We propose innovations in the static compiled code by introducing the notion of *introspective kernels*. An introspective kernel adaptively monitors the health of a GPU device and triggers runtime workload reallocation scheme to migrate tasks on healthy stream cores. After detection of faulty stream cores (SCs), a just-in-time compilation process replaces the introspective kernel with a *healthy* kernel that responds to the specific health state of the GPU device. This method can efficiently isolate faulty stream cores, and migrate their tasks to other functional cores. We further show the benefit of this approach for a GPU with aged stream cores. By shifting the workload from aged stream cores to healthy ones, the faulty hardware components are gradually healed. This results in efficient use of hardware components and increases the device lifetime

which reduces the overall hardware cost. We discuss this approach in Chapter 3.

As mentioned earlier, it is becoming more important to use resources on programmable hardware accelerators in a more efficient way. In the rest of dissertation, we propose methods at different levels to efficiently use the available hardware resources. We perform a case study to find out if there are any redundancy in the design of hardware accelerators that can be removed or replaced with a more efficient design choice. Traditionally, memory structures are augmented with reliability-related redundancy in order to become resilient to errors, which results in area and energy overhead. We evaluate the necessity of these redundancies and the reliability of unprotected caches in GPU. We further study the usefulness of a negligible overhead tag error mitigation mechanism to replace parity bits. This method distributes memory accesses more efficiently with a new cache indexing mechanism to mitigate some pathological address strides that cause error and also increases memory throughput. At a negligible impact on resiliency, this architecture eliminates the need for parity protection in the cache tag SRAM structures. This approach is general and does not induce any constraints or inflexibility to the system and can be integrated in newer generation of accelerators. This approach, which is discussed in **Chapter 4**, can be applied to any system that uses cache memory, including off-the-shelf GPUs.

We further present a source-level optimization approach that targets both GPU and FPGA. This technique identifies and removes unnecessary redundancy in programs developed for GPUs or design specifications developed for FPGAs. The unnecessary redundancy in programs might be caused by two reasons. First, these programs might be developed by software developers who are not familiar with low-level hardware details. Second, the application might have inherent tolerance to some degree of inexactness which can provide further optimization opportunity. Optimizing the program manually, especially in the second case, is not easy. In **Chapter 5**, we introduce GRATER which is a source-level automatic optimizer to reduce unnecessary computations. Our approach automatically simplifies expensive computations in the program. This results in improved performance and reduced hardware resource requirements. For example, by performing fixed-sized computations instead of floating point computations, using single-precision

floating point instead of double-precision floating point, or fewer number of bits for integer computations, GRATER can improve resource utilization and performance. These modifications are all done automatically during compile time without any programmer intervention. GRATER transcompiler is useful for both GPU and FPGA platforms. This optimization method is fast, requires no effort from user, and can be applied to any program or design specification. This approach can be applied to improve the efficiency in both fully functional and faulty hardware accelerator.

To improve the efficiency of HLS-based FPGA design, we present an approach to automatically find reuse opportunities in the design specifications with inherent regularities and implicitly change the scheduling. This approach uses compiler frontend as an independent preprocessing step to explore the design space and adds an automated source-to-source transformation step before HLS. In particular, it shows how inherent regularity in applications can be used to construct a workflow that analyzes the specification, explores the design space for resource optimization opportunity, and transforms the program accordingly. The transformed program can be synthesized using the HLS tool. This approach, which is explained in **Chapter 6**, takes advantages of resource sharing opportunities to reduce resource utilization while keeping latency and energy efficiency similar to the original design.

Moreover, we perform a case study to examine the impact of algorithmic modification to increase efficiency of FPGA accelerators. For the growing field of deep neural network applications, in **Chapter 7**, we show resource saving and power reduction advantages of using a more hardware-friendly algorithm and its harware-aware implementation over off-the-shelf convolutional neural networks. This approach, despite its longer development time, is the most effective solution for improving resource utilization of hardware accelerators. However, this approach is cumbersome compared to automated source-level and compiler-level techniques. Moreover, an algorithmic optimization of this kind does not necessarily work for other applications. This approach indicates that using hardware-friendly algorithms improves the efficiency, in exchange for high development cost. In fact, this is the most effective approach for efficient use of hardware resources, since we are considering the full stack from algorithm to hardware.

Finally, **Chapter 8** concludes the dissertation and gives future directions. We argue that the use of our source-level and compiler-assisted optimization alongside the isolation and task migration techniques is a *general* approach that can be *easily* applied to fault-susceptible commodity programmable hardware accelerators and improve their efficiency in terms of both cost per performance and energy.

# Chapter 2

# Background

This section introduces some preliminary concepts and definitions useful to briefly build a background for this work. First, we provide background information on FPGA architecture and design flow. Further, we discuss the directive-based method to enable isolation of faulty primitives in FPGAs. Then we discuss OpenCL programming model which can be used for both FPGA and GPU accelerators. Furthermore, we briefly discuss a sample GPU architecture that we mostly used in the dissertation.

### 2.1 Background on FPGA and Synthesis Process

Field Programmable Gate Array or **FPGA** is a reconfigurable hardware platform which can be configured after manufacturing. FPGAs are composed of programmable logic and memory blocks which are connected using programmable interconnects. FPGA reconfiguration allows it to perform a wide variety of complex tasks. The basic structure of an FPGA is composed of elements like look-up table (LUT) (which performs logic operations), Flip-Flop (FF) (register element to store the result of operations), memory blocks (BRAM), and digital signal processing (DSP) blocks that perform specific functions. The type and number of elements available on an FPGA depends on the vendor, family, and specific device. FPGA is mainly an island of elements arranged in a two dimensional grid of sections called *tiles*. There are several different types of tiles: CLB, DSP, BRAM, and interconnect. CLBs (Configurable Logic Blocks) are the resources for implementing logic on the FPGA. A CLB occupies a single tile on the device and is connected to a switch matrix to access the general routing structure. Each CLB is comprised of number of interconnected slices. Many of the tiles can be broken down into smaller components called primitive types. Primitive types are the smallest unit on FPGA. Each primitive is identified by its (X,Y) location on the device (e.g SLICE\_X39Y53, DSP48A\_X1Y7). One example of a primitive type found within a tile is a slice. For example, in our target FPGA, each slice is made up of two LUTs, two storage units, wide-function multiplexers, carry logic, arithmetic gates, and routing interconnect. Another primitive type is DSP slice. Each slice supports many independent functions, including multiplier, multiplier followed by an adder, or barrel shifter. The slices can also be connected together to form wide math functions. These function could be implemented using more general logic resources resulting in higher performance, and efficient device utilization.

**High-Level Synthesis** (HLS), also known as behavioral synthesis or algorithmic synthesis, is a design process that given a high-level behavioral specification of a digital system and a set of constraints, automatically generates a Register-Transfer Level (RTL) structure that implements the desired behavior [79]. Different HLS tools use different high-level behavioral specification languages like C, C++, SystemC, or OpenCL, which are untimed or partially timed algorithmic descriptions, to describe the design. This description is transformed to a fully-timed and bit-accurate RTL implementation by the HLS flow. HLS process usually consists of a number of tasks which are done in different steps. HLS front-end performs lexical processing, control and data flow analysis, and optimizations in order to build and optimize an intermediate representation to be used in the subsequent steps. In HLS synthesis step, the design constraints. By *scheduling, resource allocation*, and *resource binding* the number and type of hardware

modules to be used is established and each instruction is scheduled and assigned to one of the hardware resources that can execute it. Finally in the last step of HLS, an RTL implementation is generated containing control and steering logic circuits.

Logic Synthesis and Implementation is the process to synthesize the RTL design and implement the final design on FPGA. Synthesis optimizes a design for a specific implementation target, such as a FPGA chip or a semi-custom ASIC chip. The outcome of high-level synthesis is typically a structural netlist. The netlist contains the primitives on the FPGA and the connections between them. Implementation is the process of taking the previously generated netlist and preparing the design to be configured onto a specific device. It consists of a number of steps as follows. Mapping is the process of pairing the generic logic to the specific primitives (slices, BRAMS, etc.) in the target FPGA. After mapping, placement and routing is performed. During placement, the placer assigns each primitive to a physical site on the device. Then it routes, or connects, the components using the wires in the FPGA as defined by the netlist. Placement and routing typically use sets of heuristics to achieve optimization objectives in an expeditious manner. A placement takes as it inputs the netlist, together with a device map showing the location of each of its functional units, in order to select a legal location on the FPGA for each functional block in the netlist, such that the routing of these blocks is optimized. In general, synthesis tools allow some freedom in the users preference of the placement of circuit. The design is then passed on to the bitstream generator which generates all the information needed to configure a design onto a device.

## 2.2 Isolating faulty primitives in FPGA

We earlier stated that faulty component isolation on FPGA is straightforward, here we describe how it can be done. We employ a mechanism to periodically detect permanent faults on FPGAs using testing methods [37]. If a permanent fault is detected, the system identifies and reports the exact location of the fault [82, 89]. As soon as the location of the faulty primitive

is known, we can isolate it on FPGA, and perform placement and route again. In order to isolate the faulty block in FPGA, we can use the capability that the synthesis tool provides us to include specific primitive cells in the design. To make sure our design is not mapped to the faulty primitive, we can force the placement process to use it for a dummy operation that we intentionally add to the design. For example, in Xilinx synthesis tool, to isolate a faulty primitive, we define a dummy element in the RTL design and put a **KEEP** directive on it. This way the synthesizer will keep this dummy element in the design despite the fact that it is not connected anywhere and thus would be normally removed by synthesis tools. We then force this dummy element to be placed on the faulty primitive using **set\_property LOC** command in the constraint file. This way none of our blocks in the design is placed on that faulty primitive. This process can be easily automated by generating a simple script.

### **2.3 OpenCL Execution Model on GPU and FPGA**

OpenCL is a standard framework for developing parallel programs that execute across heterogeneous platforms consisting of GPUs and FPGAs. OpenCL uses a subset of ISO C99 with added extensions for supporting data and task-based parallel programming models. The programming model in OpenCL comprises of one or more device kernel codes in tandem with the host code. The host code typically runs on a CPU and launches kernels on other compute devices like the GPUs and/or FPGAs through API calls. These kernels execute on compute devices that are a set of compute units (CUs), each comprising of multiple processing elements having ALUs. Each instance of the OpenCL kernel is called a work-item. The work-items execute on a single processing element and exercise the ALU. The OpenCL platform model from the programming model to the framework of the compute devices is illustrated in Fig. 2.1. To launch a kernel, the programmer determines a group of work-items to execute on the device which is referred as an ND-Range. A group of work-items, typically 256 work-items, form a work-group that shares a local memory space. Work-items from one work-group cannot access the local memory of other work-groups. Work-items are further grouped into wavefront which is composed of 64 work-items, as the unit of scheduling.

Figure 2.1: OpenCL platform model.

GPUs and FPGAs exploit data-level parallelism differently. GPUs are single-instruction multiple-data (SIMD) devices that exploit data-level parallelism: they group processing elements in a CU to perform the same operation but on their own individual data. On the other hand, FPGAs exploit pipeline parallelism in a CU where different stages of the instructions are applied to different work-items concurrently. FPGAs can further improve the performance benefits by creating multiple copies of the kernel pipelines (synthesized version of an OpenCL kernel). As the kernel pipelines can be executed independently from one another, the performance would scale linearly with the number of copies created owing to the data-level parallelism model supported by OpenCL. Altera OpenCL SDK [1] and Xilinx SDAccel [6] allow programmers to use high-level OpenCL kernels to generate an FPGA design with high performance per Watt [19].

## 2.4 GPU Architecture

GPUs are large parallel structure of processing cores. The original intent when designing GPUs was to use them exclusively for graphics rendering that often carry same operations on multiple data items and the processed data is usually destined for termination on a screen buffer. However, the massive parallelism of compute operations was quickly recognized as useful beyond large scale graphics rendering, into solving scientific computational problems. To serve these needs, GPUs evolved into General Purpose GPUs or GP-GPUs that feature an instruction set sufficient to carry one entire computation without the need for a "main" general purpose processor to be GPU would normally be an accelerator. In the big picture, the GPU consists of many small processors and has its own data storage hardware. The main GPU vendors, NVIDIA and AMD, use different terminologies for their structures. In this dissertation, we mainly use an AMD GPU for our experiments, expect from chapter 4 that we target an NVIDIA GPU. Since the high-level architecture of GPUs are similar, we introduce our target GCN-based AMD GPU architecture here.

#### 2.4.1 AMD GCN architecture

AMD Graphics Core Next (GCN) architecture is a RISC SIMD architecture that replaces the older VLIW SIMD architecture. In this dissertation, we target Radeon HD 580 RX (Ellesmere) device which has 36 compute units (CUs). The block diagram of this architecture is shown in Fig. 2.2. Every CU has four SIMD units and a wavefront scheduler. Each of the four SIMD units can be scheduled independently. The CU has its own hardware scheduler that is able to assign wavefronts to available SIMD units with limited out-of-order capability to avoid dependency bottlenecks. Each SIMD unit has 16 stream cores (SCs); therefore, it brings a total number of 64 SCs per CU and 2304 SCs per Ellesmere device. The CU has a scratchpad memory, where OpenCL local memory is allocated. In these GPUs, sixteen work-items are executed in SIMD fashion, and the whole wavefront (64 work-items) is executed over four clock cycles.

Figure 2.2: Block diagram of the Radeon GCN architecture

Therefore, a work-group is comprised of up to 4 wavefronts that share the execution resources in a CU. To manage these resources, a wavefront scheduler dynamically selects wavefronts for execution. For efficient hardware utilization, the work-item count should be an integer multiple of 64. Each CU executes one or more work-groups at a time. When the CPU launches an OpenCL kernel into the GPU, the work-groups are mapped into the CUs until all of them reach to their maximum occupancy. When a work-group finishes execution, the associated CU allocates a new waiting work-group, and this process is repeated until the entire ND-Range is executed.

# **Chapter 3**

# **Enabling Task Migration to Isolate Corrupted Cores in GPUs**

Graphic Processing Units (GPUs) offer high computational throughput using hundreds of parallel cores. As technology scales down and device dimensions near atomic scales, manufacturing features are no longer as "chiseled" as in larger dimensions. This makes devices increasingly more susceptible to different types of errors occurred during manufacturing or lifetime of device. In this chapter, we present a software-based methodology to isolate faulty units and mitigate hardware failures of GPUs. This method enables task migration and rescheduling to quarantine the defective hardware units and ensure correct execution. The compilation strategy along with proposed *introspective* and *healthy* kernels can adaptively shift the workload from less reliable units to more reliable units. By isolating defective units, we can make use of other available units and improve the cost and lifetime of the GPU. We evaluate the effectiveness of the proposed method for various OpenCL kernels on AMD GPU architectures.

# 3.1 Introduction

Due to many factors such as transistor scaling, low voltage, and high frequency, todays processors are more than ever subject to fallouts. Defects can happen during the manufacturing process, some of which might not be detected during factory testing and might progressively be detected during processing. Variability of process parameters in conjunction with aging caused by non-uniform stress is also one source of failure for GPUs with thousands of cores [12]. If a core in GPU gets erroneous, it should no longer perform any task, or otherwise the GPU cannot ensure functional correctness. In fact, the corrupted core should be isolated and its workload should be assigned to other functional cores. However, scheduling and allocation is embedded in GPU hardware, and it can not be modified. Therefore, with current GPUs, the device can no longer be used in case any error is detected.

Parallel execution in GPUs provides an important ability to reallocate workloads in response to the health state of the system. To increase the lifetime of GPU, we introduce a software approach to enable rescheduling and faulty core isolation. Accordingly, we make the following main contributions:

- We propose innovations in the static compiled code by introducing the notion of *introspective kernels*. An introspective kernel adaptively monitors the health state of a GPU device and triggers runtime workload reallocation scheme. On detection of corrupted cores, a just-in-time compilation process replaces the introspective kernel with a *healthy* kernel that responds to the specific health state of the underlying GPU device.

- To isolate the faulty cores, the healthy kernel is customized to seamlessly bypass the workload from the degraded cores by shifting the workload to the healthy counterparts. To reduce the performance penalty due to the time-multiplexing of available cores, the generated healthy kernels can be further tuned according to the number of degraded cores.

- We further show the benefit of this approach for a GPU with aged cores. By shifting the

workload from an aged core to healthy ones, the aged hardware units can be gradually healed. This reduces the overall hardware cost due to efficient use of hardware components and increases its lifetime and improves system cost.

We evaluate our technique on the the AMD graphics core next (GCN) architecture introduced in chapter 2. We implement our approach targeting OpenCL (Open Computing Language) applications. OpenCL kernels can be executed on both AMD and Nvidia GPUs [87]. Moreover, our technique can easily be extended for CUDA-based platform.

### **3.2** Detecting and locating faulty cores

Our approach can be used for isolating cores in the event of intermittent and permanent faults or prediction of timing-induced faults. This type of faults can be caused by defects or variations during the manufacturing process or aging during the lifetime of system. Due to aging, the threshold voltage of a transistor increases, which causes delay-induced failures and raises the propagation delay of logic gates over time. Due to static variation and different load on different compute units, they age with different pace. The device lifetime is limited by the most aged component in the chip.

We assume that only compute units are vulnerable as memory in GPU is protected by parity or ECC bits. The objective is to build a map indicating which core is reliable and which one is unreliable. For detecting and locating faults, we either can use functional testing techniques, or delay monitoring sensors. The health result through testing or sensors are written in memory and it can be accessed by software.

The first fault detection and location solution is to launch tests at a regular pace. This test consists of a series of benchmarks targeting error detection such as [33] combined with the ability of locating faulty unit at hardware level. The second solution is to use delay monitoring sensors. To ensure necessary observability for non-uniform aging degradation, *in situ* delay monitoring sensors with digital outputs have been proposed and validated on silicon [105]. These

sensors enable high-volume data collection to guide dynamic management schemes and warn of impending device failure. Using compact delay monitoring sensors [105] that provide  $\Delta V_{th}$ measurement with 3 $\sigma$  accuracy of 1.23 mV for a wide range of temperature, enables large scale data-collection across all the components. Test chips that has been fabricated efficiently consider multiple sensors banks containing up to total 256 NBTI sensors, hence the power overhead of laying out thousands of these sensors would only be a few hundreds of  $\mu$ W at maximum, which is a small fraction of power in our case [105].

### **3.3** Proposed methodology to quarantine faulty cores

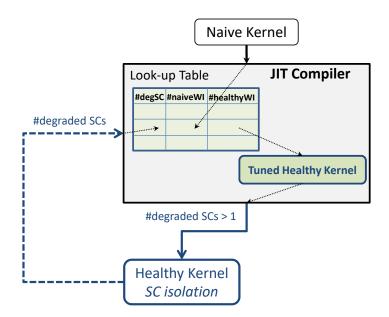

We propose a compilation strategy to enable isolation of faulty stream cores and increase the lifetime of a GPU device through adaptive workload shifting from degraded SCs to other available SCs. A run-time system needs to observe the current health state of SCs to be able to adapt the kernel code accordingly. As described in the previous section, this information is written in part of memory that can be read by software. The AMD Compute Abstraction Layer (CAL) provides an easy-to-use interface to the parallel processor arrays found in AMD GPUs. CAL, part of the AMD accelerated parallel processing software stack, abstracts the hardware details of the AMD stream processor. CAL provides a device driver library that allows applications to interact with the stream cores at the lowest-level. We re-factor the naive kernel code by inserting a custom API, check\_degradation\_status (), to access the test/sensor measurements. This new version of the naive kernel is called an *introspective kernel*, in which every work-item investigates the degradation information of its corresponding SCs. The introspective kernel can query to check health information in memory to find out whether the SC used by the work-item is faulty or not by calling check\_degradation\_status(). Figure 3.1 illustrates the overall compilation flow for adapting kernels. The introspective kernel identifies the reported amount of degradation, and consequently SC isolation might be triggered.

Figure 3.1: Kernel adaptation flow

### **3.3.1** Stream core isolation

The key idea of SC isolation method is to generate healthy kernels by modifying the normal distribution of workload so that the faulty SC is isolated. This is done by adaptively idling faulty SCs and assigning its work-items to the other healthy SCs in the same CU. For any given kernel, an introspective kernel is compiled and executed. When any of the SCs is degraded, it should be isolated and the workload should be removed from it. Therefore, for each naive kernel, a healthy version is generated in which all the work-items from those degraded SCs are moved to the other healthy SCs within the same CU. Since in an OpenCL kernel, there is no explicit mapping between a work-item and a SC, a set of extra work-items are spawned that exactly perform the same task as those on the degraded SCs. The work-items that have been assigned to any of the degraded SCs will not perform any operation.

Considering the adaptation flow in Fig 3.1, when the introspective kernel runs, each work-item checks the memory corresponding to the test result or the output of delay monitoring sensor for that SC. Fig 3.2 shows the code snippet for the introspective kernel. Besides the normal execution of the naive kernel, the introspective kernel reports the required number of

Figure 3.2: Introspective kernel

redundant work-items (*RWIs*), i.e., the number of extra work-items that a work-group requires to bypass the faulty SCs. If this number is more than zero, the just-in-time compiler compiles a healthy version of the naive kernel. The healthy kernel is launched with a different work-item count which simply can be the default work-item count for the naive kernel plus the reported redundant work-item count by the introspective kernel. In other words, for every work-item that is mapped to the degraded SC, a new redundant work-item should be generated to be mapped on another healthy SC. This is doable when the naive work-item count plus the required redundant work-item count is less than 256 (which is the limit for work-item count per work-group in Ellesmere GPUs). For cases that the new work-item count is greater than 256, the work-item count is decreased and the work-group count is increased instead in the healthy kernel. Further, the compiler is able to tune the number of work-items of a healthy kernel based on a specific degradation scenario described in Section 3.4.1.2.