# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

mm-Wave Phase Shifters and Switches

#### **Permalink**

https://escholarship.org/uc/item/1v16x7pd

#### **Author**

Adabi Firouzjaei, Ehsan

#### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

#### mm-Wave Phase Shifters and Switches

by

Ehsan Adabi Firouzjaei

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Science

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Jan M. Rabaey Professor Paul K. Wright

Fall 2010

## mm-Wave Phase Shifters and Switches

Copyright Fall 2010 by Ehsan Adabi Firouzjaei

#### **Abstract**

#### mm-Wave Phase Shifters and Switches

by

#### Ehsan Adabi Firouzjaei

Doctor of Philosophy in Engineering–Electrical Engineering and Computer Science

University of California, Berkeley

Professor Ali M. Niknejad, Chair

The ever increasing speed of transistors in mainstream silicon-based technologies made the mm-wave domain open to consumer electronic applications. Solutions that previously had to be implemented in advanced compound (III-V) technologies and were limited to high-end systems due to cost purposes, are now entering the market of low-cost consumer electronic products. Emerging mm-wave market contains various applications from extremely high data rate transceivers in "Personal Digital Assistant (PDA)" devices to automotive radar modules and to point to point links for replacing the fiber connectivity in sparse areas. Chapter one highlights the specific requirements of each application that makes it more compatible with a certain type of technology.

To have a complete mm-wave system suitable for low cost applications, a single chip or a single package solution is preferred. To achieve this goal integrated low loss transmit / receive switching structures that are highly linear should be employed. A miniature transformer-based shunt T/R switch is introduced and implemented in a standard 90nm CMOS technology. Design equations and trade-offs for such a structure are described in this thesis.

Due to a much higher free space path loss of a 60GHz signal compared to its low frequency counterparts (30dB higher loss than WiFi), and lower performances extractable from devices at these high frequencies, phased antenna array structures should be exploited to add passive antenna gains to the transceiver and help meet the link budget requirement. Fundamentals of phased antenna array structures are described and two different implementations, one through true time delay elements and the other one employing phase shifters are presented.

For wideband applications and for very large arrays intended to have a wide field of view, true time delay elements should be employed to steer the array pointing beam. This work investigates true time delay elements, and an "inductance tuning technique" is introduced which enhances the delay tunability of a synthesized transmission line while keeping its characteristic impedance constant. In most mm-wave applications, delay cells in antenna array structures can be approximated and replaced with phase shifters. Hence different types of phase shifters are studied and an active I-Q interpolating phase shifter in the RF-path is designed and implemented at 60GHz.

# **Contents**

| Li | st of I | Figures       |                                                     | iii |

|----|---------|---------------|-----------------------------------------------------|-----|

| Li | st of T | <b>Fables</b> |                                                     | vii |

| 1  | mm-     | -Wave o       | opportunities and choice of technologies            | 1   |

|    | 1.1     | mm-W          | Vave opportunities                                  | 2   |

|    |         | 1.1.1         | 60GHz connectivity                                  | 2   |

|    |         | 1.1.2         | Automotive radar                                    | 4   |

|    |         | 1.1.3         | Imaging                                             | 5   |

|    |         | 1.1.4         | Point to point links, Gigabit ethernet              | 6   |

|    | 1.2     | Standa        | ard digital CMOS vs. SiGe technology                | 8   |

|    |         | 1.2.1         | Cost of the process                                 | 8   |

|    |         | 1.2.2         | Performance                                         | 9   |

|    |         | 1.2.3         | Quantitative comparison                             | 13  |

|    |         | 1.2.4         | Choice of technology                                | 14  |

| 2  | Trar    | nsmit/R       | eceive Switching                                    | 16  |

|    | 2.1     | Anteni        | na array reuse via T/R switching                    | 17  |

|    |         | 2.1.1         | On-chip or On-package antennas                      | 17  |

|    |         | 2.1.2         | Size and loss trade-off in a transmit/receive array | 18  |

|    | 2.2     | T/R sw        | vitching configurations                             | 20  |

|    |         | 2.2.1         | Series vs Shunt switching                           | 20  |

|    |         | 2.2.2         | The transformer based shunt switching structure     | 22  |

|    | 2.3     | Design        | n equations of a transformer based T/R switch       | 24  |

|    |         | 2.3.1         | Equivalent shunt loading                            | 24  |

|    |         | 2.3.2         | Center frequency and matching                       | 26  |

|    |         | 2.3.3         | Insertion Loss                                      | 27  |

|    |         | 2.3.4         | Leakage                                             | 27  |

|    |         | 2.3.5         | Isolation                                           | 28  |

|    | 2.4     | Transf        | former based switch design example in 90nm CMOS     | 29  |

|    |         | 2.4.1         | MOS transistors performance in switch mode          | 29  |

| Bi | bliogr          | caphy                                                                         | 98       |

|----|-----------------|-------------------------------------------------------------------------------|----------|

| 6  | Con             | clusion                                                                       | 95       |

|    |                 | 5.3.2 Measurement results                                                     | 88       |

|    |                 | 5.3.1 Transformer matching networks                                           | 86       |

|    | 5.3             | mm-Wave implementation of the active phase shifter                            | 86       |

|    |                 | 5.2.3 Signal dividers / combiners                                             | 83       |

|    |                 | 5.2.2 Variable Gain Amplifiers                                                | 81       |

|    |                 |                                                                               | 76       |

|    | 5.2             | Active phase shifter: I-Q interpolation                                       |          |

|    |                 | 5.1.2 Butler mixer and high/low pass filters                                  | 74       |

|    |                 | 5.1.1 Varactor-based passive phase shifting structures                        |          |

|    | 5.1             | Passive phase shifters                                                        | 69       |

| 5  | Phas            | se Shifting Structures                                                        | 69       |

|    |                 |                                                                               | 50       |

|    | 4.5             | Conclusion                                                                    | 68       |

|    | ¬. <del>¬</del> | · · · · · · · · · · · · · · · · · · ·                                         | 63       |

|    | 4.4             | Active mode implementation of delay elements employing inductance multiplica- | U        |

|    | 4.3             | tion technique                                                                | 60       |

|    | 4.2             | Inductance tuning technique                                                   | 31       |

|    | 4.2             | 4.1.2 Synthesized transmission lines                                          | 57       |

|    |                 | 4.1.1 Slow wave transmission lines                                            |          |

|    | 4.1             | Tunable delay structures                                                      |          |

| 4  |                 | e Time Delay Elements                                                         | 52<br>52 |

| 1  | Two             | Time Delay Floments                                                           | E^       |

|    | 3.5             | Phase shifters or delay elements                                              | 48       |

|    |                 | •                                                                             |          |

|    |                 | 3.4.1 Radar Equation                                                          | 45       |

|    | 3.4             | $\mathcal{E}$ 1                                                               | 44       |

|    |                 | 1 ,                                                                           | 43       |

|    |                 |                                                                               | 42       |

|    |                 |                                                                               | 42       |

|    | 3.3             |                                                                               | 42       |

|    | 3.2             | Advantages of phased arrays                                                   |          |

|    | 3.1             | Fundamentals of phased arrays                                                 | 37       |

| 3  | Phas            | sed Array Structures                                                          | 37       |

|    | ۷.3             | From the astronomic results                                                   | 34       |

|    | 2.5             | 2.4.2 Prototype design                                                        |          |

|    |                 | 2.4.2 Prototype design                                                        | 30       |

# **List of Figures**

| 1.1 | 2007 ITRS roadmap failed to predict current mm-wave design trend [1]                            | 2   |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 1.2 | 60GHz wireless connectivity for video streaming and WPAN applications                           | 3   |

| 1.3 | Long range(left) and short range(right) automotive radar solutions                              | 4   |

| 1.4 | mm-wave imaging for medical and security applications                                           | 5   |

| 1.5 | Point to point links are preferred to operate at frequency bands where mm-wave                  |     |

|     | signals free space absorption loss is minimum[2]                                                | 7   |

| 1.6 | At each process node SiGe has more number of mask layers, however in advanced                   |     |

|     | CMOS technologies the difference is diminishing[3]                                              | 9   |

| 1.7 | Cost per die size of each CMOS process node equals to that of a SiGe technology                 |     |

|     | which is two generations older [4]                                                              | 10  |

| 1.8 | Digital intensive solutions get shrunk considerably as they are migrated to newer               |     |

|     | process nodes and the die cost will go down                                                     | 11  |

| 1.9 | Comparing $f_t$ and $NF_{min}$ of 65nm CMOS and 130nm SiGe technologies                         | 12  |

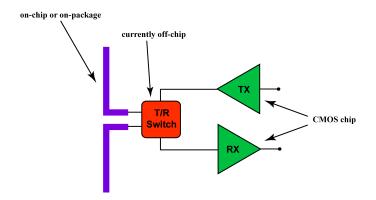

| 2.1 | A fully integrated transceiver with an on-chip antenna requires an integrated T/R               |     |

| 2.1 | switch to save die area                                                                         | 17  |

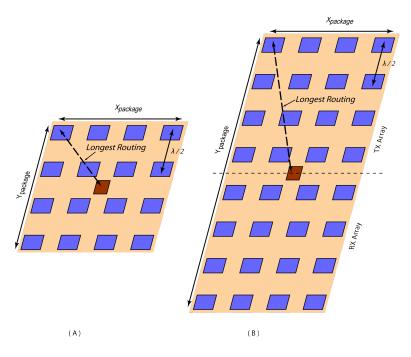

| 2.2 | In case of not including T/R switches, two separate RX and TX arrays are required               | 1 / |

| 2.2 | (B), which correspondingly lengthens interconnection routings and increases their               |     |

|     | associated loss                                                                                 | 18  |

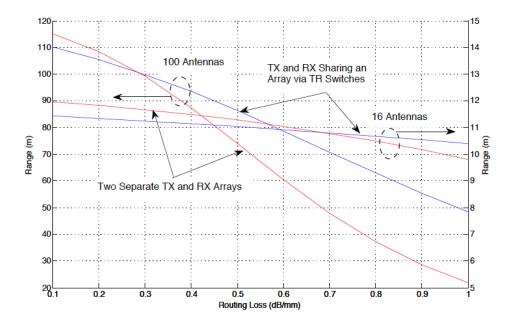

| 2.3 | Graph of the maximum achievable communication range in two configurations                       |     |

|     | of shared or separate arrays (for both small and large arrays). For larger arrays               |     |

|     | the routing loss is more detrimental than the T/R switch loss and higher quality                |     |

|     | packaging should be employed                                                                    | 19  |

| 2.4 | Measured $S_{21}$ of an NMOS transistor acting as a series switch in a 50 $\Omega$ environment. | 20  |

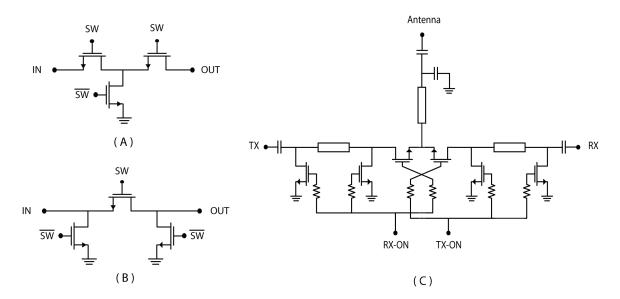

| 2.5 | Combinations of series and shunt switches in a $T$ (A) or $\pi$ (B) or $L$ -shape config-       |     |

|     | uration (C)[33] decrease the amount of off-state leakage at the price of degrading              |     |

|     | the on-state insertion loss                                                                     | 21  |

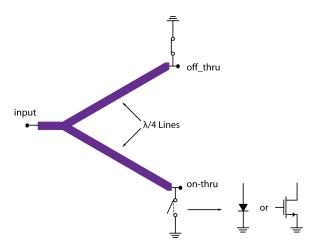

| 2.6 | Traditional shunt switches occupy a large footprint as a result of employing quarter            |     |

|     | wavelength transmission lines                                                                   | 22  |

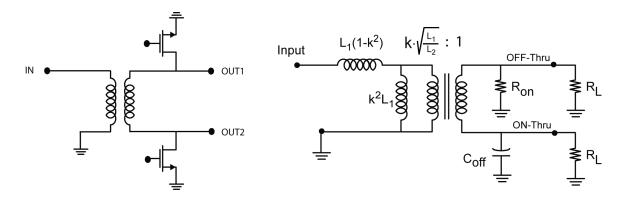

| 2.7 | Schematic diagram of a transformer-based shunt switch and its equivalent circuit                |     |

|     | model                                                                                           | 23  |

| 2.8  | Simplified model of the SPDT network including loading effects                                                                                                          | 24 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

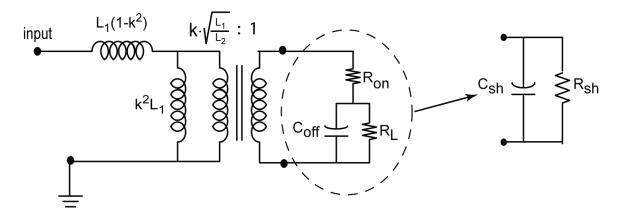

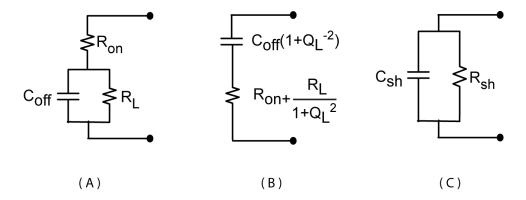

| 2.9  | Calculating the shunt equivalent loading network                                                                                                                        | 25 |

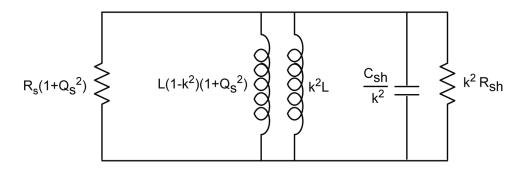

| 2.10 | Parallel tank equivalent network of the switch for calculating the center frequency .                                                                                   | 26 |

|      | Equivalent circuit for calculating the isolation between two thru ports                                                                                                 | 28 |

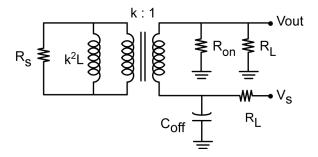

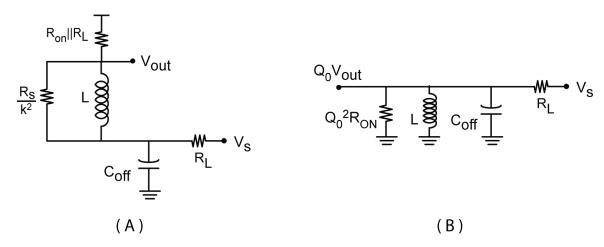

| 2.12 | Source network is transferred to the load side (A) and then the structure is con-                                                                                       |    |

|      | verted to a parallel tank configuration (B)                                                                                                                             | 28 |

| 2.13 | Higher biasing impedance at the gate not only improves the insertion loss but also                                                                                      |    |

|      | results in less distortion to the output signal and a higher linearity number for the                                                                                   |    |

|      | T/R switch                                                                                                                                                              | 30 |

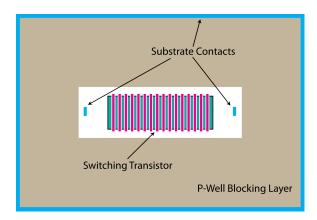

|      | Layout example of a MOS transistor to be used as a switch                                                                                                               | 31 |

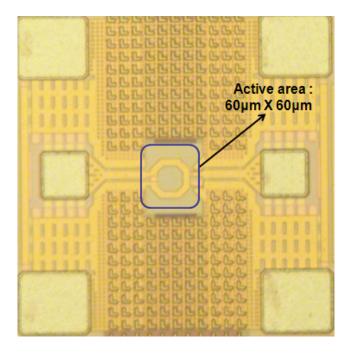

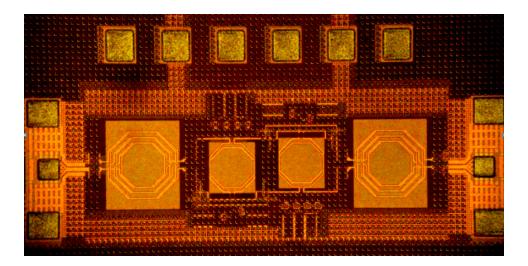

|      | Die microphotograph of the miniaturized shunt switch employing a transformer                                                                                            | 32 |

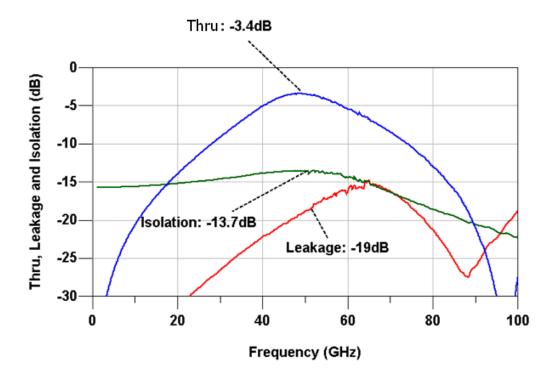

| 2.16 | Measured insertion loss, leakage(input to the off-thru port) and isolation (between                                                                                     |    |

|      | the on-thru and off-thru ports)                                                                                                                                         | 33 |

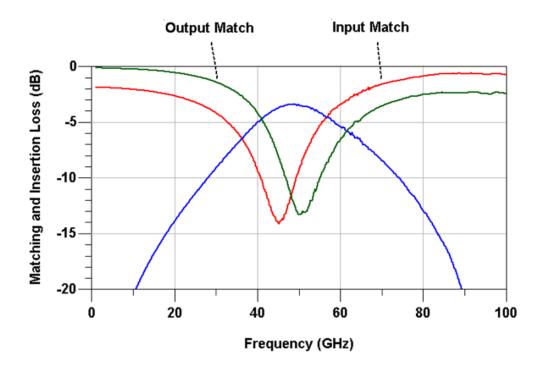

|      | Measured gain, input and output return loss curves                                                                                                                      | 34 |

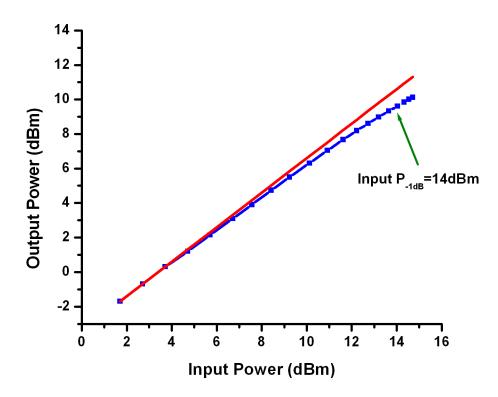

| 2.18 | Large signal measurement $(P_{-1dB} = 14dBm)$                                                                                                                           | 35 |

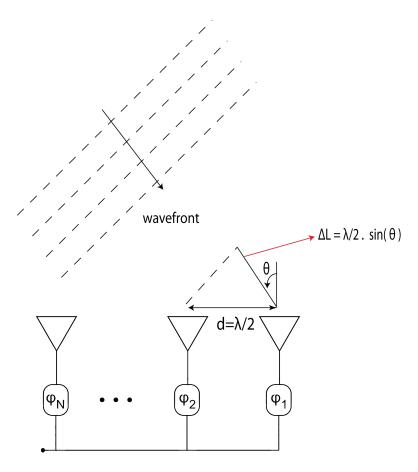

| 3.1  | The incoming wavefront reaches each antenna element at a different time and cor-                                                                                        |    |

|      | responding delay element are needed in each path to compensate for that                                                                                                 | 38 |

| 3.2  | The passive gain achieved through array directivity increases the EIRP and relaxes                                                                                      |    |

|      | PA design requirements                                                                                                                                                  | 39 |

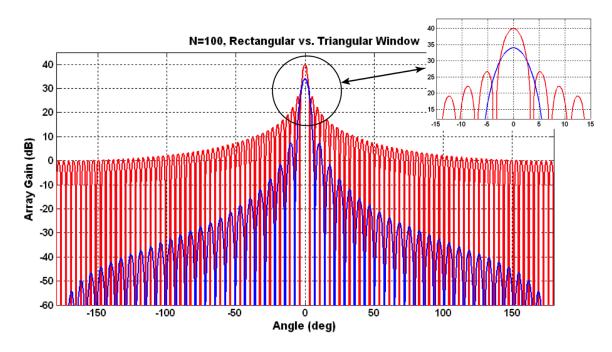

| 3.3  | A simple triangular gain windowing significantly decreases side lobe levels at the                                                                                      |    |

|      | price of less main lobe gain and lower main lobe resolution (wider half-power                                                                                           |    |

|      | beam-width)                                                                                                                                                             | 40 |

| 3.4  | In a phased array receiver, signals add up in voltage domain whereas uncorrelated                                                                                       |    |

|      | noises add up in power domain. This increases the overall sensitivity of the receiver                                                                                   |    |

|      | array                                                                                                                                                                   | 41 |

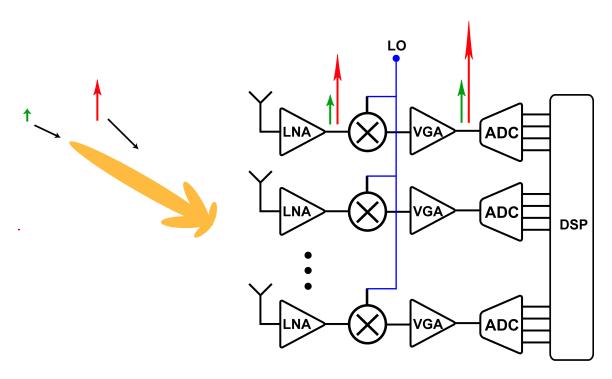

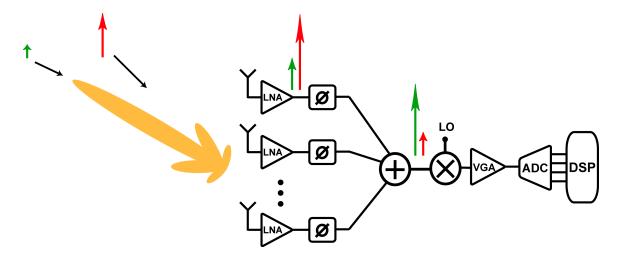

| 3.5  | Accomplishing the phase shifting and signal combining in the digital domain has                                                                                         |    |

|      | the advantage of ultimate flexibility and programability. It results in the highest                                                                                     |    |

|      | component count and area consumption as well has higher required dynamic range                                                                                          |    |

|      | for the entire chain                                                                                                                                                    | 43 |

| 3.6  | A LO phase shifting scheme has less component count with respect to digital phase                                                                                       |    |

|      | shifting. Phase shifter non-idealities are not directly in the RF path. A fully sym-                                                                                    |    |

| 2 =  | metric LO distribution network is necessary                                                                                                                             | 44 |

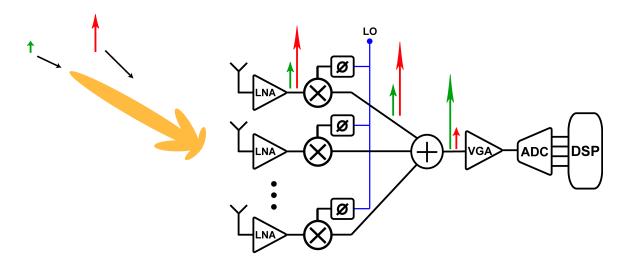

| 3.7  | The RF phase shifting scheme has the least component count and area/power con-                                                                                          |    |

| 2.0  | sumption. Phase shifter noise and non-linearity are directly in the signal path                                                                                         | 45 |

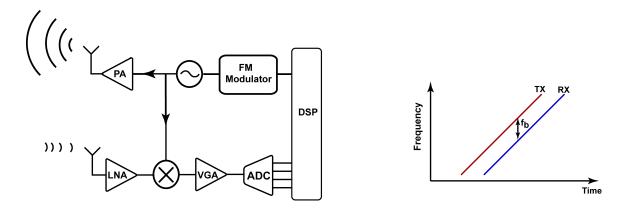

| 3.8  | Bulding block diagram of an FMCW radar                                                                                                                                  | 46 |

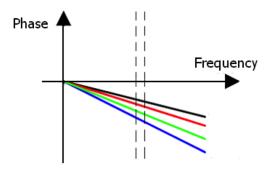

| 3.9  | In a narrowband system, true time delay elements (linear phase response vs. fre-                                                                                        |    |

|      | quency) can be approximated with phase shifters (constant phase response vs. frequency)                                                                                 | 40 |

| 2 10 | quency)                                                                                                                                                                 | 49 |

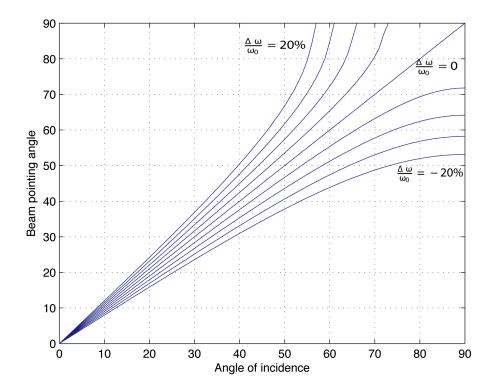

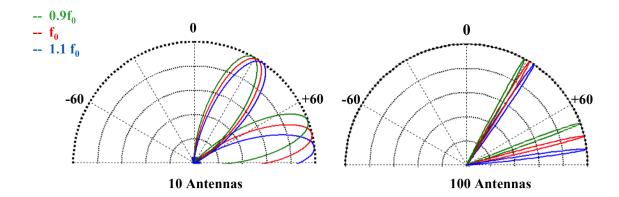

| 3.10 | The nonlinear relation of equation 3.16 leads to erroneous estimation of direction of arrival for end-fire angles (frequency deviation is swept up to 20% in 5% steps). | 50 |

|      | of arrival for end-ine angles (frequency deviation is swept up to 20% in 3% steps).                                                                                     | )( |

| 3.11 | As the array gets larger, the HPBW shrinks and the phase shift approximation of delay elements fails for incident angles closer to the end-fire angle even for narrowband signals                                                                                                    | 51  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

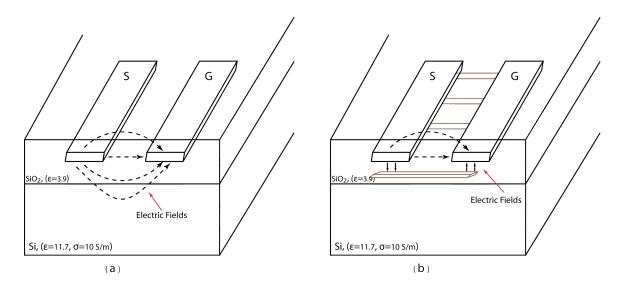

| 4.1  | Electric field pattern in a normal (a) and a slow wave (b) transmission line                                                                                                                                                                                                         | 53  |

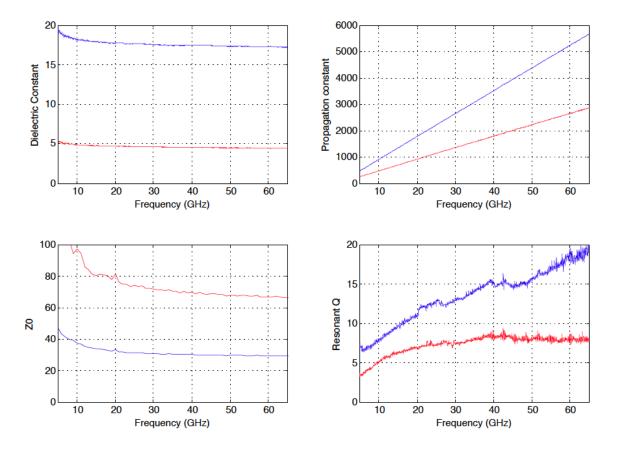

| 4.1  | Measurement comparison of a slow wave structure (blue) with a normal transmission (red) line in terms of the dielectric constant( $\epsilon$ ), propagation constant( $\beta$ ), characteristic impedance( $Z_0$ ), and resonant quality factor( $Q_{res} = \frac{\beta}{2\alpha}$ ) | 54  |

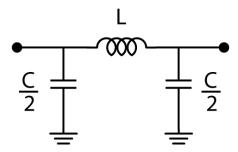

| 4.3  | A $\pi$ -section of an artificial transmission line synthesized out of lumped component inductors and capacitors instead of infinitesimal distributed inductance and                                                                                                                 |     |

| 4.4  | capacitance of a classic transmission line                                                                                                                                                                                                                                           | 55  |

|      | solution for tunable synthesized transmission lines                                                                                                                                                                                                                                  | 56  |

| 4.5  | Inductance tunability, net magnetic flux crossing a loop is altered via the flux gen-                                                                                                                                                                                                |     |

|      | erated by another loop                                                                                                                                                                                                                                                               | 57  |

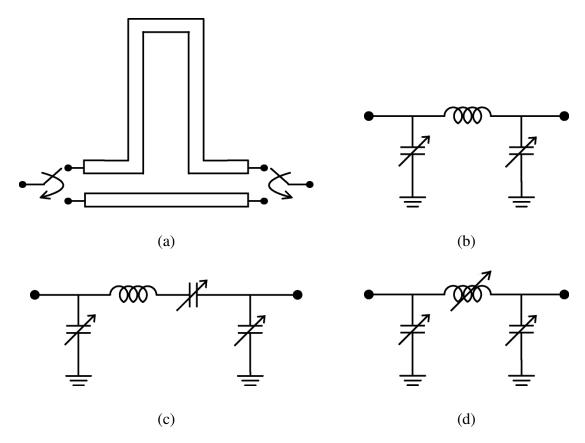

| 4.6  | Four different ways to realize inductance tuning: (a) Using a current amplifier, (b) varying the mutual inductance, or by rerouting the current in the secondary in a (c)                                                                                                            |     |

|      | single-ended or (d) differential manner.                                                                                                                                                                                                                                             | 59  |

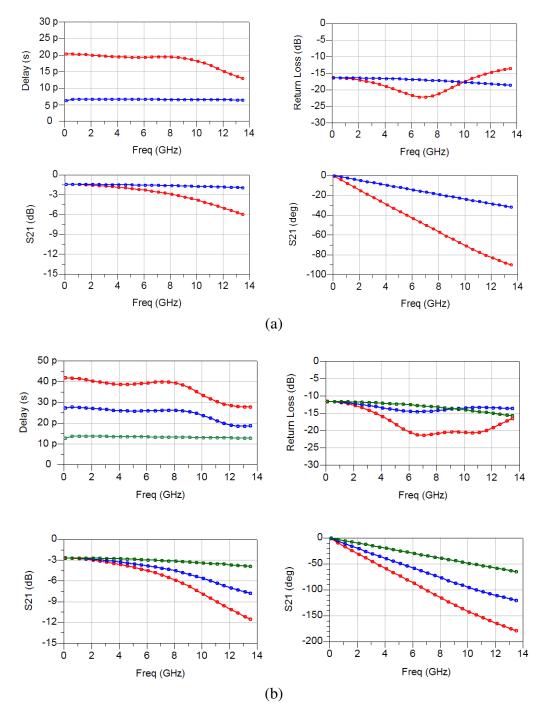

| 4.7  | Group delay, return loss (input/output) and phase response of a single delay cell and a cascade of two delay cells are demonstrated in (a) and (b) respectively                                                                                                                      | 61  |

| 4.8  | Die Microphotograph                                                                                                                                                                                                                                                                  | 62  |

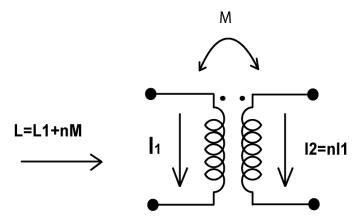

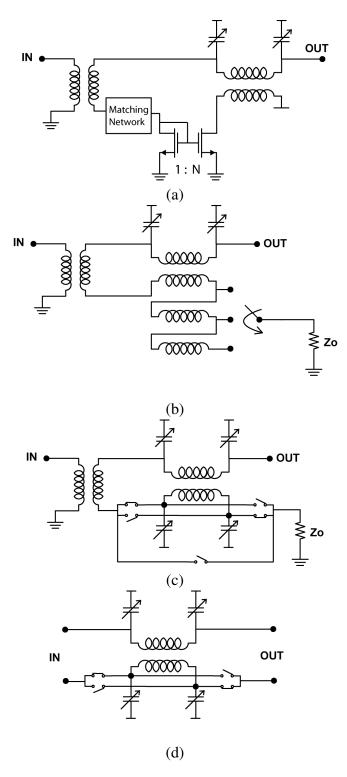

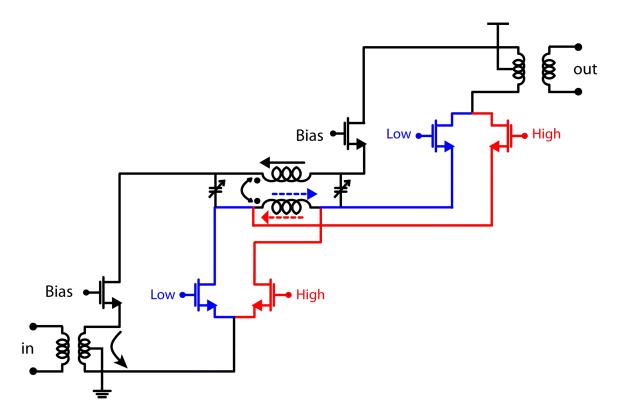

| 4.9  | A variable delay amplifier implemented in CMOS technology                                                                                                                                                                                                                            | 63  |

| 4.10 | A variable delay amplifier in BiCMOS SiGe technology with $V_{DD}=3.3V$ that                                                                                                                                                                                                         |     |

|      | can be used to stack more devices                                                                                                                                                                                                                                                    | 65  |

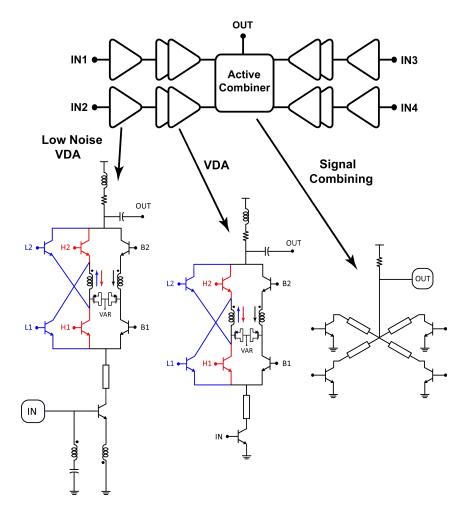

| 4.11 | A 4-way phased array receiver comprising of 4 low noise VDAs, 8 VDAs and a 4                                                                                                                                                                                                         |     |

|      | to 1 combining network implemented in 130nm SiGe technology                                                                                                                                                                                                                          | 66  |

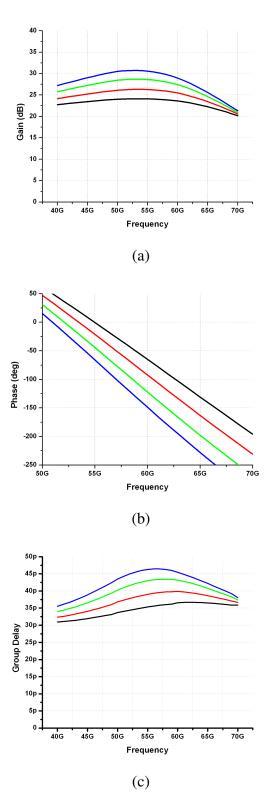

| 4.12 | (a) Gain response of each channel for different delay settings, (b) phase response                                                                                                                                                                                                   |     |

|      | of each channel for different delay settings (c) group delay $	au = -rac{d\phi}{d\omega}$                                                                                                                                                                                           | 67  |

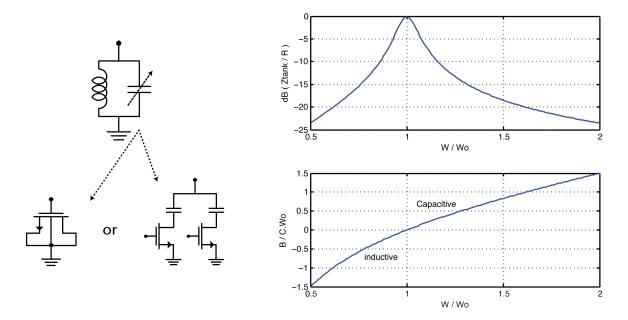

| 5.1  | The reactance of a variable tank provides $180^{\circ}phaseshift$ , but due to the variation                                                                                                                                                                                         |     |

| J.1  | of its normalized impedance $(\frac{Z}{R_P})$ it can not act as an all-pass filter on its own                                                                                                                                                                                        | 70  |

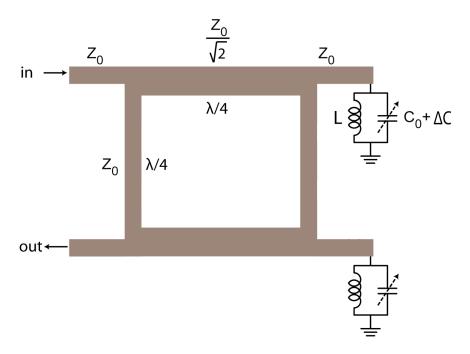

| 5.2  | A quadrature hybrid structure in conjunction with two variable tanks form a reflec-                                                                                                                                                                                                  | , ( |

| J.2  | tive type phase shifting structure (RTPS)                                                                                                                                                                                                                                            | 71  |

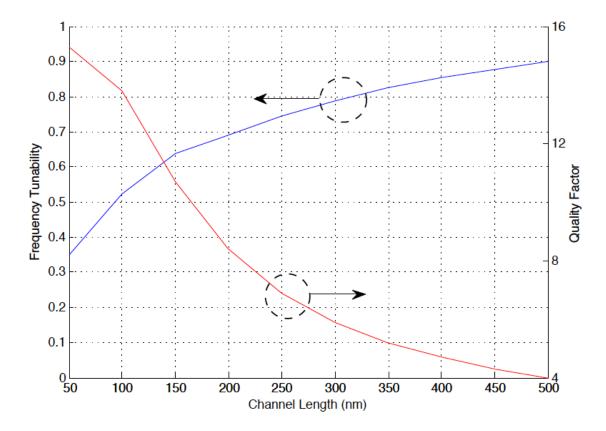

| 5.3  | Increasing the channel length of a MOS varactor increases $\frac{C_{max}}{C_{min}}$ and hence the                                                                                                                                                                                    |     |

|      | frequency tunability $((\frac{C_{max}}{C_{min}})^{\frac{1}{4}} - (\frac{C_{min}}{C_{max}})^{\frac{1}{4}})$ at the price of lowering the varactor                                                                                                                                     |     |

|      | quality factor                                                                                                                                                                                                                                                                       | 73  |

| 5.4  | Two types of passive phase shifters that do not use varactors to achieve phase                                                                                                                                                                                                       |     |

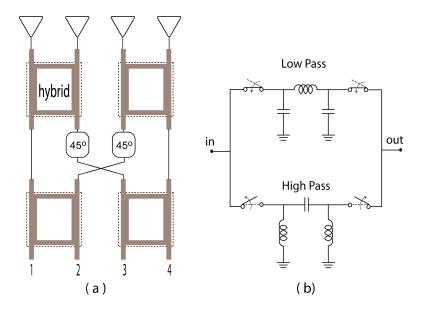

|      | variation (Butler mixer and high-pass/low-pass networks)                                                                                                                                                                                                                             | 74  |

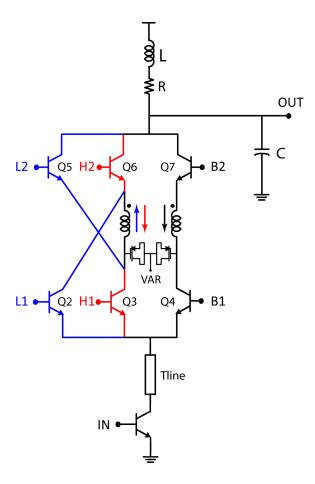

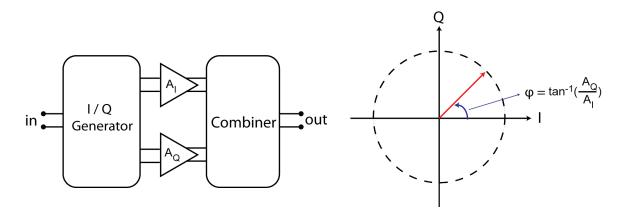

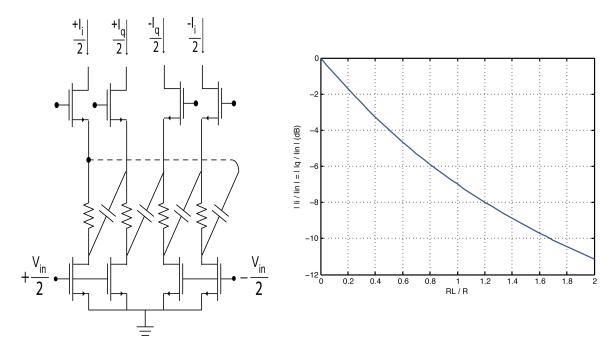

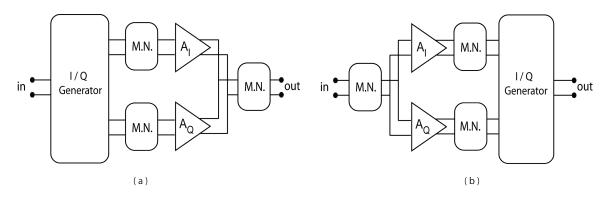

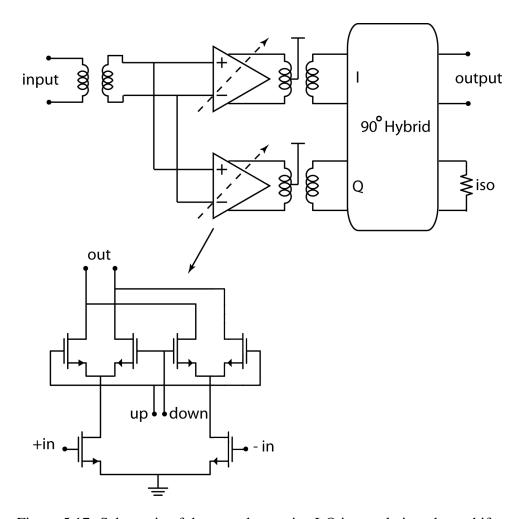

| 5.5  | Schematic diagram of an I-Q interpolating active phase shifter                                                                                                                                                                                                                       | 75  |

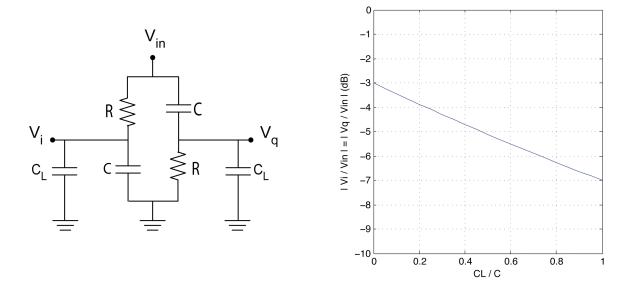

| 5.6  | A voltage domain poly phase filter (left) and its gain degradation as loading capac-    |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | itances being presented output nodes                                                    | 77 |

| 5.7  | Adding the poly phase filter lowers the input impedance of a MOS amplifier which        |    |

|      | results in lower matching network Q and consequently lower gain through the chain       | 78 |

| 5.8  | A current mode poly phase filter (left) and its gain degradation as a nonzero load      |    |

|      | impedance being presented at the output                                                 | 79 |

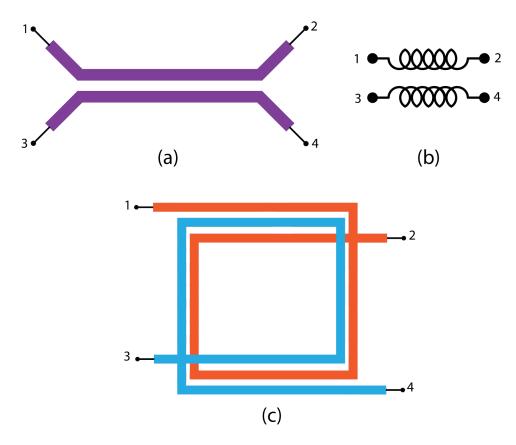

| 5.9  | a) A transmission line coupler, b) A transformer can be exploited for the lumped        |    |

|      | version of a transmission line coupler, c) 1.25 turn loops comprising a transformer     |    |

|      | coupler resemble a quadrature hybrid                                                    | 80 |

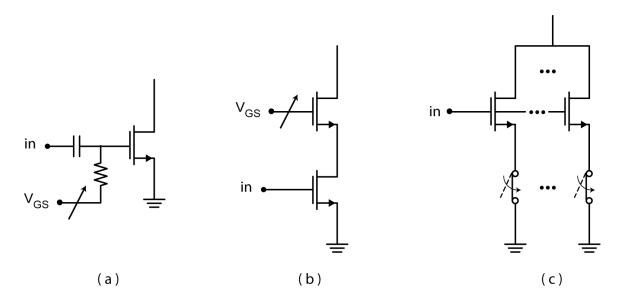

| 5.10 | Gain variation capability can be achieved through changing bias conditions of an        |    |

|      | NMOS transistor                                                                         | 82 |

|      | A phase inverting building block with input and output tuning inductances               | 83 |

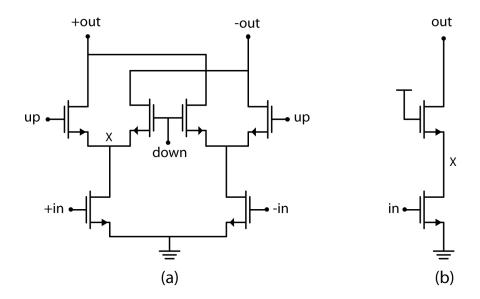

| 5.12 | Schematic of core transistors for a current commuting type VGA (a) and a fixed          |    |

|      | gain cascode amplifier (b)                                                              | 84 |

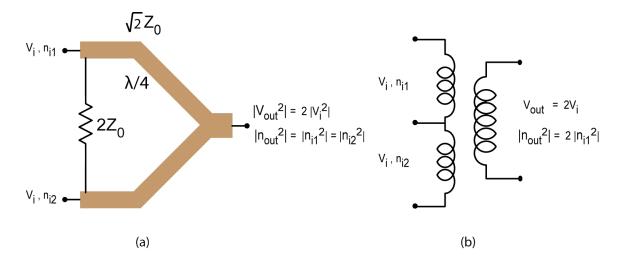

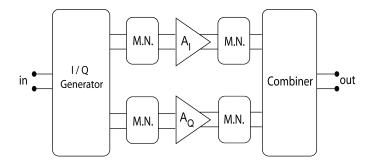

|      | Traditional microwave method of signal dividing and combining                           | 85 |

| 5.14 | Two lumped component version for dividing and combining signals in current (a)          |    |

|      | or voltage (b) mode                                                                     | 85 |

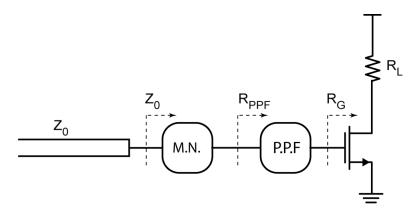

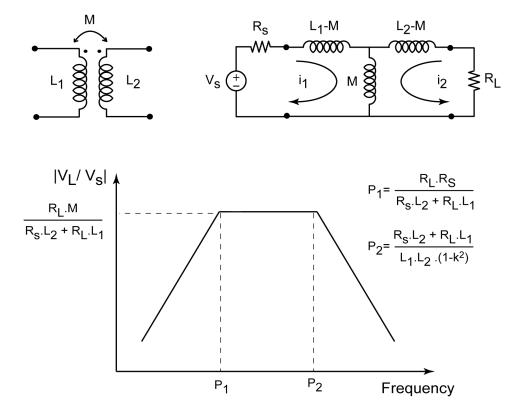

|      | A transformer acts as a wideband matching network                                       | 86 |

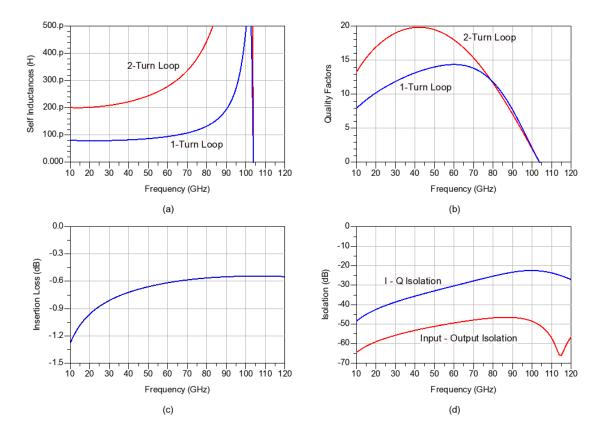

| 5.16 | (a)-Simulated Self inductances of a 2 : 1 transformer, (b)- quality factors of pri-     |    |

|      | mary and secondary windings, (c)-transformer insertion loss, (d)- coupling be-          |    |

|      | tween transformers                                                                      | 87 |

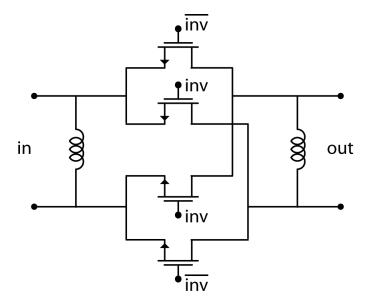

|      | Schematic of the complete active I-Q interpolating phase shifter                        | 89 |

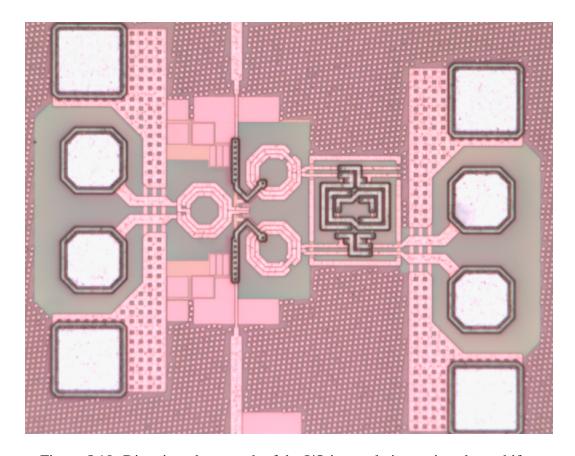

|      | Die microphotograph of the I/Q interpolating active phase shifter                       | 90 |

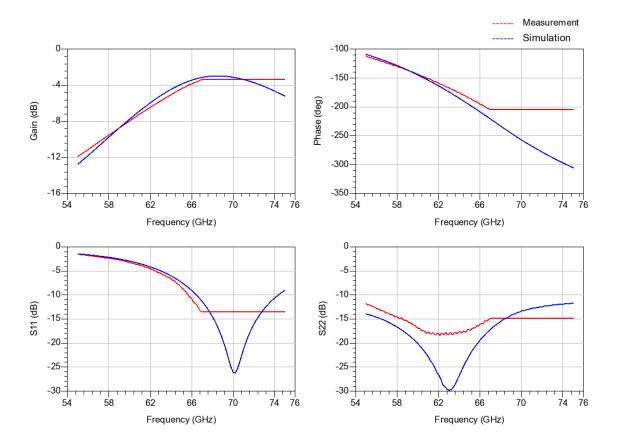

| 5.19 | Measurement data for gain, phase and return losses at input and output and their        |    |

|      | comparison with simulation prediction                                                   | 91 |

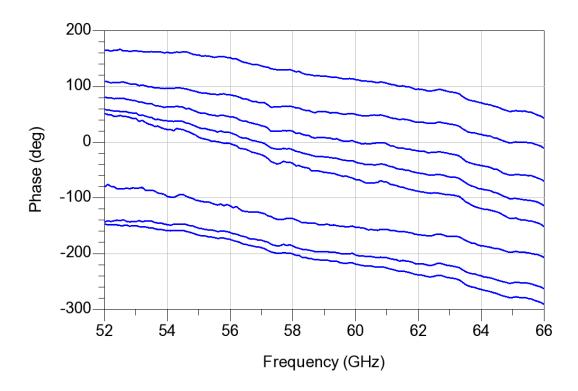

|      | Measured phase responses for different phase shift settings                             | 92 |

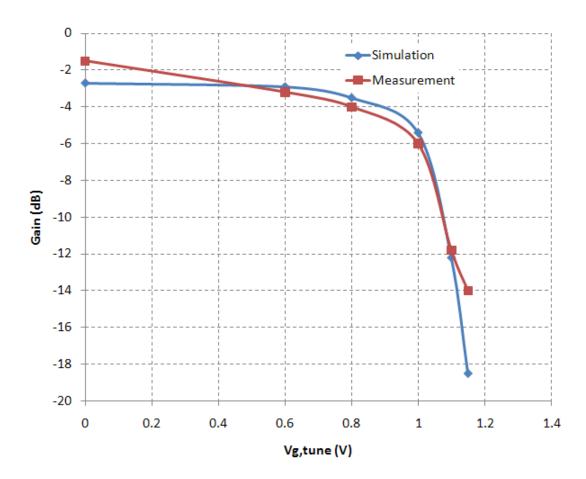

|      | $V_{g,tune}$ can be varied from $V_{DD}$ down to $V_{DD}/2$ in order to adjust the gain | 93 |

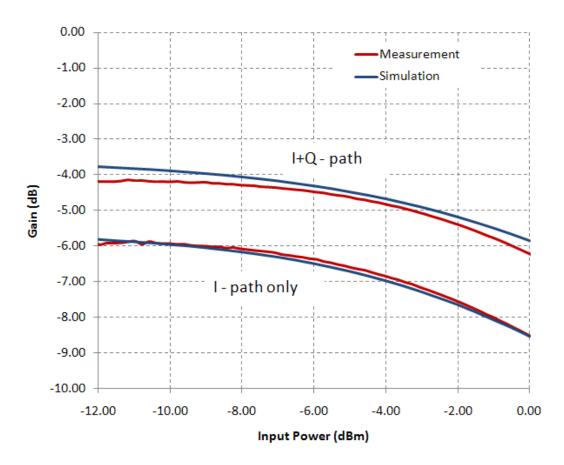

| 5.22 | Large signal measurements for two extreme cases of I+Q and only-I settings and          |    |

|      | their comparison with simulation data                                                   | 94 |

# **List of Tables**

| 1.1 | For comparable $f_t$ and current dissipation, CMOS technology has less intrinsic par-   |    |  |

|-----|-----------------------------------------------------------------------------------------|----|--|

|     | asitics which makes it more vulnerable to layout added parasitics and their variations. | 13 |  |

| 2.1 | Comparison to recently published mm-wave T/R switches                                   | 36 |  |

#### Acknowledgments

There are many people who I am grateful for knowing and working with them during my stay at Berkeley. First of all, my advisor professor Ali Niknejad who I am thankful for all the time and energy that he dedicated. For the directions that he showed and schools of thoughts that he made me familiar with. For his patience to go through my lengthy reports and give me his feedbacks and for classes he taught (EE142-EE217-EE242) that covered cutting edge "Radio Frequency Integrated Circuit" topics.

I am also thankful of my thesis committee members professor Jan Rabaey and professor Paul Wright. I had the pleasure to have them on my qualification exam committee as well and not only I had the opportunity to have their brilliant comments during the qualification exam and the thesis review, but also I benefited from their visionary discussions and presentations at the "Berkeley Wireless Research Center(BWRC)" and its retreats. I am also thankful of professor Robert Meyer who kindly accepted to be in my qualification committee and let me learn from his comments and ideas. I thank professors Yablonovitch, Nikolic, Carmena, Bahai , Kuroda and Dr. Shana for courses they offered and I had the opportunity to take.

I learned a lot in EE247 from professor Haideh Khoramabadi, but her kindness and caring character in the years afterwards made me think of her like my mom and I am greatly thankful of her. I bugged Mary Burns, Ruth Gredje and Patrick Hernan a lot during my PhD program and I thank them all for their help and patience.

My group-mates Babak Heydari and Mounir Bohsali who I was co-working with for three years made me long lasting good memories of doing research at BWRC. Discussions that I had with Amin Arbabian and Bagher Afshar wether they were about research topics or class projects made me realize that there are always different angles to look at something. I also thank the mm-wave group members Alex Pai, Omar Bakr, Ashkan Borna, Steven Callendar, Jiashu Chen, Wei-hung Chen, Debo Chowdhury, Zhiming Deng, Mohan Dunga, Shinwon Kang, Cristian Marcu, Nuntachai Poobuapheun, Maryam Tabesh and my other colleagues at BWRC along with BWRC staffs and directors for making a productive environment and an enjoyable research center.

I would like to thank my co-workers Alfred G. Besoli and Michael Boers at Broadcom Corp. where I did an internship working on phase shifting structures. Attending UC Berkeley gave me the opportunity to live at the lively Berkeley community, benefit from its intellectual people, the "International House" and much more. I will be always proud of being part of the Berkeley community.

# **Chapter 1**

# mm-Wave opportunities and choice of technologies

The RF revolution has opened up a huge market for personalized devices that transmit and receive wireless data. The main characteristic of a product targeted for a consumer electronic market is its aim to be as cost effective as possible with respect to other competitive solutions. Therefore readily available and less expensive technologies that are advanced enough to meet the system requirements have a clear chance of victory for such applications. Nowadays highly scaled and advanced CMOS technologies have stablished themselves as primary solutions for many RF circuits and systems design at multi-GHz frequency band. mm-Wave solutions that deal with circuits and systems functioning at multi-ten gigahertz range of frequencies are gaining momentum to enter the consumer electronic market. Different technologies are suitable for different types of applications due to their technical requirements and the corresponding size of the market.

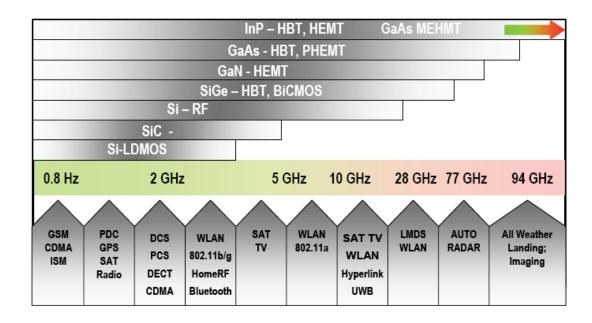

2007 ITRS roadmap (Fig. 1.1) [1] had suggested that CMOS technology would not be used for multi-ten gigahertz applications and even BiCMOS (SiGe) technologies wouldn't be deployed in applications beyond the frequency range of 60GHz. Silicon technologies have lower speeds compared to their more advanced compound (III-V) technologies and their lower breakdown voltages pose challenges on the transmit power of silicon-based solutions. However feasibility studies over the past few years ([44] [48] [53]) showed that advanced silicon technologies are capable of handling mm-wave applications. To create the communication link for different types of applications, different link budgets and overall system requirements are needed to be met which demands for a case by case study of respective applications. The next few years will be decisive to figure out the direction of silicon-based products in the consumer electronic market. In next section, various mm-wave opportunities and their criteria for being implemented efficiently will be covered.

Figure 1.1: 2007 ITRS roadmap failed to predict current mm-wave design trend [1]

# 1.1 mm-Wave opportunities

# 1.1.1 60GHz connectivity

The universal availability of 7GHz of unlicensed bandwidth around 60GHz opens up opportunities for high data rate short range communications. Wirelessly streaming HD video that replaces the HDMI cable has a great potential as most portable media player devices will have HD capabilities in the future. 1600x1200 pixels at 24bits (true color) per pixel with a 120 Hz refresh rate lead to 10Gbit/s of uncompressed data-rate. Transmitting and receiving uncompressed video helps to remove the latency and cut the power dissipation associated with the video processing unit. Larger bandwidth available around 60GHz and much more relaxed limits on the transmit power levels are key advantages of 60GHz over WiFi and UWB solutions respectively.

In WPAN realm, as the capacity of storage devices is steadily increasing, more time is needed to synchronize the data between different devices. High speed wireless connectivity between personal computers, external hard drives, HD cameras and USB devices is highly desired in the future of WPAN applications. 60GHz can be used to connect PDAs, smart phones, portable media players and other personal devices while enhancing the overall efficiency (Joule/bit number) of communication.

60GHz can also be used for very high speed Gbps WLAN connectivity. 7GHz of bandwidth, opportunity to transmit high power levels and high path losses through walls and obstacles make 60GHz communication an option for high data rate and secure indoor communication where out-

Figure 1.2: 60GHz wireless connectivity for video streaming and WPAN applications

sider interferences are greatly attenuated. Small wavelengths at 60GHz make a complete phased array solution with relatively large number of antennas for such applications (8-64 antennas) realizable in either a SOC (system on a chip) or SOP (system on a package) configuration. With antenna arrays being embedded on chip or on the package, the phased array solution enhances the flexibility of the system in addressing multiple devices at the same time by exploiting the spatial multiplexing on top of time and frequency domain multiplexing.

Since most of the above mentioned applications are handheld and battery operated, the complete mm-wave system should be delivered with a reasonable power consumption, small footprint and a low cost of on the order of a dollar including testing and packaging costs. However due to the large volume of these products ( $\sim$ 10B per year), the estimate market size would be around a 10B\$ revenue annually which is large and a great incentive for employing a routine and inexpensive technology such as standard digital CMOS technologies in the design.

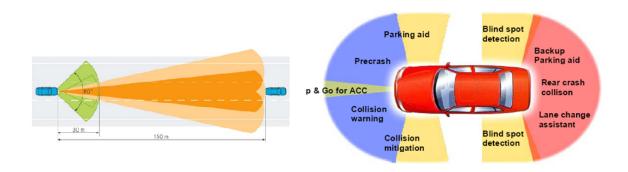

Figure 1.3: Long range(left) and short range(right) automotive radar solutions

#### 1.1.2 Automotive radar

It is well known that motor vehicle accidents are one of the leading causes of death. 90 percent of fatal accidents involve driver errors. Therefore having some kind of system that recognizes situations where drivers are not responding accordingly and takes action that results in prevention or mitigation of the accident would be much beneficial. A key part of such a system is an automotive radar to detect objects surrounding a vehicle. Automotive radar solutions have been around for more than a decade now. Due to stringent requirements, all automotive radars were implemented exploiting advanced and expensive III-V MMIC modules. Using MMIC modules in discrete designs sets the price level of the complete solution to a high level which is out of reach for being installed on vehicles other than high-end cars.

Demanding requirements of detection range, range and angular resolutions, and target discrimination in heavily cluttered areas make the single chip solution of an automotive radar system in silicon technologies challenging. However, the ever increasing speed of transistors in emerging Si process nodes due to the scaling, and the luxury of being able to implement a microprocessor residing next to a radar chip are bridging the gap to make an automotive radar commercially viable for the purpose of being included in every single vehicle as a standard option for added safety and driving comfort. mm-Wave silicon technologies can directly revolutionize the automotive radar industry in terms of cost, size and power consumption. Having a single chip fully integrated carradar module or a single package solution with all the antennas being included, decreases the size and hence the cost of the system considerably. Being implemented on an standard silicon technology makes it possible to have the digital processing part in the same chip that includes the RF part, which yields in a highly flexible single chip solution with the capability of calibrating and programming various parameters as well as incorporating built in self test (BIST) techniques. Upcoming novel solutions in the car industry such as smart electric cars open up a great opportunities to design short to high range radars that are compatible and can be easily embedded in electric car systems.

Right now the 24GHz band is allocated for pulse based UWB communication for short range

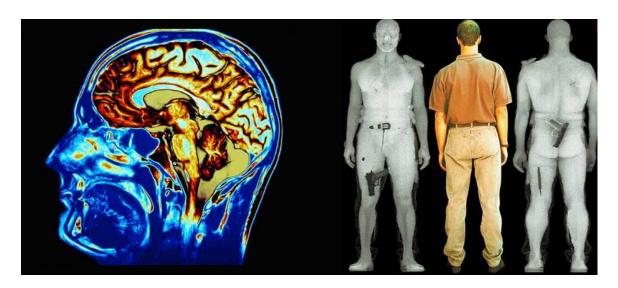

Figure 1.4: mm-wave imaging for medical and security applications.

radar(SRR) applications that help with parking, blind spot detection, lane detection, stop and go in traffic and collision avoidance/mitigation. By 2013, 24GHz band for UWB short range radars will be moved to 79GHz. 77GHz band is already dedicated to FMCW long range radar(LRR) solutions. 77GHz FMCW radar aids with the adaptive cruise control (ACC) that is primarily intended for highway driving. ACC allows target detection from a distance of few meters up to 150m. The data can be provided to the driver as an assistance or as an ultimate goal, with help of digital processing units it could be used for autonomous driving.

As depicted in figure. 1.3, 8 of car radar modules is needed per vehicle. Taking into account that 50 million cars are being made worldwide each year and the estimated unit price of an automotive radar module to be around \$10, it is clear that mm-wave automotive radar is a market with few billion dollars( $\sim$ \$4B) of revenue each year. After 60GHz connectivity, automotive radar market seems to be the next domain that silicon technology will spread into and replace compound technologies.

# 1.1.3 Imaging

Basic principles of microwave imaging have been understood for decades. Extending these imaging techniques to higher carrier frequencies where larger bandwidths are also available enabling for higher image resolutions both in depth and lateral spacing. Two main areas that can benefit from this enhanced imaging technology are medical diagnosis and security (figure 1.4).

There are two types of imaging systems, passive and active. Passive mm-wave imaging exploits an array of very low noise receivers to reconstruct a high resolution image of an object. All objects at a temperature greater than absolute zero emit blackbody radiation. This energy emission occurs at a broad range of spectrum with emission peaks at infrared frequencies. The amount of radiation

at mm-wave frequencies is  $10^8$  times smaller than that emitted at the infrared range. However state of the art mm-wave receivers have at least  $10^5$  times better sensitivity with respect to infrared detectors and the temperature contrast can recover the remaining factor of 1000. This makes mm-wave passive imaging solutions comparable to infrared imaging systems. For optimal detection the imaging windows are chosen where the atmospheric loss is minimum, namely at 35GHz, 94GHz, 140GHz, 220GHz. Passive imaging can be used in various applications such as airport safety, weather radar, remote sensing for environmental and geological explorations and non-invasive and non-destructive in-situ testings.

In active imagers, an ultra high bandwidth pulsed based system reconstructs an image of the object based on the scattered components of the radiated short-duration pulses. Strength of each scattered component determines the intensity of the corresponding pixel in the image. Pulse based active mm-wave imaging can be used in medical diagnosis since reflection properties of various tissues and substances are different. It can be as well used in security systems for detection of drugs and weapons. Because of the fact that mm-wave signals can easily pass through clothing but can not do so through the body and will get reflected through metallic / liquid objects.

As silicon technologies are capable of integrating large arrays of transceivers, the mm-wave imaging technology could be a low cost competitor to existing technologies such as MRI, CAT scan and infrared imaging systems. However silicon based mm-Wave imaging is an active area of research and there are still parts with challenging requirements that pose a great challenge for the complete system to be implemented in a monolithic fashion. Since their target applications are mainly medical diagnosis and security, they are anticipated to have a unit price in the range of \$100-1000 and the annual demand would be 10-100K parts. So an annual revenue of about \$50M is estimated for the silicon based mm-wave imaging market.

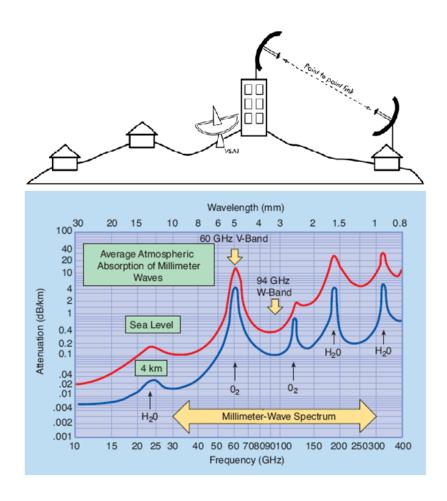

# 1.1.4 Point to point links, Gigabit ethernet

The cost of realizing fiber optic links in remote areas that are not heavily populated can hamper the implementation of such links. In those circumstances having wireless point to point links between base stations (BTS) and network nodes is a key solution to decrease the implementation cost. Since point to point links are kilometer-range links, it is mostly desired that frequency bands where the free space path loss is minimum be allocated for such applications. Although the fiber optic infrastructure already exists in many urban areas for realizing LAN connectivity. However, hardware implementation of wired communication in the first/last mile to reach the end users is extremely costly. Replacing the fiber link with a high data rate mm-wave wireless link in the first/last mile is an option to reduce the overall cost and make it a more feasible solution.

As of now, for such applications frequency spectrum is allocated in the unlicensed 24.25-24.45GHz and 25.05-25.25 GHz bands. However, the 72.5-82.5GHz ISM band (E-band) is going to be used to extend LAN backbones. Communication at the E-band requires smaller antennas, resulting in a more directive antenna array being implemented at a given specified area devoted to radiation elements. E-band communication with the throughput in the range of multi-10Gbps is foreseen to be employed as a solution with carrier grade performance for achieving link dis-

Figure 1.5: Point to point links are preferred to operate at frequency bands where mm-wave signals free space absorption loss is minimum[2]

tances over several kilometers. It will provide means for interconnection and backhaul of 3G and 4G (WiMAX and LTE) networks. Other applications of E-band communication will be gigabit ethernet access, fiber backup, path redundancy and network extension applications.

Due to the nature of these applications, each unit will be on the order of \$1000 and the total need is 10k parts per year. So the market(\$10M) is smaller than the market size for previously mentioned applications. Cost for these systems are less important with respect to issues like performance and reliability.

# 1.2 Standard digital CMOS vs. SiGe technology

Although III-V compound technologies have the best performance at the mm-wave regime and most MMIC based mm-wave solutions exploit these high performance technologies nowadays. Due to their high cost of implementation as a result of their demand for specialized substrates and low process yields, and because of their lack of flexibility which comes from the inability to integrate digital circuitry on the same die, they are not suitable for consumer electronic markets. To investigate the most suitable technologies for emerging high volume markets of mm-wave applications, we focus our study on two promising silicon technologies: standard digital CMOS technology and the BiCMOS (SiGe) technology. They are both capable of providing low cost solutions that exact requirements of different applications may favor one with respect to the other one. In next sections important criteria for a mm-wave system design will be investigated and advantages and disadvantages of CMOS and SiGe technologies with respect to each other will be pointed out. As it is the case in other situations, price and performance are the two main parameters that rule the choice of technology to be adopted for mm-wave design.

#### 1.2.1 Cost of the process

#### Is CMOS really cheaper?

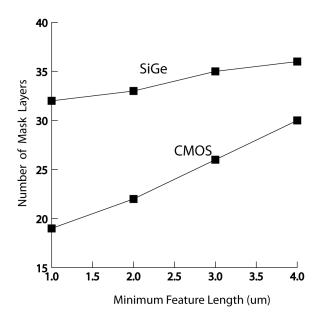

Ever increasing speed of transistors is the main scaling advantage for RF-Silicon technologies. However scaling below 100nm of feature length poses strong technical challenges in the fabrication which requires highly advanced and expensive tools (sources with smaller wavelengths) or new process techniques such as off-axis illumination and phase-shift masking which considerably adds to the complexity of the fabrication process. Therefore with the introduction of each new process node there is a hike in the cost per die size to account for more advanced tools and techniques employed in the fabrication process. At a given node, CMOS normally requires less masking steps than SiGe. This will result in faster fabrication cycle time and lower cost. However as depicted in figure 1.6, since masking steps increase with CMOS scaling, the gap between masking layer counts of CMOS and SiGe technologies is diminishing as new generations of scaling emerge [3].

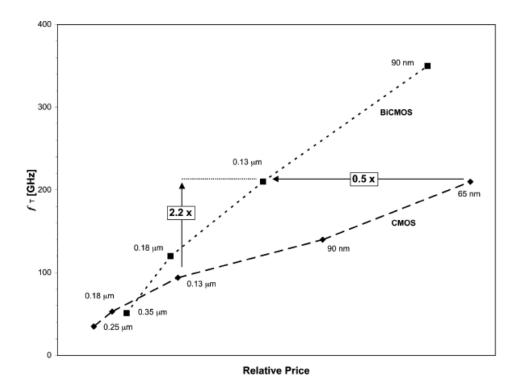

Although at each process node the cost of manufacturing a SiGe chip is more than the cost per die area of a CMOS chip, due to higher performance of SiGe technologies a newer CMOS technology should be employed to compete with an older SiGe technology. In fact cost of each process node of CMOS technology is comparable to that of a SiGe technology which is two generations older(figure 1.7)[4]. If we look at the same transit frequency ( $f_t$ ) as a figure of merit for performance, it can be seen that for each process node, SiGe technology has a better performance which is slightly more than twofold. Hence price per performance ( $f_t$ ) for SiGe technology is marginally better than that of CMOS technologies if the cost of the die area is considered to be the dominant factor in determining the total system cost. Therefore for applications that the size is mostly ruled by passive component footprints and hence does not change with proceeding to newer process nodes, die area cost is almost the same for similar performance obtained out of CMOS and SiGe

Figure 1.6: At each process node SiGe has more number of mask layers, however in advanced CMOS technologies the difference is diminishing[3].

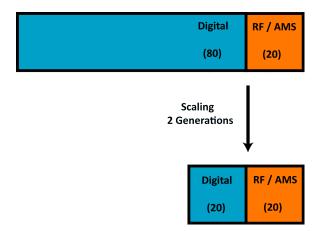

technologies and therefore it is not the major key player for the choice of the technology. On the other hand for applications that are digitally intensive and a great portion of the chip is occupied by digital or analog/mixed signal blocks, their size will shrink by migrating to a newer generation of scaled technology and then CMOS technology would be more die area cost effective (figure 1.8).

mm-Wave solutions need a more specialized package since RF interfaces are at such high frequencies and are prone to parasitics which are considered negligible for other applications at lower frequency bands. In most cases, antennas will be embedded in the same chip or they will be placed on a substrate in the flip chip package configuration that the mm-wave chip can be directly mounted on top of it. These special cares make the cost of testing and packaging a noticeable portion of the overall cost of a complete mm-wave system. Again CMOS technology with the capability of fully exploiting the built-in self test (BIST) feature can profit from the scaling and reduce this portion of the cost. Moreover making use of a standard CMOS fab that offers no specialized options and relies only on standard options as offered in the fabrication of all-digital processors has the advantage of much less lead time that can help lower the price by lowering the time to the market.

#### 1.2.2 Performance

#### Intrinsic gain

A figure of merit for amplifier design is the intrinsic gain of the device  $(g_m \cdot r_o)$ . Due to the exponential I-V characteristic of bipolar transistors, SiGe offers a better transconductance $(g_m)$

Figure 1.7: Cost per die size of each CMOS process node equals to that of a SiGe technology which is two generations older [4].

over CMOS where the output current has a quadratic relationship with input voltage (for highly scaled short channel devices, as a result of velocity saturation this relationship approaches toward a linear relationship and makes the situation even worse for the CMOS transconductance). SiGe BiCMOS technology provides a knob for the device designer to tweak the emitter germanium concentration and modify the electric field at the base, as a result of it one can improve the early voltage and the intrinsic output resistance of the device. In CMOS technology, in order to improve the reliability of analog and RF applications, a few extra processing steps are needed to increase the break-down voltage (eg. dual oxide technology), as well as additional implants to compensate for the short channel effects (eg. halo implants to control the punch through). These reliability precautions usually end up with lower output resistance for CMOS and hence considerably lower intrinsic gain. Although for many RF applications the quality factor of passive components which are tuning out the output capacitance determines the total loading at the output of the device, higher  $g_m$  of the SiGe technology eventually results in higher gain for SiGe designs of RF and mm-wave amplifiers.

Figure 1.8: Digital intensive solutions get shrunk considerably as they are migrated to newer process nodes and the die cost will go down.

#### Matching

Matching is an important criteria for analog and RF circuits and systems design. For mm-wave application where there are multiple TX and RX chains to form a phased array solution, good matching between paths relaxes design requirements and simplifies algorithms that control the phased array operation. In the case of bipolar devices, the matching of short circuited base-emitter potential drop  $(V_{BES})$  is determined by the doping profiles of p/n areas across the emitter/base junction. With each technology improvement these doping levels are increasing and better matching is obtained consequently. Matching between threshold voltages  $(V_{TH})$  is playing the equivalent role in CMOS devices. The CMOS threshold voltage depends not only on the doping profile, but it also depends on the lateral parameters such as channel length and finger width of the device. These are much more process dependent and less stable which result in inferior matching performance of the CMOS technology with respect to bipolar SiGe counterparts.

#### Noise

For mm-wave amplifiers and buffers where there is no frequency translation,  $NF_{min}$  is sufficient to characterize a technology in terms of the noise performance. In VCOs, mixers and other building blocks where up-converting of low frequency noise takes place, flicker (1/f) noise should be considered as well.

FET and BJT transistors have different mechanisms in generating the 1/f noise. In bipolar technologies flicker noise is generated in the emitter-base junction. In CMOS technologies, defects at the interface of  $Si-SiO_2$  is responsible for the trap and release of charges that leads to the noisy current flow. The quality of the emitter-base junction and  $Si-SiO_2$  interface determines the power of the flicker noise. Present-day SiGe devices have a high-quality of Si-SiGe interface which makes their flicker noise behavior superior to CMOS devices. Furthermore CMOS scaling moves

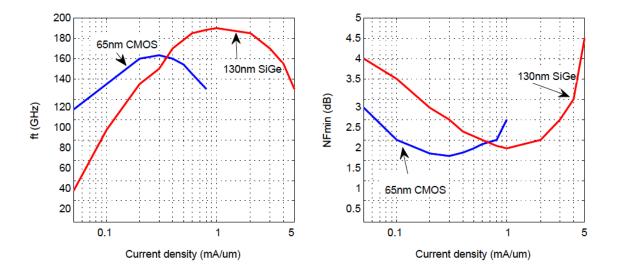

Figure 1.9: Comparing  $f_t$  and  $NF_{min}$  of 65nm CMOS and 130nm SiGe technologies

the oxide interface closer to the active channel which worsens the 1/f noise performance in each new generation of scaling.

In terms of  $NF_{min}$ , although in older technologies SiGe had a clear advantage over CMOS processes for high frequency noise, today CMOS technologies with higher source and drain dopings (lower parasitic  $R_S$  and  $R_D$ ) and higher transconductances as a result of shorter effective gate lengths (which results in lower thermal noise generated by the channel), the  $NF_{min}$  is comparable to the minimum noise figure attainable via SiGe technologies (figure 1.9).

#### $f_t$ and $f_{max}$

The most important FOMs for high frequency applications are current gain cut-of frequency  $(f_t)$  and maximum oscillation frequency  $(f_{max})$ . Maximum oscillation frequency is the highest frequency that an active device is capable of providing power gain and hence  $f_{max}$  sets a higher limit for amplifier and fundamental-frequency oscillator designs in each process node. With each generation of scaling, lateral and vertical dimensions shrink and these two FOMs increase. As depicted in Fig. 1.7,  $f_t$  of each CMOS process node is comparable to  $f_t$  of a SiGe technology which is two generations older in terms of scaling. A careful layout that minimizes external added parasitics associated with routings and interconnections will result in a  $f_{max}$  which is larger than  $f_t$  for both technologies. The quantitative relations are derived in [3] and [9]:

$$f_{max,CMOS} = \frac{f_{t,CMOS}}{2} \cdot \sqrt{\frac{C_{GS} + C_{GD}}{r_g \cdot (g_m C_{GD} + g_{ds} C_{GS} + g_{ds} C_{GD})}}$$

(1.1)

| Table 1.1: For comparable $f_t$ and current dissipation, CMOS technology has less intrinsic parasitics |

|--------------------------------------------------------------------------------------------------------|

| which makes it more vulnerable to layout added parasitics and their variations.                        |

| Technology       | CMOS(65nm) | SiGe(130nm) |

|------------------|------------|-------------|

| $I_{dc}$         | 14.5mA     | 15mA        |

| $f_t$            | 152GHz     | 160GHz      |

| $g_m$            | 40mS       | 300mS       |

| $c_{gs}/c_{\pi}$ | 30fF       | 240fF       |

| $c_{gd}/c_{\mu}$ | 12fF       | 60fF        |

$$f_{max,SiGe} = \sqrt{\frac{f_{t,SiGe}}{8\pi \cdot R_B \cdot C_{\mu}}}$$

(1.2)

As seen from above equations, lowering loss and resistive parasitics in the layout as well as decreasing the amount of output signal fed back to the input through  $C_{GD}/C_{\mu}$ , results in an  $f_{max}$  number higher than the  $f_t$  value which is a significant aid to amplifier design. An  $f_{max}$  number as high as three times the  $f_t$  has been reported in [48] which allows for amplifier and oscillator design beyond the  $f_t$  of the process.

## 1.2.3 Quantitative comparison

There are multiple figure of merits that characterize each process for the RF design.  $f_t$  and  $f_{max}$  set the limit for the operating frequency of signal generation and amplification.  $NF_{min}$  sets the minimum achievable noise figure and is very important for designing low noise amplifiers in sensitive receivers. Maximum current handling capability and break-down voltages are principal parameters determining maximum power that can be delivered to the output load in each technology. Robustness and parasitic tolerance are also important parameters for fist-pass designs that depending on the situation can favor one technology to the other one.

As depicted in figure 1.9, 65nm CMOS and 130nm SiGe technologies are on par with each other in terms of peak  $f_{max}$  and minimum NF. Consequently designing for amplifier's gain and noise figure or oscillator's maximum allowable frequency have comparable challenges in these two technologies. On the other hand peak  $f_t$  and minimum NF happens at a higher current density for the SiGe technology. Being capable of handling higher currents in SiGe  $(1.2mA/\mu m)$  with respect to CMOS  $(0.5mA/\mu m)$  and also having higher breakdown voltages  $(BV_{SiGe}=4V)$  compared to

$BV_{CMOS}=2.4V)$  make SiGe technologies more attractive for applications that output power delivery is the main concern. Higher supply voltages allow for more headroom at the output and higher linearity for building blocks designed in SiGe, therefore due to the higher gain and linearity the power figure of merit  $(FOM_{PA}=P_{out}\cdot G\cdot PAE\cdot f^2)$  of a SiGe power amplifier can be an order of magnitude higher than its CMOS counterpart.

One other aspect to compare CMOS and SiGe technologies is how insensitive these two technologies are with respect to layout parasitics and their variations, and hence how capable they are for a first pass design. According to Table 1.1 , for two CMOS and SiGe transistors biased in a way that they have the same  $I_{DC}$  and  $f_t$ , parasitic capacitances are almost an order of magnitude larger for the SiGe technology. Hence routing, interconnection and unknown layout parasitics have less effects in a SiGe design which makes this technology less sensitive and the goal of first pass design more attainable. The much higher transconductance gain of a 130nm SiGe technology ( $\sim 30mS/\mu m$ ) with respect to 65nm CMOS ( $\sim 1.4mS/\mu m$ ) makes high speed off-chip capacitance driving easier for a SiGe technology, which is an important factor for two-chip solution where there is a need for a high-speed interface.

## 1.2.4 Choice of technology

As it was stated earlier, thanks to the scaling, both standard CMOS and SiGe technologies are capable of operating at mm-wave frequency regimes. Inherently a CMOS technology is optimized mainly for digital circuitry, and digital requirements are the drive behind the direction of each generation of scaling. SiGe technologies are optimized for high frequency and RF designs with a superior metallization stack and higher performance RF transistors. Noticeably higher power handling capability and faster switching of off-chip capacitances are advantages for the SiGe technology. However for mm-wave designs in which, the antenna array is implemented in an on-chip or on-package fashion( in order to minimize RF interface parasitics), there is a flexibility in terms of antenna impedance to make it closer to the optimum output impedance that the power amplifier desires to interface. Moreover due to the small wavelengths, a larger antenna array can be utilized to exploit the spatial power combining and bridge the power delivery gap between CMOS and SiGe technologies. In conclusion both technologies can handle mm-wave design and depending on the application wether it is digital intensive (high definition video transmission, WPAN applications, etc) or more high frequency oriented (radar and imaging systems, point to point links, etc) one can be favored with respect to the other one.

Considering the cost, even though the cost of CMOS and SiGe technologies with equivalent performance seems to be comparable in terms of the die area cost, since digitally intensive applications can benefit from the area reduction as a matter of scaling, CMOS technology can result in a more cost efficient solution. Furthermore since there are more foundries worldwide offering CMOS technologies with more flexible schedules, it is more suitable for high-volume products which usually require shorter lead times. Since the technical characteristics of different runs offered by multiple foundries are similar, re-tweaking the design and sending it to another foundry should be easy with a CMOS choice which again makes it the more flexible and more suitable

pick for high-volume products. Nonetheless application that typically have smaller markets but need the extra RF performance, can benefit from the SiGe technology which is optimized to have higher performance under those circumstances. More advanced III-V compound technologies will be limited to very specialized and customized solutions in the future of mm-wave systems and circuits design.

In conclusion CMOS has advantages of lower power, lower wafer cost at a comparable node and shorter fab cycles. SiGe offers advantages of high speed combined with high drive capability and low noise. The ultimate selection will be based on system specifications.

# **Chapter 2**

# **Transmit/Receive Switching**

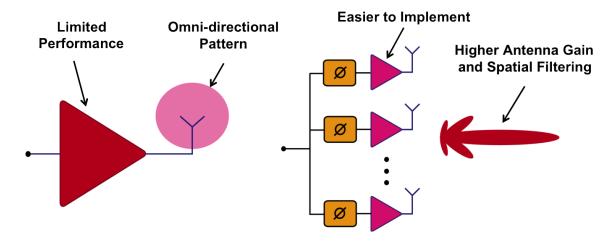

Previous works [44]-[48] have demonstrated the feasibility of many key mm-wave transceiver building blocks in standard digital CMOS processes. On the other hand, there have been relatively few demonstrations of transmit/receive switches operating at mm-wave frequencies, which is a key building block in RF systems. Operating at mm-wave frequencies has many advantages. One key advantage is due to small wavelengths, which allows antennas to be realized on chip or on the package, further reducing the cost of a system. Moreover many antennas could be integrated with suitable phase shifters to create phased array systems that effectively increase the aperture size and directivity of transmit/receive antennas by a factor of N (number of antennas). Spatial filtering achieved by a phased antenna array system alleviates impairments such as delay spread and co-channel interference and further helps to extend the communication range and bandwidth. Without a transmit/receive (T/R) switch, two separate antennas should be employed for the receiver and transmitter, which translates to half the transmit/receive antenna gain and aperture size for a given area. Whereas if T/R switches with performances that pass the system requirements can be implemented in the same CMOS chip, a single antenna will be shared between the transmitter and receiver and twice the number of antennas (antenna array gain) will be realizable out of the same die area. Hence T/R switch can save a great deal of area, and thus lower the cost, since antennas are relatively large. Therefore designing CMOS T/R switches at mm-wave frequencies is an important goal toward the realization of a low cost mm-wave system.

The design of T/R switches is challenging since it resides before the LNA and after the PA. In order not to degrade the sensitivity of the receiver and the transmit power, switches should incur low insertion loss in the ON mode. To have enough directivity, insertion loss should be rather high when the switch is OFF. To keep the LNA and PA isolated, enough isolation between the two thru ports should be ensured and finally switches should be capable of handling high powers beyond the PA output compression point. As with all high frequency circuits, input and output ports should be matched to guarantee adequate return loss for incident signals.

Figure 2.1: A fully integrated transceiver with an on-chip antenna requires an integrated T/R switch to save die area.

# 2.1 Antenna array reuse via T/R switching

#### 2.1.1 On-chip or On-package antennas

Modern CMOS technologies are fabricated on a relatively conductive substrate (conductivity of  $\sigma \sim 10 S/m$ ). The high permittivity of silicon substrate ( $\epsilon = 11.7$ ) tends to redirect the electromagnetic energy radiated by on-chip antennas to the lossy substrate. Surface and substrate modes are additional problems needed to be addressed with on-chip antenna design. There are techniques to mitigate these problems, one such technique is placing an electromagnetic hemispherical lens on the backside of the die ([30]). An electromagnetic lens on the backside of the wafer reshapes the medium underneath the antenna, collects surface and substrate mode radiations and converts them to a useful radiation from the back. Despite these solutions, having on-chip antennas incur a noticeable loss in advanced CMOS technologies due to conductive substrate and thin metal stacks. Moreover since the wavelength at 60GHz is 5mm, accounting for  $\epsilon$  of  $SiO_2$  reduces the size of the antenna but still the spacing between antennas should be  $\lambda_0/2$  where  $\lambda_0$  is the wavelength of the signal in the air. The on-chip real estate that would be devoted to the antenna array would be substantial for large number of antennas in the array. Therefore having antennas on the package seems to be a viable solution according to these facts:

- 1. Higher performance antennas will be available on the package which has less conductive and dielectric losses compared to a silicon substrate.

- 2. Large arrays will be implemented on low-cost packages instead of a more expensive silicon wafer. This lowers the implementation cost.

- 3. Multi-layer boards with high-quality metallization not only provide good design environments for the antenna array, but they can also be employed to route signal, power and ground lines and furthermore act as a heat-sink to take the dissipated power off the chip.

Figure 2.2: In case of not including T/R switches, two separate RX and TX arrays are required (B), which correspondingly lengthens interconnection routings and increases their associated loss

## 2.1.2 Size and loss trade-off in a transmit/receive array

Even when antennas are implemented on a package, having a smaller package makes the over-all solution more cost-effective and allows for easier adoption of the solution by WPAN applications such as smart phones, portable media players, etc. But whenever the package size is a secondary issue, then removing TR switches should result in a better over-all performance since there is no extra component after the PA to harm the TX linearity and output power nor is there a component before LNA which degrades the receiver noise figure and consequently sensitivity. However in practical cases, for solutions without the TR switch, bigger size of the package means longer on-package routings to connect front-ends residing on the chip to the antennas implemented on the package (figure 2.2). The routing loss is as important as the TR switch loss since it directly affects the transmit power and receive sensitivity. Depending on the array size and and on-package transmission line loss characteristics, the resultant routing loss can offset the benefit of not including a T/R switch.

To have a quantitative comparison we consider the scenarios described in figure 2.2. In figure 2.2-a, one antenna array is shared between TX and RX via TR switches and In figure 2.2-b two separate arrays are used for RX and TX portions of the transceiver. To compare these two scenarios we compare the maximum communication range achievable by each case while assuming nominal values of transmitter  $P_{out}$ =10dBm, receiver NF=10dB and a required SNR of 10dB for

Figure 2.3: Graph of the maximum achievable communication range in two configurations of shared or separate arrays (for both small and large arrays). For larger arrays the routing loss is more detrimental than the T/R switch loss and higher quality packaging should be employed.

maintaining the communication link at the frequency band of 57 - 64GHz.

According to the Friis equation [12](if we account for the transmit and receive array directivities in the TX effective radiated power (EIRP) and RX sensitivity and not in the free space path loss), the maximum achievable communication link is related to the maximum tolerable path loss as:

$$Path \ Loss = \left(\frac{\lambda}{4\pi R}\right)^2 \Rightarrow R = \frac{\lambda}{4\pi\sqrt{Path \ Loss}}$$

(2.1)

To calculate the maximum allowable path loss we need to know the effective isotropic radiated power at the transmitter and the minimum detectable signal at the receiver:

$$Path \ Loss = EIRP - P_{Noise} - NF - SNR_{min} \tag{2.2}$$

The effective isotropic radiated power for an array of N omnidirectional antenna elements will be :

$$EIRP = P_{PA} + 20Log(N) - Loss_{TR} - Loss_{Routing}$$

(2.3)

In a N-element phased array receiver since signals add up in the voltage domain and noises get combined in the power domain, as it will be derived in the next chapter, the total noise factor of the array will be reduced to:

$$F_{Array} = \frac{1}{N}(F_{element}) \tag{2.4}$$

Figure 2.4: Measured  $S_{21}$  of an NMOS transistor acting as a series switch in a 50 $\Omega$  environment.

Where  $F_{element}$  is the noise factor of each path at the antenna:

$$F_{element} = 1 + \frac{F_{receiver} - 1}{Loss_{routing} + Loss_{TR}}$$

(2.5)

Routing loss depends on the dies size, array size/shape and the loss characteristic of the package. For the scenario depicted in figure 2.2, the maximum routing length will be calculated as:

Routing Length =

$$\sqrt{\left(\frac{X_{package} - X_{Chip}}{2}\right)^2 + \left(\frac{Y_{package} - Y_{Chip}}{2}\right)^2}$$

(2.6)

Assuming inter-element spacing of half the wavelength and plugging previously mentioned numbers for these two array configurations, figure 2.3 depicts the maximum achievable communication range as a function of the routing transmission line loss. As can be seen from figure 2.3, for larger arrays (100 element array in this case) transmission line routing loss is more pronounced and unless very low loss routing is realizable on package, including the T/R switch will provide better overall performance. For smaller arrays (16 antenna element in figure 2.3) more routing loss is tolerable. However for ultimate single-chip solutions where the antenna array is realized on chip, due to higher on-chip routing losses ( $\sim 1dB/mm$ ) a solution with a shared array between TX and RX through a T/R switch looks more promising.

# 2.2 T/R switching configurations

## 2.2.1 Series vs Shunt switching

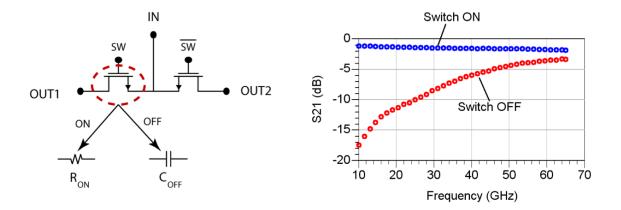

By its nature, when the gate terminal of a MOS transistor is driven by a rail to rail voltage, it acts as a switch. In fact this single transistor switch is sufficient for many digital and analog

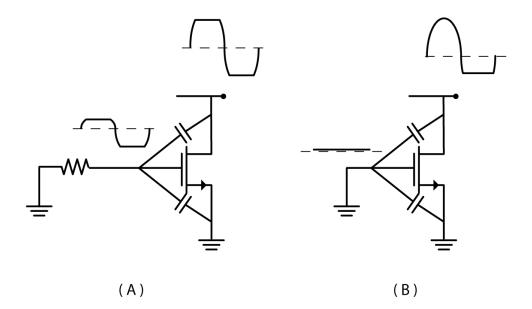

Figure 2.5: Combinations of series and shunt switches in a T (A) or  $\pi$  (B) or L-shape configuration (C)[33] decrease the amount of off-state leakage at the price of degrading the on-state insertion loss