# UC Santa Cruz UC Santa Cruz Electronic Theses and Dissertations

## Title

Improving Performance of Solid State Drives (SSDs) Using Machine Learning

## Permalink

https://escholarship.org/uc/item/1t04t9mg

# Author

Chakraborttii, Chandranil

# Publication Date

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution-ShareAlike License, available at <u>https://creativecommons.org/licenses/by-sa/4.0/</u>

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

### IMPROVING PERFORMANCE OF SOLID-STATE DRIVES USING MACHINE LEARNING

A dissertation submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

### COMPUTER SCIENCE

by

### Chandranil Chakraborttii

June 2021

The Dissertation of Chandranil Chakraborttii is approved:

Professor Heiner Litz, Chair

Professor Ethan Miller

Professor Yang Liu

Quentin Williams Vice Provost and Dean of Graduate Studies Copyright © by

Chandranil Chakraborttii

2021

# **Table of Contents**

| Al | ostrac  | et      |                                                                      | vii |

|----|---------|---------|----------------------------------------------------------------------|-----|

| Li | st of l | Figures |                                                                      | ix  |

| Li | st of [ | Fables  |                                                                      | xii |

| 1  | Intr    | oductio | n                                                                    | 1   |

| 2  | Bac     | kground | 1                                                                    | 9   |

|    | 2.1     | Flash I | Memory                                                               | 9   |

|    |         | 2.1.1   | Garbage Collection and Write Amplification in Flash                  | 13  |

|    | 2.2     | Prefeto | ching                                                                | 16  |

|    | 2.3     | Machi   | ne Learning Techniques                                               | 18  |

|    |         | 2.3.1   | Oversampling and Boosting                                            | 19  |

|    |         | 2.3.2   | Isolation Forests                                                    | 21  |

|    |         | 2.3.3   | Long Short Term Memory Networks                                      | 22  |

|    |         | 2.3.4   | Auto Encoders                                                        | 26  |

|    |         | 2.3.5   | Embeddings                                                           | 27  |

|    |         | 2.3.6   | Temporal Convolutional Networks                                      | 28  |

| 3  | SSD     | Failure | e Prediction                                                         | 31  |

|    | 3.1     | Introdu | uction                                                               | 31  |

|    | 3.2     | Resear  | ch Questions (RQ)                                                    | 35  |

|    |         | 3.2.1   | RQ A: Which SSD telemetry features contribute to SSD failures?       | 35  |

|    |         | 3.2.2   | RQ B: Can we predict SSD failures by training only on healthy drives |     |

|    |         |         | (one class training)?                                                | 35  |

|    |         | 3.2.3   | RQ C: How does the performance of one-class model training compare   |     |

|    |         |         | with state-of-the-art techniques?                                    | 36  |

|    |         | 3.2.4   | RQ D: Can we interpret SSD failures?                                 | 36  |

|    |         | 3.2.5   | RQ E: Can one class models be used to predict unseen SSD failures? . | 36  |

|    | 3.3     | Resear  | ch Contributions                                                     | 37  |

|    |         | 3.3.1   | Accurate Prediction of SSD Failures                                  | 37  |

|   |     | 3.3.2          | Predicting unseen failures                                                                                                |

|---|-----|----------------|---------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.3.3          | Interpreting SSD Failures 44                                                                                              |

|   | 3.4 | Metho          | dology                                                                                                                    |

|   |     | 3.4.1          | Data Preprocessing                                                                                                        |

|   |     | 3.4.2          | Feature Selection                                                                                                         |

|   |     | 3.4.3          | Oversampling and Boosting 49                                                                                              |

|   |     | 3.4.4          | 1-Class ML Models                                                                                                         |

|   |     | 3.4.5          | Deployed System                                                                                                           |

|   | 3.5 | Result         | s52                                                                                                                       |

|   |     | 3.5.1          | Oversampling and Boosting                                                                                                 |

|   |     | 3.5.2          | Accurate Prediction of SSD Failures                                                                                       |

|   |     | 3.5.3          | Adaptivity to Unseen Failures                                                                                             |

|   |     | 3.5.4          | Interpreting SSD Failures                                                                                                 |

|   |     | 3.5.5          | Sensitivity Studies                                                                                                       |

|   | 3.6 |                | $ssion \dots \dots$ |

|   |     | 3.6.1          | 1-Class Isolation Forest                                                                                                  |

|   |     | 3.6.2          | 1-Class Autoencoder                                                                                                       |

|   | 3.7 |                | usion                                                                                                                     |

|   | 3.8 | Public         | ations                                                                                                                    |

| 4 | Neu | ral Netv       | work based Prefetching 68                                                                                                 |

| • | 4.1 |                | uction                                                                                                                    |

|   | 4.2 |                | rch Questions                                                                                                             |

|   |     | 4.2.1          | RQ A: Can sequence-to-sequence deep learning models learn the IO                                                          |

|   |     |                | access patterns in real-world applications?                                                                               |

|   |     | 4.2.2          | RQ B: Can the neural network address timeliness by predicting multiple                                                    |

|   |     |                | accesses ahead of time?                                                                                                   |

|   |     | 4.2.3          | RQ C: How does the performance of the neural network-based                                                                |

|   |     |                | prefetcher compare with state of the art?                                                                                 |

|   |     | 4.2.4          | RQ D: Can we use the learned IO access patterns to predict IO accesses                                                    |

|   |     |                | in new, unseen workloads?                                                                                                 |

|   |     | 4.2.5          | Neural Network based Prefetching                                                                                          |

|   | 4.3 |                | m Statement                                                                                                               |

|   | 4.4 | Propos         | sed Prefetching Technique                                                                                                 |

|   |     | 4.4.1          | Data Preparation for Reducing the Output Label Space                                                                      |

|   |     | 4.4.2          | Model Architecture                                                                                                        |

|   |     | 4.4.3          | Timeliness                                                                                                                |

|   |     | 4.4.4          | Address Mapping Learning    80                                                                                            |

|   | 4.5 | Metho          | dala and Engening and al Catage Of                                                                                        |

|   |     |                | dology and Experimental Setup 81                                                                                          |

|   |     | 4.5.1          | Model Training                                                                                                            |

|   |     | 4.5.2          | Model Training81Prefetcher Simulation Environment83                                                                       |

|   |     | 4.5.2<br>4.5.3 | Model Training                                                                                                            |

|   |      | 4.6.1   | Prefetcher Accuracy, Precision and Recall                            | 84  |

|---|------|---------|----------------------------------------------------------------------|-----|

|   |      | 4.6.2   | Impact of Cache Size, Look-Back, and Predict-Ahead                   | 85  |

|   |      | 4.6.3   | Evaluation of Address Mapping Learning                               | 88  |

|   | 4.7  | Conclu  | usion                                                                | 89  |

|   | 4.8  | Publica | ations                                                               | 90  |

| 5 | Red  | ucing W | Vrite Amplification in SSDs using Machine Learning                   | 91  |

|   | 5.1  | Introdu | uction                                                               | 91  |

|   | 5.2  | Resear  | ch Questions                                                         | 94  |

|   |      | 5.2.1   | RQ A: Can sequence-to-sequence deep learning models learn the death- |     |

|   |      |         | time patterns of logical block addresses in real-world applications? | 94  |

|   |      | 5.2.2   | RQ B: Can we design a data placement policy for optimizing GC over-  |     |

|   |      |         | head, having perfect knowledge of future death-times?                | 95  |

|   |      | 5.2.3   | RQ C: How does the performance of our machine learning-based data    |     |

|   |      |         | placement policy (ML-DT) compare with state-of-the-art techniques? . | 95  |

|   |      | 5.2.4   | RQ D: Can we use the learned death-time patterns to predict IO death |     |

|   |      |         | time patterns in new, unseen workloads?                              | 95  |

|   | 5.3  | Prior V | Work on reducing Write Amplification (WA)                            | 96  |

|   |      | 5.3.1   | Write Amplification Problem                                          | 96  |

|   |      | 5.3.2   | Hot-Cold Separation                                                  | 97  |

|   |      | 5.3.3   | Frequency-based approaches                                           | 97  |

|   | 5.4  | Death-  | time Technique                                                       | 98  |

|   |      | 5.4.1   |                                                                      | 100 |

|   |      | 5.4.2   | 6                                                                    | 102 |

|   |      | 5.4.3   | 5                                                                    | 106 |

|   | 5.5  | -       |                                                                      | 108 |

|   |      | 5.5.1   | 1                                                                    | 108 |

|   |      | 5.5.2   | 6                                                                    | 109 |

|   |      | 5.5.3   | FTL Simulator                                                        |     |

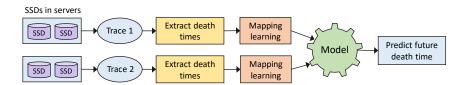

|   |      | 5.5.4   | Mapping Learning                                                     |     |

|   | 5.6  |         | S                                                                    |     |

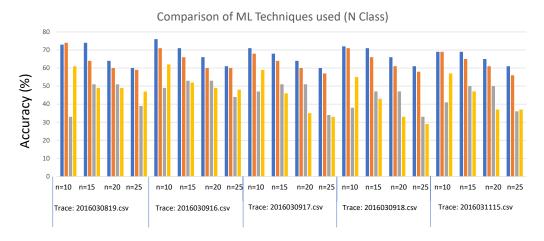

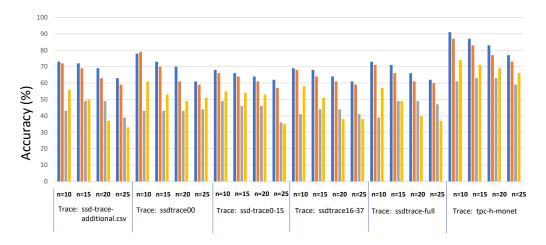

|   |      | 5.6.1   | Evaluation of ML models                                              |     |

|   |      | 5.6.2   | Guaranteeing no GC overhead with Oracle-DT                           |     |

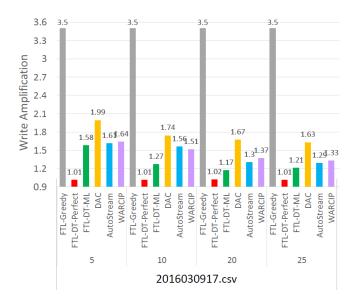

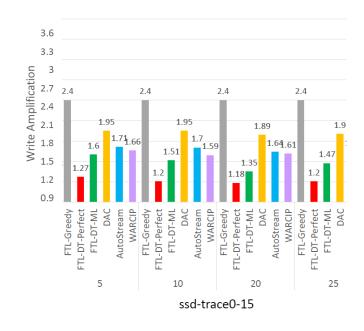

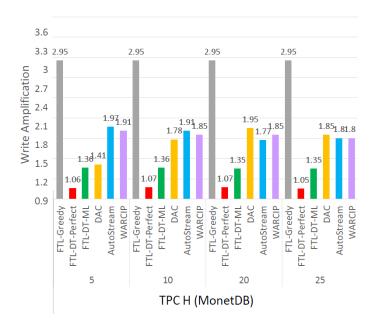

|   |      | 5.6.3   | Comparison with baselines                                            | 117 |

|   |      | 5.6.4   | 1 1                                                                  | 121 |

|   |      | 5.6.5   | 5 5 1                                                                | 122 |

|   |      | 5.6.6   | FI 8 8                                                               | 124 |

|   | 5.7  | Conclu  |                                                                      | 126 |

|   | 5.8  | Publica | ations                                                               | 127 |

| 6 | Rela | ted Wo  | rk                                                                   | 128 |

|   | 6.1  |         |                                                                      | 128 |

|   | 6.2  | Neural  | Network based Prefetching                                            | 132 |

|    | 6.3 Garbage Collection Optimization using Machine Learning | 137 |  |

|----|------------------------------------------------------------|-----|--|

| 7  | Conclusion                                                 | 142 |  |

| 8  | Acknowledgements                                           | 144 |  |

| BI | BIBLIOGRAPHY                                               |     |  |

### Abstract

### Improving Performance of Solid-State Drives using Machine Learning

by

#### Chandranil Chakraborttii

Flash-based storage drives such as solid-state disks are replacing traditional spinning disk drives for an increasing number of applications. User interfacing cloud-based applications benefit from the low, sub-millisecond access latency of solid-state drives (SSDs). Virtually all smartphones are using flash memory as their storage media due to features such as low power consumption, larger storage density, small footprint and shock resistance. SSDs provide faster boot times, higher read and write bandwidth as well as improved durability. Nevertheless, flash-based storage devices show several disadvantages. Technology scaling, 3D integration as well as multi-level bit cells have continuously increased storage density and capacity, however, this has also reduced the reliability of flash. Flash memory also suffer from overheads such as garbage collection, which can reduce write bandwidth and introduce high tail latency. Furthermore, while NAND flash devices provide significantly lower latency than spinning disks, flash has still orders of magnitude higher latency than DRAM.

This work leverages machine learning techniques to improve the performance of flash based storage systems. This improvement reflects in three major directions - improving response time, reliability and lifetime of flash based storage devices. For improving response time, we leverage sequence-to-sequence machine learning techniques to learn the spatial IO access patterns thereby improving prefetching performance. To achieve high performance, we address the challenges of prefetching in very large sparse address spaces, as well as prefetching in a timely manner by predicting ahead of time. To improve reliability, we propose an approach of automatically predicting and interpreting future drive failures. Finally, we present a machine learning based approach for reducing the number of rewrites required to store data in log structured file systems via death-time prediction of logical block addresses. We leverage the predicted death-times in designing *ML-DT*, a near-optimal data placement technique that minimizes the number of extra writes required to store data in log structured storage systems thereby improving device lifetime.

# **List of Figures**

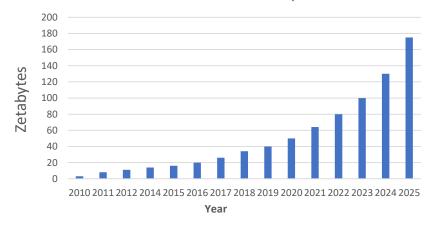

| 1.1  | Annual Size of Global Datasphere                        | 2  |

|------|---------------------------------------------------------|----|

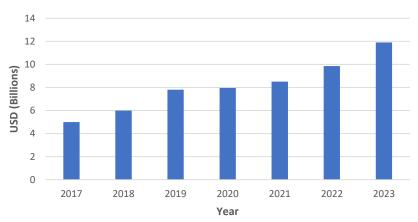

| 1.2  | Investment in Global Data Center Market                 | 4  |

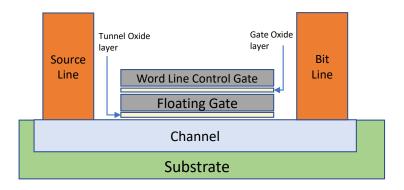

| 2.1  | Representation of flash memory cell                     | 10 |

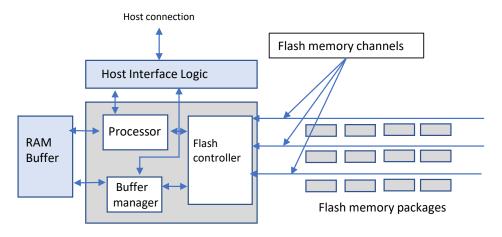

| 2.2  | General architecture of a Flash SSD                     | 11 |

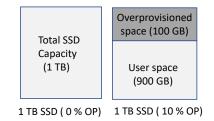

| 2.3  | Overprovisioning in SSDs                                | 14 |

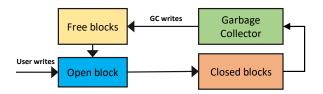

| 2.4  | Lifecycle of an SSD block                               | 15 |

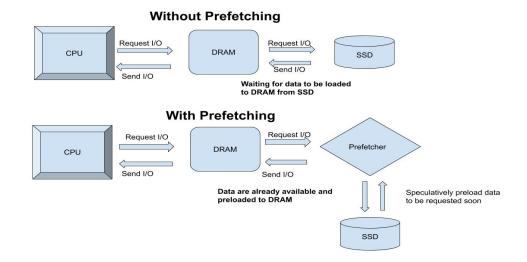

| 2.5  | Demonstration of Prefetching in SSDs                    | 18 |

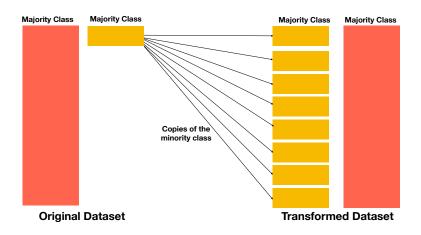

| 2.6  | Demonstration of Oversampling process                   | 19 |

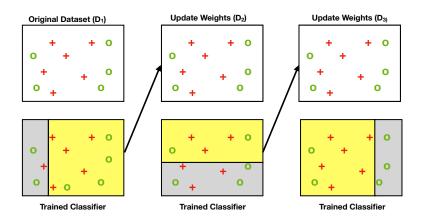

| 2.7  | Demonstration of Boosting                               | 21 |

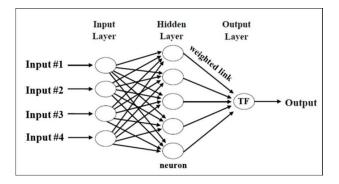

| 2.8  | General architecture of vanilla ANN                     | 22 |

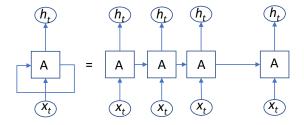

| 2.9  | General architecture of vanilla RNN                     | 23 |

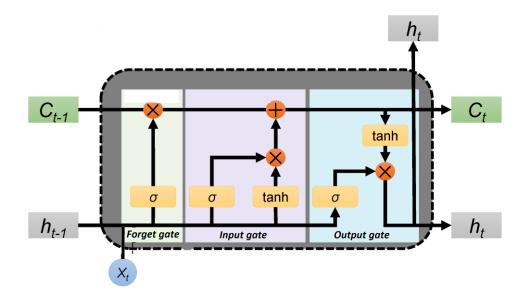

| 2.10 | General architecture of an LSTM cell                    | 24 |

| 2.11 | Internal design of Auto Encoders                        | 26 |

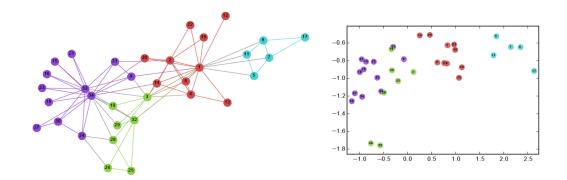

| 2.12 | Demonstration of Embeddings [1]                         | 27 |

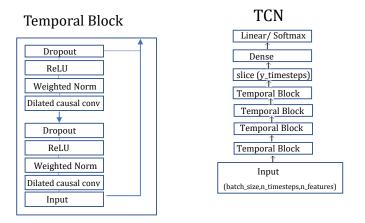

| 2.13 | General architecture of temporal convolutional networks | 29 |

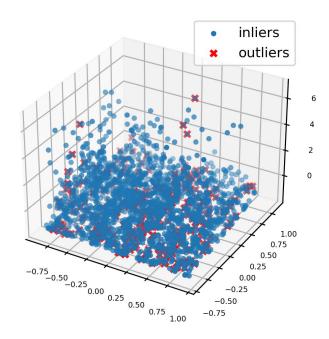

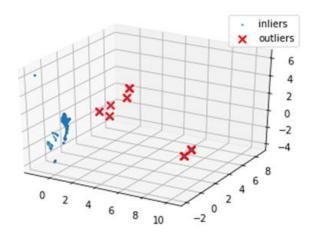

| 3.1  | PCA with all 21 Features                                                       | 39 |

|------|--------------------------------------------------------------------------------|----|

| 3.2  | PCA with Top 9 Selected Features                                               | 40 |

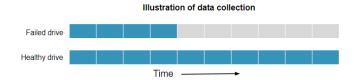

| 3.3  | Illustration of data collection process                                        | 41 |

| 3.4  | Autoencoder Design                                                             | 43 |

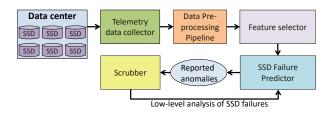

| 3.5  | Block diagram of the Deployed System                                           | 52 |

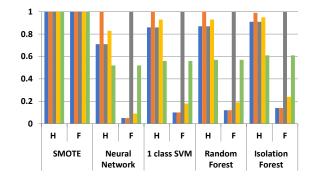

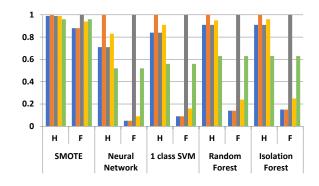

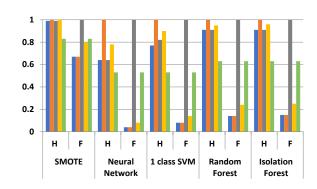

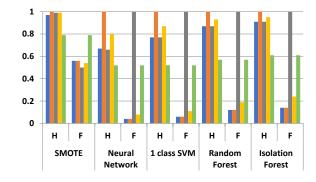

| 3.6  | Predicting 1 week ahead (N=1)                                                  | 54 |

| 3.7  | Predicting 2 weeks ahead (N=2)                                                 | 54 |

| 3.8  | Predicting 3 weeks ahead (N=3)                                                 | 55 |

| 3.9  | Predicting 4 weeks ahead (N=4)                                                 | 55 |

| 3.10 | Comparison of Different Machine Learning Approaches for Prediction of          |    |

|      | Healthy (H) and Failed (F) drives                                              | 55 |

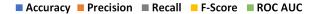

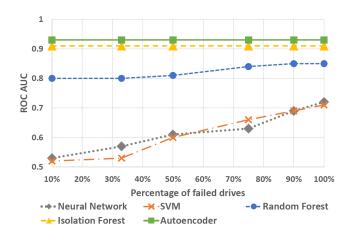

| 3.11 | ROC AUC Score comparison of the five evaluated Machine Learning Techniques     | 57 |

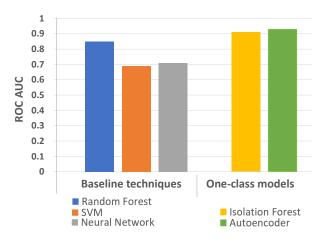

| 3.12 | Accuracy, Precision, Recall and Fscore for the five evaluated Machine Learning |    |

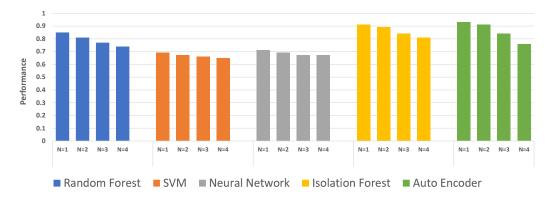

|      | Techniques                                                                     | 58 |

| 3.13 | Predicting unseen failures                                                     | 60 |

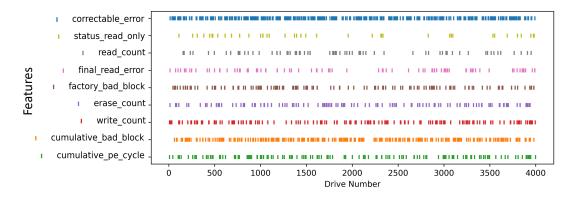

| 3.14 | Interpreting SSD Failure Reasons                                               | 60 |

| 3.15 | ROC AUC score when predicting up to 4 days ahead                               | 62 |

| 3.16 | Impact of Feature Selection Techniques                                         | 65 |

| 4.1  | Prefetching motivation                                                         | 69 |

| 4.2  | Model architecture                                                             | 79 |

|      |                                                                                |    |

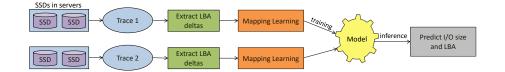

| 4.3  | Block diagram of the Address Mapping Learning process                          | 80 |

| 4.4  | Block diagram of the evaluation process using our simulator                     | 83  |

|------|---------------------------------------------------------------------------------|-----|

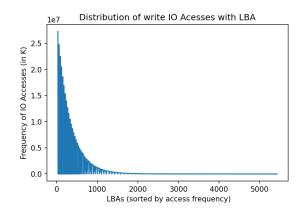

| 5.1  | LBA write frequency distribution for VDI                                        | 92  |

| 5.2  | Baseline vs. Frequency vs. Oracle-DT Policy                                     | 100 |

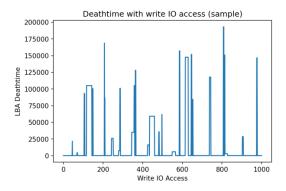

| 5.3  | Death-times varying widely (sample)                                             | 101 |

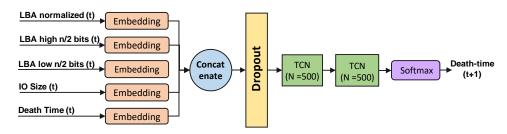

| 5.4  | Model Architecture                                                              | 104 |

| 5.5  | Mapping Learning Architecture                                                   | 110 |

| 5.6  | Comparison of ML Techniques for VDI traces (N Class)                            | 114 |

| 5.7  | Comparison of ML Techniques for RocksDB and TPC-H traces (N Class)              | 114 |

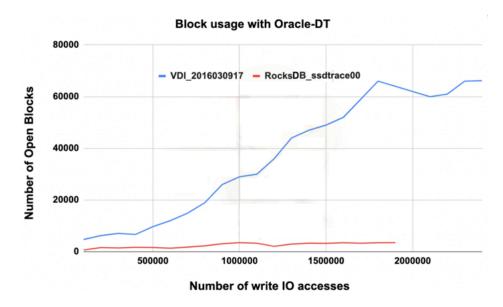

| 5.8  | Block usage per trace with <i>Oracle-DT</i>                                     | 115 |

| 5.9  | Block usage over time with <i>Oracle-DT</i>                                     | 116 |

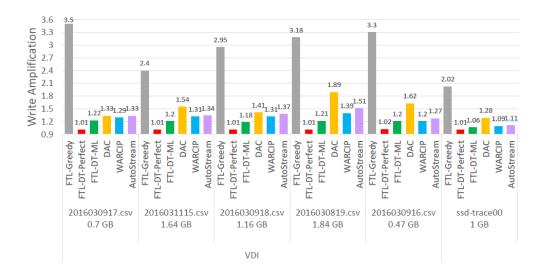

| 5.10 | FTL comparison with baselines (VDI traces)                                      | 117 |

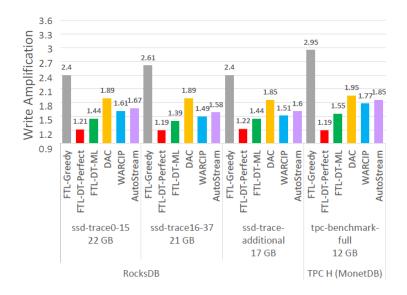

| 5.11 | FTL comparison with baselines (RocksDB and TPC-H traces)                        | 118 |

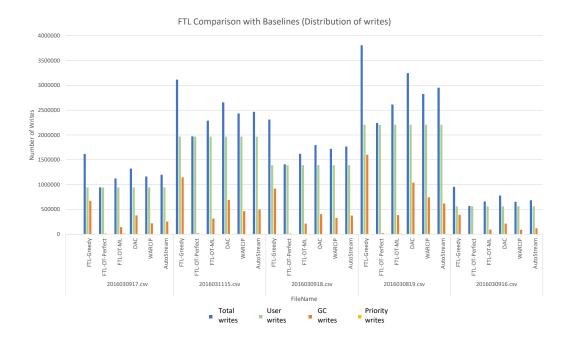

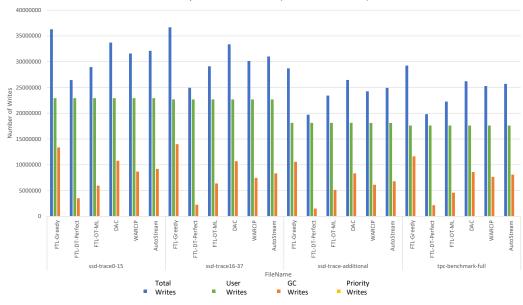

| 5.12 | Distribution of writes comparison with baselines (VDI traces)                   | 119 |

| 5.13 | Distribution of writes comparison with baselines (RocksDB and TPC-H traces)     | 119 |

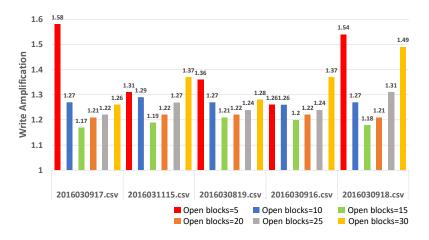

| 5.14 | Impact of number of open blocks (VDI trace)                                     | 122 |

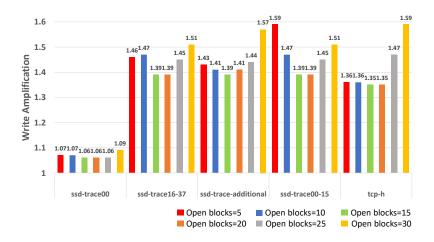

| 5.15 | Impact of number of open blocks(RocksDB trace)                                  | 123 |

| 5.16 | Impact of number of open blocks(TPC-H trace)                                    | 123 |

| 5.17 | Sensitivity Study (VDI traces)                                                  | 124 |

| 5.18 | Sensitivity Study (RocksDB and TPC-H)                                           | 124 |

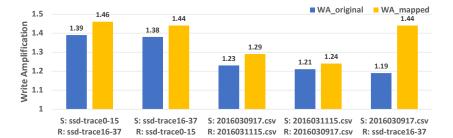

| 5.19 | Mapping learning results using different Source (S) and Recipient (R) workloads | 126 |

# **List of Tables**

| 3.1 | All 21 features collected                                                  | 46  |

|-----|----------------------------------------------------------------------------|-----|

| 3.2 | Top features selected                                                      | 49  |

| 3.3 | Results from SMOTEBoost and RUSBoost                                       | 54  |

| 3.4 | Model training time (N = 1)                                                | 66  |

|     |                                                                            |     |

| 4.1 | Dataset Description                                                        | 82  |

| 4.2 | Performance comparison of Our proposed prefetcher against baselines        | 86  |

| 4.3 | Impact of different predict values on our prefetcher performance           | 87  |

| 4.4 | Impact of cache size on the accuracy of our and two baseline prefetchers   | 87  |

| 4.5 | Performance of Address Mapping Learning (AML)                              | 89  |

|     | ~                                                                          |     |

| 5.1 | Comparison of machine learning approaches for death-time range prediction. | 112 |

# **Chapter 1**

# Introduction

Flash memory is a persistent storage technology. Flash memory is used as a means of persistent storage in mobile devices and as mass storage for cloud or general computing systems. Modern flash-based solid-state drives (SSDs) present as a high-performance and cost-effective storage solution, providing terabytes of capacity, over a million I/O operations per second (IOPS), and sub 100 microsecond read latency. The two most common types of flash storage include NAND flash and NOR flash. NAND flash provides higher write and erase speeds than NOR flash; hence, it is used more commonly than NOR flash.

Prior to the advent of SSDs, hard disk drives (HDDs) were the most popular secondary storage choice. A conventional HDD is a storage device with spinning disks and a head to read the data, making it susceptible to mechanical failures. On the other hand, SSDs can store data within a chip without requiring any moving parts and hence is less prone to mechanical failures. Flash-based solid-state drives (SSDs) offer superior read/write performance and have higher ability to withstand harsh conditions such as shocks, vibrations, and temperature fluctuations, compared to the traditional hard-disk drives (HDDs). For example, the slowest SSD can outperform the fastest HDD in terms of the number of read/write operations. Flash storage devices can perform read operations as fast as dynamic random-access memory (DRAM) and can perform write operations hundreds of times faster than HDDs. For example, a computing system running Windows 10 operating system (OS) in SSD can start a usable desktop in less than 10 seconds [2]. SSDs are more economical in terms of power usage as they are tuned to go to sleep and wake up quickly and reliably. They can also withstand vibrations, making them durable and ideal for use within portable devices [3]. Although the storage cost per bit is higher for SSDs, they are faster, cooler, and more silent than traditional HDDs. Additionally, SSDs have a lower Annual Replacement Rate (ARR) than their hard-disk drive counterparts [4].

Annual Size of Global Datasphere

Figure 1.1: Annual Size of Global Datasphere

The recent decade has seen a major shift towards NVME flash-based storage from traditional HDDs, especially for data centers supporting cloud services. Studies [2] have shown

an 5-fold increase in the use of SSDs for cloud systems in the last decade alone. The lower access latency combined with lower power consumption and higher bandwidth render make flash-based solid-state drives (SSDs) a higher-performance alternative to hard disk drives in the cloud and mobile environments.

Recent advances in flash technologies such as transistor scaling and multiple layered cells (MLC) have increased the storage density and capacity, and modern SSDs can offer a storage capacity of tens of terabytes (TB). In addition to the huge volume, SSD's high throughput meets the requirements for enterprise applications by virtue of its massively parallel architecture at the back-end, including multiple channels, multiple dies per channel, multiple logic units (LUNs) per die, and multiple planes per LUN. Parallel I/O operations can be performed among independent planes giving rise to a great potential for very high I/O performance.

Along with the rise of the popularity of SSDs, the recent decade has also seen an explosion in storage requirements for data. From Figure 1.1, we can see a nearly exponential increase in storage requirements since 2010. Future storage requirements are expected to increase further to 175 zeta bytes (ZB) in the year 2025 [5]. Data centers are high-performance computers that store and process data. Every organization, which requires handling of user data uses data centers. Data centers usually consist of racks and cabinets containing computer hardware and batteries with backup generators to guard against power breakdown. They also maintain high-grade cooling systems to keep the computers from overheating. Data in the cloud are stored in data centers located in remote locations, and the users access them via the internet. Data centers store massive amounts of data worldwide and are projected to store most user data

in the future. They allow fast, reliable, and secure access to data. Investments in data centers have seen a continuous year upon year increase, as can be seen from Figure 1.2.

Investment in Global Data Center Market

Figure 1.2: Investment in Global Data Center Market

Modern data centers offer a variety of services at different pricing levels with performance depending on cost. For example, training AlexNet [6] on a virtual machine (VM) with no GPU support will take significantly longer time for training than a system with GPU support. In modern data centers, just optimizing for performance is not enough as we need to take into account the cost of the hardware and operational costs. Hence the most important metric for optimization is total cost of ownership (TCO)/Performance. The goal is to maximize the return on investment and performance given the cost or hardware constraints. Requirements of such a system include high reliability, efficient resource utilization, and high endurance. High reliability requires the system components to be robust to unforeseen circumstances (such as power failures or voltage fluctuations) and continue delivering high performance. In contrast, high resource utilization ensures that we get the maximum performance out of the system. High endurance deems the system can run without replacement or repair for a significant period to recuperate the investment. (5000-50000 write/erase cycles for flash drives).

Flash drives are very attractive for use within mass storage systems. However, they have some limitations. The flash memory chips have a limited lifetime as the number of write operations per memory cell is limited, and the performance of flash chips degrades over time due to wear out. To improve the lifetime of flash, the system firmware needs to distribute the writes as evenly as possible, referred to as wear leveling. Thus, it is challenging to guarantee a 'stable' flash memory-based system that is as highly reliable as a disk-based system. Although SSDs have lower Annual Failure Rates (AFR) than disk-based alternatives [4], they are more susceptible to bad sectors and block errors. With the recent advances in flash technology, the flash chip capacity has increased manifolds over the past decade, but it also resulted in a decrease in the reliability of flash memory [7]. Moreover, SSD-related failures are considered more critical than HDD-related failures. According to a study, SSD-related failures resulted in the replacement of 79% of the drives in the cloud, compared to 11% for HDD-related failure [8]. Hence, SSDs remain vulnerable to sudden device failures resulting in data loss or application crashes, which is undesirable.

Another limitation of Solid-state drives (SSDs) is the access latency or the bandwidth bottleneck. Although SSDs deliver significantly higher speeds than HDDs, SSDs still remain a performance bottleneck of computing systems [9]. Processors and DRAM technologies support three orders of magnitude lower access latency. As a result, the system's performance is often bottlenecked by the speed of SSDs, resulting in poor utilization of resources as higher levels of memory have to wait for the slower SSDs to respond to the request.

SSDs also suffer from the problem of write-amplification due to a lack of support for in-place data updates. Instead of overwriting the data directly in place, SSDs need to first perform an erase operation before another program operation (erase-then-write) can occur. Furthermore, erase operations are performed at the granularity of blocks, whereas a block can hold multiple 4K pages (the unit of writes). As a result, SSDs support updates by implementing a log-structured storage mechanism [10], where overwritten pages are appended to an open block. A logical-to-physical (L2P) translation table maps logical block addresses (LBA) to physical locations in the flash chips. When an LBA is overwritten, the L2P is updated so that the LBA points to the new physical location of the page, invalidating the old physical location of the LBA. When an SSD exhausts its blocks, garbage collection (GC) cleans up the blocks by moving valid pages to other free blocks, inducing write amplification in the process. Write amplification is problematic for two reasons. First, by introducing additional writes, the lifetime and endurance of the SSDs are reduced. Second, the extra GC writes introduce performance interference by delaying the regular user reads. Modern SSDs and operating systems offer a wide range of telemetry data for analysis. Utilizing I/O access tracing in hardware and software enables the collection of large, clean, and automatically labeled datasets that can fuel powerful machine learning models. This work attempts to alleviate the problems mentioned above using machine learning techniques.

To improve the reliability of SSDs, we introduced a novel machine learning (ML)

based technique to predict which drives are likely to fail within a specific time range in the future. In order to train the machine learning model to predict failures, we first collect the telemetry information from more than 30,000 SSDs running live applications in Google datacenters over a period of 6 years. We show that our proposed approaches can effectively predict failures in drives with high accuracy and recall, thereby capturing all predicted failures. Furthermore, we leverage autoencoders to interpret the reasons for why the machine learning model flags a drive to fail. We discuss the project in more detail in Chapter 3.

For improving resource utilization, we propose a deep neural network (DNN) based prefetching to reduce response time. Prefetching predicts future block accesses and preloads them into the main memory ahead of time. In Chapter 4, we discuss the challenges of prefetching in SSDs, explain why prior approaches fail to achieve high accuracy, and present a neural network-based prefetching approach that significantly outperforms the state-of-the-art. To achieve high performance, we address the challenges of prefetching in very large sparse address spaces, as well as prefetching in a timely manner by predicting ahead of time. We collect I/O trace files from several real-world applications running on cloud servers and show that our proposed approach consistently outperforms the existing stride prefetchers by up to  $800 \times$  and prior prefetching approaches based on Markov chains by up to  $8 \times$ . Furthermore, we propose an address mapping learning technique to demonstrate the applicability of our approach to previously unseen SSD workloads.

In order to improve the endurance of SSDs, we present a machine learning-based approach for reducing write amplification in log-structured file systems via death-time prediction of logical block addresses. We define the death-time of a data element (LBA) as the number of write I/O accesses before which a given data element is overwritten. We leverage the sequential nature of I/O accesses to train lightweight yet powerful, temporal convolutional network (TCN) based models to predict death-times of logical blocks in SSDs. We leverage the predicted death-times in designing ML-DT, a near-optimal data placement technique that minimizes write amplification (WA) in log-structured storage systems. Our proposed approach results in up to 14% reduction in write amplification compared to the best baseline technique. Additionally, we present a mapping learning technique to test the applicability of our approach to new or unseen workloads and present a hyper-parameter sensitive study.

# **Chapter 2**

# Background

In this chapter, we first provide background on flash memory and provide details on the garbage collection process and write amplification within SSDs. We then describe prefetching in systems and finally discuss the various machine learning models used in this thesis.

## 2.1 Flash Memory

Flash memory was invented by Fujio Masuoka in 1980 and later commercialized by Toshiba in 1987. SanDisk Corporation (formerly SunDisk) followed Toshiba and entered the commercial market in 1989. The first commercial flash drive shipped by SanDisk was a 20MB solid-state drive (SSD) plugged in using a PC card and retailed for over \$1000 and was used by IBM in their Thinkpad laptop series [11]. In 1995, some of the mission-critical applications in military and aerospace industries started using flash-based SSDs, as they offered superior read/write performance and the ability to withstand harsh conditions such as shocks, vibrations, and temperature fluctuations. The latest generation of SSDs introduced by GigaByte in 2019 can perform sequential reads at the rate of 15000 megabytes per second (MBps) and sequential writes at the rate of 15200 MBps [11].

In flash memory, the data is written serially in an entire chip or large block of contiguous data bytes [12]. Flash memory is popularly used as a means of persistent storage in mobile devices and as mass storage for cloud or general computing systems. The two most common types of flash storage include NAND flash and NOR flash. NOR flash was the first one to be developed, although NAND flash is used more commonly as NAND flash provides higher write and erase speeds compared to NOR flash. Typically in an enterprise environment, an array of NAND flash memory is used as secondary storage of user data. In contrast to traditional hard disk drives, which use rotating disks, modern SSDs use flash chips to store data.

Figure 2.1: Representation of flash memory cell

The Flash memory cell (FMC) is the fundamental building block of flash memory. It follows a similar design to standard MOSFET (metal-oxide-semiconductor-field-effect transistor), but unlike a MOSFET, the FMC has two gates. The cells represent an electric switch where

the two gates, a floating gate (FG) and a control gate (CG), control the amount of current flowing between the two terminals (source and drain). FG and CG are used to control the voltage in the cell resembling the logical states 0 and 1. The internal architecture of a flash memory cell is shown in Figure 2.1. Hence, NAND flash drives or SSDs are non-volatile memory devices that store individual bits on floating gate transistors. Floating gate transistors are arranged in large bit cell arrays, increasing not only the storage capacity but also the access latency. Flash cells suffer from limited endurance and frequent bit errors, which are exacerbated by transistor scaling and the introduction of techniques such as multi-level cells [13]. To ensure data integrity, multiple reads using different reference voltages need to be performed, and the controller needs to perform error detection and correction as part of each read, increasing the read latency. As a result, the I/O access latency of SSDs (100us) is three orders of magnitude higher than the latency of reading DRAM (100ns).

Figure 2.2: General architecture of a Flash SSD

The general architecture of an SSD is presented in Figure 2.2. The SSD contains a NAND flash memory array, an embedded CPU (optional), Flash Memory Controllers (FMCs), and Dynamic Random Access Memory (DRAM). The host interface controller supports a specific bus interface protocol, such as Serial Advanced Technology Attachment(SATA), Statistical Analysis System (SAS), or Peripheral Component Interconnect (PCI-e) [14]. Lately, NVMe (Non-Volatile Memory Express) has come forth as a new interface providing additional features such as lower latency and scalable bandwidth compared to other storage interfaces. The NVMe interface allows the host resources to be utilized for memory and computations for flash management, such as address mapping and wear leveling.

Flash memory is composed of multiple blocks, which are further composed of multiple pages. A page is a unit of a read operation, while a block is a unit of erase operation. In contrast to HDDs, SSD's performance scales with the number of NAND flash chips on a device [15]. The flash memory controllers transfer data between DRAM and NAND flash chips using Direct Memory Access (DMA). They are also responsible for maintaining data integrity using Error Correction Codes (ECC) such as BCH (Bose Chaudhuri Hocquenghem code) [16], or Reed Solomon [17]. An FMC is also responsible for multi-way interleaving over multiple NAND flash chips on a shared I/O bus using multiple chip-enabled signals [15]. Multi-channel interleaving can also be used with independent channels and FMCs. This combination of multichannel interleaving over multiple NAND flash chips deployment improves the performance of both sequential and random accesses. Dedicated hardware for FMC is also used for further improving the performance and power efficiency. It can also be used for implementing an application-specific instruction set processor which can support a wide variety of NAND flash memory commands. The Embedded CPUs, in combination with SRAM, are responsible for maintaining the execution environment for supporting the Flash Translation Layer (FTL) [18], the flash management firmware. The FTL interprets the host commands and maintains a mapping table [15] as it translates a logical block address (LBA) to a physical address on the NAND flash memory chips. Usually, a 32 bit RISC (Reduced instruction set computer) processor is used, but based on the requirements, multiple embedded CPUs can be integrated to support multiple host requests simultaneously. The DRAM is responsible for storing FTL metadata and user data temporarily. The DRAM is typically operated at a high clock frequency as it is the target of data transfers from both the FMCs and the host interface [15].

#### 2.1.1 Garbage Collection and Write Amplification in Flash

Garbage collection is method of automatic memory management in log structured storage systems [19]. An essential property of flash is that in order to update the data already written, it needs to erase the old data first and then rewrite the whole data again as erase operations happen at a block-level. Flash memory is typically divided into blocks, which are further divided into pages. Data can be written at the page level. However, erases or updates can only be performed at the granularity of blocks. Hence, to free-up, the space taken up by stale data, all the valid pages within the block must be copied to empty pages of another free block first. Thereafter, we can perform the erasure at block level to prepare it for new valid incoming data [20].

If the data within the pages of a block are invalidated (also called stale pages), only the

pages with valid data in that block are read and rewritten into another previously erased or empty block. This frees up the pages by erasing all stale data to make space for new incoming data. This process of copying live data to new blocks and reclaiming old blocks is called Garbage Collection (GC). GC is a cardinal process with all SSDs, but it can be designed in various ways, which can impact the overall SSD performance and lifetime.

Figure 2.3: Overprovisioning in SSDs

To facilitate copying of valid data to new free blocks, the SSD usually reserves a portion of the memory as spare, also known as the over-provisioned capacity (OP). It is defined as the ratio between the reserved capacity (physical capacity - user capacity) vs. the physical capacity of the device (Figure 2.3). Increasing the OP ratio increases the speed of the device by reducing the number of writes needed in GC. It also increases device lifetime by spreading wear-leveling over more physical blocks. However, it comes at the cost of reduced storage capacity of the device.

Over Provisioning (OP) = (Total SSD capacity - User capacity ) / Total SSD capacity

The garbage collection algorithms are responsible for copying all valid data into a free

space and erasing the original invalid data. The lifecycle of a block within an SSD is shown in Figure 2.4. In a fresh SSD, all blocks start out as free-blocks. Written pages are appended to an open-block and when the block is fully written, it is regarded as a closed-block. As pages are overwritten, closed-blocks contain an increasing number of invalid pages. Finally, the GC mechanism cleans a block by moving all the valid pages to another block before erasing it, so that it can be added back to the list of free-blocks. Garbage collection is performed when there are no free blocks available or when the number of free blocks in the device is lower than a predefined threshold value. The steps followed during a typical garbage collection process is listed below are:

- The virtual blocks meeting the conditions are shortlisted for deletion.

- The valid physical pages are copied into a block with free pages available.

- The entire physical block is freed to make space for new data

Figure 2.4: Lifecycle of an SSD block

Garbage Collection is performed at the Flash Translation Layer [18] for NAND Flash memory devices. The Flash translation layer (FTL) is a software/hardware mechanism inside NAND flash memory that maps logical blocks in an SSD to physical blocks. Since the data within the logical blocks may span multiple physical blocks, the garbage collection may erase more than one physical block. Garbage collection induces a performance overhead on flash devices as more number of writes are used to store the data within the flash memory. This overhead is measured using a metric referred to as called Write Amplification (WA), defined as the ratio of the physical pages required to be programmed inside the device for storing logical block data from the host.

#### WA = Num pages programmed inside SSD / Num page updates issued by host

Write amplification due to internal copying directly reduces application throughput and the lifetime of the device due to increased writes and wear leveling. The impact of garbage collection on write amplification is influenced by the level of over-provisioning and the choice of reclaiming policy. There exist two common techniques for reclaiming victim blocks for GC. Greedy mechanisms [21] choose the block with the lowest number of valid blocks. Cost-benefit mechanisms [22] consider the future writes that may invalidate additional pages before choosing a victim block. In a fresh SSD, all blocks start out as free blocks. Written pages are appended to an open block, and when the block is fully written, it is regarded as a closed block. As pages are overwritten, closed blocks contain an increasing number of invalid pages. Finally, the GC mechanism cleans a block by moving all the valid pages to another block before erasing it so that it can be added back to the list of free blocks.

## 2.2 Prefetching

A computer system typically consists of several levels of memory running at different performance (registers, cache, DRAM, SSD, SATA, etc.) with the goal of reducing the overall access time. A memory hierarchy [23] has been developed which determines the memory organization of the system. Prefetching in systems is the process of preloading data from a slow storage device into faster memory, generally DRAM, to decrease the overall read latency. Accurate and timely prefetching can effectively reduce the performance gap between different levels of memory.

There are three important metrics used to compare prefetchers, including coverage, accuracy, and timeliness of prefetchers [9]. Coverage is the ratio of the number of SSD reads that can be prefetched to the total number of SSD reads. Accuracy is the ratio of the number of data blocks being prefetched to the number of prefetched data blocks that were actually requested by the application. Timeliness requires data blocks to be prefetched sufficiently ahead of time so that the data is present in DRAM whenever the application performs the read request. If the prefetched data blocks are not available when they are needed, the application is required to stall, rendering prefetching ineffective. Furthermore, if the data is prefetched too early, it may not be available anymore when it is actually needed due to the eviction from the capacity-limited cache. Inaccurate prefetches that read in unneeded data are harmful as they waste I/O bandwidth and DRAM capacity. If prefetching is performed too conservatively, coverage is low, and the overall performance gains are limited. Hence, the ideal prefetcher has high coverage, high accuracy and executes timely prefetches so that the data is fetched exactly when needed. A basic prefetching mechanism is shown in Figure 2.5.

The SSD prefetcher (P) is responsible for predicting candidate data blocks (C) to prefetch from the SSD (S) into a fast cache (DRAM) buffer (B) of size. The cache eviction

policy (E) is responsible for evicting the data blocks from B in order to make space for new incoming data. Candidates x2 and x3, however, were present in the cache when requested, and hence, resulted in a cache hit. In this example, at times, P determines candidates x1, x2, x3, and x4 for prefetching, but the actual data requested at time t is x1, x2, and x3. Here, x1 was prefetched too early while x4 was inaccurately prefetched, resulting in cache miss in both cases.

Figure 2.5: Demonstration of Prefetching in SSDs

## 2.3 Machine Learning Techniques

Machine learning is the science of developing systems that can learn automatically from data to make decisions or inferences without being explicitly programming the system to perform the task [24]. There are several broad areas of machine learning including supervised learning [25], unsupervised learning [26], semi-supervised learning [27], and reinforcement learning [28]. One of the goals of supervised learning is to build predictive models that can learn from labeled examples, where the labels represent the category to which a particular example belongs, and upon training the model, it can be used to make predictions on unseen examples of data that the model has not seen before. The goal of unsupervised learning is to draw inference from the data in the absence of labels, for example, is to find patterns or groupings within the unlabeled data set [29]. Semi-supervised learning [30] approaches utilize a large

number of unlabeled examples together with a relatively small number of labeled examples of data to train predictive models. In this thesis, we use supervised, semi-supervised, and unsupervised learning approaches to improve the performance of storage systems. Next, we describe the specific machine learning techniques that we used in this thesis.

Figure 2.6: Demonstration of Oversampling process

### 2.3.1 Oversampling and Boosting

One of the problems that is sometimes encountered while building predictive models is that there are a very few examples of one category (also known as the minority class) and relatively large number of examples for the other category (also known as the majority class) present in the labeled or training dataset. This often leads to a model that overfits to the examples of majority class. One of the ways to deal with this class imbalance problem is to use oversampling techniques that artificially add samples to the minority classes using various methods (such as SMOTE [31]) to make the dataset more balanced and improve learning (Figure 2.6). The performance of Machine Learning models can also be improved by combining several learners, a process called Boosting [32]. The basic principle behind the working of the boosting algorithm [33] is to generate multiple weak learners and combine their predictions to form one strong rule. These weak rules are generated by applying base ML algorithms on different distributions of the data set. These algorithms generate weak rules for each iteration. After multiple iterations, the weak learners are combined to form a strong learner that will predict a more accurate outcome.

We used SMOTEBoost [34] and RUSBoost [35] algorithms for classifying the observations. It employs a mix of SMOTE [31] and the standard boosting procedure AdaBoost [36] to model the minority class. It works by giving the model not just with minority class data points that were misclassified in the previous boosting iteration, but also with broader representation of those instances (achieved by SMOTE). SMOTE also increases the diversity in the minority class samples in each iteration by creating synthetic samples. The SMOTE (Synthetic Minority Over-Sampling Technique) function takes feature vectors with dimension(v, n) and the target class with dimension(v,1) as the input. It returns final features vectors with dimension (v', n) and the target class with dimension (v',1) as output SMOTE [31]. Figure 2.7 demonstrates boosting process used in machine learning. Boosting uses the performance of trees from previous iteration to assign weights to the next tree to be built. More weight is assigned to data that are difficult to separate. Models are produced sequentially one by one to update each of the weights. After all trees are generated, new information is predicted based on the weighted performance of the trees on input data.

Figure 2.7: Demonstration of Boosting

### 2.3.2 Isolation Forests

Anomaly detection [25] methods are commonly used to find rare events or observations in the data which differ significantly from the majority of the data points. Anomaly detection can be performed in a supervised, semi-supervised, and unsupervised manner. It works well with imbalanced data since it makes a model using the majority class. We used unsupervised and semi-supervised approaches for detecting anomalous data points using Isolation Forests [37]. Semi-supervised approaches use only good, non-anomalous data points for training. It assumes that we only know which data points are non-anomalous, and we do not have any information on the anomalous data points. While making predictions, the model evaluates similarity between the new observations with respect to the training data and checks whether it fits the model. A supervised approach, on the other hand trains on both genuine and anomalous data points. It doesn't require labelling which can be hard and time consuming. We use the isolation forest algorithm to separate out the anomalous data points. The Isolation Forest algorithm

value between the maximum and minimum values of the selected feature. We build multiple decision trees so that the trees isolate the observations in their leaves. Ideally, each leaf of the tree isolates exactly one observation from the data set. Isolation Forest can scale up to tackle huge data sizes with high-dimensionality.

Figure 2.8: General architecture of vanilla ANN

### 2.3.3 Long Short Term Memory Networks

Artificial neural networks (ANN or NN) [38] combine machine learning algorithms for solving specific tasks. The architecture of neural networks is analogous to a synapse within our nervous system where a signal can be transmitted from one neuron to the other. The layers are connected further by links defined between neurons from one layer to the next. Neural Networks similarly consist of layers, where each layer contains many artificial neurons. A NN typically comprises multiple layers, each performing a computational task that contributes towards a solution to the task at hand. The first layer is called the input layer, which feeds the input to the NN in a numerical format. The input layer is followed by one or more layers which eventually lead to the final layer called the output layer. The output layer performs similarly to a decision-maker, and the layers between the input and the output layer are called "hidden" layers. The hidden layers are responsible for the 'actual learning' of the data. The general structure of a vanilla ANN is shown in Figure 2.8. Deep learning, also called deep structured learning or hierarchical learning, is part of a broader family of ML techniques based on ANN [39].

The data in an ANN "propagates" by way of transformation sequentially starting from the input layer, through the hidden layers, eventually ending at the output layer. Such a network is called a 'feedforward neural network'. Recurrent neural networks (RNN) [40], work similar to vanilla NN, with the difference that RNNs utilizes a concept of memory using a different kind of link, which enables feedback. Contrary to feedforward NN, the outputs of some layers are fed back to the inputs of previous layers. This enables them to analyze sequential data while taking into account the input sequence of the data. The feedback links work in the reverse direction and help to learn abstractions based on context. The general architecture of an RNN is shown in Figure 2.9.

Figure 2.9: General architecture of vanilla RNN

Long short term memory (LSTM) [41] is a variant of recurrent neural network ar-

chitecture used in the field of deep learning. LSTMs are a subset of artificial neural networks, which can take time and sequence into consideration. (i.e., they have a temporal dimension). LSTMs were designed by Sepp Hochreiter and Juergen Schmidhuber to learn and recognize patterns in sequential data (for e.g., weather data [42], stock markets [43], IO accesses [9], etc.) and are capable of learning long-term dependencies in data due to the feedback connections. They can process the entire data sequence, not only just single data points as in pictures. LSTMs are popularly used in a wide variety of problems such as speech recognization, market prediction, grammar learning and protein homology detection.

Figure 2.10: General architecture of an LSTM cell

The architecture of an LSTM cell is shown in Figure 2.10. It is composed of four layers with three logistic gates and a 'tanh' [44] layer in contrast to RNNs, which have a single neural net layer of 'tanh'. Gates are used to control the information passed through the cell. The

output is typically a value in the range between 0-1, which determines the amount of information retained from the previous layer. ( output '0' means 'reject all' and output of '1' means 'include all'). At a given time, C(t) and h(t) represents the cell state and hidden state, respectively, and the current data input is represented by x(t). The first layer in an LSTM cell is the sigmoid layer, and it takes into two inputs - h(t-1) and x(t) and generates two outputs - h(t) and C(t). It is called the forget gate as its output (between 0-1) determines the amount of information to be discarded. The output is then point-wise multiplied with the previous cell state C(t-1). The second sigmoid layer takes in two inputs - h(t-1) and x(t) is called the additional gate as it determines what new information is added to the current cell state. The layer computes a vector of the new candidate values. The point-wise multiplication decides the amount of information to be added in that particular cell state. The result is added to the output of the forget gate multiplied with the previous cell state C(t). Finally, the output is computed using a combination of sigmoid and 'tanh' layer transforms the output in the range (-1,1). The output is generated by point-wise multiplication to produce the output of the cell h(t).

We propose to utilize Long Short-Term Memory (LSTM) based sequence-to-sequence neural networks to learn spatial I/O access patterns of application block-level I/O traces for prefeteching. LSTMs can leverage the sequential nature of IO accesses and have a "memory" that allows the model to look at recent accesses while making a decision. The architecture is capable of capturing long-term dependencies in data and can IO sequences of different lengths. LSTMs integrate model training and representation learning together without requiring additional domain knowledge, enabling the discovery of unseen patterns in the data to improve the generalization capability of a model. We leveraged LSTMs to separate the complex and interleaved I/O streams in data and addressed the challenge of timeliness of predictions by predicting multiple I/O accesses ahead of time. This enabled us to build a neural network-based prefetcher which we discuss in Chapter 4.

#### 2.3.4 Auto Encoders

Auto encoders [45] are artificial neural networks which can learn efficient representations of input data, known as codings. These codings typically represent input data in lower dimensions, making it a popular use case for dimensionality reduction [46], [47]. Auto encoders work by learning to copy their inputs to their outputs. They work by compressing the input into a latent-space representation, and then reconstructing the output from this representation. This type of network is composed of two parts:

Figure 2.11: Internal design of Auto Encoders

- Encoder: This is the part of the network that compresses the input into a latent-space representation. It can be represented by an encoding function h = f(x).

- Decoder: This part aims to reconstruct the input from the latent space representation. It can be represented by a decoding function r = g(h).

For example, it is possible to limit the size of the internal representation, or you can add noise to the inputs and train the network to recover the original inputs. These constraints prevent the auto encoder from trivially copying the inputs directly to the outputs, which forces it to learn efficient ways of representing the data. In short, the encodings are byproducts of the auto encoder's attempt to learn the identity function under some constraints.

Figure 2.12: Demonstration of Embeddings [1]

#### 2.3.5 Embeddings

An Embedding is a lower-dimensional space representation that can translate high dimension vectors. Embeddings are particularly useful for sparse vectors as they can represent the sparse input more effectively using less data such as a representation of words. The distribution of block address IO access follows a similar sparse pattern and can be represented by a sparse vector. The key to this approach is the concept of using a dense distributed representation for each input value. Embedding captures semantic similarities between data points places them close to each other in the embedding space. Embeddings can be learned from multiple models and can be reused. Popular Embeddings such as AlexNet [6], Word2Vec [48] and ImageNet

[49] are reused for various natural language processing (NLP) tasks. Embeddings are learned jointly with a neural network model with a certain task in mind (typically related to natural language processing tasks such as designing a chatbox, or document classification). The size of the vector space is specified as part of the model, such as 50, 100, or 300 dimensions. The vectors are typically initialized with small random numbers. The embedding layer is used before the first layer of a neural network and is fit in a supervised way using the backpropagation algorithm [50]. When the input to a neural network contains symbolic categorical features (e.g., features that take one of k distinct symbols, such as words from a closed vocabulary), it is common to associate each possible feature value (i.e., each word in the vocabulary) with a d-dimensional vector for some d. These vectors are then considered parameters of the model and are trained jointly with the other parameters. The one-hot encoded-words are mapped to the word vectors. If a multilayer perceptron model is used, then the word vectors are concatenated before being fed as input to the model. If a recurrent neural network is used, then each word may be taken as one input in a sequence. This approach of learning an embedding layer requires a significant amount of training data [51]. In Figure 2.12, we see an example of embeddings transforming a sequence of numbers to a higher dimensional representation.

#### 2.3.6 Temporal Convolutional Networks

Temporal Convolutional Networks (TCNs), proposed by Lea et al. (2016) [52], is a variant of convolutional neural network (CNN) [53] which employs causal convolutions [54] and dilations [55] to learn from sequential data with temporality. TCNs typically follow an encoder-decoder architecture and can process sequences of any length, mapping it to an output

Figure 2.13: General architecture of temporal convolutional networks

sequence of identical length. To accomplish this, the TCN uses a 1D-fully convoluted network architecture (FCN), where the length of every hidden layer is identical to the input layer. Padding of zero length (kernel size - 1) is added to keep succeeding layers the same length. i.e., convolutions where output at time t is convolved only with data elements from time t and earlier in the preceding layer. Using dilated convolutions, the TCNs can look back at history with size linear in the depth of the network and the filter size. An important feature is that the output (at time t) is only convolved with the data elements that appeared before t. Furthermore, as the convolutions in TCN are causal, is no information "leakage" from future to past [56] . TCNs can be represented as 1D FCN + causal convolutions (Figure 2.13)

TCNs provide several advantages over RNN based architectures by offering parallelism of computation, flexible receptive field size, and requiring lower memory for training. We used TCNs for learning representations and identifying patterns in IO accesses. As TCNs implement memory (causal dilated convolutions), it considers recent data to differentiate between interleaved I/O accesses, enabling effective predictions. TCNs also track the behavior of I/O accesses and how they evolve over time to enable accurate predictions based on the current state of the system.

# **Chapter 3**

# **SSD Failure Prediction**

## 3.1 Introduction

NAND flash based solid state drives (SSDs) represent an important storage tier in data centers holding most of today's warm and hot data. However, as SSDs are built from semiconductors lacking mechanical components such as spinning disks, they are also more reliable and less prone to failures compared to HDDs. The number of SSDs shipped each year has increased steadily by 42.5% over the last decade, now exceeding exabytes of storage capacity every year [57]. SSD manufacturers have employed three main techniques to increase the storage density over the past years including planar scaling, 3D integration, and multi-level cells. While beneficial for the storage density, these mechanisms have reduced the endurance, retention, and reliability of SSDs [58], [13], [59], requiring increasingly sophisticated encoding and fault tolerance mechanisms. Nevertheless, even with advanced fault tolerance techniques and low failure rates, large Hyperscale data centers utilizing 100,000's of SSDs suffer from

multiple device failures daily. Data center operators are interested in predicting SSD device failures for two main reasons. First, even with RAID [60] and replication [61] techniques in place, device failures induce transient recovery and repair overheads affecting the cost and tail latency of storage systems. Second, predicting near-term failure trends helps to inform the device acquisition process enabling to save costs and avoid capacity bottlenecks. As a result, it is important to predict both the short-term individual device failures as well as near-term failure trends.

Prior studies on predicting storage device failures [62], [63], [64], [65] focused primarily on traditional hard disks, however, due to the fundamentally different architecture of SSDs, prior techniques and findings are not readily applicable to SSDs. Research that has particularly focused on SSDs [66], [67], [18], [68] generally concentrated on understanding specific errors and issues within SSDs, limited to a controlled laboratory environment. Most studies that analyzed SSDs in the field focused on understanding correlations among specific workloads, their induced number of writes and bit errors, as well as their effect on the reliability of SSDs [69] [70], [71]. Alter [72] and Schroeder [7] analyzed authentic SSD logs collected in the Google cloud to leverage machine learning (ML) techniques for predicting the likelihood of SSD failures. While most related to our work, their proposed models either fall short on determining failed drives, or produce a large number of false positives, thereby lowering the performance of the prediction models. In particular, these two prior works suffer from the following main challenges. First, as they utilize black-box ML techniques, they are unaware of the underlying failure reasons rendering it difficult to determine the failure types that these

models can predict. Second, the models in prior work struggle with dynamic environments that suffer from previously unseen failures that have not been included in the training set. These two challenges are especially relevant for the SSD failure detection problem which suffers from a high class imbalance. In particular, the number of healthy drive observations is generally orders of magnitude larger than the number of failed drive observations, thus posing a problem for many ML models.

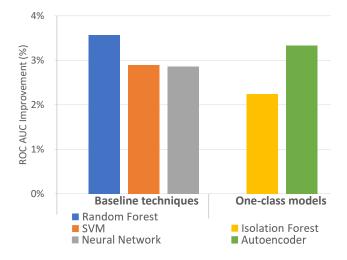

We determine the best performing ML approaches for predicting SSD failures and then explore optimization techniques, including feature selection and data normalization, to address the challenges of large feature spaces and highly imbalanced datasets. Consistent with the prior work [72], we use the receiver operating characteristic area under the curve (ROC AUC) score [73] to evaluate the performance. With these optimizations in place, our best approach outperforms all prior approaches by at least 9.5% ROC AUC score. To address the challenges mentioned earlier, we propose utilizing *1-class ML models* that are trained only on the majority class. By ignoring the minority class for training, our 1-class models avoid overfitting to an incomplete set of failure types, thereby improving the overall prediction performance by up to 9.5% in terms of ROC AUC score. The benefit of our proposed technique becomes even more evident when we reduce the types of failures included in the training set of the baselines approaches, showing 13% to 33% improvements using our proposed 1-class approaches over prior work. Furthermore, we introduce a new learning technique for SSD failure detection, *1-class autoencoder*, which enables interpretability of the trained models while providing high prediction accuracy.

In particular, 1-class autoencoders provide insights into what features and their combinations are most relevant to flagging a particular type of device failure. This enables categorization of failed drives based on their failure type, thus informing about specific procedures (e.g., repair, swap, etc.) that need be applied to resolve the failure. Given the low overall failure rates of SSDs, and the importance of predicting all failures, the goal is to predict all SSD failures with fewest number of false positives. An incorrect prediction of a drive going to fail as healthy is much more costly (due to the possibility of data loss, application crashes, etc.) than wrongly flagging a healthy drive as a potential failure. In particular, for highly imbalanced datasets where typically only one out of 10,000 SSDs fail, only a recall of greater than 99% represents a useful result.

To summarize, in this work, we address the challenge of accurately predicting the failure of individual SSDs with a comprehensive analysis [74], [37], [45], [75] of various machine learning (ML) models. For analysis and evaluation of our proposed techniques, we leverage a cloud-scale dataset from Google that has already been used in prior work [72], [76]. This dataset contains 40 million observations from over 30,000 drives over a period of six years. For each observation, the dataset contains 21 different SSD telemetry parameters including SMART (Self-Monitoring, Analysis and Reporting Technology) parameters, the amount of read and written data, error codes, as well as the information about blocks that became non-operational over time.

# **3.2** Research Questions (RQ)

The following lists the research questions that we are looking to answer in this project.

#### 3.2.1 RQ A: Which SSD telemetry features contribute to SSD failures?

The current knowledge about SSD failure characteristics is mainly supplied by vendors based on accelerated lab testing under controlled conditions using synthetic traces. There are some prior large-scale field studies on SSD failures from Facebook [4], and Google [12], [72], but they are limited in their scope, and little is understood about SSD failures in realworld situations. In this project, we collect a wide variety of SSD telemetry information (24 parameters) and run feature selection algorithms to select the most relevant characteristics that contribute to SSD failures.

# 3.2.2 RQ B: Can we predict SSD failures by training only on healthy drives (one class training)?

One of the major challenges in predicting SSD failures is class imbalance, as healthy drive data are easier to collect compared to failures (which are inherently rare). To address the challenge, we proposed a technique of predicting SSD failures which only uses the majority class for training the models. The approach is easier to scale and is independent of the number of failed drive data samples in the data.

# 3.2.3 RQ C: How does the performance of one-class model training compare with state-of-the-art techniques?

Training on one class offers many advantages, as discussed above. In this project, we compare the performance of our one-class models with state-of-the-art SSD failure prediction techniques and show that our approach improves the model performance by up to  $1.3 \times$ . Our approach also takes lower training and inference time due to the lower number of input features.

#### 3.2.4 RQ D: Can we interpret SSD failures?

Recent advances in the field of interpretable machine learning focus on understanding how a machine learning model reaches its decisions. It helps in making the models more transparent and less biased. In this project, we want to query the model to find out why a model flags a particular SSD is destined to fail. This helps vendors understand why a drive failed and also can help in re-servicing the drives to prolong the lifetime. While training on autoencoder based models, we used the reconstruction error to interpret reasons why a particular drive was flagged by the model.

#### 3.2.5 RQ E: Can one class models be used to predict unseen SSD failures?

Since one class training does not require failed SSD samples in training, we show that our approach based on training on healthy drives can predict not only unseen SSD failures but also outperform the state-of-the-art approaches for predicting SSD failures.

## **3.3 Research Contributions**

Prior work on SSD failure prediction suffers from three shortcomings:

(i) the limited overall accuracy of predicting failures,

- (ii) the inability of reliably predicting previously unseen failure types, and

- (iii) the lack of interpretability of predictions.

To address these challenges, we provide the following contributions. First, we provide a comprehensive analysis of machine learning techniques to predict SSD failures with the highest recall and accuracy for both the majority and minority classes with fewest number of false positives. We optimize our approaches by addressing the challenges of imbalanced data sets and feature explosion. Second, we show how 1-class predictive models can be used to predict previously unseen failures in a dynamic data center environment. Third, we propose 1-class autoencoder, an approach to interpret the predictions of our model, to enable understanding of the most important reasons for failures.

#### 3.3.1 Accurate Prediction of SSD Failures

Our data set contains observations from over 30,000 drives from a major cloud service provider over a time span of 6 years where each SSD observation contains the values of 24 distinct features including SMART features, the amount of read and written data, error codes, board temperature and power characteristics and more. Predicting device failures from this data poses two challenging problems. First, due to the large feature space, machine learning models suffer from the *curse of dimensionality* as the time requirements of an algorithm grow with the number of features, often exponentially. Secondly, the data from which our models need to infer failures suffer from a significant class imbalance problem, as there exist a significantly greater number of healthy than failed devices in our data set.

#### 3.3.1.1 Feature Selection