# UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Design of Topologies for Interpreting Assays on Digital Microfluidic Biochips

**Permalink** https://escholarship.org/uc/item/1bb071tp

https://escholarship.org/uc/item/1000

**Author** Grissom, Daniel

Publication Date 2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Design of Topologies for Interpreting Assays on Digital Microfluidic Biochips

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

by

Daniel Thomas Grissom

June 2014

Dissertation Committee: Dr. Philip Brisk, Chairperson Dr. Frank Vahid Dr. Qi Zhu Dr. Walid Najjar

Copyright by Daniel Thomas Grissom 2014 The Dissertation of Daniel Thomas Grissom is approved:

Committee Chairperson

\_\_\_\_\_

University of California, Riverside

## ACKNOWLEDGMENTS

I would like to thank Dr. Philip Brisk for his continual dedication to, not only our microfluidic research, but also to my personal growth and well-being. From the day I met Dr. Brisk, he has shown a true desire to challenge me, while ensuring that I am enjoying my work and keeping my sanity. His guidance and countless hours of mentoring have been foundational to my success at the University of California, Riverside (UCR) and has undoubtedly helped shape my career aspirations.

Much of the work in this dissertation has already been published and I thank the Institute of Electrical and Electronics Engineers (IEEE) and the Association for Computing Machinery (ACM) for allowing me to include significant portions of my work in this dissertation from the following published works:

- ACM Journal on Emerging Technologies in Computing Systems [28] (CHAPTER

2)

- ACM Proceedings of the Great Lake Symposium on VLSI [30] (CHAPTER 3)

- IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

[31] (CHAPTER 3)

- ACM Proceedings of the Design Automation Conference [29] (CHAPTER 4)

I would like to thank the following entities for their generous awards, fellowships and stipends which made it possible for me to focus on research during my time at UCR:

- The National Science Foundation (NSF) for the Graduate Research Fellowship

- UCR for their initial fellowship aid and Dissertation Year Fellowship

# **DEDICATION**

This dissertation is dedicated to:

- Jesus Christ, my personal savior, who gave me the idea and strength to become a graduate student

- Maritza Grissom, my beautiful wife, who has learned to say "duh" when I talk about microfluidics so it feels like it should all actually make sense to everyone listening

- William & Sandra Grissom, my amazing parents, who paid my way through undergrad and have loved and supported me through it all

- Joanna, Michael, Rebecca, Jonathan & Jeremiah, my older siblings, who have always been there for me

- The orphans, widows and all the beautiful people of Sub-Saharan Africa, who have been my inspiration for advancing the field of microfluidics

#### ABSTRACT OF THE DISSERTATION

Design of Topologies for Interpreting Assays on Digital Microfluidic Biochips

by

Daniel Thomas Grissom

#### Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, June 2014 Dr. Philip Brisk, Chairperson

In the last decade, digital microfluidic biochips have emerged as a viable candidate for the automation and miniaturization of biochemistry; however, digital microfluidic designs in previous works typically suffer from two short-comings: 1.) they are unable to respond to live feedback and errors; 2.) they are application-specific, rather than programmable. In the early years of digital microfluidic research, the synthesis problems of scheduling, placement and routing were performed offline (before runtime) due to their algorithmic complexity, typically yielding application-specific devices that could perform only one type of biochemical reaction and could not respond to live feedback in a timely manner, due to the complexity of their algorithms.

This dissertation offers topological solutions toward realizing digital microfluidic biochips that are both dynamic and programmable in nature. We begin by presenting interpretation, which is a form of dynamic synthesis. Instead of static compilation which generates a deterministic electrode activation sequence, interpretation acts like an operating system that manages resources as an assay is being executed, allowing for resources to be allocated and dispatched dynamically in response to live feedback from integrated sensors and video monitoring. We also present new language constructs necessary to incorporate control flow into digital microfluidic biochips (DMFBs). We then introduce virtual topologies, a virtual organization of electrodes into "city streets and blocks," which help simplify dynamic synthesis flow algorithms; we show two new virtual topologies and describe scheduling, placement and routing algorithms to accompany them, yielding fast, reliable, dynamic, programmable DMFBs. Finally, we present a field-programmable, pin-constrained (FPPC), topology which, for the first time, offers a solution to reduce the cost of a DMFB while maintaining programmability. We include results which show our FPPC design to be the least expensive when compared to prior pin-constrained and direct addressing DMFBs, while offering unmatched flexibility next to its closest competitors in price. We conclude with the first detailed cost analysis and shed light on the relationship between PCB layer count, pin count and cost. Our results reveal that the minimization of pin-count, if not done carefully, can necessitate additional PCB layers and yield a more expensive DMFB.

# TABLE OF CONTENTS

| Acknowledgments                           | iv   |

|-------------------------------------------|------|

| Dedication                                | v    |

| ABSTRACT OF THE DISSERTATION              | vi   |

| Table of Contents                         | viii |

| List of Figures                           | xii  |

| List of Appendix Figures                  | xvi  |

| List of Tables                            | xvii |

| CHAPTER 1 Introduction                    | 1    |

| 1.1 - DMFB Droplet Manipulation           |      |

| 1.2 - DMFB Device Technology Overview     |      |

| 1.3 - High-Level Assay Synthesis Overview | 6    |

| 1.3.1 - Scheduling                        | 7    |

| 1.3.2 - Placement                         | 8    |

| 1.3.3 - Droplet Routing                   |      |

| 1.3.4 - Pin-Mapping                       |      |

| 1.3.5 - Wire Routing                      |      |

| 1.4 - DMFB Design Objectives              |      |

| 1.4.1 - Dynamic DMFBs                     |      |

| 1.4.1.1 - Barriers to Dynamic DMFBs       |      |

| 1.4.2 - Programmable DMFBs                |      |

| 1.4.2.1 - Barriers to Programmable DMFBs  |      |

| 1.5 - Contributions                       |      |

| CHAPTER 2 Interpretation                  |      |

| 2.1 - Introduction                        |      |

| 2.1.1 - Interpretation vs. Compilation    |      |

| 2.1.2 - Contribution                      |      |

| 2.2 - Virtual Topology                    |      |

| 2.2.1 - Synthesis Simplifications                    |    |

|------------------------------------------------------|----|

| 2.2.2 - Deadlock-Free 2D-Mesh Routing                |    |

| 2.2.2.1 - Analogue to 2D-Mesh Topology               |    |

| 2.2.2.2 - Differences from 2D-Mesh Topology          |    |

| 2.3 - Interpretation                                 |    |

| 2.4 - BioCoder Language and Extensions               |    |

| 2.4.1 - Lack of Universality in LoC Compilation      |    |

| 2.4.2 - Object-Oriented Organization                 |    |

| 2.4.2.1 - Example                                    |    |

| 2.4.3 - Extensions for Feedback and Control Flow     |    |

| 2.4.3.1 - Example                                    | 41 |

| 2.5 - System overview and runtime environment        |    |

| 2.5.1 - Intermediate Bytecode Format and Interpreter |    |

| 2.5.1.1 - Bytecode Instruction Format                |    |

| 2.5.1.2 - I/O Operations                             |    |

| 2.5.1.3 - Droplet Identification                     |    |

| 2.5.1.4 - Keeping Track of Time                      |    |

| 2.5.2 - Interpreting a DAG on the Virtual Topology   |    |

| 2.5.2.1 - Scheduling                                 |    |

| 2.5.2.2 - Binding                                    | 51 |

| 2.5.2.3 - Droplet Transportation Protocol (DTP)      |    |

| 2.5.3 - CFG Execution                                |    |

| 2.6 - Simulation Results                             | 56 |

| 2.6.1 - Experiment #1: Fault-tolerant Splitting      |    |

| 2.6.2 - Experiment #2: In-vitro Diagnostics          |    |

| 2.6.3 - Experiment #3: Baseline Assays               | 66 |

| 2.7 - Conclusion                                     | 71 |

| CHAPTER 3 An Efficient Virtual Topology              |    |

| 3.1 - Introduction                                   |    |

| 3.1.1 - Contribution                                 |    |

| 3.2 - Related Work                                   |    |

| 3.2.1 - Scheduling                                   |    |

| 3.2.2 - Placement                                    |    |

| 3.2.3 - Routing                                      |    |

| =                                                    |    |

| 3.2.4 - Combined Methods                                 | 77  |

|----------------------------------------------------------|-----|

| 3.3 - Virtual Topology                                   |     |

| 3.3.1 - Module Topology and Synchronization              |     |

| 3.4 - Fast Online Synthesis                              |     |

| 3.4.1 - Scheduling                                       |     |

| 3.4.2 - Placement                                        |     |

| 3.4.2.1 - Left-Edge Binding Algorithm                    |     |

| 3.4.2.2 - Path-Based Binding Algorithm                   |     |

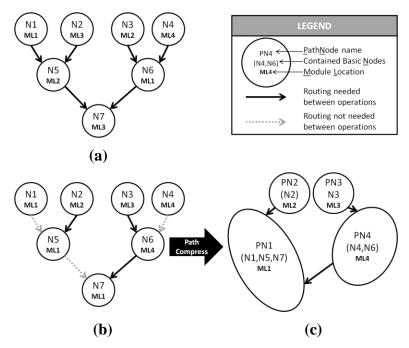

| 3.4.2.2.1 - Generating Path-Compressed Graph             |     |

| 3.4.2.2.2 - Selecting Storage Module Location            |     |

| 3.4.2.2.3 - Binding Storage To Holders                   |     |

| 3.4.3 - Routing                                          |     |

| 3.5 - Experiments                                        |     |

| 3.5.1 - Benchmarks                                       |     |

| 3.5.2 - Implementation Details                           |     |

| 3.5.3 - Experiment 1: Left-Edge Binding vs. Path Binding |     |

| 3.5.4 - Experiment 2: Topology Exploration               |     |

| 3.5.5 - Experiment 3: Comparison To Fast Free Placer     |     |

| 3.6 - Conclusion                                         |     |

| CHAPTER 4 Pin-Constrained Topology                       | 116 |

| 4.1 - Introduction                                       | 116 |

| 4.1.1 - Contribution                                     | 118 |

| 4.2 - Related Work                                       | 118 |

| 4.3 - Pin-Constrained Assignment                         |     |

| 4.3.1 - DMFB Operations and Synchronization              |     |

| 4.3.1.1 - Droplet Transport                              |     |

| 4.3.1.2 - Droplet Dispensing and Outputting              |     |

| 4.3.1.3 - Merging/Mixing                                 |     |

| 4.3.1.4 - Storage, Detection, and Splitting              |     |

| 4.4 - FPPC-DMFB SYNTHESIS                                | 129 |

| 4.4.1 - Scheduling                                       |     |

| 4.4.2 - Placement/Binding                                |     |

| 4.4.3 - Droplet Routing                                  |     |

| Appendix                                              |     |

|-------------------------------------------------------|-----|

| References                                            | 166 |

| CHAPTER 5 Conclusion                                  | 161 |

| 4.7 - CONCLUSION                                      |     |

| 4.6.5.2 - Comparison To Pin-Constrained DMFBs         |     |

| 4.6.5.1 - Comparison to General DMFB                  |     |

| 4.6.5 - Performance                                   |     |

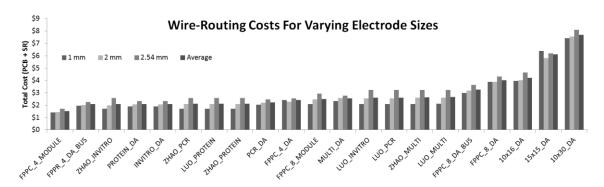

| 4.6.4 - PCB Cost Results                              |     |

| 4.6.3.1 - Metric Selection                            |     |

| 4.6.3 - Wire Routing Cost Analysis                    |     |

| 4.6.2 - PCB Layers & Orthogonal Capacity              |     |

| 4.6.1 - Benchmarks                                    |     |

| 4.6 - EXPERIMENTAL RESULTS                            |     |

| 4.5.1.1 - Cost Computation                            |     |

| 4.5.1 - Wire Routing Cost Analysis                    |     |

| 4.5 - EXPERIMENTAL METHODOLOGY                        |     |

| 4.4.4 - Co-optimizing Pin Assignment and Wire Routing |     |

| 4.4.3.2.1 - Routing Algorithm                         |     |

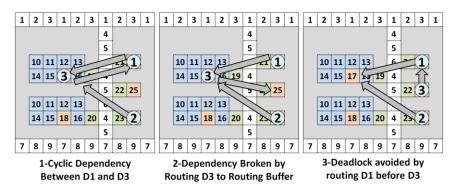

| 4.4.3.2 - Droplet Dependencies and Deadlock           |     |

| 4.4.3.1 - Route Computation                           |     |

# LIST OF FIGURES

| Figure 1-1: (a) A continuous-flow microfluidic device operates on                   |

|-------------------------------------------------------------------------------------|

| Figure 1-2: (a) A DMFB is a planar array of electrodes; (b) Cross-sectional         |

| Figure 1-3: Basic microfluidic operations form the building blocks for assays       |

| Figure 1-4: A microfluidic system typically consists of three major parts7          |

| Figure 1-5: A typical microfluidic synthesis flow dictates that a microfluidic      |

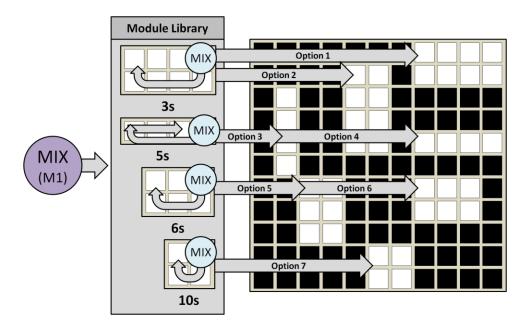

| Figure 1-6: An operation, such as the mix operation from Figure 1-5 (M1)9           |

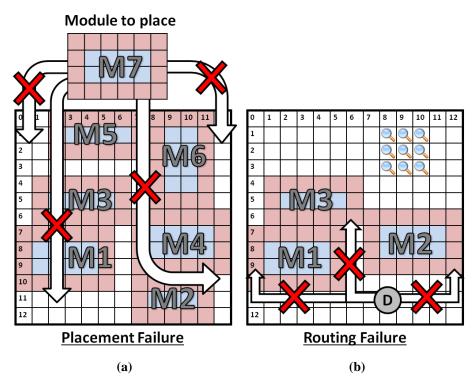

| Figure 1-7: (a) Placement failure occurs because there is insufficient space 10     |

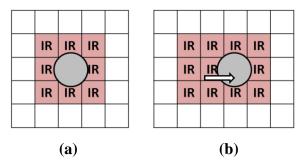

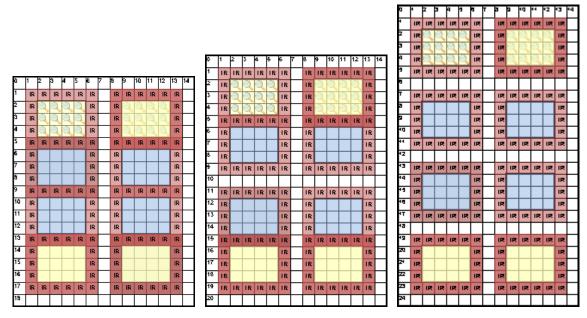

| Figure 1-8: (a) The interference region ('IR') of a droplet at the beginning 11     |

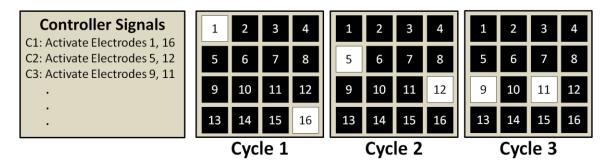

| Figure 1-9: The droplet router produces an electrode activation sequence 12         |

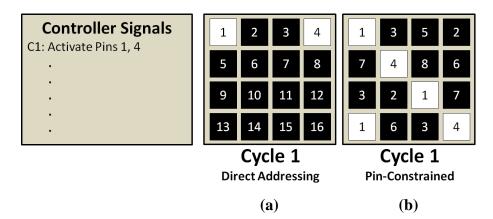

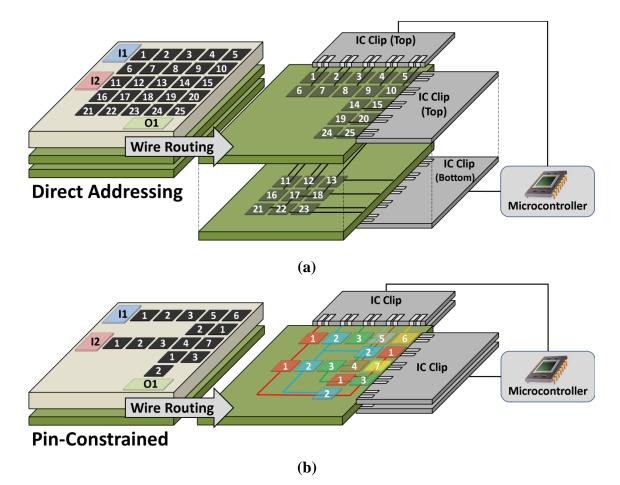

| Figure 1-10: Activating a pin on a (a) direct-addressing DMFB activates             |

| Figure 1-11: A DMFB has printed circuit boards (PCBs, green layers) 14              |

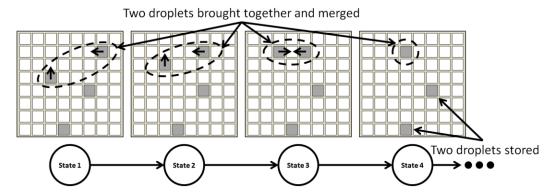

| Figure 1-12: Example of the linear state machine model of DMFB 17                   |

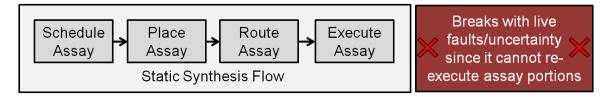

| Figure 1-13: (a) A static synthesis flow performs scheduling, placement             |

| Figure 1-14: Offline vs. online synthesis tradeoffs                                 |

| Figure 1-15: A DMFB "App Store" would allow a user to download 22                   |

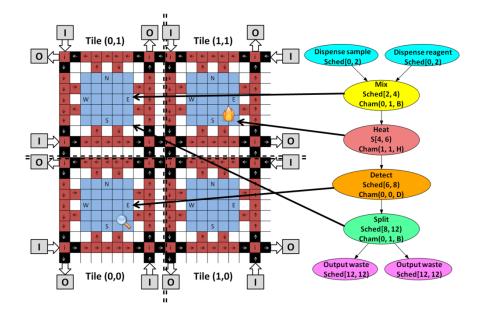

| Figure 2-1: A control-flow graph for a simple drug-discovery assay                  |

| Figure 2-2: Example of the linear state machine model of DMFB control 27            |

| Figure 2-3: In response to an error detected in state k, the assay is paused        |

| Figure 2-4: (a) A tile is the fundamental building block of the virtual topology 29 |

| Figure 2-5: The operations of a scheduled DAG are bound to the modules              |

| Figure 2-6: (a) A module rotary (the cycle formed by four streets surrounding 33     |

|--------------------------------------------------------------------------------------|

| Figure 2-7: (a) Overview of the BioCoder system and output, highlighting             |

| Figure 2-8: (a) BioCoder code for a sample assay and (b) the representative          |

| Figure 2-9: A BioConditionalGroup contains BioConditions                             |

| Figure 2-10: (a) BioCoder code illustrating the use of conditionals; (b) CFG 42      |

| Figure 2-11: Illustration of the left-edge binding solution                          |

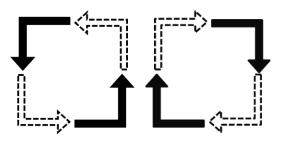

| Figure 2-12: Legal turns (black) and prohibited turns (dashed outline)               |

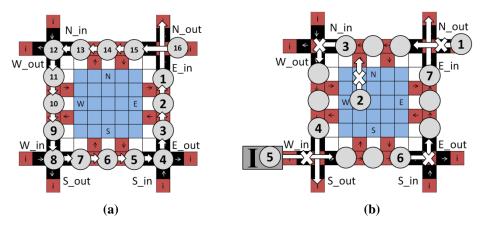

| Figure 2-13: (a) Clipping an exchange rotary ('ER'); (b) passing through 55          |

| Figure 2-14: (a) Deadlock in a module rotary; (b) Module rotary with street          |

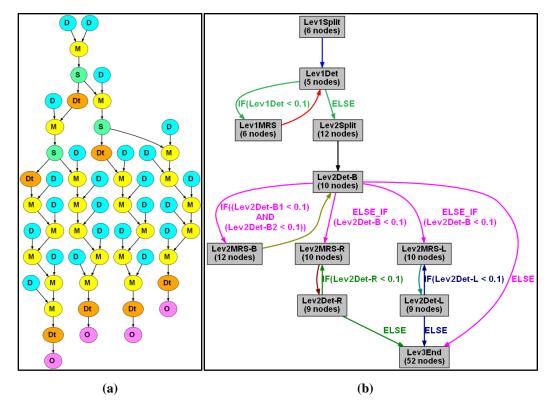

| Figure 2-15: Output from system showing (a) the initial 2-level protein              |

| Figure 2-16: (a) Parallel and (b) sequential CFG implementations of the in-vitro 63  |

| Figure 2-17: BioCoder specification of the sequential in-vitro assay for a 99% 65    |

| Figure 2-18: Simulator output for a particular run of the sequential in-vitro        |

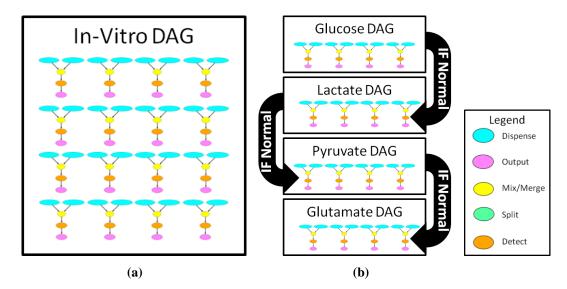

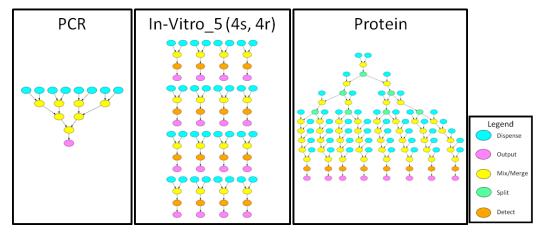

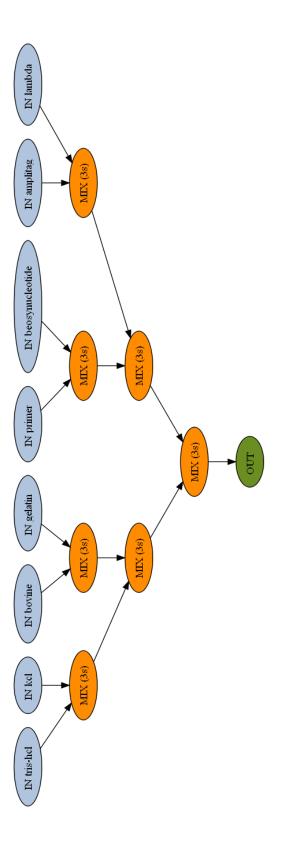

| Figure 2-19: PCR, In-Vitro and Protein DAG specifications                            |

| Figure 3-1: Virtual topology imposed onto a DMFB78                                   |

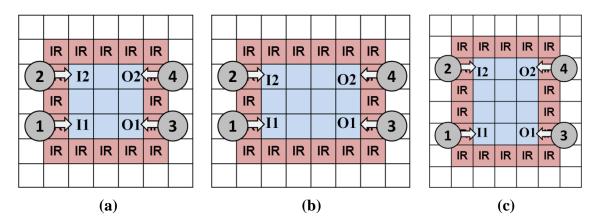

| Figure 3-2: The entrance cells (I1/I2) and exit cells (O1/O2) of (a) a 3x3 module 79 |

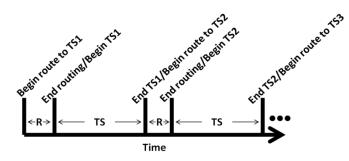

| Figure 3-3: An assay time-line showing that each fixed time-step (TS) is             |

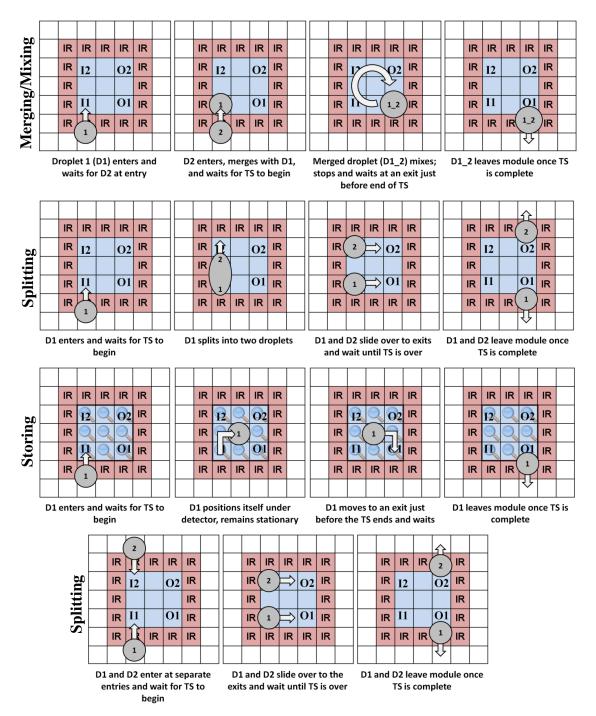

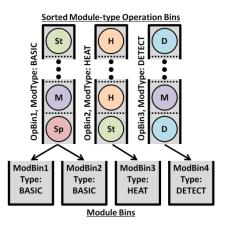

| Figure 3-4: Intra-module droplet processing/routing for microfluidic operations 82   |

| Figure 3-5: Two DMFB scenarios with droplets that are going to be split              |

| Figure 3-6: Illustration of the left-edge binding solution                           |

| Figure 3-7: Pseudocode for our left-edge-based binding algorithm                     |

| Figure 3-8: (a) Randomly-bound sequencing graph for a simple assay                   |

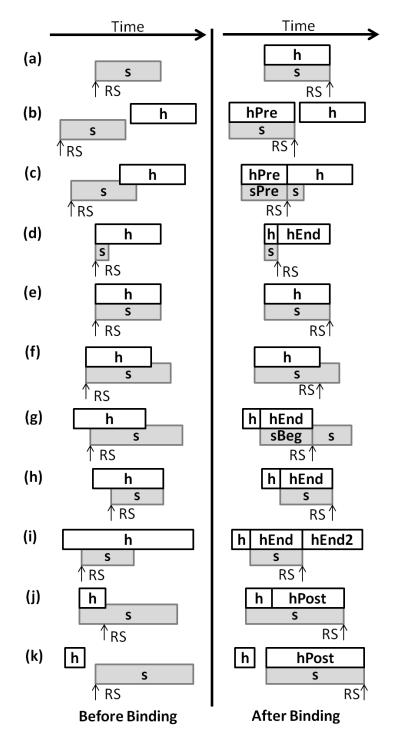

| Figure 3-9: Pseudocode for our path-based binder                                        |

|-----------------------------------------------------------------------------------------|

| Figure 3-10: Pseudocode for the GeneratePathCompressedGraph() function 95               |

| Figure 3-11: Pseudocode for the SelectModuleLocations() function                        |

| Figure 3-12: Pseudocode for the BindStorageToHolders() function                         |

| Figure 3-13: (a-k) Transformations that take place at the corresponding times 100       |

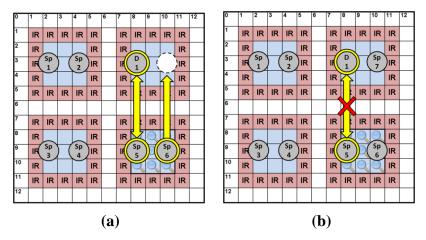

| Figure 3-14: Droplets 1 and 2 are traveling from source 1 and 2 (S1/S2) to 104          |

| Figure 3-15: Three different topologies showing modules stacked vertically 109          |

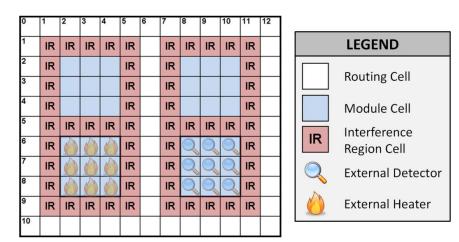

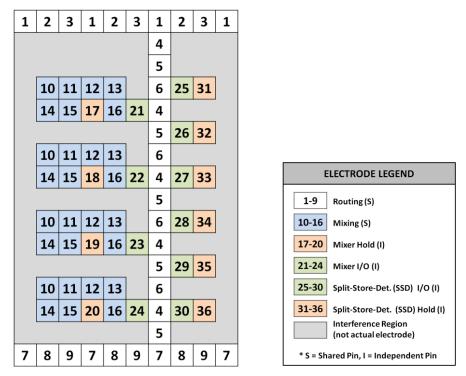

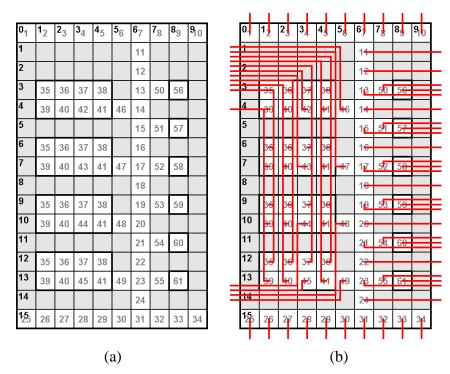

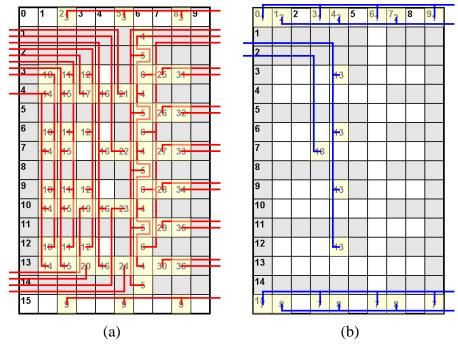

| Figure 4-1: Pin diagram for a 10×16 FPPC-DMFB which can accommodate 121                 |

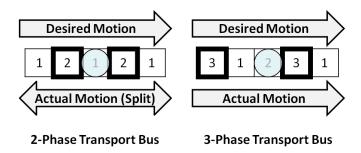

| Figure 4-2: At least 3 repeatable pins are needed to move a droplet along a 123         |

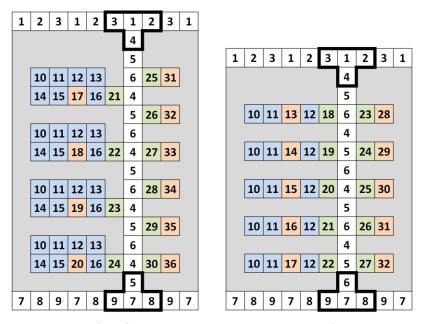

| Figure 4-3: The number or size of modules can be changed and the 3-phase 124            |

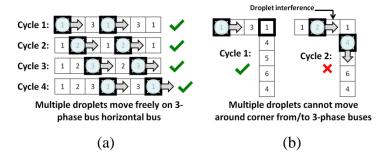

| Figure 4-4: Moving two droplets concurrently is (a) feasible when moving 124            |

| Figure 4-5: Multiple droplets moving through the vertical bus will result 125           |

| Figure 4-6: Pin-activation sequence showing how a single droplet (D2) 127               |

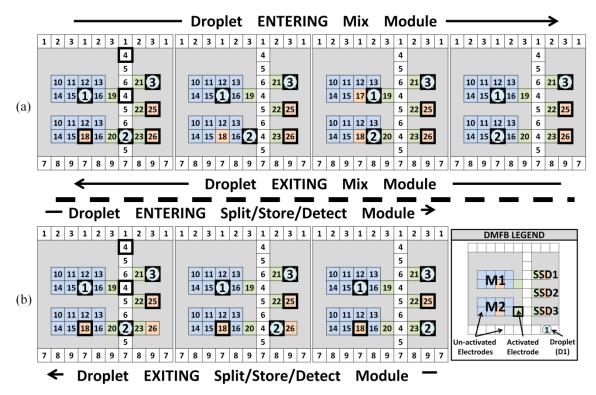

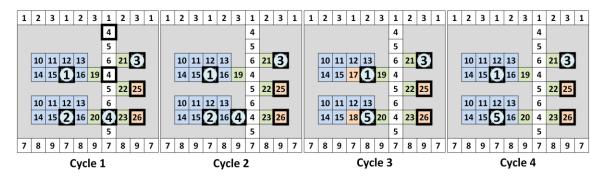

| Figure 4-7: The electrode/pin activation sequence (from Cycle 1 to 4) that 128          |

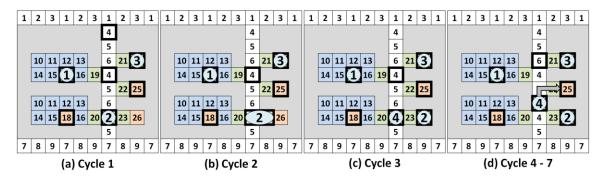

| Figure 4-8: Pin-activation sequence for splitting a droplet (D2) and storing 129        |

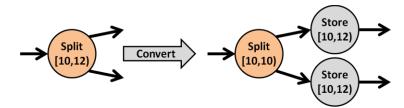

| Figure 4-9: Split operations are converted to a split and two stores for synthesis. 130 |

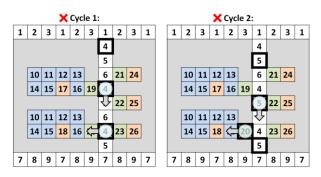

| Figure 4-10: Cyclic routing dependencies can be broken by first routing                 |

| Figure 4-11: Psuedocode for route computation                                           |

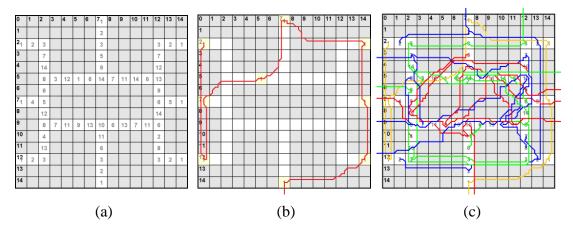

| Figure 4-12: (a) The pin-mapping for a pin-constrained DMFB for a PCR                   |

| Figure 4-13: The original FPPC-DMFB [30] detailing the (a) pin-mapping 138              |

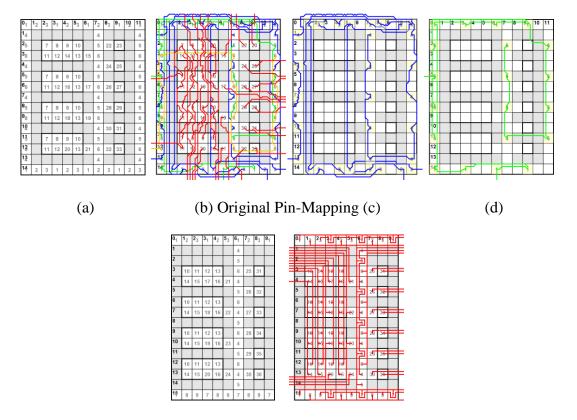

| Figure 4-14: The wire-routing model for the FPPC-DMFB generalizes                       |

| Figure 4-15: A top-down and cross-sectional view of a PCB showing dim 144               |

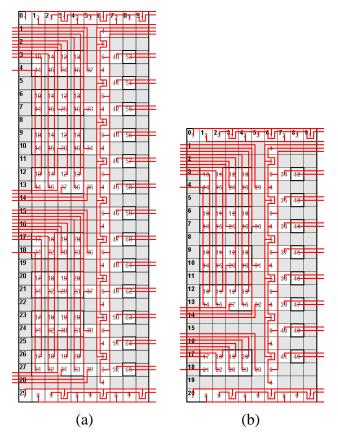

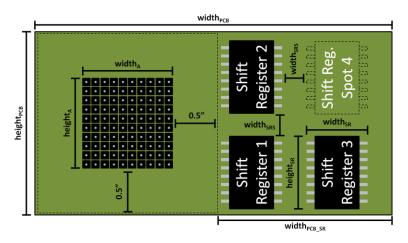

Figure 4-16: The component layout for PCB size estimation. The electrode ...... 145 Figure 4-17: An FPPC-DMFB variant that replaces 3-phase busses with direct ... 146 Figure 4-18: Two-layer wire-routing solution for *FPPC\_4\_MODULE*...... 151

Figure 4-19: Total wire-routing fabrication costs per DMFB board, including ..... 155

# LIST OF APPENDIX FIGURES

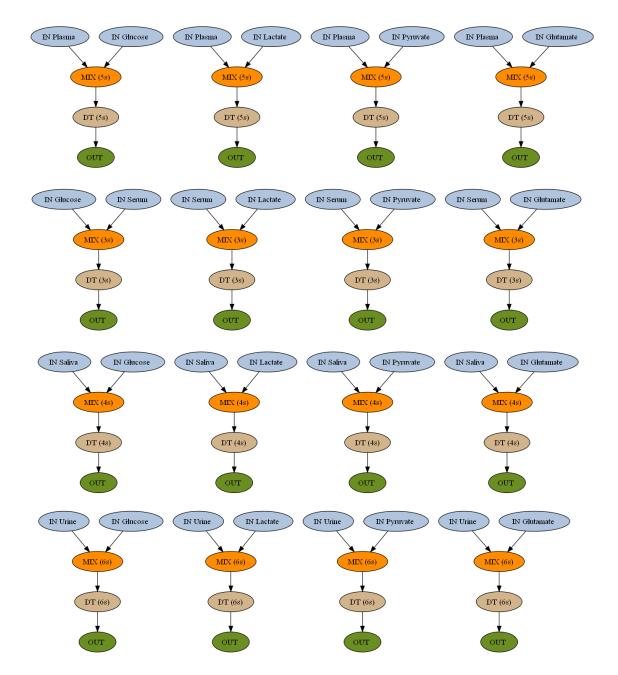

| Figure A - 1: PCR Benchmark; DAG for polymerase chain reaction mixing tree 175      |

|-------------------------------------------------------------------------------------|

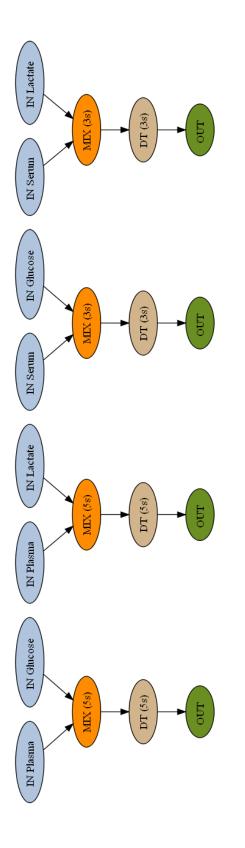

| Figure A - 2: InVitro1 Benchmark; DAG for an in-vitro diagnostics assay 176         |

| Figure A - 3: InVitro2 Benchmark; DAG for an in-vitro diagnostics assay 177         |

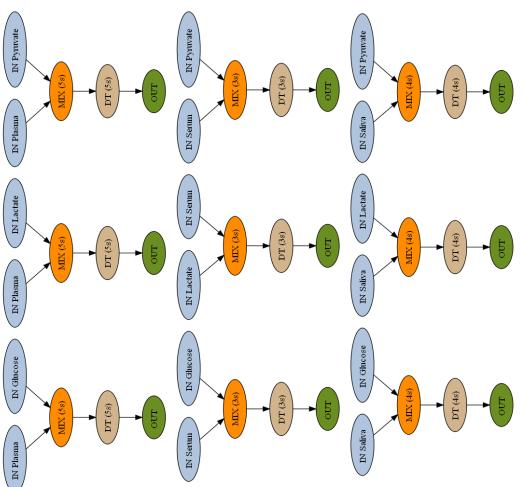

| Figure A - 4: InVitro3 Benchmark; DAG for an in-vitro diagnostics assay 178         |

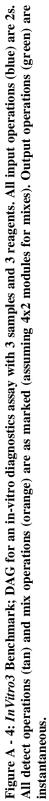

| Figure A - 5: InVitro4 Benchmark; DAG for an in-vitro diagnostics assay 179         |

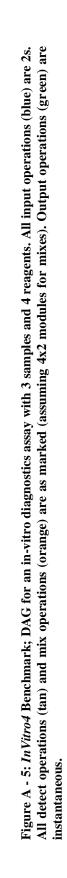

| Figure A - 6: InVitro5 Benchmark; DAG for an in-vitro diagnostics assay 180         |

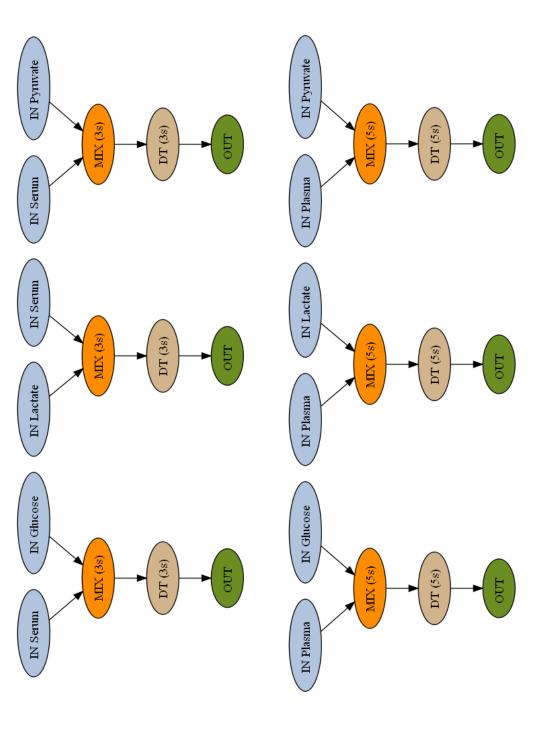

| Figure A - 7: <i>ProteinSplit1</i> Benchmark; DAG for a protein synthesis assay 181 |

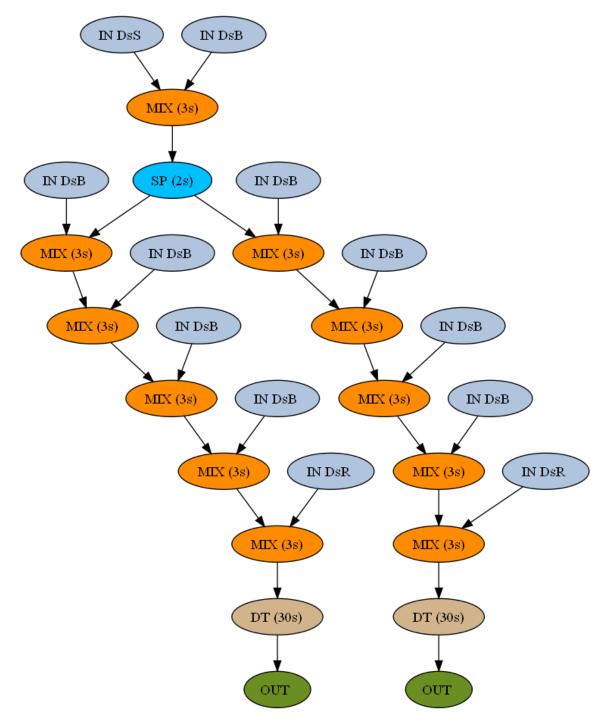

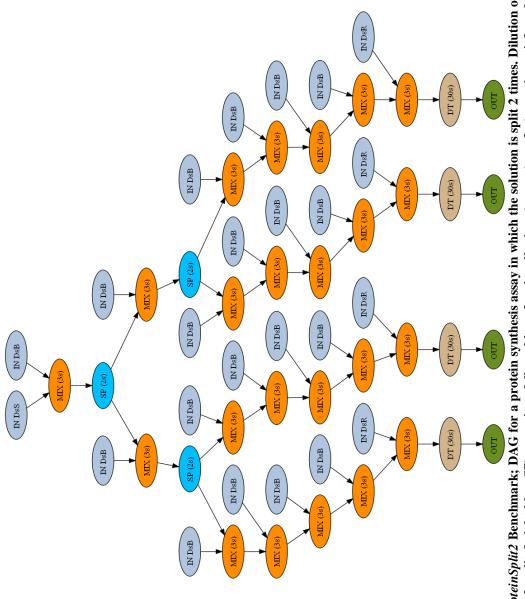

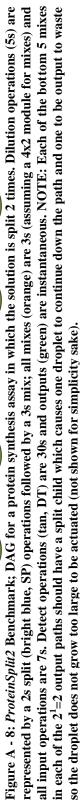

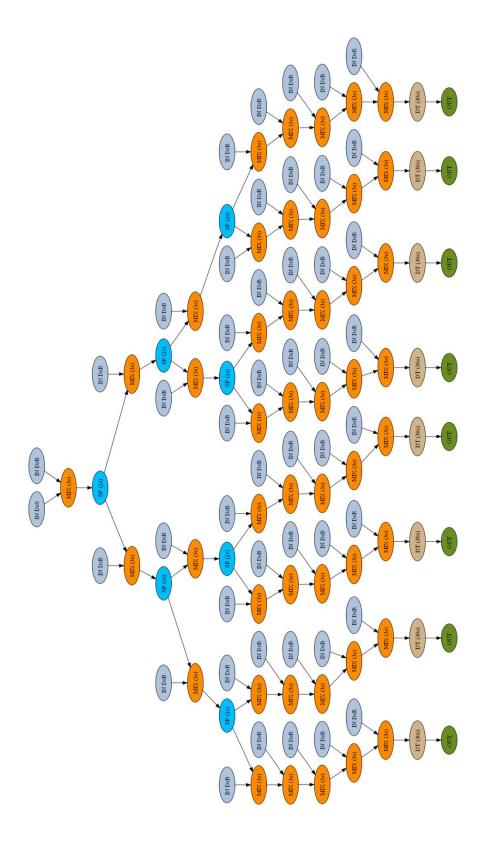

| Figure A - 8: <i>ProteinSplit2</i> Benchmark; DAG for a protein synthesis assay 182 |

| Figure A - 9: <i>ProteinSplit3</i> Benchmark; DAG for a protein synthesis assay 183 |

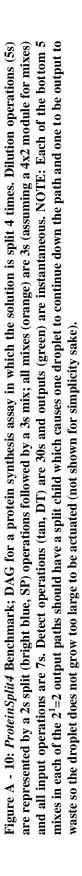

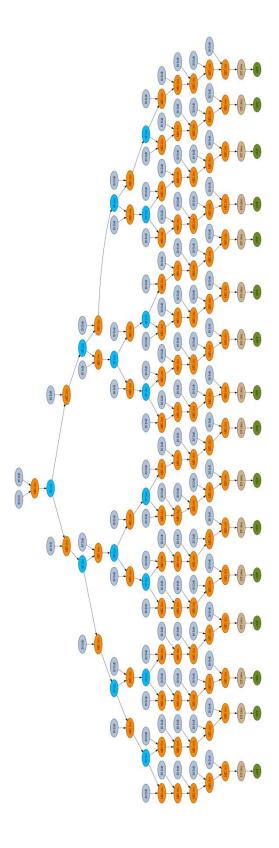

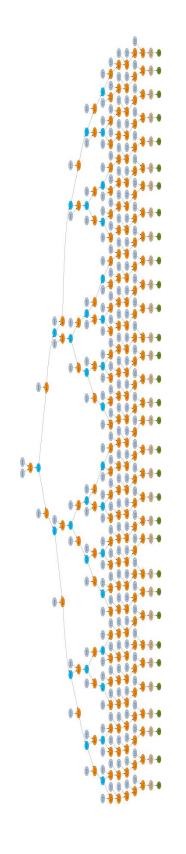

| Figure A - 10: ProteinSplit4 Benchmark; DAG for a protein synthesis assay 184       |

| Figure A - 11: ProteinSplit5 Benchmark; DAG for a protein synthesis assay 185       |

| Figure A - 12: ProteinSplit6 Benchmark; DAG for a protein synthesis assay 186       |

| Figure A - 13: ProteinSplit7 Benchmark; DAG for a protein synthesis assay 187       |

# LIST OF TABLES

Table 2-1: Prototypes for six BioCoder functions that are supported by EWoD ...... 37 Table 2-3: Microfluidic operations and BioCoder functions that enable droplet ..... 41 Table 2-4: Recovery synthesis time (averaged over 10 runs) for a 2-level protein... 62 Table 2-5: Average recovery assay runtime (averaged over 10 runs) showing ...... 62 Table 3-1: Table of benchmarks showing the number of different operation ....... 106 Table 3-2: Module library for mix operations for PCR and ProteinSplit assays..... 106 Table 3-4: Results showing the number of modules that can fit and the resultant.. 110 Table 3-5: Results showing the sizes of the DMFBs and resultant route lengths ... 110 Table 3-6: Results showing Path Binding (PB) vs. KAMER Placement (KP) ...... 113

Table 4-1: PCB Fabrication Parameters.

144

Table 4-3: The left side shows various metrics used for the Advanced Circuit ..... 151 Table 4-4: Wire routing costs for the 21 benchmarks, sorted in order of ...... 153 Table 4-5: Experimental results comparing the direct-addressing DMFB ...... 157

# **CHAPTER 1** INTRODUCTION

Over the last decade, microfluidics has emerged as a viable technology for automating and miniaturizing biochemical reactions. Instead of mixing fluids together on the order of milliliters and liters in test tubes and beakers, microfluidic devices can perform many of the same reactions by manipulating nanoliter-sized quantities of fluid on a small lab-on-chip (LoC) device. Microfluidic LoCs have been designed to execute a multitude of different biochemical applications including in-vitro diagnostics and immunoassays used in clinical pathology [75], DNA polymerase chain reaction (PCR) mixing stages used to amplify DNA [50] and protein crystallizations [81].

**Figure 1-1** shows the two major types of microfluidic LoCs. *Continuous-flow microfluidic devices* (**Figure 1-1(a**)), also called *analog microfluidic biochips*, perform biochemical reactions, known as *assays*, by actuating pumps to open and close microvalves [57]. On these devices, fluid flows through tiny channels in a continuous fashion similar to how water flows through the pipes in a house. In contrast, a newer LoC platform known as a digital microfluidic biochip (DMFB) performs assays by manipulating discrete droplets of fluid around a 2D-array of electrodes (see **Figure 1-1(b)**).

Although continuous-flow microfluidic devices are more mature and offer a solid platform for executing microfluidic assays, their micro-channel and micro-valve locations are permanently etched into the device, as seen in **Figure 1-1(a)**, which limits the LoC's capabilities since fluids can only be mixed and transported via the pre-planned layout.

Typically, continuous-flow devices are designed and fabricated to perform a single assay. DMFBs, however, offer a generic 2D-array of electrodes on which various microfluidic operations can be performed with much less restriction (see **'Section 1.1 - DMFB '**). Since DMFBs typically have no permanent regions for mixing and transportation, they are inherently reconfigurable in nature, which make them an excellent candidate for a general-purpose microfluidic device that can perform a wide assortment of assays.

Figure 1-1: (a) A continuous-flow microfluidic device operates on continuous flows of fluid that flow through micro-channels; (b) A digital microfluidic biochip (DMFB) operates on discrete droplets that move around a 2D-array of square electrodes.

## **1.1 - DMFB DROPLET MANIPULATION**

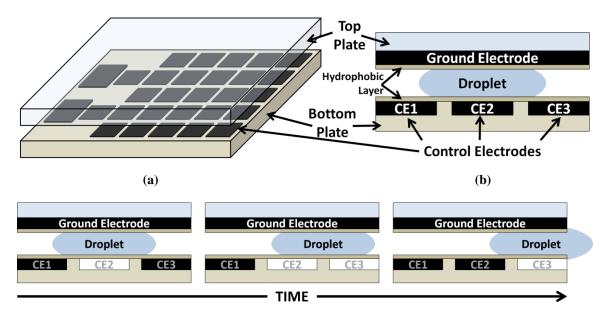

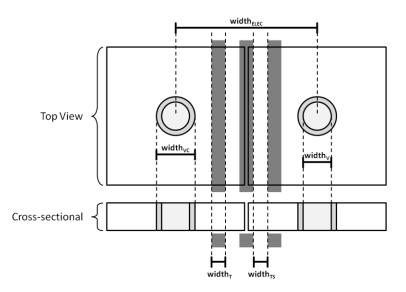

DMFBs execute assays by manipulating nanoliter-sized droplets of fluid on a 2Darray of electrodes, as seen in **Figure 1-2(a)**, and are typically based on a phenomenon known as electrowetting on dielectric (EWOD) [63]. An EWOD-based DMFB, as seen in **Figure 1-2(b)**, consists of a top and bottom plate coated with a hydrophobic layer (to prevent fluids from sticking to the DMFB). The bottom plate has an array of dropletsized control electrodes, while the top plate has a single conducting electrode that spans the entire array (**Figure 1-2(a**)) of control electrodes. Each droplet is sandwiched between the bottom and top plates and will hold its place if its underlying electrode remains activated.

(c)

Figure 1-2: (a) A DMFB is a planar array of electrodes; (b) Cross-sectional view of electrode array; (c) A droplet is transported from control electrode 2 (CE2) to CE3 by activating (white) CE3, while deactivating (black) CE2, allowing for droplets to be transported around the DMFB.

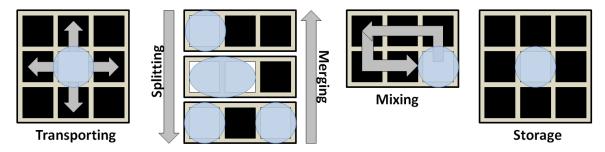

Figure 1-3: Basic microfluidic operations form the building blocks for assays to be executed.

In **Figure 1-2(b)**, a droplet is seen to overlap neighboring electrodes; when a neighboring electrode is activated, electrowetting causes an electric field change, inducing increased wetting and surface tension on that side of the droplet, which causes it to flow toward the newly activated electrodes [63]. Thus, **Figure 1-2(c)** shows that if CE3 is activated while CE2 is being deactivated, the entire droplet will move to cover CE3. As seen in **Figure 1-3**, with the proper sequence of electrode activations, several

fundamental microfluidic operations can be performed: droplet transportation, splitting, merging, mixing and storage. Sensor-based detection operations execute by moving a droplet to a detector (placed above an electrode) and storing the droplet there; among the most popular sensors beginning to be employed in microfluidic systems, optical sensors can be used to measure wavelength/color (e.g., a certain reaction may be considered complete when the solution turns a certain wavelength/color) [49][65][71], while capacitive sensors can be used to measure the volume and validate the presence of a droplet [64]. Dispense and output operations are performed by I/O reservoirs on the perimeter of the DMFB.

If a droplet is not centered over or adjacent to any activated electrodes, it will *drift* across the DMFB in an undetermined and unpredictable manner. In contrast, activating an electrode underneath a droplet will hold it in place as long as the electrode remains activated, inducing the storage operation seen in **Figure 1-3**.

### **1.2 - DMFB DEVICE TECHNOLOGY OVERVIEW**

There are several classes of DMFBs that provide varying levels of droplet control. Typical *direct-addressing* (*individually-addressable*) DMFBs have one control pin for each electrode (i.e.  $(M \times N)$  control pins for an  $(M \times N)$  array of electrodes) so each electrode (droplet) can be independently controlled at all times. However, the wiring cost of independently controlled electrodes, especially as array sizes grow, has motivated cheaper designs [82].

*Cross-referencing* DMFBs use (M + N) control pins to control an  $(M \times N)$  array of electrodes [23]. In this scheme, each row and each column has a single control pin; when

a particular column m and row n are activated, the electrode at (m, n) is activated. Multiple columns and rows can be simultaneously activated, but may cause superfluous electrode activation, yielding undesired droplet movement [80]. Thus, once a route for a direct-addressing DMFB is computed, each droplet-actuation cycle is serialized across multiple droplet-actuation cycles, resulting in prolonged routing times and increased algorithmic complexity.

*Pin-constrained* DMFBs represent another addressing scheme. An assay is first synthesized as if on a direct-addressing DMFB; then, special heuristics attempting to solve the clique partitioning problem (NP-Hard) are used to minimize the total number of control pins, based on which electrodes can be activated together without causing undesired droplet movement [80].

Active-matrix addressing designs are emerging which give independent control of  $(M \times N)$  electrodes while using only (M + N) control pins [60]. Active matrix addressing can scale without growing prohibitively expensive, while maintaining the maximum level of flexibility and control so that assays can be programmed with minimal levels of algorithmic complexity; however, the fabrication process of these devices is difficult and has not yet been mastered.

To summarize, pin-constrained designs offer minimal product costs, are inflexible, and cannot be reprogrammed after being manufactured; cross-referencing DMFBs are reprogrammable, but add another layer of complexity that must be handled to serialize droplet motion [80]. Individually-addressable and active-matrix DMFBs provide the most programmability and flexibility, in terms of droplet control; however, individuallyaddressable designs are expensive and the active-matrix fabrication process is not stable enough to yield reliable devices.

## **1.3 - HIGH-LEVEL ASSAY SYNTHESIS OVERVIEW**

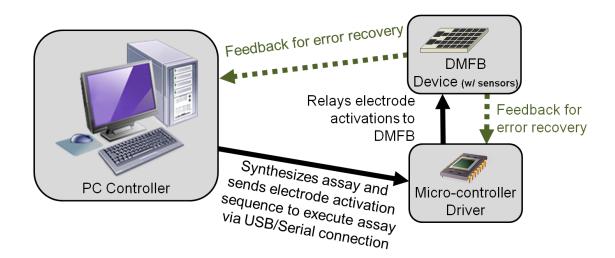

A digital microfluidic system typically consists of three parts, as seen in **Figure 1-4**: a PC controller, a micro-controller and a "wet" DMFB which contains the droplets where the microfluidic reaction is performed. The PC controller performs the computations which map a microfluidic reaction to a DMFB; this process is known as *synthesis* and yields an electrode activation sequence (see **'Section 1.3.3 - Droplet Routing'**) which is sent to the microcontroller. The microcontroller and its accompanying circuitry amplifies and "plays" this sequence of signals to the DMFB to activate the DMFB's electrodes, in turn performing the microfluidic reaction. Today, modern DMFBs have optical and capacitive sensors which can communicate back to the PC and microcontroller to help ensure proper execution of the microfluidic reaction and provide feedback for error recovery.

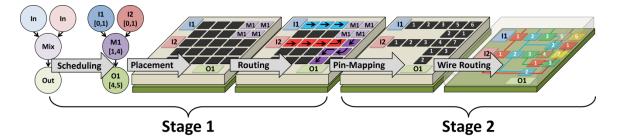

**Figure 1-5** details the general synthesis flow used for DMFBs. An assay can be represented as a directed acyclic graph (DAG), where the nodes represent microfluidic operations (e.g. mix, split, etc.) and the edges represent precedence (i.e., a partial order of operations). The left side of **Figure 1-5** depicts a simple assay in which two droplets are input, mixed, and finally, output from the DMFB.

Figure 1-4: A microfluidic system typically consists of three major parts: a PC controller, a microcontroller and a DMFB.

Figure 1-5: A typical microfluidic synthesis flow dictates that a microfluidic assay is represented in the form of a DAG; in Stage 1, its operations are scheduled and placed onto the DMFB array and droplets are routed between operation locations. In Stage 2, pin-mapping and wire routing are performed to eliminate unused electrodes and connect the electrodes to an external edge of the device to be driven by a microcontroller.

#### **1.3.1 - SCHEDULING**

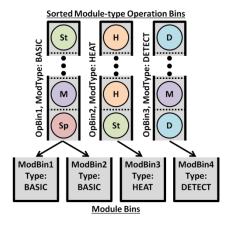

The first step of synthesis is scheduling. In this step the scheduler assigns an absolute start and stop time to each operation (e.g., the mix operation, M1, will execute from time 1 to 4). The scheduler must ensure that no operation starts before any of its parent operations end and that there are enough resources to simultaneously perform any concurrently scheduled operations (e.g., the scheduler must guarantee that two detection

operations are not scheduled at the same time if there is only one available detection module on the DMFB).

#### **1.3.2 - PLACEMENT**

Once a schedule has been computed, placement is performed. The placer decides where on the DMFB to perform each operation. For input operations, an input reservoir containing the appropriate fluid is selected. However, operations such as mixing and splitting can be performed at a variety of different locations on the DMFB. For example, in **Figure 1-5**, the mix operation MI is placed in the 2×2 array of cells in the top-right corner of the DMFB. However, MI could be placed in any unoccupied 2×2 array of cells on the DMFB. This array of cells used to denote the location of an operation is temporary and is known as a *module*. As seen in **Figure 1-6**, a mix operation may be placed into a variety of different module sizes, although the time it takes to complete the mix operation may vary based on the module size. This allows the placer flexibility when placing operations. It should be noted, however, that if the placer changes the module size, the schedule may need to be recomputed because of the new module's required change in operation length.

Figure 1-6: An operation, such as the mix operation from Figure 1-5 (M1), leverages a module library to select its duration and module shape (7 distinct horizontal/vertical orientation options shown given the 4 module shapes) and is then placed anywhere onto an empty DMFB.

At each time-step of the schedule, all of the executing operations and stored droplets must be placed at different locations on the chip while simultaneously ensuring that modules are arranged in such a way as to avoid placement failure (e.g., **Figure 1-7(a)**). In particular, operations that required specialized external devices, such as heating or detection, must be placed on DMFB locations that are accessible to the appropriate specialized devices [76]. In addition, module placement should leave enough space around modules to prevent droplet routing failure; in the case of a poor placement, a droplet may not be able to reach its destination because every possible path is being blocked by an existing module (as seen in **Figure 1-7(b**)), causing the assay to fail.

Figure 1-7: (a) Placement failure occurs because there is insufficient space for M7 to be placed given the placement of modules M1-M6; (b) Routing failure occurs because the droplet (D) is attempting to reach the detection zone (marked with magnifying glass lenses) but cannot because modules M1-M3 are placed in such a way that block all paths to the destination.

### **1.3.3 - DROPLET ROUTING**

Next, once operations have been scheduled and their corresponding modules have been placed onto the DMFB, droplet routing is performed to compute paths between the modules where each operation is performed. Operations can be routed from input reservoirs to modules, from modules to modules, and from modules to output reservoirs. Referring back to the scheduled DAG in **Figure 1-5**, the edges also represent the points in the assay when a droplet may need to be routed to a new location on the DMFB.

The router must ensure that a droplet reaches its destination and that it does not collide or interfere with any other droplets currently being routed or performing an operation (e.g., a newly routed droplet could interfere with an ongoing mix). To avoid droplet interference, a set of simple rules is followed. An *interference region* is defined as the cells directly adjacent to a droplet, as seen in **Figure 1-8(a)**. A *droplet actuation cycle* (or *cycle*) is the discrete time-step that it takes for a droplet to move from the center of one electrode to the center of an adjacent electrode; the cycle length is determined by the electrode size, applied voltage and fluidic properties, and thus, can differ from system to system. At the beginning of each cycle, an interference region is set around each droplet at its current location. As a droplet moves, its interference region expands to include the entire region around the two cells the droplet occupied during that cycle (see **Figure 1-8(b)**). No droplet can move into a cell containing another droplet or into the interference region of any other droplet at any time, unless those droplets are part of the same merge or split operation. This set of rules keeps droplets safe by prohibiting any other droplets to move into potentially adjacent cells at any time during a cycle.

Figure 1-8: (a) The interference region ('IR') of a droplet at the beginning of a cycle represents its static constraints; (b) The interference region at the end of a cycle demonstrate its dynamic constraints.

$$|X_i(c+1) - X_j(c+1) \ge 2|$$

and  $|Y_i(c+1) - Y_j(c+1) \ge 2|$  (1.1)

$$|X_i(c+1) - X_j(c) \ge 2|$$

and  $|Y_i(c+1) - Y_j(c) \ge 2|$  (1.2)

$$|X_i(c) - X_j(c+1) \ge 2|$$

and  $|Y_i(c) - Y_j(c+1) \ge 2|$  (1.3)

For the sake of completeness, a formal description of the fluidic constraints, as detailed in ref. [78], is included in **Equations 1.1-1.3**. Let *n* be the number of droplets in the system, and  $0 \le i, j < n$ . Then, the constraints seen in **Equations 1.1-1.3** must hold for all pairs of droplets  $D_i$  and  $D_j$ ,  $i \ne j$ . The 2D microfluidic array is represented by the coordinates (X, Y), where  $(X_i(c), Y_i(c))$  is used to represent the location of droplet  $D_i$  at the beginning of cycle *c*. We assume that no droplet  $D_i$  is initialized inside the interference region of any other droplet  $D_j$ . **Equation 1.1** ensures that the locations of  $D_i$  and  $D_j$  are not adjacent to each other at the end of cycle *c*. **Equation 1.2** and **Equation 1.3** guarantee that  $D_i$  and  $D_j$  never enter each other's interference regions (the extended region seen in **Figure 1-8(b**)) at any time during cycle *c*.

The output of the droplet router is a list of electrodes to activate each cycle; a *cycle* is the time it takes to move a droplet from one electrode to the next. In **Figure 1-9**, a "dry" controller (e.g., a PC and/or microcontroller) sends signals to activate electrodes during each cycle on the "wet" DMFB.

Figure 1-9: The droplet router produces an electrode activation sequence, driven by a microcontroller (left), which corresponds to droplet movement on the DMFB.

#### 1.3.4 - PIN-MAPPING

Once droplet routing is complete, an optional step called pin-mapping can be performed when DMFB manufacturers want to reduce the cost of the device. As mentioned in **'Section 1.2 - DMFB Device Technology Overview'**, in an individually addressable DMFB, each electrode is wired to an external electrical pin on the edge of the DMFB; in turn, each pin is connected to and driven by the microcontroller such that each electrode can be independently controlled (see Figure 1-10(a)). Individually addressable DMFBs offer the most flexibility in terms of droplet coordination; however, they are expensive to fabricate because the number and complexity of wire routes that must exist to connect each electrode to an external pin on the DMFB can require an increasing number of printed circuit board (PCB) layers (Figure 1-11(a)), which significantly adds to the cost of a DMFB.

Figure 1-10: Activating a pin on a (a) direct-addressing DMFB activates (white) exactly 1 electrode per pin; (b) a pin on a pin-constrained DMFB activates 1+ electrodes per pin, depending on the pin layout.

Figure 1-11: A DMFB has printed circuit boards (PCBs, green layers) underneath the substrate containing the control electrodes that serve as the medium for wire-routing. A microcontroller sends signals to and interfaces with the DMFB via one or more integrated circuit (IC) clips. (a) A direct addressing DMFB, may require many PCB layers, while (b) a pin-constrained DMFB is designed to perform wire routing with fewer PCB layers.

Pin-constrained DMFBs employ pin-mapping techniques to reduce the wire-routing complexity by connecting multiple electrodes together in such a way that activating a single external pin (via a single signal from the microcontroller) can activate multiple electrodes (**Figure 1-10 (b**)). In **Figure 1-5**, the pin-mapping step removes the 10 non-used electrodes and connects the remaining electrodes in such a way that reduces the number of pins from 15 to 7.

The scheduling, placement and routing steps of synthesis are performed as on a direct addressing DMFB for a particular assay (as seen in Stage 1 of **Figure 1-5**); then the resultant electrode activation sequence is examined to compute a pin-mapping that will successfully execute the synthesized assay using fewer pins [82]. The drawback of this approach is that the DMFB is now physically tailored to execute a single assay.

### **1.3.5 - WIRE ROUTING**

The last stage of synthesis is wire routing. The control electrodes reside on the lower substrate of the DMFB (seen in **Figure 1-2(b)**), while the wire-routing is performed below this substrate on one or more printed circuit board (PCB) layers (the green layers in **Figure 1-5** and **Figure 1-11**). In an individually addressable DMFB, this stage computes wire-routes to connect each electrode to its own pin on the peripheral of the DMFB, allowing the DMFB to be controlled by the microcontroller signals (**Figure 1-11(a**)).

In a pin-constrained DMFB, the wire router must first connect all of the electrodes together with the same pin-number. For example, in **Figure 1-11(b)**, all the electrodes with a "1" must be connected together (done so with the red wires), all the electrodes with a "2" must be connected with each other (blue), and so on and so forth. Each network of wires connecting a group of electrodes with the same pin-number is known as a *net*. Once the nets are connected together, a wire must be routed to connect each net to its own pin on the peripheral of the DMFB. Because of the reduction of electrodes and combination of pin signals, pin-constrained devices typically have fewer and smaller PCB layers, making them much more cost-effective than direct addressing DMFBs.

## **1.4 - DMFB DESIGN OBJECTIVES**

This dissertation addresses two major objectives and goals in the design of DMFBs:

- 1. DMFBs that are dynamic in nature

- 2. DMFBs that are programmable

The following sub-sections provide a brief background and explain why these objectives are important and why they are not currently being addressed.

#### **1.4.1 - DYNAMIC DMFBs**

High-level synthesis for DMFBs has been studied for over a decade and began by employing a static compilation flow [73]. In a static compilation flow, scheduling, placement and routing are performed in their entirety and the output is compiled into a deterministic electrode activation sequence, as described in **'Sections 1.3.1 - Scheduling'** and **'Section 1.3.3 - Droplet Routing'**; however, a number of errors can occur during the execution of an assay, such as:

- A droplet might not move as intended from one electrode to the next

- A mix operation might not reach a uniform concentration in its pre-allotted time

- A droplet might not split into two droplets of perfectly equal size, as expected

The deterministic nature of static compilation assumes that there are no errors during assay execution; thus, without live feedback from the DMFB, it is very difficult to know if an assay run by a deterministic state machine (i.e., static compilation) has executed properly since there is no way to detect and respond to an error.

**Figure 1-13(a)** shows the basic order of a static synthesis flow (i.e., static compilation) and that scheduling, placement and routing are performed exactly once; the

resultant electrode activation sequence attempts to execute the assay in its entirety. In fact, static synthesis is typically performed for a particular assay during the DMFB design process and the electrode activation sequence is compiled as a bit-vector (containing the *On/Off* signals for each electrode at each cycle) onto the DMFB long before an end-user ever receives the final biochip; the resultant electrode activation sequence mimics droplet movement and is the driver for droplet actuation, as seen in **Figure 1-12**. Since an assay is compiled once during the design process, complex, long-running algorithms (e.g., it could take hours to compute synthesis steps) are typically used to yield highly-optimized results (e.g., shortest overall execution time; fewest number of electrodes utilized) [73][75][76].

Figure 1-12: Example of the linear state machine model of DMFB control. The output of each state is the subset of electrodes in the DMFB that will be activated during each time step (shown in gray). The state machine is timed, based on the activation frequency, typically 100Hz. In this example, two droplets are transported to a common location so that they can be merged, and two droplets are stored in place.

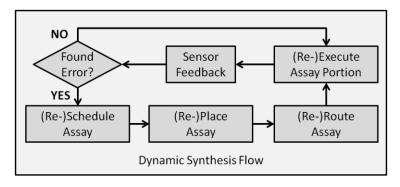

Today's DMFBs can now integrate optical and capacitive sensors for detecting live errors during an assay's execution [21][64][71]. Although many of these sensors were developed during the same time-frame as the initial DMFB synthesis publications [65][73][75], synthesis works have not attempted to dynamically integrate live feedback from sensors until more recently [6][7][36][52][53][54]. A dynamic synthesis flow, as seen in **Figure 1-13(b)**, may perform an initial synthesis for an entire assay, but executes smaller portions in between sensor-feedback checkpoints. A dynamic synthesis flow can continue executing the assay as originally synthesized until an error is detected, at which point it will re-synthesize the assay to account for the unexpected events.

**(a)**

**(b)**

Figure 1-13: (a) A static synthesis flow performs scheduling, placement and routing exactly once, and will break in the presence of errors since it cannot adjust to live feedback; (b) a dynamic synthesis flow computes an initial schedule, placement and routing, but then executes portions of the assay while checking sensor feedback. If an error is found, portions of the assay can be re-synthesized.

Error-recovery is not the only reason for a dynamic synthesis flow. In addition, livesensor feedback allows dynamic decisions to be made about intermediate results. For example, given the completion of a clinical diagnostic on a DMFB, one might want to continue by running a particular sub-assay based on whether the initial result was positive or negative. Thus, dynamic synthesis also allows the introduction of control flow into DMFB research.

### **1.4.1.1 - BARRIERS TO DYNAMIC DMFBS**

There are two major problems with current synthesis methods that make them poor dynamic synthesis algorithm candidates for DMFBs:

- 1. Current synthesis algorithms take too long

- 2. Current synthesis algorithms do not guarantee legal solutions

As mentioned in the 'Section 1.4.1 - Dynamic DMFBs', static synthesis methods typically employ long-running algorithms that can take hours or days to yield results. In contrast, many assays only take seconds or minutes to perform in their entirety; thus, in a dynamic environment where synthesis methods are called to re-map an assay in response to runtime errors or control flow, it is not feasible to wait hours or even minutes to resynthesize portions of the assay. Synthesis methods are needed that can dynamically interpret the assay (in response to live feedback) in milliseconds (or less) such that the overall execution time of the assay is not impacted in any significant way.

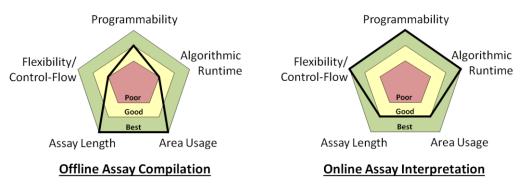

In contrast to static offline compilers, which synthesize assays as deterministic statemachines, a *dynamic online interpreter* will act more like a virtual machine which manages the DMFB's resources and interprets assays on-the-fly. **Figure 1-14** shows the tradeoffs that need to be made when moving synthesis online. During offline compilation, optimized designs are created with little concern to algorithmic runtime (time need for synthesis) since the synthesis process is run once and the compiled "executable binary" is packaged into an application-specific device. With a programmable DMFB, the end-user will have to wait each time a programmed assay is synthesized. Furthermore, each time a branch is taken, the user will have to wait as the target assay of the branch is interpreted online. Thus, new synthesis methods are needed that concede optimality in assay length (i.e. schedules) and area to reduce algorithmic runtimes from seconds/minutes to milliseconds and achieve a greater amount of flexibility [52].

Secondly, current synthesis algorithms do not guarantee legal solutions. For example, a droplet routing algorithm has the task to compute routes from any source to any destination, as dictated by the placement stage; however, all previous droplet routing algorithms found cases that proved to be unroutable (no path existed from source to destination) or yielded deadlock (i.e., so much congestion existed that droplets would get stuck in an irresolvable "traffic jam" and be unable to reach their destinations) [11][16][26][88]. In these cases, it may be possible to re-perform the scheduling and placement stages in an attempt to provide routable problems; however, these operations are computationally expensive in the context of dynamic synthesis and can cause the enduser to wait for significant periods of time, while his or her assay is being executed, in an attempt to find a new synthesis solution. *Thus, it is imperative that dynamic synthesis methods guarantee a valid solution on the first attempt to successfully execute the assay to completion.*

### **1.4.2 - PROGRAMMABLE DMFBS**

It is crucial that DMFBs remain programmable. In an effort to optimize and reduce the cost of DMFBs (see 'Section 1.3.4 - Pin-Mapping and 'Section 1.3.5 - Wire Routing'), many papers have been published in the microfluidics community detailing algorithms to design assay-specific DMFBs [39][40][41][50][51][82][86]. Although there is a valuable place for this type of research, this means that only a few, select applications will make their way to DMFB technologies, as seen fit and profitable by the handful of DMFB vendors currently in existence. In contrast, we believe that the continued development of programmable DMFBs could enable researchers around to globe to specify and execute their own experimental assays, taking advantage of real-time sensory feedback to perform biochemical reactions with greater accuracy and speed than ever. Ultimately, programmable DMFBs will ease and encourage the development of new applications, allowing this emerging technology the exposure and traction that it needs to fully catch on in the scientific community and general populous.

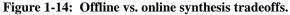

Just as the iPhone is made more useful by its robust app market, we believe that DMFBs will become ubiquitous as independent researchers are able to contribute their own DMFB assay protocols to the scientific community for fast, concise, and reliable reproduction of scientific experiments and clinical tests. Imagine an assay is developed to detect a new strain of flu. Instead of having to develop a unique DMFB hardware solution, an end-user (presumably a physician's office, but, perhaps, someday a patient him/herself) can simply download and install the new assay protocol onto their low-cost, programmable DMFB and purchase a "fluids kit" that has the necessary reagents to

perform the assay (see **Figure 1-15**). This overall usage flow promises to be much more efficient concerning both time and money.

Figure 1-15: A DMFB "App Store" would allow a user to download an assay specification to run on their own DMFB; separate fluid kits could be developed and purchased, as well.

### **1.4.2.1 - BARRIERS TO PROGRAMMABLE DMFBS**

As mentioned in 'Section 1.3.4 - Pin-Mapping', 'Section 1.3.5 - Wire Routing', and 'Section 1.4.2 - Programmable DMFBs', many synthesis flows map assays to highly-optimized pin-constrained DMFBs that, although cost effective, are severely limited in application. Typically, these DMFBs are designed to perform a small handful of assays (e.g., 3), at most, and are not able to perform much else. Work exists which takes an already-existing DMFB design and attempts to map two independent droplet movements onto it to obtain a general-purpose DMFB [51]; although this may lead to some limited opportunities for error-recovery and very basic assays, it does not allow for more-complex, generic assays to be synthesized on low-cost DMFBs. *Thus, it is imperative that synthesis algorithms and DMFBs are designed to not only be inexpensive, but also to perform any sequence of basic operations, instead of specific assays.*

## **1.5 - CONTRIBUTIONS**

This dissertation details significant contributions to the primary design objectives, detailed in 'Section 1.4 - DMFB Design Objectives', of achieving programmable and dynamic DMFBs. In CHAPTER 2, we present interpretation, which is a form of dynamic synthesis. Instead of static compilation which generates a deterministic electrode activation sequence, interpretation acts like an operating system that manages resources as an assay is being executed, allowing for resources to be allocated and dispatched dynamically in response to live-feedback. We also provide new language constructs necessary to incorporate control flow into DMFBs. CHAPTER 3 presents the idea of a virtual topology, which is an abstract organization of electrodes into "city streets and blocks," which help simplify dynamic synthesis flow algorithms; we introduce several variations of a virtual topology and detail scheduling, placement and routing algorithms that accompany them to yield fast, reliable, dynamic, programmable DMFBs. CHAPTER 4 details a pin-constrained physical topology which offers a solution to reduce the cost of a DMFB while maintaining programmability. Our design is pinconstrained, and thus, very inexpensive, but also designed to perform basic microfluidic operations, making it general-purpose in nature. In this chapter, we provide the first detailed cost analysis for DMFB PCB layers and shed light on the relationship between, PCB layer count, I/O pin count and cost. Finally, CHAPTER 5 concludes by summarizing the general findings of this dissertation.

# **CHAPTER 2** INTERPRETATION

## **2.1 - INTRODUCTION**

At present, LoC programming is either done at the machine level (i.e., manually choosing a sequence of actuation signals to send to the device over time), or is highly restricted, e.g., to assays that can be represented as DAGs without control flow and without the ability to take action based on feedback provided by the device. This chapter introduces a software interpreter that performs online execution of assays featuring control flow, allowing them to be scheduled and executed immediately in response to live, sensor-based feedback. To allow the programmer to express control flow operations, language extensions to a high-level biochemical programming language are introduced as well. The long-term objective of this research is to open the door for new microfluidic capabilities and applications.

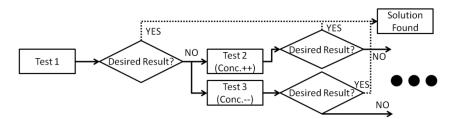

**Figure 2-1** motivates the need for control-flow and online interpretation with a drug discovery application. The assay performs a test (Test 1), detects the result, and then automatically responds by determining that it has found a valid solution, or continues exploring the solution space by executing new assays (Test 2 and 3) with varying concentrations. **Figure 2-1** shows the first few tests, but this procedure could be extended and repeated hundreds or thousands of times, adjusting various parameters along the way, until a valid solution is found.

Without control-flow, this application is intractable for all but the smallest examples because the designer must create a single DAG offline that describes and handles each possible path through the application [6]. Instead, an online interpreter could leverage control-flow to instantly schedule and dispatch new assays (in **Figure 2-1**, the boxes labeled Test 1-3) upon detection of any terminating, dependent assays.

Figure 2-1: A control-flow graph for a simple drug-discovery assay that increases (++) or decreases (--) concentrations based on the results of previous tests.

Although synthesis has been performed entirely offline up to this point, Ho, Chakrabarty and Pop suggest that online systems are forthcoming with the development of "specialized heuristics" which can perform synthesis in milliseconds [36]; Luo, Chakrabarty, and Ho [52] have implemented one such specialized heuristic for an error detection and recovery scheme based on check-pointing: at each checkpoint, a droplet is routed to a sensor that detects whether its concentration is satisfactory; if not, the assay is re-synthesized on-the-fly to repeat the sequence of operations that produced the droplet, interleaving the schedule of these newly-introduced operations with concurrent operations that do not depend on the droplet that failed the checkpoint.

### 2.1.1 - INTERPRETATION VS. COMPILATION

Historically, assays have been specified as DAGs, without control flow. A typical compilation sequence is shown in **Figure 1-5**. The DAG is first scheduled [20][33][61] [65][75]; dimensions for each operational module are selected [77][83]; scheduled operations are then placed onto the 2D grid, ensuring that no concurrently executing

operations overlap to prevent interference [45][76][87]; lastly, non-interfering droplet routes are computed to deliver droplets to the appropriate DMFB locations at appropriate times [11][16][38][48][66][67][69][78][88]; in some cases, all of these problems can be solved in conjunction with one another [56].

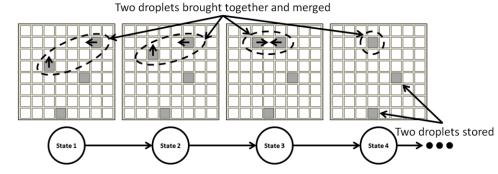

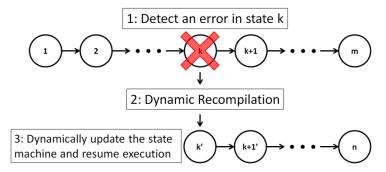

The control program that is generated by the compiler is a linear state machine, as shown in **Figure 2-2**. Each state specifies a subset of electrodes that will be activated; it typically takes 10 ms to transport a droplet to an adjacent cell, and mixing/dilution times during assay execution are on the order of seconds or tens-of-seconds. The linear state machine control model is wholly deterministic, which is acceptable for a scheduled DAG with no operation variability. To cope with bounded variability, it is possible to enumerate schedules for all possible combinations of operation times, which is exponential in the general case [6]. An alternative approach, which can accommodate assay operations that fail and require partial re-computation, is to pause assay execution temporarily and recompile the assay on-the-fly [7][52][90]. Although this overall approach results in the execution of a non-linear state machine, it uses dynamic recompilation to replace one linear state machine with another, as shown in **Figure 2-3**.

Figure 2-2: Example of the linear state machine model of DMFB control. The output of each state is the subset of electrodes in the DMFB that will be activated during each time step (shown in gray). The state machine is timed, based on the activation frequency, typically 100 Hz [88]. In this example, two droplets are transported to a common location so that they can be merged, and two droplets are stored in-place.

Figure 2-3: In response to an error detected in state k, the assay is paused and recompiled, which includes the insertion of new states to recompute fluids that have been lost due to erroneous processing, which may execute concurrently with other ongoing assay operations that were not adversely affected. The output is a new linear state machine that compensates for and corrects the errors that occurred.

### **2.1.2 - CONTRIBUTION**

We have developed a compiler and runtime system to translate assays specified using a high-level language into an executable form appropriate for a DMFB. Assays are specified using BioCoder [9], a C++ library for biological protocol specification developed at Microsoft Research, India. We present new language extensions to BioCoder that facilitate user-specified control-flow operations (e.g., conditionals, loops, droplet-transfer mechanisms). The interpreter can execute assays with control flow, use feedback from the DMFB to make control flow decisions, and does not rely on complex re-synthesis methods that dynamically recompile the assay when control flow becomes unpredictable [6][7][52][90]. To date, prior compilers targeting DMFBs are limited to assays specified as DAGs and cannot handle arbitrary control flow or feedback from sensors integrated onto the DMFB. The framework presented herein addresses these challenges through dynamic interpretation, thereby enlarging the space of assays that can be compiled onto EWoD devices.

### **2.2 - VIRTUAL TOPOLOGY**

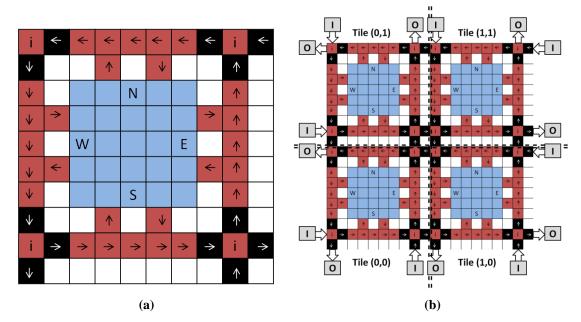

The system outlined in this chapter interprets assays dynamically, rather than compiling them statically and then (possibly) recompiling dynamically. Similar to prior work by Griffith et al. [26], the approach taken here imposes a *virtual topology* (Figure 2-4) on the DMFB that restricts the functions that different cells can perform; the interpreter exploits the restrictive structure to achieve fast algorithmic runtimes. Input and output reservoirs are placed on the perimeter of the DMFB, as seen in Figure 2-4(b). The city blocks are referred to as (*work*) *modules*, because all non-I/O assay operations occur there. Each module can perform one operation (e.g., merging, mixing or splitting) or can store up to four droplets. External devices such as heaters or optical detectors can be affixed to the DMFB above or below a module. All streets are 1-way; eight 1-way streets meet together at rotaries, which offer an abstraction like a network router. Droplets travel clockwise through these rotaries.

Without loss of generality, a droplet traveling north that enters a rotary could continue straight, or turn left (west) or right (east); our routing algorithms do not allow droplets to reverse directions, so a droplet would not enter a rotary traveling north and then exit traveling south. A *tile* consists of a module and the four adjacent streets

surrounding it, as shown in **Figure 2-4(a)**. If the module is 5x5, then a tile requires a 10x10 array of cells. Tiles are then repeated in two dimensions to form the virtual topology. For example, **Figure 2-4(b)** shows a virtual topology that is a 2x2 array of tiles.

Figure 2-4: (a) A tile is the fundamental building block of the virtual topology and contains a work module (blue) where operations are performed and a network of one-way "streets" (red/black) for droplet transportation; (b) the virtual topology is imposed onto a DMFB by tiling the fundamental building blocks to create a 2D array of tiles.

### **2.2.1 - Synthesis Simplifications**

The virtual topology simplifies the problems of scheduling, placement and routing, which facilitates low-overhead dynamic interpretation and responsiveness to control flow:

**Scheduling:** With no virtual topology, the scheduler estimates the number of modules it can support from the dimensions of the microfluidic array. Ambitious estimations overestimate the number of concurrent operations that can occur on the DMFB surface and often leads to placement and routing errors; in these, cases, resource

estimation and scheduling will need to be performed again. In contrast, a virtual topology provides a concise number of resources that are guaranteed to fit in the array, ensuring that placement and routing errors do not occur; thus, scheduling only needs to be performed once to compute an initial schedule.

**Placement:** Rather than placing operations at any location on the DMFB, the interpreter dynamically *binds* operations to modules, as shown in **Figure 2-5**. In principle, any available work module can be chosen; when multiple modules are available, the best choice is generally the one that is closest to the sources of the droplet(s) that are the operation's inputs; this minimizes droplet transportation latency.

**Routing:** The traditional approach to droplet routing is chaotic and disorderly, in part, driven by the fact that the placement of assay operations is likewise. The virtual topology, in contrast, imposes an orderly network of city streets that all droplets must follow. This limits the number of legal routes between each source-destination pair, which simplifies the process by which routes are computed. The approach taken here is to adapt deadlock-free 2D mesh network routing algorithms [18] to be compatible with DMFB technology. Thus, droplet routing follows a simple *protocol*, rather than solving a challenging constrained-optimization problem.

Figure 2-5: The operations of a scheduled DAG are bound to the modules indicated during the specified time steps.

### 2.2.2 - DEADLOCK-FREE 2D-MESH ROUTING

The virtual topology organizes the DMFB as a 2D-mesh network of work modules, where the rotaries play a role akin to network routers. One contribution of this chapter is to adapt deadlock-free 2D-mesh routing algorithms [18] to DMFBs using this virtual topology. Deadlock-free routing is important in an online system where assays are scheduled and executed on-the-fly because it is imperative to guarantee droplets can reach their destination.

To motivate the design for our virtual topology, we highlight the similarities and differences between our virtual topology and a 2D-mesh network in the following subsections. Later on, **'Section 2.5.2.3 - Droplet Transportation Protocol (DTP)'** shows how 2D-mesh routing algorithms are leveraged to achieve deadlock-free routing in our

system. Griffith et al. [26], it should be noted, also achieved deadlock-freedom in their virtual topology, but did so by limiting the injection rate of droplets into the system.

#### 2.2.2.1 - ANALOGUE TO 2D-MESH TOPOLOGY

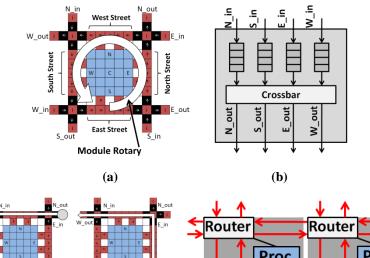

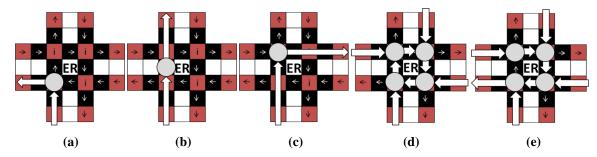

As shown in **Figure 2-4**, a tile contains a module surrounded by one-way streets on each side. The module has an entry and exit on each side and each corner of the tile contains an intersection in which droplets can choose to stay in the current tile or travel to a neighbor (**Figure 2-6(a)**). The four streets and intersections surrounding the module form a counter-clockwise traffic circle called the *module rotary*. In **Figure 2-6(c)**, *exchange rotaries*, which allow droplets to move from one tile to its neighbors, are formed between tiles.

The virtual topology presented here shares many similarities with 2D-mesh networks:

**Modules and I/O to Processors:** In a computer network, processors send packets to one another. Likewise, a DMFB can route droplets from one module to another, or between modules and I/O reservoirs.

**Module Rotaries to Routers: Figure 2-6(a)** depicts a module rotary, which is similar to a traffic circle. The four intersections marking its corners are the entry points of the tile. The four streets (which are unidirectional) are similar to the buffers in a network router, shown in Figure 2-6(b).

**Exchange Rotaries to Wires: Figure 2-6(c)** depicts an exchange rotary. The cells extending from the module rotary (the inputs and outputs in **Figure 2-6(a)**) are similar to wires in a 2D-mesh (**Figure 2-6(d**)). The exchange rotary connects four adjacent tiles,

which form an inner cycle, similar to cycles formed among adjacent routers in a 2Dmesh, e.g., Proc(0, 1) in Figure 2-6(d).

**Streets to Buffers:** Streets hold droplets, similar to input buffers of routers (see **Figure 2-6(a-b)**).

Figure 2-6: (a) A module rotary (the cycle formed by four streets surrounding a module and their intersections) is similar to (b) a 2D-mesh network router; (c) an exchange rotary (the clockwise inner loop) and a long counterclockwise cycle (outer loop) of a tiled virtual topology form equivalent connections to a (d) 2D-mesh network.

### 2.2.2.2 - DIFFERENCES FROM 2D-MESH TOPOLOGY

Integrated circuits use wires to propagate signals, which are stored in buffers (flipflops); in general, there is a clear separation between logic, storage, and interconnect. In contrast, DMFBs use cells for droplet transportation and storage. Also, the 2D-mesh router (**Figure 2-6(d**)) employs a crossbar (**Figure 2-6(b**)), which allows up to four signals to pass through concurrently. Exchange rotaries within DMFBs cannot employ crossbars, as droplets passing through the crossbar would inadvertently mix with one another.

## **2.3 - INTERPRETATION**

The ability to perform deadlock-free droplet routing enables abstraction layers that share some principle similarities with the TCP/IP stack used in computer networks. This, in turn, facilitates an *intermediate bytecode format* (motivated by virtual machines, such as the JVM), which simplifies the design of the interpreter. Without loss of generality, suppose that we want to dynamically issue the command: "Mix droplets *x* and *y*." Under the recompilation paradigm described previously, the placement must be updated to make room for the new mixing operation (which, literally, could be anywhere on the chip, especially if other ongoing operations need to be moved), and then routes to deliver the two droplets must be computed algorithmically on-the-fly. In contrast, our interpreter could select *any* available work module, knowing that the *droplet transportation protocol* will deliver the two droplets (unless the device suffers from a physical failure). Similarly, this capability facilitates the interpretation of assays that feature control flow operations, as runtime decisions (i.e., which module executes each assay operation) can be made dynamically with minimal overhead.

## **2.4 - BIOCODER LANGUAGE AND EXTENSIONS**

BioCoder [9] is a C++ library developed at Microsoft Research, India, for specifying biological protocols in an unambiguous fashion. BioCoder's compiler converts the assay specification into an English language description that is similar to a recipe in a cookbook. BioCoder's original purpose was to eliminate ambiguities that often occur when biological protocols are disseminated in peer-reviewed literature. The authors of the paper that introduced BioCoder suggested that it could be used as an input language to program an LoC; however, their initial work did not attempt to do so.

### 2.4.1 - LACK OF UNIVERSALITY IN LOC COMPILATION

BioCoder was designed to specify a wide variety of assays including many that are not compatible with the DMFBs that we target in this chapter. For example, BioCoder supports solid chemical data types and centrifugation; DMFBs cannot manipulate solids, and do not generally have integrated centrifuges; therefore, they cannot perform these operations. Unlike computer hardware and software, biochemistry has no theoretical notion akin to Turing completeness that can bound the capabilities of LoCs [8]. Similarly, there is no "universal" set of components akin to "universal" logic gates (e.g., **NAND**, or **AND-OR-INV**) that can provably implement any combinational logic function.

On the one hand, any language or library for specifying biological protocols must evolve as new components are developed for use: new operators (languages) or functions (libraries) to specify the usage of these components must be added; otherwise, the language or library itself will become stale over time. On the other hand, a compiler targeting a specific LoC technology is likely to support only a subset of the language; for example, any attempt to compile an assay that includes a centrifugation operation targeting a DMFB *must* fail, due to the lack of a centrifuge. This generally does not occur in software compilation. For example, many microcontrollers do not contain hardware multipliers, dividers, or floating-point units, but can still support these operations in software; compilation only fails when the device has insufficient memory. As biochemistry has no notion of a universal operator, compilation fails when the assay specification does not match the physical resources of the target device.

### **2.4.2 - OBJECT-ORIENTED ORGANIZATION**

As mentioned earlier, BioCoder is a C++ library containing a variety of **structs**, global variables, and **static** functions. BioCoder's compiler creates an internal data structure that represents an assay as a DAG. The DAG is traversed to convert the assay into English language output. Assay information is not saved, and the data structure is deallocated during the traversal. We discovered that this library format was incompatible with the instantiation and maintenance of multiple assays at the same time.

One of our goals was to introduce control flow into biochemical specifications in order to support assays where decisions are taken based on feedback from the LoC. This requires a control flow graph (CFG) where each basic block is represented as a BioCoder assay (i.e., a DAG). Naturally, any CFG containing control flow requires multiple assays.

BioCoder was converted to several C++ classes that enabled the construction of protocols comprised of multiple assays that no longer mangled one another when constructed. To specify an assay, the user instantiates an instance of the **BioCoder** class; assay operations are specified as method calls. The compiler converts the program into a

graph-based intermediate representation using a new class that we introduced called **AssayProtocol**, which effectively represents the CFG. **AssayProtocol** enables the protocol to be saved, copied, and executed multiple times (if desired).

| BioCoder Functions Supported by DMFBs |                                                             |  |  |  |

|---------------------------------------|-------------------------------------------------------------|--|--|--|

| Microfluidic Operations               | BioCoder Function                                           |  |  |  |

| Dispense                              | void measure_fluid (Fluid f, Volume v, Container c)         |  |  |  |

| Output                                | void drain (Container c, string outputSinkName)             |  |  |  |

| Mix/Merge                             | void vortex (Container c, Time t)                           |  |  |  |

| Split                                 | void measure_fluid (Container c1, Volume v, Container c2)   |  |  |  |

| Heat                                  | <pre>void store_for (Container c, float temp, Time t)</pre> |  |  |  |

| Detect                                | string measure_fluorescence (Container c, Time t)           |  |  |  |

Table 2-1: Prototypes for six BioCoder functions that are supported by EWoD-based LoCs.

All original BioCoder functionality was left intact, so it remains possible to convert

the assay to an English-language description or graphical representation if desired.

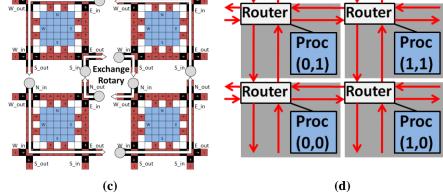

Figure 2-7(a) depicts the new capabilities within the original BioCoder flow.

**(b)**

Figure 2-7: (a) Overview of the BioCoder system and output, highlighting the addition in this work; (b) System overview, showing the BioCoder environment, the runtime environment, and the interface between them.

**Table 2-1** lists six BioCoder functions that are compatible with the capabilities of EWoD-based LoCs. In our new implementation, these functions are methods of the **BioCoder** class. The data types **Fluid**, **Volume**, **Time** and **Container** used in **Table 2-1** are part of the original BioCoder specification. In traditional benchtop chemistry, the meaning of container is literal—e.g., it could be a test tube, beaker, or flask that *contains* fluid; in the case of our LoC, a **Container** is effectively used as a proxy for a droplet, which represents *embodiment*, rather than containment, of fluid.

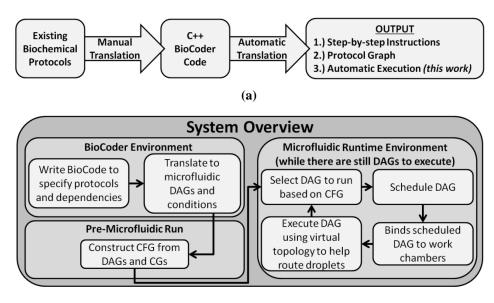

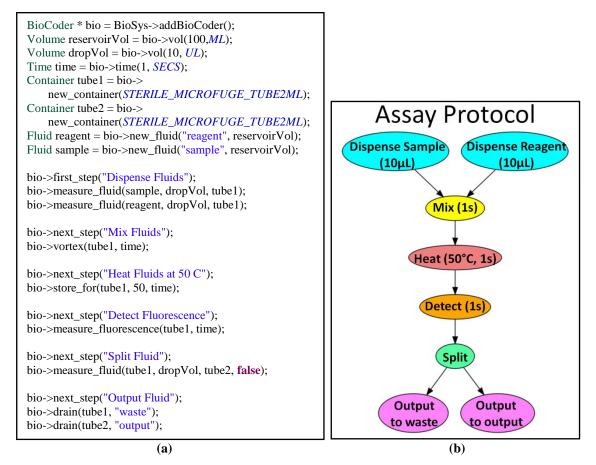

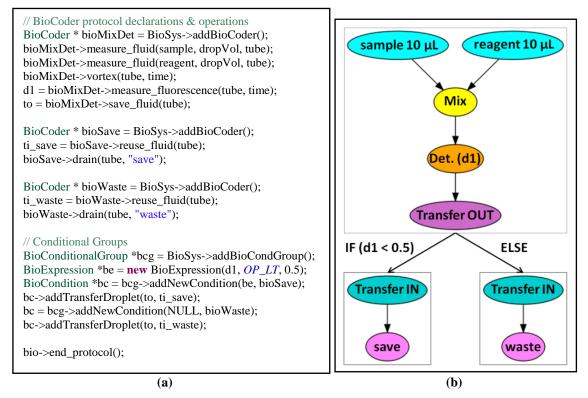

### **2.4.2.1 - EXAMPLE**

**Figure 2-8** illustrates a simple protocol built using BioCoder. **Containers** represent droplets that carry fluids from one step to the next, while instances of the **Fluid** class act as input reservoirs. The protocol dispenses and mixes 10µl of a sample and reagent for 1s, heats the mixture for 1s at 50°C, detects the fluorescence for 1s, splits and outputs the two resultant droplets to the "output" and "waste" reservoirs. Each edge in the assay protocol graph represents a droplet flowing from one operation to the next, i.e., the fluidic analogue of a data dependency.

Figure 2-8: (a) BioCoder code for a sample assay and (b) the representative DAG structure. This assay does not require control flow.

### 2.4.3 - EXTENSIONS FOR FEEDBACK AND CONTROL FLOW

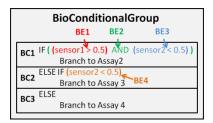

To support feedback and control-flow constructs, several new BioCoder classes have been created: **BioSystem**, **BioConditionalGroup**, **BioCondition**, and **BioExpression**. A **BioSystem** contains a list of **BioCoder** protocols and **BioConditionalGroups** which dictate the order in which the **BioCoder** assays are executed at runtime. As seen in **Figure 2-9**, a **BioConditionalGroup** is an **IF/ELSE-IF/ELSE** statement, where each **IF**, **ELSE-IF** and **ELSE** in the **BioConditionalGroup** is a **BioCondition**. Each **BioCondition** contains a **BioExpression** which can be evaluated to true or false at runtime and is used to determine which assay protocols to execute next.

Figure 2-9: A BioConditionalGroup contains BioConditions (BC1-BC3). A BioCondition is evaluated by its BioExpressions (BE1-BE4).

**Table 2-2** shows the five general types of **BioExpressions**. **BioExpressions** with operation types of AND, OR, and NOT are composed of one or more **BioExpressions**, which may be nested. **BioExpressions** are evaluated recursively at runtime to determine the result (True or False). The one- and two-sensor comparisons support decision-making based on feedback from sensors on the device. The functionality of the comparison depends on the data type returned by the sensors.