# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Variability Modeling and Statistical Parameter Extraction for CMOS Devices

#### **Permalink**

https://escholarship.org/uc/item/19x656kn

#### **Author**

Qian, Kun

#### **Publication Date**

2015

Peer reviewed|Thesis/dissertation

#### Variability Modeling and Statistical Parameter Extraction for CMOS Devices

by

#### Kun Qian

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Costas J. Spanos, Chair Professor Chenming Hu Professor Philip B. Stark

Spring 2015

#### Abstract

Variability Modeling and Statistical Parameter Extraction for CMOS Devices

by

#### Kun Qian

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Costas J. Spanos, Chair

Semiconductor technology has been scaling down at an exponential rate for many decades, yielding dramatic improvements in power, performance and cost, year after year. Today's advanced CMOS transistors have critical dimensions well below 24nm. This means that controlling the manufacturing process is increasingly difficult. Process and material fluctuations cause device and circuit characteristics to deviate from design goals, and introduce significant device-to-device variability due to spatial variations across silicon wafers. Accurate modeling of these spatial process variations has become critical to both foundries and circuit designers that seek optimal power/speed/area balance.

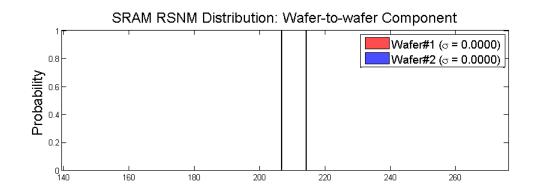

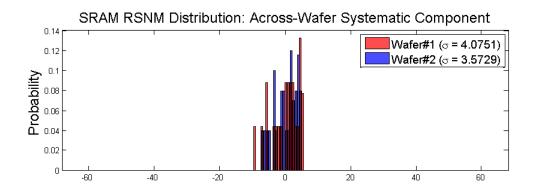

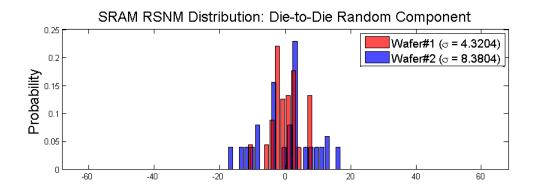

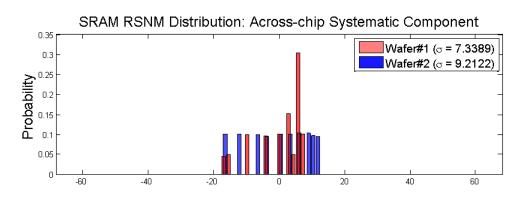

To understand the nature of spatial process variations, we first carried out a comprehensive variability analysis of data measured from thousands of variability-sensitized test structures, including ring oscillators, SRAM bit cells and their internal transistors. We manufactured these test chips using early stage 90nm and 45nm commercial semiconductor processes. We proposed a hierarchical variability model to capture the systematic and random components of device parameter variations across silicon wafers, and across chips. The detailed decomposition of the process variation profile reveals significant across-wafer systematic component for the delay and leakage of ring oscillators, and across-chip systematic component for the read/write margins of SRAM bit cells, as well as their internal transistors. The proper modeling of each hierarchical component proved to be crucial for the accurate estimation of the statistics of device performance distribution and its parametric yield.

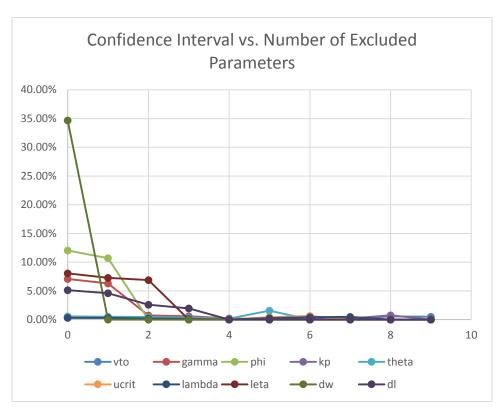

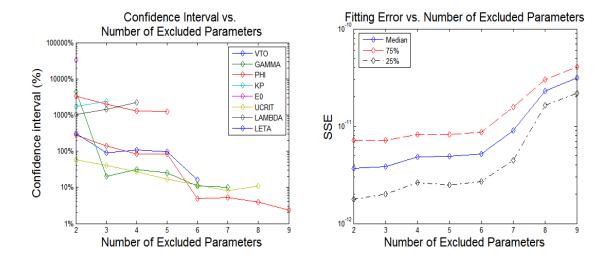

The knowledge gained about process variation from carefully designed test structures was leveraged into estimating the variation and parametric yield of new devices and circuits. This was accomplished by improved the statistical compact model parameter extraction

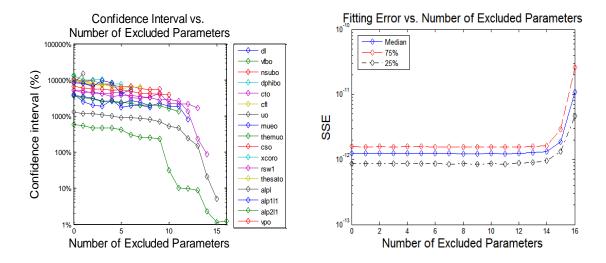

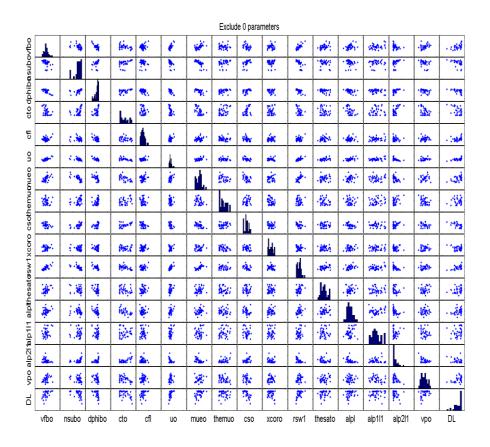

methodology, and by proposing a stepwise parameter selection method. We used a normalized notional confidence interval and, and the sum of squares of fitting residuals as extraction and fitting quality criteria. This allowed us to determine the essential model parameters for accurate fitting over a large number of transistors. We applied this methodology to EKV and PSP with both simulated and experimental data, demonstrating its effectiveness. Finally, we combined the results from statistical parameter extraction with the hierarchical spatial variability model. This, compared to traditional methods, produced much-improved estimates of device performance and manufacturing yield.

To my mom

# **Contents**

| 1     | Intr  | oduc                                         | etion                                                | 1  |  |

|-------|-------|----------------------------------------------|------------------------------------------------------|----|--|

|       | 1.1   | Mot                                          | 1                                                    |    |  |

|       | 1.2   | Var                                          | iability Models                                      | 1  |  |

|       | 1.3   | Res                                          | 4                                                    |    |  |

|       | 1.4   | 1.4 Dissertation Outline                     |                                                      |    |  |

|       | 1.5   | Stat                                         | istical Notes                                        | 6  |  |

| 2     | Hie   | rarch                                        | nical Model for Spatial Variations                   | 8  |  |

|       | 2.1   | Clas                                         | ssification of Process Variations                    | 8  |  |

|       | 2.1   | .1                                           | Environmental, Temporal, and Spatial Variations      | 8  |  |

|       | 2.1   | .2                                           | Systematic and Random Variations                     | 9  |  |

|       | 2.1   | 3                                            | Global and Local Variations                          | 10 |  |

|       | 2.2   | Con                                          | mmon Sources of Process Variations                   | 10 |  |

|       | 2.3   | 3 Variation Modeling with Hierarchical Model |                                                      | 15 |  |

|       | 2.3.1 |                                              | Variability Decomposition                            | 15 |  |

|       | 2.3   | 3.2                                          | Hierarchical Variability Model                       | 19 |  |

|       | 2.4   | Sun                                          | nmary                                                | 20 |  |

| 3     | Tes   | t Chi                                        | p Design, Characterization, and Variability Analysis | 21 |  |

|       | 3.1   | Intr                                         | oduction                                             | 21 |  |

|       | 3.2   | 90nm Ring Oscillator Test Chip               | 21                                                   |    |  |

|       | 3.2   | 2.1                                          | Chip Design Overview                                 | 21 |  |

| 3.2.2 |       | 2.2                                          | Sampling and Measurement Scheme                      | 22 |  |

|       | 3.2   | 2.3                                          | Variability Observation                              | 23 |  |

|       | 3.3   | The                                          | 45nm Ring Oscillator and SRAM Test Chips             | 34 |  |

|       | 3.3   | 3.1                                          | Chip Overview                                        | 34 |  |

|       | 3.3   | 3.2                                          | Ring Oscillator Variability Observation              | 40 |  |

|       | 3.3   | 3.3                                          | SRAM Variability Observation                         | 48 |  |

|   | 3.4 Summary |        |                                                           |     |

|---|-------------|--------|-----------------------------------------------------------|-----|

| 4 | Stat        | istica | al Compact Model Parameter Extraction                     | 61  |

|   | 4.1         | Intr   | oduction                                                  | 61  |

|   | 4.2 Stat    |        | istical Compact Model Parameter Extraction                | 61  |

|   | 4.2         | .1     | Compact Model Parameter Extraction                        | 61  |

|   | 4.2         | .2     | Basics of Optimization                                    | 63  |

|   | 4.2         | .3     | Backward Stepwise Parameter Selection                     | 66  |

|   | 4.2         | .4     | Sequential Extraction                                     | 71  |

|   | 4.3         | Sim    | ulated Experiment with the EKV Model                      | 73  |

|   | 4.3         | .1     | EKV Model Introduction                                    | 73  |

|   | 4.3         | .2     | Experiment Setup                                          | 74  |

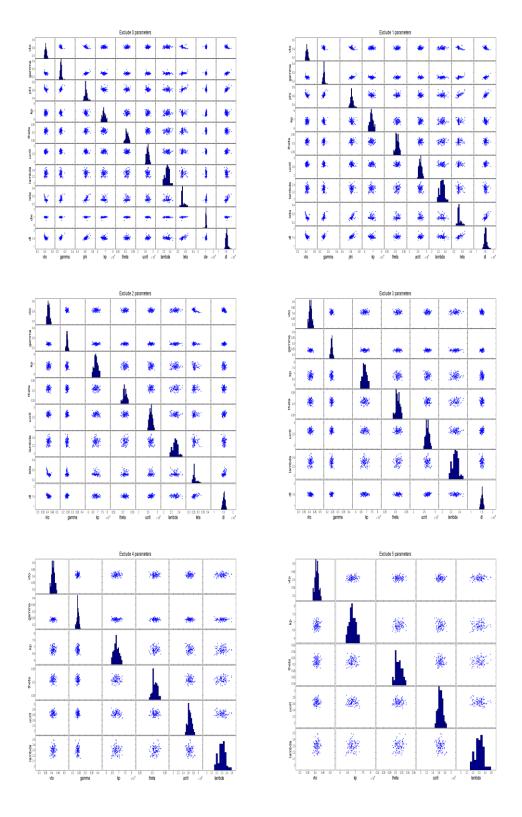

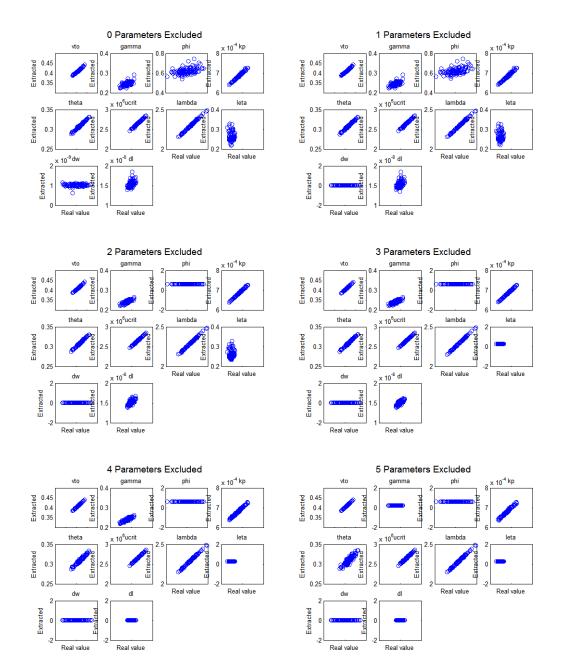

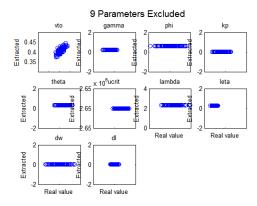

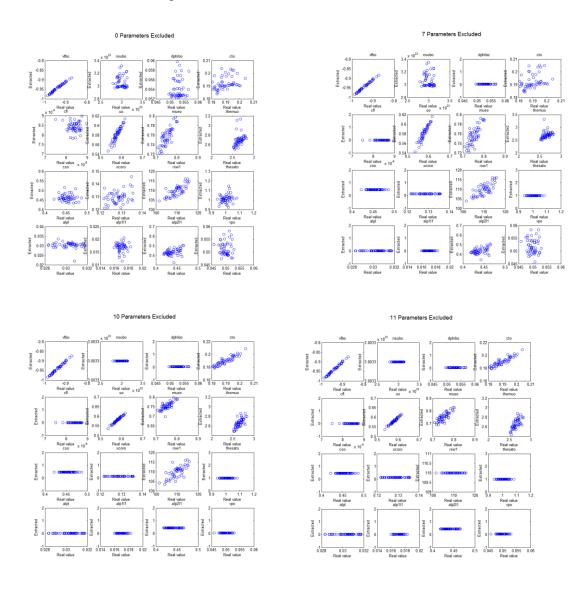

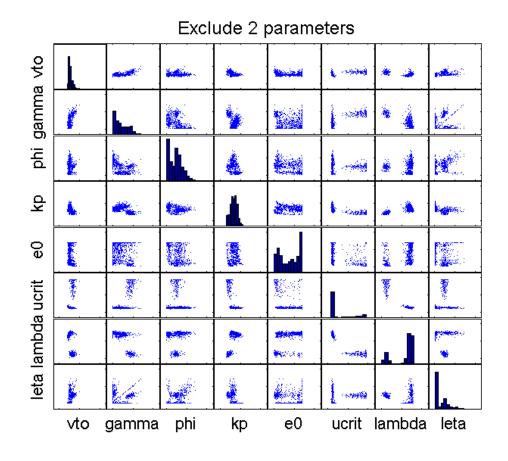

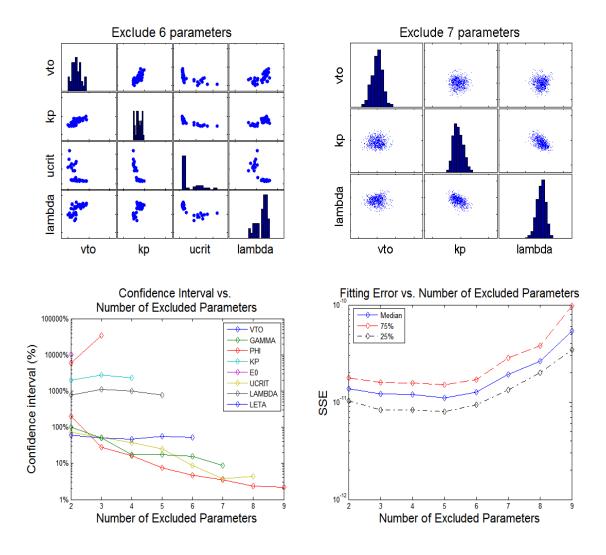

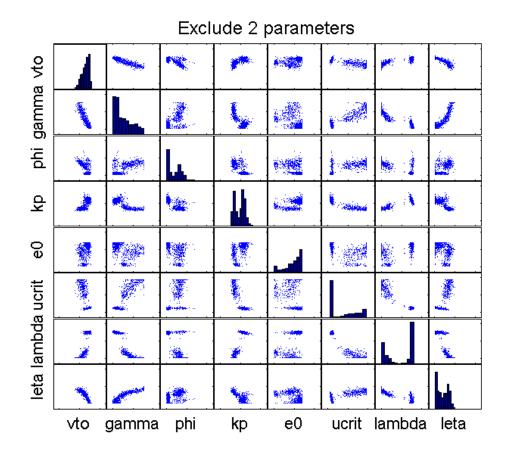

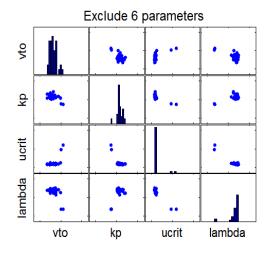

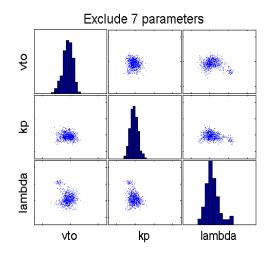

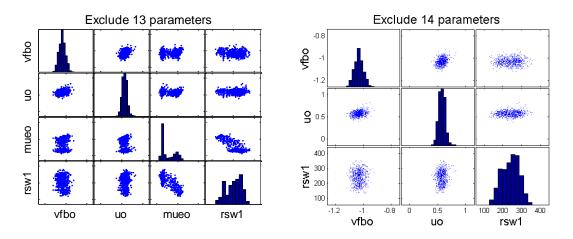

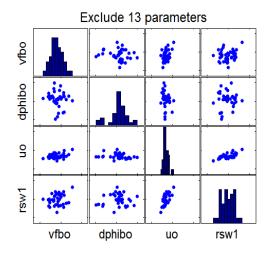

|   | 4.3         | .3     | Stepwise Parameter Selection                              | 77  |

|   | 4.4         | Sim    | ulated Experiment with PSP model                          | 83  |

|   | 4.4         | .1     | PSP Model Introduction                                    | 83  |

|   | 4.4         | .2     | Experiment Setup                                          | 84  |

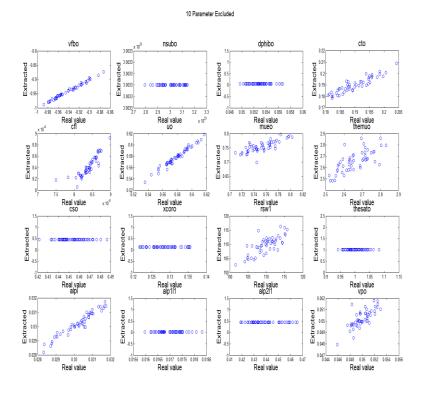

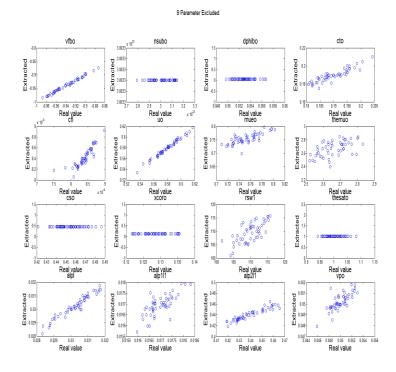

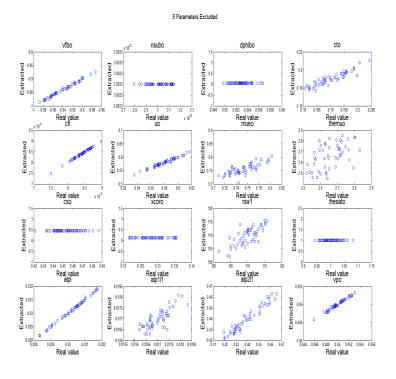

|   | 4.4         | .3     | Stepwise Parameter Selection in Sequential Extraction     | 86  |

|   | 4.5         | Sun    | nmary                                                     | 92  |

| 5 | Stat        | istica | al Extraction and Modeling with Experimental Silicon Data | 93  |

|   | 5.1         | Intr   | oduction                                                  | 93  |

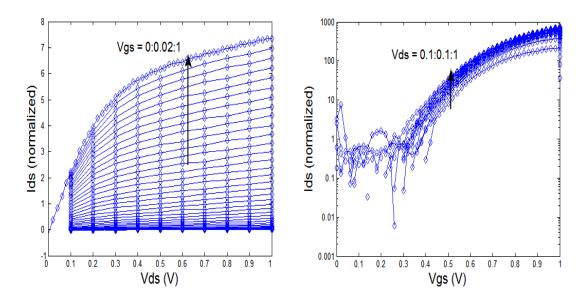

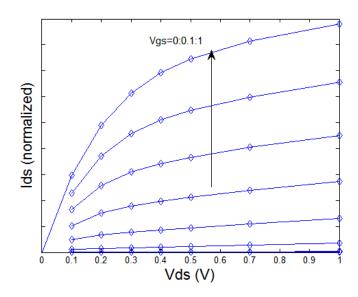

|   | 5.2         | Mea    | asurement for Parameter Extraction                        | 93  |

|   | 5.3         | Para   | ameter Extraction with EKV Model                          | 95  |

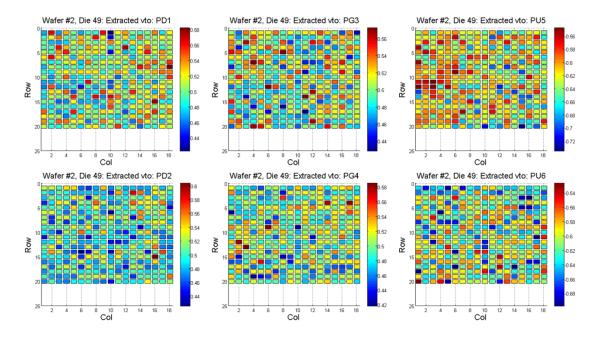

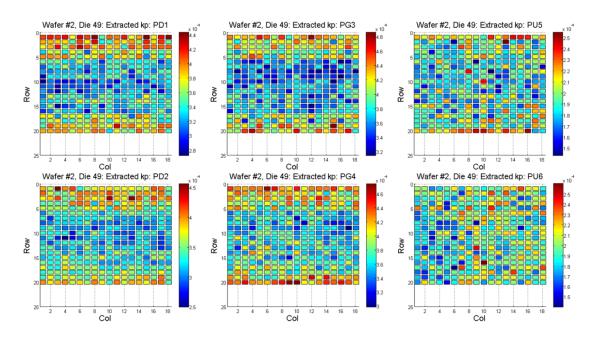

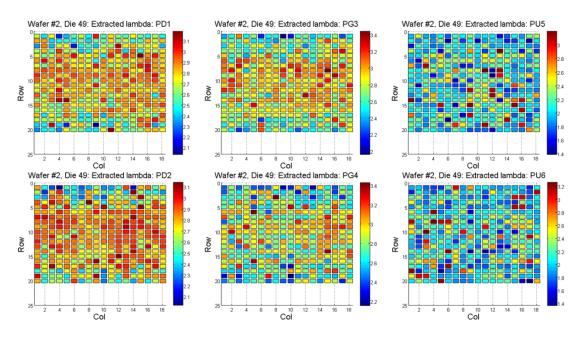

|   | 5.3         | .1     | Parameter Extraction                                      | 95  |

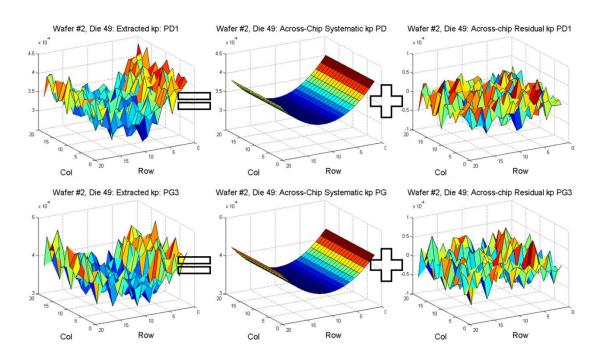

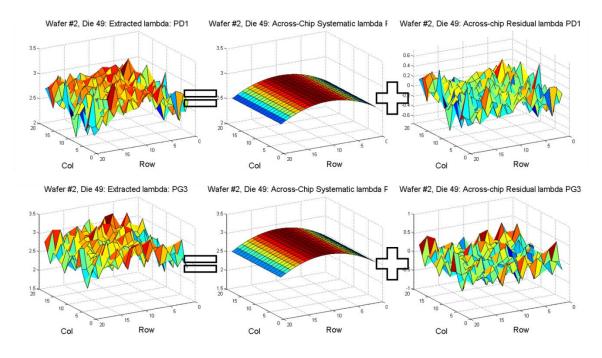

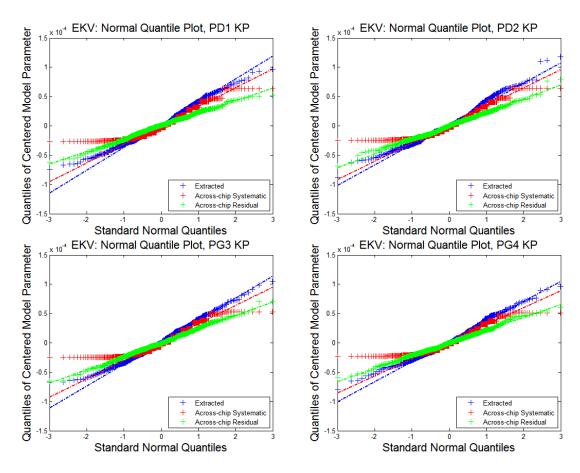

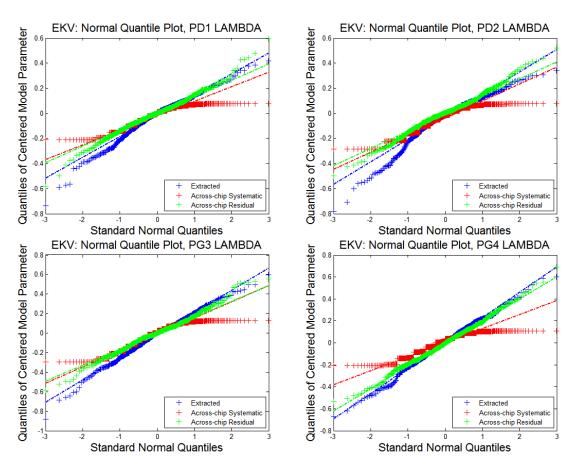

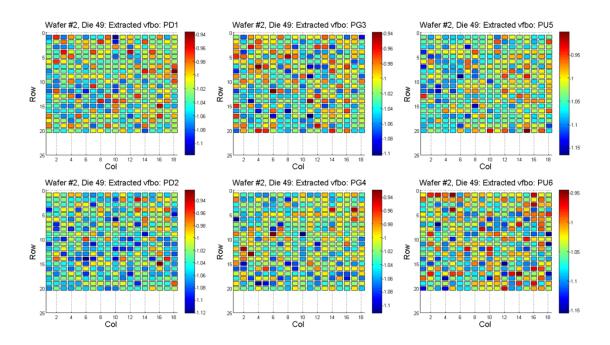

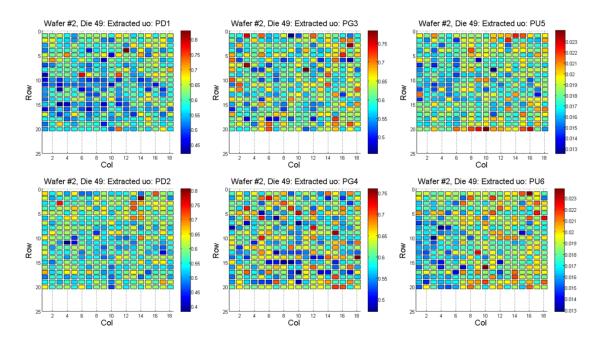

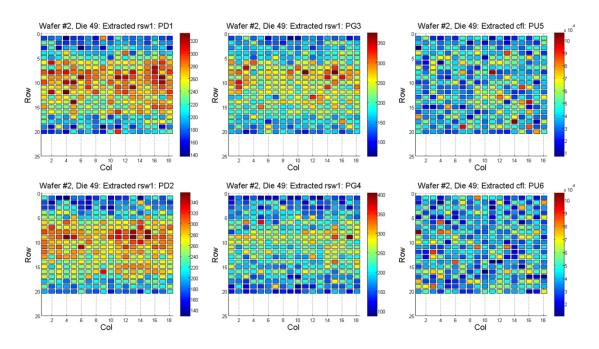

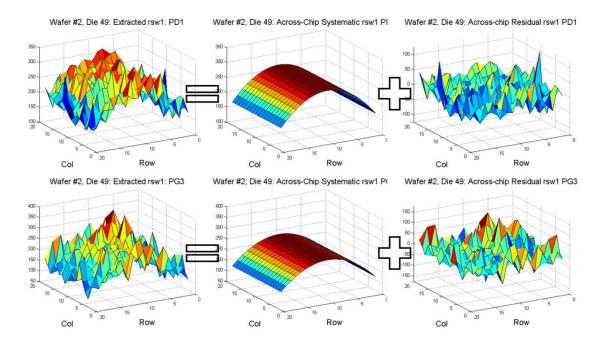

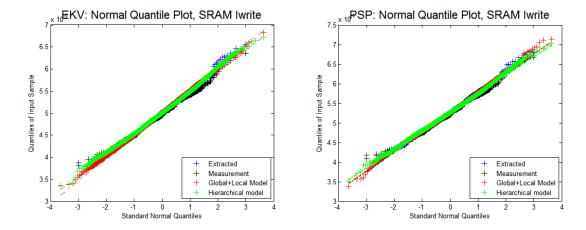

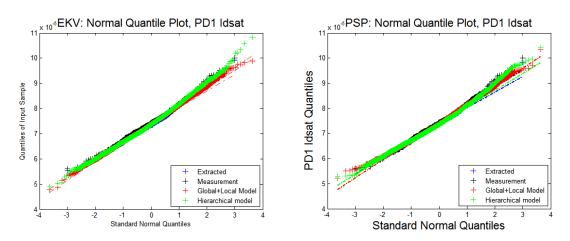

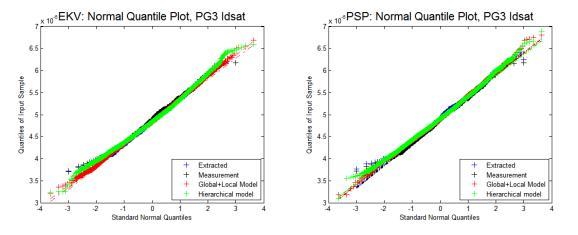

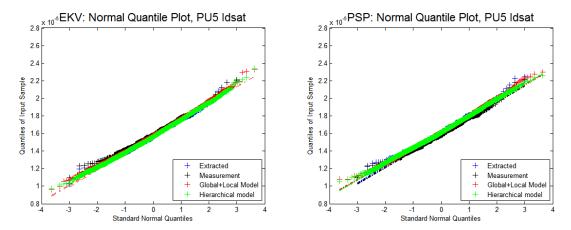

|   | 5.3.2       |        | Parameter Variability Modeling                            | 102 |

|   | 5.3         | .3     | Parameter Variability Reconstruction                      | 109 |

|   | 5.4         | Para   | ameter Extraction with PSP Model                          | 113 |

|   | 5.4         | .1     | Parameter Extraction                                      | 113 |

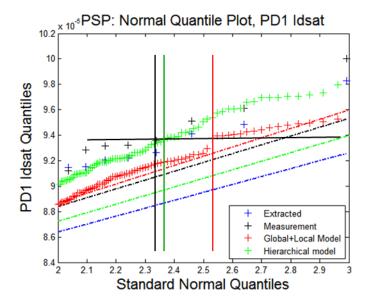

|   | 5.4         | .2     | Parameter Variability Modeling                            | 121 |

|   | 5.4         | .3     | Parameter Variability Reconstruction                      | 126 |

|   | 5.5         | Hie    | rarchical Model Application for Extracted Parameters      | 128 |

|   | 5.6         | Sun    | nmary                                                     | 133 |

| 6            | Conclusion |                   |     |

|--------------|------------|-------------------|-----|

| 6.           | .1         | Key Contributions | 135 |

| 6.           | .2         | Future Work       | 136 |

| Bibliography |            |                   | 138 |

#### Acknowledgments

I would like to first express my sincere gratitude to my research advisor, Prof. Costas J. Spanos. This work would not be possible without his profound knowledge of semiconductor process, sharp technical insight, and years after years of patient guidance. I can't thank Costas enough for always being supportive, both academically and personally, making graduate school such a memorable adventure for me.

I would also like to thank Prof. Borivoje Nikolić, for his mentoring throughout the collaborated variability characterization project. Under his advisory, I was fortunate to get the opportunity to collect and analyze real silicon variability data from advanced commercial processes, which became the foundation of this dissertation. And I need to extend special thanks to my fellow graduate students from Prof. Nikolić's group: Liangteck Pang, Zheng Guo, and Seng Oon Toh, not only for creating and sharing their designs of variability testing circuits, but also teaching me various skills including electrical characterization, circuit simulation and layout design. They are wonderful people to work with and to learn from, and I wishes them best with their careers.

I'm also very grateful to Prof. Chenming Hu, Prof. John Wawrzynek, and Prof. Philip B. Stark for serving on my qualifying exam and dissertation committee. Their sharp questions and critiques make me think deeper and think in perspective. In particular, Prof. Stark provided an enormous amount of help in refining my usage of statistical tools in interpreting semiconductor devices variations.

I'll miss all the students and staff of my research group BCAM: DK, Qianying Tang, Yu Ben, Ning Ma, Jing Xue, Ying Qiao, Zhaoyi Zhang, Claire Baek, and Changrui Ying – you folks make the office a lively, cozy space to work and to laugh. I want to thank my colleagues at GLOBALFOUNDRIES, I learned so much from you which inspired several ideas in my dissertation. And yes, I need to thank all the friends I made in Berkeley. You are the ones that did the magic that turned Berkeley into a place I would forever call home.

Lastly, I owe my deepest gratitude to my family and my girlfriend Carrie for all the timeless love and support.

# Chapter 1

# Introduction

#### 1.1 Motivation: Process Variations

For almost five decades, the semiconductor industry has, phenomenally, kept pace with Moore's Law [1]: Every 18 months, transistor density has doubled, as a result of reducing key device dimensions such as channel length and oxide thickness. However, decreasing dimensions further is increasingly difficult as CMOS technology scaling continues into sub-100nm feature size. Among the many emerging challenges, the increased importance and complexity of process variations is one of the most prominent.

Many variations during manufacturing process impact physical properties of devices and circuits. Lithographic variations [2], line-edge roughness [3][4], random dopant fluctuations [5], layout-dependent stress variations, rapid thermal annealing (RTA) temperature induced variations [6][7], well-proximity effects (WPE) [8], deposition and growth processes, and chemical mechanical polishing (CMP), all cause variations in device parameters such as dimensions, oxide thickness, doping concentrations, diffusion depth, and mobility.

The non-uniformity of transistor characteristics produces timing variations of circuit critical paths [9], smaller read/write noise margins for SRAM memory cells [10], and higher off-state leakage currents, which culminate in yield losses. In general, circuits need to be designed conservatively to cope with performance losses introduced by process variations, which requires devices to have larger area and higher power consumption.

It is critical to understand and quantify process-induced variability to avoid unnecessarily pessimistic designs. Improving the characterization and modeling of variability can help designers optimize performance, power, area, and yield.

# 1.2 Variability Models

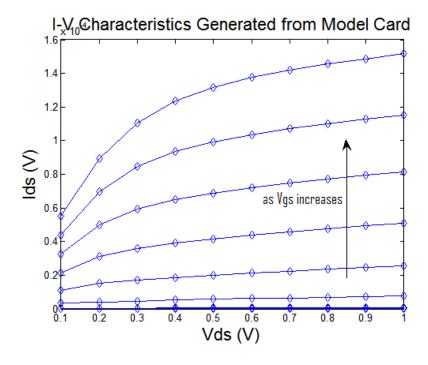

Currently, foundries track on-wafer monitoring structures, including all sorts of active and passive devices, to estimate the performance distribution of devices and circuits. *I-V* data collected from test structures are later used to calibrate compact device models, such as BSIM [11] or PSP [12], and statistical models of device characteristics, which are used in circuit simulations.

Two types of statistical device models are conventionally used by modelers and designers to account for device parameter variations resulting from manufacturing process fluctuations: corner models and Monte Carlo models.

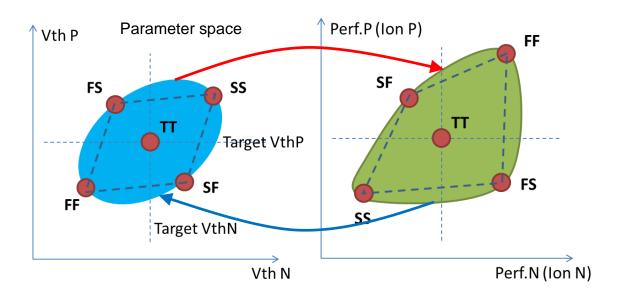

Corner models, often referred to as "worst-case design," seek to characterize worst-case and best-case device parameters. There are typically five worst-case corners, each identified by a two-letter acronym that indicates the relative performance of the n-channel and p-channel devices. Each letter summarizes the device performance of one channel type as typical (T), fast (F), or slow (S). The first letter indicates the performance of the n-channel device and the second letter indicates the p-channel device. Combinations of the performance levels for the n-channel and p-channel devices form the following list of corner cases:

- TT (typical *n*-channel, typical *p*-channel): the nominal or typical device performance the manufacturing process targets.

- FF (fast *n*-channel, fast *p*-channel): model parameters that reflect a process shift that yields fast operation for both the *n* and *p*-channel devices.

- SS (slow *n*-channel, slow *p*-channel): model parameters that yield slow operation for both the *n* and *p*-channel devices.

- FS (fast *n*-channel, slow *p*-channel): the *n*-channel device is fast, and the *p*-channel device is slow, which could represent the asymmetry of the rising and falling edge of signals in a critical path.

- SF (slow *n*-channel, fast *p*-channel): the *n*-channel device is slow and the *p*-channel device is fast.

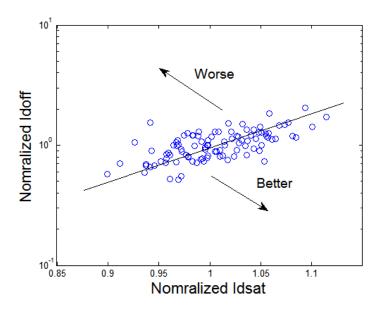

Monte Carlo device models, on the other hand, attempt to represent the unpredictable characteristics of devices, rather than extreme behavior. Monte Carlo methods model device parameters as stochastic, typically assuming that each parameter is a realization of a Normal or uniform distribution. Monte Carlo inputs to SPICE simulations generally also assume that device model parameters are independent across instances of each transistor. Device and circuit performance distributions are derived from the assumed stochastic distributions of model parameters using Monte Carlo simulation. Often, Monte Carlo simulations are used to calibrate worst-case corner models for device performance parameters, such as *Ion* and *Ioff*.

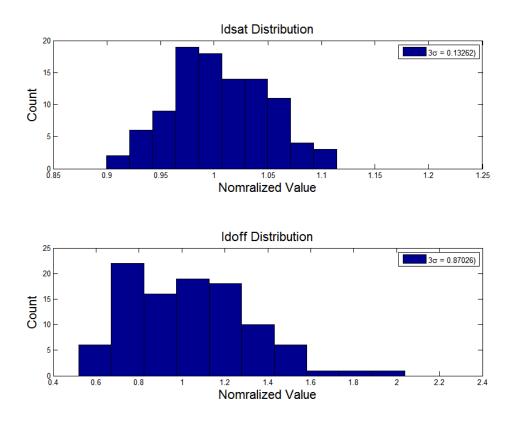

Figure 1.1 depicts the typical relationship between CMOS transistor device parameter space, performance space, and the corresponding worst-case corners. Parameters include device characteristics such as the threshold voltage parameter Vt for NMOS and PMOS. Performance space refers to the distribution of device performance metrics, such as Ion of NMOS and PMOS. For any assumed distribution of device parameters, Monte Carlo device models can be created to simulate the performance of any circuit of interest; on the other

hand, device parameters are usually extracted from the device performance space, using techniques such as corner lots, statistical process control (SPC) [13], or process and device simulations. Worst-case corner models are commonly defined as the most "probable" combination of device parameters (in the parameter space) that would produce  $3\sigma$  departures of combination of the performance parameters of the *n*-channel and *p*-channel devices (in the performance space) from their nominal values. For example, the FF corner is the combination of NMOS and PMOS when both *Ion,n* and *Ion,p* are at their high  $3\sigma$  point, and the SS corner is when both are at their lower  $3\sigma$  point. At the FS corner, the difference between *Ion,n* and *Ion,p* reaches its higher  $3\sigma$  point, while at the SF corner it reaches its lower  $3\sigma$  point. Modelers can then search the parameter space for the most probable (under the assumed model) combination of *Vth,n* and *Vth,p* that attains the worst-case corner values. In more complicated cases, the performance parameter can be a critical characteristic of a specific circuit, such as the delay of a ring oscillator, which is useful to characterize the worst-case operation of large-scale circuits.

Figure 1.1: Typical CMOS transistor device parameter space and performance space with corresponding worst-case corners.

#### 1.3 Research Goal

The goal of this research is to develop a method that can accurately model the stochastic transistor behavior induced by process variations, so that circuit designers can accurately estimate the parametric yield for a given design.

This goal can be achieved through the following steps:

#### Characterize and analyze the composition and structure of process-induced variation in CMOS devices and circuits.

A key factor in calibrating statistical device models is to have an accurate representation of both the systematic (deterministic) and random (stochastic) variations. In the context of chip fabrication, the concept of systematic and random variations is inevitably entangled with the spatial hierarchy. Traditionally, lot-tolot, wafer-to-wafer, and chip-to-chip variations are treated as a single pseudorandom component "global variation" from the perspective of individual chips. Global variation is supposed to be similar for all transistors on the same chip. Within-chip variations, on the other hand, are further decomposed into across-chip systematic and local random variations. These variations are modeled by independent Gaussian distributions. A number of previous studies have analyzed process-induced variability and its impact on circuit power performance. Asenov's team built an atomic-level simulation framework for predicting and modeling the intrinsic random variations of transistor parameter variations [14]–[19]. Boning and his students designed ring oscillator arrays for fast delay characterization and a within-chip spatial variability study [20], [21]. Wafer-level and die-level spatial variability of for inter layer dielectric (ILD) thickness variations were studied and modeled with ANOVA [22], [23].

In this thesis, electrical measurements are collected using arrays of standard-variability monitoring structures, such as transistors, ring oscillators, and SRAM bit cells. Several tens of chips are measured for each of the three test wafers fabricated in early commercial 90nm and 45nm low-power CMOS processes, providing full wafer-scale spatial coverage. A hierarchical model of variability is used to analyze the measured device characteristics, decomposing the total variability into random and systematic components at the wafer level and die level.

**❖** Develop a methodology that accurately and robustly translates the variability characteristics from the electrical measurements to the industry standard statistical device models.

Circuit designers rely on statistical compact-device models to estimate performance variations of devices and circuits. The two most commonly used statistical models are the worst-case corner models and Monte Carlo models. Corner models use a finite set of compact model parameters to represent the typical and worst-case conditions of transistors, while the Monte Carlo model involves inventing a joint probability distribution for compact model parameters, then simulating realizations of those distributions. The key task of variability modeling in both cases is to accurately translate the measured *I-V* characteristics into the distribution of compact model parameters.

Traditionally, a few key compact model parameters with clear physical meanings are used to capture the variability in the *I-V* characteristics [24]–[26]. The extracted populations of these parameters are correlated, due to their physical relationship and due to the numerical procedure for estimating them. For this reason, some studies use principal component analysis (PCA) to extract statistically independent components of device variability, which are later used to simulate the compact model parameter variations [27], [28].

This dissertation shows that existing methodologies can be improved in two ways. First, the selection of the model parameters for direct extraction can be tailored more precisely to the silicon data. Only parameters found to be statistically significant will be retained in the fitted stochastic model of device variation; the remaining parameters will be fixed to their nominal values from the typical corner extraction. This is expected to reduce covariance among parameter estimates without relying on combinations of parameters (such as those PCA produces) that are incompatible with SPICE simulations. Second, we show that a full hierarchical model of spatial variability for the extracted compact model parameters allow a more faithful reproduction of device performance variations in Monte Carlo simulations.

# ❖ Study the impact of spatial-process variations on the performance and parametric yield of real silicon devices using the improved statistical transistor modeling methodology.

We use an improved statistical parameter-extraction procedure to identify parameters that can be extracted reliably, and analyze their spatial variability in detail. A statistical device model is extracted from the transistor *I-V* measurements of the SRAM bit cells from the 45nm test chips using this improved methodology. It illustrates good accuracy in predicting the read/write margins collected from the same set of SRAM cells. The accuracy of the spatially hierarchical statistical

transistor model is compared to the conventional method; and its advantage in yield estimation accuracy is evaluated.

#### 1.4 Dissertation Outline

Chapter 2 reviews the sources of variability in the modern semiconductor fabrication process. Based on the stochastic or deterministic nature of the variations and their respective spatial scope of effect, a hierarchical model is proposed to describe the combined effect of the process variations.

Chapter 3 presents the measurement results from two sets of variability characterization test chips, the first from a commercial, general purpose 90nm CMOS process and the other from a commercial 45nm strained-Si CMOS process. Ring oscillator (RO) frequency and leakage data from both sets of test chips are evaluated. The hierarchical model of variability is proved to be very effective in fitting to the RO data. The same hierarchical variability analysis is applied to the read/write margin and the transistors *I-V* measurements collected from the SRAM bit cells from the 45nm test chips.

Chapter 4 details our improved method for modeling the spatial variability of transistors with compact models. A parameter extraction procedure is developed and tested with simulated data for two popular compact models: EKV [29] and PSP [12].

Chapter 5 applies the statistical compact-model extraction methodology to the actual silicon data collected from the SRAM bit cells from the 45nm test chip. For each of the EKV and PSP models, a set of model cards is extracted, to which the hierarchical model of variability is then applied to create a custom statistical compact model. These statistical compact models illustrate better accuracy in predicting device performance variations than conventional method.

Chapter 6 summarizes the highlights of this dissertation and discusses future research directions.

#### 1.5 Statistical Notes

This dissertation uses a variety of statistical methods and concepts, including linear and nonlinear regression, hierarchical models, expectations, variances, hypothesis tests including t-tests, significance levels, p-values, and confidence intervals. However, the generative stochastic model for the data that would be required for those methods to apply

as statistical methods does not hold; moreover, if such a model did hold, in general, there would be more efficient methods than those employed here. Rather, all uses of statistical concepts and methods in this dissertation are to be considered *algorithmic*, rather than statistical. The justification for using the methods is not any underlying statistical theory, but instead the empirical performance of the resulting model for the task at hand: understanding process variability and predicting device performance and yield.

# Chapter 2

# Hierarchical Model for Spatial Variations

#### 2.1 Classification of Process Variations

#### 2.1.1 Environmental, Temporal, and Spatial Variations

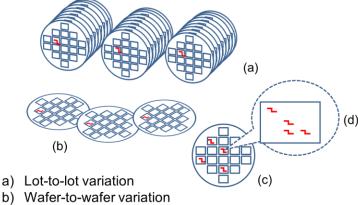

Process variability can be environmental, temporal, or spatial [30]. Environmental variations consist of variability in the surrounding temperature, power supply voltage, and even cosmic radiation. Temporal variations, as the name suggests, refer to device-performance change over periods of time ranging from nanoseconds, for the SOI history effects [14] and self-heating effect, to seconds or hours, for the negative bias temperature instability (NBTI) [31], to years, for dielectric material deterioration after repeated programming and erasing operations in flash memories. Spatial variations, are performance differences among devices that depend on the distances between the devices or the locations of the devices on a chip. Typical spatial variations, such as line width or film thickness non-uniformity, universally exist across lots, across wafers, across chips and dies, and between circuit blocks and devices (Figure 2.1). As a result, the circuit performance of chips from wafers produced with the same design and process over a period of manufacturing time will never be the same.

Of the three types, environmental and temporal variability are often accounted for using reliability models, while spatial variability is commonly part of statistical device models. This dissertation studies the spatial variations.

- b) Wafer-to-wafer variation

- c) Chip-to-chip or across-wafer variation

- d) Within-chip variation

Figure 2.1: Illustration of the spatial process-variation hierarchy: (a) lot-to-lot, (b) wafer-to-wafer (c) chipto-chip, and (d) within-die variations

#### 2.1.2 Systematic and Random Variations

Systematic variations, also called deterministic variations, are repeatable deviations from nominal device characteristics depending on the device's spatial position on the die and on the wafer and/or the layout context surrounding the device being tested. Common sources of systematic variability include the non-ideality of the lithographic system, such as defocus, misalignment, and line-width roughness [32]; chamber effects that contribute to across-wafer patterns [33]; and various layout-dependent effects, such as WPE [34], optical proximity effects [2], strained silicon effects [35], and CMP [22].

Random variations, or stochastic variations, are unpredictable components of device variability, such as non-uniformities resulting from random fluctuations in the fabrication process, microscopic fluctuations of the number and location of dopant atoms in the transistor channel [17], [36], LER due to photoresist granularity [4], and atomic-scale oxide-thickness variation [16].

Systematic and random variations differ in how they impact device and circuit performance. Systematic spatial variation can cause large differences in performance among devices that are far apart on the die. From a modeling point of view, such an effect in the chips may directly contribute to the spatial correlation among transistors [37]. Random variations, however, are usually treated as independent fluctuations at their corresponding spatial hierarchy level (lot level, wafer level, chip level, etc.).

The classification of systematic and random variations is not absolute. In practice, the running status of equipment or the exact location of the device and circuit on the wafer and chip are often unavailable to circuit designers, rendering it impossible to predict the exact amount of systematic variation. In such cases, systematic variations are often treated as random. Such an approximation is an important source of error in estimating the actual devices' variability and yield.

#### 2.1.3 Global and Local Variations

Another commonly used classification divides device variability into global variation and local variations [38], [39]. As illustrated in Figure 2.1, there are multiple hierarchies above the actual chips in the manufacturing process. From the point of view of an individual chip, variability from the higher hierarchies, such as lot-to-lot, wafer-to-wafer, and chip-to-chip, will be almost equally applied to every transistor on the chip. These variations, whether systematic or random, are lumped together and called "global variations". Correspondingly, the remaining within-chip variations are referred to as "local variations." In SPICE Monte Carlo simulations, the same global-variation component is generated for all devices of the same model, while each device will have its own unique local-variation component. The accurate modeling of the global and local variations plays an important role in estimating the power and performance scaling with circuit complexity, as the local variations will get averaged out among large number of transistors or long critical paths, while the global variations will add up and shift the average power/performance of the entire chip.

#### 2.2 Common Sources of Process Variations

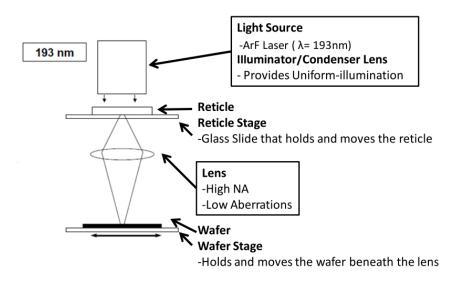

#### **\Delta** Lithographic variations

The uniformity of the printed feature sizes depends heavily on the control of the lithographic imaging system. It affects the two key requirements in integrated circuit manufacturing: the critical dimension (CD) and the overlay control. In a typical step-and-scan lithography stepper (Figure 2.6), the mask reticle and the wafer are simultaneously moving in opposite directions while a slit of light scans the whole mask and projects the image onto the wafer [40]. Even tiny vibrations in the scanner system and variations of the movement speed of the wafer and reticle stage may lead to significant non-uniformities in the depth of focus (DOF) and the light-exposure dose. This can lead to non-uniformity of the critical dimension (CD) of printed lines and may vastly change the speed and leakage of CMOS transistors. Meanwhile, errors in aligning the reticle to the features on the wafer will create variations in misalignment

[41], which can be a crucial problem in achieving the intended line width and good electrical contact between the existing patterns and the new layers of the circuit.

Figure 2.2: A typical lithography imaging system [41]

Another key source of variation in the lithographic patterning process is the post-exposure bake (PEB). The PEB step involves rapidly heating up and cooling down the entire wafer to activate additional chemical reactions and the diffusion of the chemicals within the photoresist. All these phenomena are very sensitive to the PEB temperature trajectory; thus, the uneven temperature in the plate may cause significant CD variations afterward.

Figure 2.3: Plate temperature non-uniformity near the end of the PEB step [42]

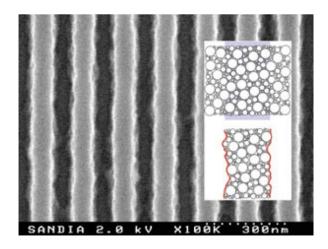

#### **❖** Line-edge roughness

As the gate critical dimension shrink continues into the sub-100nm scale, the tolerance of gate line-width control becomes comparable to the size of a resist polymer unit [4], [43]. The granularity of the photoresist creates a non-uniform channel length along the poly gate. This leads to an increased overall leakage current as the off-state current increases exponentially with the reduction in effective channel length. This phenomenon is called line-edge roughness (LER). It contributes to additional threshold voltage variations and degrades the short channel characteristics of transistors. LER is generally considered an intrinsic, random variation.

Figure 2.4: Typical LER in a photoresist (Sandia Labs) [44]

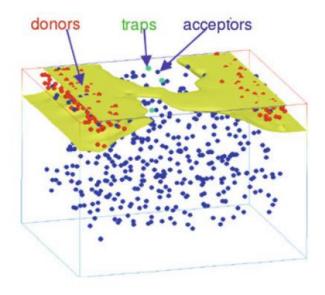

#### **Random dopant fluctuation**

Random dopant fluctuation (RDF) refers to the random microscopic fluctuation of the number and location of dopant atoms in the MOSFET channel region. It causes fluctuations of the transistor electric parameters, such as the threshold voltage (Vt), short channel effect, and drain-induced barrier lowering (DIBL). With the gate CD scaling down to sub-100nm, the total number of dopant atoms under the gate is reduced to thousands or even hundreds (Figure 2.5), leading to significant variations in the threshold voltage and drive current [45]. RDF is the single most important source of random variations in the modern CMOS process.

Figure 2.5: Electron distribution in a 30nm "atomistic" MOSFET at threshold [44]

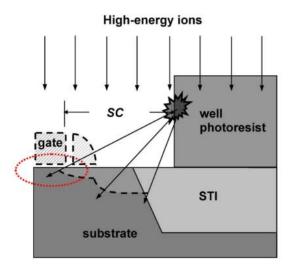

#### **❖** Well-proximity effect

The well-proximity effect is an important layout-dependent effect in the deep submicron manufacturing process. It originates from the lateral scattering of implantation ions during the well-implantation step. The incoming high-energy ions collide with the edge of the photoresist on top of the shallow trench isolation (STI), and they get reflected into the channel area before the poly-silicon gate is actually formed. The closer the transistor gate is to the edge of the well, the higher the dopant concentration inside the channel. As a result, transistors with a smaller gate-to-STI distance will have higher threshold voltages.

Figure 2.6: Origin of well-proximity effect. High-energy dopant ions scatter at the well photoresist edge during well ion implantation and are reflected into the channel before the gate is formed [34]

#### **Strained-silicon effects**

The strained-silicon effect is another important source of layout-dependent variation. Currently, advanced CMOS processes intentionally introduce mechanical stress over the channel to enhance the carrier mobility of transistors [46]–[48]. Experiments have shown an electron mobility increase of more than 20% for NMOS with a tensile silicon nitride capping layer and a hole mobility enhancement of more than 50% for PMOS [46] using selective epitaxial Si<sub>1-x</sub>Ge<sub>x</sub> in source and drain. STI stress can also be modulated with gap-fill material to increase the transistor performance by up to 12% with proper layout design and wafer/channel orientation [48]. Studies have shown that the stress profile in the channel can be very sensitive to the length of diffusion (LOD) [49]. Consequently, transistors with the same gate size but a different LOD may have very different speeds.

# Tensile Capping Layer NiSi Gate Si<sub>1-x</sub>Ge<sub>x</sub> Channel Stressor

Figure 2.7: An example of the uniaxial strained-silicon process [46]

#### **\*** Other variability sources

Other sources of spatial process variation include the pattern density dependency of the CMP process [22], oxide thickness non-uniformity [17], non-uniformity in reactive ion etching (RIE), traps and defects in material, etc. These variations will have their own unique impact on transistor characteristics and require extra margin in the design.

# 2.3 Variation Modeling with Hierarchical Model

#### 2.3.1 Variability Decomposition

From the modeling perspective, process variations can be decomposed in several different ways. Circuit designers commonly treat process variation as a combination of global variation and local variation. This method lumps all the chip-to-chip and wafer-to-wafer variations into one global variation component, and the remaining variations as one local variation component. These are also referred to as "inter-chip" and "intra-chip" variations. With the assumption that variations at different hierarchy levels have very little cross-interaction, the variation in a given device parameter *P* can be simply decomposed as:

$$\Delta P = \Delta P_{Global} + \Delta P_{Local}$$

$$= \Delta P_{inter-chip} + \Delta P_{intra-chip}$$

(2.1)

Here the inter-chip variation component is the lumped sum of the lot-to-lot, wafer-to-wafer, and chip-to-chip components:

$$\Delta P_{inter-chip} = \Delta P_{lot-to-lot} + \Delta P_{wafer-to-wafer} + \Delta P_{chip-to-chip}$$

(2.2)

Conventionally, the global and local variations are modeled as two independent, normally distributed random variables.

$$\Delta P_{inter-chip} \sim N(\mu_{inter-chip}, \sigma_{inter-chip}^2)$$

(2.3)

$$\Delta P_{intra-chip} \sim N(\mu_{intra-chip}, \sigma_{intra-chip}^2)$$

(2.4)

With the increasingly significant systematic variability, such as layout-dependent effects in the process, some variability models added an additional across-chip systematic component of parameter *P* to the equation, which is modeled as a normally distributed random variable independent of the other components:

$$\Delta P = \Delta P_{inter-chip} + \Delta P_{intra-chip \, random} + \Delta P_{across-chip \, systematic}$$

(2.5)

$$\Delta P_{across-chip\ systematic} \sim N(\mu_{across-chip\ systematic}, \sigma_{across-chip\ systematic}^2)$$

(2.6)

A prior variability study, however, shows that the systematic variations, particularly at the wafer and chip level, will cause the device parameter distribution to deviate from normal distributions at extreme quantiles [50]. To improve the accuracy of the variability model, the systematic and random components should be individually characterized for each level of the fabrication hierarchy, mainly at the wafer level (chip-to-chip) and chip level (device-to-device).

#### **❖** Variation at lot level and above

State-of-the-art semiconductor manufacturing involves various batch processes that apply to multiple wafers at the same time for a high wafer throughput. For example, the chemical vapor deposition (CVD) heats up multiple wafers in the furnace, where the reactive gas forms a thin film on the surface of the wafers [13]. The batches are usually referred to as lots, which conventionally contain 25 wafers each. As a result, some process conditions are applied to all the wafers in the same lot but there are changes from lot to lot, leading to *lot-to-lot variation*. Meanwhile, wafers within the same lot are also subject to non-uniformity in the chamber environment, such as the temperature and the speed of the gas flow, which results in *within-lot variations*.

During single-workpiece processes, such as lithographic imaging and reactive ion etching (RIE), each wafer is processed individually. Naturally, this will lead to variability between different wafers, which is called *wafer-to-wafer variation*.

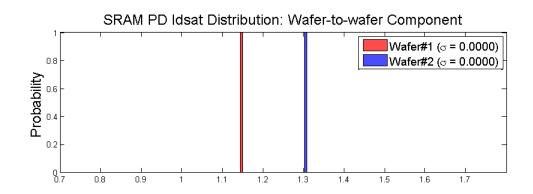

In theory, one can model the lot-to-lot and wafer-to-wafer variations using time-series models [13] and fit the systematic signatures of within-lot variations. In practice, however, such a practice requires long-term monitoring over a significant number of lots and wafers. It is often more convenient to lump them together as a single variation component that varies from wafer to wafer, denoted as  $\Delta P_{W2W}$ .

In this thesis, without loss of generality, we assume that the wafer-to-wafer variation  $\Delta P_{W2W}$  can be sufficiently modeled as a normally distributed variable independent to the other variation components. This assumption typically holds well in a reasonably mature semiconductor process without process splits. Thus, the *random wafer-to-wafer variation* is described by

$$\Delta P_{W2W} \sim N(0, \sigma_{W2W}^2) \tag{2.7}$$

#### **\*** Variation at the wafer level

Wafer level non-uniformity can come from deposition, photoresist spinning effects, temperature non-uniformity in post-exposure baking or plasma etching, and other equipment non-uniformities that result in a smooth, low-frequency across-wafer variation pattern. In particular, wafer-level variation often exhibits symmetric radial ("dome" or "bull's eye") patterns [51]. We call such repeatable wafer-level variability *systematic* across-wafer variation. Since the chip size is usually much smaller than the wafer diameter, we can assume that the across-wafer pattern is approximately constant within a chip's scale. Therefore, for a device from chip location  $(x_W, y_W)$  on the wafer, the systematic across-wafer variability component can usually be sufficiently represented by an elliptic paraboloid function, denoted as  $\Delta P_{AW}(x_W, y_W)$ :

$$\Delta P_{AW}(x_W, y_W) = a_W \cdot x_W^2 + b_W \cdot x_W + c_W \cdot y_W^2 + d_W \cdot y_W + e_W \cdot x_W y_W + f_W$$

(2.8)

In addition, process variations, such as the focus and exposure fluctuation in lithographic imaging, may introduce additional variability from chip to chip. Lumped together with the fitting residual of the systematic across-wafer variation, we call it the *random chip-to-chip variation* (or across-wafer random variation), denoted as  $\Delta P_{AWR}$ . It may be modeled by a Gaussian variable, as described in Equation 2.9.

$$\Delta P_{AWR} \sim N(0, \sigma_{AWR}^2) \tag{2.9}$$

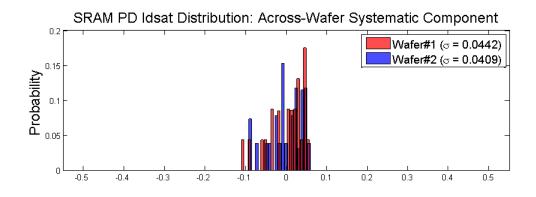

#### **\*** Variation at the die/chip level

Intra-die variation or within-die variation refers to the fluctuation of device properties on the same chip/die. Similar to wafer-level variations, chip-level variations also consist of systematic and random components. Typical sources of systematic spatial variations include stepper-induced variations (illumination, lens aberrations) [52], reticle imperfections, and CMP [50], [53]. The *systematic across-chip variation* of a device with location  $(x_C, y_C)$  on the die/chip can often be approximated by an elliptic paraboloid as well, as described by Equation 2.10 [50], [52], [53]:

$$\Delta P_{AC}(x_C, y_C) = a_C \cdot x_C^2 + b_C \cdot x_C + c_C \cdot y_C^2 + d_C \cdot y_C + e_C \cdot x_C y_C + f_C$$

(2.10)

The random across-chip variations (device-to-device or local mismatches), on the other hand, include intrinsic variability, such as RDF, interface-trapped charge fluctuations, atomic oxide-thickness fluctuations, and LER. These intrinsic random variations are dominant at the deep-submicron device scale. They are modeled as a normally distributed random variable independent to the other variation components, which is denoted as  $\Delta P_{ACR}$ :

$$\Delta P_{ACR} \sim N(0, \sigma_{ACR}^2) \tag{2.11}$$

Last, the layout-dependent variations, such as those due to optical-proximity effects, strained-silicon effects, and plasma micro loading, will cause devices with similar design parameters but different layout designs and/or sounding layout contexts to differ significantly in device characteristics, such as gate CD and mobility. In this work, we adopt the assumption that the layout-dependent effects do not interact with the rest of the spatial variations in the system; thus, the layout-dependent variation is a simple additive term described by Equation 2.12.

$$\Delta P_{layout} = F(layout\ pattern)$$

(2.12)

#### 2.3.2 Hierarchical Variability Model

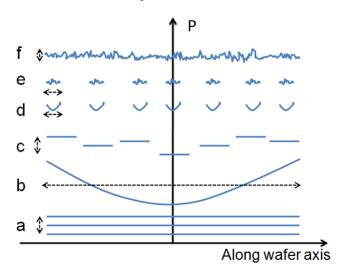

Figure 2.8: One-dimensional illustration of the hierarchical variability components of parameter *P*: a) lot-to-lot and wafer-to-wafer random, b) across-wafer systematic, c) chip-to-chip random, d) across-chip systematic, e) layout-dependent, and f) device-to-device random.

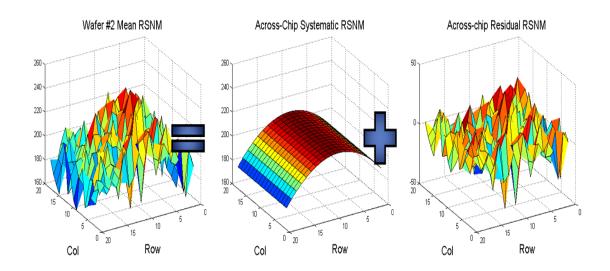

Figure 2.8 is an illustration of the hierarchical variability model we proposed for capturing the systematic and random components in the integrated circuit manufacturing process. Assume device parameter P is a process-related physical quantity and that its variations from different sources or hierarchy levels have relatively small interactions. In this case, the total variation of parameter P can be simply modeled as the sum of the different variability components:  $\Delta P = \Delta P_{source-1} + \Delta P_{source-2} + \cdots \Delta P_{source-N}$ .

Given the variability decomposition scheme previously described, the total spatial variation of parameter P can be decomposed as the sum of the wafer-to-wafer random variations, across-wafer systematic variations, chip-to-chip (across-wafer) random variations, across-chip systematic variations, device-to-device (across-chip) random variations, and layout-dependent variations.

$$\Delta P = \Delta P_{W2W} + \Delta P_{AW} + \Delta P_{AWR} + \Delta P_{AC} + \Delta P_{ACR} + \Delta P_{Layout}$$

(2.13)

Such an additive hierarchical model can also be applied to the estimates of those device or circuit parameters that are linearly proportional to additive physical quantities. For example, the effective gate length (*Leff*) of transistors is often such a physical parameter that satisfies the additive requirement. Consequently, the ring oscillator stage delay, which is proportional to *Leff* to the first order, can also be modeled in this additive fashion

(Equation 2.14). The additive model cannot be applied to the ring oscillator frequency, however, as it follows 1/*Leff* (Equation 2.15).

$$\Delta Delay = k \Delta L_{eff} = k \left( \Delta L_{eff,source-1} + \Delta L_{eff,source-2} \right)$$

$$= \Delta Delay_{source-1} + \Delta Delay_{source-2}$$

$$\Delta freq = \frac{1}{k \Delta L_{eff}} = \frac{1}{k \left( \Delta L_{eff,source-1} + \Delta L_{eff,source-2} \right)}$$

$$= \left( \Delta freq_{source-1}^{-1} + \Delta freq_{source-2}^{-1} \right)^{-1}$$

$$\neq \Delta freq_{source-1} + \Delta freq_{source-2}$$

$$(2.14)$$

$$(2.14)$$

$$= \Delta freq_{source-1} + \Delta freq_{source-2}$$

## 2.4 Summary

In this chapter, we first reviewed the various classifications of process variability. By nature, process variations can be environmental, temporal, or spatial. With regard to repeatability, process variations can be systematic or random, and with regard to their scope of impact, process variations are divided into global variations and local variations.

The common sources of the systematic and random components of spatial process variation are then discussed in detail. The most prominent effects include variations in lithographical imaging and post-exposure baking (PEB), random dopant fluctuations (RDF), line-edge roughness (LER), well-proximity effects (WPE), strained silicon effects, chemical mechanical polishing (CMP), thin film-thickness fluctuation, etc.

Lastly, an additive hierarchical variability model was proposed to capture the various components of spatial process variations. The total variability of device parameter *P* was modeled as the sum of the random wafer-to-wafer, chip-to-chip, and device-to-device variations; the systematic across-wafer and across-chip variations; and the layout-dependent variations. This simple but effective spatial variability model will be used in characterizing the variability profile in the near-mature commercial-quality silicon data in Chapter 3 and Chapter 5.

# Chapter 3

# Test Chip Design, Characterization, and Variability Analysis

#### 3.1 Introduction

We experimented with multiple test wafers with custom test structures to investigate the influence of process variability in modern semiconductor manufacturing and to understand the underlying mechanism. The test circuits were designed by BWRC students and faculty [54]–[57], and fabricated by our foundries partners using the 90nm and 45nm bulk process. We characterized key variability test structures, including ring oscillator (RO) arrays for delay and leakage current measurement, SRAM arrays, and individually measurable padded-out transistors of the SRAM cells.

## 3.2 The 90nm Ring Oscillator Test Chip

#### 3.2.1 Chip Design Overview

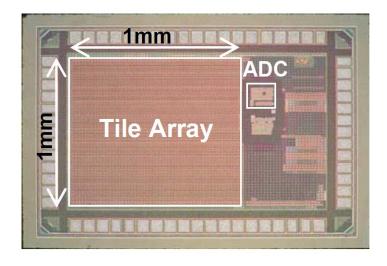

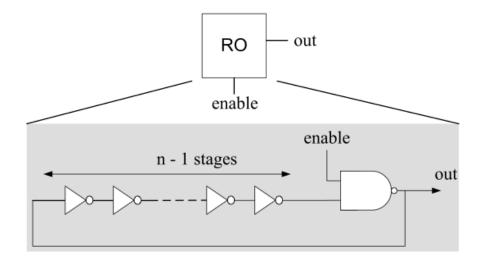

A test chip is designed and implemented in a general-purpose 90nm CMOS technology process from STMicroelectronics to characterize the process-induced circuit variations [54]. The approach we use is to measure the oscillating delay and transistor source-drain leakage currents of an array of ring-oscillator test structures.

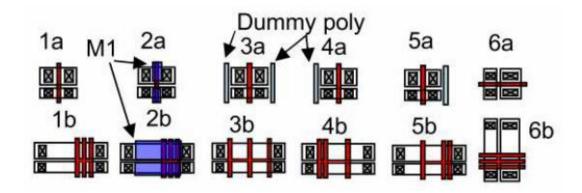

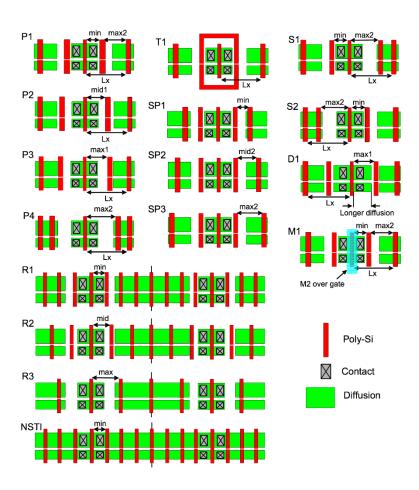

The test chip is made up of 10 rows × 16 columns of tiles of test structures. Each tile contains twelve 13-stage RO and 12 off-state NMOS transistors, one for each of the 12 different layout styles (Figure 3.2). The tiles are separated by 62.5um horizontally and 100um vertically. The total array area is 1mm × 1mm, and the overall die size, including the peripherals, is about 1.8mm × 1.4mm. Layout pattern styles include gate stacks that consist of 1 to 3 Poly-Si fingers with varied length of diffusion (LOD). The Poly-Si pitch of neighboring dummy features is varied, and one layout has a Poly-Si orientation rotated by 90 degrees. Asymmetric masks are used to test the coma effect. The first metal layer coverage over gates is varied as well. The test chip also includes a leakage current measurement circuit, which sits right beside the ROs with the same layout.

Figure 3.1: Die photo of 90nm test chip [54]

Figure 3.2: Layout configuration in the 90nm test chip [54]

## 3.2.2 Sampling and Measurement Scheme

There are two requirements on the sampling scheme based on our variability model. First, there must be enough measuring points inside each chip to capture the systematic and random components at chip level. Second, these points should be spread out across the wafer to capture the wafer level variations.

For this 90nm test wafer, we examined the delay and static leakage (IDDQ) data collected from 36 chips distributed mostly across the right half of the wafer. Each chip was measured exhaustively to get a complete and statistically significant spatial coverage over the 1mm × 1mm RO array. The ring oscillator delays were measured off-chip with a

20GSPS oscilloscope and averaged over about 100 periods. The transistor off-state currents were measured using an on-chip single-slope analog-to-digital converter (ADC) [58]. The wafer-level measurement plan and the collected RO data are shown in Figure 3.4.

Figure 3.3: Ring oscillator with n stages [58]

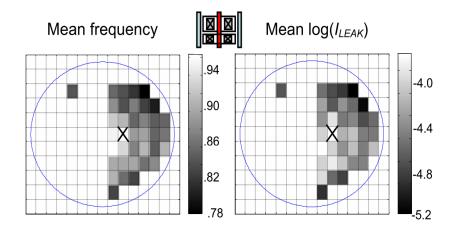

Figure 3.4: Wafer maps of mean RO frequency and mean Log(I<sub>LEAK</sub>) for layout 3A [54]

## 3.2.3 Variability Observation

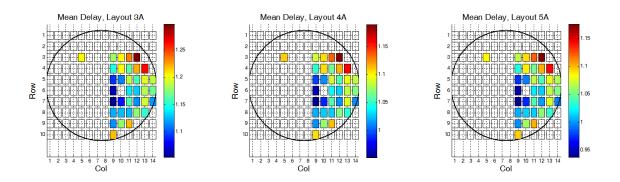

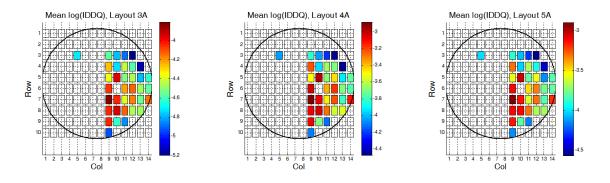

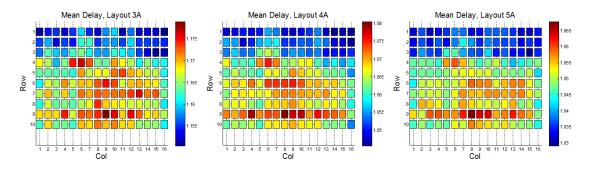

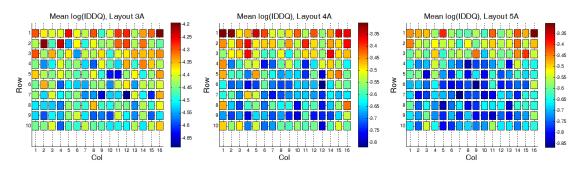

Devices of three representative layouts—3A, 4A, and 5A—are selected for studying the wafer-level, chip-level, and layout-to-layout variations. Wafer-level RO delay and leakage (IDDQ) variation of these layouts are shown in Figure 3.5 and Figure 3.6. Each

data block stands for the average value over all the 160 tiles, which is noted by symbol  $D\langle -DWP \rangle$  and  $I\langle -DWP \rangle$ . Similarly, chip-level RO delay and leakage variations are shown in Figure 3.7 and Figure 3.8. Each data block stands for the average value of all 36 dies, which is noted by symbol  $D\langle T-WP \rangle$  and  $I\langle T-WP \rangle$ .

If we assume that the majority of systematic variations are from the effective gate length ( $L_{eff}$ ) variability, then the following simple model describes the RO delay and leakage (SPICE simulations confirm that this is a good approximation when the gate length variation is small):

$$delay: D = D_0 \left(\frac{L_{eff}}{L_0}\right)$$

$$leakage: \log IDDQ = \log IDDQ_0 \left(\frac{L_0}{L_{eff}}\right)$$

(3.1)

As a simple function of the physical quantity  $L_{eff}$ , RO delay is a good candidate for the application of the additive hierarchical variability model. According to the hierarchical model, the total variation of devices of a given layout pattern on a single wafer can be decomposed into across-wafer systematic (AW), across-wafer random (AWR), across-chip systematic (AC), and across-chip random (ACR). Statistical analysis shows that the across-wafer gate RO delay variation can be approximated adequately by a second-order polynomial, of the form in Equation 3.2. Note that due to the lack of the left half of the wafer, the quadratic term in the X-direction is statistically insignificant; we set that coefficient to zero. Meanwhile, the across-chip variation can also be fitted by a chip-level second-order polynomial. Statistics show the variation along different columns does not have a significant systematic component, while variation along the different rows displays a significant (half-) parabolic pattern. The simplified approximation is shown in Equation 3.3.

$$D\langle -DWP \rangle = D\langle -DWP \rangle_{AW} + D\langle -DWP \rangle_{AWR}$$

$$D\langle -DWP \rangle_{AW} = a_W X_W^2 + b_W X_W + 0 \times Y_W^2 + d_W Y_W + e_W$$

(3.2)

$$D\langle T - WP \rangle = D\langle T - WP \rangle_{AC} + D\langle T - WP \rangle_{ACR}$$

$$D\langle T - WP \rangle_{AC} = 0 \times X_C^2 + 0 \times X_C + c_C Y_C^2 + d_C Y_C + e_C$$

(3.3)

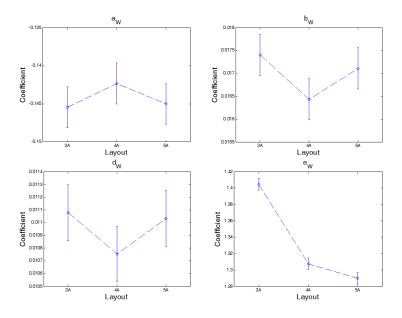

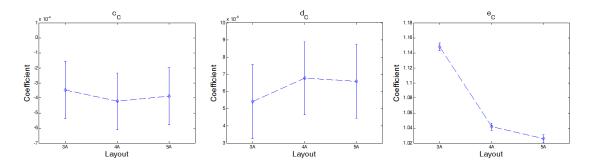

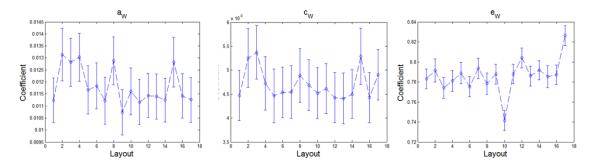

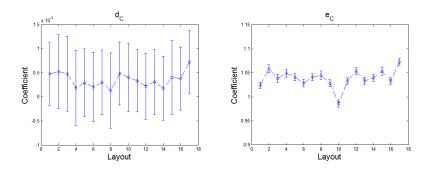

Using RO delay as an example, the fitted coefficients and their 95% confidence intervals are shown in Figure 3.9: and Figure 3.10.

Below, I apply statistical tests *algorithmically* rather than *statistically*: the underlying statistical models do not hold: there is no basis for the assumed probability distribution of the data, and all the null hypotheses are false. The tests do not have their nominal significance levels in this problem; indeed, it is not clear what "significance level" would even mean. Nonetheless, applying statistical tests may provide insight into which components of variation are worth modeling, and may lead to models that make more reliable and useful predictions.

To examine the layout dependence effects on the variation pattern, we used *t*-statistic to compare the estimates of fitted coefficients from the three layout designs. Use  $a_W$  as example, and under the assumption null-hypothesis  $H_0$ :  $a_{W_{3A}} = a_{W_{4A}}$  is rejected if:

$$t_{a_{W_{3A}},a_{W_{4A}}} = \frac{\left|\hat{a}_{W_{3A}} - \hat{a}_{W_{4A}}\right|}{\sqrt{SE_{a_{W_{3A}}}^2 + SE_{a_{W_{4A}}}^2}} > t_{\frac{\alpha}{2},N-1}$$

(3.4)

The estimates of mean and standard error (SE) in the linear regression model (Table 3.1), give

$$t_{a_{W_{3A}},a_{W_{4A}}} = \frac{|-0.1454 + 0.1423|}{\sqrt{1.903 \times 10^{-6} + 1.867 \times 10^{-6}}} = 1.612$$

$$< t_{\underline{0.05},5757} = 1.96$$

(3.5)

Similarly,

$$t_{a_{W_{3A}},a_{W_{5A}}} = \frac{|-0.1454 + 0.145|}{\sqrt{1.903 \times 10^{-6} + 1.902 \times 10^{-6}}} = 0.224$$

$$< t_{\underbrace{0.05}_{2},5757} = 1.96$$

(3.6)

$$t_{a_{W_{4A}},a_{W_{5A}}} = \frac{|-0.1423 + 0.145|}{\sqrt{1.867 \times 10^{-6} + 1.902 \times 10^{-6}}} = 1.385$$

$$< t_{\underline{0.05},5757} = 1.96$$

(3.7)

None of the three pair-wise null hypotheses is rejected. This suggests it may be adequate to take the coefficient  $a_W$  to be equal for all three layout designs. Similar

analysis leads us to model the rest of "shape" coefficients  $b_W$  and  $d_W$  as equal for the three layout designs. On the other hand, the same tests for the intercept coefficient  $e_W$  give:

$$t_{e_{W_{3A}},e_{W_{4A}}} = 19.1 > 1.96 \tag{3.8}$$

$$t_{e_{W_{3A}},e_{W_{5A}}} = 22.4 > 1.96 \tag{3.9}$$

$$t_{e_{W_{4A}},e_{W_{5A}}} = 3.47 > 1.96 \tag{3.10}$$

Because these differences are (nominally) statistically significant, we retain differences among the intercept terms  $e_W$  for layouts 3A, 4A and 5A. It is also worth noting that the *t*-statistics between layout 4A and 5A are much smaller than that between either of those layouts and layout 3A.

|       |                 | 3A       | 4A       | 5A       |

|-------|-----------------|----------|----------|----------|

| $a_W$ | Estimate        | -0.145   | -0.142   | -0.145   |

|       | $SE^2$          | 1.9E-06  | 1.87E-06 | 1.9E-06  |

| $b_W$ | Estimate        | 0.0174   | 0.0164   | 0.0171   |

|       | $SE^2$          | 5.27E-08 | 5.17E-08 | 5.27E-08 |

| $d_W$ | Estimate        | 0.0111   | 0.0108   | 0.0110   |

|       | $SE^2$          | 1.26E-08 | 1.23E-08 | 1.26E-08 |

| $e_W$ | Estimate        | 1.40     | 1.31     | 1.29     |

|       | SE <sup>2</sup> | 1.31E-05 | 1.29E-05 | 1.31E-05 |

Table 3.1: Estimates and standard errors of fitting coefficient  $a_W$ ,  $b_W$ ,  $d_W$  and  $e_W$  for the across-wafer spatial variation patterns of layout 3A, 4A and 5A

The number of pairwise statistical tests of coefficient equality required can grow quickly as more layout designs are in comparison. As an alternative, we simply observe

the trend of confidence intervals (CI) of the fitting coefficients across different layouts. While not a statistically valid test for a difference, we treat these shape coefficients as equal if their CIs have large overlaps.

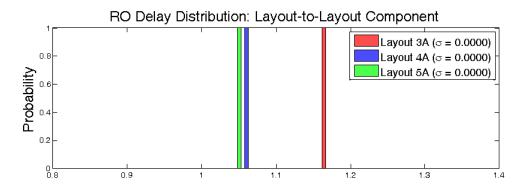

With this alternative method, we found that most of the layout-dependent effects are accounted for by differences in the intercept terms  $e_W$  and  $e_C$ . We model the layout-dependent component in this process as an additive component on top of the systematic across-wafer and across-chip component. The large overlap of the confidence intervals of the layout component  $e_W$  and  $e_C$  between layouts 4A and 5A while layout 3A is far apart is consistent with the fact that layouts 4A and 5A are mirror images while 3A has a different pattern density. Therefore, the layout-dependence differences between them are minimal, while layout 3A with dummy polys on both sides of the gate actually behaves as a slower device in general. This observation is contradictory to the common knowledge that a more regular poly-grating structure will result in a narrower printed poly gate critical dimension (poly CD). Unfortunately, it requires more detailed electrical tests as well as physical examination of the device cross-section to reveal the root cause. Last, a similar conclusion can be drawn if we perform the same experiment on the RO leakage data.

Figure 3.5: Wafer maps of mean RO delay of layouts 3A, 4A, and 5A [54]:  $D\langle -DWP \rangle$

Figure 3.6: Wafer maps of the mean RO log(IDDQ) of layouts 3A, 4A, and 5A [54]:  $I\langle -DWP \rangle$

Figure 3.7: Chip maps of the mean RO delay of layouts 3A, 4A, and 5A [54]: D(T - WP)

Figure 3.8: Chip maps of the mean RO log(IDDQ) of layouts 3A, 4A, and 5A [54]: I(T - WP)

Figure 3.9: Estimate and confidence interval of across-wafer fitting coefficients: layouts 3A, 4A, and 5A

Figure 3.10 Estimate and confidence interval of across-chip fitting coefficients: layouts 3A, 4A, and 5A

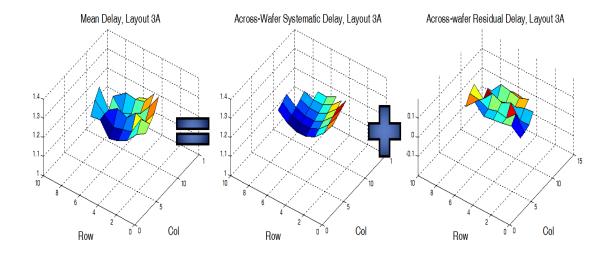

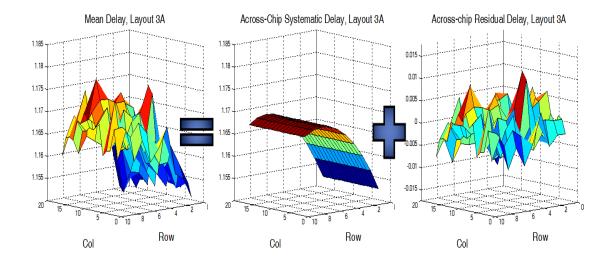

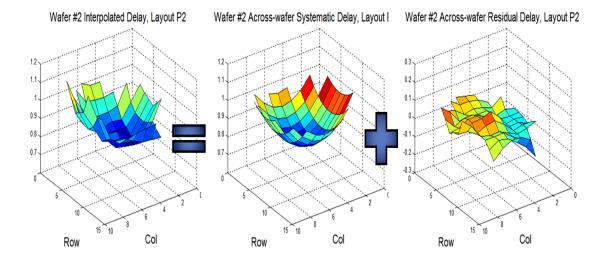

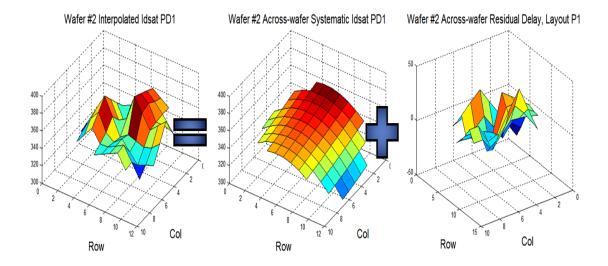

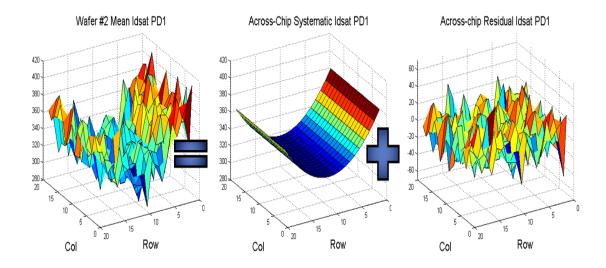

Figure 3.11 and Figure 3.12 illustrate the decomposition of across-wafer and across-chip RO delay variations of layout 3A. The fitting residuals after the removal of the systematic across-wafer and across-chip components become much closer to a standard Gaussian distribution, as shown in Figure 3.14.

To test how much the hierarchical variability model improves on the conventional "Global+Local" variability model, Monte Carlo experiments are performed to simulate the distribution of the RO delay of 10,000 chips with 160 test devices per chip. Assume each chip has the exact equal chance to be chosen from the 36 chip locations on the wafer, and each test device has the exact equal chance to be chosen from the 160 tile locations on the chip. Under the simple "Global+Local" model, the delay of each RO device is the sum of two Gaussian random variables. One carries the same variance as the total chip-to-chip variation from the raw measurement, while the other carries the same variance as the total within-chip variance of the raw measurement data. Under the hierarchical variability model, the RO delay is still modeled as the sum of the chip-level component and the within-chip component. However, each component is now composed of a systematic across-wafer/across-chip component in addition to the residual Gaussian random variation. The formula for simulating the distribution is shown in equation 3.11 to 3.13.

RO delay of the kth layout from the jth tile on the ith chip:

$$D_{i,j,k} = Layout_k + Chip_i + Tile_j$$

(3.11)

"Global+Local" variation model:

$$Chip_{i} \sim N(0, \sigma_{Global})$$

$$Tile_{i} \sim N(0, \sigma_{Local})$$

(3.12)

Hierarchical model:

$$Chip_{i} \sim f_{AW}(X_{W_{i}}, Y_{W_{i}}) + N(0, \sigma_{AWR})$$

$$Tile_{j} \sim f_{AC}(X_{C_{j}}, Y_{C_{j}}) + N(0, \sigma_{ACR})$$

$$(3.13)$$

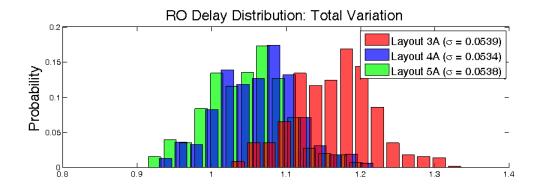

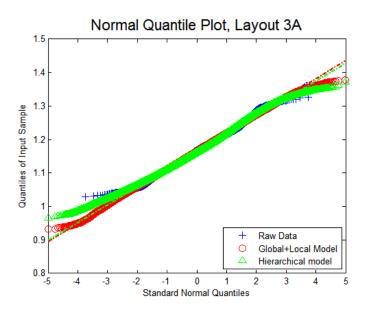

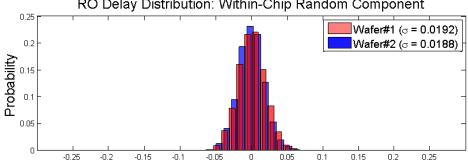

The normal quantile plots (Figure 3.15) provide direct comparisons of the two models' Monte Carlo experiment results. Both model predictions are fairly close to the raw measurement for the most part within  $\pm 2\sigma$ . At  $\pm 3\sigma$ , the hierarchical model starts to show less deviation from the raw measurement than the "Global+Local" model, especially on the fast side. The numerical comparisons of  $\pm 3\sigma$  and the median delay of layouts 3A, 4A, and 5A are shown in Table 3.2. The two models are within 0.5% of each other at  $+3\sigma$  for all three layouts, while at  $-3\sigma$ , the hierarchical model consistently shows 2% better accuracy than the simple "Global+Local" model.

Figure 3.11: Decomposition of wafer-level variation of layout 3A:  $D\langle -DWP\rangle = D\langle -DWP\rangle_{AW} + D\langle -DWP\rangle_{AWR}$

Figure 3.12: Decomposition of wafer-level variation of layout 3A:

$$D\langle T-WP\rangle = D\langle T-WP\rangle_{AC} + D\langle T-WP\rangle_{ACR}$$

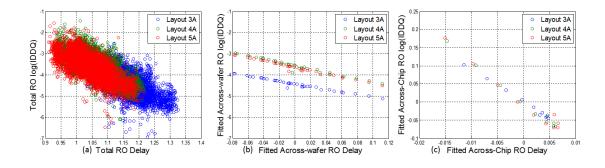

Figure 3.13: Correlation between RO leakage and delay:

(a)  $I\langle TDWP \rangle$  vs.  $D\langle TDWP \rangle$ ; (b)  $I\langle T-WP \rangle_{AW}$  vs.  $D\langle T-WP \rangle_{AW}$ ; (c)  $I\langle -DWP \rangle_{AC}$  vs.  $D\langle -DWP \rangle_{AC}$

Figure 3.14: Histogram of the RO delay distribution as well as the systematic across-wafer, layout-to-layout, random chip-to-chip, systematic across-chip, and random tile-to-tile variability

Figure 3.15: Comparing the prediction accuracy of the "Global+Local" model versus the hierarchical model for the RO delay distributions of layout 3A

|           |            | Measurement | "Global+Local" Model | Hierarchical Model |

|-----------|------------|-------------|----------------------|--------------------|

| Layout 3A | +3σ        | 1.317       | 1.327 (+0.8%)        | 1.324 (+0.5%)      |

|           | Median     | 1.168       | 1.165 (-0.2%)        | 1.162 (-0.5%)      |

|           | $-3\sigma$ | 1.036       | 1.004 (-3.1%)        | 1.024 (-1.1%)      |

| Layout 4A | +3σ        | 1.212       | 1.225 (+1.1%)        | 1.226 (+1.2%)      |

|           | Median     | 1.066 | 1.062 (-0.4%) | 1.059 (-0.7%) |

|-----------|------------|-------|---------------|---------------|

|           | $-3\sigma$ | 0.935 | 0.904 (-3.3%) | 0.926 (-1.0%) |

| Layout 5A | +3σ        | 1.198 | 1.214 (+1.3%) | 1.218 (+1.7%) |

|           | Median     | 1.051 | 1.048 (-0.4%) | 1.045 (-0.6%) |

|           | $-3\sigma$ | 0.919 | 0.890 (-3.2%) | 0.909 (-1.2%) |

Table 3.2: Median and +/- 3s of simple "Global+Local" model and the hierarchical variability model in comparison with the measurements (difference to measurement shown in percentages)

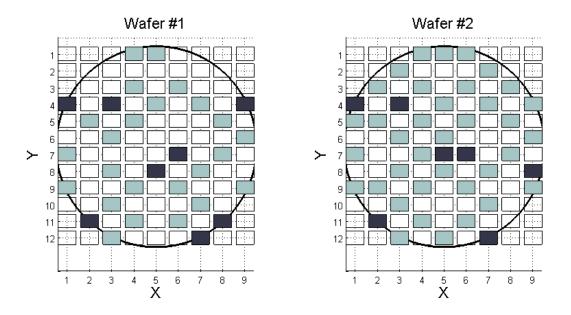

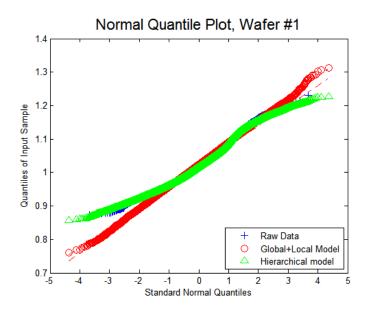

## 3.3 The 45nm Ring Oscillator and SRAM Test Chips 3.3.1 Chip Overview

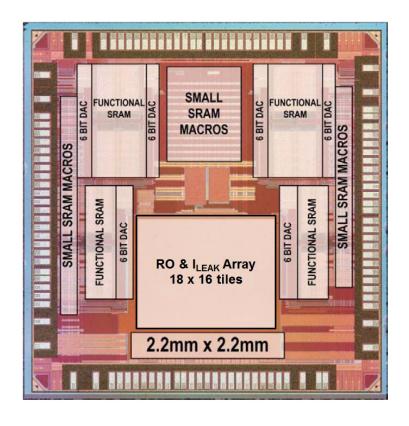

To further investigate the process dependency of the device and circuit variability, a newer set of 45nm test chip circuitries was designed by Liang-teck Pang et al. [57] and Zheng Guo [59]. The test chips were fabricated using a 45nm low-power strained-Si CMOS process [47], [48], [60], with an array of ROs and corresponding off-state leakage current measurement circuitry, as well as 18 SRAM macros that allow the characterization of SRAM padded-out transistors and the SRAM read/write margins. The die photo is shown in Figure 3.16.

To keep up with the aggressive technology scaling, new fabrication practices and stricter design rules have been introduced to the 45nm technology. Poly spacing can no longer be freely adjusted; instead, only a small continuous range followed by a discrete jump in Poly-Si spacing is allowed. All transistor channels are oriented in the <100> direction, which enhances PMOS mobility and makes it insensitive to stress [61]. Two major sources of stress are introduced both by design and unintentionally in this process: strain caused by the contact-etch stop layer (CESL) and the shallow trench isolation (STI) stress. Subatmospheric chemical vapor deposition oxide (SACVD) largely reduces usually strong compressive STI stress and turns it into a weak tensile one. CESL is formed by intentionally depositing a nitride layer on top of NMOS transistors, which introduces a strong horizontal tensile strain that greatly enhances the electron mobility. Another important feature of the new 45nm test chip fabrication is the different gate-trimming treatment for the two wafers we have, aiming at a nominal 4nm reduction in gate CD from the slower wafer (#1) to the faster wafer (#2). The major features of the 45nm process are summarized in Table 3.3.

Figure 3.16: Die photo of the 45nm test chip

| Process Feature                | 45nm Process                               | Effect               |

|--------------------------------|--------------------------------------------|----------------------|

| Si substrate                   | [100]-oriented channel                     | Higher PMOS mobility |

| Shallow trench isolation (STI) | Sub-atmospheric deposited oxide            | Lower STI stress     |

| Contact etch stop layer (CESL) | Nitride layer creating high tensile strain | Higher NMOS mobility |

| Immersion lithography          | NA > 1                                     | Improved resolution  |

| Backend dielectric             | Low k ~2.5                                 | Low RC delay         |

Table 3.3: Summary of the 45nm process

The RO array contains  $18 \times 16$  identical tiles. Each tile consists of 17 thirteen-stage ROs and 17 pairs of off-state NMOS and PMOS transistors for leakage measurements, each with the same transistor sizing embedded in a different layout pattern. A total of 17 different RO transistor layouts are designed based on the new process and design rules to

capture possible layout-dependent effects, including various Poly-Si gate-dummy pitches, different source/drain areas with and without STI, and orientation of transistor placement. The layouts are presented in Figure 3.17 and Figure 3.18. Note that the pre-OPC patterns depicted in Figure 3.17 are subject to OPC treatment prior to fabrication, the specifics of which remain unknown to us. Measurement circuitry was adopted from the design of the 90nm test chip. The RO delay and corresponding off-state NMOS/PMOS transistor leakage currents were measured in our laboratory after the wafers were diced and the chips were packaged.

Figure 3.17: Sixteen pre-OPC RO layout configurations in the 45nm test chip, all arranged horizontally (An additional configuration using the same design of layout P1 but arranged vertically is shown separately in Figure 3.18)

Figure 3.18: Two different RO implementations of the layout pattern P1: (a) horizontal arrangement, (b) vertical arrangement

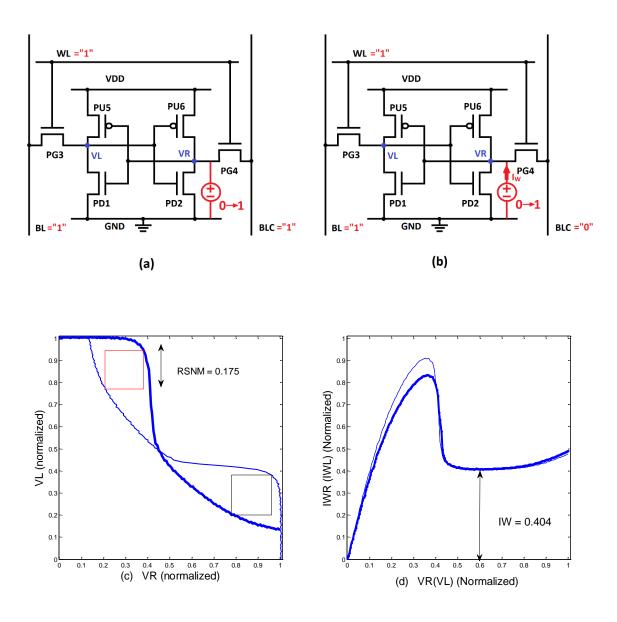

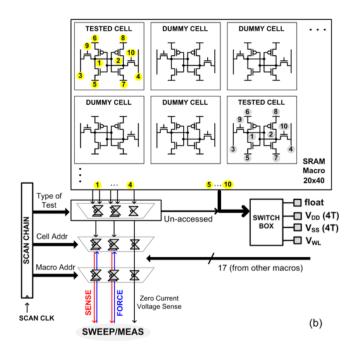

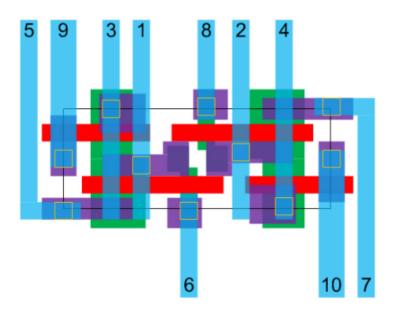

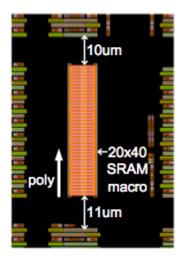

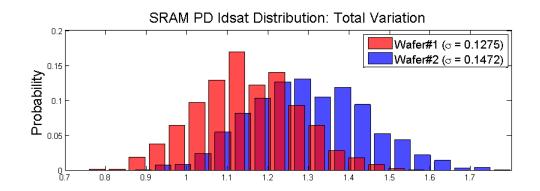

SRAM is known to be sensitive to process variation, especially threshold voltage variations caused by random dopant fluctuation, line-edge roughness, work function fluctuations and etc. To characterize the variability of SRAM in a modern semiconductor process, SRAM test structures were also incorporated in these 45nm test chips. Each test chip contains 18 SRAM macros, and each macro contains 20 rows ×40 columns of SRAM cells, as shown in Figure 3.22. Along the diagonal of each macro, 20 bit-cells have all their internal nodes accessible through a switch network (Figure 3.20), thus allowing the automated measurement of SRAM functional metrics as well as the electrical characteristics of each of the 6 individual transistors in a bit cell.

Typical SRAM functional metrics consist of read stability and write stability, which stand for the amount of disturbance bit cells can withstand without accidental change of the data stored during a read cycle or a write cycle, respectively. The read stability is usually characterized by the Read Static Noise Margins (RSNM), which is extracted by measuring a pair of voltage transfer characteristics (VTC), more commonly known as the "butterfly curves" [62]. The RSNM is quantified as the largest square that can fit into the pair of read VTC from the same bit cell. Meanwhile, SRAM write stability can often be represented by the writeability current ( $I_W$ ), which is extracted from the N-curve for writeability [63].  $I_W$  is defined as the minimum current past the inverter trip point (the sudden drop in current in the N-curve). Figure 3.13 illustrates both setups for characterizing SRAM cell-design margins.

Figure 3.19: (a) Bit cell measurement setup for the "butterfly curve" to extract the Read Static Noise Margin [63] (RSNM), (b) measurement setup for the "N-curve" to extract the writeability current (*I<sub>W</sub>*) [64], (c) butterfly curve with its corresponding measurement highlighted, (d) N-curve with corresponding measurement highlighted

Figure 3.20: All-internal-node access scheme in SRAM macros [56]

Figure 3.21: Layout cartoon for a 0.374  $\mu m^2$  bit cell with all 10 internal nodes wired out (*Courtesy: Zheng Guo, UC Berkeley*)

Figure 3.22: Layout view of a 20 ×40 SRAM macro, with poly in the vertical direction, using all internal node access surrounded by a large STI [56]

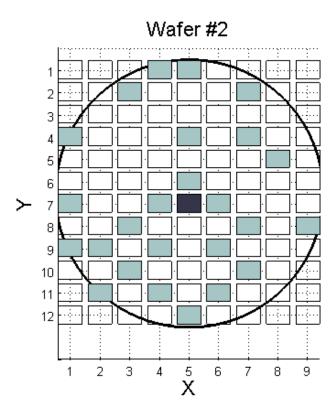

### 3.3.2 Ring Oscillator Variability Observation

A total of 76 dies from the 2 wafers are packaged for characterization. Bearing the systematic across-wafer variation profile in mind, more emphasis is put on the dies near the periphery and the center of the wafer for better coverage of the leading and trailing edge of the performance distribution. At least 8 tiles of the  $18 \times 16$  RO array are measured at each die site, while full-array characterization had been done for 15 selected dies, as shown in Figure 3.23.

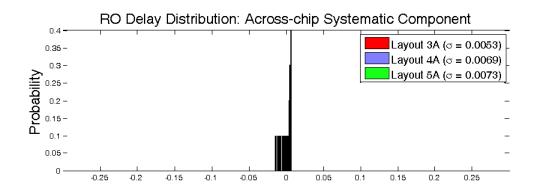

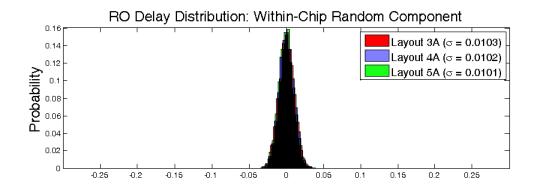

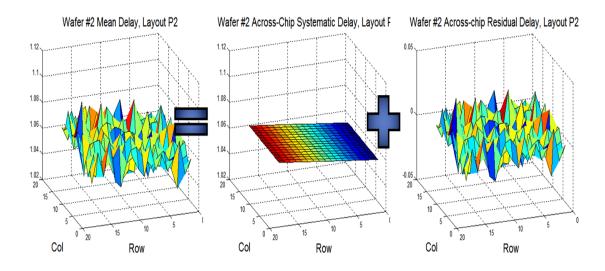

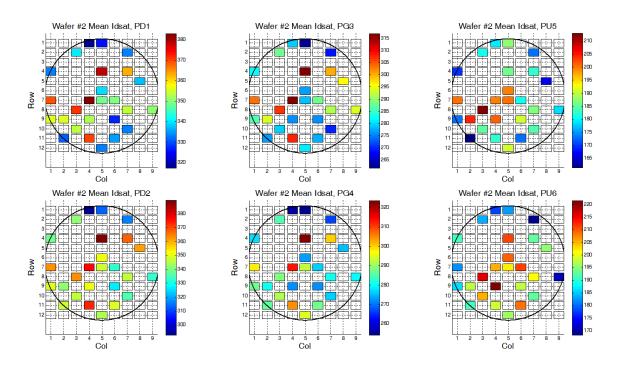

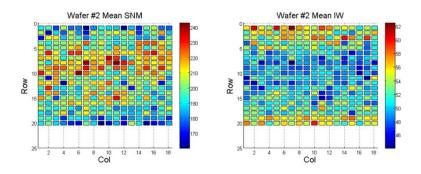

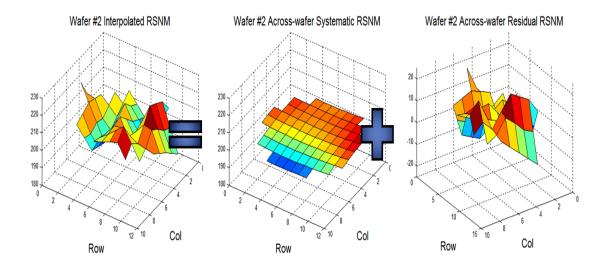

The within-chip RO variability averaged over 15 fully characterized dies is shown in Figure 3.25. The figure shows that there is no strong systematic across-chip variation. Thus, it is reasonable to estimate full within-chip statistics from a random sample of locations within a die. A simple decomposition of the variability (see Figure 3.31) shows that within-chip variation (~2%) is relatively small compare to wafer-level variations (20~30%). Hence, even a small sample of devices from the die should suffice to estimate the chip median and the across-wafer variability accurately. We chose to measure only 8 sites per chip for the majority of chips, which saves a significant amount of characterization time without noticeably compromising the accuracy of estimates of across-chip variability.

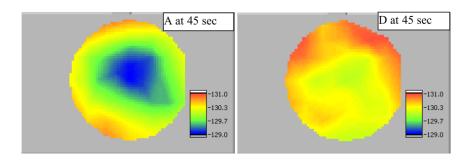

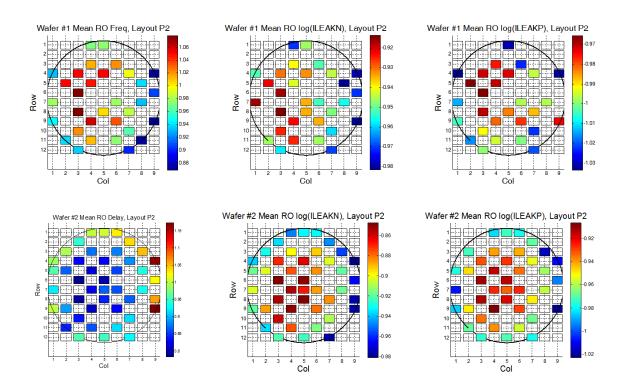

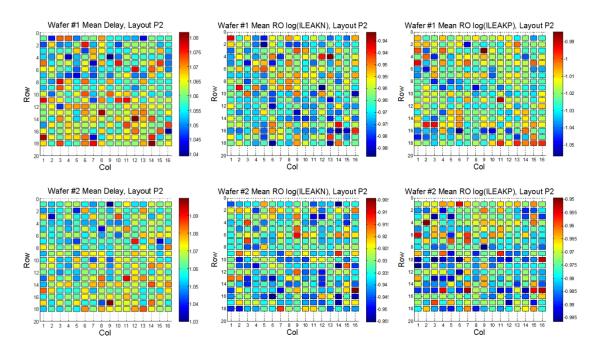

Wafer-level RO delay and leakage (NMOS and PMOS) variation of layout P2 are shown in Figure 3.24. Each data block stands for the mean delay/leakage over the measured tiles, which is noted by symbol  $D\langle -DWP\rangle$ ,  $I_{LEAKN}\langle -DWP\rangle$ , and  $I_{LEAKP}\langle -DWP\rangle$ . Similarly, chip-level RO delay and leakage variation are shown in Figure 3.25. Each data

block stands for the average value of the 15 fully characterized dies, which is noted by symbol  $D\langle T - WP \rangle$ ,  $I_{LEAKN}\langle T - WP \rangle$ , and  $I_{LEAKP}\langle T - WP \rangle$ .

The basic assumptions about the composition of variations are very similar to those described in Section 3.2, used to analyze the 90nm technology. The across-wafer RO delay variation can be approximated adequately by a second-order polynomial, as shown in Equation 3.14. The across-chip variation can be approximated adequately by a linear surface, as shown in Equation 3.15. In modern processes, two major sources contribute to the across-wafer systematic variation. First, during post-exposure-bake (PEB), the wafer temperature is non-uniform during the rapid heating step [65]. Second, during plasma etching, higher temperatures near the center of the wafer typically cause over-etch, leading to faster devices [66]. Both may cause the gate critical dimension (gate CD) to have a bull's-eye pattern across the wafer.

$$D\langle -DWP \rangle = D\langle -DWP \rangle_{AW} + D\langle -DWP \rangle_{AWR}$$

$$D\langle -DWP \rangle_{AW} = a_W (X_W - X_0)^2 + c_W \times (Y_W - Y_0)^2 + e_W$$

(3.14)

$$D\langle T - WP \rangle = D\langle T - WP \rangle_{AC} + D\langle T - WP \rangle_{ACR}$$

$$D\langle T - WP \rangle_{AC} = 0 \times X_C^2 + 0 \times X_C + 0 \times Y_C^2 + d_C Y_C + e_C$$

(3.15)

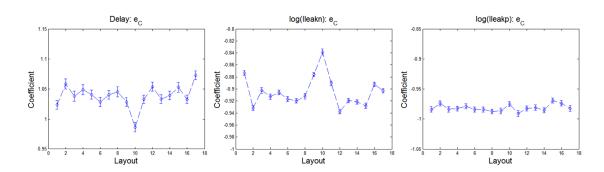

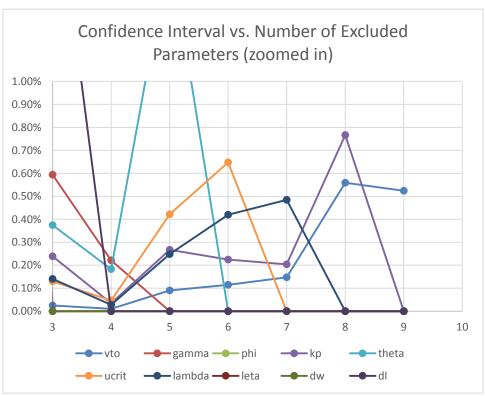

Still using RO delay as an example, the fitted coefficients and their 95% confidence intervals of all 17 layouts are shown in Figure 3.26 and Figure 3.27. As was the case for the 90nm test chip results, the confidence intervals for the "shape parameters" of both wafer-level  $(a_W, c_W)$  and chip-level systematic variations  $(d_C)$  overlap across all layouts. Again we treat these parameters as equal even without rigorous statistical proof. Most layout-dependent effects are thus captured by the intercept terms  $e_W$  and  $e_C$ , and we model the layout-dependent component in the 45nm process as an additive term in addition to the systematic across-wafer and across-chip components. For RO delay variability, the devices showing the strongest layout-dependent effects were layout #10 (D1), which features the largest diffusion width, and layout #17, which has the vertical RO placement.

To better understand the underlying mechanisms, we compare the layout effect components from the RO delay analysis as well as from the NMOS and PMOS leakage data. We focus on the intercept term from the within-chip fitting of RO delay and leakages for all 17 layouts, as in Figure 3.28. We can see that the layout dependence of the RO delay and log NMOS leakage are both significant and strongly correlated, while PMOS leakage

shows little layout dependence and does not correlate to the RO delay or NMOS leakage. This suggests that the layout-to-layout gate length variation might not be the actual source of variability since NMOS and PMOS are both subject to gate length related effects. A more plausible explanation is that the threshold voltage depends on the layout pattern. One such mechanism is the STI stress, which causes NMOS Vt to decrease and the mobility to increase with a larger length of diffusion (LOD) and smaller STI width [67], [68]. PMOS, however, is not as sensitive to stress effects due to the <100> channel orientation of this specific 45nm process. This can explain the higher speed and higher NMOS leakage for layout #10 (D1). Further investigation would require access to the internal transistors, which is not possible with this chip.

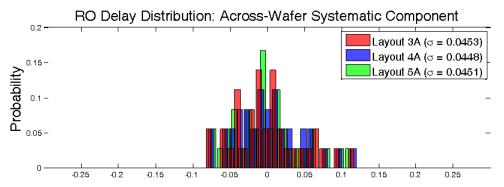

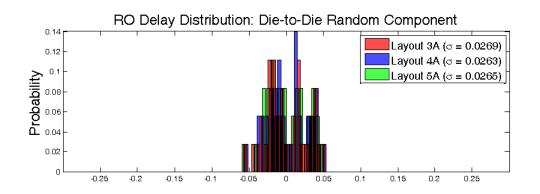

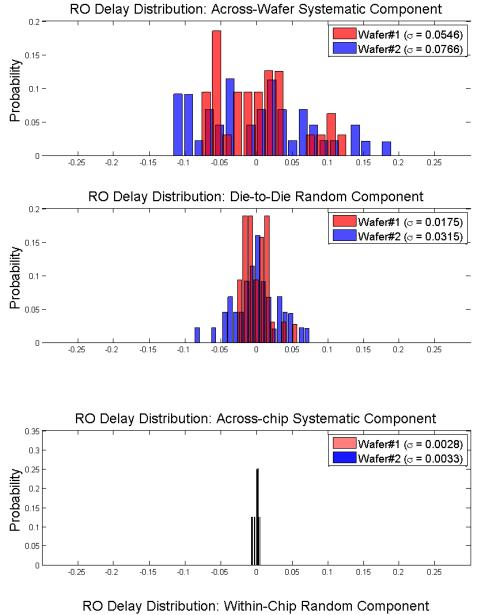

Overall, the variability of 45nm RO delay (or leakage) can be well summarized as the sum of a strong layout-to-layout-dependent component, a strong across-wafer paraboloid "bowl" (or "dome"), a smaller chip-to-chip Gaussian random noise, and a within-chip site-to-site Gaussian random noise of similar magnitude as the chip-to-chip random noise. The across-chip systematic component is negligible.

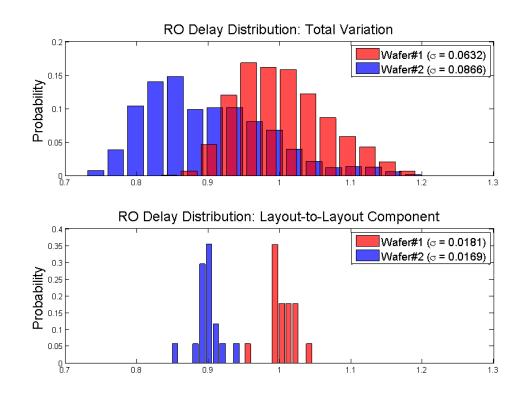

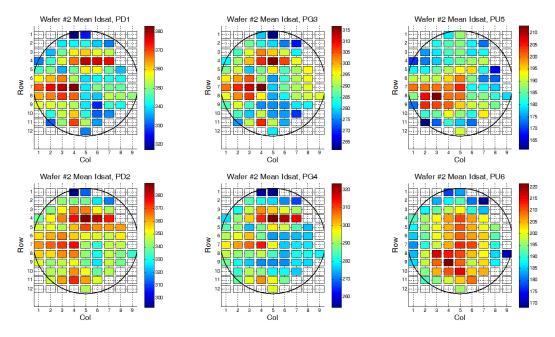

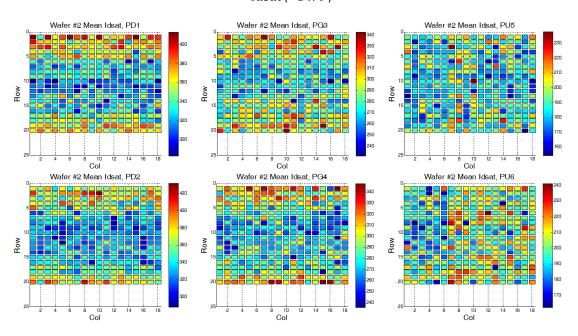

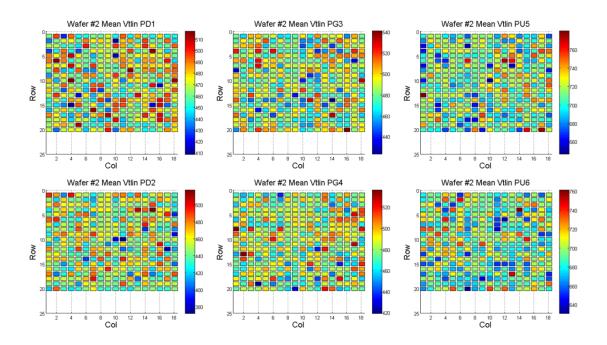

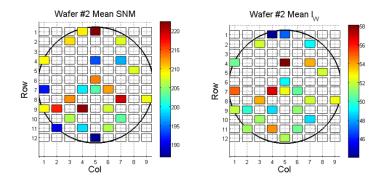

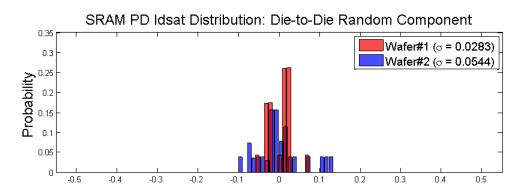

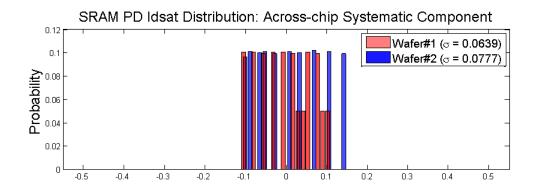

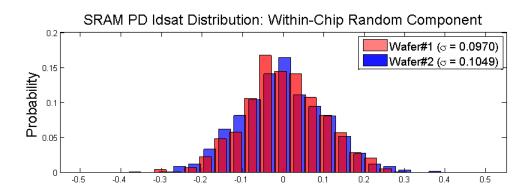

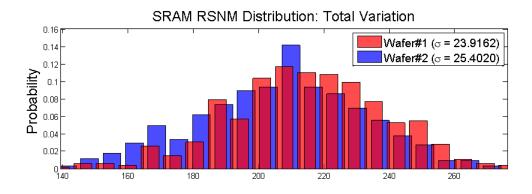

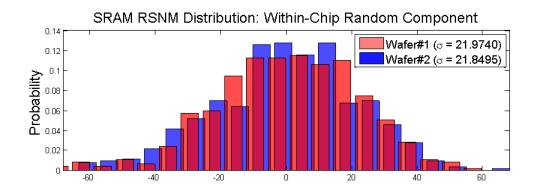

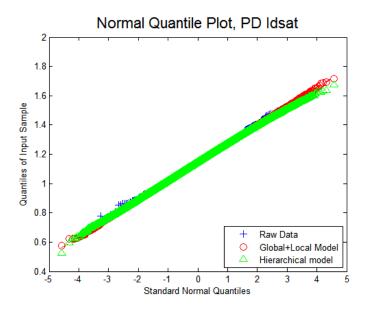

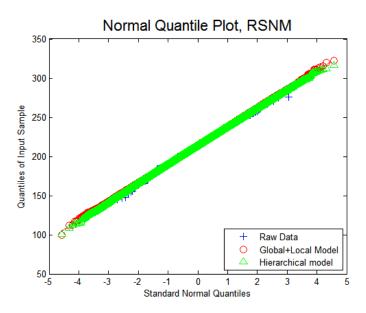

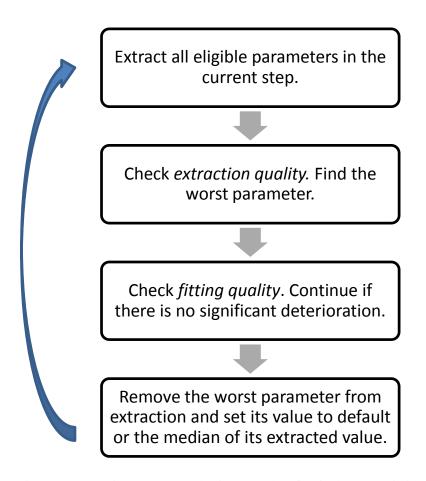

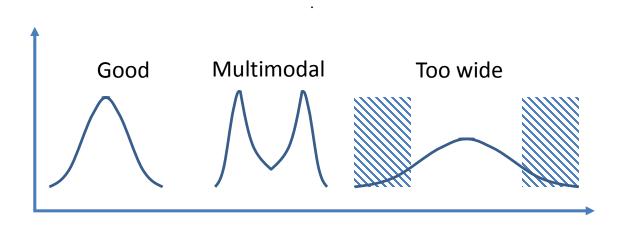

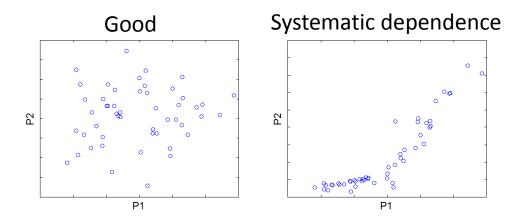

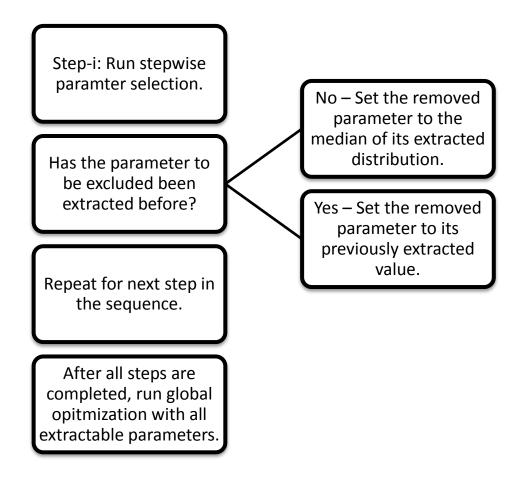

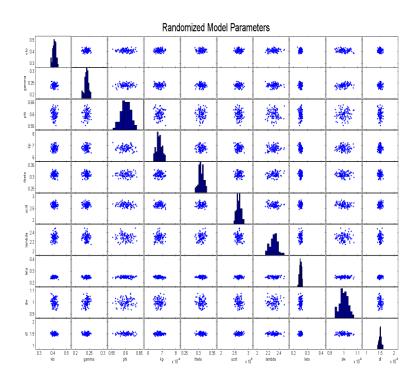

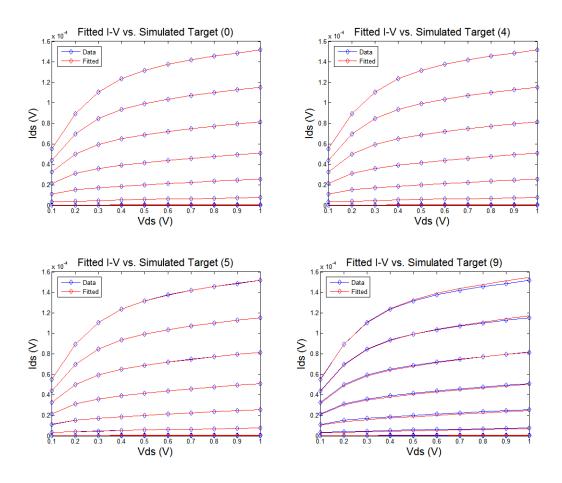

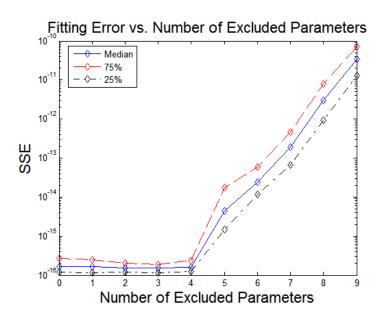

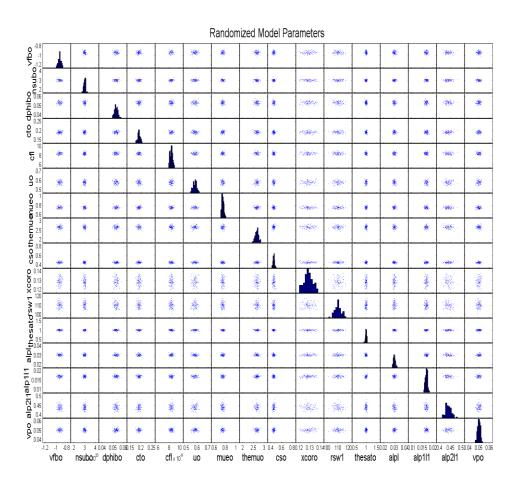

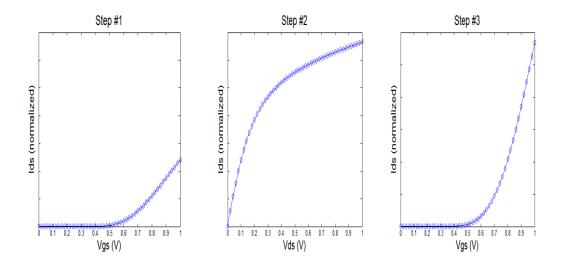

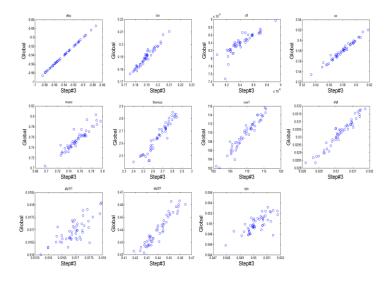

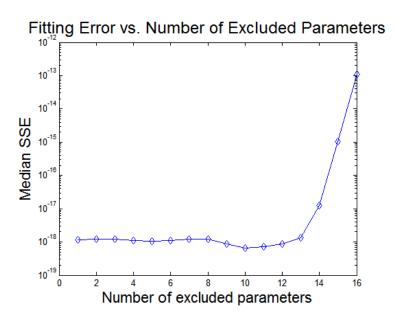

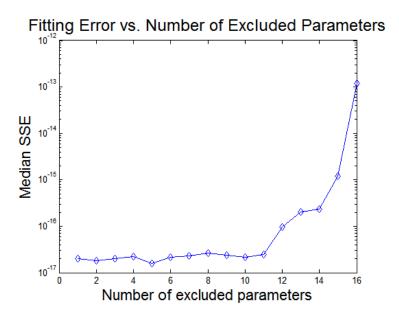

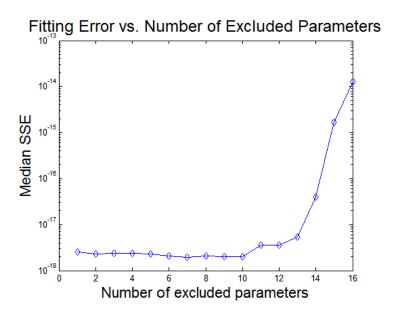

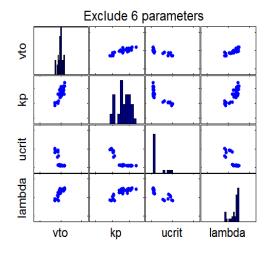

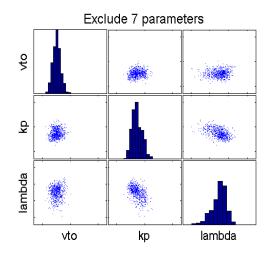

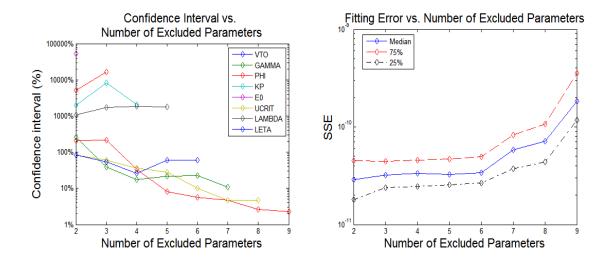

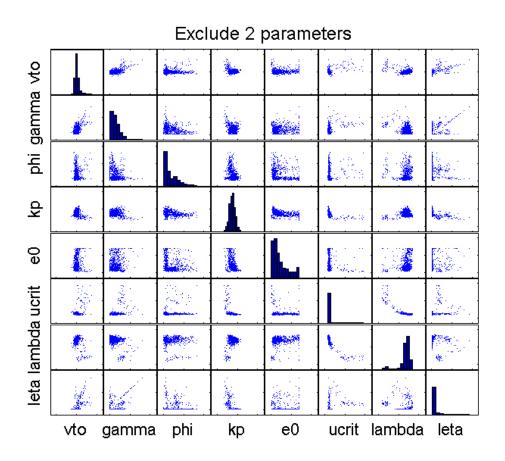

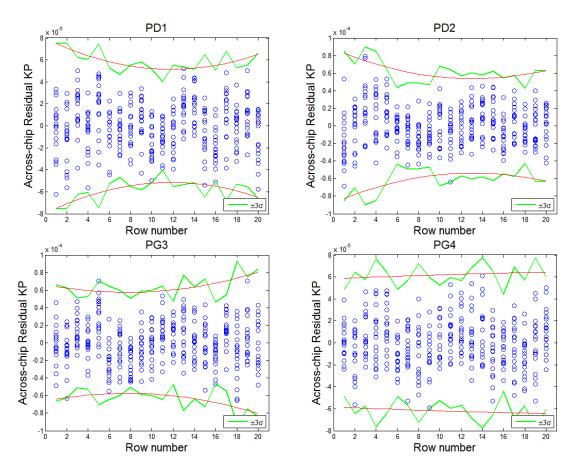

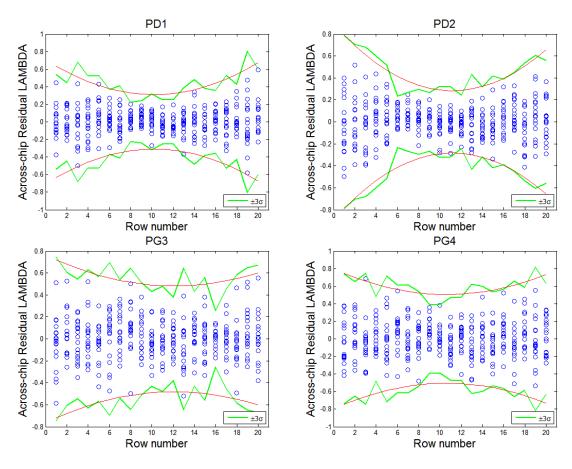

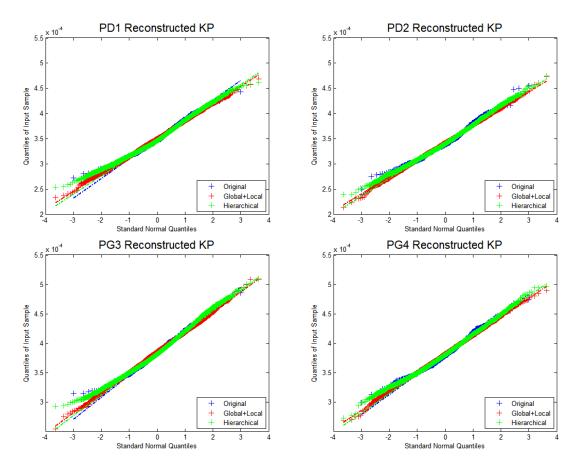

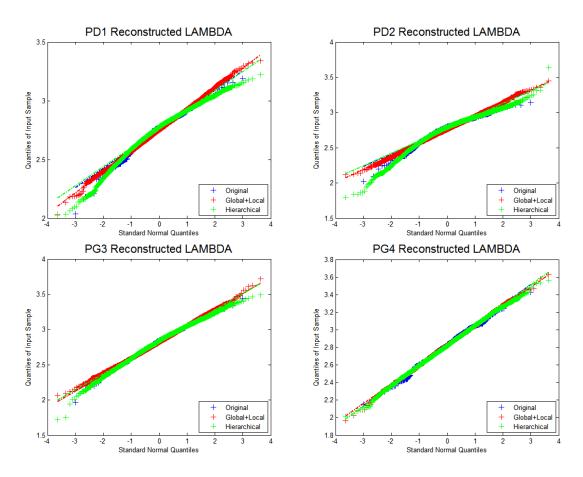

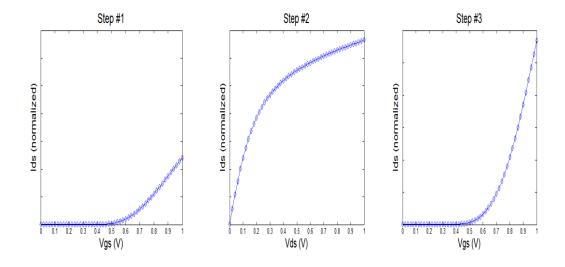

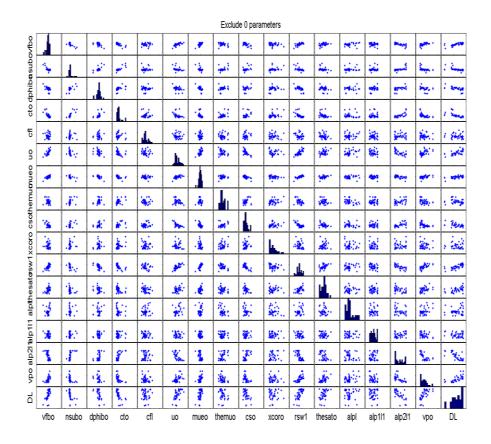

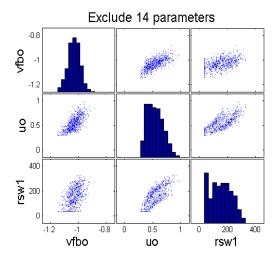

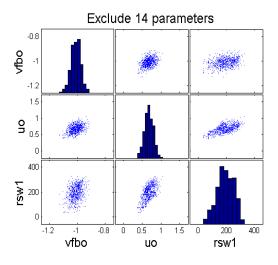

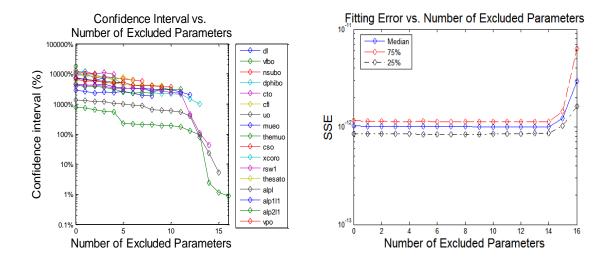

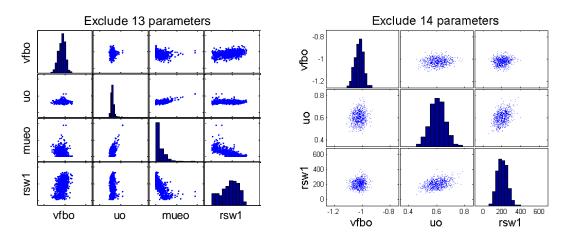

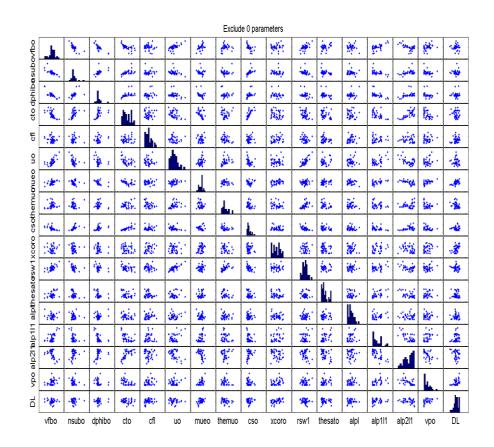

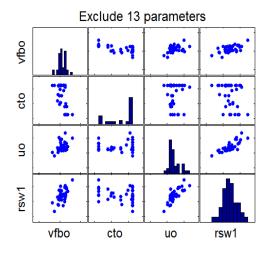

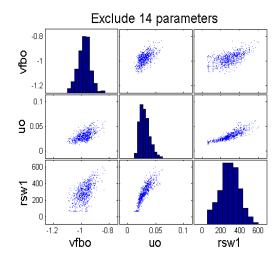

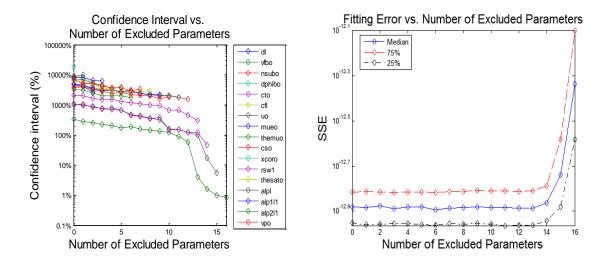

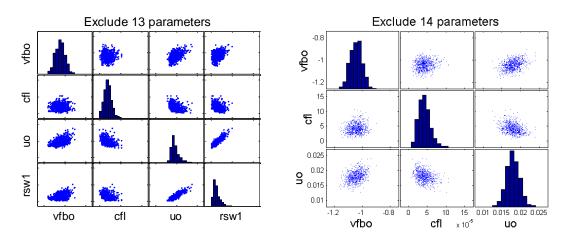

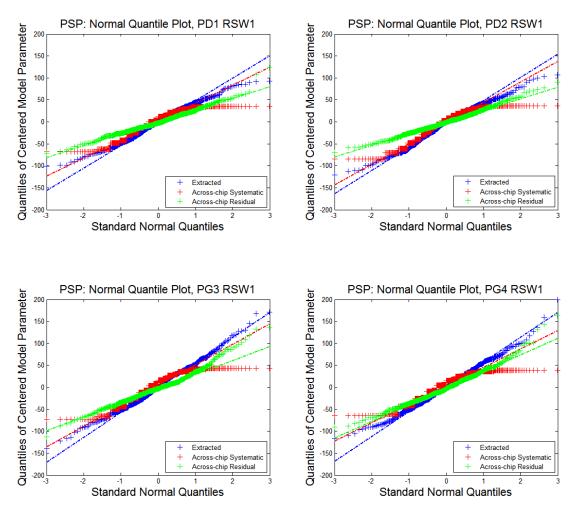

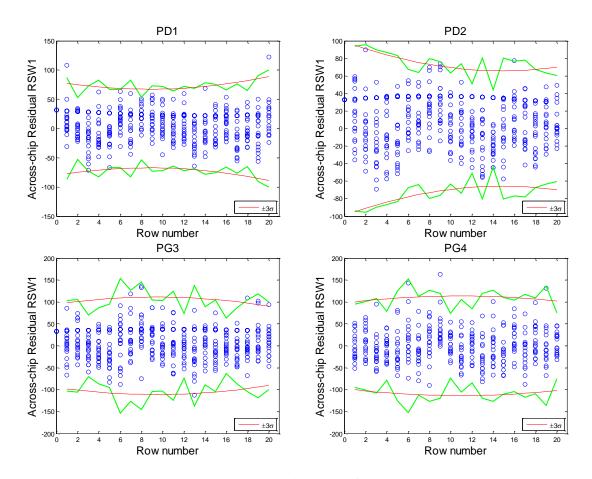

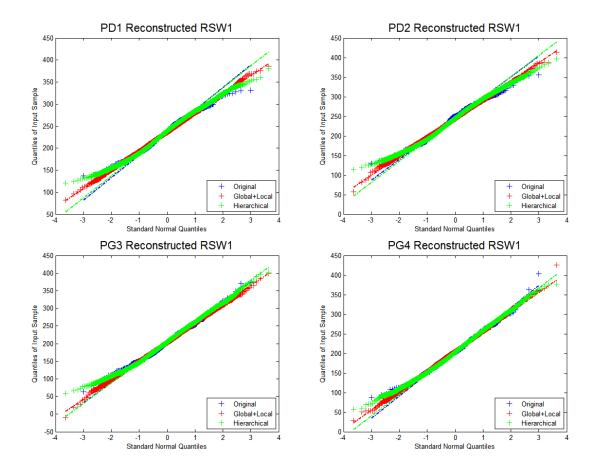

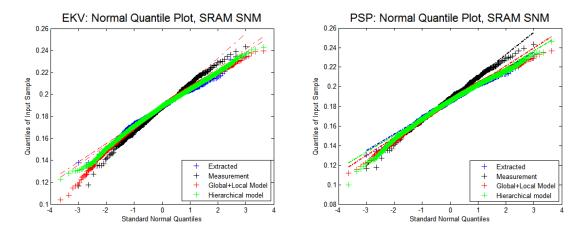

The same methodology as described in Section 3.2.3 is applied to compare the simple "Global+Local" model against the hierarchical variability model in this 45nm process. Distributions of delay and leakage from 10,000 chips with 8 tiles each are simulated in accordance with the actual measurement scheme with emphasis on the across-wafer variability and less so on the within-chip variations. Results of the Monte Carlo experiment are shown in Figure 3.32. Due to the strong systematic across-wafer variability, the delay distribution has a long tail on the slower end. The "Global+Local" model does not capture this behavior nearly as well as our hierarchical model: at  $-3\sigma$ , the estimate based on the simple model is as much as 18% lower than the measured delay, while the hierarchical model is consistently within 5% of the measurement at all key quantiles (Table 3.4). This is shows how ignoring systematic variability will bias estimates of the total variation in the process, possibly leading to pessimistic designs.