# UC Davis UC Davis Electronic Theses and Dissertations

### Title GPU Load Balancing

**Permalink** https://escholarship.org/uc/item/0t681813

**Author** Osama, Muhammad

Publication Date 2022

Peer reviewed|Thesis/dissertation

# GPU Load Balancing

By

### MUHAMMAD OSAMA DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

John D. Owens, Chair

Venkatesh Akella

Jason Lowe-Power

Committee in Charge

2022

Copyright © 2022 by Muhammad Osama All rights reserved. To my parents, Shahid and Fozia, my siblings, Umair and Sahar, and my fiancée Melissa.

# CONTENTS

| Tit | tle Pa      | ge            |                                                          | i    |  |  |

|-----|-------------|---------------|----------------------------------------------------------|------|--|--|

| Co  | Contents iv |               |                                                          |      |  |  |

| Lis | st of H     | Figures       |                                                          | viii |  |  |

| Lis | st of T     | <b>Fables</b> |                                                          | ix   |  |  |

| Lis | st of A     | Algorith      | ims                                                      | X    |  |  |

| Lis | st of I     | Listings      |                                                          | xi   |  |  |

| Ab  | ostrac      | t             |                                                          | xii  |  |  |

| Ac  | know        | ledgme        | nts                                                      | xiv  |  |  |

| 1   | Intro       | oductio       | n                                                        | 1    |  |  |

|     | 1.1         | Contril       | butions                                                  | 3    |  |  |

| 2   | Bacl        | kground       | 1                                                        | 5    |  |  |

|     | 2.1         | Graphi        | cs Processing Unit (GPU) Architecture                    | 5    |  |  |

|     |             | 2.1.1         | CUDA's Compute Hierarchy                                 | 5    |  |  |

|     |             | 2.1.2         | CUDA's Memory Hierarchy                                  | 6    |  |  |

|     |             | 2.1.3         | Impact on Load-Balancing                                 | 7    |  |  |

| 3   | A St        | irvey of      | GPU Load-Balancing Techniques for Irregular Applications | 9    |  |  |

|     | 3.1         | Related       | d Works                                                  | 10   |  |  |

|     |             | 3.1.1         | Compressed Sparse Data Structures                        | 11   |  |  |

|     | 3.2         | Taxono        | omy of GPU Load Balancing                                | 12   |  |  |

|     |             | 3.2.1         | Configuration: Static vs. Dynamic                        | 13   |  |  |

|     |             | 3.2.2         | Accuracy: Exact vs. Approximate                          | 14   |  |  |

|   |             | 3.2.3    | Granularity: Hierarchical vs. Flat             | 14               |

|---|-------------|----------|------------------------------------------------|------------------|

|   |             | 3.2.4    | Topology: Centralized vs. Distributed          | 15               |

|   |             | 3.2.5    | Communication: Cooperative vs. Non-Cooperative | 16               |

|   | 3.3         | Impler   | nentations of Load Balancing on GPUs           | 16               |

|   |             | 3.3.1    | Thread-Mapped                                  | 17               |

|   |             | 3.3.2    | Group-Mapped                                   | 18               |

|   |             | 3.3.3    | Work-Oriented                                  | 20               |

|   |             | 3.3.4    | Binning and Reordering                         | 22               |

|   |             | 3.3.5    | Task-Oriented Scheduling                       | 27               |

|   | 3.4         | Comm     | on Low-Level Algorithmic Primitives            | 33               |

|   |             | 3.4.1    | Challenge: Counting Non-zeros or Work Items    | 33               |

|   |             | 3.4.2    | Challenge: Searching for Work Tiles and Items  | 35               |

|   |             | 3.4.3    | Challenge: Efficient Binning of Work Items     | 36               |

|   |             | 3.4.4    | Challenge: Assigning Compute Resources         | 37               |

|   | 3.5         | Summ     | ary of Load-Balancing Techniques               | 37               |

|   | 3.6         | Optim    | izations Orthogonal to Load Balancing          | 40               |

|   |             | 3.6.1    | Kernel Strategy for Load-Balancing Operations  | 40               |

|   |             | 3.6.2    | Synchronization Avoidance                      | 42               |

|   |             | 3.6.3    | Shared Memory                                  | 43               |

|   | 3.7         | Conclu   | usion: A Look Ahead                            | 45               |

| 4 | A D.        | a ano ma | ming Model for GPU Load Balancing              | 47               |

| 4 | <b>4</b> .1 | U        |                                                | <b>4</b> 7<br>48 |

|   |             | C        |                                                |                  |

|   | 4.2         |          | Balancing Abstraction                          | 50               |

|   |             | 4.2.1    | Input from Sparse Data Structures              | 51               |

|   |             | 4.2.2    | Defining Load Balancing                        | 52               |

|   |             | 4.2.3    | Defining Work Execution                        | 53               |

|   | 4.3         | e        | Level Framework Implementation                 | 54               |

|   |             | 4.3.1    | Implementing Sparse Data Structures            | 54               |

|   |             | 4.3.2    | Implementing Load-Balancing Schedules          | 54               |

|   |     | 4.3.3   | Implementing Work Execution                   | 55 |

|---|-----|---------|-----------------------------------------------|----|

|   | 4.4 | Implen  | nentation Details                             | 57 |

|   |     | 4.4.1   | Flexible, Composable CUDA-enabled Ranges      | 57 |

|   |     | 4.4.2   | Implementing Non-Trivial Load-Balancing       | 59 |

|   |     | 4.4.3   | Application Space                             | 62 |

|   | 4.5 | Evalua  | tion                                          | 63 |

|   |     | 4.5.1   | Performance Overhead                          | 64 |

|   |     | 4.5.2   | Improved Performance Response                 | 65 |

|   |     | 4.5.3   | Lines of Code (LOC)                           | 67 |

|   | 4.6 | Related | d Work                                        | 68 |

|   | 4.7 | Conclu  | sion                                          | 70 |

| 5 | Wor | k-centr | ic Parallel Decomposition for GEMM on the GPU | 71 |

|   | 5.1 | Backgi  | round                                         | 74 |

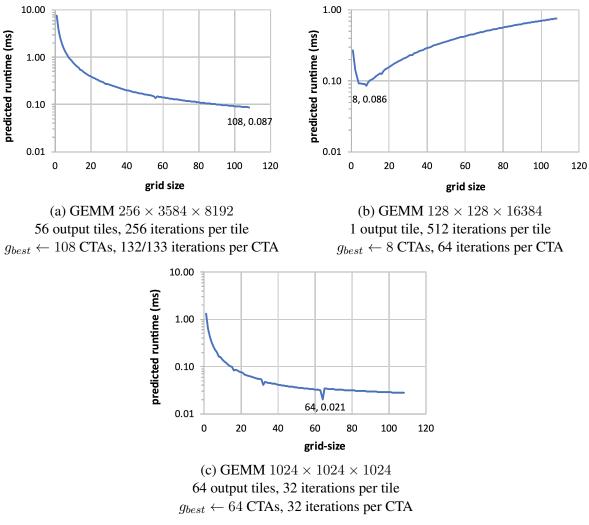

|   | 5.2 | Work I  | Decomposition Strategies                      | 76 |

|   |     | 5.2.1   | Sequential Cache-Blocked                      | 76 |

|   |     | 5.2.2   | Data-parallel                                 | 76 |

|   |     | 5.2.3   | Fixed-split                                   | 78 |

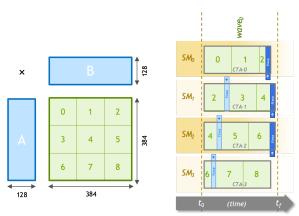

|   |     | 5.2.4   | Stream-K                                      | 78 |

|   | 5.3 | Implen  | nentation Details                             | 82 |

|   |     | 5.3.1   | Kernel Configuration                          | 83 |

|   |     | 5.3.2   | Data-parallel Hybridization                   | 87 |

|   | 5.4 | Perform | nance Evaluation                              | 88 |

|   | 5.5 | Conclu  | sion                                          | 93 |

| 6 | Con | clusion |                                               | 95 |

|   | 6.1 | Future  | Research Directions                           | 95 |

|   |     | 6.1.1   | Multi-GPU Load Balancing                      | 95 |

|   |     | 6.1.2   | Heuristics using Roofline Model               | 96 |

|   |     | 6.1.3   | Standardization of Sparse-Matrix Formats      | 97 |

|   |     |         |                                               |    |

| Reference | S                              | 100 |

|-----------|--------------------------------|-----|

| 6.1.6     | Beyond Today's CUDA            | 99  |

| 6.1.5     | Stream-K Abstraction           | 98  |

| 6.1.4     | Programming Model for Locality | 98  |

# 7 References

# LIST OF FIGURES

| 1.1 | Visualization of regular and irregular matrices                       | 3  |

|-----|-----------------------------------------------------------------------|----|

| 2.1 | Graphics Processing Unit (GPU) Architecture                           | 6  |

| 3.1 | Lower-bound search used for searching load balanced work              | 35 |

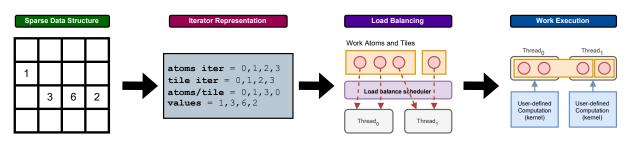

| 4.1 | Load balancing abstraction as a simple pipeline                       | 50 |

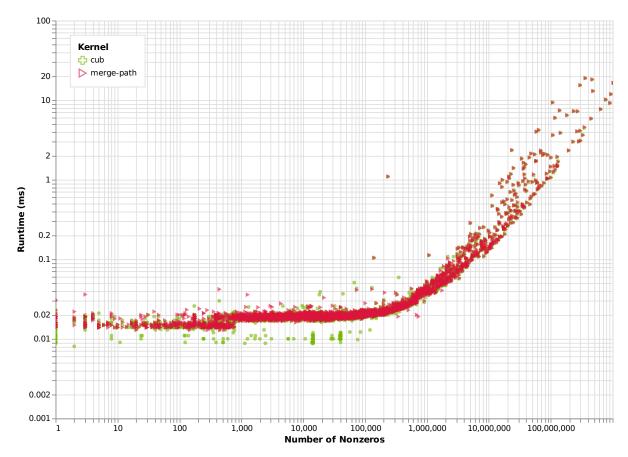

| 4.2 | Load balancing abstraction performance overhead analysis vs. CUB      | 64 |

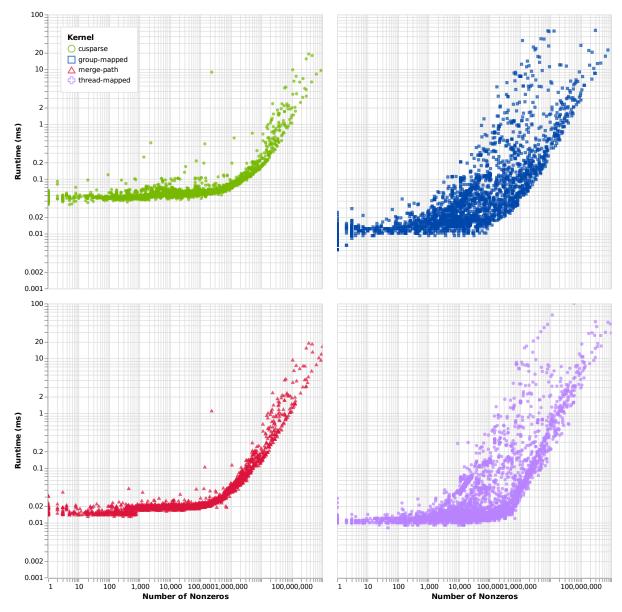

| 4.3 | Complete SpMV performance landscape with improvements                 | 66 |

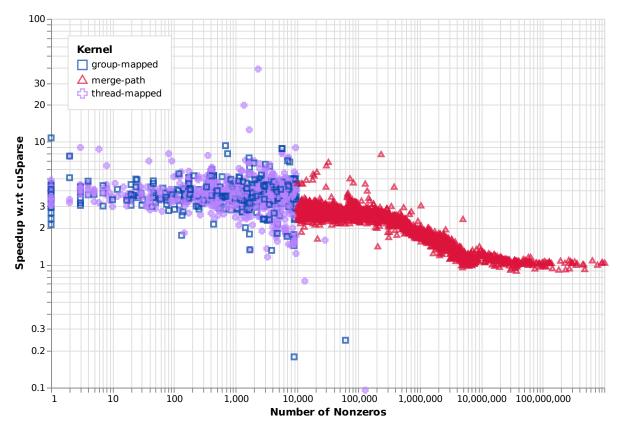

| 4.4 | Speedup of our framework's SpMV vs. cuSparse's SpMV                   | 67 |

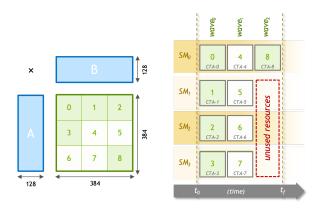

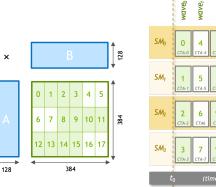

| 5.1 | Data-parallel execution schedules                                     | 72 |

| 5.2 | Tile-splitting execution schedules                                    | 73 |

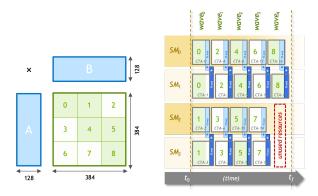

| 5.3 | Basic <i>Stream-K</i> vs. hybrid execution schedules                  | 82 |

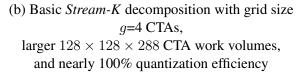

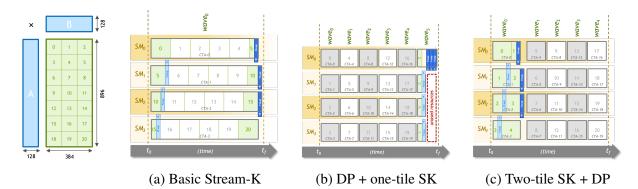

| 5.4 | Modeled <i>Stream-K</i> performance on NVIDIA A100                    | 85 |

| 5.5 | Strong-scaling comparison of <i>data-parallel</i> and <i>Stream-K</i> | 86 |

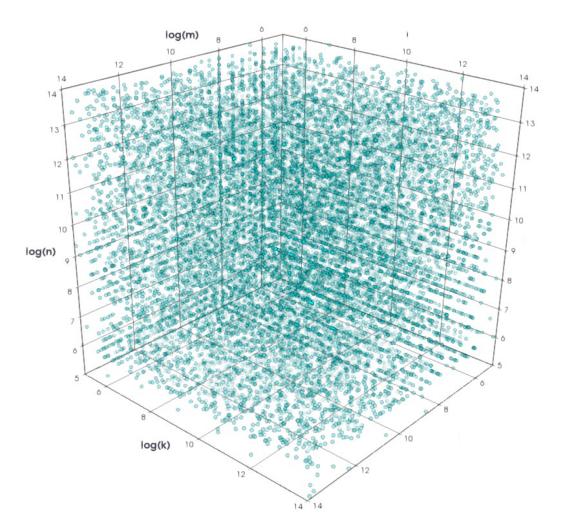

| 5.6 | The test domain of 32,824 GEMM problem shapes                         | 89 |

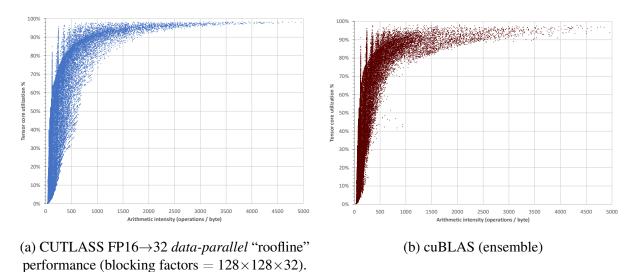

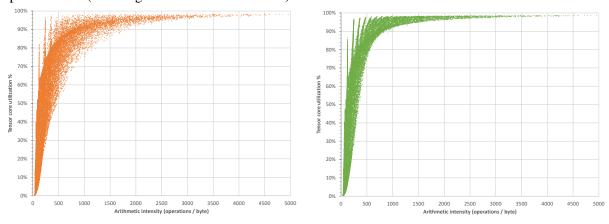

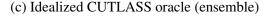

| 5.7 | FP16 $\rightarrow$ FP32 GEMM performance landscape                    | 90 |

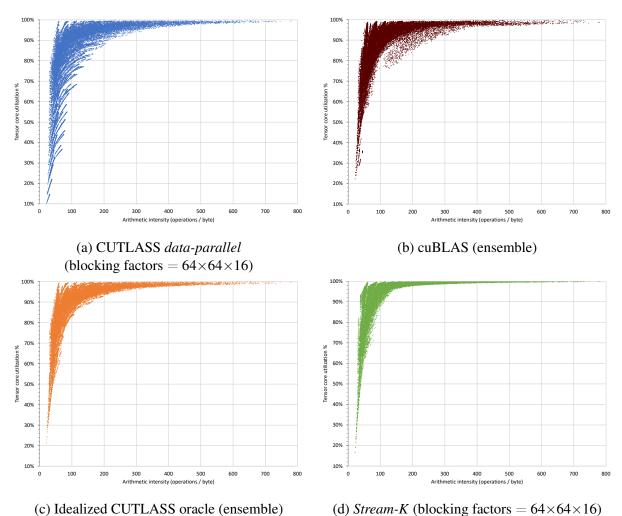

| 5.8 | FP64 GEMM performance landscape                                       | 91 |

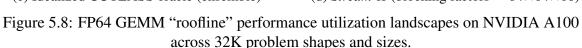

| 5.9 | Stream-K speedup vs. cuBLAS                                           | 93 |

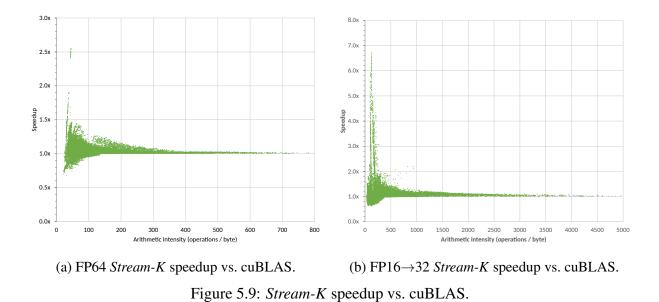

| 6.1 | Oracle SpMV vs. cuSparse's SpMV                                       | 97 |

# LIST OF TABLES

| 3.1 | Taxonomy of Load-Balancing techniques for GPUs             | 13 |

|-----|------------------------------------------------------------|----|

| 3.2 | Annotated bibliography of load-balancing techniques        | 38 |

| 3.3 | Annotated bibliography of load-balancing techniques        | 39 |

| 4.1 | Lines of code (LoC) comparison versus CUB                  | 68 |

| 5.1 | <i>Stream-K</i> FP64 Relative Performance                  | 92 |

| 5.2 | <i>Stream-K</i> FP16 $\rightarrow$ 32 Relative Performance | 92 |

# LIST OF ALGORITHMS

| 1  | SpMV using thread-mapped scheduling                        | 18 |

|----|------------------------------------------------------------|----|

| 2  | SpMV using group-mapped scheduling                         | 20 |

| 3  | SpMV using work-oriented scheduling                        | 23 |

| 4  | SpMV using binning-based scheduling                        | 26 |

| 5  | BFS using queue-based scheduling                           | 29 |

| 6  | Sequential cache-blocked GEMM                              | 77 |

| 7  | Data-parallel GPU GEMM                                     | 78 |

| 8  | CTA-wide MacLoop() subroutine                              | 79 |

| 9  | <i>Fixed-split</i> GPU GEMM with splitting factor <i>s</i> | 80 |

| 10 | Basic Stream-K GPU GEMM with grid size g                   | 81 |

# LIST OF LISTINGS

| 4.1 | CSR format expressed within our framework              | 55 |

|-----|--------------------------------------------------------|----|

| 4.2 | Thread-mapped load-balancing algorithm                 | 56 |

| 4.3 | SpMV implemented within our load-balancing abstraction | 58 |

| 4.4 | Load-balanced SpMM computation                         | 62 |

| 4.5 | SSSP graph primitive implementation                    | 63 |

| 6.1 | An example of generic SpMV.                            | 98 |

#### ABSTRACT

#### **GPU Load Balancing**

Fine-grained workload and resource balancing is the key to high performance for regular and irregular computations on the GPUs. In this dissertation, we conduct an extensive survey of existing load-balancing techniques to build an abstraction that addresses the difficulty of scheduling computations on the GPU.

We propose a GPU fine-grained load-balancing abstraction that decouples load balancing from work processing and aims to support both static and dynamic schedules with a programmable interface to implement new load-balancing schedules. Prior to our work, the only way to unleash the GPU's potential on irregular problems has been to workload-balance through application-specific, tightly coupled load-balancing techniques. With our open-source framework for load-balancing, we hope to improve programmers' productivity when developing irregular-parallel algorithms on the GPU, and also improve the overall performance characteristics for such applications by allowing a quick path to experimentation with a variety of existing load-balancing from work processing within our abstraction, managing and extending existing code to future architectures becomes easier.

Using our insights from load-balancing irregular workloads, we build *Stream-K*, a workcentric parallelization of matrix multiplication (GEMM) and related computations in dense linear algebra. Whereas contemporary decompositions are primarily tile-based, our method operates by partitioning an even share of the aggregate inner loop iterations among physical processing elements. This provides a near-perfect utilization of computing resources, regardless of how efficiently the output tiling for any given problem quantizes across the underlying processing elements. On GPU processors, our *Stream-K* parallelization of GEMM produces a peak speedup of up to  $14 \times$  and  $6.7 \times$ , and an average performance response that is both higher and more consistent across 32,824 GEMM problem geometries than state-of-the-art math libraries such as CUTLASS and cuBLAS. Furthermore, we achieve this performance from a *single* tile size configuration per floating-point precision, whereas today's math libraries employ complex kernel-selection heuristics to select from a large ensemble of kernel variants.

#### ACKNOWLEDGMENTS

I owe my deepest gratitude to my advisor John D. Owens. He gave me the opportunity and the freedom to seek exciting research and become who I am today. His enthusiasm for research and admiration of his students made the last seven years of my life truly exciting and endearing. He has helped me find my own style of research, writing and mentoring, and these are the best gifts anyone can ever hope to receive. Thank you John, you taught me how to look for and attempt to solve challenging problems, and I am honored to have been a part of your exceptional research family.

Over the years, I also had the pleasure of learning and discussing research with remarkable individuals. Through early part of my Ph.D., Yuechao Pan and Yangzihao Wang mentored me and taught me much of what I know about parallel programming, graphical processing units (GPUs) and graph analytics. During the later half I had the pleasure of learning from Serban D. Porumbescu, a terrific post graduate of our research group. Since joining our group, Serban has been a key resource and has helped me not just with the academic but also personal and professional matters. He is also responsible for helping me edit many of my research works, and I will forever be grateful for the time that he has spent making my graduate school experience truly extraordinary.

Among the folks in the industry, I was lucky enough to learn CUDA from the CUDA architect himself, Stephen Jones! Stephen has always been a great friend to the group, but has been especially kind to me and taught me the value of good software design and engineering. From Duane Merrill and Cris Cecka I learned everything about low-level optimizations and writing high-performance GEMM kernels. I also had the chance to work with Michael Garland, with whom I enjoyed fruitful discussions that led to many significant design decisions within my research.

I truly enjoyed working with my co-authors and collaborators: Jonathan Wapman, Carl Yang, Minh Truong, Chenshan Yuan, Leyuan Wang, Weitang Liu, Andrew Davidson, Yuduo Wu, Andy T. Riffel, Aydin Buluç, Toluwanimi Odemuyiwa, Cameron Shinn, Collin Michael McCarthy, and Saurav Muralidharan. I also would like to thank my students Minh Truong, Jonathan Wapman, Daniel Loran, Cameron Shinn and Annie Robison, who I had the pleasure of mentoring as they found their own place within the research group. It was a privilege.

Among the terrific people already mentioned, I would like to add the rest of my outstanding colleagues, with whom I have spent large parts of the last seven years: Muhammad Awad, Kerry Seitz, Afton Geil, Agnieszka Łupińska, Saman Ashkiani, Vehbi Eşref Bayrktar, Ahmed H. Mahmoud, Yuxin Chen, Zhongyi Lin, Radoyeh Shojaei, Chuck Rozhon, Matthew Drescher, Shalini Venkataraman, Nima Johari and Teja Aluru. I am fortunate to have experienced the influence of so many talented and hardworking people in my life.

I would also like to extend my gratitude to Prof. Venkatesh Akella, Prof. Soheil Ghiasi, Jason Lowe-Power and Sean Treichler for dedicating their time and attention to be a part of my qualification exam committee, and also Prof. Akella and Jason for further providing me with feedback and guidance on my dissertation. Additionally, I would like to thank Sean and Aamer Jaleel for dedicating an hour out of their busy schedule every week for months to give feedback on mine and my colleagues' research works. I also wish to thank the past and current UC Davis ECE staff, who always work hard to remove frictions from the path of students and professors, and enable us to focus on our research. Among the staff, I especially thank Sacksith Ekkaphanh, Phil Young, Fredrick P. Singh, Jennifer Y. Torres, Carole Bustamante, and Michelle T. Walker.

Graduate school would be way too stressful without friends, and I have been lucky enough to have a lot of wonderful friends that helped me get through some of the most stressful times with lots (and lots) of distractions. The RPG, anime and manga theory crafting with Aaron Feaster and Thea Tesoro, the Dungeon & Dragons sessions and the countless hours<sup>1</sup> spent playing Destiny and Overwatch with Nate Bryant, Jesse Navarro, Christian Perry, William "Billy" Lucas, Krestine Whaley, Jace Locario and Tiffany Simonet, and the League of Legends games with Megan Vieira. My late friend Pierre "Link" Schreurs, dearly missed, who's absurdity and jokes always made us laugh till we had tears in our eyes. Thank you all for being the best of friends.

I extend my love and gratitude to my fiancée, Melissa Vieira. Despite the distance that separated us during these years, you have supported me with your love and joy. I am lucky to have you and truly excited to spend the rest of my life with you.

<sup>&</sup>lt;sup>1</sup>Please don't tell John.

My research would not have been possible without the financial support from the National Science Foundation (SI2-SSE), the Defense Advanced Research Projects Agency (XDATA, HIVE and Symphony), the United States Geological Survey Agency (USG23), equipment donations from NVIDIA and their funding of an NVIDIA AI Lab at UC Davis, and a 2022 UC Davis ECE Dissertation Fellowship.

And finally, to my family—I am what I am today because of you. I thank my parents, Shahid and Fozia, who have worked tirelessly throughout their lives, foregoing personal pleasure to raise me and my sibilings with all the love, care and support in the world, and who always taught us to learn and unravel the secrets of this world. I thank my sister, Sahar, who continues to be the symbol of patience and courage, which I needed to chase after my dreams. I thank my brother, Umair, who ever since I was a kid, has been my role model—your hardwork, passion and persevarence has led me down a path of excellence. I thank my sister-in-law and brother-in-law, Maria and Rameez, for their support and love. I thank my niece and nephews, Hadiya, Hashir, Musab, and Mahad, who are my sweet little bundles of joy and my source of happiness. Whatever I did to deserve you, it could not have been enough.

Thank you.

# Chapter 1 Introduction

Graphics Processing Units (GPUs), born out of the needs of graphics for games, dealing with vertices that make up triangles and subsequent fragments generated by the rasterizer, have evolved to be more general-purpose and programmable. GPUs now excel in many other domains beyond graphics, such as machine learning applications, graph analytics, sparse linear algebra, real-time interactive media, physical simulations, and bioinformatics. GPUs are used as a staple for accelerating data-parallel workloads within these domains, where parallelism is exploited by operating on multiple elements of data simultaneously.

Data parallelism within these application domains can be classified based on the granularity of work, where granularity (or grain size) is a measure of the amount of work performed by each task [44]. *Fine-grained* data parallelism is present when the granularity of work is much smaller than the entire problem. The problem is broken down into smaller components with small amounts of computations that map well to less sophisticated processing elements. Computations between fine-grained components have high communication overhead, and the impact of workload imbalance among processing elements is fairly large. *Coarse-grained* data parallelism is present when a program is broken down into a small number of large, computationally intensive tasks, and between the tasks, there is low communication overhead [44]. Due to their large number of cores and their throughput-oriented design, modern GPUs excel at processing fine-grained data-parallel tasks. NVIDIA's GA100 GPU, for example, boasts 128 Streaming Multiprocessors (SMs) with 8192 total cores and High Bandwidth Memory (HBM) to keep the cores fed with data, both promoting fine-grained parallelism [71].

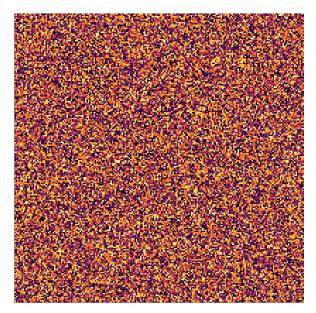

In this dissertation we take a closer look at two categories of fine-grained parallel work, *reg-ular* and *irregular* computations, and explore the fundamental underlying software technology that allows these computations to run efficiently on the GPU architecture: load balancing. In this context, a computation is defined to be regular when the neighboring processing elements have similar or identical workloads. In contrast, a computation is irregular when neighboring processing elements have varying amounts of work to process. Figure 1.1a shows an example of a dense matrix used in a General-Matrix Multiplication (GEMM) computation, a regular workload where the partition of the work can be statically and trivially determined, such that each processing element performs identical amounts of reads, writes, and multiply-accumulate instructions. In contrast, Figure 1.1b visualizes a graph represented as a sparse matrix used in sparse-linear algebra operations such as Sparse-Matrix Multiplication (SpMM), an irregular workload where each processing element has varying amounts of reads, writes, and nonzero values to process, and thus an inherent load imbalance within the dataset.

To leverage fine-grained parallelism within regular and irregular computations on a GPU, we attempt to maximize the available memory bandwidth and compute throughput. For computebound, regular problems such as GEMM, the predominant approach is to find the optimal size of chunks of the complete workload, which efficiently utilizes the GPU memory hierarchy, and map that onto the GPU cores in oversubscribed "waves" of work. These waves get scheduled onto the GPUs as resources become available until all waves/work is completed. In practice, the last wave of scheduled work often underutilizes the GPU, causing millions of instructions to parallelize over only a small subset of the total available cores. In contrast to prior approaches, which built complicated heuristics selecting different chunk sizes for the waves of work to better utilize the device, this dissertation addresses the *resource imbalance* problem for GEMM by instead balancing the total available work to a fixed, device-filling number of processing elements. Our approach is a generalization of previous parallel decompositions and removes the need for complicated heuristics for kernel selection for GEMM (and other regular problems alike).

For *irregular* computations, however, the irregularity within the program loop-structure or the data itself varies tremendously, making it difficult to find *one* parallel decomposition that

(a) An example dense matrix of size 2048×2048

used as an input to linear layer of a ConvNeXt architecture [59]. In a dense matrix-matrix

multiply (GEMM), all values of this matrix will be consumed, with neighboring threads each processing an identical number of elements.

(b) Xyce circuit simulation matrix (graph) of size 321,671×321,671 with 1,316,085 nonzero values irregularly distributed [29]. If this data is stored in a typical sparse-matrix format (e.g., CSR), only nonzero values will be consumed, and the varying amount of work per matrix row means that a straightforward mapping to a GPU results in neighboring threads consuming different amounts of work.

Figure 1.1: Visualization of regular and irregular matrices.

balances all problems onto available GPU resources. Instead, there is an inherent tradeoff between the quality of the balance and the amount of extra work needed to compute the workload balance. This dissertation addresses the *workload balancing* problem for irregular workloads with a load-balancing abstraction, which separates workload mapping from work execution. We argue and demonstrate that this is the superior approach to building high-performance kernels for irregular applications as it promotes reuse of existing load-balancing techniques and facilitates improved portability and programmability.

# **1.1 Contributions**

This dissertation makes several contributions to the areas of load balancing regular and irregular computations on the GPU.

- We conduct a survey of current load-balancing techniques used for sparse-irregular applications (Chapter 3).

- We present our GPU load-balancing abstraction that promotes the separation of concerns between workload mapping and work execution. Our GPU load-balancing framework reconstructs existing application-dependent techniques that address irregularity to be more general, portable, and programmable (Chapter 4).

- We provide a solution to the *resource balancing* problem for dense-regular computations such as GEMM. Our approach provides improved performance compared to highly-optimized vendor library, cuBLAS, generalizes existing solutions and removes the need for complicated heuristics to select the right set of tile sizes and shapes when scheduling (Chapter 5).

# Chapter 2

# Background

# 2.1 Graphics Processing Unit (GPU) Architecture

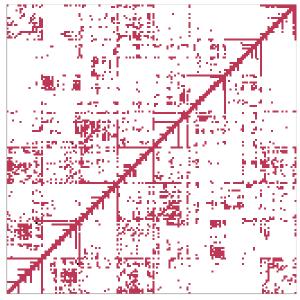

Modern GPU architectures feature two separate hierarchies, one targeted at the individual processing cores organized into a parallel compute hierarchy (Figure 2.1b) and the second targeted at the memory scopes such as L1 and L2 cache, programmable shared memory, and global memory, all organized into a memory hierarchy (Figure 2.1a). Using NVIDIA's popular Compute Unified Device Architecture (CUDA) programming model for parallel computing, the compute and memory hierarchies are exposed for programmers to build general-purpose computing applications for GPUs. In this chapter, we provide a brief overview of CUDA's compute and memory hierarchies and highlight their significance for load balancing.

### 2.1.1 CUDA's Compute Hierarchy

The compute hierarchy within the CUDA programming model leverages multiple compute "perspectives" that get mapped onto physical streaming multiprocessor cores (SMs) on the GPU. The SMs feature a *Single Instruction Multiple Thread (SIMT)* programming model to achieve multithreaded data-parallel execution [24]. CUDA further expands the compute hierarchy within the SMs using a software abstraction of threads, the smallest unit, grouped to create larger compute perspectives like a warp, a block, and more. Figure 2.1b illustrates how a CUDA grid, mapped onto the physical SM, is broken down into a number of compute perspectives. The finer-grained perspectives within the hierarchy allow us to do more flexible, higher-performance communication when compared to coarser-grained perspectives. The following list summarizes

(a) **CUDA's Memory System** NVIDIA A100 sizes for global memory, L1- and L2-caches, registers used as an example.

(b) **CUDA's Compute Hierarchy** Shows how a kernel is mapped onto the individual threads of a CUDA grid.

Figure 2.1: GPU architecture illustrated as CUDA's memory system and compute hierarchy.

each of these perspectives and their purpose:

- **Thread** The smallest processing unit. Each thread runs an instance of a GPU program called a *kernel*.

- Warp 32 CUDA threads that run in lockstep. Threads in a warp are divergent-free, and run in a Single Instruction Multiple Data (SIMD) fashion.

- **Block** A block or Cooperative Thread Array (CTA) in a GPU is a group of threads that cooperate together to process a slice of data in an algorithm and map onto the same Streaming Multiprocessor (SM). Multiple blocks may run on the same SM concurrently.

- Clusters A thread block cluster is a collective of blocks, co-scheduled on adjacent SMs.

- Grid The collection of all blocks that run on all the SMs in a single device.

### 2.1.2 CUDA's Memory Hierarchy

The CUDA memory model is similar to modern CPU architectures. It features *L1- and L2-cache*, with varying caching policies and traits depending on the GPU architecture. It also features the following list of programmable memory scopes:

- Global Memory An off-chip memory shared by all SMs.

- Shared Memory Fast on-chip memory shared among different threads in a single block, but not between blocks. Shared memory is limited per SM and is often used to store data that is accessed across an entire block. On some architectures, shared memory shares the same pool of memory as the GPU's L1 cache and the programmer may specify how much of this pool to assign to cached vs. explicit data storage.

- **Registers** Any scalar variables declared within the scope of a kernel are by default stored within registers. Register data is only visible locally at the thread-level scope. It is the fastest memory in a GPU.

### 2.1.3 Impact on Load-Balancing

High-performance implementations of fine-grained parallel workloads require programmers to design their kernels with the previously described compute and memory hierarchies in mind. Warps' SIMD execution model is hardware-efficient and is a great match for many workloads. However, it forces programmers to avoid any discrepancies in instructions between the neighboring threads within the same warp. Load-balancing techniques must ensure that threads within the same warp have approximately the same amounts of work to process as well as the same set of instructions. At a block level, NVIDIA's hardware scheduler also plays an important role in scheduling blocks to the underlying SM as resources become available. Work scheduled to the GPU is often oversubscribed to its resources, therefore, the blocks get scheduled out as they finish their set of work with new blocks assigned to keep the GPU fully utilized. Programmers often spend time balancing the workload for a given block (or various compute hierarchies) and then rely on the hardware scheduler or the data workload distribution itself to balance the resources of an SM to a given problem. We discuss this and other load-balancing techniques in detail in Chapter 3.3.

Memory hierarchy also plays a significant role in optimizing kernels, where the most important consideration is minimizing the memory accesses required to access data at a thread-level granularity. This includes coalesced memory accesses, where multiple memory accesses are grouped into a single transaction. However, many irregular problems inherently result in uncoalesced loads and stores where the accesses become serialized; this is due to the sparse or random access nature of these workloads. For both regular and irregular workloads, memory hierarchy is utilized to reduce the number of off-chip (global memory) accesses needed by caching the accesses to L2/L1, registers, and the shared memory.

# Chapter 3

# A Survey of GPU Load-Balancing Techniques for Irregular Applications

Graphical Processing Units (GPUs) excel at and are generally designed for regular fine-grained parallel problems, such as General Matrix Multiplication (GEMM). In regular problems like GEMM, neighboring threads have similar or identical workloads and often achieve nearly 100% of peak GPU theoretical performance. What is much more challenging is an application with ample *fine-grained* parallelism but *irregular* parallelism. In such applications, neighboring threads running in a lockstep fashion will have different workloads—perhaps different amounts of work—making an efficient implementation on a highly parallel machine like a GPU a significant challenge.

Consider Sparse-Matrix Vector Multiplication (SpMV), a critical kernel within scientific computing for sparse linear algebra and sparse eigenvalue solvers [31]. A sparse matrix **A** and a dense vector x defined as inputs, SpMV computes the output vector  $y = \mathbf{A}x$  and is an example of irregular fine-grained parallelism. Unlike in GEMM, the sparse matrix in SpMV can contain irregularity within the rows of the matrix: the rows of the matrix can have different numbers of non-zero entries. A simple mapping of one row to each GPU thread can expose this irregularity, where the neighboring threads may get different amounts of non-zeros to process, causing threads within the same warp<sup>1</sup> to wait on threads with large amounts of non-zeros. The

<sup>&</sup>lt;sup>1</sup>Reminder: A CUDA warp is a collection of 32 threads that execute instructions in lockstep. Threads in a warp are divergent-free, and run in a Single Instruction Multiple Data (SIMD) fashion.

imbalance created due to this irregularity—specifically, when the work is not equally distributed among the parallel actors, and consequently, some actors are idle while others do more work is defined as the load imbalance problem. Current approaches to addressing the load-imbalance problem is by distributing the work evenly among threads using sophisticated load-balancing techniques.

In this survey, we look at these fine-grained GPU load-balancing techniques that are used to date to implement high-performance kernels for irregular applications such as graph algorithms (Breadth-First Search), sparse-linear algebra (Sparse-Matrix Multiplication), and many others. But this problem is not specific to GPUs alone. In the past several decades, researchers have proposed many solutions to load imbalance for SIMD and SIMT programming models alike [10, 12, 58]. However, given the prevalence of GPUs, their unique compute and memory model (see Chapter 2), this work addresses the need for a broad understanding of the literature space. Our contributions are the following:

- 1. A taxonomy of GPU load-balancing techniques to categorize the load-balancing algorithms (Section 3.2).

- 2. A deeper dive on key techniques that appear in the literature (Section 3.3).

- 3. An understanding of implementation details and building-block algorithms required to implement these techniques (Section 3.4).

The irregularly-parallel workloads we encountered in our survey predominantly focus on sparse linear algebra (with problems such as sparse-matrix dense-vector multiplication, sparse-matrix sparse-matrix multiplication), graph analytics (with algorithms such as breadth-first search, single-source shortest path, triangle counting, and general graph analytics programming abstractions), and computer graphics (ray traversal).

### **3.1 Related Works**

To the best of our knowledge, only one other paper from 2017 conducts a survey of GPU loadbalancing techniques [16]. Busato and Bombeiri explain some of the key techniques used at that time to implement load balancing on older GPU architectures, and provide and performance, power and energy analysis on a small subset of sparse datasets. Contemporary to Busato and Bobeiri's approach, our survey not only updates the load-balancing survey literature with new and old techniques, but also provides a deeper dive into their implementations and the underlying low-level primitives. We also build a fine-grained GPU load balancing taxonomy to characterize any current or future load-balancing algorithms.

### **3.1.1** Compressed Sparse Data Structures

Irregularly-parallel applications often operate on *sparse* datasets, or datasets in which a significant portion of the data consists of "zero" values that make up the bulk of the data in the data structure, but that would be wasteful to store. Sparse data formats allow the programmer to both store the data more efficiently in memory by omitting explicit "zero" values as well as access the data more efficiently once it is in a sparse format without performing useless work. Since many sparse workloads are bandwidth-bound rather than compute-bound, the cost of moving data into the GPU's memory hierarchy is a key factor in determining the performance of a sparse workload. In fact, load balancing is often a function of making sure that all processors are *reading or writing* equal amounts of data rather than performing arithmetic on equal amounts of data. Performant sparse data formats commonly group logically-adjacent work items in memory so that they can be read or written in a single memory transaction, so that elements within a group share data (such as row or column metadata), or so that the size of all groups in the data structure are equal. In this section we describe a few common compressed data structures that are used to represent these datasets.

First, consider a matrix where only a handful of the elements are non-zero. We can represent this matrix as a *COO* (coordinate) format, which is a simple list of nonzero elements. Each element is stored as a tuple of row, column, and value. These tuples are often sorted first by row and then by column within each row, but this step is optional. The COO format works well when the programmer simply wants to split nonzeros into multiple groups.

The primary downsides of the COO format are that it uses more space than necessary due to explicitly-stored row and column indices for each nonzero, and it is computationally expensive to perform queries on the matrix, especially if it is unsorted by row and column. For example, determining the number of nonzeros in a row requires an iteration over the list, as do random accesses into the matrix. To solve this problem, we can use the Compressed Sparse Row (CSR) format, which is a more space-efficient format that stores nonzero elements in a compressed format. CSR uses a simple row-major list of nonzero column indices and values, as well as a prefix-sum that stores a running total of the sum of the nonzeros in all previous rows. Compared to COO, this eliminates the need for row index storage, allows kernels to quickly determine the number of nonzeros in each row with a single subtraction operation, and enables faster random or iterative accesses into a given row.

There are many other alternative data structures that typically require more preprocessing, as described in Table II by Fillipone et al. [31]. In general, preprocessed formats are a form of static load balancing, where the programmer analyzes how the data will be accessed and uses this information to optimize the data structure, with an assumption that the cost of preprocessing the data format will pay off on net, either by amortizing the preprocessing cost over many computations or by significantly speeding up the computation. In this work we primarily focus on CSR and COO formats in part because they are the most common formats used in sparse linear algebra on GPUs, and in part because they represent two different ways of organizing data with opposing trade-offs. COO is a list of coordinate/value tuples, where the programmer can easily subdivide the data structure based on an equal split of nonzeros, but where the cost to access information about the row the nonzero is a part of is more expensive. In contrast, CSR is a compressed format allows the programmer to pay an additional cost to load balance *across* rows or access a random nonzero element.

### 3.2 Taxonomy of GPU Load Balancing

This section focuses on building a taxonomy of GPU load balancing. Our goal with this taxonomy is to (1) characterize existing load-balancing techniques found in GPU literature (see Section 3.3 for a deeper-dive on implementations, Section 3.4 for a study on common lowlevel algorithmic primitives used for load-balancing, and 3.5 for a complete summary), and (2) provide an abstraction to classify future works searchability.

| Configuration | Accuracy    | Granularity | Communication   | Topology    |

|---------------|-------------|-------------|-----------------|-------------|

| Static        | Exact       |             | Cooperative     | Centralized |

| Dynamic       | Approximate |             | Non-Cooperative | Distributed |

Table 3.1: Taxonomy of Load-Balancing techniques for GPUs, a layout elaborating how load-balancing algorithms can be characterized.

### **3.2.1** Configuration: Static vs. Dynamic

Load-balancing algorithms fall into two distinct approaches; static and dynamic. Static algorithms use only the information known before the algorithm launches. This may include the number of work items or tiles in the dataset, the number of threads or SMs in a given GPU, or any other characteristics of a given dataset, algorithm, or GPU architecture that can be determined without actually running the algorithm. The work distribution does not change as the algorithm proceeds, and static load-balancing strategies do not account for any runtime changes in the state of the processors or the problem. Therefore, static load-balancing algorithms have no notion of the load on each processor during the execution period. Conversely, dynamic loadbalancing algorithms account for the changing incoming or outgoing load on each execution unit by measuring and (re-)distributing that load at runtime. For example, some kernels may dynamically create new work during runtime, and a dynamic load-balancing strategy allows the kernel to immediately process this new work with idle processors rather than waiting for a later kernel launch to do so. Other load balancing strategies may rely on processors greedily requesting or donating work during runtime. Because dynamic approaches can redistribute work at runtime, they can potentially have better overall performance than static approaches, which do not. But this performance comes at the cost of additional runtime work. Thus dynamic approaches win only if the performance gains from better load balance exceed the additional cost of the runtime work to compute it. This is not always a win; Yang et al.'s sparse-matrix multiplication analysis [88] and concludes that static approaches for this problem deliver better overall performance.

For load-balancing techniques that use both static and dynamic approaches, we use the classification of **Hybrid** [22]. Hybrid algorithms may use a static technique for one segment of

the problem (or one part of the compute hierarchy) and a dynamic technique for another.

### 3.2.2 Accuracy: Exact vs. Approximate

The ideal load-balancing strategy aims to minimize runtime. In practice, such a strategy aims to balance work evenly across all compute elements (threads, warps, or blocks) so that each compute element completes its work at the same time and no units are ever idle waiting for others to finish. Optimal algorithms use the properties of the problem and the number of available execution units to determine the exact amount of work to assign to each unit to ensure all execution units are fully utilized at all times. These algorithms may achieve optimal load balancing for a given cost function. In GPUs, the cost function often results in modeling the variance of work between neighbouring threads, and the goal of the load-balancing is to attempt to assign equal amount of work items per thread (an "even-share" schedule [8, 26, 35, 63, 64, 78], another cost function may model execution time, and a load-balancing schedule optimizes this cost function to ensure that each thread runs for approximately the same time). However there is often an overhead associated with load balancing techniques that attempt to achieve exact workload balance across all processing units. Approximate load-balancing algorithms, on the other hand, focus on metrics within the problem or the dataset, or the attributes of the system (such as the number of threads) to attempt to distribute the work equally across processors. Approximate algorithms may achieve inconsistent load balancing depending on the metrics used, but can be tuned to reduce the overhead required to achieve a balanced workload. The resulting trade-off between the cost of load balancing and the quality of the workload balanced achieved is an important consideration when opting for an exact or approximate load-balancing algorithm.

### **3.2.3** Granularity: Hierarchical vs. Flat

**Hierarchical** schedules leverage the compute hierarchy available within NVIDIA GPUs by breaking the workload into coarse-grained chunks that map to the highest level of the compute hierarchy (for example the blocks) and then further break down the work into smaller granularities that proportionally map to smaller computation constructs such as warps and/or threads [64]. Section 2.1 explores this concept in more detail. **Flat** scheduling algorithms are designed to target the smallest computational unit in the hierarchy (threads) and are not

mapped to the compute hierarchy available within GPU architectures [28, 65, 84]. Hierarchical schedules often improve load balance by ensuring that a given work chunk maps to a group of computational units instead of a single (smallest) unit with proportional computation capabilities, and process the mapped work in parallel using the compute hierarchy within the group (CUDA's compute hierarchy explained in Chapter 2). For example, a row in a CSR matrix with few nonzeros may be most efficiently processed with a single thread, since processing this row with an entire block would leave many threads sitting idle when they could otherwise be processing other rows. As another example, to avoid significant amounts of atomic contention, a queue-based algorithm may assign a single thread to fetch a large chunk work on behalf of all threads in a block, but then further subdivide this work amongst the threads in the block. Beyond their increased complexity, the primary downside of hierarchical schedules is that the performance gains from leveraging coarser-granularity workers may not be enough to outweigh imperfect load balance within the coarser-granularity work chunks.

### **3.2.4** Topology: Centralized vs. Distributed

**Centralized** schedules focus on a distribution unit responsible for assigning work items to multiple processors. As an example, the GPU's (hardware) block scheduler distributes work to all SMs, assigning a new block to an SM when the SM is ready for new work. In contrast, **distributed** schedules rely on individual processors making independent, local decisions about when they need more work.

Consider a shared queue of work, accessible by all blocks. A centralized strategy for managing this queue has a single entity (either hardware or software) that is responsible for distributing work to processors. A distributed strategy instead delegates the responsibility for fetching new work to each processor: processors must actively fetch new work for themselves as needed, while competing with other processors to claim work from the queue. Centralized and Distributed schedules only apply to *dynamic* schedules. In static schedules, each processor already knows exactly which work items it must process, so there is no concept of "shared" work that could go to one of many processors depending on runtime decisions.

### **3.2.5** Communication: Cooperative vs. Non-Cooperative

**Cooperative** schedules allow processing entities to communicate with each other, for example in work-stealing load-balancing algorithms where threads are able to steal work from other threads within a warp or another block [11]. **Non-cooperative** algorithms require processors to operate autonomously within their own pool of work and with no ability to access pools of work that may be simultaneously accessed by *other* processors. In a throughput-oriented architecture, such as a GPU, cooperation often requires expensive synchronization, such as locks or atomics on queues. However, cooperation may result in a better workload balance [22]. Similar to Centralized and Distributed schedules, the concept of "cooperation" only applies to *dynamic* schedules. Cooperation requires that processors are able to make decisions at runtime about whether they need more work, or whether they have additional work to give to another processor.

### **3.3 Implementations of Load Balancing on GPUs**

In this section we conduct a study of how load-balancing techniques (summarized in Table 3.2) actually get implemented. We characterize these implementations using the taxonomy built in the previous section, and group each implementation under common patterns of scheduling work.

**Terminology** For consistency, we will use the following terms to describe the partitions of *work* within the different load-balancing techniques.

- Work Item: A single unit of work that is to be scheduled onto the GPU; for example, a non-zero element of a sparse matrix.

- Work Tile: A collection of work items, for example, a single row of a sparse matrix.

- **Tile Set:** A collection of work tiles that together comprise the entire problem, for example, an entire sparse matrix.

The terminologies summarized above are later built into a complete abstraction for loadbalancing on the GPU, and are explained in detail in Section 4. As an example to illustrate the terminology, consider Sparse-Matrix Dense-Vector Multiplication (SpMV). The irregular work in SpMV is within the sparse matrix, where the work items (the smallest units of work) are the non-zero elements, a work tile is a row of the sparse matrix, and a tile set is the entire sparse matrix. The work items are scheduled onto the GPU using a load-balancing technique.

The rest of this section describes different strategies for load-balancing work. We can choose to assign an equal number of work tiles to each thread (Section 3.3.1) or to a group of threads (Section 3.3.2), or instead assign an equal number of work items to each thread (Section 3.3.3). We use several low-level algorithmic building blocks to construct these load-balancing techniques, such as *parallel prefix-sum* (*scan*), *binary search*, *sorting*, and more. We defer a detailed explanation of these building blocks to Section 3.4.

### 3.3.1 Thread-Mapped

### Definition

Assign a fixed, constant number of work tiles to each thread. Resultant work items from each work tile are processed sequentially within the thread.

#### Characterization

Static, Approximate, Flat.

### Evaluation

Works well for small, balanced work tiles; not recommended for tile sets where the variance between work tile size is large (e.g., scale-free graphs).

Perhaps the most natural way to parallelize across work tiles is to assign each work tile to a GPU thread, and sequentially process the work items within the work tile. For problems where the workload is inherently balanced, the additional overhead of a sophisticated load-balancing scheduling of work can often be detrimental to performance. In such cases, this simple thread-mapped assignment can prove to be a viable substitute. However, the resultant workload balance with this method is often at a coarser granularity. As discussed in detail in Merrill et al.'s "Merge-Based Parallel Sparse Matrix-Vector Multiplication" [64], the performance for a thread-mapped assignment is typically not as good as other schedules if the problem is highly irregular or if there are large amounts of fine-grained parallelism left to explore. Because each

thread contains a fixed-size set of tiles and in a highly irregular dataset, each tile may contain a different amount of work, such datasets cause threads within the same warp to be waiting on threads with significantly more work, causing very low warp or block utilization and poor performance. Furthermore, since a thread is assigned an entire work tile, the work items within a tile—for example, the nonzeros within a sparse-matrix's row—are sequentially processed, and the fine-grained parallelism within the work tile is effectively serialized, leaving the device underutilized. Algorithm 1 shows a simple example of thread-mapped assignment as a scheduling strategy where each thread is assigned a fixed, statically determined input and output elements to process [14, 65, 84].

Algorithm 1 Simple pseudocode to illustrate thread-mapped scheduling where each thread is assigned to work on N input and output elements of the saxpy operation.

```

\begin{split} \mathbf{N} &\leftarrow \mathbf{4} \vartriangleright \text{Four items per thread.} \\ \textbf{procedure THREAD-MAPPED}(\alpha, \mathbf{x}, \mathbf{y}) \\ \mathbf{t}_{id} &\leftarrow \mathbf{N} \times \textbf{ThreadIndex}() \\ \vartriangleright \text{Loop can be perfectly unrolled.} \\ \textbf{for } \mathbf{k} \leftarrow \mathbf{0}, \mathbf{k} + +, \textbf{while } \mathbf{k} < \mathbf{N} \textbf{ do} \\ \mathbf{y}[t_{id} + \mathbf{k}] \leftarrow \alpha \cdot \mathbf{x}[t_{id} + \mathbf{k}] + \mathbf{y}[t_{id} + \mathbf{k}] \\ \textbf{end for} \\ \textbf{end procedure} \end{split}

```

### **3.3.2 Group-Mapped**

### Definition

Assign an equal amount of work tiles to a group of threads (warp or block). Threads within each group process individual work items in parallel.

### Characterization

Static, Approximate, Hierarchical.

### Evaluation

Exposes fine-grained parallelism within a work tile, and is highly tunable to different problems (allowing the group size to be configured to fit a problem). Works well for fairly regular workloads where no one group takes too much GPU resources. In contrast to the coarse-grained thread-mapped approach, for irregular problems with ample amounts of fine-grained work items, consider assigning groups of threads to process a single work tile in parallel. For this approach, we can leverage the existing compute hierarchy available within CUDA's programming model: threads, warps, and blocks. A larger compute unit such as a block or a warp could potentially prove to be a better mapping for a work tile that has a large number of work items to process. This is because instead of serializing the work within a work tile, we can assign all threads within a block or a warp to process that work in parallel, promoting better utilization and load balancing within the thread group.

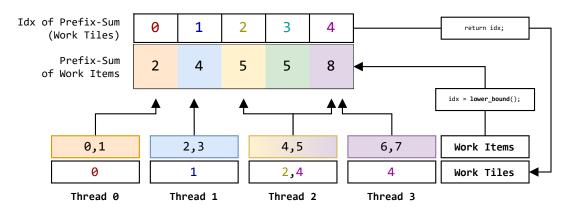

This strategy of assigning an entire tile of work to a group of threads (either a warp, a block, or a "Cooperative Group" [69]) of a GPU is called group-mapped load balancing. Group-mapped is typically implemented by first assigning an equal number of work tiles to each group, Total Work Tiles. Then to effectively map the assigned tiles onto the threads within a group, each thread individually needs two sets of information: (1) The total number of work items it is processing (a range from work item *i* to work item *j*) and (2) what work tile each work item belongs to. A parallel prefix sum gives us both pieces of information. Discussed in detail in Section 3.4, a prefix sum is a sequence of numbers that is the running total of an input sequence. In group-mapped's case, a prefix sum of work items per assigned work tiles is constructed, where the last element of the prefix sum sequence is the total number of work items assigned to the group by the number of threads within the group to get the "range" of work items any given thread is going to process. And for (2), when processing the work items within a loop, each thread performs a binary search within the prefix sum sequence to determine the work tile index the current work item corresponds to (see Algorithm 2, lines 8–10).

Using the running SpMV example, if a row of a sparse matrix is assigned to an entire warp, all 32 threads within a warp will collectively process each nonzero element within the row. Similarly, if a row is assigned to an entire block, all threads within the block will process the individual nonzero elements of the row [28].

Group-mapped load balancing exposes the fine-grained parallelism available in each work tile to a group, allowing the work items to be processed in parallel, with the cost being the overhead of a parallel prefix sum per group (warp or block) and the binary search to find the work tile within the parallel prefix sum array. A group-mapped assignment also heavily relies on the underlying hardware scheduler's ability to schedule new thread groups as a group finishes processing a work tile. This method is also commonly known as warp-mapped or block-mapped scheduling, and is often used in conjunction with dynamic scheduling techniques such as a dynamic task queue [22] to create a hybrid load-balancing strategy discussed later (see Section 3.3.5). Generally, irregular problems with structured regular blocks within them map well to this load-balancing schedule.

```

Algorithm 2 An example group-mapped scheduled kernel for sparse-matrix dense-vector mul-

tiplication (spmv), where each group is assigned an entire row and threads within the group

process individual nonzero elements.

```

- 1: input: A, CSR Matrix. x, Dense Vector.

- 2: output: y, Dense Vector.

- 3: **procedure** GROUP-MAPPED(A, x, y)

- 4: items\_per\_tile  $\leftarrow$  **Zeros**(GROUP\_SIZE)

- 5:  $t_{id} \leftarrow ThreadIndex()$

- 6:  $gt_{id} \leftarrow ThreadIndexInGroup()$

- 7:  $\triangleright$  Each group populates an array with the number

- 8:  $\triangleright$  of work items per tile.

- 9:  $items\_per\_tile[gt_{id}] \leftarrow A.offsets[t_{id} + 1] A.offsets[t_{id}]$

- 10: prefix\_sum\_array  $\leftarrow$  **ParallelPrefixSum**(items\_per\_tile, t<sub>id</sub>)

- 11:  $\triangleright$  Last element of prefix-sum array corresponds

- 12:  $\triangleright$  to total work items per group.

- 13: total\_items  $\leftarrow$  prefix\_sum\_array[GROUP\_SIZE 1]

- 14:  $\triangleright$  Loop over total work, each thread processing individual work items.

- 15: **for**  $k \leftarrow t_{id}$ ,  $k + GROUP\_SIZE$ , **while**  $k < total\_items$  **do**

- 16:  $\triangleright$  Perform a binary-search to find the tile index.

- 17: row  $\leftarrow$  **BinarySearch**(prefix\_sum\_array, k)

- 18:  $y[row] \leftarrow A.values[k] \times x[A.indices[k]]$

```

19: end for

```

20: end procedure

# 3.3.3 Work-Oriented

# Definition

All threads are assigned  $\frac{Total Work}{Number of Processors}$  work items. Each thread then sequentially processes assigned work items in a loop.

#### Characterization

Static, Exact, Flat (+ GPU hierarchy).

#### Evaluation

Works well when the upfront cost of performing a prefix sum or binary search is minor compared to the cost of processing the work items; very effective at balancing highly irregular work (such as in scale-free graphs).

So far we have considered two load-balancing techniques that map *work tiles*, the input, onto compute entities (thread- or group-mapped), however, neither are guaranteed to achieve perfect workload balancing at the device level. Instead, we consider the *work items* as the granularity targetted for load-balancing, where additional computation is done to assign equal amounts of work items to each thread in a GPU, achieving exact workload balancing. This approach is known as work-oriented scheduling and can be implemented via two predominant methods, which largely differ in the definition of a "work unit".

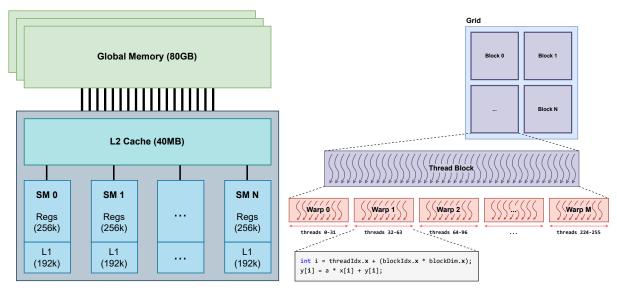

Since the goal is to assign a constant number of work items per thread, the definition of a work item is an important design decision. The first method, known as *non-zero splitting* (used for sparse-linear algebra kernels such as SpMV), considers the total number of nonzero elements within a sparse-matrix or total multiply-accumulate instructions  $(y_i += A_{ij} \times x_j)$  as the total work [8, 26, 88]. The second method, *merge-path*, considers a work item as either a nonzero element or an output, effectively associating an equal cost to a nonzero and to outputting a value to the GPU's global memory [35, 64]. Fundamentally, the work-oriented assignment is a mapping of the  $\frac{Total Work}{Number of Threads}$  to each thread, where each thread is assigned a contiguous range of work items to process in a sequential loop. A binary search per thread (a key low-level algorithm discussed in Section 3.4.2) then finds the work tile for each range of work items thread must process (see Algorithm 3).

Merge-path was originally proposed for SpMV kernels. In a merge-path SpMV, the sparsematrix is stored in a compressed sparse row format (CSR), where the row offsets of the CSR matrix are already known (the row offset array is effectively a prefix-sum array). The schedule aims to perform a 2-D split of the grid created using the row-offsets and the nonzero indices, and the search along the diagonal of the grid allows each thread to find its starting and ending rows and nonzeros. The merge-path schedule ensures that there is constant number of fix-up steps (i.e., the number of threads) required to accumulate the partial rows that were split between two threads. The result of a merge-path schedule is that work is mapped to the smallest possible compute unit in the hierarchy, but merge-path takes advantage of the compute hierarchy by first splitting the work across blocks, and then to threads within a block to reduce the search space each thread has to search through (each thread now only searches through its block's share of the work). If the data is already stored in a CSR representation (as proposed by the original paper by Merrill and Garland [64]), the cost of this method is the 2-dimensional binary search along the row offsets and the nonzero indices of the CSR matrix, and the required fix-up step for the partial tiles of work. Beyond load-balancing a CSR sparse matrix, this method can also be generalized to other sparse representations and domains such as graph analytics, with an added cost of a parallel prefix sum to create the required offsets array [14, 84]. Since there is an additional overhead attached to computing this prefix-sum, this method tends to be less performant than other low-overhead methods on an well-structured sparse data [88].

## **3.3.4 Binning and Reordering**

#### Definition

Separate work tiles into a fixed number of bins based on heuristics, such that each bin holds work tiles with approximately the same amount of work items.

#### Characterization

Dynamic, Approximate, Hierarchical, Non-Cooperative, Centralized or Distributed.

#### Evaluation

Effective at balancing workloads with contiguous work tiles with approximately the same number of work items, and with imbalance among these contiguous ranges of work tiles. This method maps well to CUDA's compute hierarchy, where bins can be assigned to a level in the hierarchy depending on the granularity of work within them.

The static load-balancing techniques discussed above aim for an even work distribution for a given problem; these techniques are inefficient when either the overhead to load-balance is Algorithm 3 An example *work-oriented* scheduled kernel for sparse-matrix dense-vector multiplication (spmv), where each thread is assigned an even share of work [64].

```

1: input: A, CSR Matrix. x, Dense Vector.

2: output: y, Dense Vector.

3: procedure WORK-ORIENTED(A, x, y)

4:

▷ Calculate work division and bounds.

5:

t_{id} \leftarrow ThreadIndex()

total_work \leftarrow A.rows + A.nonzeros

6:

items_per_thread \leftarrow \frac{\text{total_work}}{\text{num_threads}}

7:

diag \leftarrow min(items_per_thread \times t<sub>id</sub>, total_work)

8:

diag_end \leftarrow min(diag + items_per_thread, total_work)

9:

10:

(row_{start}, nz_{start}) \leftarrow 2DSearch(diag, A)

(row_{end}, nz_{end}) \leftarrow 2DSearch(diag_end, A)

11:

\triangleright Perform work on full tiles.

12:

running_total \leftarrow 0

13:

14:

for m \leftarrow row_{start}, m++, while m < row_{end} do

for k \leftarrow nz_{start}, k++, while k < A.offsets[m] do

15:

running_total += x[A.indices[k]] \times A.values[k]

16:

end for

17:

18:

y[row] \leftarrow running_total

19:

running_total \leftarrow 0

end for

20:

\triangleright Perform work on partial tiles.

21:

22:

for k \leftarrow k, k++, while k < nz_{end} do

running_total += x[A.indices[k]] \times A.values[k]

23:

24:

end for

25:

row\_carry\_out[t_{id}] \leftarrow row_{end}

value\_carry\_out[t_{id}] \leftarrow running\_total

26:

27: end procedure

28: \triangleright Fix-up step to accumulate partial tiles.

29: procedure FIX-UP(A, y, row_carry_out, value_carry_out)

30:

for t_{id} \leftarrow 0, t_{id}++, while t_{id} < num_threads do

y[row\_carry\_out[t_{id}]] += value\_carry\_out[t_{id}]

31:

end for

32:

33: end procedure

```

greater than processing the entire computation, or when there is a huge mismatch between the worker size and the work unit. Instead, when a given problem has a known bound on the amount of work, we can implement a load-balancing schedule that is reasonably efficient for a given bounded range, and particularly so if we choose the correct amounts of compute resources that match the given input range (e.g., assign a work tile with exactly 32 work items to be processed by a warp composed of 32 threads.) This is where binning-based load-balancing algorithms, which attempt to dynamically balance a given workload by categorizing each work tile into a fixed number of bins with the goal that each bin will hold work tiles that have approximately the same amount of work items, perform reasonably well. Binning-based techniques can largely be subdivided into three different phases: (1) choosing bin sizes (compile time); (2) dynamically distributing work tiles into bins based on a programmer-specified criteria (runtime); then (3) computing the contents of each bin (runtime).

One approach to binning that specifically targets the GPU compute hierarchy chooses three bins to partition the work tiles: (1) a bin with work tiles that have a number of work items equal to or greater than the size of the GPU block (number of threads per block); (2) a bin with work tiles that have a number of work items less than the size of the GPU block but larger than a warp (32 threads); and (3) a bin with work tiles that have a number of work items less than the size of the warp. For brevity, we will use the terms block-sized, warp-sized, and thread-sized bins. After the initial assignment of work tiles to their respective bins, the processing stage that perform the desired computation on the contents of each bins can be implemented in three different ways:

- 1. Launch three kernels, where each kernel is specialized to process one of the three categories of bins. For the block-sized bin, one kernel uses all threads with the block to cooperatively process the tiles. Similarly, in the warp-sized bin, the kernel uses all threads within a warp to cooperatively process the bin, And finally, the last kernel processes the thread-sized bin, where each work tile has only a few work items, my assigning one thread to each work tile [65, 84].

- 2. Launch one kernel, where each thread is initially assigned a work tile, determines the amount of work, and assumes control of the block or the warp if the size of work is enough

to saturate the compute unit. All threads within the compute unit then cooperatively work together to process each work item within the "winning" thread's tile. This process continues until the work tiles are small enough for each thread to individually process them (Algorithm 4) [28, 84].

3. Brahmakshatriya et al. proposed a variation of the one-kernel approach, where instead of threads competing to assume control of a block, each block first processes a multiple of its size worth of work items of a tile (if any), and then a warp processes multiple of its size worth of work items, and finally the threads complete the work tile by processing the remaining work items [14].

The benefit of the three-kernel specialization is that each kernel is designed to process one bin-type with no added communication or synchronization for threads within the kernel to assume control of a given compute unit or hierarchy. However, the total work now is now split among three kernel launches, making it challenging to fully utilize the device per kernel for a given work distribution. Furthermore, for problems that require a large number of iterations to successfully converge, the kernel launch overhead, which is commonly an insignificant cost and largely ignored, is now  $3 \times$  larger.

Another proposed approach, Logarithmic Radix Binning (LRB), first introduced by Green et al. within a triangle counting implementation [36], allows the load balancer to schedule work items with similar amounts of work within the same spatial and temporal region [32]. LRB assigns tasks to bins based on the *logarithm* of the amount of work required for a given task. Thus, the range of possible amounts of work across all items in a bin varies by no more than a factor of two. When a work tile is encountered with work items greater than equal to  $2^b$  and less than  $2^{b+1}$ , a counter at location b is incremented in an array of size  $B \in \{32, 64\}$ . Using these bins instead of the ones associated with CUDA's compute hierarchy (threads, warps, blocks) in the previous approach, the total workload is binned at a finer granularity such that work tiles containing a similar number of work items are grouped together for processing. To assign work tiles to threads, a modulo operation is performed on the reordered task index and a constant number of work items, P. Each thread then processes (i, P+i, 2\*P+i, ...) work items [32, 36].

Another widely used technique for reordering or grouping like-sized work together is a

Algorithm 4 An example *binning* scheduled kernel for sparse-matrix dense-vector multiplication (spmv), where work tiles are placed into bins based on the number of work items within them, and processed with the required compute resource [28, 65].

- 1: **input:** A, CSR Matrix.

- 2: **procedure** BINNING(A)

- 3: row  $\leftarrow$  **ThreadIndex**()

- 4:  $num\_nonzeros \leftarrow A.offsets[row + 1] A.offsets[row]$

- 5: **if** num\_nonzeros  $\geq$  block\_size **then**

- 6:  $cta\_bin\_ids[cta\_bin\_size] \leftarrow row$

- 7: cta\_bin\_size++

- 8: **else if** num\_nonzeros  $\geq$  warp\_size **then**

- 9:  $warp\_bin\_ids[warp\_bin\_size] \leftarrow row$

- 10: warp\_bin\_size++

- 11: **else**

- 12: thread\_bin\_ids[thread\_bin\_size]  $\leftarrow$  row

- 13: thread\_bin\_size++

- 14: **end if**

- 15: end procedure

- 16: input: A, CSR Matrix. x, Dense Vector.

- 17: **output:** y, Dense Vector.

- 18: **procedure** CTA\_BIN(A, x, y)

- 19:  $row \leftarrow cta\_bin\_ids[idx]$

- 20:  $\triangleright$  Use an entire CTA to process the row.

- 21: end procedure

- 22: **procedure** WARP\_BIN(A, x, y)

- 23: row  $\leftarrow$  warp\_bin\_ids[idx]

- 24:  $\triangleright$  Use an entire warp to process the row.

- 25: end procedure

- 26: **procedure** THREAD\_BIN(A, x, y)

- 27: row  $\leftarrow$  thread\_bin\_ids[idx]

- 28:  $\triangleright$  Sequentially process a row in the thread.

- 29: for  $k \leftarrow A.offsets[row], k++, while k < A.offsets[row + 1] do$

- 30:  $y[A.indices[k]] += x[A.indices[k]] \times A.values[k]$

- 31: **end for**

- 32: end procedure

simple (but often costly) sort to arrange tiles from most to fewest work items [13]. The sort operation reduces the work variance between adjacent tiles and therefore improves load balance. In iterative problems such as sparse-matrix dense-matrix multiplication in a deep learning workload, the overhead of the sort is amortized over the number of runs of an algorithm [33].

# 3.3.5 Task-Oriented Scheduling

## Definition

Independent workers fetch work from a work queue or queues, process the work, and optionally add new work to a queue.

#### Characterization

Dynamic Approximate, Flat, Cooperative, Centralized or Distributed.

#### Evaluation

Works well when it is too expensive to compute a static assignment of work items to processors at the start of the kernel, if the kernel dynamically generates new work items, or if the cost to process each work item is unknown.

Performs best if one thread can fetch chunks of work on behalf of an entire block, to reduce synchronization contention. Powerful when paired with hierarchical load balancing within a block, where a block fetches a chunk of work on behalf of all threads, and then further subdivides this work among its threads.

The previously-described load balancing methods divide up work at compile time or runtime and associate each chunk of work with a virtual processor, which the hardware scheduler then dynamically maps to a physical processor based on resource utilization. In contrast, task parallelism shifts the job of assigning work to processors to the programmer. Task parallelism methods are more flexible at runtime, and benefit workloads where it would be expensive to compute the optimal work distribution and assign it to individual processors in advance, or where the total amount of work to be generated in a kernel is unknown. Programmers can customize the task generation and consumption behavior to their specific use case, at the cost of some software overhead compared with the GPU's hardware block scheduler. A primary benefit of a task-parallel schedule is that it allows processors that finish their currently assigned task to immediately start work on another task without waiting for synchronization at the end of a kernel, or to generate new irregular tasks that other processors may consume without waiting for a new kernel iteration.

A classic example of task parallelism is a queue-based implementation of Breadth-First Search. After a block removes a vertex from the FIFO queue, it sets the vertex's depth then adds neighbors of that vertex to the back of the queue. In a parallel GPU system, these new work items may be popped and processed by other processors in the system. This process continues until the queue is empty and the processors no longer have new work to add to the queue.

The primary downsides of queue-based schedules are that they suffer from overheads necessary to ensure that each processing element adds or retrieves work at the correct location, and that the queue must be large enough to accomodate the worst-case number of work items in the queue. This is because memory allocations are expensive and happen outside the kernel boundary. Additionally, there is a chance that some processors may have long-running work that leaves other processors sitting idle when the queue is empty. Finally, queue-based schedules replace the hardware work distribution done by the GPU's block scheduler with user-controlled software work distribution, which adds additional overheads.

#### 3.3.5.1 Centralized Queue

#### Evaluation

Useful when the algorithm dynamically creates work at runtime, or when it's undesirable to precompute an assignment of work items to processors.

The static task list approach presented by Cederman et al. is the most basic task-oriented schedule: the kernel consists of two arrays: an "in-array" and an "out-array" [18]. The inarray contains tasks to be executed by the processors in the current iteration. As the kernel proceeds, processors iterate over their statically assigned tasks (where a block with index i handles all tasks at integer multiples of i), perform the task, and potentially add additional tasks to the "out array". This process continues until the in-array is empty, at which point the out-array becomes the new in-array. The kernel iterates between the two arrays until there are no remaining tasks in either array. Like all queue methods, this approach requires that

Algorithm 5 An example queue-based kernel for breadth-first search, where each worker is assigned an entire vertex.

```

1: input: G, CSR Graph. Q, Work Queue. s, Source Vertex.