## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

## Title

Stride: A Language for Sound Synthesis, Processing, and Interaction Design

## Permalink

https://escholarship.org/uc/item/0sc948c2

#### **Author** Tilbian, Joseph

# Publication Date 2018

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

## Stride: A Language for Sound Synthesis, Processing, and Interaction Design

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Media Arts and Technology

by

Joseph Tilbian

Committee in charge:

Prof. Curtis Roads, Committee Chair Prof. Theodore Kim Dr. Matthew Wright Dr. Andrés Cabrera

December 2018

The Dissertation of **Joseph Tilbian** is approved.

Theodore Kim

**Matthew Wright**

Andrés Cabrera

Curtis Roads, Committee Chair

June 2018

## Stride: A Language for Sound Synthesis, Processing, and Interaction Design

Copyright © 2018

by

Joseph Tilbian

For my parents:

Haig Tilbian

Mary Movsesian

#### Acknowledgments

This dissertation is one of the outcomes of a close collaboration that started in late 2013 between Dr. Andrés Cabrera and me. The drive behind this collaboration was a mutual interest to design microcontroller-based electronic platforms for sound synthesis, processing, and interaction design to supplement some of the existing popular electronic platforms which were designed for physical computing and general-purpose computation. The novelties and contributions of this dissertation are the result of hundreds of hours of conversations and discussions to design something powerful yet simple and elegant. I would like to express my sincere gratitude to Andrés Cabrera for being an indispensable partner throughout the ongoing collaboration.

I would like to thank my advisor and the chair of my dissertation committee Professor Curtis Roads and the members of the committee Professor Theodore Kim, Dr. Matthew Wright, and Dr. Andrés Cabrera for the encouragement and invaluable feedback they provided throughout the process.

I would like to thank Professor JoAnn Kuchera-Morin for having me as part of the AlloSphere Research Group as a Graduate Student Researcher and supporting this research work.

I would like to thank the Robert W. Deutsch Foundation for the generous graduate fellowship grant made possible through the AlloSphere Research Group at UCSB.

v

I would like to thank the UCSB Center for Research in Electronic Art Technology (CREATE) for a generous grant to support the development of Stride and the Systemics Lab for letting us borrow their electronic test equipment.

I would like to thank the Media Arts and Technology Program and Dr. Andrés Cabrera for the teaching assistant positions for the Digital Audio Programming course series.

I would like to thank Steffen Martin and Łukasz Olczyk for their help with the design, development, and testing of the Saturn M7 Audio Development Board, which became a target platform for Stride.

I would like to thank my colleagues at the Media Arts and Technology Program in particular Sahar Sajadieh, Gustavo Rincon, Şölen Kıratlı, Owen Campbell, and Hanna Wolfe for their friendship and the great memories.

I finally want to thank my family for their unconditional love and support.

## Curriculum Vitæ

Joseph Tilbian

## Education

| 2018 | Ph.D. in Media Arts and Technology<br>University of California, Santa Barbara     |

|------|-----------------------------------------------------------------------------------|

| 2006 | M.Sc. in Mechatronics<br>University of Applied Sciences, Aachen - Germany         |

| 2002 | B.E. in Mechanical Engineering<br>American University of Beirut, Beirut - Lebanon |

## Publications

J. Tilbian and A. Cabrera, "**Stride: A Declarative and Reactive Language for Sound Synthesis and Beyond**," in Proceedings of the 2016 International Computer Music Conference, Utrecht, 2016, pp. 472-478.

J. Tilbian and A. Cabrera, "**Stride for Interactive Musical Instrument Design**," in Proceedings of the 2017 International Conference on New Interfaces for Musical Expression, Copenhagen, 2017, pp. 446-449.

J. Tilbian, A. Cabrera, S. Martin, and Ł. Olczyk, **"Stride on Saturn M7 for Interactive Musical Instrument Design,**" in Proceedings of the 2017 International Conference on New Interfaces for Musical Expression, Copenhagen, 2017, pp. 503-504.

#### Abstract

Stride: A Language for Sound Synthesis, Processing, and Interaction Design

by

#### Joseph Tilbian

This dissertation presents Stride, a language for sound synthesis, processing, and interaction design. With a novel and unique approach for handling sampling rates as well as clocking and computation domains, Stride prompts the generation of highly optimized target code. Optimization is achieved by giving the user of Stride control over the Stride code generator through its syntax. The optimizations render Stride an ideal language to target resource-constrained devices such as microcontrollers. Stride is a declarative language and adopts features from dataflow languages. With only two syntactic constructs, Stride is easy to learn. Through resource abstraction and separation of semantics from implementation, a wide range of computation devices could be targeted such as microcontrollers, system-on-chips, general-purpose computers, and heterogeneous systems. Users of Stride can write code once and deploy on any supported hardware.

After presenting the challenges of targeting resource-constrained microcontrollers with popular music programming languages in use today for sound synthesis and processing, a new programming language and its syntax are introduced to address these challenges. This is followed by demonstrating how the language enables its user to control the code generation process to yield efficient and optimized target code. Next, the semantics of the language and some of its core building blocks are presented in detail followed by the user-controlled concurrency model built into the language. Designing interaction using some of the core blocks is then presented through a set of examples followed by some of the advanced building blocks of the language. Finally, the language is presented as part of an encompassing development environment and all of its components including the integrated development environment and the compiler.

# Contents

## Curriculum Vitæ

### Abstract

| 1 | Intr | Introduction |                                |      |  |  |

|---|------|--------------|--------------------------------|------|--|--|

|   | 1.1  | Scope        | e                              | . 2  |  |  |

|   | 1.2  | Proble       | em Statements                  | • 4  |  |  |

|   | 1.3  | Resea        | arch Questions                 | . 5  |  |  |

|   | 1.4  | Contr        | ributions                      | . 8  |  |  |

|   |      | 1.4.1        | A New Syntax                   | . 8  |  |  |

|   |      | 1.4.2        | Signals with Rates and Domains | . 9  |  |  |

|   |      | 1.4.3        | Code Generation                | . 9  |  |  |

|   |      | 1.4.4        | Concurrency                    | . 10 |  |  |

|   | 1.5  | Dissei       | rtation Structure              | . 10 |  |  |

|   | 1.6  | Permi        | issions and Attributions       | . 12 |  |  |

|   | 1.7  | Additi       | ional Notes                    | . 12 |  |  |

|   |      |              |                                |      |  |  |

| 2 | Sur  | vey of       | Music Programming Languages    | 13   |  |  |

|   | 2.1  | Music        | Programming Languages          | . 14 |  |  |

|   |      | 2.1.1        | Csound (1985)                  | . 14 |  |  |

|   |      | 2.1.2        | Pd - Pure Data (1996)          | . 15 |  |  |

|   |      | 2.1.3        | SuperCollider (1996)           | . 17 |  |  |

|   |      | 2.1.4        | Faust (2002)                   | . 18 |  |  |

|   |      | 2.1.5        | ChucK (2003)                   | . 19 |  |  |

|   |      | 2.1.6        | Discussion                     | . 20 |  |  |

|   | 2.2  | Concu        | urrent Research                | . 20 |  |  |

|   |      | 2.2.1        | Kronos                         | . 20 |  |  |

|   |      | 2.2.2        | WaveCore                       | . 21 |  |  |

vii

viii

| 3 | Fau  | st and Targeting Microcontrollers                        | 22 |

|---|------|----------------------------------------------------------|----|

|   | 3.1  | A Simple Faust Example                                   | 22 |

|   | 3.2  | Computing Constants                                      | 27 |

|   | 3.3  | Processing Loads and Relative Rates                      | 28 |

|   | 3.4  | Concurrency                                              | 33 |

|   | 3.5  | Vector Processing                                        | 36 |

|   | 3.6  | Libraries and APIs                                       | 37 |

|   | 3.7  | Summary                                                  | 38 |

|   | 0,   | <b>,</b>                                                 | 0  |

| 4 | Imp  | rovements with Stride                                    | 39 |

|   | 4.1  | An Oscillator with Frequency Control                     | 39 |

|   | 4.2  | A New Language                                           | 41 |

|   | •    | 4.2.1 Block Declarations                                 | 41 |

|   |      | 4.2.2 Stream Expressions                                 | 43 |

|   | 4.3  | Code Generation for an Embedded Platform                 | 44 |

|   | 1.2  | 4.3.1 Oscillator with Frequency Control                  | 45 |

|   |      | 4.3.2 Oscillator's Frequency Control at Reduced Rate     | 49 |

|   |      | 4.3.3 Reactive Control of the Oscillator's Frequency     |    |

|   |      | 4.3.4 Audio Callback Optimization                        | 54 |

|   | 4.4  |                                                          | 56 |

|   | 4.4  | Summary                                                  | 58 |

|   | 4.5  |                                                          | 50 |

| 5 | Sigr | als, Rates, Domains, and Modules                         | 59 |

|   | 5.1  | Behavior of a Signal                                     | 60 |

|   |      | 5.1.1 Rates                                              | 60 |

|   |      | 5.1.2 Domains                                            | 63 |

|   | 5.2  | A Sine Oscillator Module in Stride                       | 66 |

|   | -    | 5.2.1 Sine Oscillator Stream Expressions                 | 66 |

|   |      | 5.2.2 Sine Oscillator Module                             | 72 |

|   |      | 5.2.3 Code Generation for the Sine Oscillator Module     | 78 |

|   | 5.3  | Using Modules in Stride                                  | 80 |

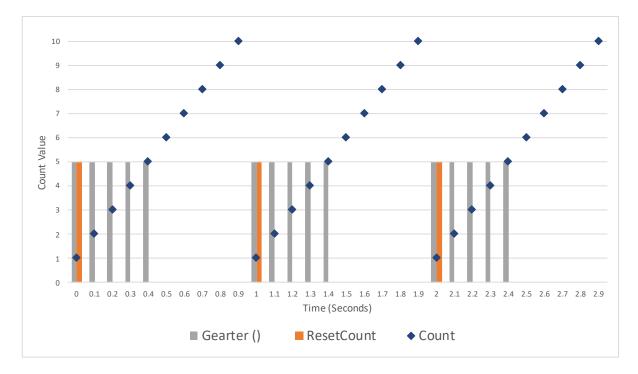

|   | 55   | 5.3.1 Level Module                                       | 80 |

|   |      | 5.3.2 Synchronous Frequency Modulation                   | 83 |

|   |      | 5.3.3 Asynchronous Frequency Modulation                  | 86 |

|   | 5.4  | Summary                                                  | 89 |

|   | J.4  |                                                          | J  |

| 6 | Don  | nains and Concurrency                                    | 90 |

|   |      | 6.0.1 Domain Execution Order                             | 91 |

|   |      | 6.0.2 Concurrency Declaration                            | 92 |

|   | 6.1  | Concurrency and Stateless C++ Template Classes           | 93 |

|   |      | 6.1.1 Asynchronous Frequency Modulation with Concurrency | 95 |

|   | 6.2  | Discussion                                               | 97 |

|   |      |                                                          |    |

|    | 6.3                | Summary                                                           | 98              |

|----|--------------------|-------------------------------------------------------------------|-----------------|

| 7  | <b>Inte</b><br>7.1 | eraction Design with Triggers and Reactions 9<br>The Switch Block | <b>99</b><br>00 |

|    | 7.2                | The Trigger Block                                                 | 21              |

|    |                    | 7.2.1 Single Domain Trigger Example                               | )2              |

|    |                    | 7.2.2 Multiple Domain Trigger Example                             | 04              |

|    | 7.3                | Reactions                                                         | •               |

|    | , g<br>7.4         | Attack/Decay Envelope in Stride                                   | •               |

|    | 7.5                | Summary                                                           |                 |

|    | 7.5                |                                                                   |                 |

| 8  | Adv                | anced Blocks in Stride 12                                         | 29              |

|    | 8.1                | The Buffer Block                                                  | 29              |

|    |                    | 8.1.1 Buffer Block as Delay Line                                  | ;0              |

|    |                    | 8.1.2 Buffers and Hardware IO Abstraction                         | 3               |

|    |                    | 8.1.3 Buffers and Vector Operations                               | ;6              |

|    | 8.2                | The Loop Block                                                    | 12              |

|    | 8.3                | The Group Block                                                   |                 |

|    | 8.4                | Summary                                                           | 64              |

|    |                    |                                                                   |                 |

| 9  | Stri               | -                                                                 |                 |

|    | 9.1                | Language Features                                                 | ;6              |

|    | 9.2                | Stride Environment                                                | ;9              |

|    |                    | 9.2.1 Stride Systems                                              | ;9              |

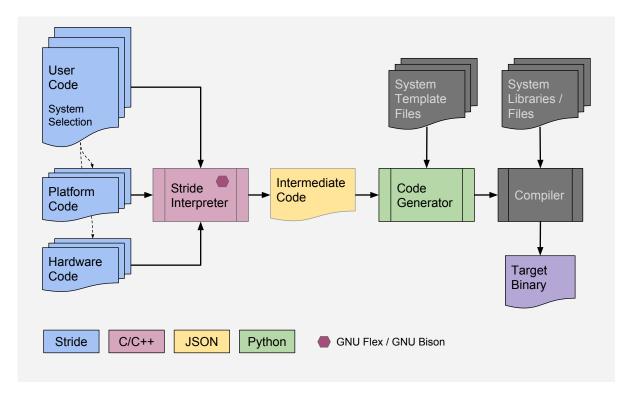

|    |                    | 9.2.2 Stride Compiler                                             | 0               |

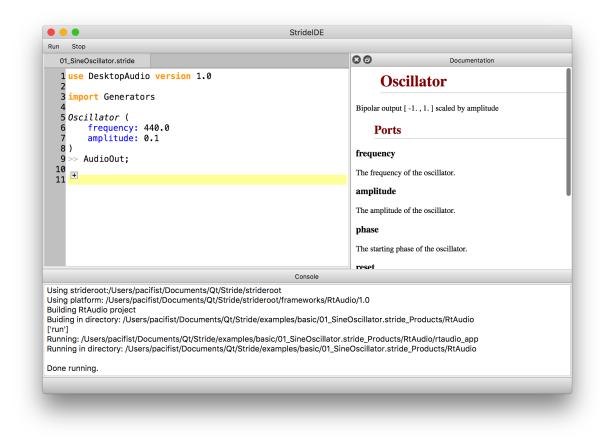

|    | 9.3                | Stride IDE                                                        | 3               |

|    | 9.4                | Stride Syntax                                                     | 4               |

|    |                    | 9.4.1 Basic Blocks                                                | 5               |

|    |                    | 9.4.2 Block Bundles                                               | 12              |

|    |                    | 9.4.3 Advanced Blocks                                             | '3              |

|    |                    | 9.4.4 Stream Expressions                                          | '8              |

|    | 9.5                | Summary                                                           | <b>)</b> 1      |

|    | <b>C</b>           |                                                                   | _               |

| 10 |                    | clusion 19                                                        |                 |

|    |                    | Summary                                                           |                 |

|    |                    | Discussion                                                        |                 |

|    | 10.3               | Future Work                                                       | 17              |

| Δ  | Fau                | st DSP and Generated Code 19                                      | 10              |

| ~  |                    | Resonant Low Pass with Constant Arguments                         |                 |

|    | 7 10 1             | A.1.1 Faust DSP Code                                              | _               |

|    |                    | A.1.2 C++ Generated Code                                          |                 |

|    |                    |                                                                   |                 |

|                                  | A.2            |                                       | 203<br>203               |

|----------------------------------|----------------|---------------------------------------|--------------------------|

|                                  | A.3            |                                       | 204<br>207               |

| В                                | Rela<br>B.1    |                                       | <b>217</b><br>217        |

|                                  | 0.1            | B.1.1 Results                         | 218<br>218<br>218        |

| C Frequency Modulation in Stride |                |                                       | 223                      |

|                                  | C.1            | C.1.1Synchronous Frequency Modulation | 224<br>224<br>231<br>239 |

| D                                | Stri           |                                       | 248                      |

|                                  | _              | Synchronization                       | 249<br>252               |

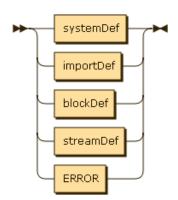

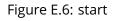

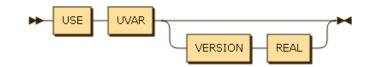

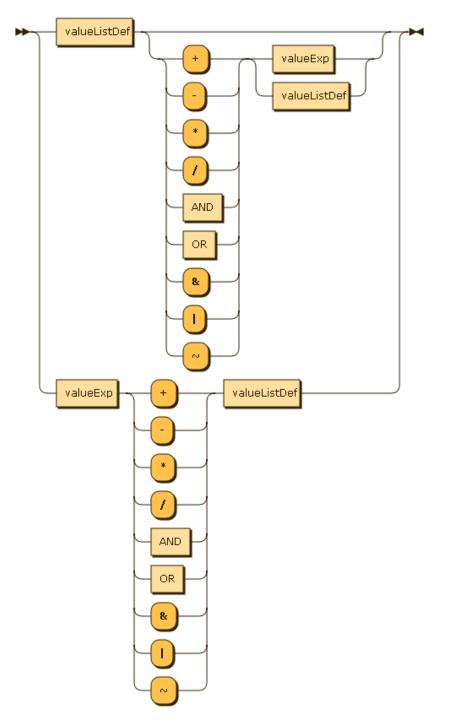

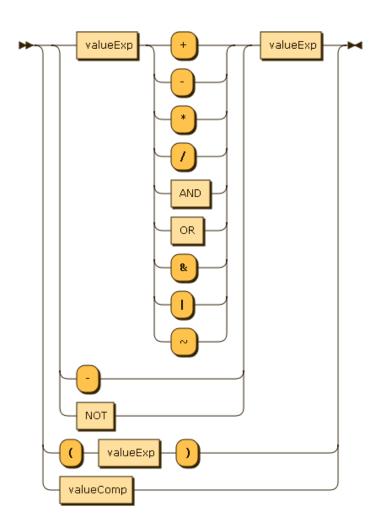

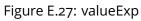

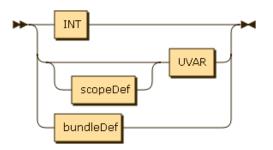

| E Stride Lexeme and Grammar      |                |                                       | 256                      |

|                                  | E.1<br>E.2     |                                       | 256<br>260               |

| Bi                               | bliog          | graphy                                | 275                      |

| Те                               | rms            | and Abbreviations a                   | 279                      |

| Gl                               | ossa           | ry 2                                  | 280                      |

| Li                               | st of          | Figures                               | 281                      |

| Li                               | List of Tables |                                       |                          |

| Li                               | List of Codes  |                                       |                          |

# **Chapter 1**

# Introduction

Over the past two decades single-board computers with microcontrollers and systemon-chips as their main processor have become popular among artists, hobbyists, and "do-it-yourself" enthusiasts. Their popularity can be attributed to making the programming of these small computers easier, thus making them more accessible to people who lack the technical expertise required otherwise.

Most single-board computers have been designed with physical computing, generalpurpose computing, or graphical applications in mind. Supplemental boards and hardware are usually required with these boards to generate good quality sound and enable the control of synthesis and processing parameters in real time.

Single-board computers designed for low latency, high fidelity, and high-resolution audio applications such as sound capture, reproduction, synthesis, and processing with real-time response capabilities are rare. One of the reasons appears to be the lack of a modern language for sound synthesis and processing to target the computers that power such boards.

## 1.1 Scope

This dissertation covers the design of a new programming language for sound synthesis, processing, and interaction design to target resource-constrained single-board computers specifically and any computer or computer system generally.

Popular music programming languages for sound synthesis and processing, running on modern general-purpose computers characterized by their computational power and the abundance of memory, achieve desired qualities such as real-time performance, high sound resolution (bit depth and sampling rate), and precision (double precision floating-point). However, microcontrollers generally only possess a small fraction of the computation power those machines offer. Many synthesis techniques also require ample memory which is also a scarce resource on microcontrollers.

Historically, dedicated Digital Signal Processor (DSP) Integrated Circuits (IC) with dedicated external memory have been used to achieve those qualities, enabled through on-board circuits to perform general-purpose and specific signal processing tasks, such as single instruction multiply-add operations or Fast Fourier Transforms.

In recent years, with the introduction of microcontrollers designed to target multimedia applications, such as those designed around an Arm<sup>®</sup> Cortex<sup>®</sup>-M core, the line between DSPs and microcontrollers has become blurred.

2

These modern microcontrollers have Central Processing Units (CPU) clocked at threedigit MHz speeds, come with dedicated single precision or double precision Floating-Point Units (FPU), and are capable of performing multiply add operations as well as operate on multiple data with a single CPU instruction in a single clock cycle. These are features common to DSPs. These microcontrollers also feature peripherals supporting electrical serial bus interface standards for digital audio communication among ICs like I<sup>2</sup>S (Inter-IC Sound) or S/PDIF (Sony/Philips Digital Interface) among others.

Another stark difference between general-purpose computers and microcontrollers appears in the need for an operating system. Almost all general-purpose computers today run an operating system that hosts applications designed for it. Microcontrollers on the other hand either run a real-time operating system or run bare metal<sup>1</sup>. Running code on a bare metal microcontroller reduces overhead introduced by an operating system. This latter case is an important consideration when designing a language to target microcontrollers.

Therefore, designing a language and a code generator that could target bare metal microcontrollers and produce code with the smallest possible footprint and least overhead is one, if not the most important, criterion to consider.

Because microcontrollers have limited resources, it is important to give the user the ability to control how often computations happen and in which context these computations happen. Another consideration is giving the user control over the code generator through the language syntax, rather than through passing compilation flags to the compiler, to generate efficient and optimized code that meets the computational

<sup>&</sup>lt;sup>1</sup>A computer system that does not contain an operating system.

or aesthetic needs of the user.

Prior to embarking on the design of a new language it is only reasonable to assess whether current music programming languages would be up to the task of supporting resource-constrained systems by introducing modifications to their syntax and/or internal processes.

From this point on we will refer to single-board computers as microcontroller-based embedded systems<sup>2</sup>.

## **1.2** Problem Statements

Popular computer music languages in use today (Csound, Pd, SuperCollider, Faust, and ChucK) for sound synthesis and processing are designed for general-purpose computers or embedded systems running an operating system. Although some produce highly efficient code, they are not designed to run on or generate code for resource-constrained microcontroller-based embedded systems.

To reduce the overhead introduced by running an operating system on a resourceconstrained system it is paramount to run bare metal. Programming bare metal systems is not trivial and requires expert knowledge of the target device making them inaccessible to artists, hobbyists, and "do-it-yourself" enthusiasts.

Microcontroller cores designed to perform digital signal processing tasks come with

<sup>&</sup>lt;sup>2</sup>An embedded system is a dedicated computer system designed and embedded in a device that includes various electrical and mechanical components.

dedicated digital signal processing libraries that are optimized for the core. Abstracting these libraries and giving the user the ability to utilize them during code generation is of utmost importance to take full advantage of the device's capabilities and optimize for it.

Microcontrollers communicate with the outside world through peripherals. Software running on a microcontroller, usually referred to as firmware, controls and communicates with these peripherals through drivers<sup>3</sup>. Different microcontroller manufacturers have different hardware implementations and usually provide drivers for them. This renders code generated for one target useless for another target. Separating semantics from implementation and abstracting hardware and drivers in a uniform way across manufacturers is one way to enable moving code from one device to another.

Modern microcontrollers can have more than one core or be part of a heterogenous system. Concurrency and data integrity become immediate concerns that need to be addressed especially when memory is shared between cores or computations are distributed across components of a heterogenous system.

## **1.3 Research Questions**

The following are the research questions that arise from the problem statements described above as well as ones related to designing a programming language for sound synthesis, processing, and interaction design.

<sup>&</sup>lt;sup>3</sup>A piece of software that abstracts hardware and enables an operating system or other software to communicate with the hardware.

- Q1 Can a language for sound synthesis, processing, and interaction be designed with only a few syntactic constructs that meet the following specifications?

- Simplify or unify the interfacing between entities

- Enable parallel expansion of entities and interfaces

- Abstract the static and dynamic allocation of entities

- Perform computations on a per sample basis, on real and complex numbers, in both time and frequency domains

- Handle synchronous and asynchronous data and events

- Abstract threading and thread synchronization

- Enable seamless interfacing of entities running at different rates and in different threads

If one were to design a modern language for sound synthesis, processing, and interaction design, the language should meet most of, if not all, the specifications put forward by this question. It is also important to incorporate most of the features from existing music programming languages that have made them popular and successful among their users. Given the processing capabilities of host computers today, it is possible to design complex interpreters that not only parse, process, and interpret user code in fractions of a second but also analyze the code and recommend potential optimizations to the user.

Q2 How can the unit generator / processor approach be adapted to resource-constrained systems to enable optimized code generation with the smallest memory footprint?

How and to what extent can a user control the optimization? How would the units behave in a multi-threaded or heterogenous environment?

The unit generator / processor design approach has been incorporated into almost all music programming languages since its inception as part of MUSIC III in the sixties by Max Mathews. In modern computer music languages, designed around the object-oriented programming paradigm, unit generators and processors are abstracted as classes from which instances of these units are created. Depending on the type of the unit, the class that represents it might incorporate states. In a multi-core or heterogenous system, where control and signal computations can be distributed across various threads, this abstraction of unit generators might not meet the optimization goals required by resource-constrained targets because it would result in the need for a class to accommodate various concurrency scenarios.

Q3 Could various hardware components (inputs, outputs, clocks, cores, etc.) and software architectures (application programming interfaces, real-time operating systems, etc.) be abstracted in a unified way?

To make the user code portable from one target to another the underlying hardware and software architectures need to be abstracted. This can be achieved by separating semantics from implementation.

Q4 *Can various types of interactions with the system be abstracted in a unified way?* Interactions with a microcontroller-based embedded system can come in various forms and from multiple sources. These interactions could be used to control the sound synthesis and processing parameters on the system. Interactions could come from a knob or switch, a sensor, a periodic or aperiodic impulse train, a message over a serial bus peripheral or over a network (following message protocols like MIDI[1] or Open Sound Control (OSC)[2]). Abstracting these interactions in a unified way and incorporating it into the language would allow the user to seamlessly switch from one interaction type to another without having to modify the core synthesis and processing blocks.

## 1.4 Contributions

This dissertation makes the following contributions to the field of computer music in general and to sound synthesis and processing in particular.

## 1.4.1 A New Syntax

Stride presents a new syntax to design signal processing algorithms as well as to implement and develop sound synthesis techniques with real-time control. The syntax is made up of only two constructs. The syntax is mostly declarative which allows for expanding the capabilities of the language by adding new "blocks". Entities in the language are connected to each other with a single operator. Unlike regular dataflow languages where only data is exchanged between connected entities, in Stride information provided by the user in the code is also exchanged between entities, such as rates and domains<sup>4</sup>.

<sup>&</sup>lt;sup>4</sup>A context in Stride where code is executed. The concept is discussed in detail in this dissertation.

#### 1.4.2 Signals with Rates and Domains

In Stride, data exchange between entities is abstracted through signals. Stride takes a novel approach by allowing the user to specify the rate and the domain of every signal, giving the user control over how often an expression where the signal appears is evaluated and in which thread and computation device this evaluation takes place. The rate and domain of signals specified by the user propagate throughout the code to replace placeholder aliases of other signals that are embedded within modules. This approach puts the user in full control of generating code optimized for a given target.

#### 1.4.3 Code Generation

Modules in Stride, which abstract unit generators and processors, translate to stateless C++ template classes through its code generator and helper classes. The generated code significantly differs from ones that usually appear in music synthesis and processing libraries or ones generated by other music programming languages. This approach results in classes with independent processes mapped to domains which in turn can be distributed across threads and devices, thus breaking down and distributing computations defined inside a unit generator or processor.

#### 1.4.4 Concurrency

Stride incorporates a flexible concurrency model that is controlled by the user by defining policies controlling shared memory between domains. This model allows for the segmentation and distribution of processes across threads and devices while maintaining data integrity and avoiding race conditions and priority inversions.

## 1.5 Dissertation Structure

This dissertation is presented through the following chapters:

In chapter 2, "Survey of Music Programming Languages", we present a set of popular music programming languages in use today and discuss their limitations or incompatibility with targeting resource-constrained systems. We also present concurrent research related to the problem statements and research questions posed and addressed by this dissertation.

In chapter 3, "Faust and Targeting Microcontrollers", we discuss the limitations of Faust when it comes to generating optimized code for a microcontroller-based embedded system. We also identify a few optimization schemes that could result in efficient code for such systems.

In chapter 4, "Improvements with Stride", we introduce a new programming language and its syntax through a simple sine oscillator example, we demonstrate how the user of this language could generate efficient and optimized code. In chapter 5, "Signals, Rates, Domains, and Modules", we present the core building blocks of Stride and discuss their semantics and behaviors. We demonstrate the use of these blocks through examples of synchronous and asynchronous frequency modulation.

In chapter 6, "Domains and Concurrency", we present the user-controlled concurrency scheme built into the language and discuss how it affects the code generation process.

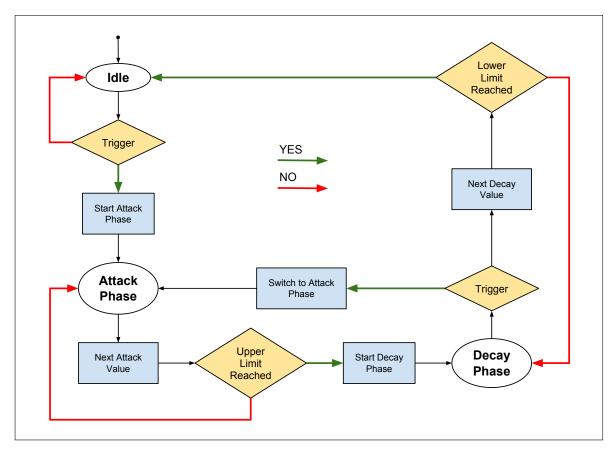

In chapter 7, "Interaction Design with Triggers and Reactions", we demonstrate how interaction is modeled and designed in Stride by presenting additional core building blocks of the language. We also demonstrate how a state machine is created in Stride.

In chapter 8, "Advanced Blocks in Stride", we present additional building blocks of the language, which bring advanced features to the language and simplify the user code.

In chapter 9, "Stride", we present the features of Stride as a programming language. We also present the language as a component of the Stride Environment which also comprises a compiler and an integrated development environment. We also present the formal definitions of the core and advanced building blocks of the language and expand on the semantics that control expressions in the language.

In chapter 10, "Conclusion", we summarize the research carried out to produce this dissertation and address its research questions. We also discuss related future work.

11

## **1.6** Permissions and Attributions

The syntax diagrams for the grammar were generated using Railroad Diagram Generator by Gunther Rademacher, URL: http://www.bottlecaps.de/rr/ui [accessed November 7, 2018].

All other figures, charts, and diagrams appearing in this dissertation have been created by the author for the purpose of this document.

## 1.7 Additional Notes

All Stride code examples included in this dissertation are shown in their expanded form. All block properties and their default values are explicitly stated, which is not generally required.

# **Chapter 2**

# Survey of Music Programming Languages

Targeting microprocessors and DSP boards with music programming languages to achieve real-time control in sound synthesis and processing has a long history dating back to the late seventies and early eighties. In this chapter we will briefly touch on a few of these languages and focus on ones that are still in use today or were introduced later for general-purpose computers. We will also mention some concurrent research and projects.

## 2.1 Music Programming Languages

One of the early examples of a music programming language targeting a DSP board is the 4CED language[3] designed to target the 4C machine[4] at Institut de recherche et coordination acoustique/musique (IRCAM), hosted on a PDP-11 computer, for realtime sound synthesis.

Max[5][6] (currently sold as a commercial product, Max/MSP, by Cycling '74 and Ableton) was developed to run on a NeXT machine as part of the IRCAM Music Workstation to target signal processing boards based on the intel i860 microprocessor[7].

A comprehensive list of music programming languages to target DSP boards along with their host machines can be found in The Computer Music Tutorial[8, chapter 17].

## 2.1.1 Csound (1985)

Csound[9] designed and developed by Barry Vercoe and introduced in 1985 followed the MUSIC-N model and was a translation of MUSIC11 into the C programming language (C), making it host independent.

In 1989 Csound was used to target Inmos transputers[10] to considerably enhance its speed of execution.

In 1990 a new version of Csound[11] was introduced with real-time capabilities which could run on a MacII host to target a real-time DSP system based on a Motorola DSP56000. The real-time capabilities of Csound with greatly expanded with the introduction of Csound Extended[12] where support for the SHARC 21060 DSP by Analog Devices was introduced.

#### **Comments on Csound**

Although still popular and in use today, the syntax of Csound is a markup language for defining instruments and a score, which seems outdated when compared to most modern programming languages since its roots are in the MUSIC-N family of languages.

To introduce new unit generators or algorithms that run efficiently the user has to write them in C and introduce corresponding opcodes into Csound using an Application Programming Interface (API). This presents a particular challenge when it comes to microcontrollers, specifically when it comes to using their optimized DSP libraries. A new opcode that performs the same task is required to target a different core.

Csound is not designed for single sample processing<sup>1</sup> and it only supports two rates: control rate and audio rate.

## 2.1.2 Pd - Pure Data (1996)

Pd[13] was introduced in 1996 by Miller Puckette based on his earlier work on Max and FTS[14] at IRCAM. Like Max, Pd is a graphical programming language. Unlike Max, Pd

<sup>&</sup>lt;sup>1</sup>The control rate could be temporarily set to one (setksmps 1). However, this is not efficient.

was designed to perform all control and audio processing on the host's CPU rather than target a DSP system.

Like Csound, Pd can be extended through an API to enable users to add their own control and audio processing code written in C.

#### **Comments on Pd**

Targeting microcontrollers with Pd is not ideal since Pd is designed to dynamically invoke objects' methods at runtime. For non-audio signals these methods are invoked based on events. Invoking methods dynamically adds an overhead which sometimes taxes the system more than the actual process the method accomplishes. One way to overcome this would be to take the signal graph from Pd and generate static target code from it. This approach has been successfully implemented by Enzien Audio with their Heavy compiler[15]. The compiler supports a limited list of Pd objects.

Since Pd follows the dataflow programming paradigm, it suffers from limitations when it comes to object-oriented programming concepts. Creating parallel processes or managing a large list of objects is not possible due to the lack of constructors and destructors.

Single sample processing in Pd is not possible (Max/MSP introduced Gen to achieve single sample processing). Pd runs at two rates. The first is the audio sampling rate and the second is the control rate where data is processed once per 64 samples of audio.

#### 2.1.3 SuperCollider (1996)

In 1996, James McCartney introduced SuperCollider[16], an environment for real time synthesis. It featured a programming language designed on the object-oriented programming paradigm. It supported closures and had a garbage collector.

Later versions of SuperCollider featured two applications, a client and a server, which communicated over a modified version of OSC[17]. The server ran the synthesis engine and the client ran on top of the language engine. Multiple clients could connect to a single server and perform in real-time.

SuperCollider has a synthesis class library which generates C++ code that can be loaded on its synthesis engine running on the server. The synthesis engine also has a C linkage API which allows users to write instruments in C and load them on the server.

Instead of supporting a single control rate, unit generators can be written to run at any power of two division of the audio clock rate. Values are linearly interpolated when connecting to unit generators running at different rates.

#### **Comments on SuperCollider**

SuperCollider's language syntax and architecture was a departure from the markup and graphical languages for music programming. Due to its architecture, SuperCollider is not suited for microcontroller-based embedded systems. However, it offers many valuable solutions that one needs to consider when designing a new language. SuperCollider can achieve single sample processing if the audio buffer size on the synthesis engine running on the server is set to one. However, this requires a machine capable of handling the load introduced by this change.

#### 2.1.4 Faust (2002)

Designed at Grame (Centre National de Création Musicale) by by Yann Orlarey et al., Faust[18] was first introduced in 2002. It is a purely functional programming language with an algebraic block diagram syntax.

Faust compiles its block diagram syntax to highly efficient C++ code which operates at the sample level. Operating at the sample level makes it possible to create recursions (sample feedback) and create low-level signal processing functions. These functions can then be brought together using high-level composition operators to create more complex signal processing functions.

Faust does not rely on any external modules or libraries to generate code and is selfcontained. The generated static C++ code could be compiled and used on any target as long as the target has a C++ compiler.

#### **Comments on Faust**

Faust would be the ideal candidate among the languages presented in this section to target microcontrollers. The following chapter is dedicated to discussing the capabilities and limitations of Faust when it comes to targeting embedded systems.

### 2.1.5 ChucK (2003)

ChucK, designed and developed by Ge Wang et al., was introduced in 2003. ChucK is a concurrent and strongly timed language for real-time sound synthesis, composition, and performance.

The syntax of Chuck is C-like and designed with the object-oriented paradigm. The ChucK operator (=>) is used to connect entities together. Because of its strong unified timing mechanism, it is capable of multi-rate events and control processing. ChucK code is dynamically compiled to ChucK virtual machine bytecode that runs on the Chuck Virtual Machine. This architecture allows for on-the-fly programming in ChucK. A "Shred" in ChucK abstracts threads and fits into the concurrency model built into ChucK. Single sample processing is supported in ChucK since the user is responsible for "advancing time" and can do so by the duration of a single sample.

#### **Comments on Chuck**

Because of its architecture and reliance on a virtual machine, ChucK is not suited for microcontroller-based embedded systems for sound synthesis and processing. However, many features of ChucK are worth considering when designing a new language, specifically the ChucK Operator which seamlessly enables the connection of entities running at different rates.

## 2.1.6 Discussion

Having reviewed some of the popular music programming languages in use today, Faust seems to be the best candidate to consider for targeting microcontrollers. Faust meets many of the desired specifications to target a resource constrained system, specifically its ability to generate efficient C++ code and define low-level signal processing functions.

Many features from the other languages are worth considering if one were to design a modern language, particularly ones that result in the new language meeting the specifications set forward in the introduction of this dissertation.

## 2.2 Concurrent Research

The following research works are closely related to that presented in this dissertation.

#### 2.2.1 Kronos

Kronos[19] is a functional high-level language and a just-in-time compiler[20]. It is well suited to build digital signal processing solutions due to its capability to generate high performance code. The language implements the functional reactive paradigm and can handle multi-rate processing.

## 2.2.2 WaveCore

WaveCore[21] is a coarse-grained reconfigurable processor (CGRP) architecture, based on the dataflow paradigm. It is designed to target any Field-Programmable Gate Array (FPGA) because it is designed in VHDL<sup>2</sup>, which is a target independent language. The WaveCore programming model is based on explicitly describing a dataflow graph in a declarative manner.

Prior to WaveCore, finite difference physical models of musical instruments were implemented on FPGAs that can be configured, modified, and played in real time[22]. However, WaveCore abstracts the implementation with a scalable and interconnected cluster of Processing Units, where each unit embodies a small floating-point RISC processor.

An experimental compiler has been designed to target the WaveCore Processor with Faust code. Kronos was also used to target the WaveCore Processor to design a lowlatency parallel graphic equalizer[23].

<sup>&</sup>lt;sup>2</sup>VHSIC (Very High Speed Integrated Circuit) Hardware Description Language

# Chapter 3

# **Faust and Targeting Microcontrollers**

Faust has its limitations when it comes to generating optimized code for a resourceconstrained microcontroller-based embedded system. This chapter will present some of the optimizations Faust performs and discuss the shortcoming of these optimizations when targeting microcontrollers. Some improvements will also be proposed to make the generated code better suited for a microcontroller.

## 3.1 A Simple Faust Example

Faust generates code in various languages including C, C++, Java, Web Assembly, LLVM IR, etc. In the following discussion, we will focus on the C++ version of the generated code. Almost all modern compilers targeting embedded systems compile target code from C and/or C++. Among the many programming languages, C and C++ are considered the de facto programming languages for modern embedded systems development[24, section 2.3.2].

By analyzing the code generated by Faust, the following optimizations are identified:

- Computing expressions that result in constant values throughout the execution of the program only once.

- Computing slow changing control variables once per audio rendering callback.

- Performing all remaining computations on a per sample basis in the audio rendering callback.

In the following sections we will look at a simple Faust example, a resonant low pass filter, to highlight Faust optimizations and analyze their impact on microcontrollerbased embedded systems. We will also propose some improvements in order to achieve further optimization.

The Faust code in Code 3.1 represents processing a signal through a resonant low pass filter with constant arguments.

```

1 import("stdfaust.lib");

2

3 // Cutoff Frequency

4 ctFreq = 500;

5 // Q Factor

6 q = 5;

7 // Gain

8 gain = 1;

9

10 // Resonant Low Pass

11 process = fi.resonlp(ctFreq,q,gain);

```

Code 3.1: Faust resonant low pass filter with constant arguments.

With C++ set as the target language, the Faust compiler generates a single class called mydsp (default compiler option) with multiple methods<sup>1</sup>. Out of these methods, two are relevant to this discussion.

The first method, called instanceConstant, is where values that remain constant throughout the execution of the program are computed. For the case of the resonant low pass filter with constant arguments, the method is shown in Code 3.2.

```

1 virtual void instanceConstants(int samplingFreq) {

2  fSamplingFreq = samplingFreq;

3  fConst0 = tanf((1570.79639f / min(192000.0f, max(1000.0f, float(

fSamplingFreq))));

4  fConst1 = (1.0f / fConst0);

5  fConst2 = (1.0f / (((fConst1 + 0.20000003f) / fConst0) + 1.0f));

6  fConst3 = (((fConst1 + -0.20000003f) / fConst0) + 1.0f);

7  fConst4 = (2.0f * (1.0f - (1.0f / mydsp_faustpower2_f(fConst0))));

8 }

```

Code 3.2: Faust generated instanceConstant method for a resonant low pass filter with constant arguments.

The second method is compute. This method is responsible for computing the audio samples to fill the audio buffer. The constant values computed in the first method are used in this one to compute the audio samples. For the case of the resonant low pass filter with constant arguments the compute method is shown in Code 3.3.

In the case where the arguments of the resonant low pass filter are constant, the compute method is efficient and optimized for a microcontroller. Only computations necessary to compute the audio samples are included in it. When the arguments of the resonant low pass filter are replaced with variables, the generated compute function is no longer efficient or optimized.

<sup>&</sup>lt;sup>1</sup>The generated code in its entirety is available in Appendix A

```

1 virtual void compute (int count, FAUSTFLOAT ** inputs, FAUSTFLOAT **

outputs) {

2

FAUSTFLOAT* input0 = inputs[0];

3

FAUSTFLOAT* output0 = outputs[0];

for (int i = 0; (i < count); i = (i + 1)) {</pre>

4

5

fRec0[0] = (float(input0[i]) - (fConst2 * ((fConst3 * fRec0

[2]) + (fConst4 * fRec0[1]))));

output0[i] = FAUSTFLOAT((fConst2 * (fRec0[2] + (fRec0[0] +

6

(2.0f * fRec0[1]))));

7

fRec0[2] = fRec0[1];

fRec0[1] = fRec0[0];

8

9

}

10 }

```

Code 3.3: Faust generated compute method for a resonant low pass filter with constant arguments.

Code 3.4 replaces the constant arguments in Code 3.1 with variable arguments. These variable arguments are controlled by horizontal sliders appearing on a Graphical User Interface (GUI).

```

1 import("stdfaust.lib");

2

3 // Cutoff Frequency Horizontal Slider

4 ctfreq = hslider("cutoffFrequency",500,50,10000,0.01);

5 // Q Factor Horizontal Slider

6 q = hslider("q",5,1,30,0.1);

7 // Gain Horizontal Slider

8 gain = hslider("gain",1,0,1,0.01);

9

10 // Resonant Low Pass

11 process = fi.resonlp(ctFreq,q,gain);

```

Code 3.4: Faust resonant low pass filter with variable arguments.

The instanceConstant and compute methods generated after replacing the constant arguments with variable ones are shown in Code 3.5.

As a result of these changes, variables that are evaluated in the compute method can be divided into two sets. The first set of variables are those designated by fSlow. Every time compute is called, these variables get evaluated only once before the code appearing in the for-loop is evaluated. The second set of variables are those evaluated inside the for-loop. For the rest of this discussion we will refer to the first set of variables as control variables and the second set as audio variables.

Audio variables are associated with computing the audio samples, while control variables are associated with the arguments passed to the resonant low pass filter in the Faust code. Generally, control signals in Faust relate to GUI elements, MIDI messages, OSC messages, or physical sensors.

```

1 virtual void instanceConstants(int samplingFreq) {

fSamplingFreq = samplingFreq;

2

fConst0 = (3.14159274f / min(192000.0f, max(1000.0f, float(

3

fSamplingFreq))));

4 }

5 virtual void compute(int count, FAUSTFLOAT** inputs, FAUSTFLOAT**

outputs) {

FAUSTFLOAT* input0 = inputs[0];

6

7

FAUSTFLOAT* output0 = outputs[0];

float fSlow0 = (1.0f / float(fHslider1));

8

9

float fSlow1 = tanf((fConst0 * float(fHslider2)));

10

float fSlow2 = (1.0f / fSlow1);

float fSlow3 = (((fSlow0 + fSlow2) / fSlow1) + 1.0f);

11

float fSlow4 = (float(fHslider0) / fSlow3);

12

float fSlow5 = (1.0f / fSlow3);

13

14

float fSlow6 = (((fSlow2 - fSlow0) / fSlow1) + 1.0f);

float fSlow7 = (2.0f * (1.0f - (1.0f / mydsp_faustpower2_f(fSlow1

15

))));

for (int i = 0; (i < count); i = (i + 1)) {</pre>

16

fRec0[0] = (float(input0[i]) - (fSlow5 * ((fSlow6 * fRec0[2]))

17

+ (fSlow7 * fRec0[1]))));

18

output0[i] = FAUSTFLOAT((fSlow4 * (fRec0[2] + (fRec0[0] +

(2.0f * fRec0[1]))));

19

fReco[2] = fReco[1];

fReco[1] = fReco[0];

20

21

}

22 }

```

Code 3.5: Faust generated instanceConstant and compute methods for a resonant low pass filter with variable arguments.

## 3.2 Computing Constants

When targeting microcontrollers, one of the optimization goals is keeping the size of the compiled executable binary file small. The executable file is usually loaded and stored in flash memory<sup>2</sup>. Microcontrollers have limited onboard flash memory and this limitation should be taken into consideration.

In Code 3.5, the only argument passed to the instanceConstant method is the sampling rate. Some of the constants are computed based on this sampling rate. This approach is generally ideal, since the class generated by Faust gets incorporated into a platform specific target application where the sampling rate is usually passed at runtime. An audio plugin used in a Digital Audio Workstation (DAW) is one example, where the sampling rate needs to match that of the DAW when the plugin is instantiated.

However, if the sampling rate is predetermined at compile time, computing the constant values during code generation would result in a smaller binary file and faster startup time.

The code generation in Faust could be tailored to such use cases by adding a compiler option and passing the sampling rate at compile time, thus making the compiler generate more suitable code for a microcontroller-based embedded system.

$<sup>^{2}\</sup>mbox{A}$  solid-state non-volatile computer storage medium that can be electrically erased and reprogrammed.

### 3.3 Processing Loads and Relative Rates

Minimizing the amount of computations on a microcontroller is another optimization goal. Unnecessary computations result in additional power consumption and have a direct effect on the responsiveness of a microcontroller-based embedded system. Setting the size of the audio buffer to a single sample to achieve glitch-free real-time performance (single sample latency) is possible when running on a bare metal microcontroller. However, to realize this the audio rendering callback needs to run as efficiently as possible.

In Faust the relative computation time spent on computing control variables and audio variables in the compute method is dependent on the buffer size of the audio rendering callback.

As the buffer size of the audio rendering callback increases, the ratio of CPU cycles required to compute control variables to those required to computing audio variables decreases. Regardless of the audio buffer size, the amount of computation required to compute the control variables stays constant, while the amount required to compute the audio buffer.

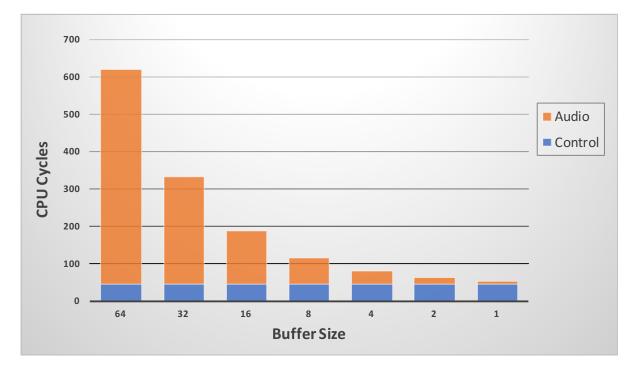

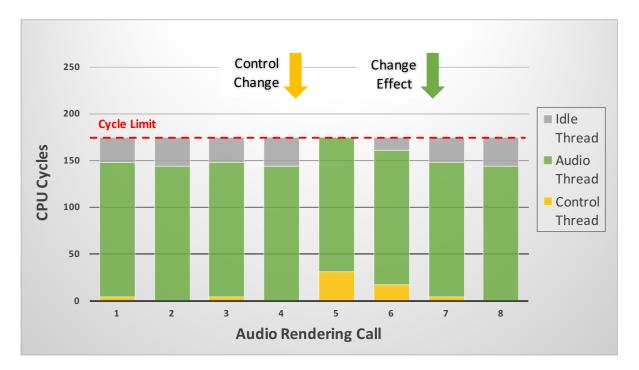

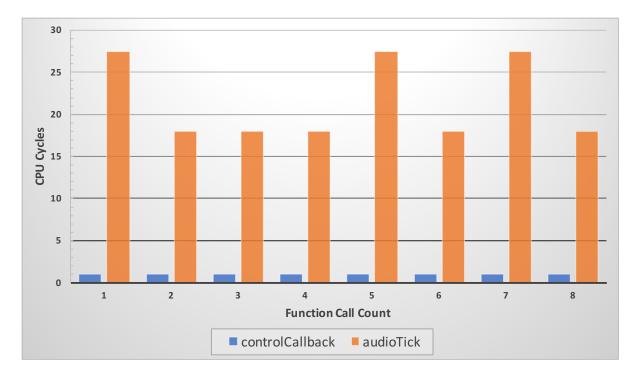

For the resonant low pass filter with variable arguments this relationship is shown in Figure 3.1. If we only consider the arithmetic and trigonometric operations in the compute method, 44.5 CPU cycles are needed to compute the control variables per audio rendering callback and 9 CPU cycles to compute each audio sample<sup>3</sup>.

For large buffer sizes this is not an issue. However, as the buffer size decreases, the

<sup>&</sup>lt;sup>3</sup>The CPU cycles are based on an analysis in Appendix B.

Figure 3.1: CPU cycles required per audio rendering callback for various buffer sizes.

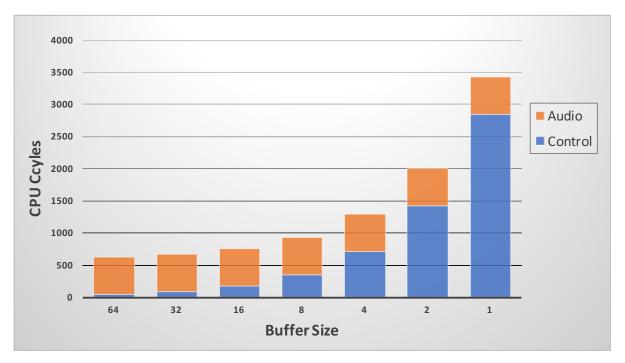

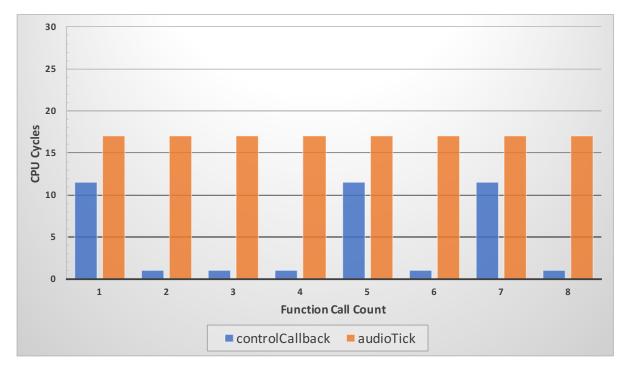

effort spent on computing control variables per audio rendering callback becomes significant. With the audio buffer size set to 64 samples, 7.17% of the CPU cycles required to render the audio samples in the audio buffer are for computing the control variables. If the buffer size is reduced to a single sample, 83.18% of the CPU cycles are for computing the control variables. Reducing the buffer size results in a significant reduction in the computation efficiency, given the control signals will not change at the audio sampling rate. The reduction in computation efficiency is shown in Figure 3.2.

Spending 83.18% of computation time per audio rendering callback to compute control variables that might never change or change at a very slow rate relative to the audio sampling rate is far from efficient.

There are multiple improvements that can be made to achieve an efficient audio ren-

Figure 3.2: CPU cycles required to process 64 audio samples per audio rendering callback for various buffer sizes.

dering callback for the case of the resonant low pass filter with variable arguments. The first would be by adding a simple comparison to check if any control variable changed from the previous callback.

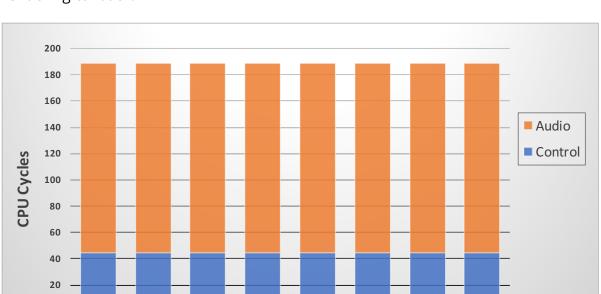

Figure 3.3 shows the CPU cycles required for the resonant low pass filter with variable arguments when the audio buffer size is set to 16 samples and Figure 3.4 shows the impact of adding a comparison check on the control variables in the audio rendering callback to the CPU cycles.

A further improvement could be made by computing the control variables on a thread different from the one where the audio rendering callback executes. This would result in a very efficient audio rendering callback where only audio variables are computed. The thread responsible for computing the control variables would have a lower prior0

1

2

3

ity and could be set to run at a lower rate than the thread responsible for the audio rendering callback.

**Compute Method Call**

5

6

7

8

4

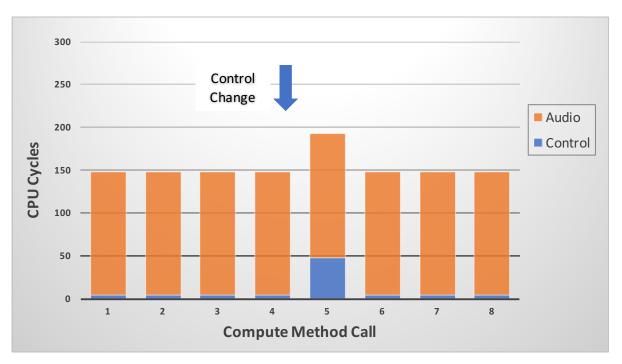

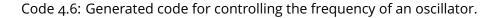

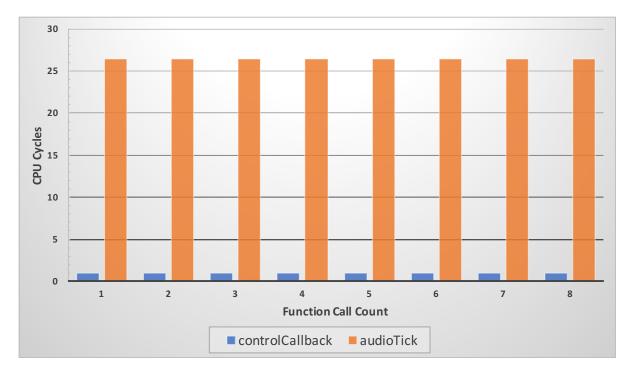

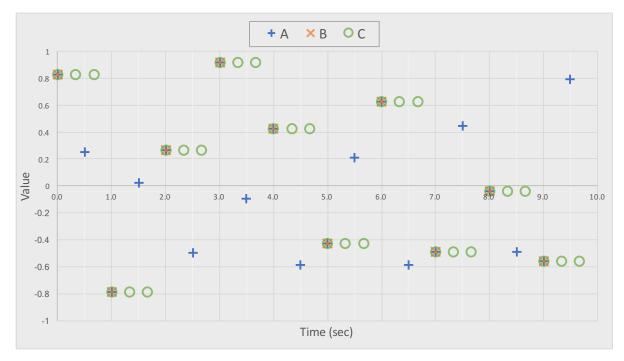

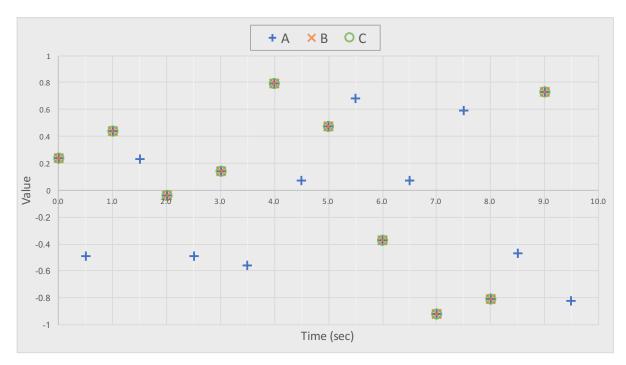

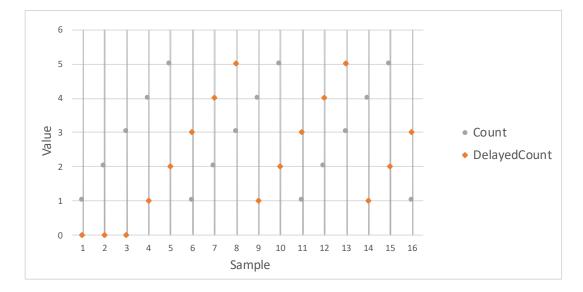

A potential thread profile is shown in Figure 3.5 with 175 CPU cycles available to the processor relative to the rate of the audio rendering callback<sup>4</sup>. The control thread rate is set to half of the audio thread. The chart shows how a control variable change would affect the system and when it would affect the audio samples.

The two-thread approach will not only affect the CPU cycles and performance but also the relative update rate between control and audio variables. The relative rate between processing control variables and audio variables in Faust is fixed and dependent on the audio buffer size. Moreover, both types of variables in Faust are computed within the same method making them synchronous. The relative rate and

Figure 3.3: CPU cycles required per audio rendering callback for a 16-sample buffer size.

<sup>&</sup>lt;sup>4</sup>CPU cycles required for context switching are ignored.

Figure 3.4: CPU cycles required per audio rendering callback for a 16 sample buffer size with a control variable change check.

Figure 3.5: CPU thread profile showing the impact of a control change and its effect.

synchronicity affect the output generated by Faust and tie it directly to the size of the audio buffer. With a two-thread implementation, the control and audio variables become asynchronous and the relative rate between them becomes independent of buffer size.

To realize this two-thread approach, significant changes need to be made to the Faust code generation engine. Even if the code generation engine is modified to accommodate this approach, the relationship between various signals will still be target specific and dictated by the specificities of the implementation of the target. Hence, the user will be constrained by the implementation. Giving the user the ability to decide how often and in which thread variables are computed enables them to optimize and tune a system to their need.

## 3.4 Concurrency

Modern microcontrollers can run complex tasks simultaneously in real-time. Managing concurrency plays an important part in achieving the required real-time performance. Thus, giving the user control over the concurrency scheme is crucial.

The Faust framework does not have a concurrency model built into it. Updating control values and computing audio samples based on control value changes happen sequentially, thus eliminating the need for a concurrency model in the Faust framework itself.

All controls (GUI, MIDI, hardware, etc.) of a target platform are mapped to Faust wid-

gets that are updated on every audio callback. This update happens prior to computing the audio samples and involves the sampling and updating of every control value. This approach moves the necessity of having a concurrency model in the Faust framework to having one in the target platform's software. Instead of defining a concurrency model, target platforms often rely on the atomic data types supported by their processor. When sampled, all control values are stored as FAUSTFLOAT, a type definition (typedef) for a floating-point data type in the Faust framework.

To demonstrate this interaction between the Faust framework and a target platform we will consider the Bela platform<sup>5</sup>. Excerpts of the bela.cpp target platform definition file<sup>6</sup> are shown in Code 3.6.

The Faust framework expects a target platform definition file to include and implement two methods: setup() and render(), among other classes and methods.

In the setup() method (lines 31 to 48), after allocating memory for the audio buffers, an instance of the DSP object is created. The DSP object is then linked to the user interface of the target platform, where Faust widgets are mapped to controls. By establishing this link, the DSP instance gains access to the sampled control values through widgets.

In the render() method (lines 50 to 58), prior to calling the compute() method where the audio samples are calculated (as discussed in section 3.1), the update() method is called on the user interface instance to read and/or write all the controls and synchronize them. The update occurs through Faust widgets.

<sup>&</sup>lt;sup>5</sup>https://bela.io/ [accessed November 7, 2018]

<sup>&</sup>lt;sup>6</sup>The platform definition file in its entirety is available in Appendix A

The update() method of the user interface in turn calls the BelaWidget.update() method defined as part of a widget class of the target platform (lines 2 to 17) for every single control that is being utilized. For example, if the 8th analog input on the Bela board is used as a control input, the kANALOG\_7 (line 10) case is invoked where the analogReadNI() method (line 11) is called to fetch the value from the corresponding Analog to Digital Converter (ADC) input. The analogReadNI() method is implemented as part of the Bela platform and not Faust. If the Bela platform implements a concurrency model it would appear in the analogReadNI() method.

```

1 // The widget class where the update method is impelmeneted

2 class BelaWidget

3 {

4

. . .

5

public:

6

. . .

void update(BelaContext *context) {

7

switch (fBelaPin) {

8

9

. . .

10

case kANALOG_7:

*fZone = fMin + fRange * analogReadNI(context, 0, (int)

11

fBelaPin);

12

break;

13

. . .

14

}

15

}

16

. . .

17 };

18

19 . . .

20 // Array of pointers to context->audioIn data

21 FAUSTFLOAT **gFaustIns;

22 // Array of pointers to context->audioOut data

23 FAUSTFLOAT **gFaustOuts;

24 . . .

25 // Bela User Interface (Hardware)

26 BelaUI gControlUI;

27 // Pointer to a Faust DSP instance

28 dsp * gDSP = NULL;

29 . . .

30

31 bool setup(BelaContext *context, void *userData) {

32

33 // Allocate deinterleaved inputs

```

Faust and Targeting Microcontrollers

```

gFaustIns = new FAUSTFLOAT *[context->audioInChannels];

34

35

// Allocate deinterleaded output

36

37

gFaustOuts = new FAUSTFLOAT *[context->audioOutChannels];

38

39

// Faust DSP instance declaration

40

gDSP = new mydsp ();

41

. . .

42

// Initializing the DSP instance

43

gDSP -> init (context -> audioSampleRate);

// Mapping Bela Analog/Digital IO and Faust widgets

44

gDSP ->buildUserInterface(&gControlUI);

45

46

47

return true;

48 }

49

50 void render(BelaContext *context, void *userData) {

51

// reads Bela pins and updates corresponding Faust Widgets zones

52

53

gControlUI.update(context);

54

// synchronize all GUI controllers

55 GUI::updateAllGuis();

56

// process Faust DSP

gDSP->compute(context->audioFrames, gFaustIns, gFaustOuts);

57

58 }

```

Code 3.6: Excerpts from the platform definition file for the Bela platform.

## 3.5 Vector Processing

Some microcontrollers support advanced instruction sets that are capable of operating on multiple data with a single instruction. They are known as Single Instruction Multiple Data (SIMD) instructions. Most compilers are capable of translating C++ code into machine code by utilizing these advanced instructions. However, special data types and code organization are required to trigger the compiler to use these instructions. The original version of Faust (currently known as Fausto) has a compiler option that directs the code generator to generate C++ code suitable for vector operations. When the option is enabled, the code generator restructures the C++ code in a way to direct the C++ compiler to use SIMD instructions. An example of using this option is shown in [25], where the generated code performs better when compiled with an Intel ICC 11.0 compiler. However, the same code might not trigger the use of SIMD instructions when compiled with a different compiler.

A better approach is needed for the users to express their intent for vector processing and the use of SIMD instructions. The approach should not be tied to a particular compiler or compilers.

## 3.6 Libraries and APIs

Many microcontrollers come with dedicated libraries optimized to perform specific tasks. These libraries are optimized for performance and size. An example of such a library is the CMSIS DSP Software Library developed by ARM for the Cortex-M series[26]. The library contains a list of optimized signal processing functions. Having the ability to access these libraries is an advantage when it comes to generating efficient code. One way to access them would be through a Foreign Function Interface (FFI) designed into a language.

Faust does not have a FFI mechanism to access such libraries and does not offer a way to utilize these libraries during code generation.

Microcontroller manufacturers also provide APIs to access resources on a device and configure them. If a high-level code generation language like Faust lacks a FFI, modifying configurations or changing the state of resources would not be possible through Faust user code. Configurations and resource allocations will have to be hard coded in external files specific to each platform.

## 3.7 Summary

In this chapter we identified a few optimization schemes that could result in the generation of efficient code for resource-constrained microcontroller-based embedded systems. We demonstrated how CPU processing loads and relative rates between variables have a big impact on efficiency. Allowing users to control rates and the distribution of computations across multiple threads could result in drastic improvements on the real-time performance of a system by making it more efficient. Allowing users to control the concurrency model could yield similar improvements. Further optimizations could be achieved through building a FFI into the language to access optimized libraries as well as configure and manage device resources.

# Chapter 4

# **Improvements with Stride**

In the previous chapter we proposed some code optimization strategies to target resource-constrained microcontroller-based embedded system. One of the strategies was to control the relative rates at which computations are performed and to distribute computations across multiple threads. In this chapter we present a new language and its syntax. This new language enables the user to control the code generation process to realize this strategy. We will demonstrate this with a simple example.

## 4.1 An Oscillator with Frequency Control

A sine oscillator with frequency control is a basic unit generator. In this section we will examine a simple implementation of this unit generator. A simple sine oscillator with frequency control can be implemented by tracking its phase over time. The output of the oscillator is the trigonometric sine of the phase. The phase is incremented by a phase increment after computing each output. The phase increment is calculated based on the desired frequency and sampling rate. The phase is wrapped when its values is equal to or greater than two pi. This simple sine oscillator implementation is shown in Code 4.1 as a function in the C language.

Four expressions (lines 7, 10, 13, and 16) are evaluated every time the SinOsc function is called. If the frequency of the oscillator does not change from one function call to the next, calculating the PhaseIncrement is not necessary. That is, out of the four expressions only the ones directly related to the Phase need to be evaluated to compute the next oscillator output.

```

1 #define M_PI 3.14159265359

2

3 void SinOsc(float &output, float frequency) {

4

static float Phase, PhaseIncrement = 0.;

5

6

// Compute the phase increment relative to the frequency and

sampling rate

7

PhaseIncrement = 2 * M_PI * frequency / SamplingRate;

8

9

// Compute the sin of the phase as the output

10

output = sin(Phase);

11

12

// Increment the phase

Phase += PhaseIncrement;

13

14

15

// Wrap the phase if it is greater than two Pi

if (Phase >= 2 * M_PI) Phase -= 2 * M_PI;

16

17 }

```

Code 4.1: A simple sine oscillator with frequency control in C.

## 4.2 A New Language

Before attempting to generate code, we will introduce a new language and its syntax. This language is called Stride. Stride will enable the user to declare signals, invoke modules, and connect them to create a dataflow graph. Stride will also enable the user to control its code generator to optimize the generated code.

The new language has two constructs: Block Declarations and Stream Expressions. We will introduce the syntax of these constructs in the following subsections.

#### 4.2.1 Block Declarations

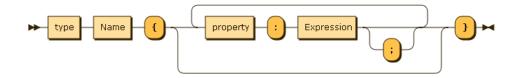

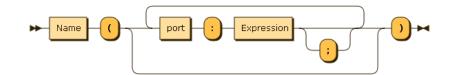

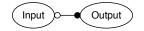

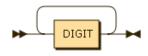

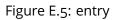

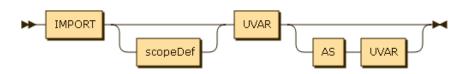

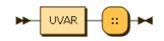

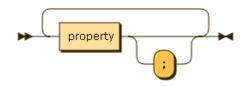

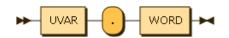

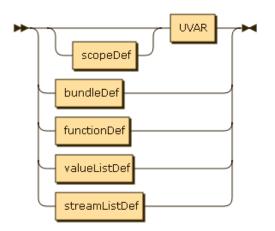

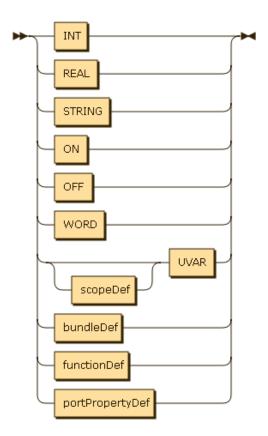

The first construct of the new language is the block declaration. The syntax diagrams to construct declarations are shown in Figure 4.1 and Figure 4.2.

Every block declaration starts with a type and a name. A declaration encloses a set of assignable properties. Block declarations with different types have different properties. The syntax diagram in Figure 4.1 is for a block declaration. Its corresponding grammar is:

```

Block ::= type Name '{'(property ':' Expression ';'?)*'}'

```

Figure 4.1: Block declaration syntax diagram.

Code 4.2 is an example block declaration. The block is of type signal and is called Block. The signal block has four properties called default, rate, domain, and meta. They are assigned the values 0.0, AudioRate, AudioDomain, and "A signal block" respectively.

| 1 | <pre>signal Block {</pre> |                  |   |                     |

|---|---------------------------|------------------|---|---------------------|

| 2 | default:                  | 0.0              | # | Default value       |

| 3 | rate:                     | AudioRate        | # | The signal's rate   |

| 4 | domain:                   | AudioDomain      | # | The signal's domain |

| 5 | meta:                     | "A signal block" | # | Meta information    |

| 6 | }                         |                  |   |                     |

Code 4.2: A block declaration of type signal called Block.

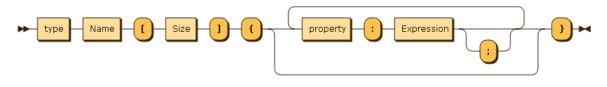

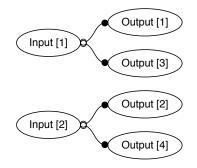

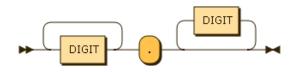

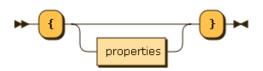

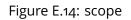

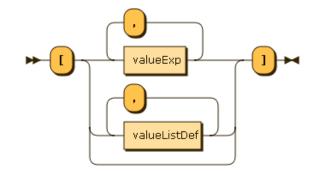

The syntax in Figure 4.2 is a block bundle declaration. Blocks in a bundle share the same type and property assignments. The grammar for a block bundle declaration is:

```

Bundle ::= type Name '['Size']' '{'(property ':' Expression ';'?)*'}'

```

Figure 4.2: Bundle declaration syntax diagram.

Code 4.3 is an example block bundle declaration. The bundle is of type signal and it is called Bundle. The bundle is composed of two signal blocks.

A block in a bundle can be accessed through indexing. The first block in the bundle is accessed by Bundle[1] and the second by Bundle[2].

```

1 signal Bundle [2] {

2

default:

# Default value

1.0

AudioRate

3

# The signal's rate

rate:

4

domain:

AudioDomain

# The signal's domain

5

meta:

"A signal bundle"

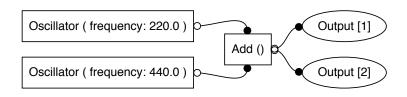

# Meta information

6 }

```

Code 4.3: A bundle declaration of type signal and size 2 called Bundle.

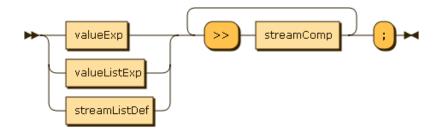

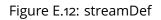

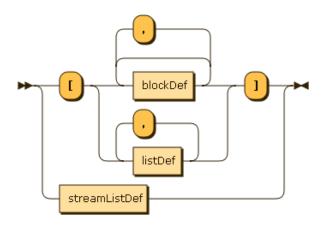

### 4.2.2 Stream Expressions

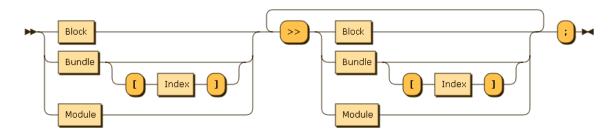

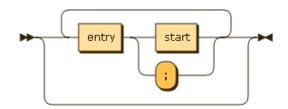

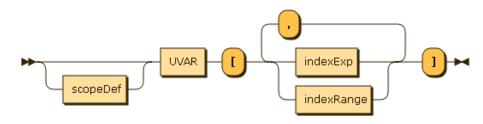

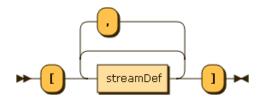

The second construct of the new language is the stream expression. The syntax diagram to construct a stream expression is shown in Figure 4.3.

Figure 4.3: Stream expression syntax diagram.

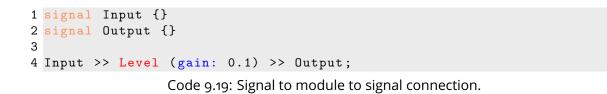

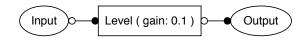

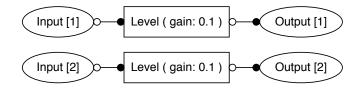

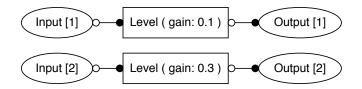

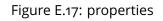

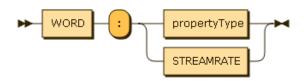

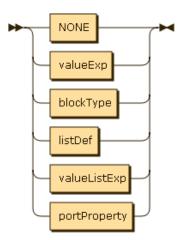

A stream expression is constructed by connecting blocks, bundles and/or modules<sup>1</sup> using the stream operator >>. The grammar for a stream expression is:

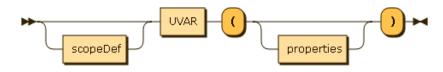

A module encapsulates blocks, bundles, and stream expressions to perform specific operations. The syntax diagram to invoke a module in a stream expression is shown in Figure 4.4 and its corresponding grammar is:

<sup>&</sup>lt;sup>1</sup>Modules will be covered in detail in the following chapter.

```

Module ::= Name '(' ( port ':' Expression ';'? )* ')'

```

Figure 4.4: Module invocation syntax diagram.

Code 4.4 is an example stream expression. The Input signal is connected to the main input port<sup>2</sup> of the Process module. The main output port of the Process module is connected to the Output signal. The Process module has a single property port called property. The property port is connected to a signal called Control.

```

1 signal Input {}

2 signal Output {}

3 signal Control {}

4

5 Input >> Process ( property: Control ) >> Output;

Code 4.4: A stream expression.

```

## 4.3 Code Generation for an Embedded Platform

Now that we have defined a new language and its syntax, we will use it to target a microcontroller-based embedded system. We will deploy a sine oscillator with frequency control on the target platform and generate efficient and optimized code for it.

<sup>&</sup>lt;sup>2</sup>Ports will be covered in detail in the following chapter.

Let us imagine an audio development board with a microcontroller as its main processor. The microcontroller is coupled with an audio codec<sup>3</sup> with a mono output. A rotary potentiometer is connected to one of the microcontroller's ADC pins. We will refer to this audio development board as the platform.

The goal is to generate code for the platform to play a sine wave though the mono audio output while controlling the wave's frequency through the potentiometer.

Let us assume we have a code generator that could add code to a pre-existing template. The template contains configuration code for the platform and presents the code generator with two functions assigned to hardware triggered callbacks. The code generator can insert code into these two functions. The first function is called audioTick. The audio output will be computed in the audioTick function. The second function is called controlCallback. In this function the potentiometer's value will be captured. To simplify the analysis, let us assume audioTick and controlCallback will be called at the same rate and audioTick in running on a thread that has a higher preemption priority over the thread where controlCallback is running.

#### 4.3.1 Oscillator with Frequency Control

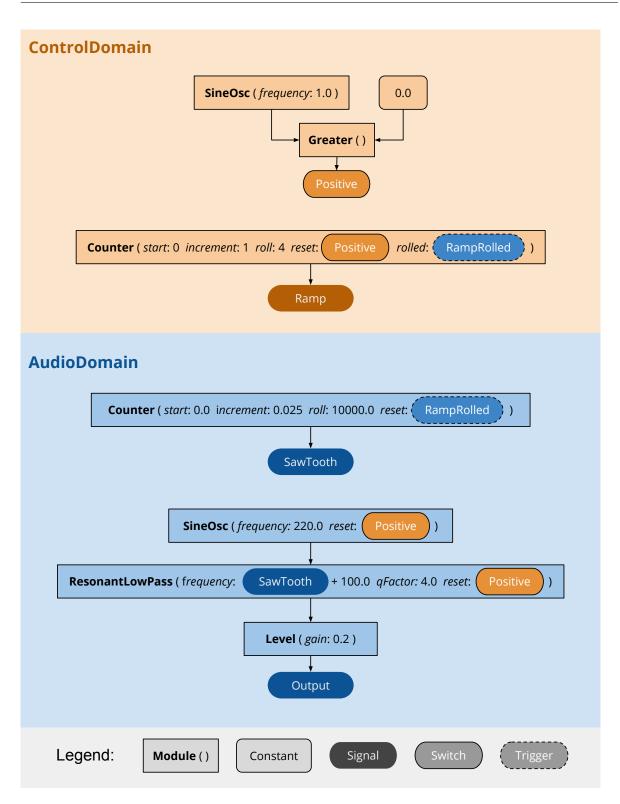

Using the new language and its syntax, we declare and define the setup we are trying to realize on the platform. The code is shown in Code 4.5.

The code consists of a block declaration (lines 1-5) and two stream expressions (lines 7-12 and 14-18).

<sup>&</sup>lt;sup>3</sup>A device or computer program for encoding or decoding a digital data stream or signal.

The declaration is of type signal and is called Frequency. Three of the signal's properties are shown in the code. The first property, default, sets the initial value of the signal. The second property, rate, sets the rate of the signal and is set to AudioRate. The third property, domain, sets the domain of the signal and is set to AudioDomain.

A domain abstracts a function. On this platform, AudioDomain abstracts the audioTick function. The audioTick function has a fixed callback rate, equal to the audio sampling rate. AudioRate abstracts this rate.

```

1 signal Frequency {

default: 440.0

2

rate: AudioRate

domain: AudioDomain

3

4

5 }

6

7 ControlIn[1]

8 >> Map (

9

55.0

minimum:

10

maximum:

880.0

11)

12 >> Frequency;

13

14 Oscillator (

"Sine"

15

type:

16

frequency: Frequency

17)

18 >> AudioOut;

```

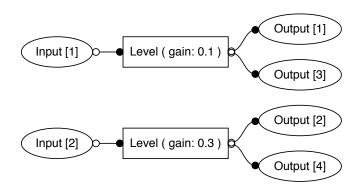

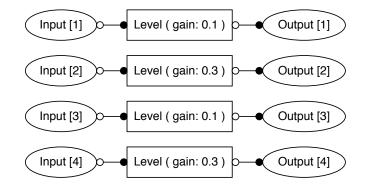

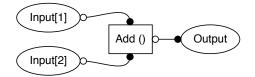

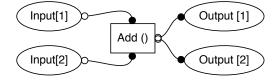

Code 4.5: Stride code to control the frequency of a sine oscillator.