# **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Energy-Efficient 60GHz Phased-Array Design for Multi-Gb/s Communication Systems

#### **Permalink**

https://escholarship.org/uc/item/09z098bd

#### **Author**

Kong, Lingkai

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

# Energy-Efficient 60GHz Phased-Array Design for Multi-Gb/s Communication Systems

by

Lingkai Kong

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Ali M. Niknejad Professor Paul K. Wright

Fall 2012

# Energy-Efficient 60GHz Phased-Array Design for Multi-Gb/s Communication Systems

Copyright 2012 by Lingkai Kong

#### Abstract

Energy-Efficient 60GHz Phased-Array Design for Multi-Gb/s Communication Systems

by

#### Lingkai Kong

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Elad Alon, Chair

Recent advance in wireless technologies has enabled rapid growth of mobile devices. Consequently, emerging applications for mobile devices have begun demanding data rates up to multiple Gb/s. Although advanced WiFi systems are approaching such data rates, the narrow bandwidth at ISM band fundamentally limits the achievable data-rate. Therefore, the unlicensed 7GHz of bandwidth at 60GHz band provides an opportunity to efficiently implement these communication systems with a potential to achieve >10Gb/s throughput. Besides the wider bandwidth, operating at higher frequency theoretically has higher achievable signal-to-noise ratio in area limited applications. This is because the maximum achievable antenna gain within limited aperture increases with frequency and it can be achieved using phased-array technique. This thesis therefore focuses on the design of 60GHz phased-array transceivers to support energy-efficient high data-rate communication systems.

Despite the advantages of 60GHz, mobile applications often require low power consumption as well as low cost implementation, making the design of 60GHz phased-array systems challenging. Taking into account the limited power budget, this research investigates the design choices of the number of elements in phased-array transceivers, and identifies that the overhead power is the bottleneck of energy efficiency. In order to reduce the overhead power in the transmitter, a new architecture using a fast start-up oscillator is proposed, which eliminates the need of explicit modulator and 60GHz LO delivery. Measurements has shown that the transmitter efficiency is boosted by more than 2X. More importantly, the overhead power is significantly reduced down to 2mW, making this architecture a good candidate for large number phased-array. On the other hand, suffering from the similar overhead problem, the receiver unfortunately could not share the same architecture. A different architecture that stacks the mixer on top of LO generation is thus proposed to reduce the power consumption in the receiver. This approach demonstrated a 2X power reduction in receiver overhead, and the resulted optimum number of receiver elements is close to 4.

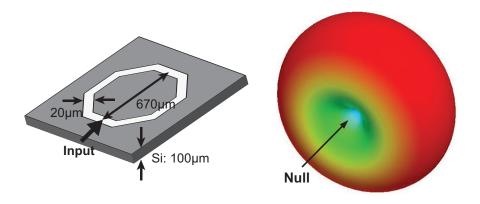

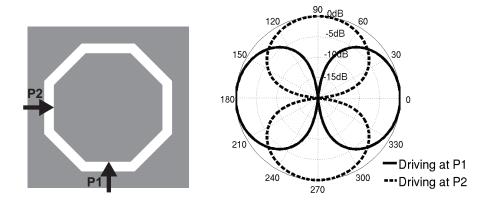

Besides using CMOS technologies, on-chip antenna is also studied in order to further reduce the system cost. Slot-loop antenna is identified as a good candidate because that its intrinsic ground plane eases the integration with the rest of circuitry. Although the simulation shows an efficiency as high as 30%, the planar nature of the on-chip antenna limits its coverage in end-fire directions. Antenna diversity is thus proposed to overcome this limitation by utilizing multiple drive points on the same antenna. Because the antenna is fully integrated on-chip, antenna diversity can be implemented without extra high frequency I/Os, eliminating the loss that would be introduced otherwise.

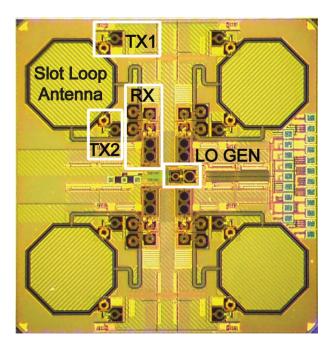

Using the proposed transceiver architectures, a 4-element phased-array with on-chip antennas was fabricated on TSMC's 65nm CMOS technology as a test vehicle. Consuming 50mW in the transmitter and 65mW in the receiver, this 10.4Gb/s phased-array covers a range larger than 45cm in all directions. This achieves a state-of-art energy-efficiency of 11pJ/bit. The 29mW/element power consumption also demonstrates the lowest power of a single phased-array element.

To My Parents

# Contents

| Contents |       |                                                            | ii   |  |

|----------|-------|------------------------------------------------------------|------|--|

| Li       | st of | Figures                                                    | v    |  |

| Li       | st of | Tables                                                     | viii |  |

| 1        | Intr  | roduction                                                  | 1    |  |

|          | 1.1   | The 60GHz Band                                             | 2    |  |

|          | 1.2   | Link Budget with Limited Area                              | 3    |  |

|          | 1.3   | Design Challenges                                          | 3    |  |

|          | 1.4   | Structure of Thesis                                        | 4    |  |

| 2        | Pha   | sed-Array Architectures for Energy-Efficient Communication | 5    |  |

|          | 2.1   | Introduction to Phased-Array                               | 5    |  |

|          | 2.2   | Choice of Number of Elements in a Phased-Array             | 7    |  |

|          |       | 2.2.1 Transmitter                                          | 7    |  |

|          |       | 2.2.2 Receiver                                             | 9    |  |

|          | 2.3   | Phased-Array Architectures                                 | 11   |  |

|          |       | 2.3.1 RF Phase Shifting                                    | 11   |  |

|          |       | 2.3.2 LO Phase Shifting                                    | 14   |  |

|          |       | 2.3.3 Baseband Phase Shifting                              | 15   |  |

|          |       | 2.3.4 Transmitter Phased-Array Architecture                | 16   |  |

|          | 2.4   | Phase Resolution                                           | 16   |  |

|          | 2.5   | Modulation Scheme                                          | 18   |  |

|          | 2.6   | Summary                                                    | 19   |  |

| 3        | Imp   | plementation of Baseband Phase Shifting                    | 20   |  |

|          | 3.1   | Implementation of Phase Shifter Resolution                 | 20   |  |

|          | 3.2   | Effect of I/Q Mismatch                                     | 21   |  |

|          | 3.3   | Implementations of VGAs                                    | 22   |  |

|          |       | 3.3.1 Variable Current Source                              | 22   |  |

|          |       | 3.3.2 Segmentation                                         | 23   |  |

|   |     | 3.3.3 Comparison                                     |

|---|-----|------------------------------------------------------|

|   | 3.4 | Power Reduction in Segmented Approach                |

|   | 3.5 | Phase Shifter Demonstration and Measurement Results  |

|   | 3.6 | Summary                                              |

| 4 | Fno | rgy-Efficient Phased-Array Transmitter 30            |

| 4 | 4.1 | Low Overhead Transmitter Architecture                |

|   |     |                                                      |

|   | 4.2 | 1                                                    |

|   | 4.3 | 1                                                    |

|   |     | 4.3.1 Oscillator Implementation                      |

|   |     | 4.3.1.1 Oscillator Startup Time                      |

|   |     | 4.3.1.2 Faster Startup                               |

|   |     | 4.3.1.3 Shut-down of Oscillation                     |

|   |     | 4.3.2 Power Amplifier Design                         |

|   | 4.4 | Timing Generation                                    |

|   | 4.5 | Transmitter Demonstration                            |

|   |     | 4.5.1 Waveform Measurement                           |

|   |     | 4.5.2 Phased-Array Functionality Validation          |

|   | 4.6 | Conclusion                                           |

| 5 | Ene | rgy-Efficient Phased-Array Receiver 49               |

|   | 5.1 | Stacked Mixer with LO Buffer                         |

|   | 5.2 | Hybrid Design                                        |

|   | 5.3 | Incorporating the Mixer with the 60GHz LO Generation |

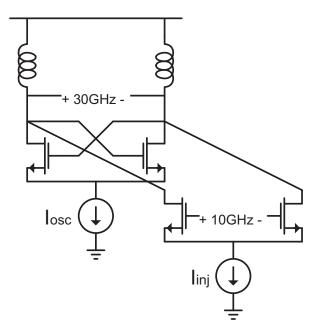

|   |     | 5.3.1 Stacked 30GHz VCO with Mixer                   |

|   |     | 5.3.2 Stacked Push-Push with Mixer                   |

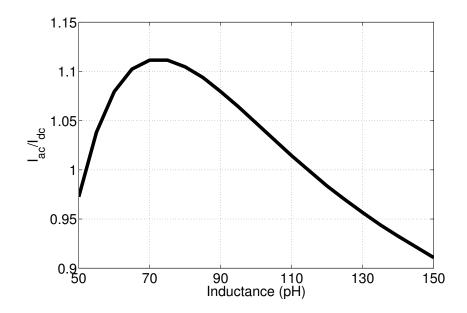

|   |     | 5.3.2.1 Optimization of Push-Push Inductance         |

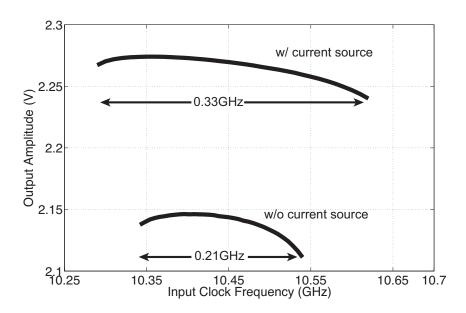

|   |     | 5.3.2.2 Sharing LO between Elements 60               |

|   |     | 5.3.2.3 Sizing of Push-Push                          |

|   |     | 5.3.3 30GHz Generation                               |

|   | 5.4 | Receiver Demonstration                               |

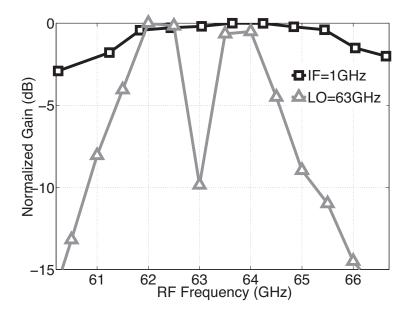

|   | 9   | 5.4.1 Bandwidth Measurement                          |

|   |     | 5.4.2 LO Performance                                 |

|   | 5.5 | Summary                                              |

| c | On  | Chip mm-Wave Antennas 69                             |

| 6 |     | 1                                                    |

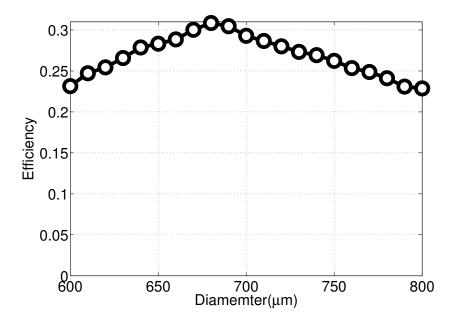

|   | 6.1 | On-Chip Antenna Efficiency                           |

|   |     | 6.1.1 Slot-Loop Antenna Design                       |

|   |     | 6.1.1.1 Diameter                                     |

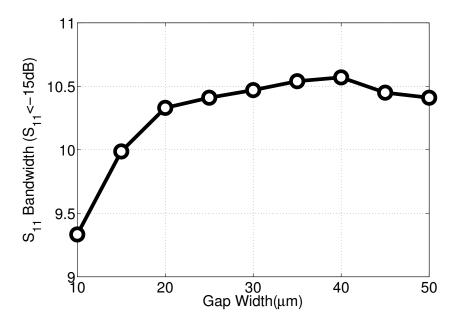

|   |     | 6.1.1.2 Gap Width                                    |

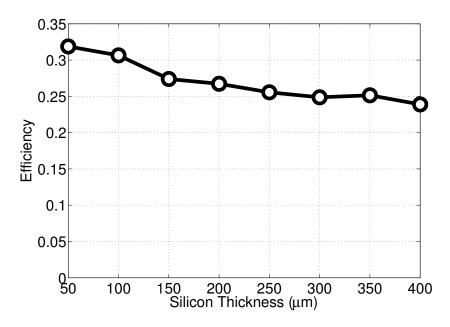

|   | 0.0 | 6.1.1.3 Substrate Thickness                          |

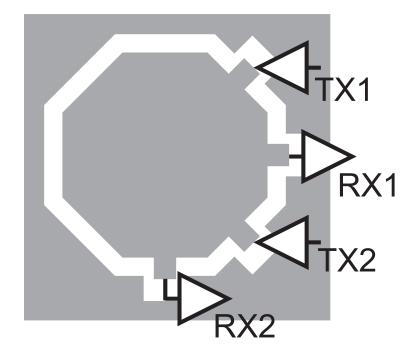

|   | 6.2 | Multiple-Access On-Chip Antenna                      |

|                           |        | 6.2.1 Antenna Multiplexing                         | 75 |

|---------------------------|--------|----------------------------------------------------|----|

|                           |        | 6.2.2 Reducing Loading Effect                      | 76 |

|                           | 6.3    | Measurement Results                                | 77 |

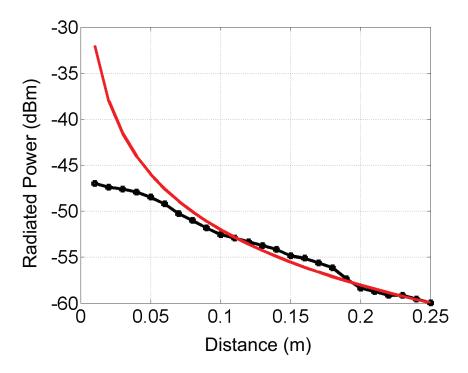

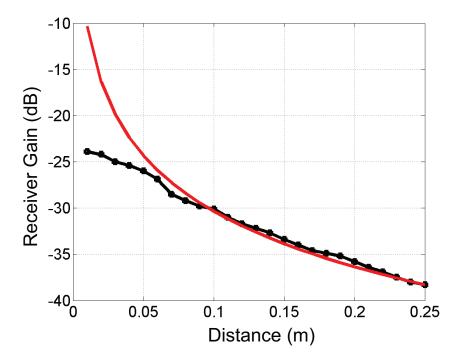

|                           |        | 6.3.1 Measured Transmitter Power and Receiver Gain | 78 |

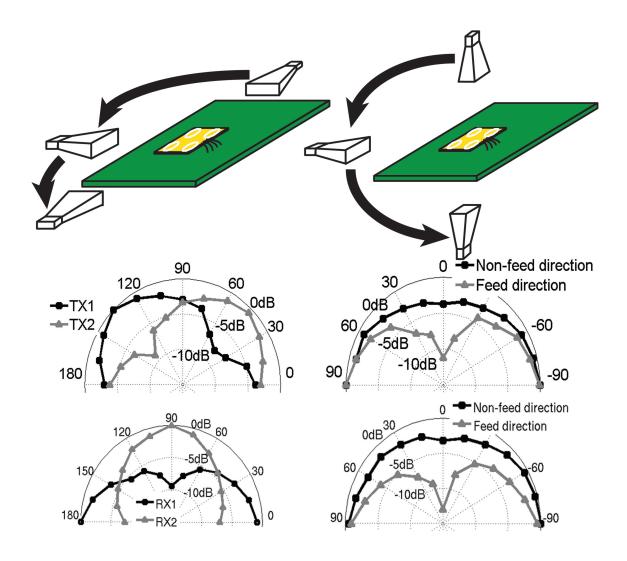

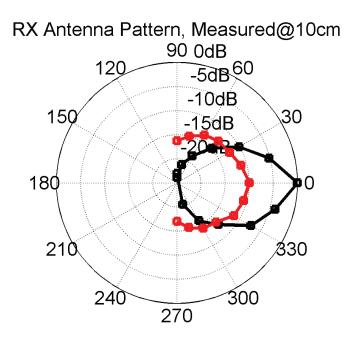

|                           |        | 6.3.2 Antenna Pattern Measurement                  | 80 |

|                           | 6.4    | Summary                                            | 80 |

| 7                         | Full   | y Integrated 4-Element Phased-Array                | 82 |

|                           | 7.1    | ·                                                  | 83 |

|                           |        | 7.1.1 Transmitter Phased-Array Measurement         | 83 |

|                           |        | 7.1.2 Receiver Phased-Array Measurement            | 84 |

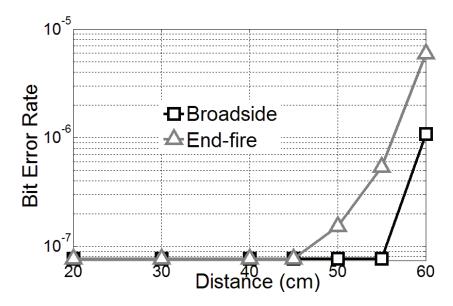

|                           | 7.2    | Link Measurement                                   | 84 |

|                           | 7.3    | Summary                                            | 86 |

| 8                         | Cor    | aclusions                                          | 89 |

|                           | 8.1    | Thesis Summary                                     | 89 |

|                           | 8.2    | Future Directions                                  | 91 |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog | graphy                                             | 92 |

# List of Figures

| 1.1 | Alliance (WiGig).)                                                                       | 1  |

|-----|------------------------------------------------------------------------------------------|----|

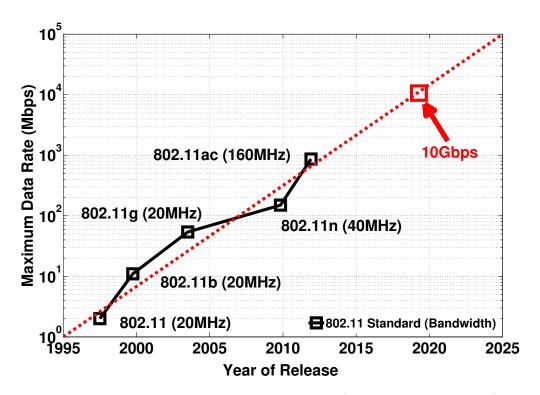

| 1.2 | Data rate of 802.11 standards. (Source: IEEE 802.11.)                                    | 2  |

| 2.1 | Operating principle of a phased array transmitter                                        | 6  |

| 2.2 | Principle of phased array II: peak and null                                              | 7  |

| 2.3 | SNR improvement versus number of receiver elements                                       | 11 |

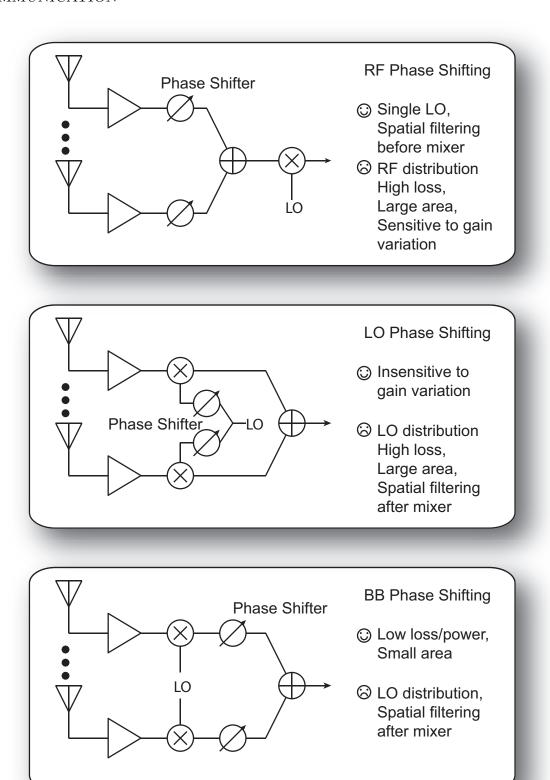

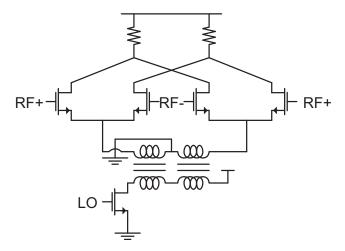

| 2.4 | Phased-array architectures: RF, LO and baseband phase shifting                           | 12 |

| 2.5 | Directivity at different directions with different phase shifter resolution              | 17 |

| 2.6 | Peak to side lobe ratio at different directions with different phase shifter resolution. | 17 |

| 2.7 | Bit error rate (BER) versus peak SNR                                                     | 18 |

| 3.1 | Baseband phase shifter utilizing variable gain amplifier                                 | 21 |

| 3.2 | Variable gain amplifier controlled by variable bias current                              | 24 |

| 3.3 | Variable gain amplifier controlled by segmentation                                       | 25 |

| 3.4 | Phase shifter constellations using (a) VGA with variable current source (b) seg-         |    |

|     | mentation                                                                                | 25 |

| 3.5 | Phase shifter constellations using (a) straightforward I/Q summation and (b)             |    |

|     | proposed I/Q partial sharing scheme                                                      | 26 |

| 3.6 | Phase shifter implementation of (a) conventional (b) proposed architectures              | 27 |

| 3.7 | Quadrature implementation using (a) butterfly switches (b) 4-to-1 MUX                    | 28 |

| 3.8 | Measurement result of a phase shifter with 5-bit per quadrant resolution                 | 29 |

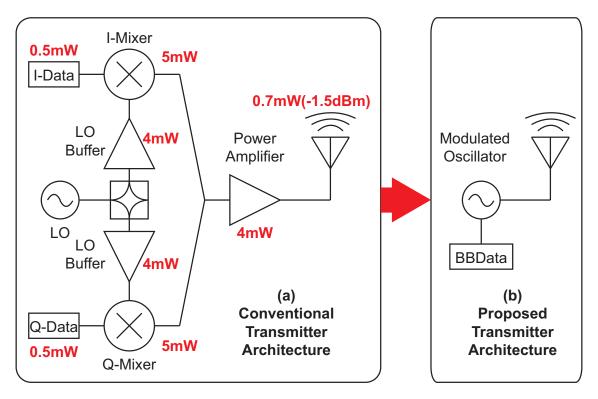

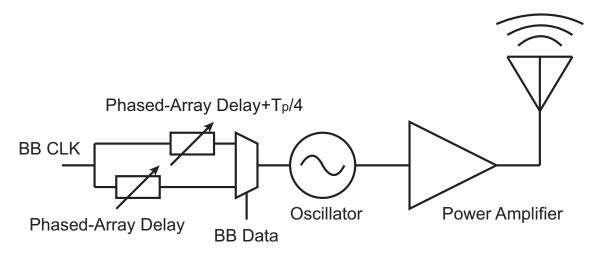

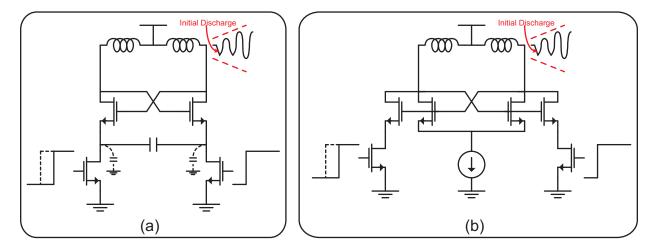

| 4.1 | Transmitter architectures for (a) conventional and (b) proposed approaches               | 31 |

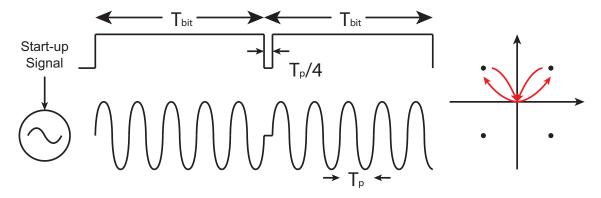

| 4.2 | Oscillator phase modulation by baseband delay                                            | 32 |

| 4.3 | Oscillator phase modulation by baseband delay to support phased-array func-              |    |

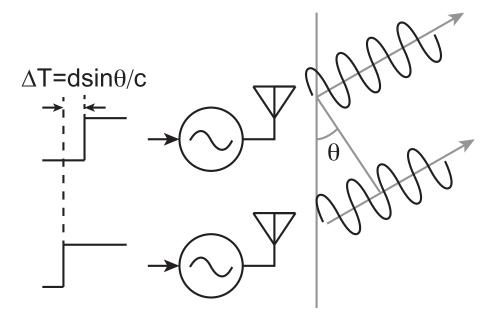

|     | tionality                                                                                | 32 |

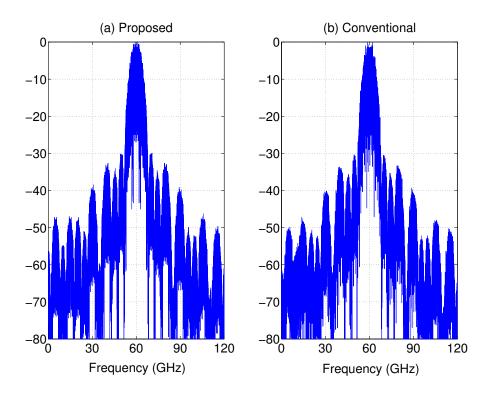

| 4.4 | Transmitter spectrum of (a) proposed architecture and (b) conventional architec-         |    |

|     | ture                                                                                     | 33 |

| 4.5 | Transmitter block diagram.                                                               | 34 |

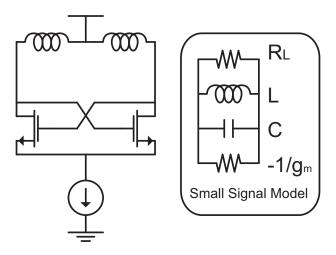

| 4.6 | Cross coupled oscillator and its small signal model                                      | 35 |

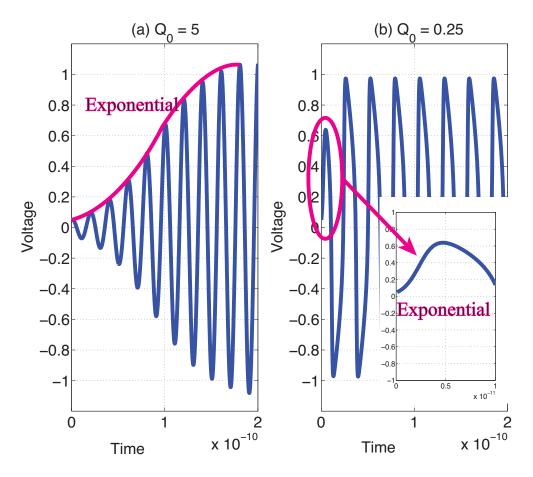

| 4.7 | Oscillator startup with (a) $Q_0 = 5$ and (b) $Q_0 = 0.25$                               | 37 |

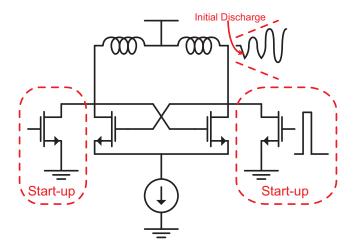

| 4.8<br>4.9 | Cross coupled oscillator with start-up circuitry                                  |

|------------|-----------------------------------------------------------------------------------|

| _          | couple                                                                            |

| 4.10       | Fast start-up oscillator: complete schematic                                      |

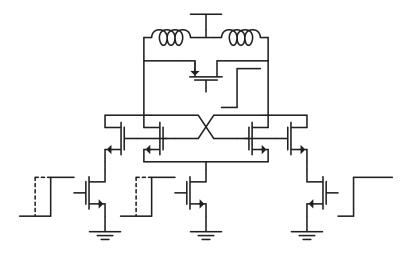

|            | Optimization of shut-down transistor size                                         |

|            | Power amplifier with (a) one-stage (b) two-stage                                  |

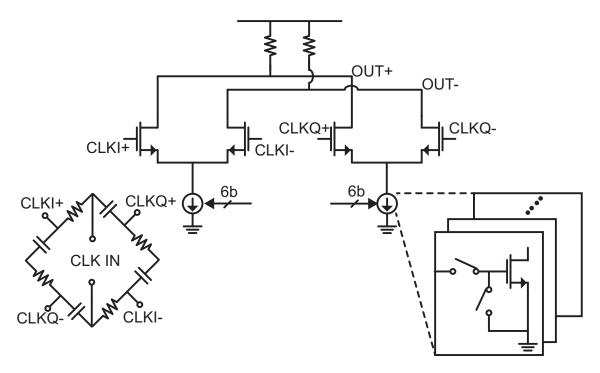

|            | Phase interpolator for high-resolution clock interpolation                        |

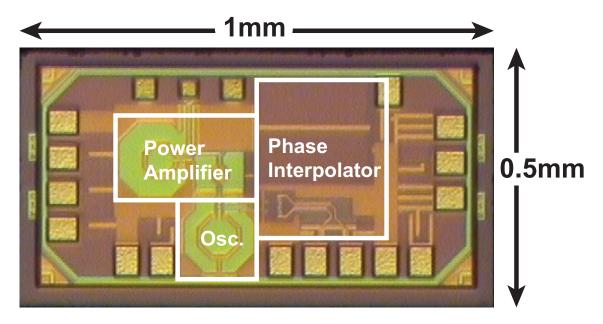

|            | Die photo of transmitter test chip                                                |

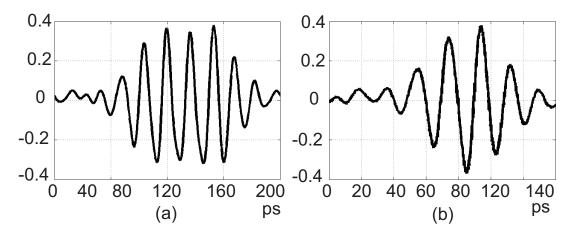

|            | Measured waveform at (a) 5GS/s and (b) 7GS/s                                      |

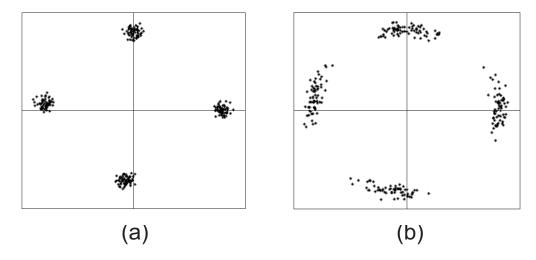

|            | Measured transmitter constellation at (a) 5GS/s and (b) 7GS/s                     |

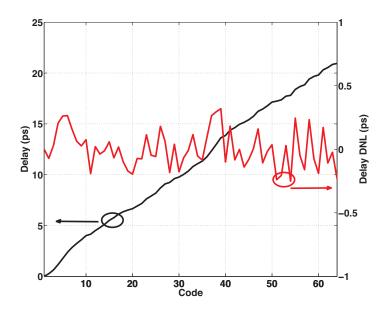

|            | Measurement of DNL and INL of the TX phase interpolator                           |

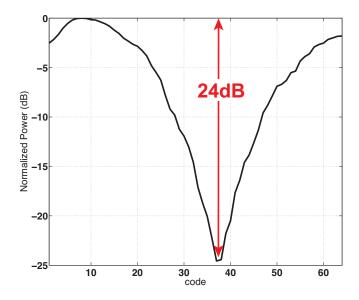

|            | Measurement 2-element phased array                                                |

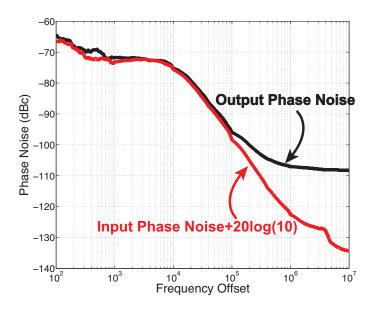

|            | Measured output phase noise of the transmitter; in comparison with input phase    |

| _          | noise referred at output frequency                                                |

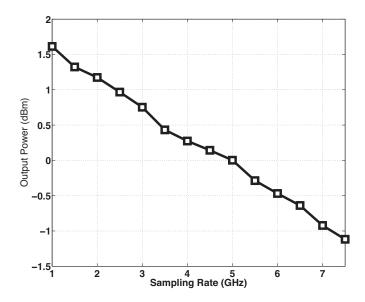

| 4.20       | Measured output average power versus sampling rate                                |

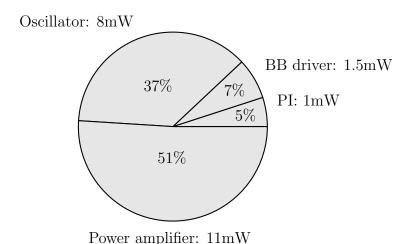

|            | Power breakdown of the first demonstrated transmitter with 3dBm peak output       |

|            | power                                                                             |

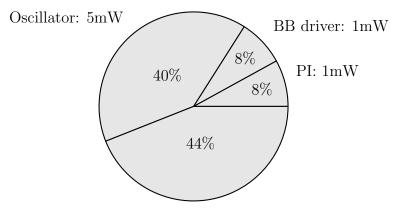

| 4.22       | Power breakdown of the second demonstrated transmitter with 0dBm peak output      |

|            | power                                                                             |

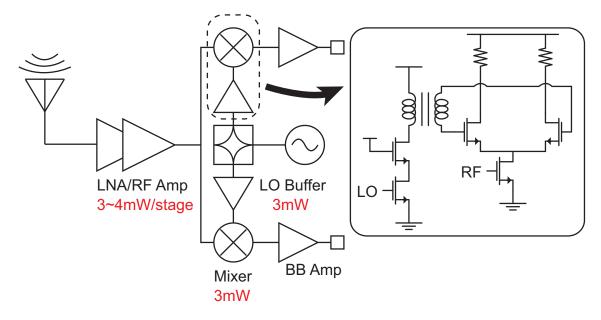

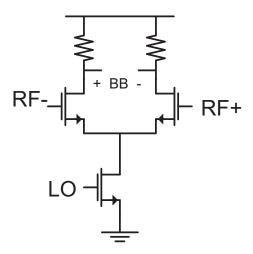

| 5.1        | Conventional receiver architecture and implementation of mixer with LO buffer. 50 |

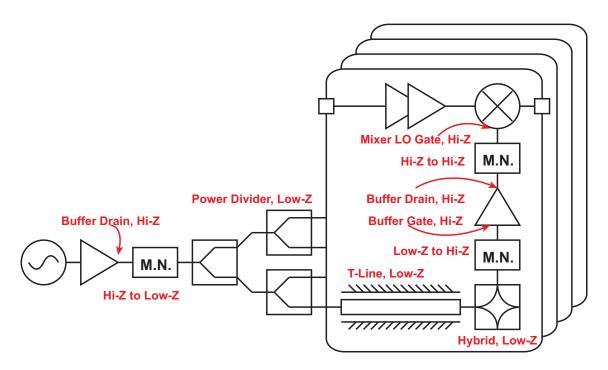

| 5.2        | Impedance transformation in LO distribution                                       |

| 5.3        | Low supply mixer using transformer coupled LO port                                |

| 5.4        | Switched transconductance mixer                                                   |

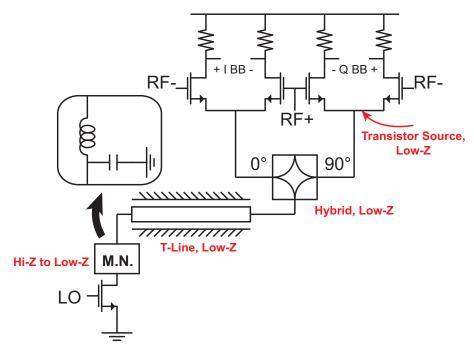

| 5.5        | Proposed LO distribution scheme built inside mixer                                |

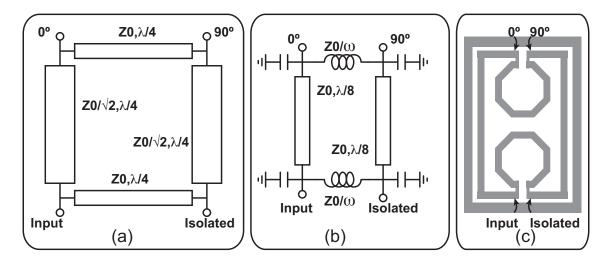

| 5.6        | Branch-line coupler (a), its miniaturization (b) and physical implementation 53   |

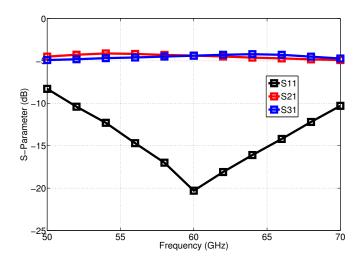

| 5.7        | Simulation result of proposed hybrid                                              |

| 5.8        | Stacked mixer on 30GHz oscillator                                                 |

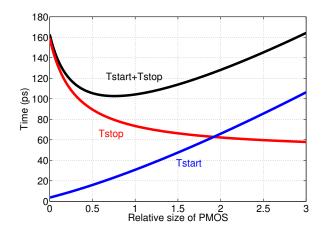

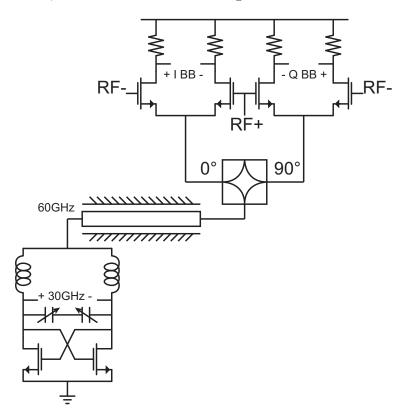

| 5.9        | Stacked mixer on 30GHz push-push doubler                                          |

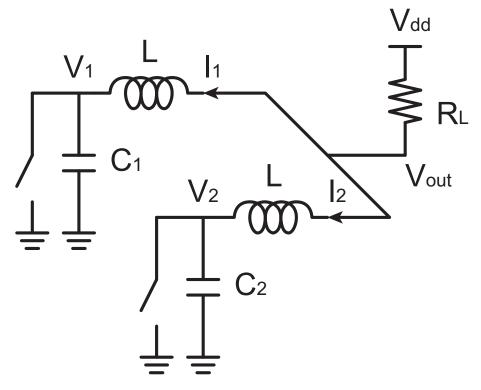

| 5.10       | Circuit model for push-push doubler                                               |

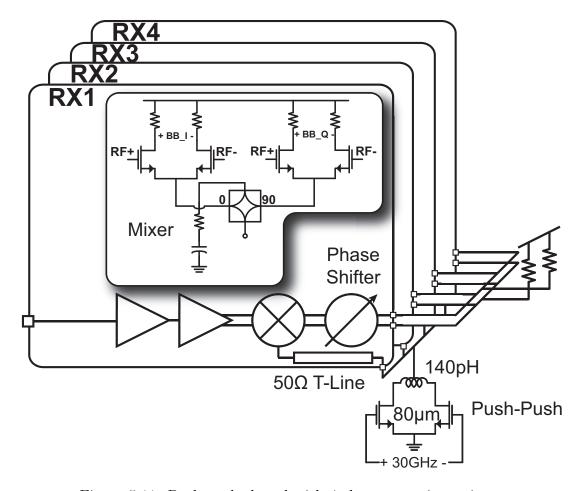

| 5.11       | Push-push shared with 4-element receiver mixers                                   |

| 5.12       | Sizing of inductor in push-push doubler                                           |

|            | 30GHz injection locked tripler                                                    |

| 5.14       | Locking range with and without current source                                     |

| 5.15       | Measurement of receiver bandwidth                                                 |

| 5.16       | Receiver LO locking range                                                         |

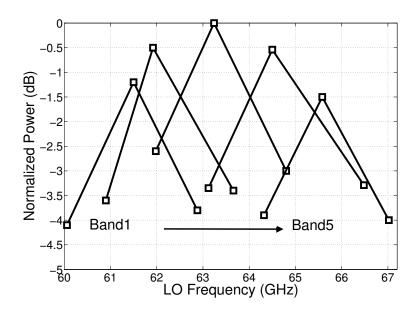

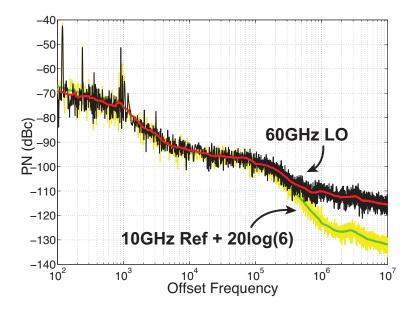

| 5.17       | Phase noise of the receiver LO at monitor port 6                                  |

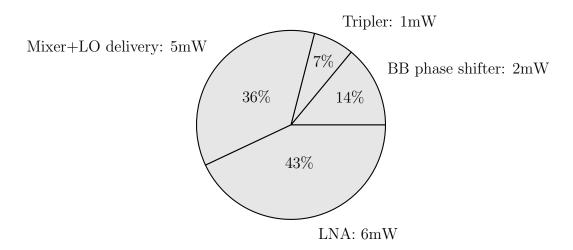

| 5.18       | Power breakdown of the proposed receiver                                          |

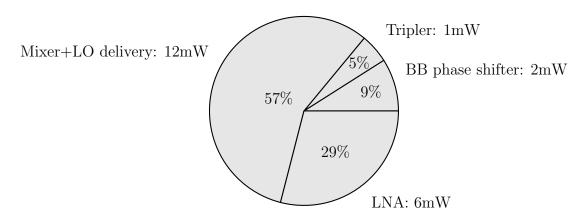

| 5.19       | Predicted power breakdown of a receiver using conventional architecture 68        |

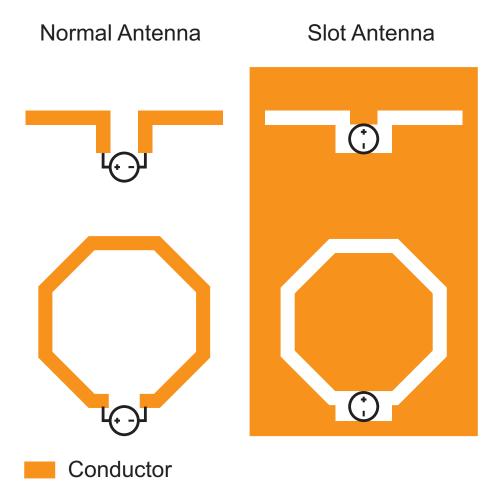

| 6.1        | Normal antennas and its slot correspondence                                       |

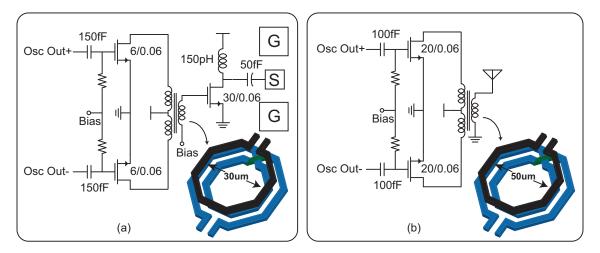

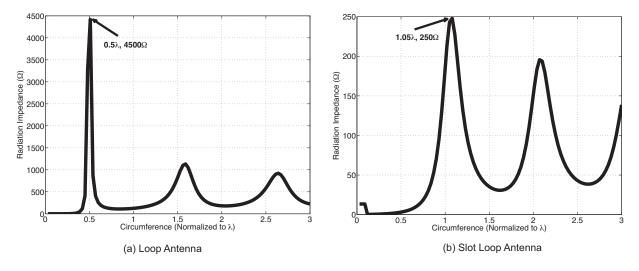

| 6.2        | Radiation resistance of (a) loop antenna and (b) slot loop antenna                |

| 6.3  | Simulated efficiency versus antenna diameter                                           | 72 |

|------|----------------------------------------------------------------------------------------|----|

| 6.4  | Simulation setup of antenna gap, feed line, and port                                   | 72 |

| 6.5  | Simulated S11 bandwidth versus gap width                                               | 73 |

| 6.6  | Simulated radiation efficiency versus silicon thickness                                | 74 |

| 6.7  | Slot loop antenna and its radiation pattern                                            | 74 |

| 6.8  | Antenna diversity using two driving ports                                              | 75 |

| 6.9  | Antenna switching as well as T/R switch                                                | 75 |

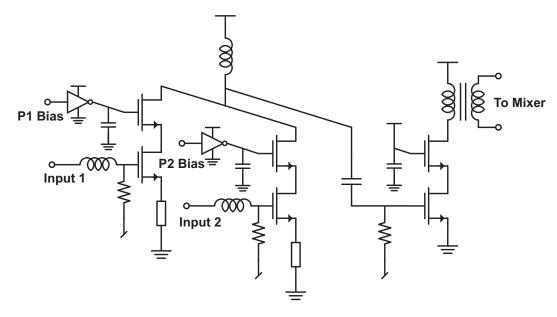

| 6.10 | Input multiplexer embedded in low noise amplifier                                      | 76 |

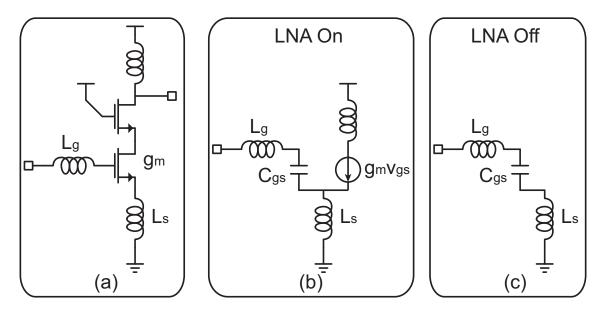

| 6.11 | (a) Schematic of source degenerated LNA and its impedance with bias (b) on and         |    |

|      | (c) off                                                                                | 77 |

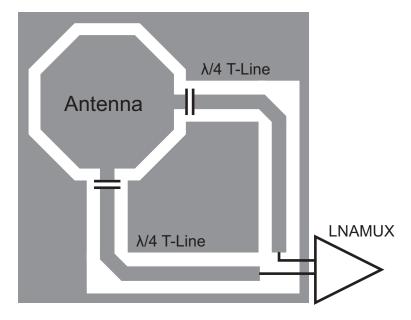

| 6.12 | $\lambda/4$ transmission line inserted for impedance transformation while also serving |    |

|      | the purpose of routing the antenna ports to a single location                          | 78 |

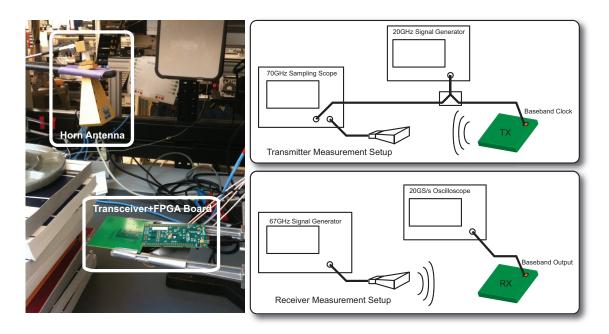

| 6.13 | Antenna measurement setup                                                              | 78 |

|      | Transmitter radiated power versus distance                                             | 79 |

|      | Receiver gain versus distance                                                          | 80 |

| 6.16 | Transmitter radiation pattern with different configurations; receiver antenna pat-     |    |

|      | tern with different configurations                                                     | 81 |

| 7.1  | Die photo of complete transceiver                                                      | 82 |

| 7.2  | Transmitter antenna array pattern inside PCB plane                                     | 83 |

| 7.3  | Receiver antenna array pattern inside PCB plane                                        | 84 |

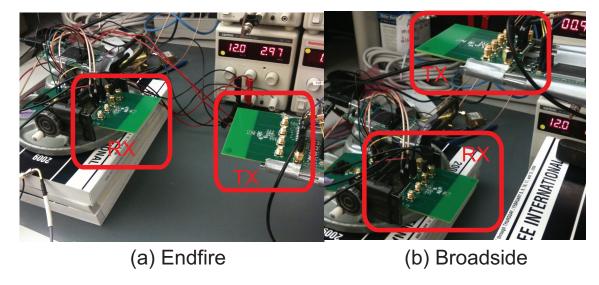

| 7.4  | Link measurement setup of (a) end-fire direction and (b) broadside direction           | 85 |

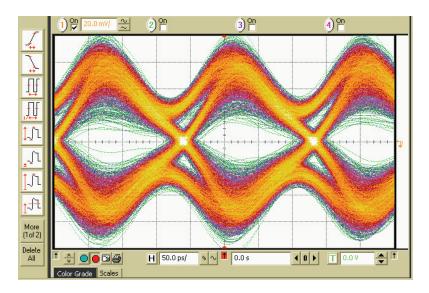

| 7.5  | Receiver eyediagram of I-channel data at 5.2GS/s                                       | 85 |

| 7.6  | BER measurement versus distance, different directions                                  | 86 |

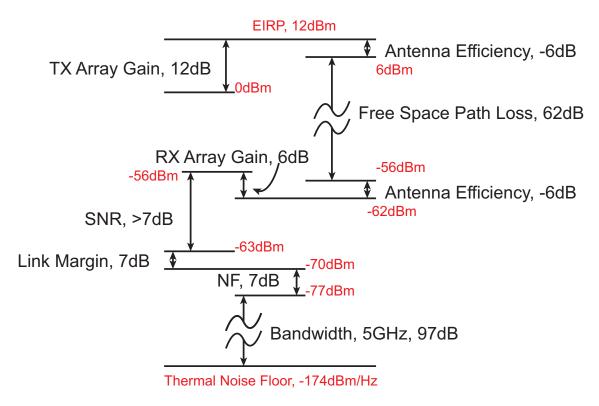

| 7.7  | Link budget calculation with 4-TX/4-RX phased-array at 0.5m distance                   | 87 |

|      |                                                                                        |    |

# List of Tables

| 4.1 | Comparison table of transmitter design          | 46 |

|-----|-------------------------------------------------|----|

| 7.1 | Comparison table of mm-wave transceiver designs | 88 |

### Acknowledgments

My life at UC Berkeley has been a wonderful journey and I was fortunate to have many great companions throughout this five and half years. This work would not have been possible without their help and support, so I would like to take this opportunity to express my gratitude to each and every of them.

First I would like to thank my advisor Prof. Elad Alon. Coming from a communication background, I have learned most of my circuit knowledges from him, either during his wonderful lectures or from the discussions with him. During our discussions, I was always amazed that he could decompose my research problems into the most fundamental pieces and provide the most effective solutions. Without all these inspiring conversations, this work would not have been possible.

I would like to thank Prof. Ali M. Niknejad for his extensive guidance and feedback over numerous projects. His suggestions and support on my job search have been invaluable. I would also like to thank Prof. Ahmad Bahai and Prof. Paul K. Wright for being a part of my qualification exam committee and providing valuable feedback.

The multiple chip designs wouldn't be possible without my colleagues' support and collaboration. It was truly my honor and pleasure to work with Bagher Afshar, Jiashu Chen, Debopriyo Chowdhury, Antoine Frappe, Kwangmo Jung, Shinwon Kang, Yue Lu, Cristian Marcu, Jungdong Park, Dongjin Seo, Maryam Tabesh, Chintan Thakkar, and Yanjie Wang.

I have also learnt more than I could have imagined during my research in BWRC, and most of it is because of my classmates and other senior colleagues: Ehsan Adabi, Louis Alarcon, Amin Arbabian, Omar Bakr, David Chen, Stanley Chen, John Crossley, Zhiming Deng, Yida Duan, Simone Gambini, Tsung-Te Liu, Michael Mark, Rikky Muller, Ji-Hoon Park, Jesse Richmond, Dusan Stepanovic and Zhengya Zhang.

BWRC has been a wonderful working place and it would not be this way without the kind support from all the staff at the center. I would like to express my gratitude to all of them but especially to Tom Boot, Gary Kelson, Susan Mellers and Brian Richards for their support on my project.

Finally I would like to acknowledge the love and support from my parents Yiqin and Xiangsheng. Without their love, encouragement and support, I could have never been where I am now, and for that I dedicate this thesis to them.

# Chapter 1

# Introduction

In the past decade, wireless technology has had a significant impact on our daily life. Ubiquitous wireless connectivity provides us connectivity anywhere at anytime. Moving forward, emerging applications including wireless docking, wireless HD streaming, and near-field file sharing/exchange will demand data rates of up to multiple Gb/s. In order to enable these applications on mobile platforms such as smartphones and tablets, the cost as well as energy consumption of these systems have to be minimized while achieving higher performance. This research therefore investigates design trade-offs in such systems and develops techniques to achieve these goals.

Figure 1.1: Emerging wireless applications at mm-wave band. (Source: Wireless Gigabit Alliance (WiGig).)

### 1.1 The 60GHz Band

The wireless industry has been pushing the envelop of data rate for years. Based on the IEEE 802.11 standard operating in the 2.4GHz ISM band, existing WLAN solutions provide service at data rate as high as 150Mb/s. The upcoming 802.11ac utilizes 160MHz bandwidth at the 5GHz ISM band and improves data rate up to 877Mb/s for mobile applications in the range of 10s of meters (Fig. 1.2). However, the achievable data rate is limited by the available bandwidth in these bands.

Figure 1.2: Data rate of 802.11 standards. (Source: IEEE 802.11.)

The 7GHz unlicensed bandwidth at 60GHz therefore provides a good opportunity to achieve much higher data rate. Despite its wide bandwidth, the fractional bandwidth is only  $\sim 10\%$ , allowing a conventional implementation using tuned circuitry. Notice that the 60GHz was abandoned before due to its extra loss in air for long-haul applications. However, for the short-range applications we are interested in, the additional air loss (0.002 dB/m) [1, 2] is negligible.

### 1.2 Link Budget with Limited Area

One of the concerns of using mm-wave frequency is its high free-space-path-loss (FSPL). In area-limited applications, however, moving up in spectrum may actually improve the efficiency despite its higher path loss. This is because the reduced wavelength at high frequency increases the achievable gain of an antenna within a limited area. As shown in [3], for commonly used antennas, including dipole, loop, and etc., the maximum gain is related to the physical size by

$$G_{max} = \frac{4\pi A}{\lambda^2} \tag{1.1}$$

where A is the physical size of the antenna or the aperture and  $\lambda$  is the wavelength. Plugging the gain of the antenna into the Friis transmission equation [4], the signal-to-noise ratio (SNR) can be derived as:

$$SNR = \frac{P_{TX}G_{TX}G_{RX}}{N_o} (\frac{\lambda}{4\pi d})^2$$

$$= \frac{P_{TX}A_{TX}A_{RX}\lambda^2}{d^2N_o}$$

(1.2)

where  $P_{TX}$  is the transmitted power;  $N_o$  is the effective noise power at the receiver input and d is the communication distance.

Equation (1.2) clearly shows that, with constrained area for the antennas, the SNR improves with frequency quadratically. Thus, besides wide bandwidth, this proves the potential for high SNR at 60GHz, making it an even better candidate for an energy-efficient high-data-rate wireless system.

### 1.3 Design Challenges

The benefit of higher SNR provided in equation (1.2) could be potentially eliminated if the system is not well designed. First, the maximum antenna gain can only be achieved when the entire area is efficiently utilized. To make full use of the aperture, phased-array techniques can be employed, where multiple transmitters and receivers are implemented with independent antennas. Originally proposed for military applications, most phased-array systems simply replicate the transceivers with extra phase-shifting functionality, resulting in a rather high power consumption[5, 6]. Therefore, this research focuses on optimizing the performance of phased-array systems within a limited power budget.

Secondly, operating at mm-wave frequency challenges the performance of existing devices. SiGe technologies have successfully demonstrated transceivers at these frequencies [7, 8], but suffer from high power consumption as well as high cost when integrated with existing digital signal processing components, which are usually implemented in CMOS. On the other hand, typical CMOS technologies today provide a maximum oscillation frequency ( $f_{max}$ ) of around

250GHz, which is only 4 times higher than the operating frequency of the RF front-end. When operating at such frequencies close to  $f_{max}$ , transistors tend to be less efficient in delivering power as well as more noisy. As shown in equation (1.2), these two effects will significantly reduce the SNR. Although technology advances have provided us transistors with higher and higher  $f_{max}$ , the speed of improvement has slowed down recently. With this limited device performance, circuit level techniques at mm-wave frequencies are necessary to achieve our requirements with high energy-efficiency. Significant efforts to reduce power consumption have been made recently [9, 10, 11]. Employing techniques like high-impedance matching and etc., these designs have successfully reduced power consumption of single element transceiver to  $300 \text{mW} \sim 400 \text{mW}$ . This thesis carries these existing techniques and describes more circuit level techniques dedicated to phased-array design, in order to further improve the energy efficiency.

### 1.4 Structure of Thesis

As discussed earlier, this thesis begins with a discussion of phased-array architectures in Chapter 2, including a study of the number of elements as well as phase-shifting schemes and phase resolution requirements. Overhead power from phase shifters, modulator in the transmitter, and downconverter in the receiver is identified as the bottleneck of the system efficiency. Chapter 3 therefore investigates circuit implementations to minimize power consumption of the phase shifters. A transmitter architecture eliminating modulator is proposed in Chapter 4, and a receiver architecture is described in Chapter 5 to reduce the power consumption of the downconverters. Design procedures as well as experimental results are provided. In Chapter 6, on-chip antennas are discussed in order to further reduce the cost of the system. Integrating antenna on die also provides opportunities to achieve antenna diversity for better coverage. To verify these ideas, a complete transceiver is designed and fabricated in TSMC's 65nm CMOS technology. Measurement results are then shown in Chapter 7, followed by the conclusion for the entire thesis in Chapter 8.

# Chapter 2

# Phased-Array Architectures for Energy-Efficient Communication

Phased-array techniques essentially provide an electronically steerable antenna to focus energy in certain directions selectively. The implementation of phased-arrays has been well studied in the past for military or scientific usages, where performance is the major driving force and high power consumption is tolerable. In order to enable the applications mentioned in Chapter 1, the energy efficiency of phased-arrays has to be significantly improved. This chapter therefore studies the optimization of the phased-array architecture within a constrained power budget. To enable this analysis, we first revisit the basics of phased-array operation.

## 2.1 Introduction to Phased-Array

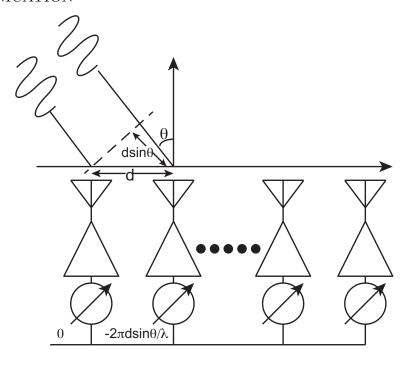

A phased-array system consists of multiple transceiver elements. Each of them has its own antenna and phase shifter that can control the phase of input/output signals independently. The antennas are placed in various array patterns, but 1D or 2D arrays are commonly used for their simplicity. The spacing between antennas is typically  $\lambda/2$  to perform Nyquist sampling in space [12].

Fig. 2.1 illustrates the operating principle of a phased-array transmitter. For simplicity, the left two transmitters are considered and each transmitter transmits its own signal through an omnidirectional antenna. In an arbitrary direction  $\theta$ , due to the physical distance between these two antennas, a phase difference between signals from these two elements occurs. Far away from the antennas, the phase difference can be approximated as:

$$\phi = \frac{2\pi d}{\lambda} \cos\theta. \tag{2.1}$$

Here d and  $\lambda$  denote the distance between elements and the wavelength, respectively.

Due to this phase difference, if the antennas are driven with the same phase, the E-field generated by these two antennas are not added in phase in this direction, resulting in less

Figure 2.1: Operating principle of a phased array transmitter.

than the maximum amplitude. However, this phase difference can easily be compensated by phase shifters within the transmitter. Specifically, either phase shifting the signal from the left element by  $\phi$  or phase shifting the signal from the right one by  $-\phi$  can realign the signals in space. Assuming replicated transmitters, this results in E-field amplitude twice as large as that with a single transmitter. Because energy is proportional to the square of E-field amplitude, the energy delivered in this direction is boosted by a factor of 4 compared to the single antenna case. In a generalized system with  $N_{TX}$  elements, the transmitted energy is increased by  $N_{TX}^2$ .

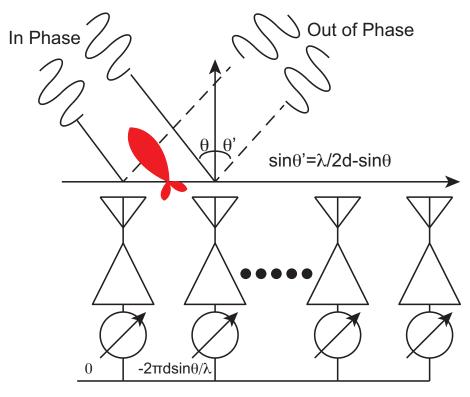

It is worth noting that the total energy radiated into space is only increased by the number of transmitters. The square law relation is due to the fact that energy is now focused (beam-formed) in this direction. As a result, energy radiated in other directions is reduced. For example, in the direction  $\theta'$  that satisfies

$$\frac{2\pi d}{\lambda}\cos\theta' = \pi - \frac{2\pi d}{\lambda}\cos\theta,\tag{2.2}$$

signals from these two elements are out of phase (Fig. 2.2). Therefore the energy delivered in this direction is zero. Because of this feature, the phased-array technique also provides nulling capabilities to reduce the interference caused to other receivers.

Similar behavior occurs on the receiver side. In the case of two elements, the received signal in the desired direction is enhanced by a factor of 4 compared with the single element

Figure 2.2: Principle of phased array II: peak and null.

case. However, unlike the transmitter where signal power is the only metric, noise power affects the receiver significantly. Assuming the noise from two different antennas are uncorrelated, they are thus added in power (rather than in voltage). The output noise power is therefore double the single element case. The net effect is that the SNR is improved by a factor of 2 rather than 4. In a generalized case where  $N_{RX}$  elements are employed in the receiver, SNR will be enhanced by  $N_{RX}$ .

## 2.2 Choice of Number of Elements in a Phased-Array

The previous section highlighted that the number of elements in transmitter and receiver have different impact on the system SNR. This section continues the discussion by optimizing the number of elements on each side given a constraint on total power consumption.

#### 2.2.1 Transmitter

One widely used metric for transmitters is effective isotropic radiated power (EIRP), which measures the radiated power in a certain direction compared to an ideal isotropic antenna. In the case of a phased-array, EIRP can be calculated in terms of a single transmitter element's

output power  $P_{TX}$ , the number of elements  $N_{TX}$ , and the antenna gain  $G_{TX}$  as:

$$EIRP = P_{TX}N_{TX}^2G_{TX}. (2.3)$$

The DC power consumption of a transmitter usually consists of two components. One component represents the power amplifier stages, which is in general proportional to the output power; the other component has a relatively fixed DC power consumption, representing power from LO generation, LO buffers, baseband, etc. Therefore, the overall power consumption of the transmitter can be written in the form of

$$P_{DC,TX} = (P_{TX}/\eta_{PA} + P_{TX,OH})N_{TX}, (2.4)$$

where  $\eta_{PA}$  denotes the efficiency of the power amplifier and  $P_{TX,OH}$  is the overhead power consumption. Plugging equation 2.4 into equation 2.3, the EIRP can be expressed in this modified format as:

$$EIRP = (P_{DC,TX}/N_{TX} - P_{TX,OH})\eta_{PA}N_{TX}^{2}G_{TX}$$

$$= \frac{P_{DC,TX}^{2}}{4P_{TX,OH}}\eta_{PA}G_{TX} - (N_{TX} - \frac{P_{DC,TX}}{2P_{TX,OH}})^{2}P_{TX,OH}\eta_{PA}G_{TX}.$$

(2.5)

The above equation shows that, with constrained total DC power consumption  $P_{DC,TX}$ , the maximum EIRP happens when

$$N_{TX} = \frac{P_{DC,TX}}{2P_{TX,OH}}. (2.6)$$

This optimum condition states that half of the DC power should be consumed by the overhead circuitry, and the other half by the power amplifiers. The maximum achievable EIRP is

$$EIRP_{max} = \frac{P_{DC,TX}^2}{4P_{TX,OH}} \eta_{PA} G_{TX}.$$

(2.7)

Clearly the maximum achievable EIRP is proportional to the efficiency of the PA and antenna gain. More importantly, the overhead power plays a significant role in this equation. As proved here, reducing the overhead power by a factor of 2 will essentially double the achievable EIRP.

One common design practice is to optimize the number of elements with a desired EIRP to achieve the lowest overall DC power consumption. Equation 2.5 can be rewritten to solve this optimization problem easily:

$$P_{DC,TX} = \frac{EIRP}{\eta_{PA}G_{TX}} \frac{1}{N_{TX}} + P_{TX,OH}N_{TX}$$

$$(2.8)$$

. As before, the minimum DC power consumption is achieved when the overhead power equals the power amplifier power consumption. The minimum DC power and the optimum

number of elements are thus:

$$P_{DC,TX,min} = 2\sqrt{\frac{EIRP \times P_{TX,OH}}{\eta_{PA}G_{TX}}}$$

$$N_{TX,opt} = \sqrt{\frac{1}{\eta_{PA}G_{TX}} \frac{EIRP}{P_{TX,OH}}}.$$

(2.9)

With a given EIRP, this minimum DC power consumption is limited by the efficiency of the power amplifier and antenna gain, but more importantly, by the overhead power as well. Significant efforts have gone into improving PA efficiency at different power levels [13, 14, 15, 16]; unfortunately the overhead power consumption in phased-arrays is equally important but often overlooked in system designs.

It is worthwhile to mention the exact values of power levels implied by the analysis, to make sure the order of magnitudes are in a reasonable range. In CMOS designs, due to the lossy passive components at high frequencies, the impedance transformation ratio is usually limited to be lower than  $\sim 3$  before losses rise substantially. With a 50 $\Omega$  antenna impedance at 1V supply voltage, this limits the output power of a single transmitter to be somewhere between 3dBm and 13dBm with a 1V supply voltage. Techniques like power combining [17] can bring the power level up by another 6dB and lowering down supply can extend the low-end to  $\sim 0$ dBm. On the other hand, a typical 60GHz transmitter design includes roughly  $10\sim 20$  mW overhead power. Assuming an EIRP of 12dBm to achieve a range of 1m, per-element overhead power of 16mW, 30% efficiency in the PA and 30% efficiency in the antenna, the minimum DC power consumption can be evaluated as 100mW with a 3-element array. Each of the transmitters uses a 16mW power amplifier delivering 5mW to the antenna and 1.6mW into space. This is indeed within the range of output power discussed before.

### 2.2.2 Receiver

On the receiver side, because the SNR is proportional to  $N_{RX}$  rather than  $N_{RX}^2$ , the benefit of increasing the number of elements is limited. Furthermore, doubling the SNR would require doubling the number of receiver elements, therefore increasing the receiver power consumption. Assuming we have a system where the receiver noise power is inversely proportional to the DC power consumption, i.e.,

$$N_o = \frac{N_{o,Device}}{P_{RX,Single}} = \frac{N_{o,Device}N_{RX}}{P_{RX,DC}},$$

(2.10)

the receiver part of the SNR equation can be rewritten as

$$SNR \propto \frac{G_{RX}P_{RX,DC}N_{RX}^2}{N_{o,device}N_{RX}^2} = \frac{G_{RX}P_{RX,DC}}{N_{o,device}}.$$

(2.11)

Here  $N_{o,Device}$  is the noise power normalized with DC power, with a unit of  $W^2$ . It is not hard to conclude that in the scenario where a fixed power budget is given for the receiver, increasing the number of elements does not improve the SNR.

This surprising result may not hold in practice however, because the assumption that noise is inversely proportional to the DC power consumption is usually not entirely accurate. This is due to the fact that a non-negligible portion of noise is contributed from the antenna impedance, which does not scale with the receiver power consumption. Furthermore, similar to the transmitter, there is an overhead power consumption associated with each receiver that needs to be taken into account. Thus, a more precise model is

$$N_o = N_{o,Antenna} + \frac{N_{o,Device}}{P_{RX,Single} - P_{RX,OH}} = N_{o,Antenna} + \frac{N_{o,Device}N_{RX}}{P_{RX,DC} - N_{RX}P_{RX,OH}}, \quad (2.12)$$

where  $P_{RX,OH}$  denotes the overhead power in the receiver chain. This modifies equation 2.11 to be

$$SNR \propto \frac{N_{RX}(P_{RX,DC} - N_{RX}P_{RX,OH})}{N_{o,Antenna}(P_{RX,DC} - N_{RX}P_{RX,OH}) + N_{o,Device}N_{RX}}.$$

(2.13)

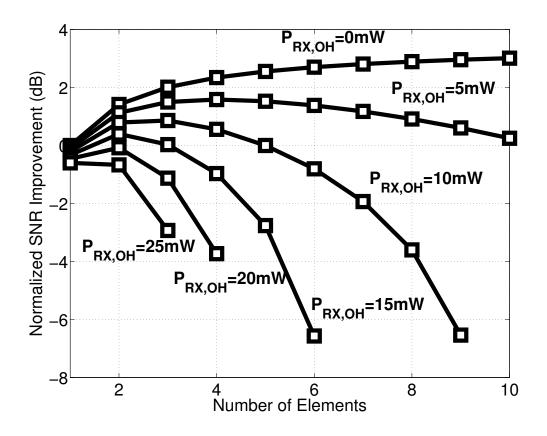

Unlike the case of the transmitter, the optimization of a receiver phased-array is rather complicated, heavily depending on the exact value of the overhead power and noise performance. Based on a sample design in [18], a  $\sim 30 \mathrm{mW}$  receiver achieves 7dB noise figure with about 10mW overhead power consumption . Therefore  $N_{o,device}$  can be extracted to be roughly  $N_{o,Antenna} \times 80 mW$ . Shown below is a sample calculation based on a total power consumption of  $100 \mathrm{mW}$ :

$$SNR \propto \frac{N_{RX}(100mW - N_{RX}P_{RX,OH})}{[100mW + N_{RX}(80mW - P_{RX,OH})]N_{o,antenna}}.$$

(2.14)

SNR improvement over a single element receiver with zero overhead power is plotted versus number of elements in Fig. 2.3 with different overhead power values. This plot shows that the effect of overhead power consumption is also critical in the receiver. When overhead power is small, the SNR improvement can be as high as 3dB compared to a single element design. When overhead power is 15mW or higher, the maximum improvement is limited to be lower than 1dB. In other words, there is not much motivation to implement a phased-array.

As discussed above, compared to a single element system, phased-array techniques can indeed improve the SNR within a limited power budget. Besides typical metrics including PA efficiency and receiver noise figure, the analysis shows that the overhead power is critical in phased-array designs. Therefore, in Chapters 4 and 5, transceiver architecture targeting low overhead power consumption will be proposed and studied.

It should be noted that even though a receiver phased-array does not improve SNR in certain conditions, it can still help to achieve spatial filtering, which can potentially allow multiple users to share the same medium and improve the system capacity. This emphasizes even further the need to reduce per-receiver overhead power so that systems that require a certain degree of directivity do not suffer from low efficiency.

Figure 2.3: SNR improvement versus number of receiver elements.

### 2.3 Phased-Array Architectures

The above analysis uses a simple model for the power consumption of a phased-array transceiver without differentiating it from a single element transceiver. However, the key difference between them is the functionality of phase-shifting and signal combining, which leads to extra power consumption. This extra power consumption can potentially eliminate the benefits of the phased-array. There are multiple architectures implementing this functionality classified based on where phase shifting is achieved. As illustrated in Fig. 2.4, this section discusses the impact on power consumption of the most common three implementations. We will start with the receiver architecture and then discuss the transmitter briefly.

## 2.3.1 RF Phase Shifting

The RF Phase Shifting approach [19, 20, 21, 22] (Fig. 2.4(a)) modifies the phase on the RF path directly. In the receiver elements, the phase-shifted signals are then combined before

Figure 2.4: Phased-array architectures: RF, LO and baseband phase shifting.

arriving at the downconverter. Because there is signal loss associated with the phase shifter, it is desired to have the phase shifting done in later stages to avoid noise penalties. In CMOS, varactors are commonly used to achieve such functionality by changing the capacitance. The range and loss of the phase shifting are therefore determined by the range of the varactor  $C_{on}/C_{off}$  as well as the quality factor of the varactor. Assuming the phase shifter works in an impedance environment of  $R_o$  and varactor on-off ratio is denoted as F, a simplified model for phase shifter loss is

$$G = \frac{R_{cap}}{R_o + R_{cap}},\tag{2.15}$$

where  $R_{cap}$  is the effective parallel resistance of the varactor. On the other hand, the range of the phase variation  $\phi$  is related to the capacitance change:

$$tan\frac{\phi}{2} = \omega R_o(C_{on} - C_{off})/2. \tag{2.16}$$

Combining the above equations to eliminate  $R_o$ , the range and loss can be related as

$$\frac{1-G}{G}\omega R_{cap}C_{avg} \times \frac{F-1}{F+1} = tan\frac{\phi}{2}.$$

(2.17)

This can be further simplified using the quality factor  $Q = \omega R_{cap} C_{avq}$ ,

$$\frac{1}{G} = 1 + \frac{1}{Q} \frac{F+1}{F-1} tan \frac{\phi}{2}.$$

(2.18)

In a typical 65nm CMOS technology where  $F \approx 3$  and  $Q \approx 3$  at 60GHz, the equation can be simplified to

$$\frac{1}{G} = 1 + \frac{2}{3}\tan\frac{\phi}{2}.\tag{2.19}$$

In a phased-array system, full coverage of 360° is usually required. One can take advantage of differential signaling to cut the range by half. However, the model here assumes single resonance and therefore can not achieve 180° coverage. Cascading two stages of identical phase shifter of 90° can fulfill the requirement, with a loss of

$$\left(\frac{1}{G}\right)^2 = \left(1 + \frac{2}{3}\tan 45^\circ\right)^2 = 0.36 \approx 8.9dB. \tag{2.20}$$

An on-chip inductor will typically lead to an extra 1dB loss, making the total loss roughly 10dB. Prior publications [23, 24] have shown performance close to this prediction with different implementations. On the other hand, a one stage power matched cascode amplifier provides about 10dB gain at 60GHz while consuming  $\sim$ 3-4mW. This gain cancels out the loss of the phase shifter. Therefore, a varactor based RF phase shifter effectively requires approximately 3mW of power.

Besides loss, the bandwidth of the RF phase shifter is also important. Given that it is inserted on to the signal path, the phase shifter needs to handle the bandwidth of the RF signal, which can also be challenging and demand extra power consumption.

Despite all the challenges of RF phase shifting, the advantage of this scheme is that it requires one single mixer, and therefore the LO signal can be generated relatively close to the receiver and does need to be split or routed.

### 2.3.2 LO Phase Shifting

In heterodyne systems, phase shifting can also be achieved on the LO path [5, 6, 25, 26]. This is because the baseband signal is a multiplication of the LO signal and the RF. The received baseband signal with a phase shift of  $\phi_{shift,RF}$  in the RF path is

$$LPF\{cos(\omega_{RF}t + \phi_{Shift,RF}) \times cos(\omega_{LO}t)\} = cos(\omega_{BB}t + \phi_{Shift,RF}), \tag{2.21}$$

while the baseband signal obtained by a phase shifted LO signal is:

$$LPF\{cos(\omega_{RF}t) \times cos(\omega_{LO}t + \phi_{Shift,LO})\} = cos(\omega_{BB}t - \phi_{Shift,LO}). \tag{2.22}$$

In the case where  $\phi_{Shift,LO} = -\phi_{Shift,RF}$ , the output of these two schemes are identical. The requirement for the phase shifter, however, is quite different. Compared with the RF phase shifting architecture, the LO path is less sensitive to the bandwidth because a single tone LO is usually delivered. The bandwidth only translates to conversion gain difference in the mixer while using different LO frequencies and can be compensated easily by boosting up the gain in the LO driver or at the baseband.

The penalty of LO phase shifting, on the other hand, is that it typically consumes significantly higher power. Although the same phase shifter used in RF phase shifting can be used here, the power needed to compensate the loss is much higher. This is because LO path usually handles the highest RF power in receiver chain to hard switch the mixer. Therefore the amplifier compensating the loss needs to provide real power rather than just gain as in the previous case. As an example, assuming the same phase shifter with 10dB insertion loss is used in both schemes. In LO phase-shifting scheme, if the point where phase shifter is inserted handles -5dBm power, extra power consumption is needed to deliver +5dBm, which is about 10mW assuming 30% efficiency. This can be improved by reducing the phase shifting range to 90° and the other quadrants are handled in the baseband assuming a complex modulation scheme. Nevertheless, the LO shifting scheme using varactor based varactors still consumes a higher power consumption than its RF counterpart.

An alternative approach to implement LO phase shifting is to use a Cartesian structure where two LO signals with 90° phase are summed together with different weights [29, 21]. Arbitrary phase of the LO signal can be generated by varying these two weights as:

$$cos(\omega_{LO}t + \phi_{Shift,LO}) = cos(\phi_{Shift,LO})cos(\omega_{LO}t) - sin(\phi_{Shift,LO})sin(\omega_{LO}t). \tag{2.23}$$

Compared to a normal LO buffer, the phase shifter consumes  $\sqrt{2}$  more power when both LO signal experiences the same weight. This results in a  $\sim 40\%$  power penalty per phase shifter. In a complex modulation system, the total power penalty is thus 80% power consumption of a normal LO buffer. Because the LO amplifiers handle a maximum impedance of  $\sim 300\Omega$ , they typically consume  $\sim 3 \text{mW}$  power, and therefore  $3 \text{mW} \times 80\% = 2.4 \text{mW}$  extra power needs to be consumed in the phase shifters.

### 2.3.3 Baseband Phase Shifting

The other option in heterodyne systems is to implement phase shifting at the baseband [27, 28, 18]. This can be shown again by comparing the original phase shifting result with the alternative approach. Here we shall look at a complex demodulation making both I/Q channel outputs available.

I:

$$LPF\{(I(t)cos(\omega_{RF}t + \phi_{Shift}) + Q(t)sin(\omega_{RF}t + \phi_{Shift})) \times cos(\omega_{LO})\}$$

$= I(t)cos(\phi_{Shift}) + Q(t)sin(\phi_{Shift}).$

Q:  $LPF\{(I(t)cos(\omega_{RF}t + \phi_{Shift}) + Q(t)sin(\omega_{RF}t + \phi_{Shift})) \times sin(\omega_{LO})\}$

$= Q(t)cos(\phi_{Shift}) - I(t)sin(\phi_{Shift}).$  (2.24)

The downconverted signal without any phase shifting is

I:

$$LPF\{(I(t)cos(\omega_{RF}t) + Q(t)sin(\omega_{RF}t)) \times cos(\omega_{LO})\} = I(t)$$

.

Q:  $LPF\{(I(t)cos(\omega_{RF}t) + Q(t)sin(\omega_{RF}t)) \times sin(\omega_{LO})\} = Q(t)$ . (2.25)

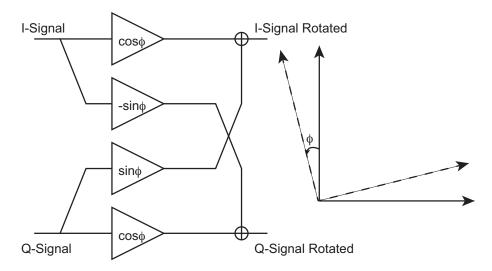

In order to obtain the same baseband signal as the phase-shifted case, a simple vector rotation can be achieved by multiplying the received signals with a rotation matrix:

$$\begin{bmatrix} cos(\phi_{shift}) & sin(\phi_{shift}) \\ -sin(\phi_{shift}) & cos(\phi_{shift}) \end{bmatrix} \times \begin{bmatrix} I(t) \\ Q(t) \end{bmatrix} = \begin{bmatrix} I(t)cos(\phi_{Shift}) + Q(t)sin(\phi_{Shift}) \\ Q(t)cos(\phi_{Shift}) - I(t)sin(\phi_{Shift}) \end{bmatrix}.$$

(2.26)

Unlike RF and LO phase shifting requiring varactors, baseband phase shifting can be implemented using variable gain amplifiers. Despite extra parasitics due to the gain control, the worst case power consumption happens when I/Q channel signals have the same gain, i.e. at 45° phase setting. To achieve the same gain G as other settings, each channel has a gain of  $G/\sqrt{2}$ , resulting in a power consumption of  $\sqrt{2}$  times a normal baseband amplifier power. The extra power consumption is therefore roughly 40% of a baseband amplifier per I/Q channel and 80% in total. Depending on the loading at baseband, the required power consumption of a differential amplifier is known to be

$$I_{DC} = \frac{GBW \times V^*C_L}{1 - GBW\gamma/\omega_T},\tag{2.27}$$

where GBW is the required gain bandwidth of the amplifier and  $\gamma$  is the ratio between drain capacitance and gate capacitance. Therefore with 10GHz gain bandwidth, 100GHz  $f_T$  at a  $V^*$  of 200mV will result in about 13mW/pF power consumption. This implies that even when driving 100fF load, the extra power consumption due to the phase shifting is only  $0.8 \times 1.3mW \approx 1mW$ , significantly smaller than the other candidates.

One benefit of RF phase shifting scheme is that the interference from non-desired directions is canceled out before the mixer; in contrast, the interfere proceeds towards the mixer in LO and BB phase shifting schemes. Because the mixer is normally a highly non-linear block, it can potentially create many undesired mixing products between interference and

the desired input signal. This is an issue in many radar systems to avoid intentional jammer. However, in a collaborative scenario where all system use beam-forming techniques, interference should be minimal.

Therefore, the rest of this thesis will focus on the design of baseband phase shifting scheme due to its promising power consumption, and a detailed design study will be demonstrated in the next chapter.

### 2.3.4 Transmitter Phased-Array Architecture

The comparison in the transmitter is even simpler than the receiver. This is because the RF path in the transmitter always handles high power levels, and thus there is no difference between LO and RF phase shifting. Therefore any loss on the RF path will turn out to be a large power penalty. Since the baseband signal is in general digital, baseband phase shifting is straightforward to implement. The interference issue mentioned in the receiver part does not exist in the transmitter, which makes baseband phase shifting definitively the best candidate.

### 2.4 Phase Resolution

In the discussion above, it was assumed that the phase can be adjusted with infinite resolution. However, all implementations have limited phase shifting resolutions. In particular, the finite resolution in phase shifter might affect the phase alignment at desired direction, causing less than maximum radiation and directly affecting the SNR. It is therefore important to quantify what resolution is needed in phase shifters.

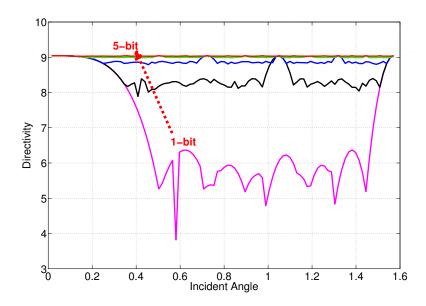

There are multiple criteria to select the number of bits in phase. One of the most commonly used ones is based on the peak directivity [12]. This is defined as the ratio between radiation intensity in the desired direction and the total radiated power. Fig. 2.5 shows the directivity when pointing at different directions with different resolutions in the phase shifters. With an 8-element phased-array as an example, when the resolution is low, instead of getting the desired 9dB directivity, the directivity is reduced by the misalignment in phase. When the resolution is 5-bit, however, there is a negligible difference between the achievable directivity and the ideal case.

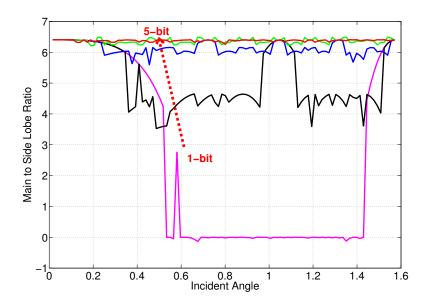

Another common measure of phased-array performance is to measure the ratio between peak directivity and the first side lobe. This provides information about how well the phasedarray rejects interfering signals. Similar to before, an 8-element array is used here as a demonstration and 5-bit resolution also shows sufficient resolution for this purpose.

The resolution requirement is actually dependent on the number of elements. A detailed analysis can be found in [30]. Intuitively, this is because the quantization noise is averaged and thus smeared out when multiple of them are added together. However, based on the simulated system performance, for a reasonable size array (4-16 elements), 5-bit resolution is usually sufficient, which translates to a  $\sim 10^{\circ}$  phase step.

Figure 2.5: Directivity at different directions with different phase shifter resolution.

Figure 2.6: Peak to side lobe ratio at different directions with different phase shifter resolution.

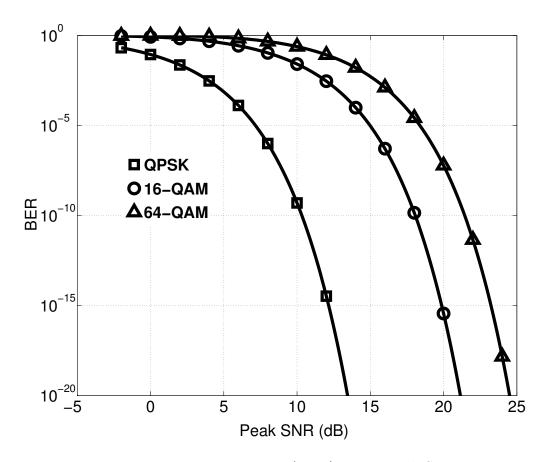

Figure 2.7: Bit error rate (BER) versus peak SNR.

## 2.5 Modulation Scheme

Another important design parameter at system level is the modulation scheme. Conventional approaches use high-order modulation scheme to achieve high data rate in a limited bandwidth. In the case of 60GHz, we propose to utilize the entire 7GHz bandwidth to achieve 10Gb/s with QPSK modulation. It is desired to compare different modulation schemes based on the same power consumption. The relation between BER and SNR for different modulation schemes was well studied [31]. Fig. 2.7 modifies the conventional plot by using Peak SNR rather than average SNR of the symbols. This is because the power consumption of the transmitter is often proportional to the peak amplitude rather than the average. As a result, shown in Fig. 2.7, with the same BER of 10<sup>-10</sup>, QPSK requires about 8dB lower SNR than 16-QAM. Notice that when targeting the same data rate, the noise power of QPSK is 3dB higher than 16-QAM and 5dB higher than 64-QAM due to its higher bandwidth. QPSK modulation therefore has a net 5dB SNR advantage over 16-QAM, which makes it appealing for our system.

### 2.6 Summary

This Chapter discussed the system level design considerations for phased-array architectures. Besides phase resolution and modulation scheme, our analysis concluded that the key to achieving high efficiency phased-array is to reduce the overhead power consumption in the transceivers. Compared to a single-element transceiver, in a phased-array system, phase shifter is one common overhead building block in both transmitter and receiver. Since our proposed baseband phase shifter is compelling compared to other candidates, the next chapter will discuss in detail the challenges as well as design procedures to implement such a scheme. Techniques for the rest of the transmitter and the receiver are then discussed in the following chapters.

# Chapter 3

# Implementation of Baseband Phase Shifting

As discussed in Chapter 2, the baseband phase shifting scheme is promising for energy-efficient phased-array systems. This chapter therefore discusses the implementation details at the circuit level. Much like normal amplifiers, a baseband phase shifter should meet certain gain, bandwidth, and noise specifications. The key difference is that the phase shifter needs to provide a certain resolution to adjust the phase of the input signal. Throughout this chapter, this requirement will be elaborated and then mapped to various implementation schemes. Understanding the trade-off helps to select the appropriate scheme in different scenarios. Methods to reduce the parasitics are also proposed and implemented for validation.

### 3.1 Implementation of Phase Shifter Resolution

Based on equation (2.26), it is straightforward to implement the phase shifter using four variable gain amplifiers (VGAs) and then summing two of the outputs respectively (Fig. 3.1). The gain settings of the variable gain amplifiers are determined by the phase shifting settings, denoted in Fig. 3.1. The resolution of the phase shifting therefore dictates the resolution of the gain control of each VGA. The relation between them is analyzed below. Assuming that only the I-to-I VGA changes its gain with one single step, the phase change is

$$\Delta \phi = \arctan(\frac{A_I + \Delta A_I}{A_Q}) - \arctan(\frac{A_I}{A_Q})$$

$$= \frac{\Delta A_I}{A_Q} \times \arctan'(\frac{A_I}{A_Q})$$

$$\approx \frac{\Delta A_I/A_Q}{1 + A_I^2/A_Q^2}$$

$$= \frac{\Delta A_I \times A_Q}{A_I^2 + A_Q^2}.$$

(3.1)

Figure 3.1: Baseband phase shifter utilizing variable gain amplifier.

where  $A_I$  and  $A_Q$  are the gain setting of the two amplifiers respectively and  $\Delta A_I$  is the single step gain variation.

It is common to keep the amplitude  $A_I^2 + A_Q^2$  relatively constant (=  $A^2$ ) so that the gain variation is small. Therefore, given the form of equation 3.1, the phase change is proportional to the gain of the Q-to-I VGA, which is maximized when its gain reaches its peak. This indicates the largest step size in the phase resolution happens when quadrant switching occurs - i.e.:

$$\Delta \phi_{max} = \frac{\Delta A_I A_{Q,max}}{A^2} = \frac{\Delta A_I}{A}.$$

(3.2)

Assuming a constant step size in VGA gain control, in order to achieve a resolution of  $\delta\phi$  with a gain coverage from -A to A, the number of steps in the gain control needs to be

$$N_{step} = \frac{2A_{I,max}}{\Delta A_I} = \frac{2}{\delta\phi(rad)}.$$

(3.3)

In the case of  $\delta \phi = 10^{\circ} = 0.17 rad$ , this translates into  $N_{step} = 12$ , or less than 4-bit resolution equivalently.

### 3.2 Effect of I/Q Mismatch

The calculation above assumes that the I/Q signals are correctly down-converted to baseband. However, impairments in the RF system can easily violate these assumptions. Fortunately, these errors can also be corrected using the proposed phase shifter by adjusting the gain in the VGAs accordingly. From a design perspective, this will increase the necessary resolution in gain control of the VGA. Quadrature phase error is examined here first. Assuming there is a phase error in the LO signal such that without any phase shifting, the output of the down-converting mixer produces

$$LPF\{(I(t)cos(\omega t) + Q(t)sin(\omega t)) \times cos(\omega t)\} = I(t).$$

$$LPF\{(I(t)cos(\omega t) + Q(t)sin(\omega t)) \times sin(\omega t + \phi_{err})\} = Q(t)cos\phi_{err} + I(t)sin\phi_{err}.$$

(3.4)

Intuitively, this means that the I-channel remains correct but that there is a portion of the I-signal leaking into the Q-channel. In a matrix format, this can be written as

$$\begin{bmatrix} I'(t) \\ Q'(t) \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ sin\phi_{err} & cos\phi_{err} \end{bmatrix} \begin{bmatrix} I(t) \\ Q(t) \end{bmatrix}.$$

(3.5)

Therefore the original signal I(t), Q(t) can be obtained by inverting the erroneous matrix.

$$\begin{bmatrix} I(t) \\ Q(t) \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -\frac{\sin\phi_{err}}{\cos\phi_{err}} & \frac{1}{\cos\phi_{err}} \end{bmatrix} \begin{bmatrix} I'(t) \\ Q'(t) \end{bmatrix}. \tag{3.6}$$

This inverted matrix indicates that the gain range of the VGA needs to be extended by  $1/\cos\phi_{err}$  to handle the inversion and the original phase shifting functionality. In other words, with the same phase resolution requirement, the number of steps needs to be extended.

Gain error correction can also be easily supported by modifying the gain of the VGA straightforwardly. Assuming the gain difference is  $A_{err}(<1)$ , the complete transfer function of the phase shifter is the multiplication of the three matrices:

$$\begin{bmatrix} I(t) \\ Q(t) \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & \frac{1}{A_{err}} \end{bmatrix} \begin{bmatrix} 1 & 0 \\ -\frac{\sin\phi_{err}}{\cos\phi_{err}} & \frac{1}{\cos\phi_{err}} \end{bmatrix} \begin{bmatrix} \cos(\phi_{shift}) & \sin(\phi_{shift}) \\ -\sin(\phi_{shift}) & \cos(\phi_{shift}) \end{bmatrix} \begin{bmatrix} I'(t) \\ Q'(t) \end{bmatrix}. \quad (3.7)$$

The number of steps required in each VGA is thus determined by

$$N_{step} \ge \frac{2}{A_{err} \times cos\phi_{err} \times \delta\phi}.$$

(3.8)

As a sample design, a phase shifter targeting 3dB gain mismatch,  $20^{\circ}$  phase error, and  $10^{\circ}$  phase resolution requires a total of 18 steps. This is just slightly larger than the case where no gain/phase error is present, and a 4-bit gain control is sufficient.

### 3.3 Implementations of VGAs

#### 3.3.1 Variable Current Source

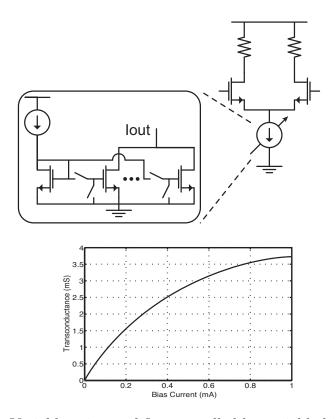

Variable gain amplifiers can be implemented in a variety of ways [32, 33, 34]. One popular topology implements variable gain by adjusting the tail current of a differential amplifier, as

shown in Fig. 3.2. The basic concept here is to change the transconductance of the differential amplifier in order to modify the gain. In a square-law device, the transconductance can be related to the bias current as

$$g_m = \sqrt{I_{bias}\mu C_{ox}W/L}. (3.9)$$

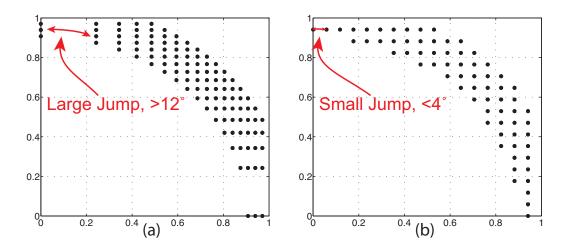

Although the transconductance does indeed vary with the current, the transfer curve from current to transconductance is not linear. Fig. 3.2 plots the simulated transconductance of a  $1\mu m$  differential pair versus tail current in 65nm CMOS technology, which is close to that predicted for a square law device. Importantly, this transfer curve is technology dependent, and therefore the gain control and phase shifting need to be calibrated before use. In the case where a uniform step-size control is used in the bias current, this non-linearity will increase the step size of transconductance step when current is low. As mentioned earlier, the worst phase step is at the quadrant switching; this additional error will further increase the step size. Using the sample device shown in Fig. 3.2, the resulting constellation is shown in Fig. 3.4(a). Clearly, the phase jump is much bigger when close to the quadrant switching compared with the phase jump at 45°. As a result, if uniform resolution in the current bias control is used, extra resolution has to be added to achieve the same phase resolution. Pre-distortion techniques can be potentially used to correct these effects, but this correction is heavily dependent on the linearity of the transistors. Furthermore, the overdrive voltage of the input devices varies with the bias current. This will result in a code-dependent signal non-linearity, which can potentially degrade the performance significantly.

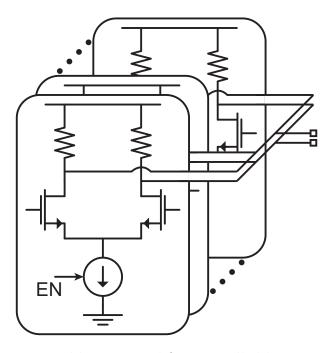

#### 3.3.2 Segmentation

In order to address these non-linearity issues, the VGA can be implemented by segmenting the amplifier into smaller pieces. The gain of the amplifier is controlled by turning on/off the segments independently (Fig. 3.3) as first proposed in [34]. Because each gm-cell is turned on/off separately, the transconductance is linear with code. This eliminates the calibration for gain control. The resulted constellation also has much better resolution at quadrant switching, as shown in Fig. 3.4(b).

## 3.3.3 Comparison

Compared to the variable current source approach, the segmentation approach clearly has the advantage of higher resolution. Because the overdrive voltage of each transconductance cell is kept constant, the linearity of the signal in a segmented approach can be the same regardless of the gain variation. Therefore, the second approach is more suitable for the receiver phase shifter because it requires to handle both the signal and inter-symbol-interference, and thus demands higher dynamic range. On the transmitter side, however, the first approach is sufficient with pre-distortion [18].

The drawback of the segmented approach, however, is that segmenting the amplifier into multiple pieces often introduces significant parasitic capacitance due to the physical

Figure 3.2: Variable gain amplifier controlled by variable bias current.

separation between them. In today's technologies, the parasitics can easily dominate over the intrinsic capacitance from the devices. Furthermore, with a large number of segments, each device can easily hit the minimum device size. These effects will substantially increase the power consumption required to achieve the same gain bandwidth. The next section therefore dives into the details of the implementation, attempting to reduce these parasitics.

## 3.4 Power Reduction in Segmented Approach

A straightforward implementation of a phase shifter requires one variable transconductance for the I-channel signal and another one for the Q-channel signal. The highest power consumption occurs when both the I and Q signals are amplified by  $g_m R_L/\sqrt{2}$  and the effective gain is only  $g_m R_L$ . The power consumption is therefore  $\sqrt{2}$  larger than a normal amplifier with the same  $g_m$ . Furthermore, the extra  $g_m$  presents capacitive loading on the output, resulting in double the self-loading. On a high-speed signal path, this will significantly reduce signal bandwidth, or increase the power consumption with the same gain bandwidth.

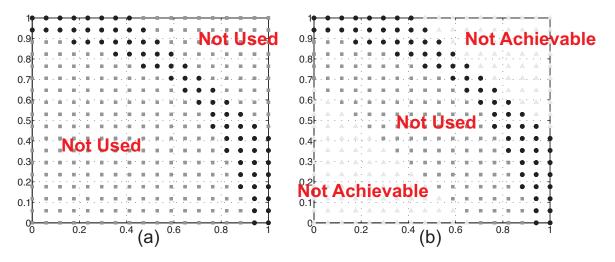

Notice that as shown in Fig. 3.5, all of the  $g_m$  cells will never be used at the same time in the phase shifter. In this particular example, segmentation of 16-unit  $g_m$  cells on each I/Q channel are implemented. The black dots on this constellation are the operating points

Figure 3.3: Variable gain amplifier controlled by segmentation.

Figure 3.4: Phase shifter constellations using (a) VGA with variable current source (b) segmentation.

selected for the phase shifter to achieve <1dB gain variation. The grey dots on the top-right corner represents the achievable constellation points that are not used due to their excess gain. In particular, the right-top corner point that represents all 32 cells being on is never used. The maximum number of  $g_m$  cells used at the same time in this scheme is only 24. This indicates that the total number of cells can be reduced by 25%, which would result in

improved power consumption.

Figure 3.5: Phase shifter constellations using (a) straightforward I/Q summation and (b) proposed I/Q partial sharing scheme.

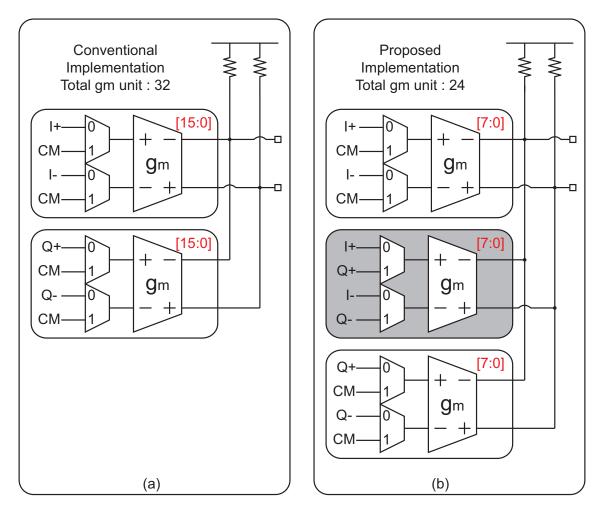

A partial sharing scheme is therefore proposed to more effectively partition and utilize the  $g_m$  cell, as illustrated in Fig. 3.6 [9, 33]. The conventional approach (a) uses 16 cells on each side, while the proposed implementation splits the  $g_m$  cells into three groups. In the first group, the input signal can be selected between I and common mode, achieving a variable gain amplifier by itself. Similarly, the third group selects between Q and common mode. The second group, however, implements a selection between the I signal and the Q signal, effectively reusing the same  $g_m$  cell when the other side is not at its peak gain. Each group consists of 8 unit  $g_m$  cells and the achievable constellations of the structures are shown in Fig. 3.5(b) for comparison. The proposed architecture eliminates the right top corner points which were not used in the conventional approach, while maintaing all of the desired constellation intact.

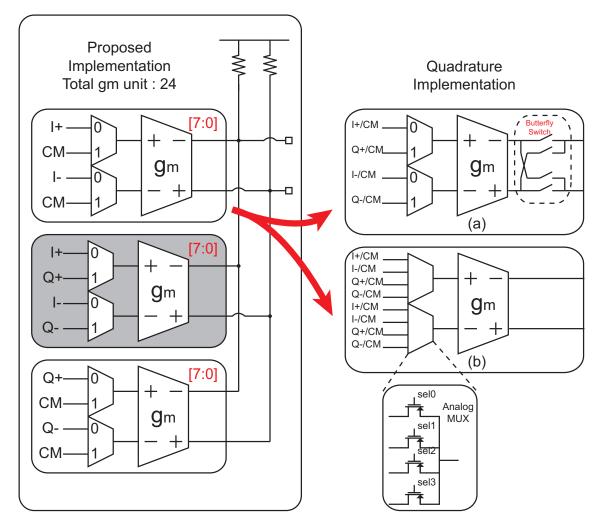

The previous discussions all focused on operation within the first quadrant. However, as seen in equation 2.26, the VGA needs to provide negative gain as well. Given differential signals are usually available at baseband, this can be easily achieved by adding multiplexers to select the polarity. One common approach is to use a butterfly switch at the output of the  $g_m$  cell to flip the sign of the output signal (Fig. 3.7). Often times this can be incorporated into the cascode transistors. This would double the self-loading due to the extra transistors, and therefore reduce the output bandwidth. More importantly, the butterfly switches will flip the offset from the input devices, creating a quadrant dependent offset at the output. Alternatively, one can extend the 2-to-1 MUX at the input to a 4-to-1 MUX to achieve the same functionality (Fig. 3.7), without modulating the input devices' offset.

Figure 3.6: Phase shifter implementation of (a) conventional (b) proposed architectures.

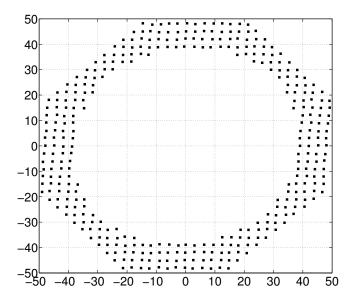

## 3.5 Phase Shifter Demonstration and Measurement Results

The proposed phase shifter has been implemented in several designs with various resolutions. In a complete transceiver shown in later chapters, a 4-bit/quadrant phase shifter was implemented using TSMC 65nm CMOS technology. The phase shifter drives roughly 50fF capacitive loading, and therefore, according to equation 2.27, it should approximately consume  $\sqrt{2} \times 13mW \times 0.05 = 0.9mW$ . With a gain of 3dB and bandwidth of 5GHz, this design employes the input MUX approach and consumes 1mW DC power, close to our expectation.

The design was characterized using a single tone test with a frequency offset between the RF and LO signals. The amplitude of output I/Q signal was then recorded as the constellation. Constellation measurement shown in Fig. 3.8 demonstrated the control of gain/phase settings of the phase shifter, including all the impairments from the RF signal

Figure 3.7: Quadrature implementation using (a) butterfly switches (b) 4-to-1 MUX.

path. It is shown here that the entire 360° range is covered with a better than 5° resolution.

## 3.6 Summary

This chapter discusses the implementation of the baseband phase shifter using variable gain amplifiers. The required phase resolution is mapped to the gain control resolution, taking into account the I/Q gain and phase mismatches due to RF impairments. Two implementation approaches of VGAs are presented and the segmented approach is chosen because of its better linearity in signal path as well as easier gain control.

To solve the issue of extra parasitic capacitances in the segmented approach, a partial sharing scheme is proposed to reduce the required segmentation to the minimum amount. The phase shifter can therefore be implemented with a power consumption that is  $\sqrt{2}$  higher

Figure 3.8: Measurement result of a phase shifter with 5-bit per quadrant resolution.

than a normal baseband amplifier with the same gain and bandwidth. An implementation in CMOS demonstrates this approach and the measurement results achieved a better than  $5^{\circ}$  resolution.

## Chapter 4

## Energy-Efficient Phased-Array Transmitter

Modern wireless transmitters have been extensively studied for numerous applications. In many applications the power amplifier consumes the majority of the DC power and hence the efficiency of the transmitter is limited by the PA efficiency. Significant effort has therefore been spent on optimizing the PA itself. However, as discussed in Chapter 2, the minimum DC power consumption of a phased-array is

$$P_{DC,TX,min} = 2\sqrt{\frac{EIRP \times P_{TX,OH}}{\eta_{PA} \times G_{TX}}},$$

(4.1)

indicating that overhead power is just as critical in a phased-array design. This chapter therefore studies the transmitter architecture, targeting a lower overhead power.

## 4.1 Low Overhead Transmitter Architecture

Fig. 4.1(a) shows a state-of-art 60GHz phased-array transmitter design[18] utilizing a conventional architecture, including a complex modulator followed by a power amplifier. The power consumption of the mixer and the LO buffers is 18mW, while the power amplifier consumes about 4mW and delivers roughly 0.7mW to the antenna. Therefore the entire 4-element phased-array delivers +10dBm EIRP with power consumption of roughly 88mW. As discussed in Chapter 2, such a system actually prefers less elements due to its high overhead power. For example, if a 2-element array is implemented where each element has 18mW overhead power and a 16mW power amplifier, the total EIRP remains the same as the 4-element system, but the DC power decreases to 68mW. Thus, reducing the modulator and LO power consumption is critical to utilize the benefit of phased-array for better performance.

One approach to reduce the overhead, as sketched in Fig. 4.1(b), modulates the oscillator phase directly using baseband data and then delivers power into the antenna. Since the oscillator power is directly proportional to the output power, the system efficiency is almost

identical to the oscillator's efficiency, eliminating almost all of the overhead power. Although conceptually simple, this architecture has only been implemented for simple modulation schemes like OOK, by turning on and off the oscillator [35, 36], resulting in a relatively low data rate. Furthermore, simply turning on/off the oscillator has no control over the phase, making this architecture hard to integrate into a phased-array system.

Figure 4.1: Transmitter architectures for (a) conventional and (b) proposed approaches.

## 4.2 Proposed Transmitter Architecture

In order to support QPSK modulation as well as phased-array functionality, the phase of the oscillator needs to be controlled. Notice that the phase of an oscillator can be determined by its startup conditions, and hence modulating the startup signal can potentially achieve the desired phase modulation of the oscillator. This concept is further illustrated in Fig. 4.2, where the oscillator is turned on and off during each baseband symbol. In the first cycle, the start-up signal starts at time 0 and therefore the phase of the first symbol is  $0^{\circ}$ . After turning off the oscillator at the end of the first symbol, the oscillator is turned back on again for the second symbol with a slight delay in the startup signal. Assuming the delay of the startup signal is controlled to be a quarter of the RF waveform period  $(T_p/4)$ , the second symbol has a phase of 90° compared to the first symbol. Similarly, 180° and 270° phase can

be achieved by increasing the delay. Alternatively, if the oscillator is differential,  $180^{\circ}$  and  $270^{\circ}$  phase can also be achieved by simply inverting the  $0^{\circ}$  and  $90^{\circ}$  symbols.

Figure 4.2: Oscillator phase modulation by baseband delay.