# UCLA UCLA Electronic Theses and Dissertations

## Title

Enabling Customized Computing in Datacenters: from Accelerator Design to System Integration

**Permalink** https://escholarship.org/uc/item/8bw0q5c8

## Author

Wei, Peng

**Publication Date** 2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Enabling Customized Computing in Datacenters: from Accelerator Design to System Integration

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Peng Wei

2018

© Copyright by Peng Wei 2018

#### ABSTRACT OF THE DISSERTATION

Enabling Customized Computing in Datacenters: from Accelerator Design to System Integration

by

Peng Wei

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2018 Professor Jason Cong, Chair

CPU-FPGA heterogeneous architectures are attracting ever-increasing attention in an attempt to advance computational capabilities and energy efficiency in today's datacenters. Such architectures provide programmers with the ability to reprogram the FPGAs for flexible acceleration of many workloads. However, this advantage is often overshadowed by two critical issues: 1) the poor programmability of FP-GAs and 2) the severe overhead of CPU-FPGA integration. For one thing, the conventional RTL-based FPGA design practice significantly slows down the application development cycle. Although recent advances in high-level synthesis (HLS) have improved the FPGA programmability to some extent, it still leaves programmers facing the challenge of manually identifying the optimal design configuration in a tremendous design space. This challenge thus demands intimate knowledge of hardware intricacies to address and a great deal of effort even for hardware experts. For another, even with a high-quality FPGA accelerator that achieves an ordersof-magnitude performance/watt gain for a computation kernel, such an impressive gain can often be dramatically offset by the extra CPU-FPGA data communication overhead, resulting in a much reduced system-wide speedup, or even slowdown.

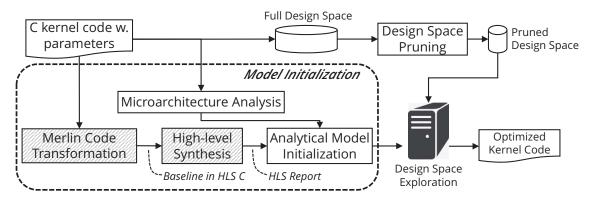

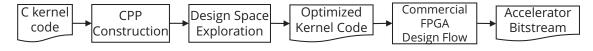

This thesis aims to address these two issues so as to facilitate the adoption of FP-GAs in datacenters. To improve the FPGA programmability, we propose a methodology that automates the heavy code reconstruction from software programs towards behavioral descriptions of high-quality FPGA designs, through well-defined architecture templates. Specifically, we propose the composable, parallel and pipeline (CPP) microarchitecture as an accelerator design template. This well-defined architecture template derives high-quality accelerator designs for a broad class of computation kernels, and substantially reduce the overall design space. Also, it enables the introduction of the CPP analytical model that quantifies the performance-resource tradeoffs among different configurations of the CPP template. This in turn leads to fast design space exploration to identify the optimal CPP configuration in a reasonable time. On top of the architecture template and its analytical model, we develop the AutoAccel framework to automatically transform an input computation kernel program into the optimal CPP-based design for it. For general application developers, AutoAccel supplies a nearly push-button experience to produce an FPGA accelerator with good performance; for FPGA design experts, it greatly reduces the effort of manual design space exploration and code reconstruction; it thus substantially improves the FPGA programmability in both cases.

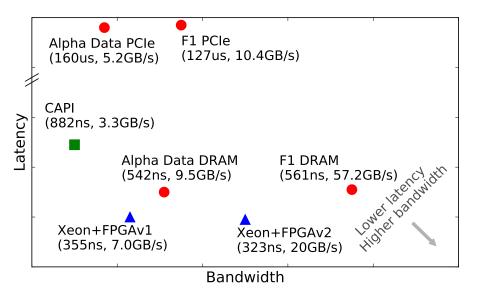

To come up with an efficient CPU-FPGA integration methodology, we first conduct a quantitative analysis on the microarchitectures of state-of-the-art CPU-FPGA platforms, with a key focus on the effective latency and bandwidth of the CPU-FPGA data communication. The analysis results reveal three important factors that affect the efficiency of CPU-FPGA integration: 1) payload size of every data transfer, 2) the complicated, multi-stage CPU-FPGA data transfer routine, and 3) sharing of the FPGA resource among CPU threads. We then propose three techniques: batch processing, fully-pipelined data communication stack and FPGA-as-a-Service (FaaS) framework, for these three factors, respectively. Batch processing packs small inputs into a large payload; the fully-pipelined stack overlaps various data transfer stages and the compute stage; both improves the data processing throughput. The FaaS framework treats the CPU threads as clients, and the FPGA as the server, and shares the server among the clients via the canonical client-server paradigm. These three techniques form our proposed methodology for efficient CPU-FPGA integration, which is demonstrated through the JVM-FPGA integration process for the genome sequencing application. The dissertation of Peng Wei is approved.

Glenn Reinman

Sriram Sankararaman

Milos Ercegovac

Jason Cong, Committee Chair

University of California, Los Angeles

2018

To my parents and wife.

## TABLE OF CONTENTS

| 1        | $\operatorname{Intr}$ | $\mathbf{roduction}$                                          | 1  |  |  |

|----------|-----------------------|---------------------------------------------------------------|----|--|--|

| <b>2</b> | Bac                   | ckground and Related Work                                     |    |  |  |

|          | 2.1                   | The High-Level Synthesis Technology                           | 8  |  |  |

|          | 2.2                   | CPU-FPGA Platforms for Datacenters                            | 3  |  |  |

|          | 2.3                   | Workloads                                                     | 7  |  |  |

|          |                       | 2.3.1 The MachSuite Benchmark Suite                           | 7  |  |  |

|          |                       | 2.3.2 Next-Generation Genome Sequencing                       | 8  |  |  |

|          | 2.4                   | Related Work                                                  | 21 |  |  |

|          |                       | 2.4.1 Enhancements to High-Level Synthesis                    | 21 |  |  |

|          |                       | 2.4.2 CPU-FPGA Platforms and Integration                      | 24 |  |  |

| 3        | Bes                   | t-Effort Code Reconstruction Guidelines for Microarchitecture |    |  |  |

| 0        | $\mathbf{ptim}$       | $\mathbf{zation}$                                             | 8  |  |  |

|          | 3.1                   | Overview                                                      | 8  |  |  |

|          | 3.2                   | Experimental Setup                                            | 81 |  |  |

|          | 3.3                   | Strategy #1: Explicit Data Caching                            | 32 |  |  |

|          |                       | 3.3.1 Cache: Not a Free Lunch Any More                        | 3  |  |  |

|          |                       | 3.3.2 Batch Processing and Data Tiling                        | 34 |  |  |

|          | 3.4                   | Go Parallel                                                   | 87 |  |  |

|     | 3.4.1 Strategy #2: Customized Pipelining $\ldots \ldots \ldots 39$                                     |

|-----|--------------------------------------------------------------------------------------------------------|

|     | 3.4.2 Strategy #3: Processing Element Replication $\ldots \ldots \ldots 41$                            |

| 3.5 | Faster Data Movement    44                                                                             |

|     | 3.5.1 Strategy #4: Double Buffering $\ldots \ldots \ldots \ldots \ldots \ldots 45$                     |

|     | 3.5.2 Strategy #5: Scratchpad Reorganization                                                           |

| 3.6 | Discussion                                                                                             |

| 3.7 | Conclusion                                                                                             |

| Aut | omated Accelerator Generation                                                                          |

| 4.1 | Overview                                                                                               |

| 4.2 | Accelerator Design Template                                                                            |

|     | 4.2.1 Problem Formulation                                                                              |

|     | 4.2.2 Composable, Parallel, Pipeline Microarchitecture                                                 |

|     | 4.2.3 Design Space Analysis                                                                            |

| 4.3 | CPP Analytical Model                                                                                   |

|     | 4.3.1 Performance Modeling                                                                             |

|     | 4.3.2 Resource Modeling                                                                                |

| 4.4 | Design Space Exploration                                                                               |

| 4.5 | Experimental Evaluation                                                                                |

|     | 4.5.1 AutoAccel Framework                                                                              |

|     | 4.5.2 Experimental Setup                                                                               |

|     | 4.5.3 Evaluation Results                                                                               |

|     | <ul> <li>3.6</li> <li>3.7</li> <li>Auto</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul> |

|   | 4.6 | Conch  | usion                                             | 89  |

|---|-----|--------|---------------------------------------------------|-----|

| 5 | CPI | U-FPC  | GA Integration                                    | 91  |

|   | 5.1 | Genor  | ne Sequencing Acceleration: The Story Begins      | 91  |

|   |     | 5.1.1  | Overview                                          | 91  |

|   |     | 5.1.2  | Experimental Setup                                | 94  |

|   |     | 5.1.3  | Harnessing FPGA in JVM                            | 97  |

|   |     | 5.1.4  | Conclusion                                        | 99  |

|   | 5.2 | The N  | Iystery of CPU-FPGA Communication                 | 99  |

|   |     | 5.2.1  | Overview                                          | 99  |

|   |     | 5.2.2  | Characterization of CPU-FPGA Microarchitectures 1 | 104 |

|   |     | 5.2.3  | Analysis and Insights                             | 115 |

|   |     | 5.2.4  | The JVM-FPGA Communication Routine                | 124 |

|   |     | 5.2.5  | Conclusion                                        | 126 |

|   | 5.3 | Batch  | Processing and FaaS: the Story Continues          | 127 |

|   |     | 5.3.1  | JVM-FPGA Communication Reduction                  | 127 |

|   |     | 5.3.2  | Sharing FPGA Among Multiple Threads               | 132 |

|   |     | 5.3.3  | Scaling FPGAs into Cluster Scale                  | 134 |

|   |     | 5.3.4  | Analysis of Communication Overhead                | 137 |

|   |     | 5.3.5  | Conclusion                                        | 139 |

|   | 5.4 | Fully- | Pipelined Communication Stack: The Story Ends 1   | 140 |

|   |     | 5.4.1  | Overview                                          | 140 |

| R | References |                                  |  |  |  |

|---|------------|----------------------------------|--|--|--|

| 6 | Conclusion | m ns                             |  |  |  |

|   | 5.4.6      | Conclusion                       |  |  |  |

|   | 5.4.5      | Experiments                      |  |  |  |

|   | 5.4.4      | Pipeline Throughput Optimization |  |  |  |

|   | 5.4.3      | Programming Model                |  |  |  |

|   | 5.4.2      | Pipelined Communication Stack    |  |  |  |

### LIST OF FIGURES

| 2.1  | Commercial HLS Tool Design Flow                                                                                                                  |    |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.2  | The Merlin Compiler Execution Flow                                                                                                               |    |  |

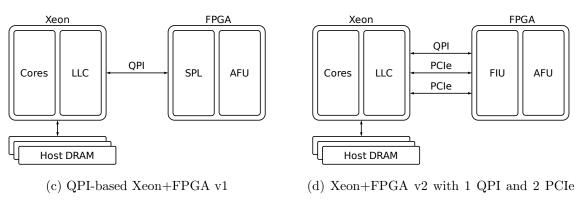

| 2.3  | A tale of five CPU-FPGA platforms                                                                                                                | 14 |  |

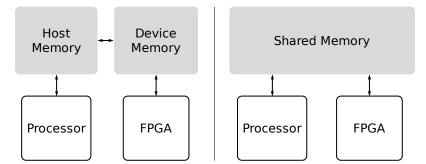

| 2.4  | Developer view of separate and shared memory spaces                                                                                              | 16 |  |

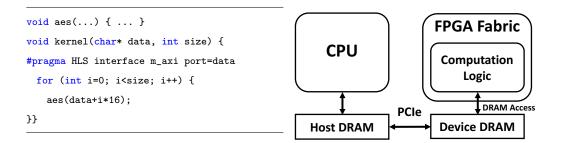

| 3.1  | Example AES kernel and naively generated architecture.                                                                                           | 33 |  |

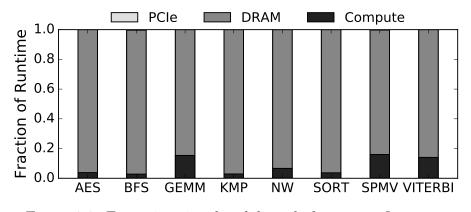

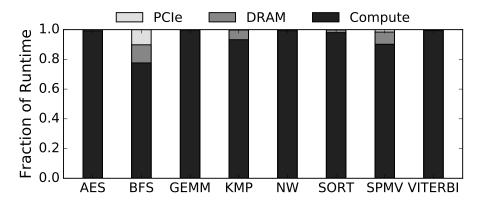

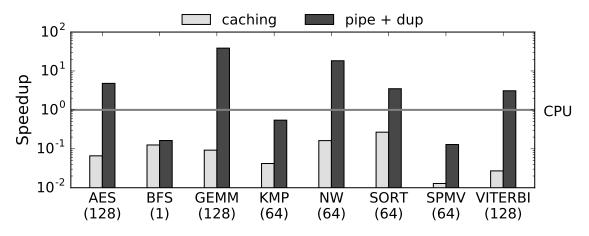

| 3.2  | Execution time breakdown before any refinement                                                                                                   | 34 |  |

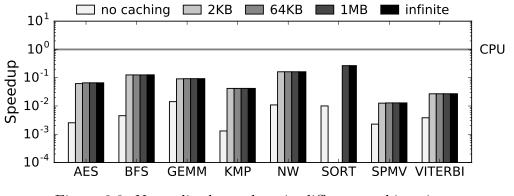

| 3.3  | Normalized speedups in different caching sizes                                                                                                   | 37 |  |

| 3.4  | Step-by-step example of applying the five optimization strategies to the AES benchmark. The complete code after applying all strategies is shown |    |  |

|      | in List 3.2                                                                                                                                      | 38 |  |

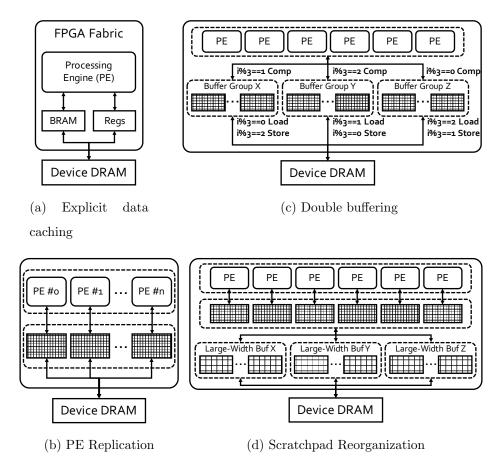

| 3.5  | High-level architecture diagram, corresponding to Figure 3.4                                                                                     | 39 |  |

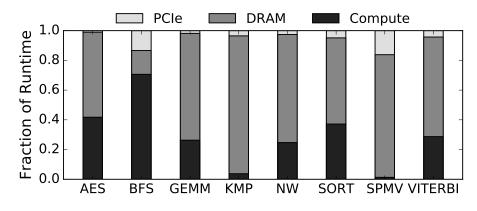

| 3.6  | Execution time breakdown before exploring parallelism                                                                                            | 41 |  |

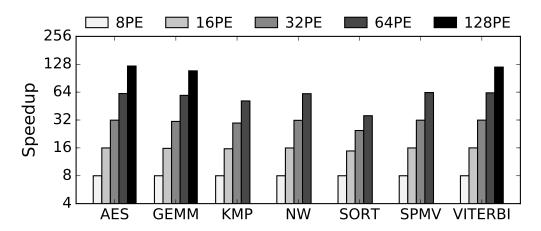

| 3.7  | Performance speedup on computation lead by PE replication                                                                                        | 44 |  |

| 3.8  | 8 Overall performance speedup after applying loop pipelining and PE repli-                                                                       |    |  |

|      | cation                                                                                                                                           | 45 |  |

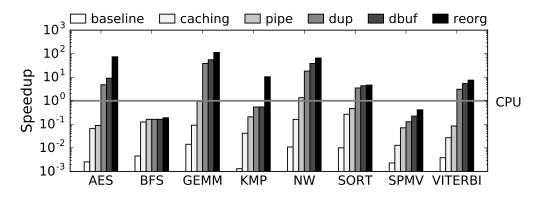

| 3.9  | Execution time breakdown before applying Strategy #4. $\ldots$ .                                                                                 | 45 |  |

| 3.10 | Performance improvement by applying five optimization techniques step                                                                            |    |  |

|      | by step (accumulative)                                                                                                                           | 51 |  |

| 4.1  | Step-by-step demonstration of the performance modeling process                                                                                   | 77 |  |

| 4.2  | Design Space Exploration Flow                                          | 80  |  |  |

|------|------------------------------------------------------------------------|-----|--|--|

| 4.3  | AutoAccel Framework Overview                                           | 85  |  |  |

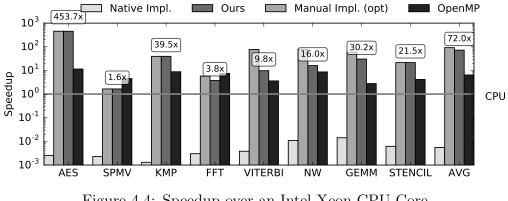

| 4.4  | Speedup over an Intel Xeon CPU Core                                    |     |  |  |

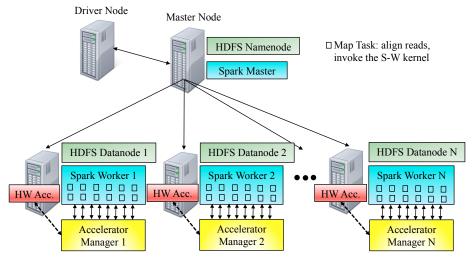

| 5.1  | An overview of the Spark-FPGA cluster                                  | 95  |  |  |

| 5.2  | Summary of CPU-FPGA communication bandwidth and latency (not to scale) | 103 |  |  |

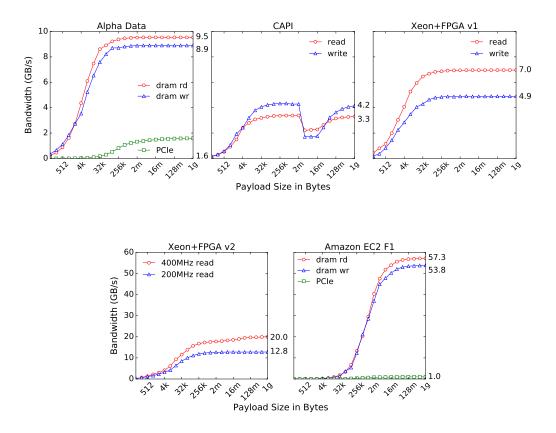

| 5.3  | Effective bandwidth of Alpha Data, CAPI, Xeon+FPGA v1 and v2, and      |     |  |  |

|      | F1                                                                     | 106 |  |  |

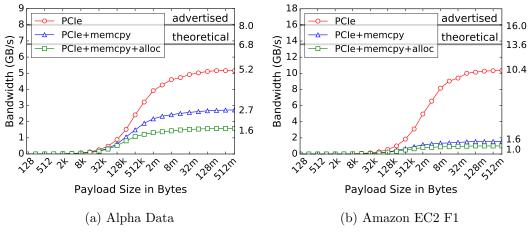

| 5.4  | PCIe-DMA bandwidth breakdown                                           | 107 |  |  |

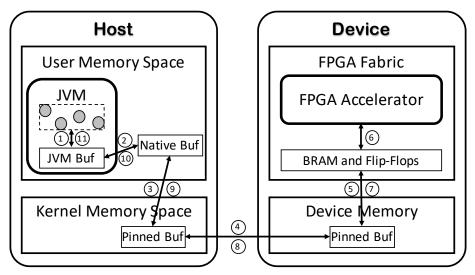

| 5.5  | JVM-FPGA Data Communication Routine                                    | 125 |  |  |

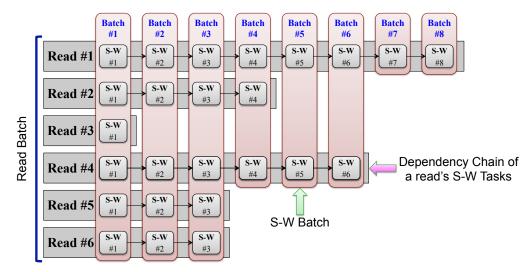

| 5.6  | Batch processing of multi-reads in CS-BWAMEM                           | 129 |  |  |

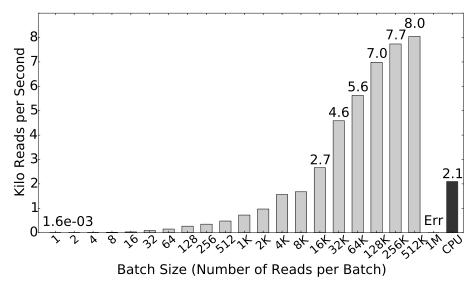

| 5.7  | Performance under different read batch sizes                           | 130 |  |  |

| 5.8  | Performance under different thresholds of Smith-Waterman batch size to |     |  |  |

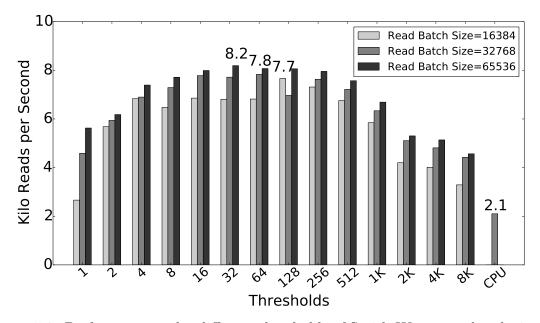

|      | decide FPGA offloading                                                 | 131 |  |  |

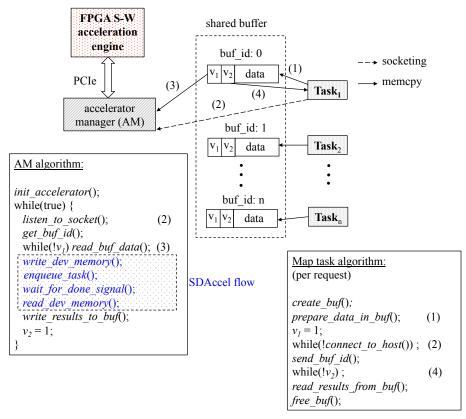

| 5.9  | FPGA as a Service (FaaS) framework [CCF16a]                            | 133 |  |  |

| 5.10 | ) Impact of thread contention                                          |     |  |  |

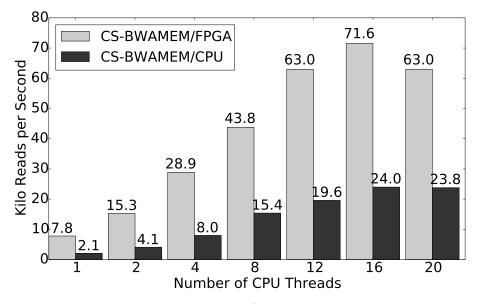

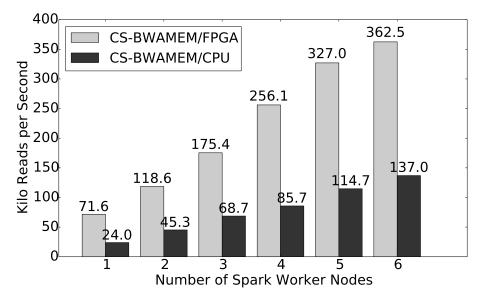

| 5.11 | Performance of CS-BWAMEM running in a cluster w/ & w/o FPGA            |     |  |  |

|      | integration                                                            | 138 |  |  |

| 5.12 | CS-BWAMEM execution time breakdown                                     | 138 |  |  |

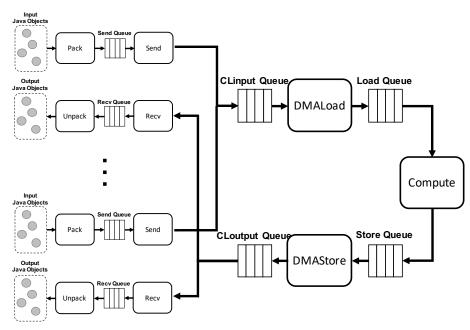

| 5.13 | JVM-FPGA Pipeline Architecture                                         | 143 |  |  |

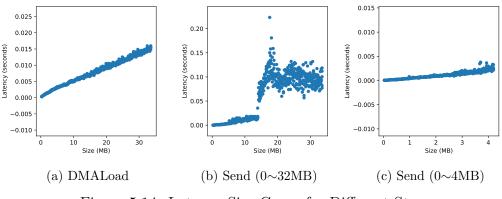

| 5.14 | Latency-Size Curve for Different Stages                                | 148 |  |  |

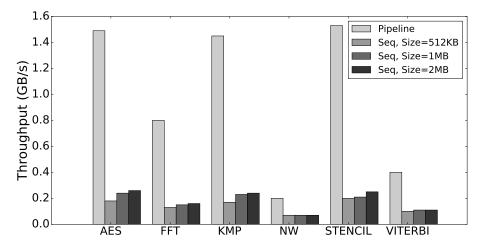

| 5.15 | Throughput comparison between the pipeline and sequential JVM-FPGA |     |  |

|------|--------------------------------------------------------------------|-----|--|

|      | communication stacks.                                              | 152 |  |

| 5.16 | Throughput comparison between the proposed approach and the ad hoc |     |  |

|      | solutions                                                          | 153 |  |

## LIST OF TABLES

| 2.1 | Merlin Compiler Code Transformations                                  | 11  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | Benchmark Description                                                 | 18  |

| 3.1 | Summary of optimization strategies.                                   | 31  |

| 3.2 | Configuration of hardware and software.                               | 32  |

| 3.3 | Performance speedup of pipelining on computation                      | 41  |

| 3.4 | PCIe transfer time normalized to CPU runtime                          | 55  |

| 4.1 | Configuration of Hardware and Software                                | 86  |

| 4.2 | Differences Between Model and HLS Reports                             | 87  |

| 4.3 | Differences Between Model and On-board Results                        | 88  |

| 5.1 | Experimental setup                                                    | 95  |

| 5.2 | Classification of modern CPU-FPGA platforms                           | 101 |

| 5.3 | Platform configurations of Alpha Data, F1, CAPI, Xeon+FPGA v1 and v21 | 105 |

| 5.4 | CPU-FPGA access latency in Xeon+FPGA 1                                | 12  |

| 5.5 | Hit latency breakdown in Xeon+FPGA                                    | 13  |

| 5.6 | Latencies of transferring a single 512-bit cache block                | 114 |

#### ACKNOWLEDGMENTS

It would not have been possible to complete this dissertation without the support of many kind people around me. It is my pleasure and honor to acknowledge their contributions.

First, I want to express my sincere gratitude to my advisor, Chancellor's Professor Jason Cong, for his profound guidance on how to systematically conduct academic research, constant support to address various research challenges, and valuable suggestions on almost every aspect of my PhD life. I am one of the very few students in the group who sets off the PhD track without any previous research experience. It is Professor Cong that devotes a great deal of effort to helping me build up my individual research capability from ground level. It is my great honor to have Professor Cong as my advisor.

Also, I want to thank Professor Glenn Reinman, Professor Sriram Sankararaman and Professor Milos Ercegovac for their serving on my dissertation committee and constructive comments regarding my dissertation. I would like to express my special thank to Professor Glenn Reinman who provides me with many valuable suggestions on the computer architecture research, which greatly helps my further study on CPU-FPGA platform microarchitectures and the methodology of efficient CPU-FPGA integration.

Many of my colleagues in the Center for Domain-Specific Computing (CDSC) have contributed to the dissertation. It is a great pleasure to work with them throughout these years. I especially thank:

• Yu-Ting Chen, for leading our long-term collaboration in genome sequencing

acceleration project, and invaluable guidance regarding both academia and career.

- Cody Hao Yu and Peipei Zhou, for our collaborations in a variety of research studies, including genome sequencing acceleration, AutoAccel, and CPU-FPGA communication pipeline, many of which form the foundation for this dissertation.

- Zhenman Fang, for his great mentoring support to my early PhD career.

- Yuchen Hao, Sen Li, Tianhe Yu, Licheng Guo, Yuze Chi and Professor Jie Lei, for their great help in our research collaborations and my PhD life.

- Young-kyu Choi and Zhenyuan Ruan, for our collaborations, technical discussions, and being so caring roommates.

- Alexandra Luong, for all the help on various paper work activities, and outstanding service on CDSC reviews and other meeting events.

- Janice Martin-Wheeler, for the hand-editing of all paper manuscripts.

The research studies in this dissertation are partially supported by CDSC under NSF Innovation Transition (InTrans) and from the CDSC industrial partners including Baidu, Fujitsu, Google, Huawei, Intel, NEC and VMWare; the NSF/Intel Partnership on Computer Assisted Programming for Heterogeneous Architectures (CAPA); C-FAR, one of the six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; CRISP, one of the six centers of the Joint University Microelectronics Program (JUMP). I would like to express my gratitude to these sponsors. Finally, I want to give my thanks to my parents and wife, the most important persons in my life. I cannot go this far without them standing behind me.

#### VITA

2010 B.S. (Computer Science), Peking University

2013 M.S. (Computer Science), Peking University, Beijing, China

2013–2018 Research Assistant, CDSC, University of California, Los Angeles

#### PUBLICATIONS

Chen, Y.T., Cong, J., Lei, J. and <u>Wei, P.</u> A novel high-throughput acceleration engine for read alignment. FCCM, 2015.

Chen, Y.T., Cong, J., Li, S., Peto, M., Spellman, P., <u>Wei, P.</u> and Zhou, P. CS-BWAMEM: A fast and scalable read aligner at the cloud scale for whole genome sequencing. HITSEQ, 2015.

Choi, Y.K., Cong, J., Fang, Z., Hao, Y., Reinman, G. and <u>Wei, P.</u> A quantitative analysis on microarchitectures of modern CPU-FPGA platforms. DAC, 2016.

Chen, Y.T., Cong, J., Fang, Z., Lei, J. and <u>Wei, P.</u> When apache spark meets FPGAs: a case study for next-generation DNA sequencing acceleration. HotCloud 2016. Cong, J., <u>Wei, P.</u>, Yu, C.H. and Zhou, P. Bandwidth optimization through on-chip memory restructuring for HLS. DAC, 2017.

Cong, J., <u>Wei, P.</u>, Yu, C.H. and Zhou, P. Latte: Locality Aware Transformation for High-Level Synthesis. FCCM, 2018.

Cong, J., <u>Wei, P.</u>, Yu, C.H. and Zhang, P. Automated accelerator generation and optimization with composable, parallel and pipeline architecture. DAC, 2018.

Yu, C.H., <u>Wei, P.</u>, Grossman, M., Zhang, P., Sarker, V. and Cong, J. S2FA: an accelerator automation framework for heterogeneous computing in datacenters. DAC, 2018.

Cong, J., <u>Wei, P.</u> and Yu, C.H. From JVM to FPGA: Bridging Abstraction Hierarchy via Optimized Deep Pipelining. HotCloud, 2018.

Cong, J., Guo, L., Huang, P.T., <u>Wei, P.</u> and Yu, T. SMEM++: A Pipelined and Time-Multiplexed SMEM Seeding Accelerator for Genome Sequencing. FPL, 2018.

Chi, Y., Cong, J., <u>Wei, P.</u> and Zhou, P. SODA: Stencil with Optimized Dataflow Architecture. ICCAD, 2018.

## CHAPTER 1

## Introduction

Due to power and energy constraints, conventional general-purpose processors are no longer able to sustain the performance and energy improvement in commercial datacenters. To overcome the inefficiency of homogeneous multicore systems, heterogeneous architectures that feature specialized hardware accelerators have been widely considered to be a promising paradigm [CSR11]. In particular, field programmable gate arrays (FPGAs), which offer the potential of orders-of-magnitude performance/watt gains for a broad class of applications while retaining reconfigurability, attract increasing attention as a mainstream acceleration technology. For example, both Microsoft and Baidu have incorporated FPGA-based accelerators in their datacenters to accelerate large-scale production workloads such as search engines [PCC14, CCP16] and neural networks [OLQ14, ORK15]. Amazon also introduced the F1 instance [amab], a compute instance equipped with one or more FPGA boards, in its Elastic Compute Cloud (EC2) [amaa]. Moreover, with the \$16.7 billion acquisition of Altera, Intel recently announced the Xeon+FPGA Accelerator Platform [harb], which provides an FPGA and a Xeon processor in a single semiconductor package. Predictions have been made that as much as 30% of datacenter servers will have FPGAs by 2020 [hara]. This suggests that FPGAs could become a common component in future servers and play an important role as primary computing resources [NSS16].

However, a major issue against the adoption of FPGAs in datacenters is the notoriously poor FPGA programmability. FPGA programming is generally recognized as an RTL (register-transfer level) design practice, which requires notable hardware expertise in designing accelerator microarchitectures such as controls, data paths, and finite state machines [Bri12]. This makes the effort of FPGA programming prohibitive to most datacenter application developers. It is even more challenging when the mainstream algorithm in an application domain is constantly evolving; i.e., an algorithm may have already been obsolete during the development process of its hardware accelerator.

Decades of research have focused on improving FPGA programmability. Highlevel synthesis (HLS) [CLN11] that allows hardware designs to be described in highlevel programming languages like C/C++ is recognized as an encouraging approach. Such C/C++ code for hardware designs is generally called the hardware behavioral description. Apparently, this high-level description, compared to its RTL counterpart, is much like the general software program. In fact, many C/C++ programs, without any modification on themselves at all, are already valid hardware behavioral descriptions, and can be compiled by state-of-the-art HLS tools like Xilinx SDAccel [sda] into working FPGA circuits. However, a high-quality software program is generally far away from a high-quality hardware behavioral description due to the lack of proper consideration regarding the underlying FPGA architecture. Our experiments show that a software program, if naively treated as a hardware behavioral description, almost always leads to an FPGA accelerator that performs orders-ofmagnitude worse than running the program on a modern CPU (see Section 3). This is because HLS still leaves programmers facing the challenge of manually identifying the optimal design configuration among a tremendous number of choices, and heavily reconstructing the software code to realize the identified optimal configuration. Addressing this challenge demands intimate knowledge of hardware intricacies, and a great deal of effort even for hardware experts. Consequently, HLS still presents a significant gap between a software program and a high-quality hardware behavioral description, which emerges as a serious impediment against the acceptance of FPGAs by datacenter application developers.

Another critical issue against the adoption of FPGAs in datacenters is the severe overhead incurred by integrating FPGA accelerators into the conventional CPU system. Although standalone FPGA accelerators promise orders-of-magnitude performance/watt gains for a variety of computation kernels, the benefit is often considerably offset by the extra CPU-FPGA data communication overhead. This in turn results in greatly reduced system-wide speedup, or even slowdown [CCF16a, HWY16, PHA17]. For example, our study on the acceleration for the genome sequencing application reveals that although the FPGA accelerator achieves over 100× speedup for the Smith-Waterman computation kernel, a straightforward integration of the accelerator into the software program is going to cause an 1000× slowdown of the entire system [CCF16a]. As a consequence, an efficient CPU-FPGA integration methodology, which is able to truly fulfill the significant gains of FPGA accelerators on computation kernels, is eagerly needed.

This dissertation is devoted to addressing the aforementioned two issues and facilitating the adoption of FPGAs in datacenters. The first objective is to improve the FPGA programmability by paving the path from a software program to a high-quality hardware behavioral description that 1) is functionally equivalent to the software program, and 2) leads to a high-performance FPGA accelerator. To meet this objective, we first conduct an analysis study to demystify the gap between software programs and hardware behavioral descriptions. Specifically, we start from a collection of benchmarks from MachSuite [RAS14] that consists of the software implementations of a broad class of computation kernels, feed these implementations without any code reconstruction into the Xilinx SDAccel tool to generate their corresponding hardware designs, and analyze the sources of microarchitectural inefficiency in these automatically generated designs. This study reveals three important insights: 1) software programs, which are designed to run on the CPU systems, poorly fit into the FPGA architectures; 2) the accelerators synthesized directly from software programs are trapped into a series of common sources of inefficiency; 3) these sources of inefficiency are able to be substantially resolved by following a besteffort code reconstruction practice of five refinement iterations. These five refinement iterations continuously improve the architecture of the generated accelerators, and finally achieve an  $42\sim29,030\times$  speedup.

Inspired by these insights, we propose our automated accelerator generation methodology to automatically transform software programs into high-quality hardware behavioral descriptions. Specifically, we derive from the best-effort code reconstruction practice an accelerator design template, called the composable, parallel, pipeline (CPP) microarchitecture, which provides a clear direction for the transformation. Such a clear direction significantly reduces the design space from "anything possible" to only the scope of CPP. Moreover, the well-defined CPP microarchitecture makes it possible to analytically quantify the performance-resource trade-offs among different design choices. We derive the CPP analytical model to achieve the analytical quantification, which in turn enables fast, analytical-based design space exploration to find the optimal CPP configuration in a reasonable time. Finally, we develop the AutoAccel framework to automate the entire code transformation process. Our experiments show that AutoAccel-generated accelerators drastically outperform the naive implementations by 27,000×, indicating that our proposed methodology has strongly addressed the gap from software programs towards hardware behavioral descriptions. Meanwhile, the AutoAccel-generated accelerators also outperform the software implementations by  $72\times$ , indicating that our approach does lead to highquality accelerator designs. For general datacenter application developers who may not want to be involved much in FPGA accelerator design, AutoAccel provides a nearly push-button experience to come up with a good design; for hardware experts who is willing to exert customized code reconstruction for better performance, AutoAccel also allows them to feed in the reconstructed code as input, and saves the manual effort in subsequent design space exploration and code transformation. In both cases, the FPGA programmability is substantially improved.

The dissertation then presents our research studies for addressing the second issue: the severe overhead incurred by the CPU-FPGA integration. In particular, we focus on the JVM-FPGA integration process since many state-of-the-art datacenter programming frameworks, e.g., Apache Hadoop [Whi12] and Spark [ZCD12], are based on the Java Virtual Machine (JVM) [LYB14]. We start from a case study in which we attempt to integrate an FPGA accelerator for the Smith-Waterman computation kernel [CCL15a] into CS-BWAMEM [CCL15b], a distributed genome sequencing software program that is based on the Apache Spark framework. The integration study reveals a rather surprising phenomenon that the system-wide performance is degraded by  $1000 \times$  if we straightforwardly integrate the accelerator with the Spark program (see Section 5.1). Our quantitative analysis reveals that even though the accelerator outperforms its software counterpart by over  $100 \times$ , it demands an extra JVM-FPGA data transfer routine to send (receive) data to (from) the FPGA, which consumes  $1000 \times$  more time than that of executing the kernel code on CPU. Therefore, the JVM-FPGA data communication overhead is the key factor to be blamed.

To acquire a better understanding of the CPU-FPGA data communication, we conduct a quantitative analysis on the microarchitectures of five state-of-the-art CPU-FPGA platforms, including the Alpha Data board [Xil17], Amazon EC2 F1 instance [amab], IBM CAPI [SBJ15], Intel Xeon+FPGA v1 and v2 [harb], with a key focus on their CPU-FPGA communication processes. The analysis results lead to a series of valuable insights for both datacenter application developers to choose the right platform and platform designers to evolve their platforms, and, moreover, suggest three key factors that affect the efficiency of the integration: 1) the payload size of each data communication transaction; 2) the complicated, multi-stage communication routine; 3) the sharing of the FPGA resource among multiple CPU threads. Inspired by these findings, we propose our integration methodology that contains three techniques for these three factors, respectively. First, we propose batch processing, which combines the input data of multiple transactions into one batch to send to the communication channel, to improve the payload size. Also, we propose a fully-pipelined JVM-FPGA data communication stack, which overlaps multiple data transfer stages and the compute stage, to improve the data processing throughput. Finally, we propose the FPGA-as-a-Service (FaaS) framework, which treats the CPU threads as clients and the FPGA accelerator as the server, and share the FPGA among the CPU threads via the canonical client-server framework, to achieve efficient resource sharing. By applying the proposed methodology back to the genome sequencing application, we not only eliminate the  $1000 \times$  slowdown, but achieve a  $3.5 \times$  system-wide performance improvement. This demonstrates the effect of our proposed CPU-FPGA integration methodology in alleviating the data communication overhead.

The remainder of this dissertation is organized as follows. Chapter 2 presents the background and related work, including recent advances of the HLS technology, stateof-the-art CPU-FPGA platforms, the MachSuite benchmark suite and the genome sequencing workload that are used for experimentation, and summaries of previous studies on the improvement for FPGA programmability and CPU-FPGA integration. Chapter 3 presents our best-effort code reconstruction practice to address the gap between software programs and hardware behavioral descriptions. Chapter 4 presents our CPP microarchitecture that is derived from the best-effort practice, its analytical model, and the AutoAccel framework. Chapter 5 presents our methodology for efficient CPU-FPGA integration, including our case study for the genome sequencing acceleration, the quantitative microarchitectural analysis regarding state-of-the-art CPU-FPGA platforms, and the three techniques that we propose to alleviate the data communication overhead. Chapter 6 concludes the dissertation and presents future research directions.

## CHAPTER 2

## Background and Related Work

This chapter presents the background information and related work for this dissertation. We first introduce recent advances of the high-level synthesis (HLS) technology, with a key focus on to what extent HLS improves the FPGA programmability and what problems HLS still leaves that prevent the programmability from being further enhanced (Section 2.1). Next, we categorize state-of-the-art CPU-FPGA platforms and summarize the microarchitectural features of each category (Section 2.2). We then describe our experimental workloads: the MachSuite benchmark suite and the genome sequencing workload (Section 2.3). Finally, we summarize the related work to this dissertation, including the previous studies on HLS enhancement, genome sequencing acceleration via distributed computing and hardware accelerators, and data communication optimization (Section 2.4).

## 2.1 The High-Level Synthesis Technology

A field-programmable gate array (FPGA) [BFR12] is an integrated circuit that contains an array of reprogrammable logic and memory blocks: lookup tables (LUTs), flip-flops (FFs), digital signal processing slices (DSPs) and block RAMs (BRAMs). Connected through a hierarchy of reconfigurable interconnects, these blocks can be customized into different circuits to solve various computation problems. Such hardware customizability allows FPGA circuits to avoid the significant overhead of the general-purpose microprocessors, resulting in orders-of-magnitude performance/watt gains for a broad class of computation kernels.

The notoriously poor programmability of FPGAs, however, emerges as a serious impediment against their acceptance by datacenter application developers. Conventionally, FPGA designers use register-transfer level (RTL) description languages, e.g., Verilog HDL (hardware description language) [TM08], to perform accelerator development for target computation kernels. Such a RTL programming practice has already made FPGA design unwelcome to most datacenter application developers who were mainly trained as software engineers. Besides, compared to simply writing a software program to implement a computation kernel, the RTL design demands a much longer development time even for hardware experts, and thus inevitably extends the time to market. Since many datacenter applications are constantly evolving, an old computation kernel may have already been obsolete before its accelerator is ready to use.

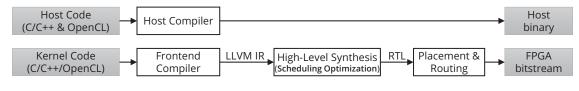

To address this issue, FPGA researchers and vendors start to resort to the HLS technology [CLN11] which uses software programming languages like C/C++ to describe hardware designs and relies on the HLS tools to transform the software-like design descriptions into the RTL descriptions. In fact, commercial HLS tools such as Xilinx SDAccel [sda] and Intel FPGA SDK for OpenCL [int] have been widely used to fast prototype user-defined functionalities expressed in high-level languages on FP-GAs without involving RTL descriptions. The example design flow used by common commercial HLS tools is shown in Fig. 2.1. First, a user input program is compiled to the LLVM Intermediate Representation (IR) [llv07], along with the construction

of its control data flow graph (CDFG). Then, the IR-to-HDL code transformation is performed to map the IR to an RTL design with scheduling optimization. This completes the HLS process that maps the behavioral description of a design to its RTL description. Subsequently, the conventional FPGA design automation flow is launched to generate the design's bitstream file that contains the configuration data for FPGA's logic and RAM blocks.

Figure 2.1: Commercial HLS Tool Design Flow

Commercial HLS tools usually have for users a set of language extensions, such as C pragmas, that provide the guidances of memory organization and task scheduling to complement the missing information of static analysis while optimizing the design. The language extensions are specified by the user at the source code level, but the core HLS code transformation and optimization happens at the intermediate representation (IR) level, indicating that the effectiveness of user guidances highly depends on its IR structure and front-end compiler. It implies that two programs with the same functionality but different coding styles (leading to different IR structures) might result in a significant performance difference. In fact, this difference can be up to several orders of magnitude based on our experiences (see Chapter 3). As a consequence, programmers have to pay attention to every detail that may affect the generated IR structure, which often demands a profound understanding of the FPGA architecture and circuit design. This easily leads to an impression that software programs and hardware behavioral descriptions, though looking quite alike, are completely different, and the gap between them is still prohibitively large.

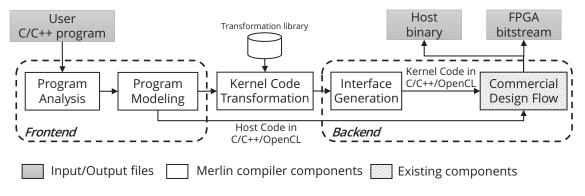

There has been existing effort that attempts to shorten this gap. The Merlin compiler [mer, CHP16a, CHP16b] is one representative example. The Merlin compiler is a source-to-source code transformation tool that brings FPGA programming to an even higher level than HLS. Specifically, it provides a transformation library that contains a series of code transformation primitives, each of which is associated with a predefined C pragma that abstracts a commonly used code reconstruction strategy, as listed in Table 2.1. As long as the developer inserts a pragma to the right place, the Merlin compiler will apply the corresponding transformation to reconstruct the computation kernel code automatically. As a result, HLS designers who harness the power of Merlin pragmas can save a great deal of labor effort in manually reconstructing their code to implement these primitives everywhere needed.

| Transformation | Target                                         | Parameters    | Description                               |

|----------------|------------------------------------------------|---------------|-------------------------------------------|

|                | Loop                                           | tilesize = S  | Tile the loop and create on-chip          |

| Data tiling    |                                                |               | buffers to cache the data with size $S$ . |

|                | Example: #pragma Accel data_tiling tilesize=16 |               |                                           |

| Memory         | Buffer                                         | bitwidth= $b$ | Pack DRAM buffer to $b$ bits.             |

| Coalescing     | Exampl                                         | e: #pragma A  | Accel bitwidth variable=buf factor=512    |

|                | Loop                                           | N/A           | Create a coarse- or fine-grained          |

| Pipeline       |                                                |               | pipeline (dataflow).                      |

|                | Example: #pragma Accel pipeline                |               |                                           |

|                | Loop                                           | factor= $N$   | Tile the loop and create $N$              |

| Parallelism    |                                                |               | processing elements (PEs).                |

|                | Example: #pragma Accel parallel factor=4       |               |                                           |

Table 2.1: Merlin Compiler Code Transformations

Based on the transformation library, Fig. 2.2 presents the Merlin compiler execution flow. It leverages the ROSE compiler infrastructure [ros00] and polyhedral framework [ZLC13] for abstract syntax tree (AST) analysis and transformation. The front-end stage analyzes the user program and separates host and computation kernel. The kernel code transformation stage then applies multiple code transformations according to user-specified pragmas. Note that the Merlin compiler will perform all necessary code reconstructions to make a transformation effective. For example, when performing loop unrolling, the Merlin compiler not only unrolls a loop but also conducts memory partitioning for the sake of avoiding bank conflict [CJL11]. Finally, the back-end stage takes the transformed kernel and uses the HLS tool to generate the FPGA bitstream.

Figure 2.2: The Merlin Compiler Execution Flow

Compared to the standard HLS solution, the Merlin compiler further improves the FPGA programmability by making design optimization "semiautomatic": instead of manually reconstructing the code to make one optimization operation effective, programmers now can simply place a pragma and let the Merlin compiler do the necessary changes. However, it still relies on programmers to determine the optimal combination and parameters of the transformation operations, and thus does not substantially relieve the burden. In this dissertation, we leverage its transformation library to agilely implement our proposed AutoAccel framework (see Chapter 4).

## 2.2 CPU-FPGA Platforms for Datacenters

A high-performance interconnect between host processor and FPGA is crucial to the overall performance of CPU-FPGA platforms. In this section, we first summarize existing CPU-FPGA architectures with typical PCIe and QPI interconnect. Then we present the private and shared memory models of different platforms.

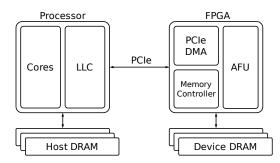

Typical PCIe-based CPU-FPGA platforms feature Direct Memory Access (DMA) and private device DRAM (Fig. 2.3(a)). To interface with the device DRAM as well as the host-side CPU-attached memory, a memory controller IP and a PCIe endpoint with a DMA IP are required to be implemented on the FPGA, in addition to user-defined accelerator function units (AFUs). Fortunately, vendors have provided hard IP solutions to enable efficient data copy and faster development cycles. For example, Xilinx releases device support for the Alpha Data card [Xil17] in the SDAccel development environment [sda]. As a consequence, users can focus on designing application-related AFUs and easily swap them into the device support to build customized CPU-FPGA acceleration platforms.

IBM integrates Coherent Accelerator Processor Interface (CAPI) [SBJ15] into its Power8 and future systems, which provides virtual addressing, cache coherence and virtualization for PCIe-based accelerators (Fig. 2.3(b)). A coherent accelerator processor proxy (CAPP) unit is introduced to the processor to maintain coherence for the off-chip accelerator. Specifically, it maintains the directory of all cache blocks of the accelerator, and is responsible for snooping the CPU bus for cache block

(a) Conventional PCIe-based platforms (e.g., Alpha Data board and F1 instance)

(b) PCIe-based CAPI platform

channels

Figure 2.3: A tale of five CPU-FPGA platforms

status and data on behalf of the accelerator. On the FPGA side, IBM also supplies a power service layer (PSL) unit alongside the user AFU. The PSL handles address translation and coherency functions while sending and receiving traffic as native PCIe-DMA packets. With the ability of accessing coherent shared memory of the host core, device DRAM and memory controller become optional for users.

Intel Xeon+FPGA v1 [harb] brings the FPGA one step closer to the processor via QPI where an accelerator hardware module (AHM) occupies the other processor socket in a 2-socket motherboard. By using QPI interconnect, data coherency is maintained between the last-level cache (LLC) in the processor and the FPGA cache. As shown in Fig. 2.3(c), an Intel QPI IP that contains a 64KB cache is required to handle coherent communication with the processor, and a system protocol layer (SPL) is introduced to provide address translation and request reordering to the user AFU. Specifically, a page table of 1024 entries, each associated with a 2MB page (2GB in total), is implemented in SPL, which will be loaded by the device driver during runtime. Though current addressable memory is limited to 2GB and private high-density memory for FPGA is not supported, this low-latency coherent interconnect has distinct implications for programming models and overall processing models of CPU-FPGA platforms.

Xeon+FPGA v2 co-packages the CPU and FPGA to deliver even higher bandwidth and lower latency than discrete forms. As shown in Fig. 2.3(d), the communication between CPU and FPGA is supported by two PCIe Gen3 x8 and one QPI (UPI in Skylake and later) physical links, which are presented as virtual channels on the user interface. The FPGA logic is divided into two parts: the Intel-provided FPGA interface unit (FIU) and the user AFU. The FIU provides platform capabilities such as unified address space, coherent FPGA cache and partial reconfiguration of user AFU, in addition to implementing interface protocols for the three physical links. Moreover, a memory properties factory for higher level memory services and semantics is supplied to provide a push-button development experience for end-users.

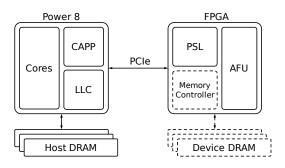

Accelerators with physical addressing effectively adopt a separate address space paradigm (Fig. 2.4). Data shared between the host and device must be allocated in both the host-side CPU-attached memory and the private device DRAM, and explicitly copied between them by the host program. Although copying array-based data structures is straightforward, moving pointer-based data structures such as linkedlists and trees presents complications. Also, separate address spaces cause data replication, resulting in extra latency and overhead. To mitigate this performance penalty, users usually consolidate data movement into one upfront bulk transfer from the host memory to the device memory. The Alpha Data board and Amazon EC2 F1 instance fall into this category.

Figure 2.4: Developer view of separate and shared memory spaces

With tighter *logical* CPU-FPGA integration, the ideal case would be to have a unified shared address space between the CPU and FPGA. In this case (Fig. 2.4), instead of allocating two copies in both host and device memories, only a single allocation is necessary. This has a variety of benefits, including the elimination of explicit data copies, pointer semantics and increased performance of fine-grained memory accesses. CAPI enables unified address space through additional hardware module and operating system support. Cacheline-aligned memory spaces allocated using **posix\_memalign** are allowed in the host program. Xeon+FPGA v1 provides the convenience of a unified shared address space using pinned host memory, which allows the device to directly access data on that memory location. However, users must rely on special APIs, rather than normal C or C++ allocation (e.g., **malloc/new**), to allocate pinned memory space.

Xeon+FPGA v2 supports both memory models by configuring the supplied mem-

ory properties factory, so that users can decide whether the benefit of having unified address space outweighs the address translation overhead based on their use case.

## 2.3 Workloads

#### 2.3.1 The MachSuite Benchmark Suite

MachSuite [RAS14] is a benchmark suite that contains a broad class of computation kernels programmed as C functions for accelerator study. For each kernel, MachSuite provides at least one implementation that is based on a commonly used algorithm in software programming, e.g., the queue-based algorithm for the BFS (breadth-first search) kernel. This feature makes MachSuite a natural fit for demonstrating our proposed design automation methodology that aims to facilitate datacenter application developers in transforming software programs into high-quality FPGA accelerator designs in a swift stroke. Table 2.2 lists its computation kernels, each with a brief description about its functionality and input settings.

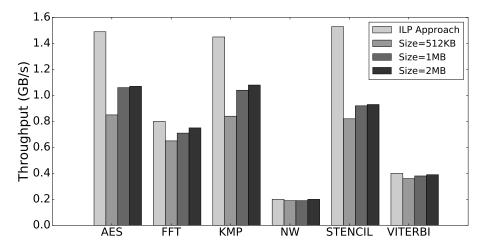

In this dissertation, the MachSuite benchmark suite is mainly used in Chapter 3 and 4 for the presentation of our automated accelerator generation methodology. Specifically, we demonstrate our best-effort code reconstruction practice via five iterations of refinement for the MachSuite computation kernel accelerators. We then use the benchmarks to evaluate the effectiveness of our proposed CPP microarchitecture and its analytical model, and the AutoAccel framework. MachSuite is also used for the evaluation of our proposed CPU-FPGA data communication pipeline in Section 5.4.

| Kernel  | Functionality and Input Settings                                                                 |  |  |

|---------|--------------------------------------------------------------------------------------------------|--|--|

| AES     | Advanced encryption standard. Input: 256-bit key; 64MB data.                                     |  |  |

| BFS     | Breadth-first search. Input: 4K nodes, 64K edges.                                                |  |  |

| GEMM    | General matrix multiplication ( $O(N^3)$ ). Input: two 1024×1024 64-bit FP matrices              |  |  |

| KMP     | Knuth-Morris-Pratt string matching. Input: 128MB string; 16B substring.                          |  |  |

| MD      | Molecular dynamics. Input: $128 \times 128 \times 128$ space, each with 16 molecules on average. |  |  |

| NW      | Needleman-Wunsch sequence alignment. Input: 64K pairs of 128-nucleotide seq.                     |  |  |

| SORT    | Merge sort. Input: 64MB integer array.                                                           |  |  |

| SPMV    | Sparse matrix-vector multiplication. Input: 4096×512 ELLPACK data and index.                     |  |  |

| VITERBI | Viterbi algorithm. Input: 1M 128-element chains.                                                 |  |  |

| FFT     | Fast Fourier transform. Input: 65536 strides each with 1KB size.                                 |  |  |

| STENCIL | Stencil computation. Input: a 4096×4096 image                                                    |  |  |

Table 2.2: Benchmark Description

### 2.3.2 Next-Generation Genome Sequencing

Next-generation sequencing (NGS) [SJ08] results from a combination of chemical engineering and computer science innovations. To sequence a human's entire genome, a number of copies of the individual's genome are fragmented into small pieces, called *reads*. These reads are fed into the chemical sequencer to determine the order of nucleotides for each of them. The sequenced reads are stored as ASCII strings, and aligned to specific locations of a golden reference genome to be assembled into an entire genome sequence. Generally, a sequencing instance processes hundreds of millions of reads, and each read is independently sequenced and aligned.

A typical genome sequencing pipeline contains the following two stages [LH10]. First, a read uses its substrings of various lengths to find candidate alignment positions on the reference genome. This stage is called *seeding*, and the substrings are called *seeds*. Second, each seed is extended leftward and/or rightward to both ends of the read. This stage is called *extending*, and a two-dimension dynamic programming algorithm, the Smith-Waterman algorithm [SW81], is applied to extend the seeds. Each read generates up to hundreds of extending tasks, i.e., up to hundreds of Smith-Waterman kernel invocations.

Various software tools have been proposed for one or more pipeline stages. The Burrows-Wheeler Aligner (BWA) [LD09, LD10, Li13] and Bowtie [LS12] are the most widely used software packages for the seeding and extending stages. The former is mainly used for DNA sequencing applications, like variant discovery, while the latter is mainly used for RNA sequencing applications, such as differential gene expression. The Genome Analysis Toolkit (GATK) [MHB10] contains a set of tools to handle the analysis after alignment. BWA, Bowtie and GATK leverage commodity multicore CPUs to explore the inherent task parallelism of next-generation genome sequencing. However, all of them are single-machine applications, which restricts the degree of parallelism to the number of CPU threads.

Scale-out computing has attracted more and more attention from both academia and industry. Big-data computing frameworks, like MapReduce [DG08, Whi12] and its successor Apache Spark with in-memory computing enhancement [ZCD12], have achieved great success in enabling easy development and deployment of big-data applications in datacenters. Next-generation sequencing has massive inherent parallelism, which makes it a good candidate for cluster scale acceleration. Recently, several cluster scale sequencing tools are being proposed to serve as alternatives of traditional tools like BWA, Bowtie and GATK. In [CCL15b], Chen et al. proposed CS-BWAMEM, a Spark-based MapReduce implementation for the seeding and extending stages. CS-BWAMEM implemented the same algorithm used in the latest BWA package, and improved the overall performance by 7x with a 25-node cluster.<sup>1</sup> In [MNH13], Massie et al. proposed ADAM, another Spark-based implementation, which provides a set of formats, APIs and tools for genome sequencing and analysis. By redefining the format of genome data to be more cluster-friendly, ADAM reports a 50x speedup on a 100-node cluster over GATK. In this dissertation we focus on the extending stage implemented in CS-BWAMEM, and use it as an application showcase to demonstrate how our proposed JVM-FPGA integration methodology reverses a  $1000 \times$  system-wide slowdown back to a  $3.5 \times$  speedup.

The two-dimension dynamic programming algorithm Smith-Waterman [SW81] used in the extending stage of the genome sequencing pipeline is a fundamental operation in computational biology. FPGA acceleration for the Smith-Waterman algorithm has attracted great attention from both academia and industry. Zhang et al. [ZTG07] implemented a systolic array based FPGA accelerator with up to 250x speedup over a 2.2GHz AMD Opteron processor. Kim et al. [Kim11] implemented a dynamic programming string matcher accelerator with 15x speedup over a 16-core CPU server. Olson et al. [OKC12] proposed a scalable FPGA-based solution that is faster than the Bowtie read aligner by 31x. Arram et al. [ATL13] implemented an approximate string matcher on a Maxeler FPGA board, outperforming the CPU-only and GPU-based implementation by 293x and 134x, respectively. Chen et al. [CCL15a] designed a throughput-oriented FPGA accelerator that is dedicated to accelerating the customized Smith-Waterman kernel implemented in BWA-MEM, the latest version of the BWA package, reporting a 26x speedup over a 12-core server. Ahmed et al. [ASH15] also designed an accelerator for the Smith-Waterman

<sup>&</sup>lt;sup>1</sup>The original BWA package is implemented in C++, re-implementing it in Java leads to a slowdown of around 2x. Therefore, only a 7x speedup is reported for a 25-node cluster.

kernel in BWA-MEM and claimed a 5.7x speedup over a 8-core server.

These proposed accelerators show a great potential for accelerating the Smith-Waterman computational kernel in genome sequencing applications, but lack integration into the full pipeline for large-scale whole genome sequencing. In this dissertation we focus on the integration of one recently-proposed Smith-Waterman accelerator [CCL15a] into the Spark implementation CS-BWAMEM.

# 2.4 Related Work

This section presents the related work to this dissertation. We first summarize the previous studies on the enhancement of the HLS technology in Section 2.4.1. Next, we present in Section 2.4.2 the studies on the CPU-FPGA integration.

### 2.4.1 Enhancements to High-Level Synthesis

High-Level Synthesis Automation. Many automated code transformations for the code reconstruction strategies covered in our best-effort practice (Chapter 3) have been proposed using commercial HLS tools like Xilinx SDAccel [sda] and Intel FPGA SDK for OpenCL [Int16], or open-source tools such as LegUp [CCA11] and CHiMPS [PBD08] as a back-end.

For on-chip data caching, existing automation strategies mainly focus on analyzing data access patterns, identifying data reuse between loop instances, and then generating on-chip buffers with proper partitions [CZZ12, PZS13, PSK15]. However, most solutions only consider arrays with affine accesses. Automated data caching for an array with arbitrary (non-affine, random, or even both) access patterns is still an open research problem. For *PE duplication*, the difficulty is that if we duplicate a large computation module, many hardware resources are required and imply less number of PEs. As a result, some researchers deal with this problem by developing algorithms to realize the duplication of a suitable PE granularity under resource constraints [HWB09, CHZ14], but leverage code modularization to users. Therefore, the restrictions on transforming user programs are still necessary. For *pipelining*, the impediments to achieving fine-grained fully pipelining mainly include 1) data/loop-carried dependency, 2) uncertain loop bounds [LBC15, LWC16], and 3) non-affine memory access [VHS15]. Although many researchers have figured out some solutions to each problem, a complete solution is still missing. For *double buffering*, the most widely used application is to form a coarse-grained (nested loop) pipeline [PKB16, LGJ14, TLZ15]. They extract necessary information from the problem using static analysis or user directives and apply predefined templates to form a coarse-grained pipeline using double buffers. Again, those solutions are not yet applicable to arbitrary user programs. On the other hand, there have some advance techniques that highly rely on hardware expertise so we do not cover in Chapter 3. For example, automated unified cache generation on FPGAs is implemented by [PKB16, WH13]. Advanced on-chip memory partition optimizations to avoid data access conflicts for improving pipelining and parallelism are also wellstudied [WLZ13, WLC14, CG15, SYZ16].

In summary, although many existing tools and frameworks are able to deal with certain HLS code optimization, simply applying all of them may not achieve high performance. The reason is that many kinds of optimization are related to hardware characteristics and may be affected by coding style a lot, so the order and type of applied optimization form a huge design space which is hard to be explored manually. However, our best-effort code reconstruction practice provides a direction for automation tool developers to figure out an effective solution of integrating existing HLS optimization to be a comprehensive framework. This is where our AutoAccel automated accelerator generation framework is inspired from.

**Domain-Specific Languages.** While generating accelerators from generic programming languages presents challenges in discovering parallelism, pipeline structures and memory access, researchers have explored domain-specific languages [SBC] to describe certain patterns and structures using domain knowledge. Lime [ABC10] is a Java-based domain-specific language that provides several parallel patterns to improve the programmability. Bluespec [Arv03] is a functional hardware description language based on Haskell with atomic actions. Chisel [BVR12] embeds hardware construction primitives with Scala and supports high-level abstractions and generators. DHDL [PKB16, KDP16] is an intermediate hardware representation that can be generated from parallel patterns such as map, reduce, zip and filter. This dataflow representation can be used to generate low-level HDL and aid design space exploration. TABLA [MPA16] provides an FPGA accelerator generator for machine learning algorithms that produces synthesizable Verilog code from user model specifications using a set of predesigned templates. Using a similar approach, DNNWeaver [SPA16] targets deep neural models.

Although these tools can provide higher productivity and generate more efficient hardware when applications have certain amenable characteristics, they are often limited to small domains and do not work well for applications outside those domains.

Analytical Modeling. Fast performance estimation on FPGAs has become popular in recent years. In general, performance analysis is mainly performed at either IR level [WHZ16, ZPW17, PKB16, KDP16, GWC16] or source code level [ZMS16]. The performance analysis at IR level has to compile the source code to the IR and perform analysis by traversing the control flow graph with dynamic profiling; while the source code level analysis is performed by statically looking at high-level constructs such as loops. Since most of the existing work performs analysis without explicitly considering back-end design flow [WHZ16, ZPW17, GWC16, PKB16, KDP16], their analysis cannot reflect the optimization done by the commercial tool. On the other hand, similar to our CPP analytical model, [ZMS16] builds the performance model with the help of the commercial tool, but [ZMS16] provides neither the resource model nor automated code transformation, so users still need to manually change the kernel code while considering the FPGA resource [PKB16, KDP16, ZPW17, ZPL16, Zha17, DZZ18], their LUT models are either based on machine learning [PKB16, KDP16, ZPW17, DZZ18] or even missing [ZPL16, Zha17].

### 2.4.2 CPU-FPGA Platforms and Integration

**CPU-FPGA Platform Analysis and Optimization.** In addition to the commodity CPU-FPGA integrated platforms summarized in Section 5.2, there is also a large body of academic work that focuses on how to efficiently integrate hardware accelerators into general-purpose processors. Yesil et al. [YOK15] surveyed existing custom accelerators and integration techniques for accelerator-rich systems in the context of data centers, but without a quantitative study as we did. Chandramoorthy et al. [CTI15] examined the performance of different design points including tightly coupled accelerators (TCAs) and loosely coupled accelerators (LCAs) customized for computer vision applications. Cotat et al. [CMD15] specifically analyzed the integration and interaction of TCAs and LCAs at different levels in the memory hierarchy. CAMEL [CGG13] featured reconfigurable fabric to improve the utilization and longevity of on-chip accelerators. All these studies were done using simulated environments instead of commodity CPU-FPGA platforms.

A number of approaches have been proposed to make accelerators more programmable by supporting shared virtual memory. NVIDIA introduced "unified virtual addressing" beginning with the Fermi architecture [Nvi09]. The Heterogeneous System Architecture Foundation announced heterogeneous Uniform Memory Accesses (hUMA) that will implement the shared address paradigm in future heterogeneous processors [Rog13]. Cong et al. [CFH17] propose supporting address translation using two-level TLBs and host page walk for accelerator-centric architectures. Shared virtual memory support for CPU-FPGA platforms has been explored in CAPI and the Xeon+FPGA family [SBJ15, harb]. This dissertation covers both the separate memory model (Alpha Data and F1 instance) and shared memory model (CAPI, Xeon+FPGA v1 and v2).

There is also numerous work that evaluates modern CPU and GPU microarchitectures. For example, Fang et al. [FMY15] evaluated the memory system microarchitectures on commodity multicore and many-core CPUs. Wong et al. [WPS10] evaluated the microarchitectures on modern GPUs. This work is the first to evaluate the microarchitectures of modern CPU-FPGA platforms with an in-depth analysis.

Integrating Accelerators into Datacenters. There is an increasing trend to integrate FPGA accelerators into modern datacenters. For example, Microsoft has developed a customized FPGA board, Catapult, and placed it into each server to accelerate the ranking stage of the Bing search engine in a 1632-node cluster [PCC14]. With a key focus on discussing the robust design of the large-scale system architecture, this publication did not reveal many details of the programming framework. Moreover, IBM has proposed the Coherent Accelerator Processor Interface (CAPI) to connect a PCIe-based FPGA board to a POWER8 processor, and integrated such FPGAs into its in-memory data structure store Redis to accelerate its Data Engine for NoSQL [BRH15]. In addition, there are some young start-ups, like Falcon [Sol] and Ryft [Ryf], that are working on the integration of FPGAs with Spark to accelerate big-data analytics. In Chapter 5 we aim to provide a more generalized methodology and insight for efficient integration of FPGA accelerators into stateof-the-art big-data computing frameworks like Spark, and therefore stimulate more innovations in this very hot area.

There are also several academic studies that deploy the Hadoop MapReduce framework or Message Passing Interface (MPI) [GGL99] in an FPGA-based cluster. In [LC13], Lin et al. deployed Hadoop in a cluster of low-end Xilinx Zynq FPGA SoC boards to accelerate a standard FIR filter. Similarly, in [NMG15], Neshatpour et al. deployed Hadoop in a Zynq-based cluster to accelerate machine learning kernels. In [MK15], Moorthy et al. deployed both OpenMPI and MPICH in a Zynq-based cluster to accelerate graph processing applications. In [TL10], Tsoi et al. proposed a heterogeneous cluster with GPUs and FPGAs, and deployed OpenMPI to accelerate N-body simulation. Our application showcase focuses on integrating FPGA accelerators into the Spark MapReduce framework due to its popularity and ease of programming and deployment for big-data applications.

Meanwhile, there are also some efforts that integrate GPU accelerators into

Hadoop and Spark. For example, in [GBS15], Grossman et al. proposed an automated flow to generate OpenCL kernels for Hadoop programs in a GPU-equipped cluster. In [LL15], Li et al. integrated GPU accelerators with Spark for deep learning algorithms. While these approaches usually target the integration of coarse-grained accelerators, we mainly focus on the integration of fine-grained FPGA accelerators, which introduces more challenges, like efficient communication and sharing.

A recent study in [SCN15] tried to automatically generate the OpenCL accelerator code from original Java code in Spark, which is an interesting and challenging direction for future work. Unfortunately it did not report any performance data. Finally, some prior efforts [YTT08, SWY10] also tried to propose a new MapReduce framework for easy accelerator development in a single-node FPGA-based platform.

# CHAPTER 3

# Best-Effort Code Reconstruction Guidelines for Microarchitecture Optimization

This chapter presents our analysis study that aims to demystify the gap between software programs and hardware behavior descriptions<sup>1</sup>. We find from this study that a best-effort code reconstruction practice with five refinement strategies is able to effectively fill this gap and lead to high-quality accelerator designs. We then are inspired to derive this best-effort practice into the composable, parallel, pipeline (CPP) microarchitecture and propose our AutoAccel framework on top of it, which is presented in Chapter 4.

# 3.1 Overview

Decades of research has been focusing on improving FPGA programmability. High-Level Synthesis (HLS) [CLN11] can derive high-quality accelerator designs directly from high-level behavioral descriptions, saving programmers from extensive handcoding in RTL and manual tuning. State-of-the-art HLS tools such as the Xilinx SDAccel [sda] and Intel FPGA SDK for OpenCL [int] allow computational kernels

<sup>&</sup>lt;sup>1</sup>This study is presented in [CFH18, CWY17]. I would like to convey my appreciation to all coauthors for their contributions to this study.

to be described in C/C++ and OpenCL, which can then be compiled and synthesized into FPGA accelerators. Using these tools, programmers can easily write synthesizable code or convert existing software implementations into FPGA accelerators. On top of the HLS compilation flows, FPGA vendors further provide system-level development environments that integrate a collection of intellectual properties (IPs), drivers, libraries and APIs. This facilitates faster integration of FPGA accelerators into CPU programs, frees developers from system-level integration such as external memory interfacing and CPU-FPGA data communication. As a result, a software programmer can extract targeted computational kernels from C programs (hosts), connect kernels to hosts via IDE-provided APIs, and feed both to the IDEs to infer FPGA accelerators from the kernels and integrate them into the hosts automatically. This demonstrates a quantum leap on FPGA programmability towards software programming, compared to the register-transfer level IC design.

However, a simple push-button process is far from producing high-performance FPGA accelerators. To demonstrate this, we compare the performance of a singlethread CPU with FPGA accelerators that are directly generated from the same software code of benchmarks from MachSuite. Unfortunately, these naive FPGA accelerators are more than 200x slower than the original software implementations running on a Xeon CPU core, which defeats our purpose of accelerating these computational kernels in the first place (see Section 3.3). To improve the quality of HLS-generated accelerators, many prior studies [HWB09, CZZ12, WH13, WLZ13, PZS13, CHZ14, LGJ14, LBC15, PSK15, VHS15, CG15, TLZ15, PKB16, LWC16, SYZ16] focus on proposing enhancements to HLS languages to express certain hardware structures. Nonetheless, most studies require the understanding of hardware intricacies in order for programmers to direct HLS tools to generate the right hardware structure. Also, choosing the right combination of optimization strategies among an exponential set of candidates is non-trivial even for experienced accelerator designers [WHZ16]. As a result, programmers often get the impression that software programs and hardware behavioral descriptions, though looking alike, are complete different.

In this study we aim to address the following questions: 1) what are the impediments that prevent software programs from being high-quality hardware behavioral descriptions? (2) Is there a common code reconstruction practice that is able to transform a broad class of computation kernel programs into high-quality behavioral descriptions? To answer these questions, we attempt to apply various HLS optimizations to the ported computational kernels from MachSuite. We are encouraged by the fact that the naively generated accelerators fall into a set of common sources of inefficiency, and a best-effort code reconstruction practice can produce quite compelling results: improving the accelerator performance by  $42 \sim 29,030 \times$  over the naive baseline, and outperforming a Xeon CPU core by  $34.4\times$  on average. Specifically, we use data-driven refinement to iteratively optimize the accelerator design: in each refinement iteration, we pinpoint the performance bottleneck and apply a set of HLS optimizations listed in Table 3.1. These HLS optimizations include explicit data caching through batch processing and data tiling, customized pipelining, processing element (PE) replication, double buffering and scratchpad reorganization. They take effect by constantly improving the underlying microarchitecture of the accelerators, which inspires us to derive the best-effort practice into the CPP microarchitecture and propose the entire automated accelerator generation methodology.

| HLS Optimization          | Counterpart in<br>Soft. Programming | Speedup   | Example             |

|---------------------------|-------------------------------------|-----------|---------------------|

| Explicit Data Caching     | Data Tiling                         | 5.6~32.1x | Fig. 3.4(a)         |

| Customized Pipelining     | Directive-Based<br>Programming      | 1.3~10.3x | Fig. 3.4(b)         |

| PE Replication            | Multithreading                      | 1.0~53.6x | Fig. <b>3</b> .4(b) |

| Double Buffering          | Comp./Comm.<br>Overlapping          | 1.0~2.1x  | Fig. 3.4(c)         |

| Scratchpad Reorganization | Bit Packing                         | 1.1~19.1x | Fig. <b>3.4</b> (d) |

Table 3.1: Summary of optimization strategies.

# 3.2 Experimental Setup

In this study we focus on the currently more accessible PCIe-based CPU-FPGA platform and HLS design flow to demonstrate the code reconstruction practice. Table 3.2 lists the detailed hardware and software configuration. A Xeon CPU is connected with an Xilinx Virtex-7 FPGA board through the PCIe interface. For a fair comparison, both the CPU and the FPGA fabric were launched in 2012. On top of the platform hardware, we use Xilinx SDAccel to provide a hardware-software co-design environment.

This study presents the code reconstruction practice through a complete accelerator design demonstration on a collection of benchmarks in MachSuite [RAS14]. Starting from the accelerators synthesized directly from the MachSuite kernel functions, Section 3.3, 3.4 and 3.5 present the five refinement strategies in the entire accelerator refinement process. The acceleration for the SORT (merge sort) kernel

| Host CPU Model        | Intel Xeon E5-2420 @ 1.9GHz (released in 2012) |  |  |

|-----------------------|------------------------------------------------|--|--|

| Host Memory           | 64GB DDR3-1600                                 |  |  |

| FPGA Fabric           | Xilinx Virtex-7 @ 200MHz (released in 2012)    |  |  |

| Device Memory         | 16GB DDR3-1600 (Max Band.: 12.8GB/s)           |  |  |

| CPU-FPGA Interface    | PCIe Gen3 x8 (Max Band.: 8GB/s)                |  |  |