## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Testing Hardware Security Properties and Identifying Timing Channels /

#### **Permalink**

https://escholarship.org/uc/item/8b530988

#### **Author**

Oberg, Jason Kaipo

## **Publication Date**

2014

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## **Testing Hardware Security Properties and Identifying Timing Channels**

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

by

Jason Kaipo Oberg

## Committee in charge:

Ryan Kastner, Co-Chair Timothy Sherwood, Co-Chair Ali Irturk Andrew Kahng Stefan Savage

Copyright

Jason Kaipo Oberg, 2014

All rights reserved.

| The Dissertation of Jason Kaipo Oberg is approved and is acceptable in |                 |

|------------------------------------------------------------------------|-----------------|

| quality and form for publication on microfilm and e                    | electronically: |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        |                 |

|                                                                        | Co-Chair        |

|                                                                        |                 |

|                                                                        | Co-Chair        |

University of California, San Diego 2014

## **DEDICATION**

To all the family, friends, and teachers who believed and supported me from the little island of Kauai.

## **EPIGRAPH**

Learning does not make one learned: there are those who have knowledge and those who have understanding. The first requires memory and the second philosophy.

Alexandre Dumas

## TABLE OF CONTENTS

| Signature Page                                                                                                                                                                                                                                                                                             | iii                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Dedication                                                                                                                                                                                                                                                                                                 | iv                              |

| Epigraph                                                                                                                                                                                                                                                                                                   | V                               |

| Table of Contents                                                                                                                                                                                                                                                                                          | vi                              |

| List of Figures                                                                                                                                                                                                                                                                                            | viii                            |

| List of Tables                                                                                                                                                                                                                                                                                             | X                               |

| Acknowledgements                                                                                                                                                                                                                                                                                           | xi                              |

| Vita                                                                                                                                                                                                                                                                                                       | xiv                             |

| Abstract of the Dissertation                                                                                                                                                                                                                                                                               | xvii                            |

| Chapter 1 Introduction  1.1 Overview  1.2 Thesis Outline  1.2.1 Background and Related Work  1.2.2 Deriving Equations for GLIFT Logic  1.2.3 Analyzing Timing Channels in Bus Protocols Using GLIFT  1.2.4 Testing Timing Channels in a System-on-Chip  1.2.5 Formal Analysis of Timing Channels and GLIFT | 1<br>1<br>5<br>5<br>5<br>6<br>6 |

| Chapter 2 Background and Related Work.  2.1 The Cost of Embedded Security  2.2 Information Flow Tracking and GLIFT  2.2.1 Using GLIFT as a Static Testing Technique  2.2.2 Example: Using GLIFT on AES  2.3 Timing-Channel Attacks                                                                         | 8<br>10<br>17<br>20<br>22       |

| Chapter 3 Fundamental GLIFT Logic Equations and Overheads  3.1 Taint and Tracking (GLIFT) Logic  3.2 GLIFT Logic for Basic Boolean Gates  3.3 GLIFT Logic Overheads  Chapter 4 Exploring Information Leaks in Bus Protocols                                                                                | 28<br>28<br>29<br>31            |

| <ul> <li>4.1 Information Flows in I<sup>2</sup>C</li> <li>4.1.1 Enforcing Non-interference in I<sup>2</sup>C</li> <li>4.1.2 I<sup>2</sup>C Non-interference Overheads</li> </ul>                                                                                                                           | 36<br>37<br>38                  |

| 4.2      | Inform  | nation Flows in USB                              | 40  |

|----------|---------|--------------------------------------------------|-----|

|          | 4.2.1   | Enforcing Non-interference in USB                | 43  |

|          | 4.2.2   | USB Non-interference Overheads                   | 43  |

| Chapter  | 5 Tes   | sting Timing Information Flows in Larger Systems | 46  |

| 5.1      | Design  | ning a Secure Crossbar in Wishbone               | 48  |

|          | 5.1.1   | Mix-Trusted System with Hardware Accelerator     | 50  |

|          | 5.1.2   | Building a Secure Cross-Bar for WISHBONE         | 52  |

|          | 5.1.3   | Secure Cross-Bar Evaluation                      | 54  |

| Chapter  | 6 For   | rmalizing Timing Channels at the Gate-level      | 59  |

| 6.1      | Threat  | Model                                            | 60  |

| 6.2      | Prelim  | ninary Definitions                               | 60  |

| 6.3      | Recap   | -Information Flow Tracking and GLIFT             | 64  |

|          | 6.3.1   | Formal definitions for GLIFT                     | 65  |

|          | 6.3.2   | GLIFT and Timing Channels                        | 68  |

| 6.4      | Isolati | ng Timing Channels                               | 70  |

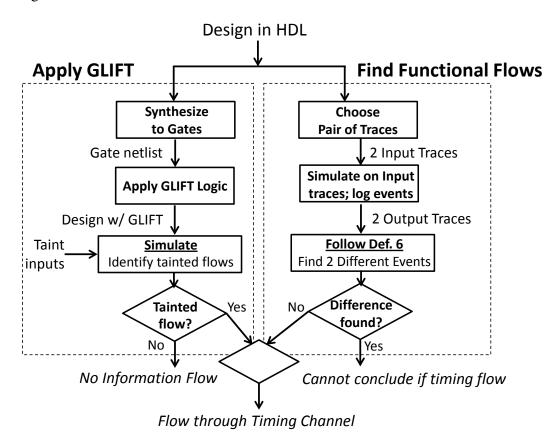

|          | 6.4.1   | Finding Functional Flows                         | 71  |

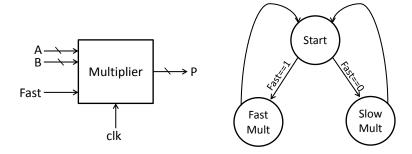

|          | 6.4.2   | A sample usage: fast/slow multiplier             | 75  |

| 6.5      | The B   | us Covert Channel                                | 76  |

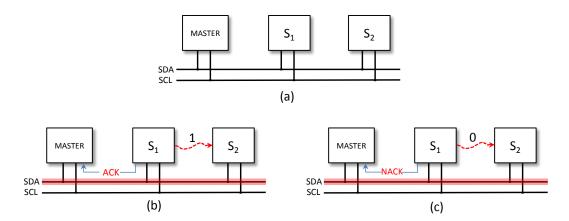

|          | 6.5.1   | Identifying Timing Flows in I <sup>2</sup> C     | 78  |

|          | 6.5.2   | Overheads                                        | 84  |

| 6.6      | Cache   | Timing Channel                                   | 85  |

|          | 6.6.1   | Overview of Access-Driven Timing Attacks         | 87  |

|          | 6.6.2   | Identifying the Cache Attack as a Timing Channel | 88  |

|          | 6.6.3   | Overheads                                        | 91  |

| 6.7      | Timing  | g Channels in RSA Encryption Core                | 92  |

|          | 6.7.1   | Detecting Leak as Timing Channel                 | 93  |

| Chapter  | 7 Co    | onclusion                                        | 95  |

| Chapter  | 8 Fu    | ture Research in Hardware Security               | 98  |

| Ribliogr | onhy    |                                                  | 101 |

## LIST OF FIGURES

| Figure 2.1. | Examples of different security lattices                                                                                                                    | 11 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2. | Simple code snippet showing information flow                                                                                                               | 12 |

| Figure 2.3. | GLIFT for a NAND gate.                                                                                                                                     | 15 |

| Figure 2.4. | GLIFT logic on a 1-bit counter.                                                                                                                            | 16 |

| Figure 2.5. | Using GLIFT as a testing technique                                                                                                                         | 18 |

| Figure 2.6. | Using GLIFT to test information flows in AES                                                                                                               | 21 |

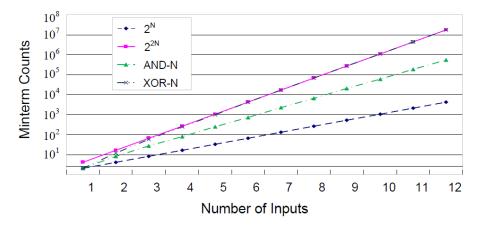

| Figure 3.1. | The number of minterms in the GLIFT logic function of gate primitives.                                                                                     | 32 |

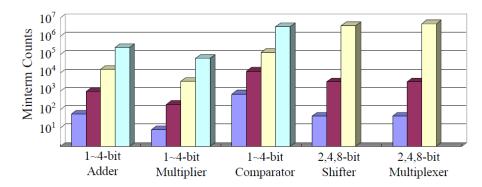

| Figure 3.2. | The number of minterms in the GLIFT logic function of several benchmarks.                                                                                  | 33 |

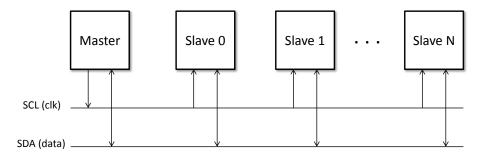

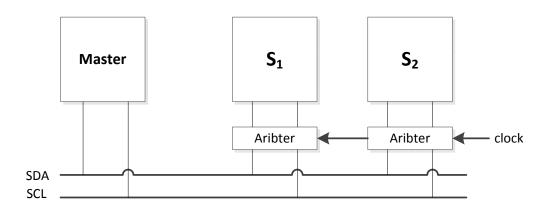

| Figure 4.1. | I <sup>2</sup> C Bus configuration. I <sup>2</sup> C can support several devices on a single global bus.                                                   | 36 |

| Figure 4.2. | I <sup>2</sup> C configured with an additional adapter to enforce TDMA. This enforces non-interference between devices under the presented test conditions | 38 |

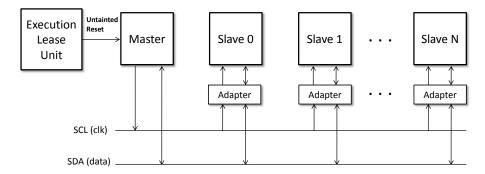

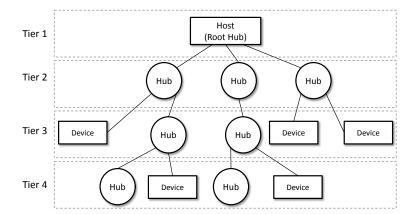

| Figure 4.3. | Packets sent from the host are broadcast onto the bus to all connected devices. The topology is a tiered star structure                                    | 41 |

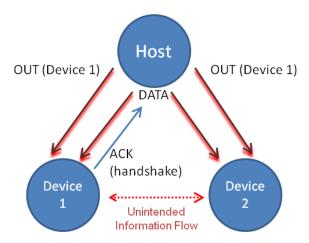

| Figure 4.4. | How USB leaks information during its broadcasting                                                                                                          | 42 |

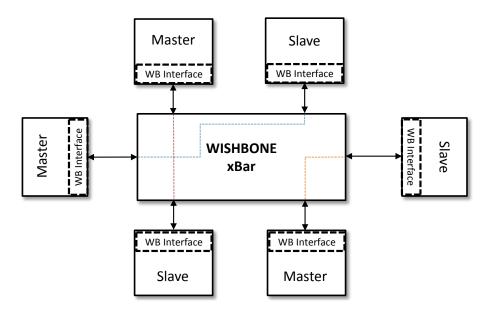

| Figure 5.1. | The WISBHONE bus architecture                                                                                                                              | 49 |

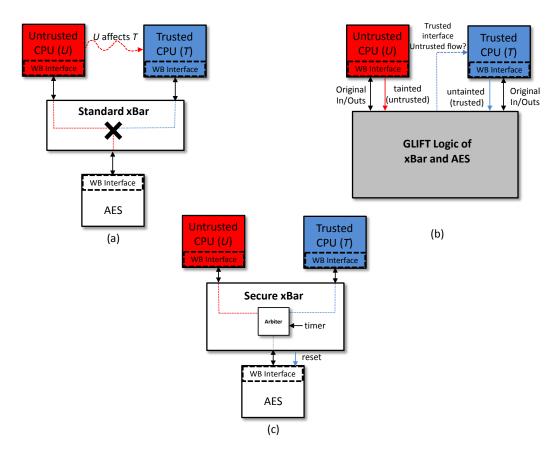

| Figure 5.2. | WISHBONE system used to test for information flows                                                                                                         | 51 |

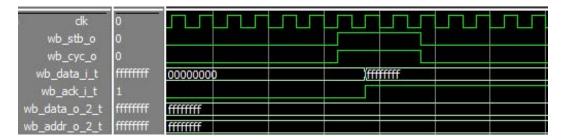

| Figure 5.3. | Waveform showing tainted information flow in WISHBONE                                                                                                      | 54 |

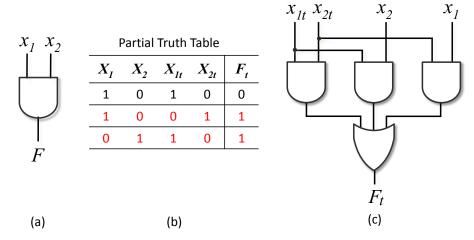

| Figure 6.1. | GLIFT tracking logic of an AND gate                                                                                                                        | 67 |

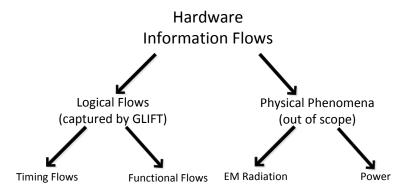

| Figure 6.2. | The classes of information flows in hardware                                                                                                               | 71 |

| Figure 6.3. | How the functional flow testing method can be used to isolate timing channels                                                                              | 72 |

| Figure 6.4. | Simple multiplier example demonstrating how to use our model to isolate timing channels | 75 |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 6.5. | The I <sup>2</sup> C bus architecture.                                                  | 79 |

| Figure 6.6. | Adding strict time-partitioning to the I <sup>2</sup> C bus                             | 81 |

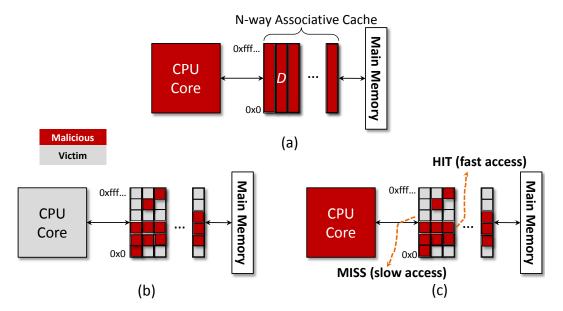

| Figure 6.7. | How timing attacks are performed on a processor cache                                   | 88 |

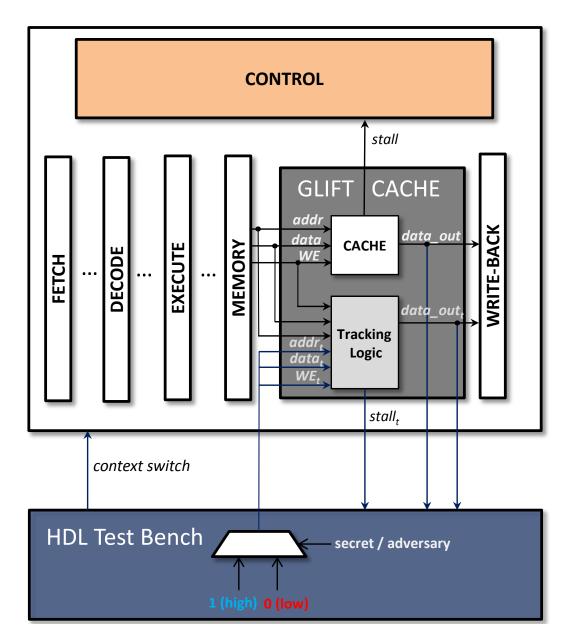

| Figure 6.8. | A block diagram of a simple MIPS-based CPU                                              | 90 |

## LIST OF TABLES

| Table 3.1. | GLIFT logic area and overhead for logic benchmarks                                                                                                                                                  | 33 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1. | Time spent simulating our particular test scenario for both the original I <sup>2</sup> C design and the one with GLIFT                                                                             | 39 |

| Table 4.2. | Area for $I^2C$ components in non-interference compliant design. This is the final system after testing and does not contain GLIFT logic                                                            | 40 |

| Table 4.3. | Time spent simulating the mentioned test scenario on USB with and without GLIFT.                                                                                                                    | 44 |

| Table 4.4. | Area Overhead for Replicating State Machines                                                                                                                                                        | 45 |

| Table 5.1. | Information flows when different applications on run on WISH-BONE system                                                                                                                            | 53 |

| Table 5.2. | Simulation times for various stages of our design. The base RTL refers to what is shown in Figure 5.2 (a). The GLIFT logic incurs at most a 2X overhead in simulation time in this system           | 57 |

| Table 6.1. | Simulation times in milliseconds associated with the three presented cases for I <sup>2</sup> C, and for a single trace. GLIFT imposes a small overhead in the simulation time for these test cases | 84 |

| Table 6.2. | Simulation times in seconds for AES running with different encryption keys, with and without GLIFT tracking logic. In general, simulating a design with GLIFT logic causes large slow-downs         | 92 |

#### **ACKNOWLEDGEMENTS**

I would first like to give the warmest aloha to everyone back on my home island of Kauai who believed in me. All the family, friends, and high-school teachers who gave motivation and encouragement in an environment which rarely promotes academics.

Although perhaps cliché, I want to acknowledge my advisor Dr. Ryan Kastner who allowed me to do research as a Sophomore undergraduate and really helped spark my interest. I would have never pursued a doctorate degree without his encouragement and support. I also want to thank Dr. Timothy Sherwood who also provided me with some of my intial research advising also as an undergraduate. Dr. Sherwood's former student, Dr. Mohit Tiwari helped me tremendously as both an undergraduate and junior graduate student. I want to acknowledge that his assistance was invaluable in developing the fundamentals presented in this dissertation.

I would also like to thank my committee members. Dr. Ali Irturk provided some crucial assistance in the early development of the work in this dissertation while I was a junior graduate student. Dr. Andrew Kahng provided me with valuable feedback about how this work applies to the hardware design space and how to effectively convey these key points. Dr. Stefan Savage motivated me to focus more attention on security beyond what my background already had. His questions and feedback made me a stronger security researcher and motivated me to think about the practical security applications of research.

None of this would have been possible without my many collaborators. I would like to thank Dr. Cynthia Irvine, Dr. Ted Huffmire, and Dr.Timothy Levin from the Naval Post Graduate School (NPS) who consitently provided me with valuable feedback and constructive criticisms about my research. I would also like to thank Dr. Irvine for the many contributions as a valuable reference. My colleagues at UC Santa Barbara also deserve the greatest thanks and acknowledgement. Dr. Xun Li, Dr. Jonathan Valamehr,

Dr. Mohit Tiwari, Dr. Fredrick Chong, Dr. Bita Mazloom, Dr. Timothy Sherwood, and Dr. Ben Hardekopf have all contributed substantially to my broader research interests and completion of my doctorate.

My many funding sources have been key to my success in my degree. I want to acknowledge the National Science Foundation for their graduate research fellowship and my participation in the Innovation Corps Program where I learned invaluable knowledge about the hardware security industry. I would also like to thank the generous women of the Achievement Rewards for College Scientists (ARCS) scholarship. Their generosity helped relieve much of the financial stress that many graduate students experience.

On a more personal note, I want to thank Dr. Ravi Chugh for the many stress relieving and glorious golf rounds and competitive late night Mario Kart. Dr. Zach Tatlock for answering my questions about programming languages, compilers, and formal verification. Wei Hu for his hard work and helpful support during our close collaboration when he was visiting UCSD between 2010-2012. Our relationship on these projects helped develop the technology in a short amount of time. Last, but certainly not least, Dr. Sarah Meiklejohn for her help with cryptography and mathematical models.

Majority of the work herein appears in both academic journals and conferences. Chapter 3, in small part, is a reprint of the material as it appears in the Design Automation Conference 2010. Oberg, Jason; Hu, Wei; Irturk, Ali; Tiwari, Mohit; Sherwood, Timothy; Kastner, Ryan; The dissertation author was the primary investigator and author of this paper.

Chapter 4, in full, is a reprint of the material as it appears in the Design Automation Conference 2011. Oberg, Jason; Hu, Wei; Irturk, Ali; Tiwari, Mohit; Sherwood, Timothy; Kastner, Ryan; This dissertation author was the primary investigator and author of this paper.

Chapter 5, in full, is a reprint of the material as it appears in the IEEE journal on

Design and Test of Computers 2013. Oberg, Jason; Sherwood, Timothy; Kastner, Ryan. The dissertation author was the primary investigator and author of this paper.

Chapter 6, in full, is a reprint of the material as it appears in the conference on Design Automation and Test in Europe 2013 and also in submission at the IEEE Transactions on Computer-aided Design of Integrated Circuits and Systems 2014. Oberg, Jason; Meiklejohn, Sarah; Sherwood, Timothy; Kastner, Ryan. The dissertation author was the primary investigator and author on both of these papers.

#### **VITA**

| 2009      | Bachelor of Science, Computer Engineering<br>University of California, Santa Barbara                   |

|-----------|--------------------------------------------------------------------------------------------------------|

| 2009      | Teaching Assistant, Department of Computer Science and Engineering University of California, San Diego |

| 2010      | Systems Engineering Intern<br>Qualcomm, San Diego CA                                                   |

| 2011      | Research Intern<br>Microsoft Research, Redmond WA                                                      |

| 2009–2014 | Research Assistant, Department of Computer Science and Engineering University of California, San Diego |

| 2012      | Master of Science, Computer Science and Engineering<br>University of California, San Diego             |

| 2014      | Doctor of Philosophy, Computer Science<br>University of California, San Diego                          |

#### **PUBLICATIONS**

Sapper: A Language for Hardware-Level Security Policy Enforcement. Xun Li, Vineeth Kashyap, Jason Oberg, Mohit Tiwari, Vasanth Rajarathinam, Ryan Kastner, Timothy Sherwood, Ben Hardekopf and Frederic T. Chong, International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2014)

SurfNoC: A Low Latency and Provably Non-Interfering approach to Secure Networks-On-Chip. Hassan M. G. Wassel, Ying Gao, Jason K. Oberg, Ted Huffmire, Ryan Kastner, Frederic T. Chong, Timothy Sherwood, International Symposium on Computer Architecture (ISCA 2013)

Expanding Gate Level Information Flow Tracking for Multi-level Security. Wei Hu, Jason Oberg, Janet Barrientos, Dejun Mu, and Ryan Kastner, IEEE Embedded System Letters, vol. 5, no. 2, May 2013

Eliminating Timing Information Flows in a Mix-trusted System-on-Chip. Jason Oberg, Timothy Sherwood, and Ryan Kastner, IEEE Design and Test of Computers, vol. 30, no. 2, March/April 2013

A Software-based Dynamic-warp Scheduling Approach for Load-Balancing the Viola-Jones Face Detection Algorithm on GPUs. Tan Nguyen, Daniel Hefenbrock, Jason Oberg, Ryan Kastner, and Scott Baden, **Journal of Parallel and Distributed Computing, January 2013**

Sapper: A Language for Provable Hardware Policy Enforcement. Xun Li, Vineeth Kashyap, Jason Oberg, Mohit Tiwari, Vasanth Rajarathinam, Ryan Kastner, Timothy Sherwood, Ben Hardekopf and Frederic T. Chong, Workshop on Programming Languages and Analysis for Security (PLAS 2013).

A Practical Testing Framework for Isolating Hardware Timing Channels. Jason Oberg, Sarah Meiklejohn, Timothy Sherwood, and Ryan Kastner, **The conference on Design Automation and Test in Europe (DATE 2013)**

On the Complexity of Gate Level Information Flow Tracking Logic. Wei Hu, Jason Oberg, Ali Irturk, Mohit Tiwari, Timothy Sherwood, Dejun Mu, and Ryan Kastner, IEEE Transactions on Information Forensics and Security (TIFS), vol. 7, no. 3, June 2012

Simultaneous Information Flow Security and Circuit Redundancy in Boolean Gates. Wei Hu, Jason Oberg, Dejun Mu, and Ryan Kastner, **The international conference on Computer-Aided Design (ICCAD 2012)**

Random Decision Tree Body Part Recognition Using FPGAs. Jason Oberg, Ken Eguro, Ray Bittner, and Alessandro Forin, The International conference on Field Programmable Logic and Applications (FPL 2012)

Trimmed VLIW: Moving Application Specific Processors Towards High Level Synthesis. Janarbek Matai, Jason Oberg, Ali Irturk, Taemin Kim, and Ryan Kastner, The Electronic System Level Synthesis Conference (ESLsyn 2012)

Theoretical Fundamentals of Gate Level Information Flow Tracking. Wei Hu, Jason Oberg, Ali Irturk, Mohit Tiwari, Timothy Sherwood, Dejun Mu, and Ryan Kastner, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 30, issue 8, August 2011

Simulate and Eliminate: A Top-to-Bottom Design Methodology for Automatic Generation of Application Specific Architectures. Ali Irturk, Janarbek Matai, Jason Oberg, Jeffrey Su, and Ryan Kastner, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 30, issue 8, August 2011

Enforcing Information Flow Guarantees in Reconfigurable Systems with Mix-trusted IP.

Ryan Kastner, Jason Oberg, Wei Hu, and Ali Irturk, The conference on Engineering of Reconfigurable Systems and Algorithms (ERSA 2011), invited paper

An Improved Encoding Technique for Gate Level Information Flow Tracking. Wei Hu, Jason Oberg, Ali Irturk, Mohit Tiwari, Timothy Sherwood, Dejun Mu, and Ryan Kastner, The International Workshop on Logic and Synthesis (IWLS 2011)

Crafting a Usable Microkernel, Processor, and I/O System with Strict and Provable Information Flow Security. Mohit Tiwari, Jason Oberg, Xun Li, Jonathan K Valamehr, Timothy Levin, Ben Hardekopf, Ryan Kastner, Frederic T. Chong, and Timothy Sherwood, In Proceedings of the International Symposium on Computer Architecture (ISCA 2011)

*Information Flow Isolation in I2C and USB.* Jason Oberg, Wei Hu, Ali Irturk, Mohit Tiwari, Timothy Sherwood, and Ryan Kastner, **In Proceedings of the Design Automation Conference (DAC 2011)**

Caisson: A Hardware Description Language for Secure Information Flow. Xun Li, Mohit Tiwari, Jason Oberg, Frederic T. Chong, Tim Sherwood, and Ben Hardekopf, In Proceedings of the conference on Programming Language Design and Implementation (PLDI 2011)

Minimal Multi-Threading: Finding and Removing Redundant Instructions in Multi-Threaded Processors. Guoping Long, Diana Franklin, Susmit Biswas, Pablo Ortiz, Jason Oberg, Dongrui Fan, and Frederic T. Chong, In Proceedings of the International Symposium on Microarchitecture (MICRO 2010).

Accelerating Viola-Jones Face Detection to FPGA-Level using GPUs. Daniel Hefenbrock, Jason Oberg, Nhat Tan Nguyen Thanh, Ryan Kastner, and Scott B. Baden, In Proceedings of the conference on Field-Programmable Custom Computing Machines (FCCM 2010).

Theoretical Analysis of Gate Level Information Flow Tracking. Jason Oberg, Wei Hu, Ali Irturk, Mohit Tiwari, Timothy Sherwood, and Ryan Kastner, In the Proceedings of the Design Automation Conference (DAC 2010).

FPGA-Based Face Detection System Using Haar Classifiers. Jung Uk Cho, Shahnam Mirzaei, Jason Oberg, and Ryan Kastner, In Proceedings of the International Symposium on Field Programmable Gate Arrays (FPGA 2009).

#### ABSTRACT OF THE DISSERTATION

#### **Testing Hardware Security Properties and Identifying Timing Channels**

by

Jason Kaipo Oberg

Doctor of Philosophy in Computer Science

University of California, San Diego, 2014

Professor Ryan Kastner, Co-Chair Professor Timothy Sherwood, Co-Chair

Computers are being placed in charge of the systems and devices we trust with our safety and security. These embedded systems control our automobiles, commercial airlines, medical devices, mobile phones, and many other aspects that we hope will behave in a secure and reliable manner. In addition, the hardware in these systems are becoming increasingly complex; making security testing and evaluation a very difficult problem. Unfortunately, we have already seen many attacks performed on many of these systems including automobiles and medical devices. Many of these issues could have been prevented had there been better methods for security assessment. Specifically,

hardware and embedded system designers are lacking the tools and methods for testing various security properties of their designs.

Recently, a method known as gate-level information flow tracking (GLIFT) was introduced to dynamically monitor information flows in hardware for security. This dissertaion shows that this same technique can be very effectively applied statically to hardware designs to systematically test various different hardware security properties (e.g. to ensure that secret encryption keys are not leaking). Even further, this thesis demonstrates that GLIFT can effectively capture timing-channels (where information leaks in the amount of *time* a computation takes). These timing channels have been exploited in many past works to extract secret keys from different stateful hardware resources such as caches and branch predictors. This thesis presents some very fundamental background of GLIFT, shows how it can be used statically using several application examples, and formalizes how it can be used to detect timing channels. These contributions ultimately provide a method to do hardware security testing and verification for our future computing systems.

# Chapter 1

# Introduction

## 1.1 Overview

Computing systems are at the heart of many of the systems we rely on for our personal safety and security. Automobiles, medical devices, commercial airlines, and mobile phones are becoming inreasingly complicated and we trust that their systems will not behave unexpectedly or leak our secret information. With exploits being exposed in many of these systems including pace-makers [41], insulin pumps [75] and automobiles [57], hardware security is becoming sought after to provide a root-of-trust. By building security in hardware, hardware specific vulnerabilites (which are very difficult to mitigate by software alone) are accounted for as well.

Security mechanisms themselves have existed in hardware for quite some time. They have existed in the form of security rings to limit the resources that processes can access and help enforce isolation between different domains (such as kernel and user space) [35, 95]. Hardware mechanisms have also long existed in the form of privileged instructions where a subset of instructions can only be executed by higher security processes (such as the kernel) [88, 37]. These instructions typically restrict operations such as I/O access and accessing protected memory regions from less privileged processes. Hardware implementations of crypto systems have also been used for quite some time

both in the form of data encryption [96, 106] and hash functions [110, 29]. In all cases, one of the primary reasons these features are designed in hardware is to increase system performance by taking some of the security burden of the software and boosting it with highly parallel and efficient implementations.

As we are seeing hardware becoming more complex, the demand for these hardware security mechanisms is increasing. The hardware itself is becoming an attack vector with fixes that have to be added in the hardware itself. As a result, efforts to combat the need for new hardware security mechanisms has seen a lot of momentum in the recent years. For example, Intel is focusing a substantial amount of attention on security with the continuous growth of its Security Center of Excellence (SeCoE). One of their most recent projects is focused on providing secure enclaves [68] for more secure execution. Specifically, they provide hardware mechanisms for isolation by allowing untrusted applications to execute in special "enclaves" that they build into their instruction set architecture (ISA). In addition, we are seeing an increasing number of hardware security modules (HSMs) being developed by both large and small companies. One example is the company ESCRYPT, which was recently acquired by Bosch [32], who's primary product is HSMs for next generation automobiles. As the hardware itself continues to rapidly progress towards mechanisms for better security, the methods for evaluating the security of these designs is unfortunately far behind. Although the methods for testing and verfication for correct functionality are quite rich in the electronic design and automation (EDA) space, the methods specific for security are extremely limited with most solutions being centered around "best-practices" and security auditing teams.

The complexity of modern hardware makes the intricate security properties that need to be tested and verified difficult. For example, a common property that often needs to be guaranteed in hardware is non-interference [38], where certain parts of the system should never interfere with other parts. An example where non-interference is

important is the Boeing 787 aircraft which has connectivity between the user and flight control networks [33]. In this type of scenario ensuring that there are no unintended information flows between the two networks is critical for the correct operation of the aircraft. This property of non-interference is also what Intel would like to demonstrate with their enclaves, by ensuring that you can have isolation between processes in the hardware. With the further development of intricate system-on-chips interacting via complex protocols, guaranteeing non-interference is a hard problem since information can flow through difficult to detect side channels.

A side-channel is defined as an entity which leaks information but was not intended for communication. The two most common side channels found in hardware are from timing (the data-dependent latency of a computation) and power (the datadependent power consumed during a computation). In this work we address only logical side-channels (timing), physical ones (power) are out of the scope of this work. As an example, in order to show that two devices on a bus are non-intefering, it is required that the devices not intefere directly (i.e., by corrupt transmitted data) or through timing (i.e., by delays in response time). At first glance, these timing variations might seem benign, but these side-channels have been recently exploited by many to extract secret encryption keys from miss/hit delays in processor caches [10, 18, 86, 40]. These attacks rely on a exploiting information leaking through a timing channel, where an attacker is able to deduce information by simply measuring execution time. Since modern hardware is now increasingly coupled with non-determinism and hidden state, methods for detecting and even reasoning about these types of information leaks is an increasingly complex problem. Recently, some work that performs information flow tracking at the level of logic gates started getting traction as a potential way for detecting these timing channels.

Information flow tracking, in general, is a way of label information (e.g. label a key as *secret*) and then tracking where this key "flows". It is a powerful mechanism

for detecting a potential security issue so that the system can take preventative actions. Information flow tracking has seen lots of attention at many levels of the computing hierarchy. It has been used in high-level languages [94, 89, 42, 16] and compilers [60, 112], binary analysis tools [113, 8, 25, 34], operating systems [114, 58, 31], and in many hardware assisted techniques [28, 27, 98, 104, 105, 93, 23]. However, performing gate-level information flow tracking (GLIFT) was only very recently explored [103]. The properties found at the gate-level (the lowest digital abstraction), specifically using GLIFT, provide a powerful mechanism for testing and proving the absence of harmful information flows in a hardware design; including those from timing channels.

GLIFT associates a label (for a 2-level security lattice, this is a single-bit) with information and then tracks this bit as it flows through boolean gates. In the past, GLIFT has been used to build a non-interfering processor [101], analyze the USB and I2C bus protocols [78], build larger systems with I/O and a microkernel [102], and analyze the security of system-on-chips [80]. In many of these applications, GLIFT was used to show non-interference. However, the specifics of how GLIFT can be used to detect and eliminate timing channels has not been thoroughly explored. This thesis demonstrates how gate-level information flow tracking (GLIFT) can be used as a static hardware security testing technique and to identify hardware timing channels. The approach taken is to first understand how information flows at the gate level and extend this understanding to make it possible to test and debug larger hardware security issues at a larger scale. It explores how GLIFT can be used on real designs and also presents a formal model for using GLIFT to detect timing channels. Specifically, This thesis is the first to formalize timing channels in hardware and demonstrate how to separate out these timing flows from other functional ones. To assist with reading this thesis, a detailed organization of each chapter are described next.

## 1.2 Thesis Outline

In this section, I give a brief description of each chapter in this this thesis, starting with some background and related work.

### 1.2.1 Background and Related Work

Before I present details of how I have used gate level information flow tracking to identify and eliminate timing channels, I will discuss some crucial background information. I will first present a discussion of the cost associated with security in Chapter 2.1. Next, I will discuss the necessary background and related work on information flow tracking in Chapter 2.2 and how our gate-level analysis can be used as a static testing technique. Lastly, I will provide a detailed discussion of timing channels and how they have been exploited in the past in Chapter 2.3. Following this section, I will discuss the details some theoretical fundamentals of GLIFT.

## 1.2.2 Deriving Equations for GLIFT Logic

As a first step, this thesis presents some theortical basics for GLIFT. This thesis expands on previous work by providing a theoretical foundation for generating and understanding Shadow (or GLIFT) Logic. Specifically, it 1) precisely defines taint and GLIFT logic; 2) derives logic equations for some gate-level primitives; and 3) discusses the overheads related to the GLIFT logic in terms of the number of minterms and area using several IWLS and ISCAS benchmarks. These three essential points provide a necessary theoretical foundation for GLIFT and are necessary for understanding the other concepts and analyses presented in this thesis. I address these points in detail in Chapter 3.

## 1.2.3 Analyzing Timing Channels in Bus Protocols Using GLIFT

Beyond the formalisms of GLIFT, this thesis demonstrates how this technique can be used to analyze information flows in some common bus protocols. Since GLIFT provides a solution for monitoring information flows in hardware and targets boolean gates it is general enough to be applied to any digital hardware. Furthermore it can precisely detect all explicit information flows as well as timing channels since it monitors the change of every bit cycle-by- cycle. As a result, this thesis will show that it is very effective for proving information flow policies about common bus protocols such as the Inter-Integrated Circuit protocol (I2C) and the Universal Serial Bus (USB). This thesis discusses how GLIFT can be used to analyze and remove unintended information flows in bus protocols using I2C and USB as examples but presents a general framework for doing so that fits in seamlessly into existing hardware design flows. The general testing framework is presented in Chapter 2 and how this framework can be applied to I2C and USB is discussed in Chapter 4. Although this thesis demonstrates a necessary first step in how GLIFT can be used to test for timing information flows in common bus protocols, it is not clear how it can be applied to larger hardware systems.

## 1.2.4 Testing Timing Channels in a System-on-Chip

Chapter 5 presents an explanation and scenario in which our GLIFT testing method can be used the test security properties of larger systems.

Specifically, Chapter 5 presents an analysis using two MIPS processors sharing a cryptographic core (the advanced encryption standard) over the WISHBONE [84] system-on-chip (SoC) bus. This chapter demonstrates how GLIFT can be used to test for timing-based information leaks in this larger SoC. This chapter describes the methodology of how it is used and the timing-based integrity properties that need to be upheld. This usage of GLIFT is the first of its kind to demonstrate how it can be used to abstract

away certain details of the design (the processors) and analyze simply the interconnect (the WISBHONE architecture) in order to demonstrate timing isolation between two processors even though they are sharing a common resource.

## 1.2.5 Formal Analysis of Timing Channels and GLIFT

An additional contribution of this thesis is a formalization of how GLIFT detects timing channels. As briefly mentioned, information leakage through time has been exploited by attackers to extract secret encryption keys in both branch predictors [11] and processor caches [86, 18, 10]. GLIFT has shown to be promising in detecting these timing channels but this claim has not been formally explored in prior work. The goal of Chapter 6 is to make this claim more apparent. We present a framework for identifying timing channels and separate them from other types of information flows.

To show the practicality of our framework, we explore in Chapters 6.5 and 6.6 two common shared resources which are at the heart of interference in modern computing systems: the shared bus and CPU cache. The shared bus in modern systems has been the source of the so called *bus-contention* channel [44] in which information can be covertly communicated through the traffic on a global bus. Previous work has explored how to identify information flows in global buses using GLIFT [78] but has fallen short of classifying these flows as functional or timing. Beyond the bus, we examine in Chapter 6.6 the CPU cache; as previously mentioned, the cache is a common vulnerability in modern systems, as it is typically susceptible to leaking secret information through timing channels. For both examples, we do not make claims about complete information security, but rather increased confidence by identifying the presence of functional information and separating it from timing channels. Before we present our formal model and its use, we outline some essential preliminary definitions in Chapter 6.2 and formal definitions of GLIFT and information flow tracking using GLIFT in Chapter 6.3.

# Chapter 2

# **Background and Related Work**

## 2.1 The Cost of Embedded Security

Hardware and embedded systems are seeing an increasing number of exploits that are costing companies millions of dollars [100]. This is primarily due to the lack of, systematic, formal methods for identifying hardware-specific security vulnerabilities (including timing channels) are non-existent. With the increasing complexity of our hardware, these vulnerabilities are becoming increasingly more of an issue.

For example, Intel states about the core i7-900 that "in some rare cases improper TLB invalidation may result in unpredictable system behavior and can hang your OS or result with incorrect data" [50]. While these bugs may not occur in common place execution, a motivated attacker may find unique ways to exploit these undocumented behaviors to leak information and/or circumvent policy. Furthermore, such "specification updates" are not at all uncommon. The same core i7-900 documentation states 152 separate issues, including 6 issues that cause "unpredictable behavior" and 11 capable of spawning "unexpected results". Assuming conservatively that this represents *all* of the issues, and that the issues are spread evenly over the 1 year lifetime during which the core is produced, this is still nearly 2 issues per week. Systematic ways for detecting these potential security vulnerabilities are necessary for more reliable and secure hardware.

Another example of a bug in an embedded system costing millions of dollars is in the Toyota unintended acceleration issue [100]. In this example, the accelator in some Camry's activated against user control and they were unable to control their automobile. Although these were unlikely to be caused by malicious intent, the security and saftely assessment of these systems was lacking. For example, the "embedded systems experts who reviewed Toyota's electronic throttle source code testified that they found it defective. They said it contains bugs – including some that can cause unintended acceleration." [100]. Toyota was forced to pay \$1.5M to the driver of the car and \$1.5M to a victim's family in a resulting crash. The jury in this case commented that "Toyota acted with 'reckless disregard' for the rights of others." This type of mishap not only costed Toyota \$3M to the plaintiffs in this case, but unmeasurable amounts in terms of PR and related market effects. Toyota may have been able to circumvent some of these issues if they had more systematic security testing to ensure that these sort of safety critical systems would not malfunction inadvertently.

Some methods for security assessment do exist but are typically done by mandated security standards set forth by various standards bodies. Some companies have their own internal security auditing teams, such as Intel's Security Center of Excellence (SeCoE), but many others follow more gonvernment mandated standards. These standards provide a safety assessment mechanisms to help remedy some of these issues in the high-assurance markets. For example, there is the FIPS 140-2 standard for cryptographic devices [81] put on by the National Institute of Standards and Technology (NIST) to provide a standard assessment mechanism for designing cryptographic modules. Much emphasis is put on tamper-resistance and TEMPEST attacks (similar to side-channel attacks) and a level from 1 to 4 is assigned based on how well the module is tested. Other standards exist to measure how well systems have been evaluated. For example, the Common Criteria [1] standard specifies a set of rules for testing and evaluation. Specifically, an

Evaluation Assurance Level (EAL) is awarded to systems based on how thoroughly they have been evaluated (assigned a number from 1 to 7). Not surprisingly, achieving a high-assurance level is not only time consuming but extremely expensive. Such assurance often requires detailed verification including strict theorem proving and third party analysis [1]. This complicated process not only takes a tremendous amount of time estimated at 10 years [97] but also costs thousands of dollars per line of code [6]. Reducing this overhead is needed to keep these operation critical systems up-to-date with current technology at a reasonable cost. Tools for making the security assessment of hardware is greatly needed to both reduce this evaluation cost and make security evaluation a primary constraint in the hardware design flow.

A powerful new technology presented in past work [103] and more thoroughly evaluated in this thesis, called gate-level information flow tracking (GLIFT), provides a mechanism for helping with hardware security assessment. It provides a method for testing various security properties about the underlying hardware in a similar flavor to functional testing and verification. This thesis is primarily focused on how GLIFT can be used to specifically detect timing channels. However, in the rest of this chapter, I will first disuss some necessary background about information flow tracking, GLIFT, and timing channels.

## 2.2 Information Flow Tracking and GLIFT

A large amount of previous work has been done in the area of information flow security for complete systems. Numerous works have been done on information flow tracking specifically in hardware because monitoring information flows at this level allows for unintended flows to be identified without significantly affecting system performance. This section discusses the previous research in information flow security for complete systems and specifically focuses on GLIFT since it is the primary technique we used in

previous and continuing analyses.

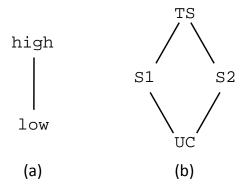

Information flow security focuses on monitoring the movement of data among different trust levels. Traditionally information flow security is guaranteed by ensuring that a particular information flow policy, such as integrity or confidentiality, is upheld. These policies can be modeled using a lattice  $(L, \sqsubseteq)$  [30], where L is the set of security labels and  $\sqsubseteq$  is a partial order between these security labels that specifies the permittable information flows. For example, consider the example lattices shown in Figure 2.1. Figure 2.1 (a) shows a typical binary security lattice. For such a binary lattice, the term *taint* is often used for the higher label on the lattice. For integrity, untrusted information is considered *tainted* in order to monitor if this taint violates a trusted (untainted) location. For confidentiality, taint is defined differently. The policy taints secret information to verify whether this leaks to an unclassified domain. Figure 2.1 (b) shows a security lattice with multiple trust levels. In both cases, integrity states that information may flow down in the lattice, but not up ("no write-up, no read-down" [19]). Confidentiality states that information can flow up the lattice but not down ("no read-up, no write-down" [17]). For simplicity, our analysis focuses on the binary lattice low  $\sqsubseteq$  high in Figure 2.1 (a).

**Figure 2.1.** Examples of different security lattices. (a) is a typical binary security lattice showing  $low \sqsubseteq high$ . (b) is a more complicated lattice with multiple labels. Here TS is top-secret, S1 and S2 are two security levels which are less secure than TS but more private than UC (unclassified).

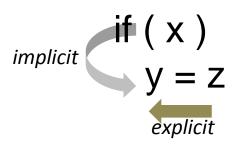

To be concrete, consider the code snippet shown in Figure 2.2 and let L(w) be the

label assigned to some variable w. First, to understand explicit information flows and how they can be tracked, consider the assignment shown y = z. For integrity, using the lattice low  $\sqsubseteq$  high, this code is secure if  $L(y) \sqsubseteq L(z)$ . In other words, this code is information flow secure only if the label assigned to z allows for information to flow into y without violating the integrity of y. Integrity in this situation is not violated as long as both y and z have the same label or y is low and z is high. Confidentiality does essentially the opposite as integrity. Using the binary lattice, the assignment is information flow secure if  $L(z) \subseteq L(y)$ . Meaning that information can only flow into y from z if y is at higher or equal security level to that of z. Implicit flows in this example follow a similar strategy except that they flow information indirectly to the variable. This particular code shows an implicit channel in the form of a branch. Here x leaks information to y because, depending on x, y will be assigned the value of z. For both confidentiality and integrity, implicit flows need to also be eliminated. In this particular example, to enforce integrity, the labels must adhere to  $L(y) \subseteq L(x)$  in a similar manner as the explicit flow. For confidentiality, a similar relation holds for the explicit flow, namely  $L(x) \subseteq L(y)$ . Note that if integrity or confidentiality is to hold for the entire code, both the information flow constraints for the explicit and implicit flows must be enforced. Using this common model of information flow security, many implementations have been made to enforce this at all layers of the system design.

**Figure 2.2.** Simple code snippet showing explicit information flow from z to y and implicit information flow from x to y.

The most common techniques for information flow security are implemented in programming languages using type based systems and in operating systems. Sabelfield and Myers [94] present a survey on the different programming language based techniques. Most work has been done in static compile based techniques which build off of the typing system of a language in order to enforce information flow security. These methods have shown to be effective and can even eliminate implicit channels due to conditional branches in execution. Jif [74, 72] is a good example of such a type based system. Similar programming language based techniques have been applied to JavaScript to help alleviate security issues such as history sniffing or executing malicious code [51, 24]. Flume [58] has been shown to enforce information flow security using abstractions for operating system primitives such as processes, pipes, and the file system. It works by providing a user-level reference monitor which allows for decentralized information flow control (DIFC) [73]. Some other operating system DIFC mechanisms [31, 114] perform similar techniques but are incorporated into an entirely new operating system. These schemes are often effective but are forced to abstract away the potential implicit flows that occur in hardware. Further, these schemes force the designer to comply with a new typing system (in programming language techniques) or reduce the overall system performance (in operating system abstractions).

To maintain system performance, information flow tracking has been proposed in hardware. The most common hardware information flow tracking strategies focus on the Instruction Set Architecture (ISA) and microarchitecture. One such technique called Dynamic information flow tracking (DIFT), proposed by Suh et al. [98], tags information from untrusted channels such as network interfaces and tracks it throughout a processor. They label certain inputs to the processor as "spurious" (tainted) and check whether or not this input causes a branch to potentially untrusted code. This technique has been shown to successfully prevent buffer-overflow [26] and format string attacks [76]. Raksha [28]

is a DIFT style processor that allows the security policies to be reconfigured. Minos [27] uses information flow tracking to dynamically monitor the propagation of integrity bits to ensure that potentially harmful branches in execution are prevented in a manner similar to Suh et al. [98]. RIFLE [104] is an information flow secure system which uses binary re-writing. Since security annotations are done on the binary itself, applications can be executed on their system without requiring additional security type annotations to programs.

These previous techniques are effective at ensuring that potentially harmful branches in control flow are prevented or guaranteeing the integrity of critical memory regions. However, these methods target a higher level of abstraction and cannot be used to monitor the information flows in general digital hardware. For this reason, these methods also fail to detect hardware specific side channels in the form of timing. GLIFT provides a solution for tracking information flows, including those through timing channels, in general digital hardware. GLIFT works by tracking each individual bit in a system as they propagate through Boolean gates. This is done using an additional tag bit commonly referred to as *taint* and tracking logic which specifies how taint propagates. Information is said to flow through a logic gate if particular *tainted* inputs have a chance to *affect* the output.

Taint is a label associated with each data bit in the system which indicates whether or not this particular data bit should be tracked. If integrity is a concern, untrusted information is tainted to ensure that this tainted information does not flow to a trusted location. In the case of confidentiality, secret information is tainted to monitor whether it leaks to a public domain. Taint is propagated whenever a particular tainted data bit can affect the output. In other words, if the output of a function is dependent on changes to tainted inputs, then the output is marked as tainted.

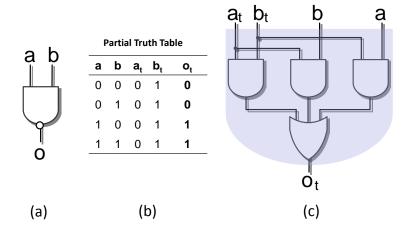

For example, consider a simple 2-input NAND gate as seen in Figure 2.3 (a) and

**Figure 2.3.** (a) A two-input NAND gate. (b) Truth table of two-input NAND gate with taint information (not all the combinations are shown). (c) The corresponding tracking logic of two-input NAND gate is  $ab_t + ba_t + a_tb_t$ . Every change at the input of the gate is precisely tracked at the output.

its corresponding tracking logic as shown in Figure 2.3 (c). For a NAND gate, only particular input changes will result in a change at the output. Specifically, consider the case in which a=0 and b=1. Here changing the value of b will cause no change at o since a=0, meaning that there is no information flowing from b to o. If b were to be tainted ( $b_t=1$ ) and a untainted ( $a_t=0$ ) in this case, o would be untainted ( $o_t=0$ ) since the tainted input does not affect the output. A subset of all such combinations can be seen in Figure 2.3 (b). Using the full truth table, a function can be derived for all similar input combinations into a tracking logic function as shown in Figure 2.3 (c). Since NAND is functionally complete, the tracking logic for any digital circuit can be derived by constructively generating the tracking logic for each gate. In other words, given a circuit represented as NAND gates, the circuit can have complete information flow tracking by interconnecting the tracking logic for each individual NAND gate. This results in a design that precisely tracks the information flow of each individual bit. As mentioned, GLIFT is a useful tool for analyzing any digital hardware because it exposes all information flows explicitly.

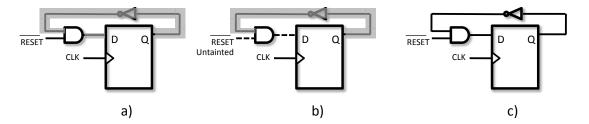

All prior work in the area has assumed that if a function is computed the output should be tagged as tainted if *any* of the inputs are tainted. This assumption is certainly sound (i.e., it should never lead to a case wherein the output which should be tainted is marked as untainted) but it is overly conservative in many important cases, in particular if something is known about the inputs at runtime. To understand the importance of precisely tracking information flow, consider a simple 1 bit counter that increments (or toggles in this case) every cycle or gets cleared back to zero from a reset. If a counter is implemented as depicted in Figure 2.4 a), and uses a conservative information flow tracking scheme as mentioned, there is no way for the counter to ever return to an untainted state once it has been marked tainted since the value of the counter will be tainted. Yet it is obvious that the system should return to an untainted state on an untainted reset. However, if GLIFT is used as described, the counter would in fact reset back to an untainted state as seen in Figure 2.4 b) and c). This is because GLIFT considers the values of the inputs to determine if it is possible for information to flow from the inputs to the outputs.

**Figure 2.4.** A 1-bit counter with reset. Our tracking logic is more precise and recognizes that an untainted reset guarantees an untainted 0 in the counter value. The gray area indicates the value here is tainted. a) Tainted counter. b) An untainted reset puts the counter back to an untainted state. c) Untainted counter

Now that the details behind how GLIFT works has been presented, it helps to see how it can be used in practice for testing for information flows.

### 2.2.1 Using GLIFT as a Static Testing Technique

Our GLIFT analysis can be accomplished *statically* (at system design time) meaning that additional gates due to our analysis logic are never actually fabricated and are used only at design time. Most of our customers have expressed interest in using our gate-level technology for static analysis so we focus on how our technology can be used in this manner.

In a static scenario, the GLIFT analysis is used to test or verify if the system complies with designer supplied security policies. This is done completely at design time, i.e., there is no need to physically instantiate the analysis logic after testing or verification is complete. In the past, we have successfully employed this in both testing [78, 53] and verification [102] using GLIFT.

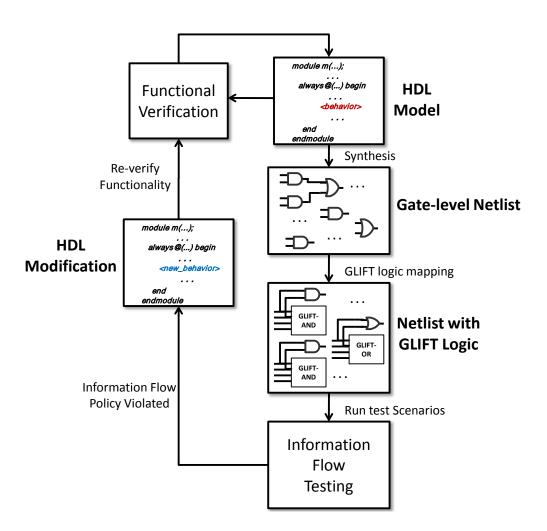

Figure 2.5 provides a possible design flow for static analysis. The system is described in a hardware description language (HDL) such as *VHDL* or *Verilog* [49]. Once the digital circuit under design has passed functional verification, it is synthesized into a gate-level netlist using standard hardware synthesis tools such as Synopsys Design Compiler. Next, each gate in the netlist is augmented with the appropriate analysis logic. There are many methods for generating this tracking logic for a given circuit all with varying computational complexity and trade-offs with preciseness. In other words, GLIFT can be imprecise since sometimes it will conservatively say there is an information flow when there is in fact not one. We have proven that generating precise GLIFT logic for a general function is *NP*-complete in past work. This thesis will not explore these topics further, but the interested reader should see our work on preciseness [46] and on the complexity of the various different GLIFT logic generation methods [47].

The most common method used to generate GLIFT logic is a constructive one, which creates GLIFT logic for each logic gate in the gate-level library individually and

**Figure 2.5.** Using gate level analysis logic for static assessment of security properties in digital system design.

then appends these new "GLIFT" gates together. In other words, every gate in the system has logic attached to it individually in a linear fashion. This design equipped with GLIFT logic is now capable of being analyzed for unintended information flows. At this stage, test vectors are run on the hardware to see if it violates the information flow policy. If the policy is violated, the description of the hardware is modified and once again undergoes functional verification and proceeds through the testing flow again. Making modifications to the hardware model is not obvious and generally requires a form of time-multiplexing to prove the absence of timing channels from the design. This has shown to be effective when analyzing processor cores and bus controllers as subsequent sections discuss in more detail.

Once the appropriate GLIFT logic is added for the design, testing and/or verification scenarios are run to check if the design potentially violates any pre-defined security policies (e.g. "does my secret key leak?"). If some policy is violated, the design is modified and re-verified until all properties of interest are pass. In the static testing or verification application scenario, the tester is responsible for specifying what properties to analyze. For example, the tester may wish to ensure that certain critical portions of the system are never affected by untrusted components or that a secret encryption key is never flowing to somewhere other than the ciphertext.

In our past work we have demonstrated the use of gate property analysis in secure hardware design as a static analysis technique. We slightly modified the I2C and USB protocols to eliminate timing channels and utilized the testing methodology to show that these new protocols adhered to strict timing behaviors [78]. This is important in many scenarios, e.g., to ensure that real-time systems do not miss their deadlines. Other recent work addresses trust issues in hardware designs that use mix-trusted IP cores from different vendors [53]. Here we use gate-level analysis to verify that there is no unintended interaction between modules that may violate security properties such as

non-interference. In [102], a static analysis technique is used to verify the concrete hardware implementation with partial software specification to be free of unintended information flows. The information flow properties of the entire design are statically verified using gate-level analysis. To present a better understanding of how this method can be used in practice, I will describe an example use case on an AES core.

#### 2.2.2 Example: Using GLIFT on AES

To understand how one might use this testing flow and how information flows at the gate-level, it is useful to think about concrete example. Let us consider a hardware encryption core. For the purposes of this discussion, I will use the advanced encryption standard (AES). I choose to use an encryption core as an example since they are very commonly built in hardware and their security is often at the core of the security of the entire system.

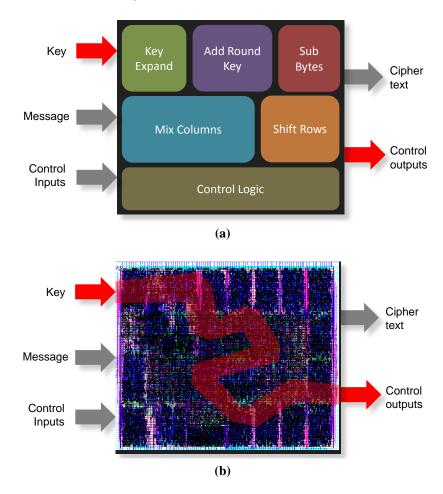

Figure 2.6a shows the overview of AES as a hardware encryption core. It is comprised of several different submodules which each perform a specific function such as *MixColumns*, *SubBytes*, etc. AES itself executes these different functions in many iterations (called rounds) using a portion of the expanded *Key* in each round to produce a ciphertext. AES itself has stood the test of time against cryptanalysis attacks and is accepted to be secure. In other words, the cryptographic community has accepted it to be mathematically infeasible to extract either the key or message from the ciphtertext. When this algorithm is built in hardware, however, there are various different control outputs that are required for ease of integration into the system. These outputs could be things such as a way for a designer to read out the encryption key when in a special debug mode or something as simple as saying when the ciphertext is ready.

In certain circumstances, flows from the secret key to these control outputs might be acceptable and in others could be disastrous to the security of the system. For example, it might be acceptable to read the key out only when in a special "debug" mode. In addition, it might be unacceptable for the key to flow to a "ready" control output since this could be a potentially exploitable timing channel (i.e. the key has the ability to affect the execution time of the core).

**Figure 2.6.** (a) An overview of the interface and internal modules of a hardware AES encryption block. (b) The layout for an AES block. Proving that the Key does not flow to a control output is non-trivial.

Unfortunately verifying a property like this is extremely non-trival. Figure 2.6b shows the layout of an implementation of AES. An intuitive way of figuring out whether or not the key flows to a control output becomes extremely difficult in the mess of thousands of gates. However, by using our gate-level technology, we can provide designers with

an easy tool to mark their key as "secret" and discover if it is actually ever leaking to an "unclassified" control output. In doing so, hardware designers can systematically evaluate the security of their design by enumerating the different properties they would like to check.

GLIFT in and of itself does not ensure that secret data does not spread across the whole machine, rather it is a static analysis technique that ensures that as secret data spreads across the machine it will always be properly detected. Tracking properties at the gate level at design time makes the most sense when coupled with the hardware and software designs that attempt to *enforce* that the desired properties hold.

## 2.3 Timing-Channel Attacks

Timing-channels are a form of side channel in which secret information leaks through the amount of time a computation takes to execute. Other forms of side channels include physical ones such as the amount of power a cryptograhic operation consumes [54, 66, 70, 71, 85], the amount of electromagnetic radiation it produces [13, 65], the sounds keys make on a computer keyboard [15], the difference in faulty behavior when a cryptographic hardware module ages [20, 21, 87], and even the minute sounds computers make (likely from the fluctuations in capacitors) when they perform a computation [36]. All of these side channels have been shown to leak secret encryption keys and other critical pieces of data. Although physical side channels are quite powerful in nature, this section focuses primarily on timing based side channels. A timing based channel when secret data affects how long a computation takes the execute and thus the secret information can be inferred from time. In addition, on the availability side, a timing-channel can be used by an attacker to provide variants of denial of service by affecting *when* a critical system component can respond. Timing-channels have seen a lot of attention in recent years with many demonstratable attacks performed on the underlying hardware. These

attacks typically exploit hardware specific features that are very frequently impossible to solve using software mechanisms without destroying system performance.

There have been many published confidentiality-based timing attacks that target cryptographic algorithms such as the advanced encryption standard (AES), the Rivest-Shamir-Adlemann (RSA) public-key crypto system, Diffie-Hellman, and others. These timing attacks exploit hardware performance mechanisms such as caches and branchpredictors. In the processor cache space many attacks of been performed in various fashions on data-caches [22, 10, 86, 18, 40] and even instruction caches in the work done by Aciicmez et al. [12, 9]. All of these cache-based attacks rely on the non-deterministic latencies of performing a memory read. For example, cryptographic algorithms will fill up the cache with data and often times the cache line in which data is mapped leaks some critical information. As been demonstrated in this past work, an attacker with the ability to measure time can extract complete encryption keys solely from the variations in time from caches. Even further, Acciicmez et al. also performed timing-based attacks on branch predictors [11] where they exploited the varying latencies of correctly and incorrectly predicting whether or not a program will take a branch. There has also been much recent research to help thwart these attacks by creating new cache designs, as done by Wang et al. [107, 108], and modifying the way in which attackers can measure time, as done by Martin et al. [67].

To give a simplified example of how a timing channel attack works, I will summarize a simplified version of the attack performed by Paul Kocher in his timing channel attack paper on RSA [55]. The Rivest-Shamir-Adleman (RSA) assymetric, public-key cryptographic system is one of the most widely used systems in the SSL/TLS standard for both symmetric key-exchange and digital-signatures. I will only briefly discuss the portions of the system that have been vulnerable to timing attacks so that the exploitability of this algorithm can be thoroughly understood. For details about the entire

algorithm, the reader should refer to the original RSA paper [92].

The security of RSA relies on the difficulting of computing discrete logarithms. Stated differently, data is encrypted and decrypted by performing modular exponentiation, which can be done efficiently. However, given a cipher text, it is computationally difficult to compute the inverse (discrete log) to extract the message or key. To be concrete, a message M is encrypted using a public key e and the ciphertext e0 is decrypted using a private key e1 as follows:

$$C \equiv M^e \pmod{n}$$

$$M \equiv C^d \pmod{n}$$

(2.1)

Where e, d, and n are derived during the key-generation process (not discussed here) using two large and distinct prime numbers. Given that an attacker has access to M, ciphertext C, public key e, and modulus n, it is accepted to be computationally infeasible to compute the discret logarithm  $\log_C(M) \pmod{n}$  to extract the secret key d.

Now, to perform modular exponentiation to take C to the d, one could naively perform:  $\underbrace{C \times C \times ... \times C}_{d}$ . This would be very inefficient since there are certain cases where a multiply is not necessary depending on the value of the exponent. To optimize this, a square-and-multiply algorithm is often used. One implementation of this algorithm can be seen in Algorithm 1.

As stated, this optimization is performed to reduce the number of multiplies the system needs to perform because they typically require more *time*. Since the decision to perform a multiply is made on the value of a key-bit, an attacker with the ability to measure the execution time can, with surprisingly high probability, extract the entire encryption key with a sufficient number of timing measurements (an interested reader

**Algorithm 1.** Basic algorithm for square-and-multiply to compute modular exponentiation. It computes  $C^d \pmod{n}$ .

```

R=1;

temp=C;

\mathbf{for}\ i=0\ \mathbf{to}\ |d|-1\ \mathbf{do}

\mathbf{if}\ \mathrm{bit}\ d[i]=1\ \mathbf{then}

R=R\cdot temp\ (\mathrm{mod}\ n)

\mathbf{end}\ \mathbf{if}

temp=temp^2\ (\mathrm{mod}\ n)

\mathbf{end}\ \mathbf{for}

\mathbf{return}\ R

```

should refer to Paul Kocher's paper [55] for specific details of the attack).

These timing-based attacks are not new and have been discussed early days of system literature (most notably by Wei Hu and other works related to the VAX Virtual Machine Monitor [52, 44, 111]). The most common solution proposed to solve this problem was to add randomness to the system to make the timing measurements more "noisy." Thus attemping to make the signal-to-noise ratio high enough that it makes stochastically difficult for an attacker to find any useful information. TimeWarp by Martin et al. [67] is a good recent example of this type of technique.

There has also been much work that is typically based on information theory to quantify how much information is leaking through a timing channel. Askarov et al. [14] present a software-based approach that black-boxes modules and adds randomness to when output events of this black box can be observed. They use information theory to bound the amount of information leaking through the timing channel. Giles et al. present "jammers" for timing channels that add randomness and then quantify the difficulty of exploting the channel using information theory. Kocher [55] presents cryptographic blinding in order to prevent timing channels. Cryptographic blinding is a way of adding randomness directly to the computation rather than adding randomness into the system itself. For example, for computing the modular exponentiation in RSA, one can multiply

the input message by a random number and then reverse the operation before decrypting. An attacker measuring time in this case would have a much more difficult time extracting the secret information because it would be blinded by this random number. In a similar manner, Köpf et al. [56] analyze how much information is leaked once cryptographic blinding is applied. Their approach is also information theoretic.

The root cause of these timing channels are typically hardware specific. For example, the *time* penalty for missing a cache is higher than hitting it, the latency for a mis-predicted branch is higher than one that is correct, or more time is spent on certain branches of computation. In general, a multi-process system will take longer to finish its work when processes contend for hardware resources. All of these hardware-specific timing vulnerabilities can, and have been exploited to extract secret information. Further, hardware-based timing channels can even violate the availability where a process or subsystem cannot meet its deadline because a less trusted component has violated its response time.

Detecting these sort of vulnerabilities, in addition to other hardware security bugs, is becoming an increasingly difficult and costly problem. Currently, there are limited (if any) methods for assisting designers in finding potential problems in their hardware. There are many methods for helping prevent these sort of attacks, but systematic methods for *detecting* them is an extremely difficult problem. As mentioned, there are many other examples in which the lack of security assessment have costed companies money and time. If these companies had a mechanism for testing the security properties of their underlying hardware, many of the bugs that are found are likely to be circumvented. This thesis provides such a tool and demonstrates how it can be used against hardware timing channels. The remainder of this thesis will explore how gate-level information flow tracking (GLIFT) can be used to detect and identify hardware timing channels. The next Chapter will first provide some essential definitions for GLIFT in order to build a

solid theoretical foundation.

## **Chapter 3**

# Fundamental GLIFT Logic Equations and Overheads

In order to have a good understand of the details behind GLIFT, it is helpful to have an understanding of some essential definitions and associated overheads. In this chapter I will present some of these definitions and give some discussions into the overheads that the logic creates.

GLIFT logic is the co-existing logic that propagates information throughout a system. This logic performs no operations that affect the way that the system operates. The GLIFT logic is used to understand where information is propagating to point out where potential security vulnerabilities are. This is done by "tainting" information and monitoring it as it flows throughout the system. Before we can discuss the necessary formal equations for GLIFT, I will first define taint. Throughout this discussion, the shadow logic for basic gate primitives (AND, OR, NAND, etc.) will be discussed.

## 3.1 Taint and Tracking (GLIFT) Logic

Taint is simply a label associated with a piece of information that renders it to be tracked. For example, if one wishes to track the movement of a secret key in a piece of hardware, then they would taint the key to indicate that it is secret. In GLIFT logic, as

we will soon discuss, every bit has an associated taint bit (for a 2-level security lattice). To this end, if a bit's associated taint bit is asserted, we say that that bit is tainted. To be more precise, a more formal definition is given in Definition 1. I will later repeat this definition for completeness in Chapter 6.

**Definition 1** (Taint). For a set of wires (inputs, outputs, or internals) X, the corresponding taint set is  $X_t$ . A wire  $x_i$  for  $x = (x_1, ..., x_i, ..., x_n) \in X$  is tainted by setting  $x_{it} = 1$  for  $x_t \in X_t$  and  $x_t = (x_{1t}, ..., x_{it}, ..., x_{nt})$ .