# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Design of Wideband Millimeter-Wave Beamformers and Transceivers in Advanced CMOS SOI Technology

#### **Permalink**

https://escholarship.org/uc/item/7xc0c9b7

#### **Author**

Gao, Li

#### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

# Design of Wideband Millimeter-Wave Beamformers and Transceivers in Advanced CMOS SOI Technology

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Li Gao

# Committee in charge:

Professor Gabriel Rebeiz, Chair Professor Gert Cauwenberghs Professor Drew Hall Professor William Hodgkiss Professor Patrick Mercier

Copyright

Li Gao, 2020

All rights reserved.

| The dissertation of Li Gao is approved, and it is acceptable in |

|-----------------------------------------------------------------|

| quality and form for publication on microfilm and electroni-    |

| cally:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

| Chair                                                           |

University of California San Diego

2020

# **DEDICATION**

To my family

# **EPIGRAPH**

Man proposes, God disposes.

# TABLE OF CONTENTS

| Signature Page .            |                                                                                                                                                                                                                                                                                                                                                                                                                                           | iii                                                                                |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Dedication                  |                                                                                                                                                                                                                                                                                                                                                                                                                                           | iv                                                                                 |

| Epigraph                    |                                                                                                                                                                                                                                                                                                                                                                                                                                           | v                                                                                  |

| Table of Contents           |                                                                                                                                                                                                                                                                                                                                                                                                                                           | vi                                                                                 |

| List of Figures             |                                                                                                                                                                                                                                                                                                                                                                                                                                           | ix                                                                                 |

| List of Tables              |                                                                                                                                                                                                                                                                                                                                                                                                                                           | xiv                                                                                |

| Acknowledgements            | s                                                                                                                                                                                                                                                                                                                                                                                                                                         | xv                                                                                 |

| Vita                        |                                                                                                                                                                                                                                                                                                                                                                                                                                           | xviii                                                                              |

| Abstract of the Dis         | sertation                                                                                                                                                                                                                                                                                                                                                                                                                                 | XX                                                                                 |

| Chapter 1 Intro 1.1 1.2 1.3 | Background                                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>3<br>4                                                                   |

|                             | 2-44 GHz Phased-Array Receive Beamformer in 45-nm CMOS SOI for Applications with 3-3.6 dB NF Introduction Block Design 2.2.1 Wideband Input and Output Matching Network 2.2.2 Wideband LNA 2.2.3 Wideband VGA and Switched Attenuator 2.2.4 Wideband Vector Modulator 2.2.5 Entire 20-44 GHz Beamforming Channel LNA, VM and VGA Block Measurement 2.3.1 LNA 2.3.2 VM 2.3.3 VGA Beamformer Channel Measurements Conclusion Acknowledgment | 7<br>7<br>9<br>9<br>12<br>14<br>18<br>21<br>22<br>22<br>24<br>25<br>27<br>29<br>30 |

| Chapter 3 | ΑH    | igh Power 24-40 GHz Transmit-Receive Front-End For Phased-Arrays |

|-----------|-------|------------------------------------------------------------------|

|           | in 45 | 5-nm CMOS SOI                                                    |

|           | 3.1   | Introduction                                                     |

|           | 3.2   | Design                                                           |

|           |       | 3.2.1 SPDT Switch                                                |

|           |       | 3.2.2 LNA Design                                                 |

|           |       | 3.2.3 PA Design                                                  |

|           | 3.3   | Measurements                                                     |

|           | 0.0   | 3.3.1 LNA                                                        |

|           |       | 3.3.2 SPDT                                                       |

|           |       | 3.3.3 Front-End Rx Mode                                          |

|           |       | 3.3.4 Front-End Rx Mode                                          |

|           | 3.4   | Conclusion                                                       |

|           | 3.5   |                                                                  |

|           | 3.3   | Acknowledgment                                                   |

| Chapter 4 | A 20  | 0-44 GHz Image Rejection Receiver with > 75 dB Image Rejection   |

| Chapter   |       | o in 22-nm CMOS FD-SOI for 5G Applications                       |

|           | 4.1   | Introduction                                                     |

|           | 4.2   | Receiver Architecture                                            |

|           | 7.2   | 4.2.1 Receiver Comparison                                        |

|           |       | 4.2.2 Image Rejection Consideration                              |

|           |       | 4.2.3 LO Feedthrough Consideration                               |

|           | 4.3   |                                                                  |

|           | 4.3   | E                                                                |

|           |       | e                                                                |

|           |       |                                                                  |

|           |       | 4.3.3 LO Chain and Mixer                                         |

|           | 4 4   | 4.3.4 IF Amplifier                                               |

|           | 4.4   | Measurements                                                     |

|           |       | 4.4.1 LNA                                                        |

|           |       | 4.4.2 LNA Harmonics and Intermodulation Study                    |

|           |       | 4.4.3 SSB Receiver: Gain, NF, IP1dB and LO Feedthrough 80        |

|           |       | 4.4.4 SSB Receiver: Complex Modulation                           |

|           | 4.5   | Conclusion                                                       |

|           | 4.6   | Acknowledgment                                                   |

| Charten 5 | Dag   | ion of 20 42 CHz IO Doodiyan in 22 nm CMOS ED SOI for 5C April   |

| Chapter 5 |       | ign of 20-42 GHz IQ Receiver in 22-nm CMOS FD-SOI for 5G Appli-  |

|           |       | ons                                                              |

|           | 5.1   | Introduction                                                     |

|           | 5.2   | Design                                                           |

|           |       | 5.2.1 LNVGA                                                      |

|           |       | 5.2.2 LO Chain and Mixer                                         |

|           |       | 5.2.3 LPF and IF Amplifier                                       |

|           |       | 5.2.4 Entire Receiver                                            |

|              | 5.3 Measurements                                            |

|--------------|-------------------------------------------------------------|

|              | 5.4 Conclusion                                              |

|              | 5.5 Acknowledgment                                          |

| Chapter 6    | Design E-/W-Band LNA in GF 22-nm CMOS FD-SOI and 45-nm CMOS |

|              | SOI 10                                                      |

|              | 6.1 Introduction                                            |

|              | 6.2 E-/W-Band LNA in GF 22-nm CMOS FD-SOI                   |

|              | 6.2.1 Technology and Transistor Characterization            |

|              | 6.2.2 Circuit Design                                        |

|              | 6.2.3 Circuit Implementation                                |

|              | 6.2.4 E-Band LNA Measurement                                |

|              | 6.2.5 W-Band LNA Measurement                                |

|              | 6.3 W-Band LNA in GF 45-nm CMOS SOI                         |

|              | 6.3.1 Technology and Circuit Design                         |

|              | 6.3.2 Measurement Results                                   |

|              | 6.4 Comparison                                              |

|              | 6.5 Conclusion                                              |

|              | 6.6 Acknowledgment                                          |

| Chapter 7    | Designing Wideband Power Amplifiers in 45-nm CMOS SOI       |

| -            | 7.1 Introduction                                            |

|              | 7.2 Distributed Amplifier Design                            |

|              | 7.2.1 Circuit Design                                        |

|              | 7.2.2 Measurement                                           |

|              | 7.3 Conclusion                                              |

|              | 7.4 Acknowledgment                                          |

| Chapter 8    | Conclusion and Future Work                                  |

| -            | 8.1 Conclusion                                              |

|              | 8.2 Future Work                                             |

| Bibliography |                                                             |

# LIST OF FIGURES

| Figure 1.1:             | Block diagram of a beamformer phased array chip                                                                                                                       | 3        |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.1: Figure 2.2: | Block diagram of a wideband $2\times 2$ beamformer chip                                                                                                               | 1.0      |

| Figure 2.3:             | $f_2$ , (c) $f_2 < f < f_1$ , (d) $f > f_1$                                                                                                                           | 10<br>11 |

| Figure 2.4:             | (a) Schematic of the output matching network; (b) Revised version; (c) Simulated results                                                                              | 11       |

| Figure 2.5:             | Schematic of the wideband single-end to differential LNA                                                                                                              | 12       |

| Figure 2.6:             | Simulated LNA input impedance matching and noise matching at 33 GHz.                                                                                                  | 13       |

| Figure 2.7:             | Simulated voltage gain of each stage in the LNA                                                                                                                       | 14       |

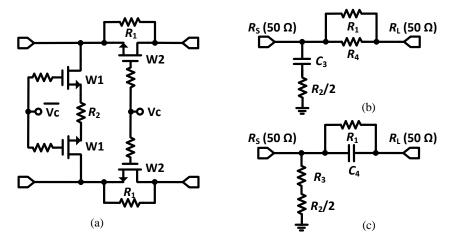

| Figure 2.8:             | One-bit 4 dB attenuator (a) schematic; (b) attenuator off circuit; (c) attenuator                                                                                     |          |

| E: 2.0                  | on circuit.                                                                                                                                                           | 15       |

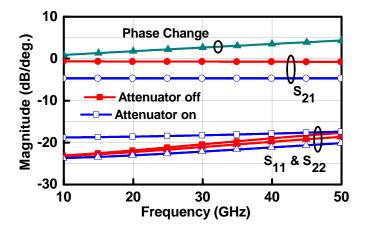

| Figure 2.9:             | One-bit 4 dB attenuator simulated results                                                                                                                             | 15       |

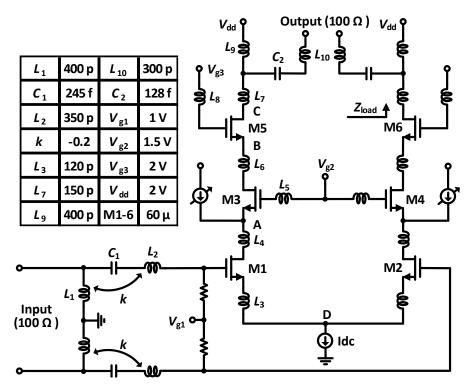

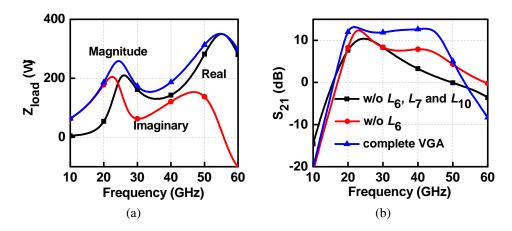

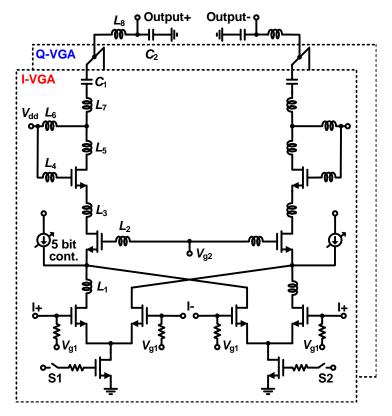

| Figure 2.10:            | Schematic of the triple-stack wideband VGA core.                                                                                                                      | 16       |

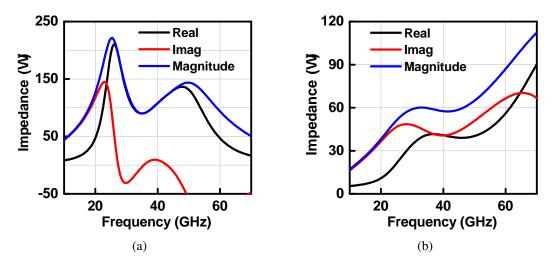

| Figure 2.11:            | Wideband VGA: (a) simulated differential load impedance; (b) simulated gain for different conditions                                                                  | 17       |

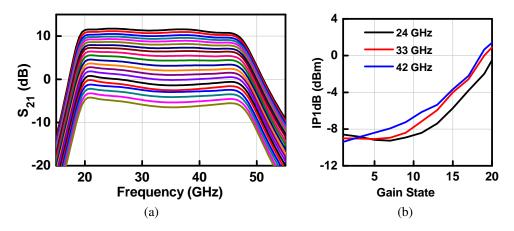

| Figure 2.12:            | (a) Simulated VGA S <sub>21</sub> ; (b) Simulated VGA IP1dB versus gain state                                                                                         | 18       |

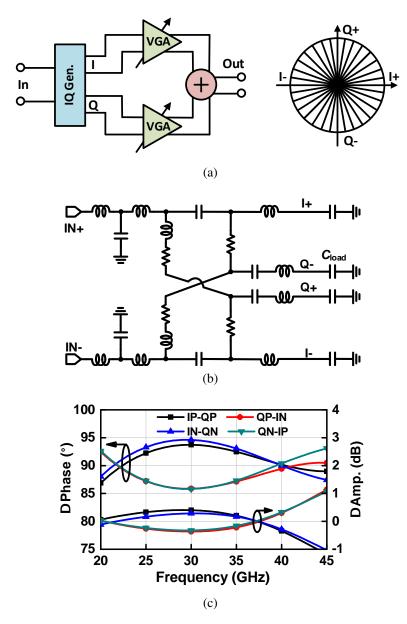

| -                       | (a) Block diagram of the vector modulator and ideal 5-bit response; (b)                                                                                               | 10       |

| 118010 21101            | wideband quadrature all-pass filter and its (c) simulated amplitude and phase mismatch                                                                                | 19       |

| Figure 2 14.            | Schematic of wideband VM using triple stack amplifier.                                                                                                                | 20       |

| _                       | Wideband beamformer channel: Gain, NF and linearity breakup                                                                                                           | 21       |

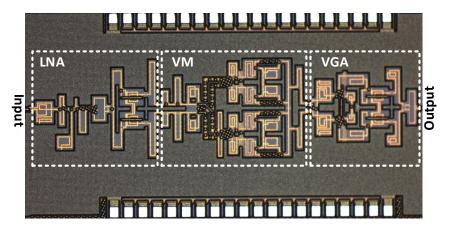

| _                       | Fabricated photograph of the one channel (Core size: $2.7 \times 0.7 \text{ mm}^2$ )                                                                                  | 21       |

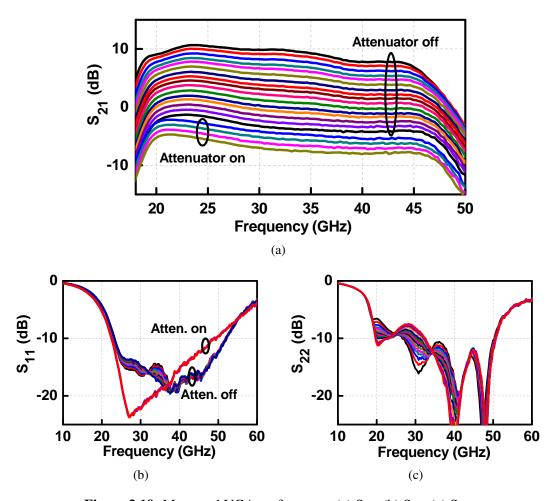

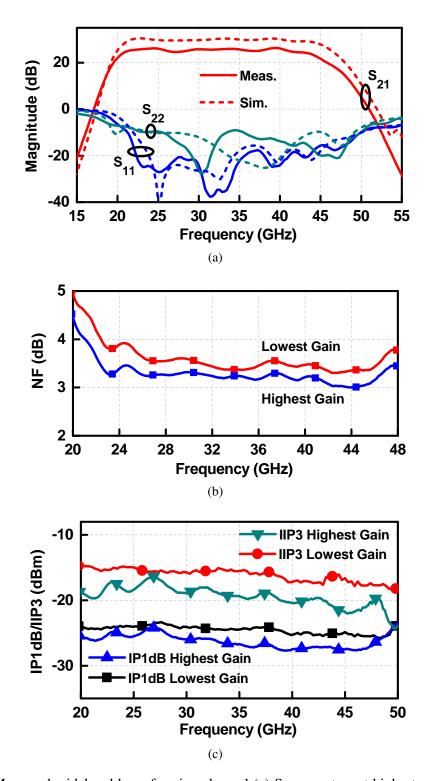

| _                       | Measured and simulated LNA: (a) S-parameters; (b) NF; (c) IP1dB                                                                                                       | 22       |

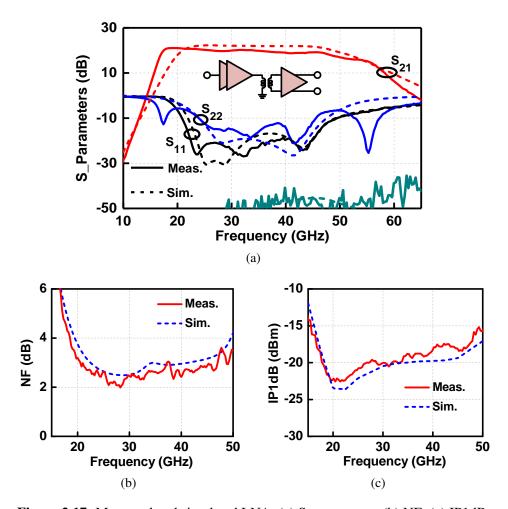

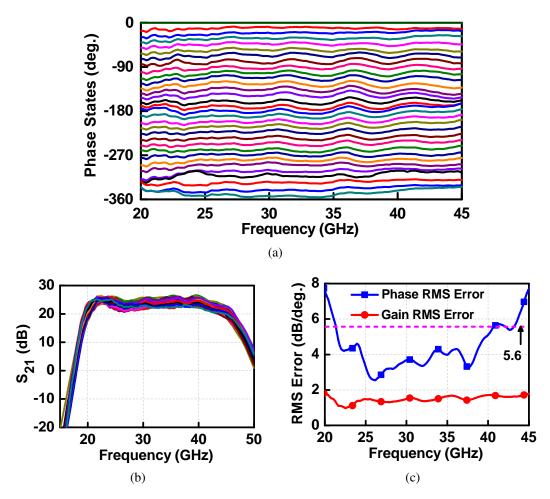

| -                       | Measured VM performance (a) Phase state; (b) S <sub>21</sub> ; (c) Phase and gain RMS                                                                                 | 24       |

| Figure 2 10:            | error; (d) $S_{11}$ and $S_{22}$ ; (e) NF and IP1dB                                                                                                                   | 26       |

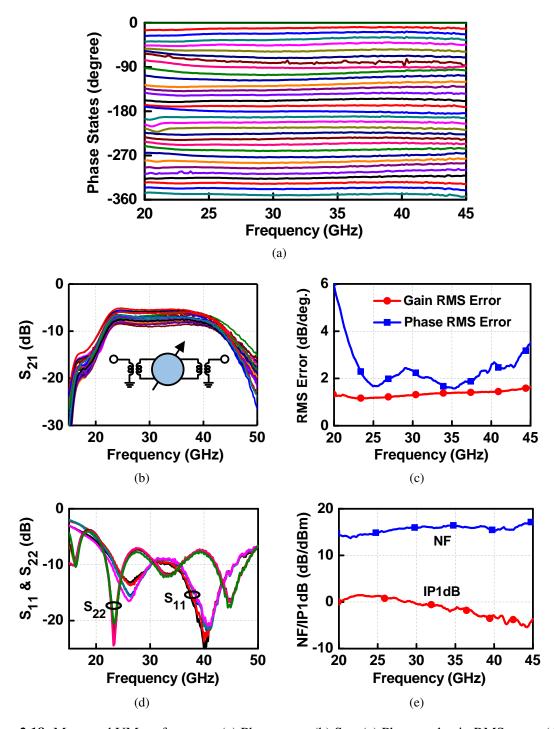

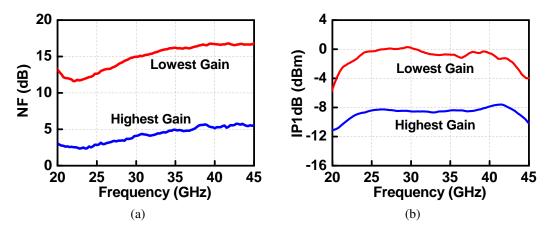

| -                       | Measured VGA at highest (10.5 dB) and lowest (-5.5 dB) gain mode (a) NF;                                                                                              | 20       |

| riguit 2.20.            | (b) IP1dB                                                                                                                                                             | 26       |

| Figure 2.21:            | Measured wideband beamforming channel (a) S-parameters at highest gain; (b) NF; (c) IP1dB and IIP3                                                                    | 28       |

| Figure 2.22:            | Measured wideband channel performance (a) 5-bit phase control; (b) S <sub>21</sub> ; (c)                                                                              |          |

|                         | Phase and gain RMS error                                                                                                                                              | 29       |

| Figure 3.1:             | A dual-band phased array beamformer channel. Several channels are com-                                                                                                |          |

| T                       | bined together on a single chip to form a 4-16 channel chip                                                                                                           | 32       |

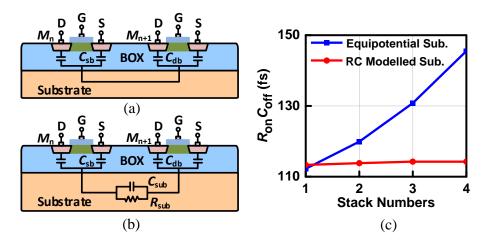

| Figure 3.2:             | (a) Cross section view of a two-stack transistor (a) using equipotential substrate assumption; (b) using RC modelled substrate; (c) Simulated $R_{\rm on}C_{\rm off}$ |          |

|                         | for different stack numbers. Schematic of the output matching network                                                                                                 | 33       |

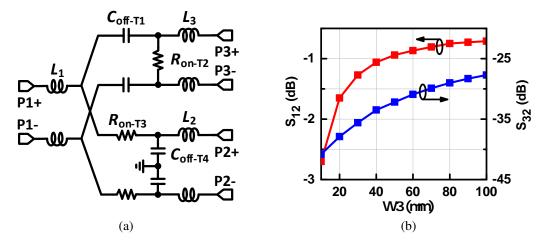

| Figure 3.3:  | Schematic of the differential asymmetrical SPDT                                                    | 34 |

|--------------|----------------------------------------------------------------------------------------------------|----|

| Figure 3.4:  | (a) Tx mode equivalent circuit; (b) Simulated insertion loss and isolation                         |    |

|              | versus transistor size at 40 GHz                                                                   | 35 |

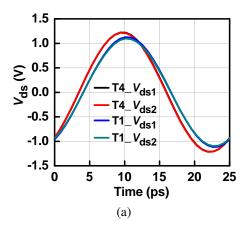

| Figure 3.5:  | Simulated waveform when P2 (differential) is excited with Pin=20 dBm (a)                           |    |

|              | Voltage across each transistor for the T1 and T4 upper arms at 40 GHz; (b)                         |    |

|              | Current across T2 and T3 at 40 GHz                                                                 | 36 |

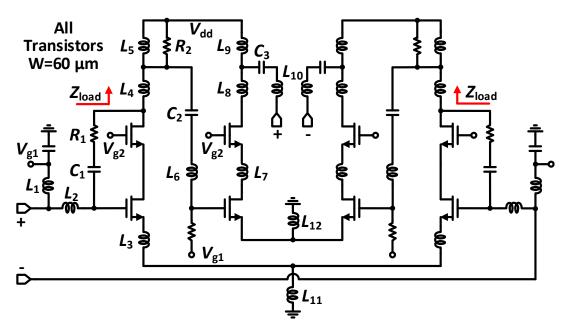

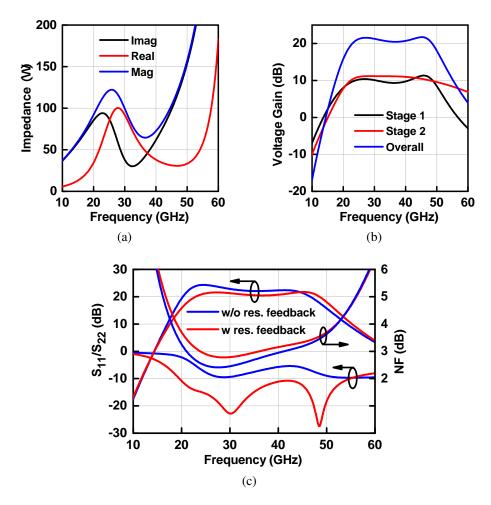

| Figure 3.6:  | Schematic of two stage differential wideband LNA                                                   | 37 |

| Figure 3.7:  | (a) Simulated load impedance of stage 1 with next stage input impedance                            |    |

| _            | (marked as $Z_{Load}$ ), (b) Simulated voltage gain of each stage of complete                      |    |

|              | circuit. (c) Simulated LNA versus resistive feedback                                               | 38 |

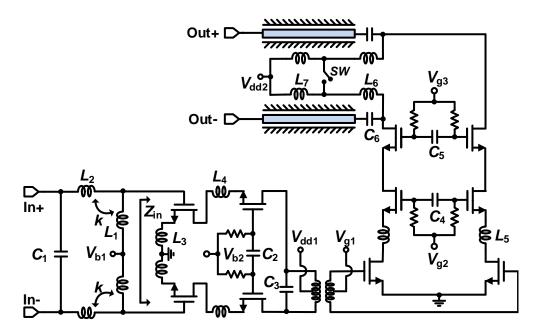

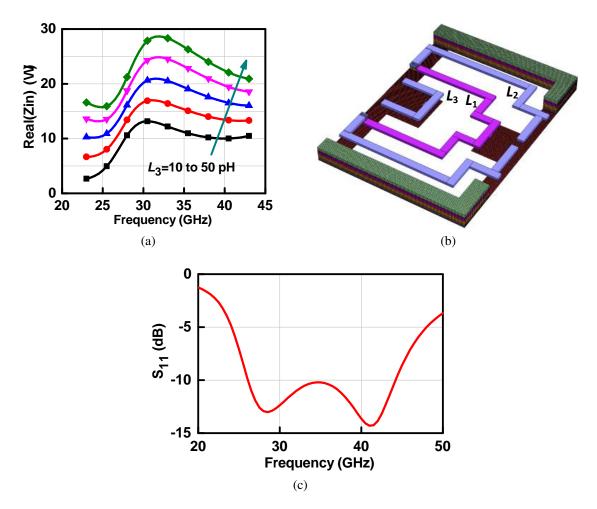

| Figure 3.8:  | Schematic of the differential two-stage dual-band power amplifier                                  | 39 |

| Figure 3.9:  | Simulated real part of the driver input impedance versus $L_3$ ; (b) 3-D layout                    |    |

|              | of $L_1$ , $L_2$ , and $L_3$ ; (c) Simulated $S_{11}$                                              | 40 |

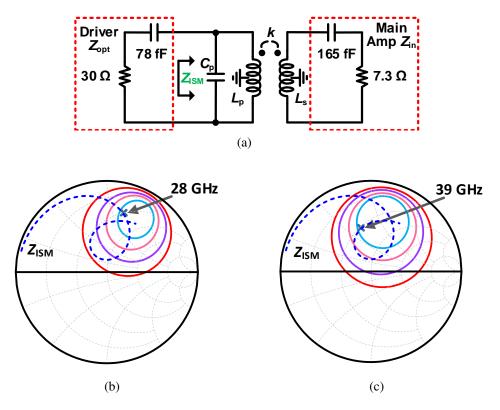

| Figure 3.10: | (a) Inter-stage transformer matching; Simulated PAE contour and input                              |    |

|              | impedance of the inter-stage matching, Z <sub>ISM</sub> , at (b) 28 GHz; (c) 39 GHz                | 42 |

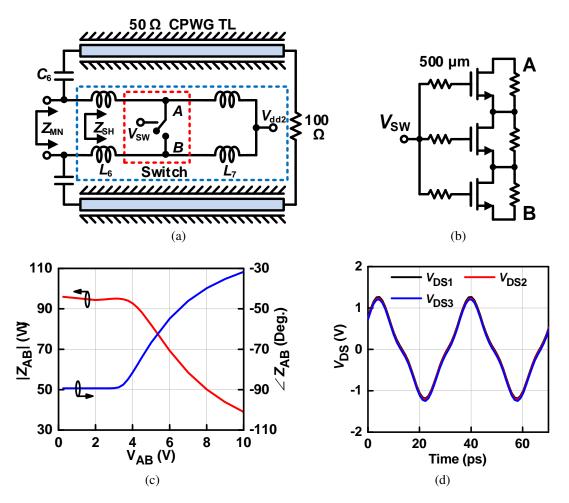

| Figure 3.11: | (a) Structure of output matching network; (b) Three-stack switch in MN                             |    |

|              | (all un-labelled resistors are $12 \text{ k}\Omega$ ); (c) Simulated switch impedance ( $Z_{AB}$ ) |    |

|              | versus voltage swing; (d) Simulated the voltage swing across the three switch                      |    |

|              | transistor at 28 GHz when operating at P1dB                                                        | 43 |

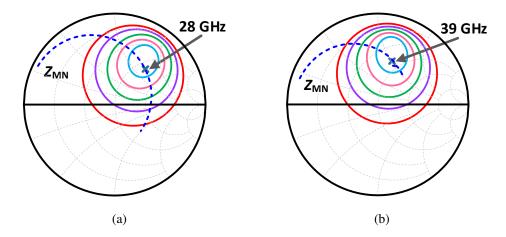

| Figure 3.12: | Simulated PAE contour and input impedance of the output matching network,                          |    |

| C            | Z <sub>MN</sub> , at (a)28 GHz (switch ON);(b)39 GHz (switch OFF)                                  | 45 |

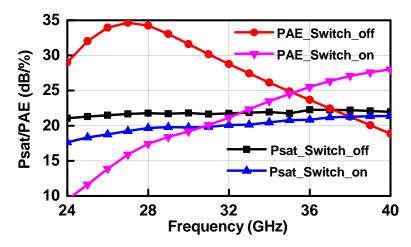

| Figure 3.13: |                                                                                                    |    |

|              | load-tuning switch in the ON (low-band) and OFF (high-band) position                               | 46 |

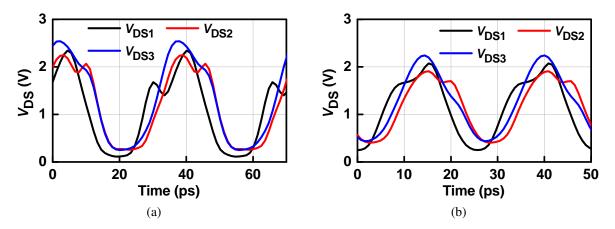

| Figure 3.14: | Simulated waveform of the stacked amplifier at (a) 28 GHz at P1dB of 21.3                          |    |

|              | dBm (switch ON); (b) 39 GHz at 20 dBm (Switch OFF)                                                 | 46 |

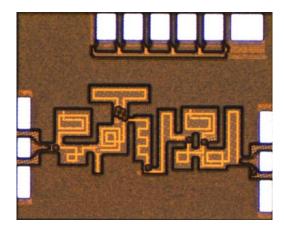

| Figure 3.15: | Microphotograph of LNA test chip (0.9×0.75 mm <sup>2</sup> )                                       | 47 |

|              | (a) Measured and simulated S-parameters of the LNA test cell; (b) Measured                         |    |

| _            | and simulated NF; (c) Measured IP1dB and IIP3                                                      | 48 |

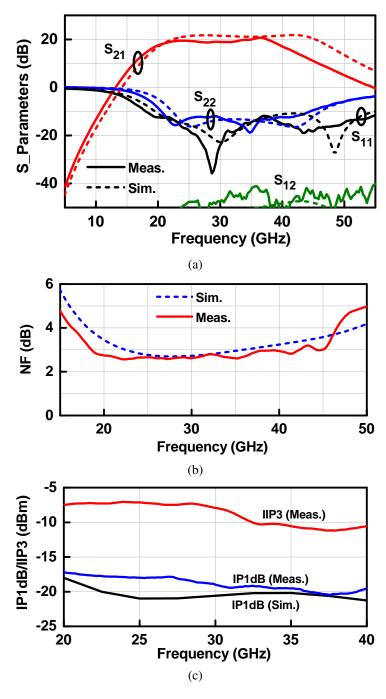

| Figure 3.17: | (a) Microphotograph of the fabricated single-end SPDT test chip (0.64×0.52                         |    |

|              | mm <sup>2</sup> ); Measured SPDT S-parameters (b) Rx mode; (c) Tx mode; (d) Mea-                   |    |

|              | sured IP1dB in the Tx and Rx modes (single-ended)                                                  | 50 |

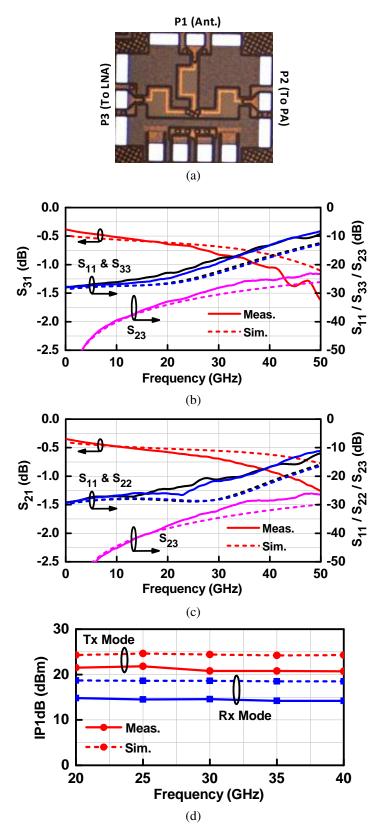

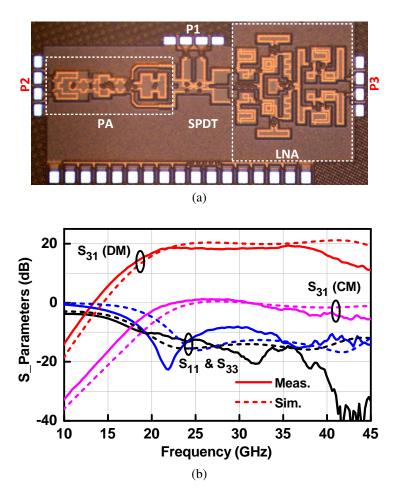

| Figure 3.18: | (a) Microphotograph of the fabricated front-end chip. Size: 2.1×1 mm <sup>2</sup> . (b)            |    |

|              | Measured and simulated S-parameters of the front-end module in the Rx                              |    |

|              | mode                                                                                               | 52 |

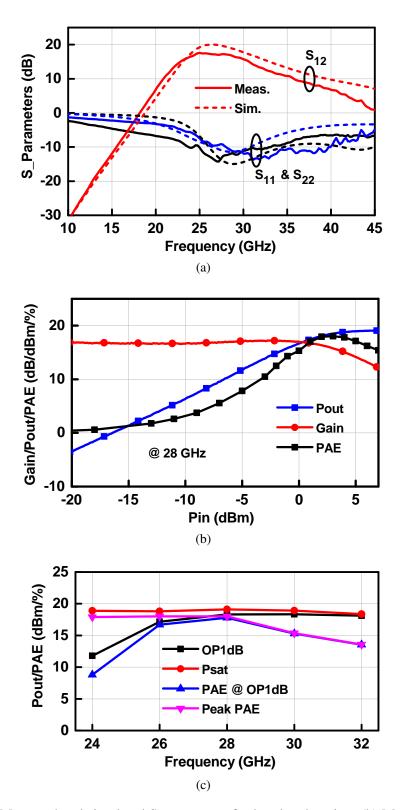

| Figure 3.19: | (a) Measured and simulated S-parameters for low-band setting; (b) Measured                         |    |

|              | Pout, PAE, Gain versus Pin at 28 GHz; (c) Measured Pout and PAE versus                             |    |

|              | frequency                                                                                          | 53 |

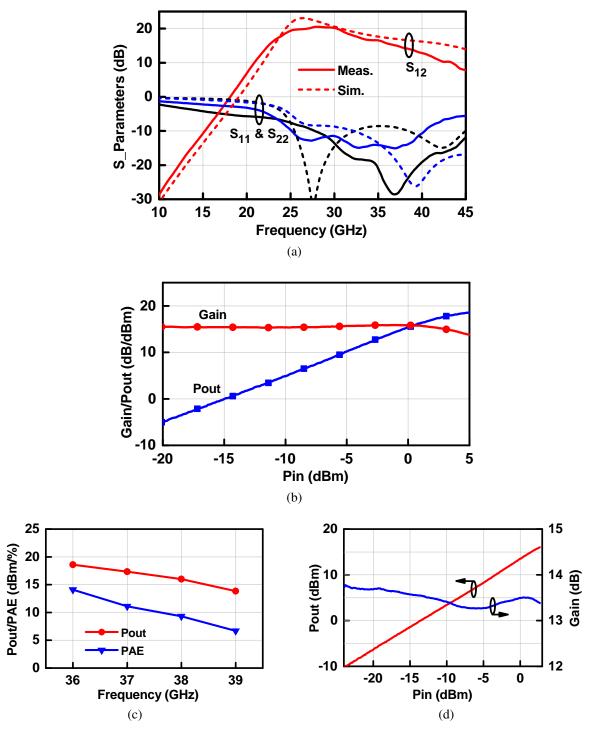

| Figure 3.20: | (a) Measured and simulated S-parameters for high-band setting; (b) Measured                        |    |

| S            | Pout vs. Pin at 36 GHz; (c) Measured highest possible Pout and correspond-                         |    |

|              | ing PAE versus frequency; (d) Measured Pout and gain versus Pin at 38 GHz                          |    |

|              | with $< 0.5$ dB compression up to 16 dBm                                                           | 55 |

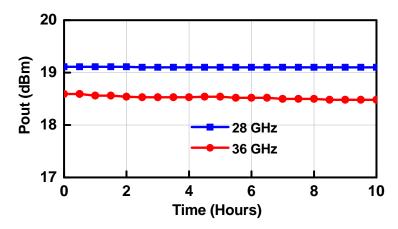

| Figure 3.21: | Measured output power at the P1dB level for a period of 10 hours.                                  | 56 |

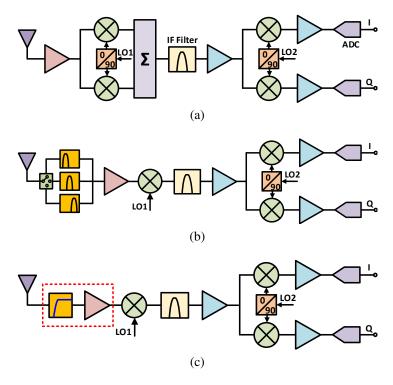

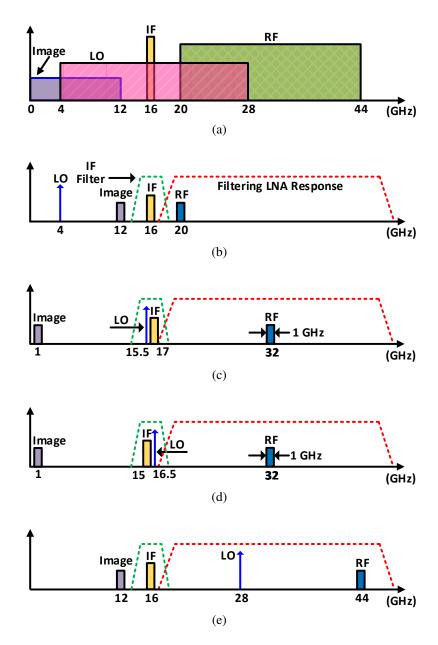

| Figure 4.1:  | (a) Traditional low-IF single-sideband receiver, (b) output power contour vs Alternative single-sideband receiver with medium IF, (c)Proposed single-                                                     |     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | sideband receiver with high IF                                                                                                                                                                            | 61  |

| Figure 4.2:  | Wideband single-sideband receiver with high IF and LO leakage cancellation                                                                                                                                |     |

|              | circuit                                                                                                                                                                                                   | 62  |

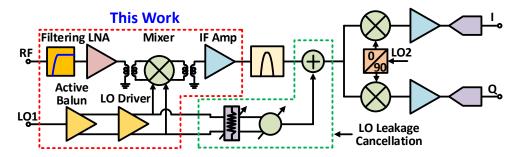

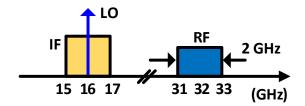

| Figure 4.3:  | (a) Frequency plan; (b) spectrum for RF=19.5-20.5 GHz, LO=4 GHz; (c) spectrum for RF=31.5-32.5 GHz, LO=15.5 GHz; (d) spectrum for RF=31.5-32.5 GHz, LO=16.5 GHz; (e) spectrum for RF=43.5-44.5 GHz, LO=28 |     |

|              | GHz                                                                                                                                                                                                       | 63  |

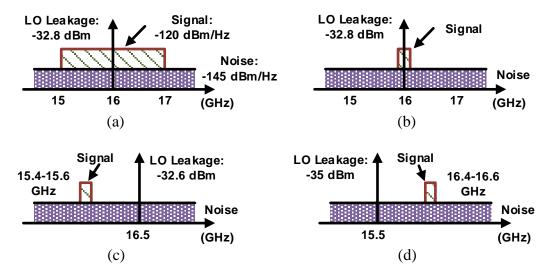

| Figure 4.4:  | Spectrum for RF=31-33 GHz and LO=16 GHz                                                                                                                                                                   | 65  |

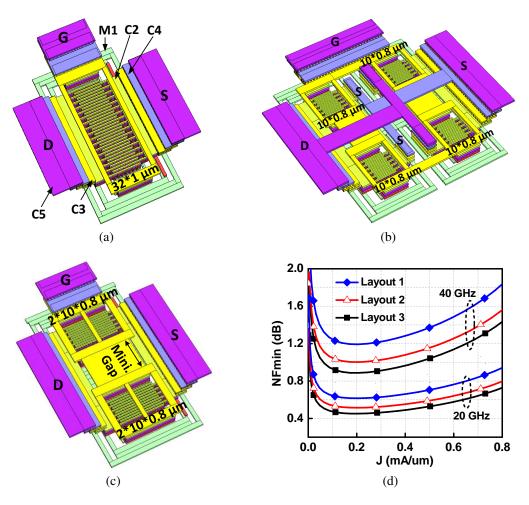

| Figure 4.5:  | Three different layouts up to C5 for a 32 µm width transistor (a) Layout 1;                                                                                                                               |     |

|              | (b) Layout 2; (c) Layout 3 and (d) Simulated NFmin                                                                                                                                                        | 66  |

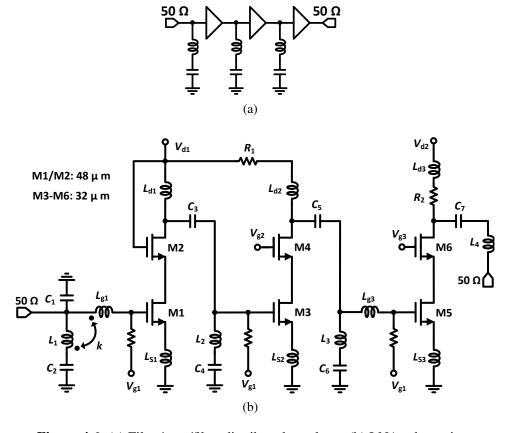

| Figure 4.6:  | (a) Filter/amp/filter distributed topology; (b) LNA schematic                                                                                                                                             | 67  |

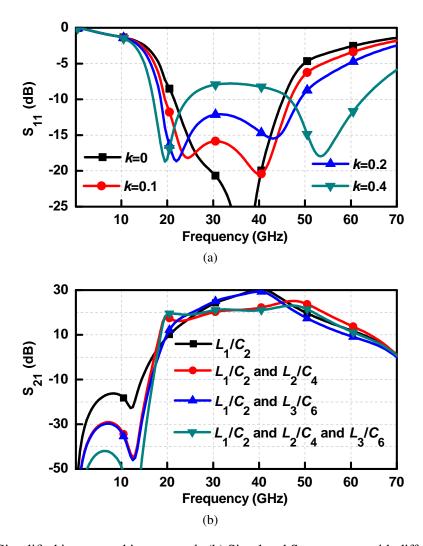

| Figure 4.7:  | (a) Simplified input matching versus $k$ ; (b) Simulated $S_{21}$ response with                                                                                                                           |     |

| E' 4.0       | different filter order.                                                                                                                                                                                   | 69  |

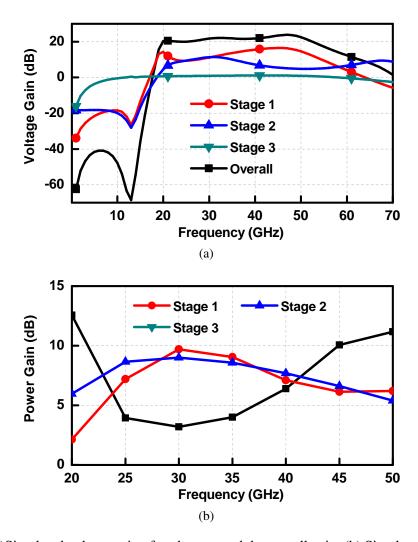

| Figure 4.8:  | (a)Simulated voltage gain of each stage and the overall gain; (b) Simulated                                                                                                                               | 7.  |

| E' 4.0       | power gain.                                                                                                                                                                                               | 70  |

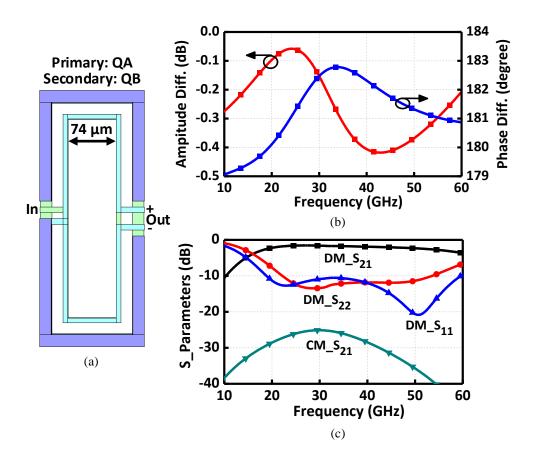

| Figure 4.9:  | (a) Structure of the wideband RF balun; (b) Simulated phase and amplitude                                                                                                                                 | 71  |

| Eigung 4 10. | difference; (c) Simulated DM and CM response                                                                                                                                                              | 71  |

| Figure 4.10: | • • • • •                                                                                                                                                                                                 | 70  |

| Figure 4.11. | the LO driver                                                                                                                                                                                             | 72  |

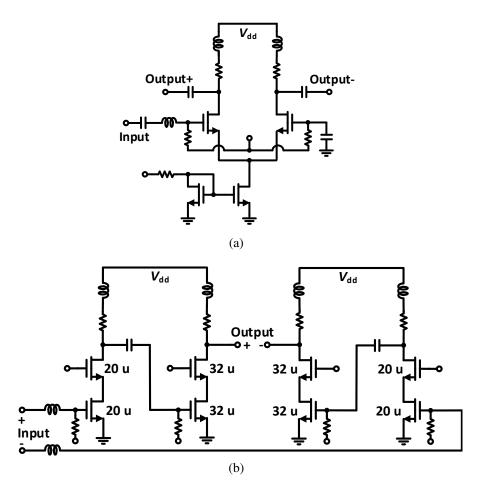

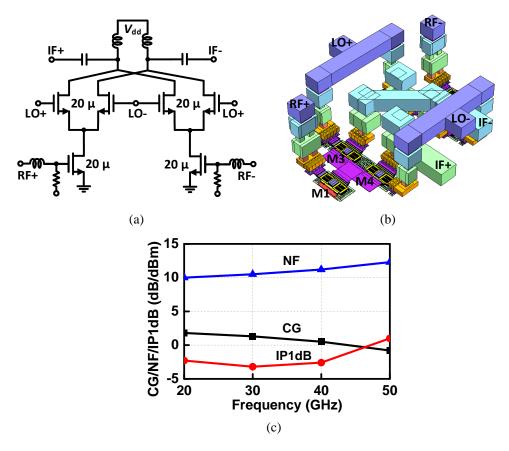

| Figure 4.11: | (a) Schematic of the double balanced mixer; (b) Core layout; (c) Simulated CG/NF/IP1dB using the wideband LO driver                                                                                       | 73  |

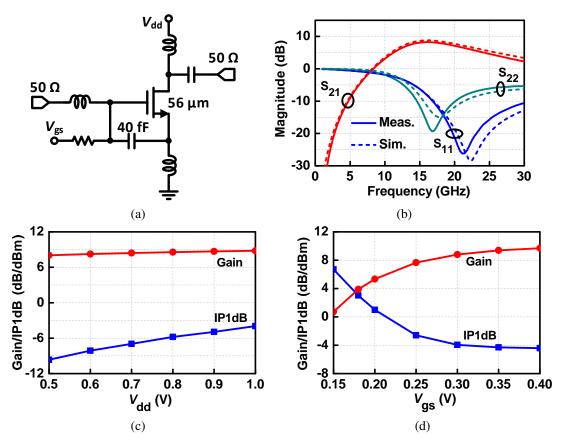

| Figure 4.12: | (a) Schematic of IF amplifier; (b) Simulated and measured S-parameters; (c)                                                                                                                               | 13  |

| 11guie 4.12. | Simulated IP1dB and gain versus $V_{\rm dd}$ ( $V_{\rm gs}$ =0.3 V); (d) Simulated IP1dB and                                                                                                              |     |

|              | gain versus $V_{gs}$ ( $V_{dd}$ =1 V)                                                                                                                                                                     | 74  |

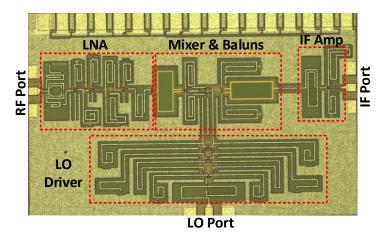

| Figure 4 13. | Microphotograph of the 20-44 GHz single-sideband receiver. $(1.8 \times 1 \text{ mm}^2)$ .                                                                                                                | 75  |

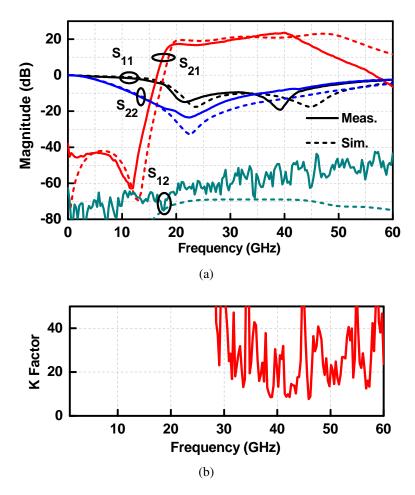

|              | (a) Measured and simulated S-parameters of the LNA; (b) Measured K factor.                                                                                                                                | 76  |

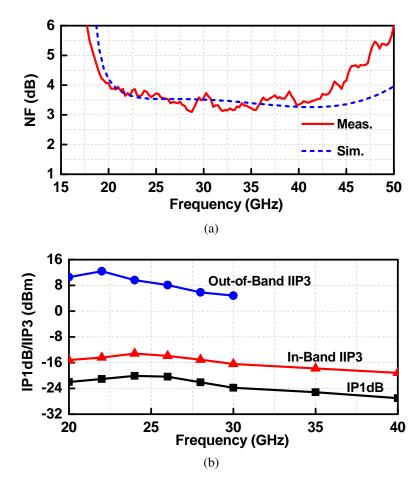

|              | (a) Measured and simulated NF; (b) Measured input P1dB, in-band IIP3 and                                                                                                                                  | , ( |

| 118010 11151 | out-of-band IIP3                                                                                                                                                                                          | 77  |

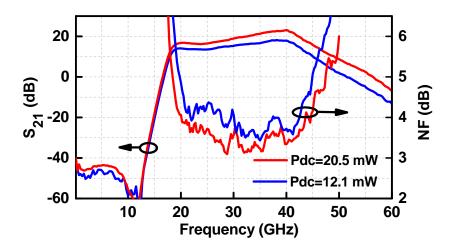

| Figure 4.16: | Measured LNA gain and NF versus DC power consumption                                                                                                                                                      | 78  |

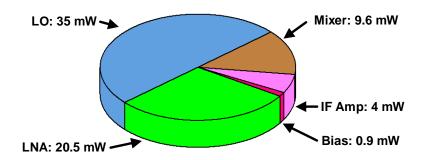

| _            | SSB receiver dc power breakdown.                                                                                                                                                                          | 80  |

| •            | Measured (a) conversion gain and $S_{11}/S_{22}$ of the 20-44 GHz SSB receiver;                                                                                                                           |     |

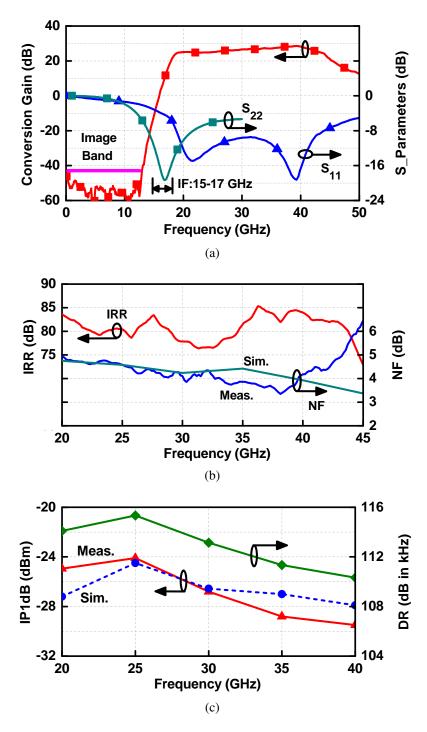

| C            | (b) IRR and NF; (c) IP1dB and dynamic range                                                                                                                                                               | 81  |

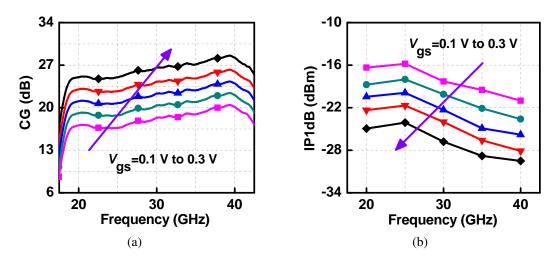

| Figure 4.19: | Measured (a) conversion gain and (b) IP1dB versus IF amplifier gate bias                                                                                                                                  | 82  |

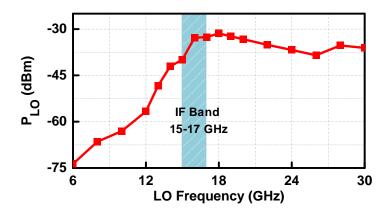

| _            | Measured LO power at the IF port                                                                                                                                                                          | 83  |

| Figure 4.21: | Output spectrum for different cases: (a) RF=31-33 GHz, LO=16 GHz; (b)                                                                                                                                     |     |

|              | RF=31.9-32.1 GHz, LO=16 GHz; (c) RF=31.9-32.1 GHz, LO=16.5 GHz;                                                                                                                                           |     |

|              | (d) RF=31.9-32.1 GHz, LO=15.5 GHz                                                                                                                                                                         | 83  |

| Figure 4.22: | (a) EVM measurement setup. Measured EVM <sub>rms</sub> for different symbol rates,                                                                                                                        |     |

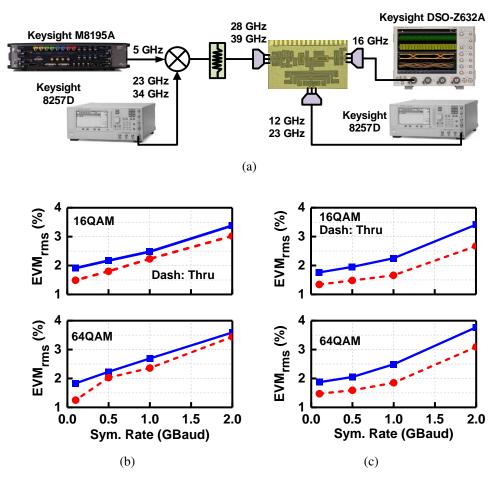

|              | different modulation and 10 dB backoff from IP1dB at (b) 28 GHz; (c) 39 GHz.                                                                                                                              | 84  |

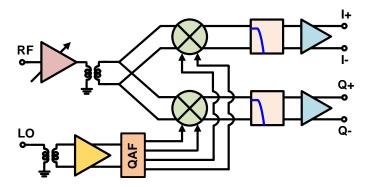

| Figure 5 1.  | Wideband IO receiver topology.                                                                                                                                                                            | 89  |

| riguic J.I.  | WIUCUANU IO IECEIVEI IUDUIUEV                                                                                                                                                                             | 07  |

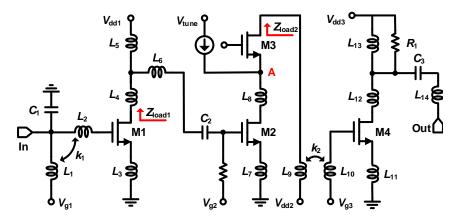

| Figure 5.2:  | Schematic of proposed LNVGA                                                                                    | 90  |

|--------------|----------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.3:  | Simulated (a) stage 1 load impedance (marked as $Z_{load1}$ ); (b) stage 2 load                                |     |

|              | impedance (marked as $Z_{load2}$ )                                                                             | 91  |

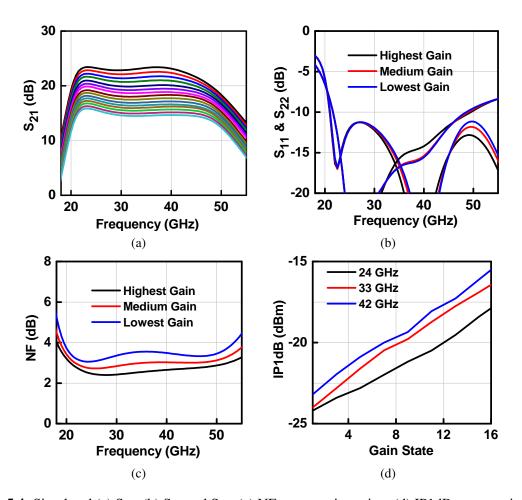

| Figure 5.4:  | Simulated (a) S <sub>21</sub> ; (b) S <sub>11</sub> and S <sub>22</sub> ; (c) NF versus gain tuning; (d) IP1dB |     |

|              | versus gain tuning                                                                                             | 92  |

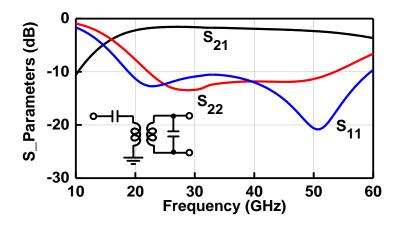

| Figure 5.5:  | Passive RF balun simulation results                                                                            | 93  |

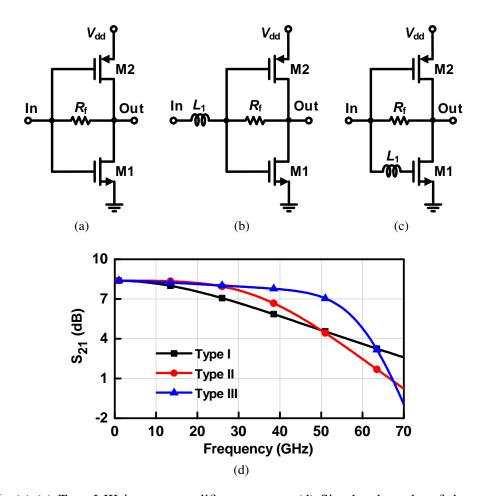

| Figure 5.6:  | (a)-(c) Type I-III inverter amplifier structure; (d) Simulated results of these                                |     |

|              | three type amplifiers                                                                                          | 94  |

| Figure 5.7:  | (a) Schematic of the LO driver amplifier; (b) Simulated results of LO balun                                    |     |

|              | and driver amplifier together                                                                                  | 95  |

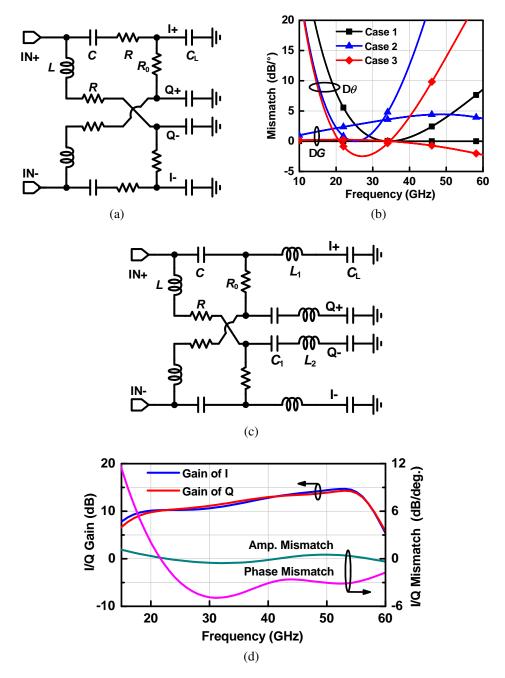

| Figure 5.8:  | (a) Schematic of traditional QAF; (b) Simulated amplitude and phase mis-                                       |     |

|              | match of the QAF for different cases; (c) Modified QAF; (d) Simulated                                          |     |

|              | amplitude and phase mismatch                                                                                   | 97  |

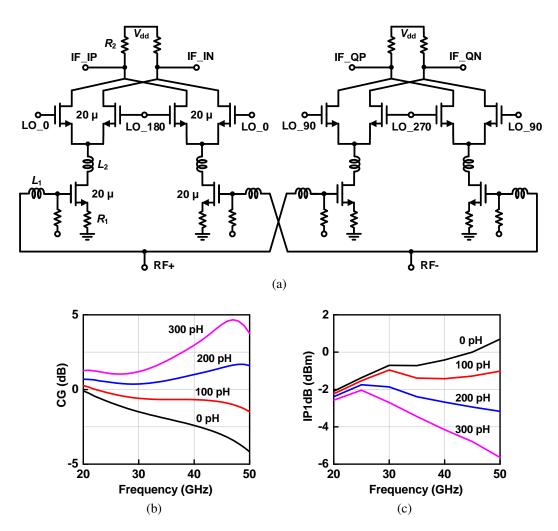

| Figure 5.9:  | (a) Schematic double balance IQ down conversion mixer; (b) Simulated CG                                        |     |

|              | versus $L_2$ ; (c) Simulated IP1dB versus $L_2$                                                                | 98  |

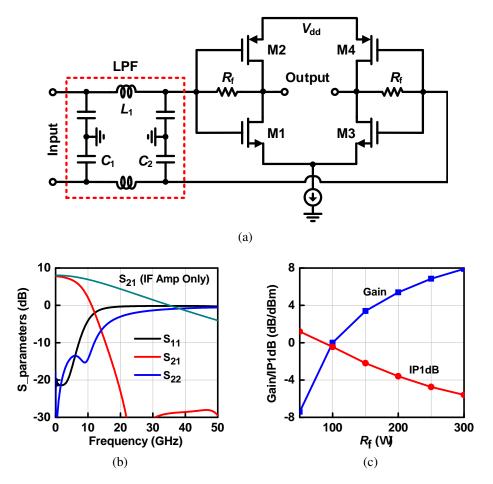

| Figure 5.10: | (a) Schematic of lowpass filter and IF amplifier; (b) Simulated S-parameters;                                  |     |

|              | (c) Simulated gain and IP1dB versus $R_f$                                                                      | 100 |

| -            | Simulated noise profile with RF=28 GHz                                                                         | 101 |

| Figure 5.12: | Microphotograph of the fabricated IQ receiver chip with core size of $1.8 \times 0.5$                          |     |

|              | $mm^2$                                                                                                         | 101 |

| Figure 5.13: | Measured and simulated (a) conversion gain and input/output matching; (b)                                      |     |

|              | NF and IP1dB                                                                                                   | 103 |

|              | Measured gain and phase error between I and Q                                                                  | 103 |

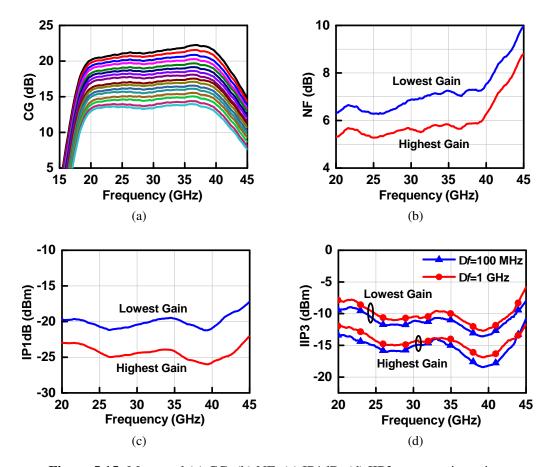

|              | Measured (a) CG; (b) NF; (c) IP1dB; (d) IIP3 versus gain tuning                                                | 104 |

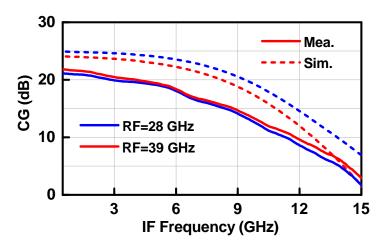

| Figure 5.16: | Measured and simulated CG versus IF frequency                                                                  | 105 |

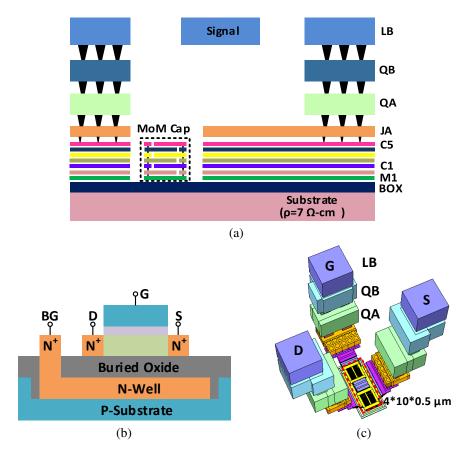

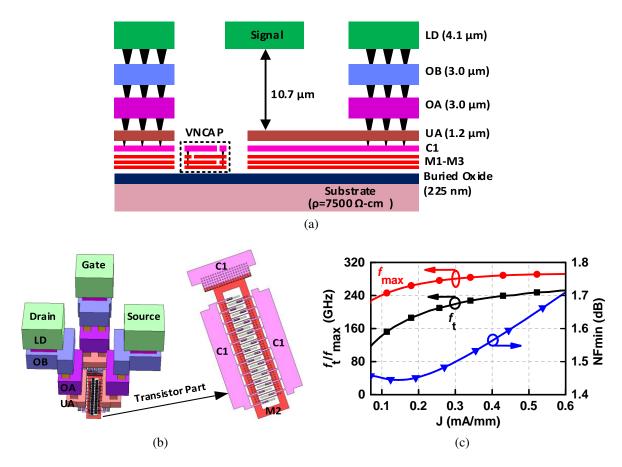

| Figure 6.1:  | (a) 22-nm FD-SOI process stack; (b) Cross section of an n-channel MOSFET;                                      |     |

| 115010 0.11  | (c) Transistor layout for $W=20 \mu m$                                                                         | 109 |

| Figure 6.2:  | (a) 22-nm FD-SOI process stack; (c) Transistor layout for $W=20 \mu m$                                         | 110 |

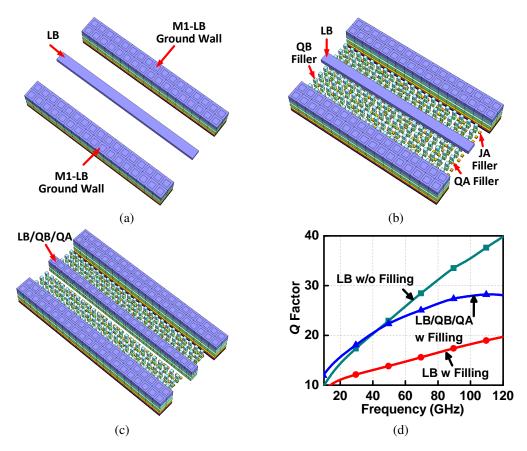

| Figure 6.3:  | A 50 pH transmission-line inductor build using (a) LB without metal fill; (b)                                  | 110 |

| 118010 0.01  | LB with metal fill; (c) LB/QB/QA with metal fill; (d) Simulated Q of a 50                                      |     |

|              | pH inductor in 22FDX for different metal-fill cases                                                            | 112 |

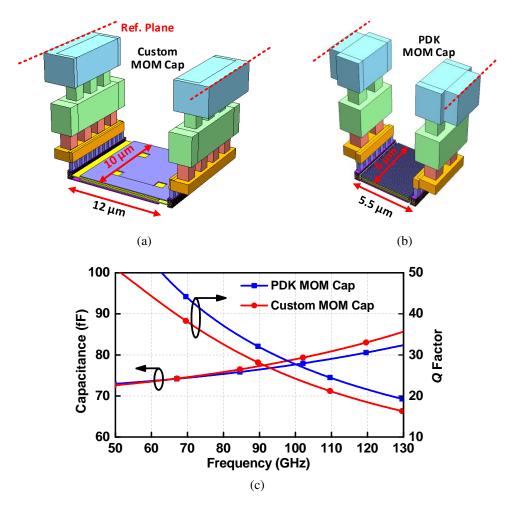

| Figure 6.4:  | 3-D structure of (a) custom MOM capacitor; (b) PDK MOM capacitor; and                                          |     |

| 8            | (c) simulated capacitance and $Q$                                                                              | 113 |

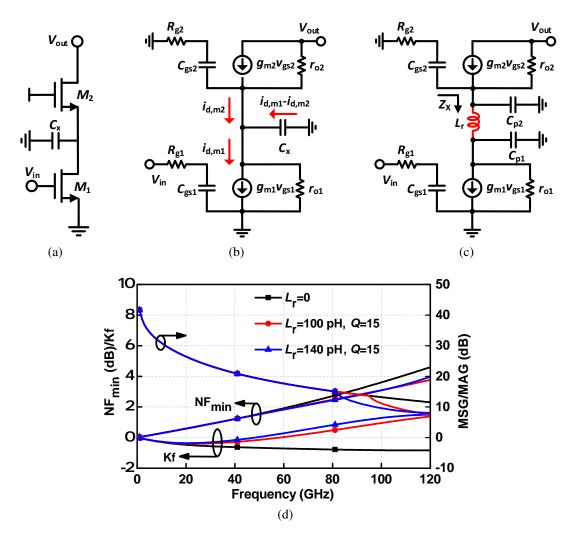

| Figure 6.5:  | (a) Cascode stage; (b) Simplified small signal model of cascode stage without                                  |     |

| S            | series inductor $L_r$ ; (c) with series inductor $L_r$ ; (d) Simulated NF <sub>min</sub> , Kf and              |     |

|              | MAG/MSG at different $L_r$ value                                                                               | 114 |

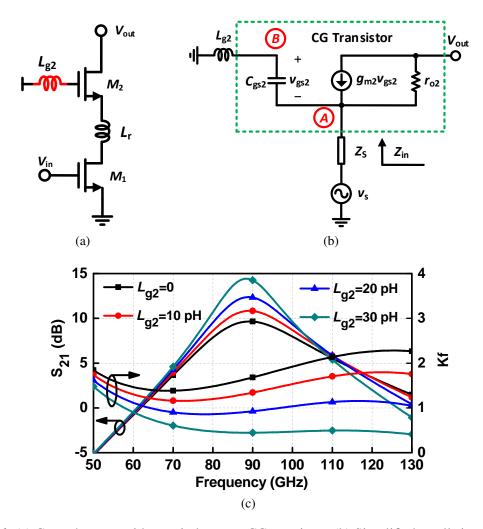

| Figure 6.6:  | (a) Cascode stage with gate inductor at CG transistor; (b) Simplified small                                    |     |

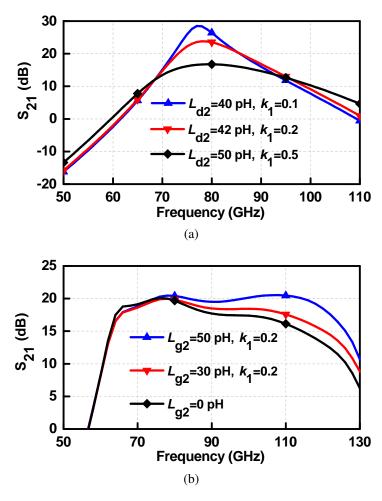

| C            | signal model; (c) Simulated $S_{21}$ and Kf at different $L_{g2}$ value for a cascode                          |     |

|              | stage                                                                                                          | 116 |

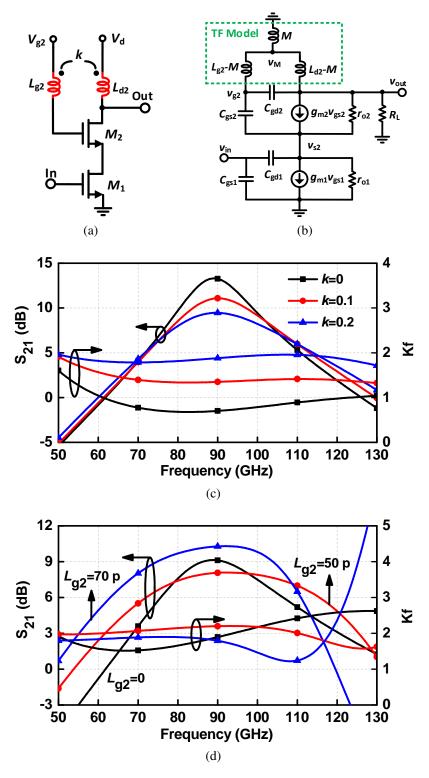

| Figure 6.7:   | (a) Cascode stage with drain-gate transformer; (b) Simplified small- signal model; (c) Simulated S <sub>21</sub> and Kf for different coupling coefficient value with |     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|               | $L_{\rm g2}$ =30 pH and $L_{\rm d2}$ =70 pH; (d) Simulated S <sub>21</sub> and Kf for different $L_{\rm g2}$ value with a coupling efficient of 0.3                   | 118 |

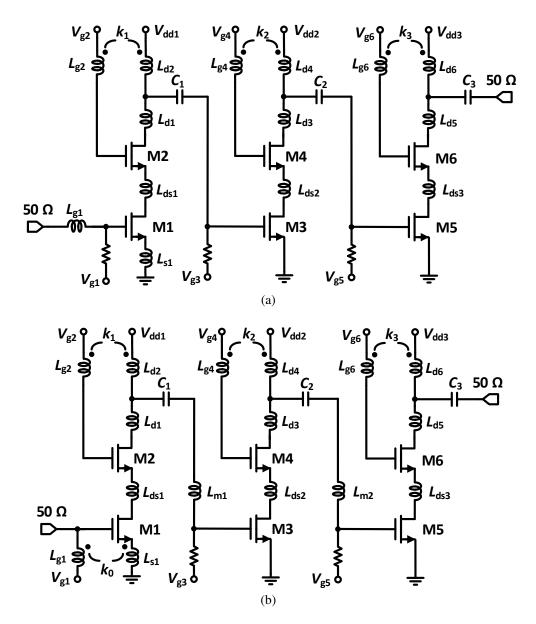

| Figure 6.8:   | Schematic of the 3-stage (a) <i>E</i> -band LNA; (b) <i>W</i> -band LNA                                                                                               | 120 |

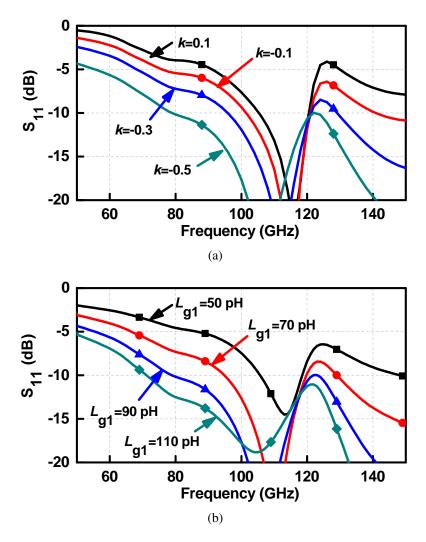

| Figure 6.9:   | Simulated input matching for the W-band LNA (a) sweep k with $L_{g1}$ =90 pH                                                                                          |     |

| $\mathcal{E}$ | and $L_{s1}$ =50 pH; (b) sweep $L_{g1}$ with $k$ =-0.5 and $L_{s1}$ =50 pH                                                                                            | 122 |

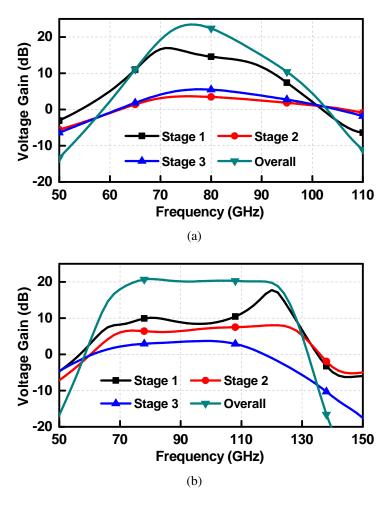

| Figure 6.10:  | Simulated voltage gain of each stage and the whole gain (a) E-band; (b)                                                                                               |     |

| C             | <i>W</i> -band                                                                                                                                                        | 123 |

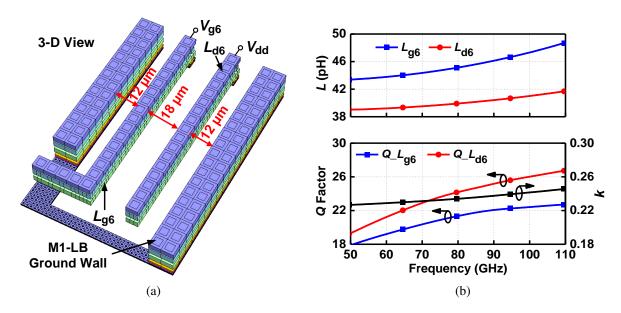

| Figure 6.11:  | (a) 3-D view of third-stage transformer of E-band LNA (metal fill is not                                                                                              |     |

|               | shown); (b) Simulated inductance, quality factor and coupling coefficient                                                                                             | 124 |

| Figure 6.12:  | Simulated effect of first stage transformer to $S_{21}$ (a) E-band LNA with $L_{\rm g2}$ =50                                                                          |     |

|               | pH; (b) W-band LNA with $L_{d2}$ =50 pH                                                                                                                               | 125 |

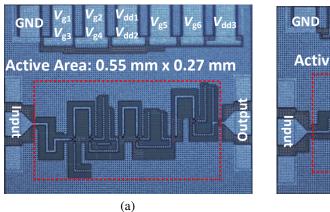

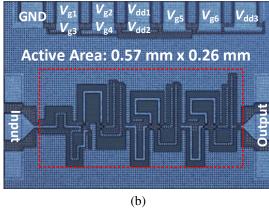

| Figure 6.13:  | Microphotograph of the (a) <i>E</i> -band LNA with a chip size of $0.7 \times 0.5 \text{ mm}^2$ ;                                                                     |     |

| _             | (b) W-band LNA with a chip size of $0.75 \times 0.58 \text{ mm}^2$                                                                                                    | 126 |

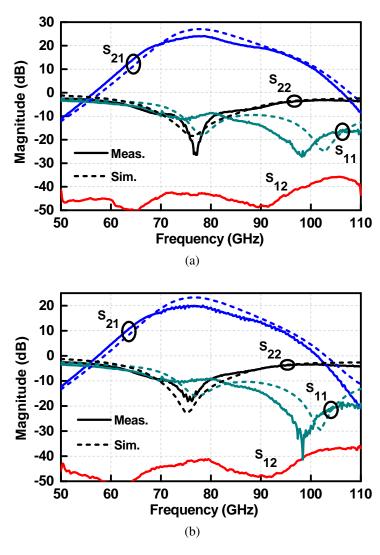

| Figure 6.14:  | Measured and simulated S-parameters of the E-band LNA with (a) 16 mW                                                                                                  |     |

|               | $P_{dc}$ ; (b) 9 mW $P_{dc}$                                                                                                                                          | 127 |

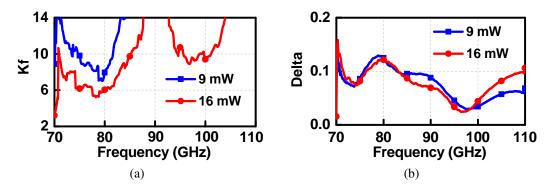

| Figure 6.15:  | Measured (a) Kf, (b) delta ( $\Delta$ ) for 16 mW and 9 mW $P_{dc}$                                                                                                   | 127 |

| Figure 6.16:  | (a) NF measurement set up; (b) Measured and simulated NF for $P_{dc}$ of 16 and 9 mW; (c) Measured and simulated output power versus input power for                  |     |

|               | P <sub>dc</sub> of 16 and 9 mW at 77 GHz                                                                                                                              | 128 |

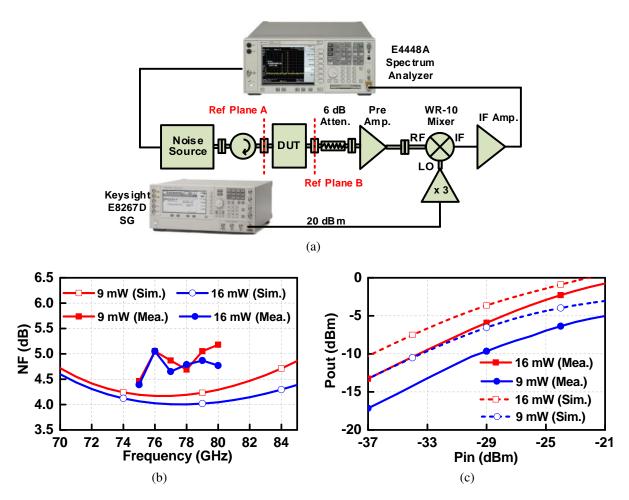

| Figure 6.17:  | (a) Measured and simulated S-parameters; (b) Measured Kf and delta; (c)                                                                                               | 120 |

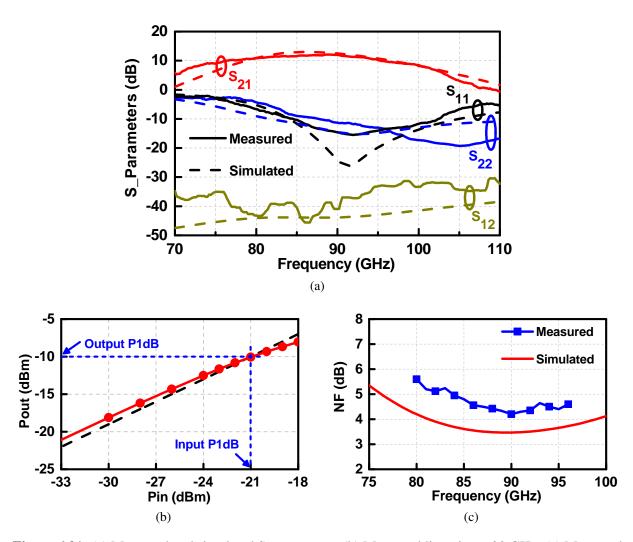

| riguic 0.17.  | Measured and simulated S-parameters, (b) Measured Rr and delta, (c)  Measured and simulated NF; (d) Measured linearity at 94 GHz                                      | 129 |

| Figure 6 18:  | (a) Cross section of GlobalFoundries 45 nm CMOS RFSOI metal back-end;                                                                                                 | 12  |

| 11gare 0.10.  | (b) Layout of a $W=20\times1$ µm transistor up to LD and C1; (c) Simulated NF <sub>min</sub>                                                                          |     |

|               | (at 90 GHz), $f_t$ , and $f_{max}$                                                                                                                                    | 131 |

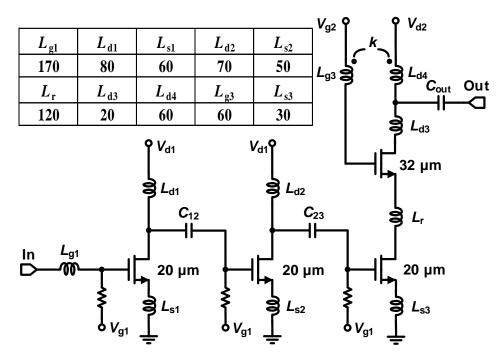

| Figure 6 19   | Schematic of the <i>W</i> -band LNA. Inductor values are in pH                                                                                                        | 132 |

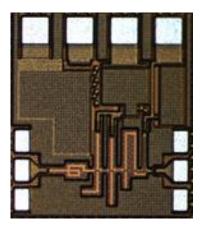

| •             | Photograph of the fabricated W-band LNA                                                                                                                               | 132 |

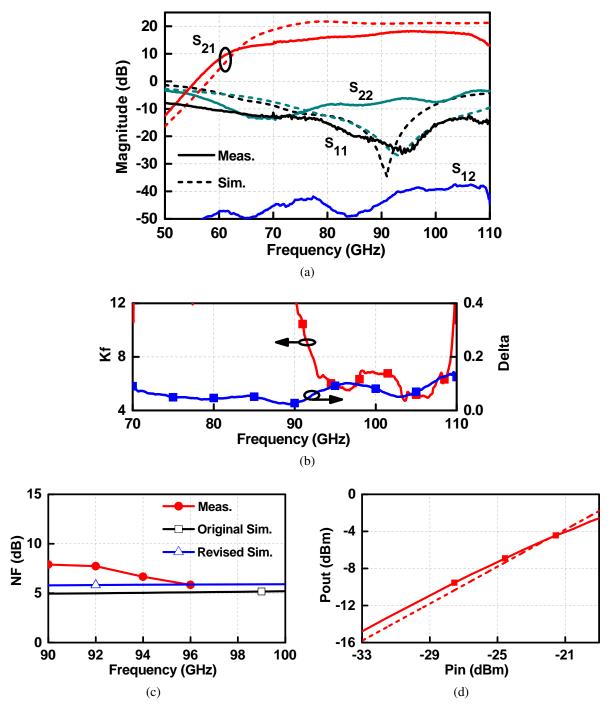

| •             | (a) Measured and simulated S-parameters; (b) Measured linearity at 90 GHz;                                                                                            | 10- |

| 118010 0.21   | (c) Measured and simulated NF                                                                                                                                         | 133 |

|               | (6)                                                                                                                                                                   |     |

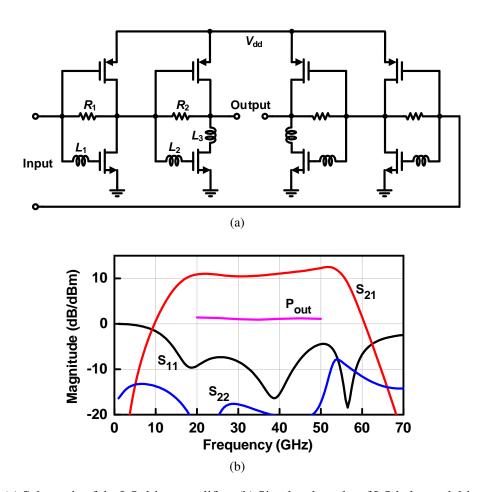

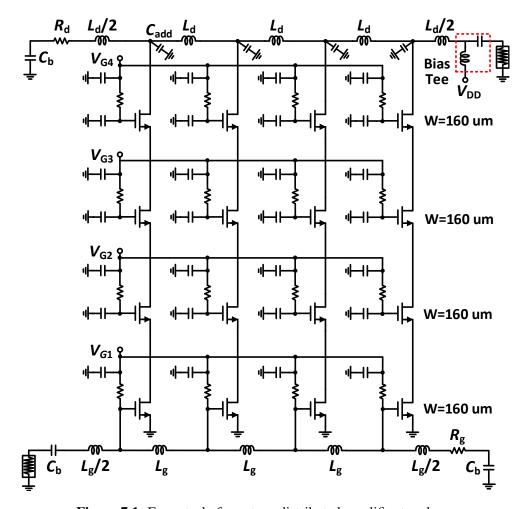

| Figure 7.1:   | Four-stack, four-stage distributed amplifier topology                                                                                                                 | 138 |

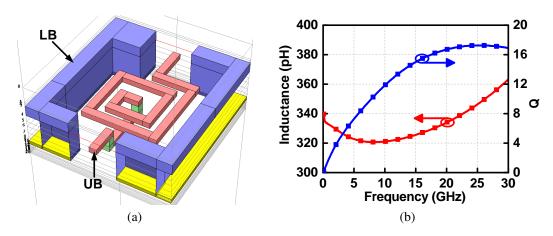

| Figure 7.2:   | (a) Structure of 330 pH inductor; (b) Simulated inductance and quality factor                                                                                         |     |

|               | (Q)                                                                                                                                                                   | 139 |

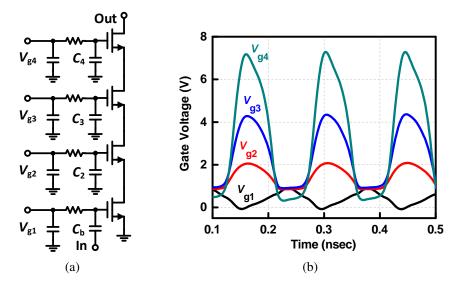

| Figure 7.3:   | (a) Structure of stacked transistors (b) Simulated gate waveforms                                                                                                     | 140 |

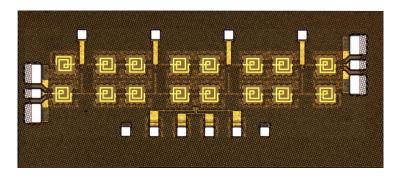

| Figure 7.4:   | Microphotograph of the distributed amplifier                                                                                                                          | 140 |

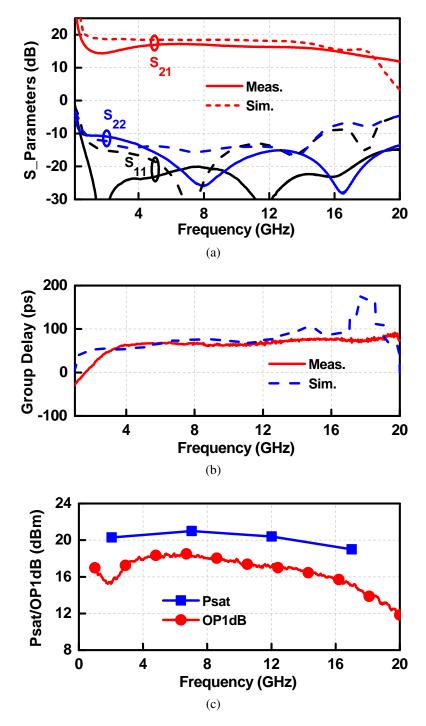

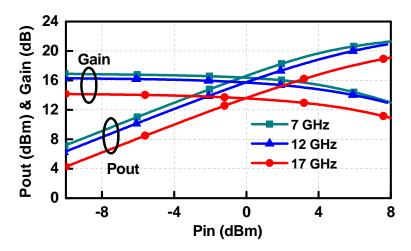

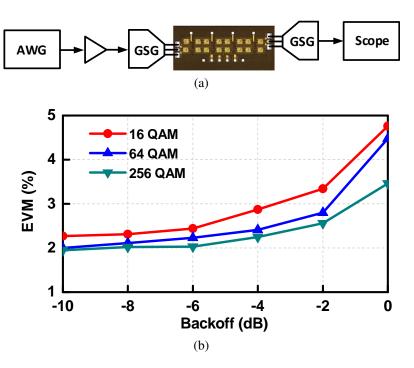

| Figure 7.5:   | Measured distributed amplifier: (a) S-parameters, (b) group delay and (c)                                                                                             |     |

|               | OP1dB and Psat                                                                                                                                                        | 141 |

| Figure 7.6:   | Measured gain and output power versus input power                                                                                                                     | 142 |

| Figure 7.7:   | (a) EVM measurement setup. (b) Measured EVM versus modulation scheme and backoff (Carrier = 4.5 GHz, Bandwidth = 2-7 GHz, Symbol Rate=5                               |     |

|               | Gbaud/s)                                                                                                                                                              | 143 |

# LIST OF TABLES

| Table 2.1: | LNA Component Values                                          | 12  |

|------------|---------------------------------------------------------------|-----|

| Table 2.2: | Comparison with State-of-the-art Wideband LNA                 | 23  |

| Table 2.3: | Comparison with Previous Wideband VGA                         | 27  |

| Table 2.4: | Comparison with State-of-the-art Wideband Beamformer Receiver | 30  |

| Table 3.1: | LNA Component Values (H or F)                                 | 37  |

| Table 3.2: | PA Component Values (H or F)                                  | 39  |

| Table 3.3: | Comparison with State-of-the-art Wideband LNA                 | 49  |

| Table 3.4: | Comparison with Wideband SPDT(Single-Ended)                   | 51  |

| Table 3.5: | Comparison with Previous Millimeter-Wave 5G Front-Ends        | 57  |

| Table 4.1: | LNA Component Values (H or F)                                 | 68  |

| Table 4.2: | LNA Harmonic-Related IM3                                      | 78  |

| Table 4.3: | LNA IIP2 with Different Frequency Scenarios                   | 79  |

| Table 4.4: | Comparison with State-of-the-art Wideband LNA                 | 80  |

| Table 4.5: | Measured Constellation with 2 GHz Bandwidth of 10 dB Backoff  | 85  |

| Table 4.6: | Comparison with Previous Wideband Receivers                   | 86  |

| Table 5.1: | LNVGA Component Values                                        | 90  |

| Table 5.2: | Comparison with Previous Wideband IQ Receivers                | 105 |

| Table 6.1: | Sheet Resistance and Routing Width for M1-C5                  | 110 |

| Table 6.2: | Parameter Value for <i>E</i> -Band LNA (Unit: pH or fF)       | 121 |

| Table 6.3: | Parameter Value for W-Band LNA (Unit: pH or fF)               | 121 |

| Table 6.4: | Comparison with Previous State-of-the-Art LNAs                | 134 |

| Table 7.1: | Comparison with Previous Distributed Amplifiers               | 143 |

#### **ACKNOWLEDGEMENTS**

First of all, I would like to express my sincerest and deepest gratitude to my supervisor Professor Gabriel M. Rebeiz for his guidance, support and encouragement. He provided me with the precious opportunity to do research in his group and let me enter the new RFIC world. Throughout the past five years, his consistent encouragement and heartfelt suggestions vitalized my persistence on the way of research. I am also thankful to Prof. Gabriel M. Rebeiz allowing me to attend conferences all over the country, expanding my knowledge of this profession and inspiring me to be exposed to many people from academia and industry and their technical experiences.

I also would like to thank my dissertation committee members, Prof. Drew Hall, Prof. Patric Mercier, Prof. Gert Cauwenberghs and Prof. William Hodgkissfor their time, interest, and valuable comments.

Besides, I must thank current TICS group members Qian Ma, Hyunchul Chung, Yaochen Wang, Abdurrahman Alijuhani, Omar Elaasar, Ahmed Nafe, Tom Phelps, Yusheng Yin, Siwei Li, Changtian Wang, Kevin Low, Zhe Zhang, Abdurrahman Alhamed and Sultan Alqarni for their technical interactions and friendship. I would also like to thank previous TICS group members, Mustafa Sayginer, Hasan Al-Rubaye, Kerim Kibaroglu, Eric Wagner, Umut Kodak, Bhaskar Rupakula and Mustafa Lokhandwala and for their help and support.

I also thank my friends in UCSD. I would not have been able to complete my studies without their encouragement, friendship, and support. My appreciation should go to Po-Han Wang, Haowei Jiang, Xiaoyang Wang, Da Ying, Xiahan Zhou, Jiannan Huang, Hui Wang, Lujiang Yan and Edwin Hsu, to name only a few.

I also would like to thank my supervisors when I was an intern in Mediatek San Jose. They provided an excellent platform for industry experience and guided me in product design. My appreciation should go to Dr. Osama Shanna, Mr. Eric Lu, Dr. Zhiming Deng and Dr. Kachun Kwok, to name only a few.

Most of all, I would like to express my sincere thanks to my family members: my parents, brother and sister for their unconditional love and support. My life and doctoral studies at UCSD would have not been ever started without their devotion.

Last and most important, I thank my beloved fiancee Qianfei Su. She accompanied me since I was an undergraduate student. Till now, it has passed ten years. During these ten years, she endured many hardships but she never gave up on me. She is the right person that I should spend all of my life to love.

The work in this dissertation was sponsored by Analog Devices, Samsung LSI, Lockheed Martin and DARPA. Also, Global Foundries provided nearly unlimited access to 45RFSOI and 22FDX which made this work possible. The material in this dissertation is based on the following papers which are either published, have been submitted for publication, or contains material that is currently being prepared for submission for publication.

Chapter 2, in full, has been accepted as it may appear in: L. Gao, and G. M. Rebeiz, "A 22-44 GHz phased-array receive beamformer in 45-nm CMOS SOI for 5G application with 3-3.6 dB NF," *IEEE Trans. Microw. Theory Techn.*, Accepted, May 2020. The dissertation author was the primary investigator and first author.

Chapter 3, in full, has been accepted as it may appear in: M. Lokhandwala, L. Gao, and G. M. Rebeiz, "A high power 24-40 GHz transmit-receive front-end for phased-arrays in 45-nm CMOS SOI," *IEEE Trans. Microw. Theory Techn.*, Accepted, Minor Revison, May 2020. The dissertation author was the second investigator and co-first author.

Chapter 4, in full, is a reprint of the material as it appears in: L. Gao, Q. Ma, and G. M. Rebeiz, "A 20-44 GHz image rejection receiver with > 75 dB image rejection ratio in 22-nm CMOS FD-SOI for 5G applications," *IEEE Trans. Microw. Theory Techn.*, Accepted. Early Access, Mar. 2020. and L. Gao, and G. M. Rebeiz, "A 24-43 GHz LNA with 3.1-3.7 dB noise figure and embedded 3-pole elliptic high-pass responses for 5G applications in 22nm FDSOI," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, pp. 239-242, Jun. 2019. The

dissertation author was the primary investigator and first author.

Chapter 5, in full, contains material that is currently being prepared for submission for publication as it may appear in: L. Gao and G. M. Rebeiz, "Design of 20-42 GHz IQ receiver in 22-nm CMOS SOI for 5G application," *IEEE Trans. Microw. Theory Techn.*, in preparation (to be submitted June 2020). The dissertation author was the primary investigator and first author.

Chapter 6, in full, is a reprint of the material as it appears in: L. Gao, E. Wagner, and G. M. Rebeiz, "Design of E- and W-band low-noise amplifiers in 22-nm CMOS FD-SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 1, pp. 132-143, Jan. 2020. and L. Gao, Q. Ma, and G. M. Rebeiz, "A 4.7 mW LNA with 4.2 dB NF and 12 dB gain using drain to gate feedback in 45nm CMOS RFSOI technology," in *IEEE Radio Frequency Integrated Circuits Symposium* (*RFIC*), pp. 280-283, Jun. 2018. The dissertation author was the primary investigator and first author.

Chapter 7, in full, is a reprint of the material as it appears in: L. Gao, Q. Ma, and G. M. Rebeiz, "A 1-17 GHz stacked distributed power amplifier with 19-21 dBm saturated output power in 45nm CMOS SOI technology," in *IEEE International Microwave Symposium (IMS)*, pp. 454-456, Jun. 2018. The dissertation author was the primary investigator and the first author.

#### **VITA**

| 2012 | B. S. in Electrical Engineering (Information Engineering), South China University of Technology, China               |

|------|----------------------------------------------------------------------------------------------------------------------|

| 2015 | M. S. in Electrical Engineering (Communication and Information Systems), South China University of Technology, China |

| 2020 | Ph. D. in Electrical Engineering (Electronics Circuits and Systems), University of California San Diego, USA         |

#### **PUBLICATIONS**

- L. Gao, and G. M. Rebeiz, "A 22-44 GHz phased-array receive beamformer in 45-nm CMOS SOI for 5G application with 3-3.6 dB NF," *IEEE Trans. Microw. Theory Techn.*, Accepted, May 2020.

- M. Lokhandwala, L. Gao, and G. M. Rebeiz, "A high power 24-40 GHz transmit-receive front-end for phased-arrays in 45-nm CMOS SOI," *IEEE Trans. Microw. Theory Techn.*, Accepted, Minor Revision. May 2020.

- L. Gao, Q. Ma, and G. M. Rebeiz, "A 20-44 GHz image rejection receiver with > 75 dB image rejection ratio in 22-nm CMOS FD-SOI for 5G applications," *IEEE Trans. Microw. Theory Techn.*, Accepted. Early Access. Mar. 2020.

- H. Jiang, P.-H. Wang, L. Gao, C. Pochet, G. M. Rebeiz, D. Hall, and P. P. Mercier, "A 22.3 nW 4.55 cm<sup>2</sup> temperature-robust wake-up receiver achieving a sensitivity of -69.5 dBm at 9 GHz," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1530-1541, Jun. 2020.

- L. Gao, E. Wagner, and G. M. Rebeiz, "Design of E- and W-band low-noise amplifiers in 22-nm CMOS FD-SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 1, pp. 132-143, Jan. 2020.

- L. Gao, T. -W. Lin, and G. M. Rebeiz, "Design of tunable multi-pole multi-zero bandpass filters and diplexer with high selectivity and isolation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 3831-3842, Oct. 2019.

- L. Gao, and G. M. Rebeiz, "A 24-43 GHz LNA with 3.1-3.7 dB noise figure and embedded 3-pole elliptic high-pass responses for 5G applications in 22nm FDSOI," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, pp. 239-242, Jun. 2019.

- L. Gao, and G. M. Rebeiz, "A 0.97-1.53 GHz tunable four-pole bandpass filter with four transmission zeros," *IEEE Microw. Wireless Compon. Lett.*, vol. 29, no. 3, pp. 195-197, Mar. 2019.

- P.- H. Wang, H. Jiang, L. Gao, P. Sen, Y. -H. Kim, G. M. Rebeiz, P. P. Mercier, and D. Hall, "A 400 MHz 4.5 nW -63.8 dBm sensitivity wake-up receiver employing an active pseudo-balun envelop detector," *IEEE European Solid-State Circuit Conference (ESSCIRC)*, pp. 35-38, Sep. 2018.

- P.- H. Wang, H. Jiang, L. Gao, P. Sen, Y. -H. Kim, G. M. Rebeiz, P. P. Mercier, and D. Hall, "A near-zero-power wake-up receiver achieving -69 dBm sensitivity," *IEEE J. Solid-State Circuits*, vol. 53, no. 6, pp. 1640-1652, Jun. 2018.

- T. -W. Lin, L. Gao, and G. M. Rebeiz, "400-560 MHz tunable 2-pole RF MEMS bandpass filter with improved stopband rejection," in *IEEE International Microwave Symposium (IMS)*, pp.510-513, Jun. 2018.

- L. Gao, T. -W. Lin, and G. M. Rebeiz, "Tunable three-pole diplexer with high selectivity and isolation," in *IEEE International Microwave Symposium (IMS)*, pp.1378-1380, Jun. 2018.

- L. Gao, Q. Ma, and G. M. Rebeiz, "A 1-17 GHz stacked distributed power amplifier with 19-21 dBm saturated output power in 45nm CMOS SOI technology," in *IEEE International Microwave Symposium (IMS)*, pp. 454-456, Jun. 2018.

- L. Gao, Q. Ma, and G. M. Rebeiz, "A 4.7 mW LNA with 4.2 dB NF and 12 dB gain using drain to gate feedback in 45nm CMOS RFSOI technology," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, pp. 280-283, Jun. 2018.

- P.- H. Wang, H. Jiang, L. Gao, P. Sen, Y. -H. Kim, G. M. Rebeiz, P. P. Mercier, and D. Hall, "A 6.1 nW wake-up receiver achieving -80.5 dBm sensitivity via a passive pseudo-balun envelop detector," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 5, pp. 134-137, May 2018.

- H. Jiang, P.- H. Wang, L. Gao, P. Sen, Y.-H. Kim, G. M. Rebeiz, D. Hall and P. P. Mercier, "A 4.5 nW wake-up radio with -69 dBm sensitivity," *IEEE International Solid-State Circuits Conference (ISSCC)*, pp. 416-417, Feb. 2017.

- L. Gao, and G. M. Rebeiz, "Design of 20-42 GHz IQ receiver in 22-nm CMOS FD-SOI for 5G application", *IEEE Trans. Microw. Theory Tech.*, in preparation (to be submitted June 2020).

#### ABSTRACT OF THE DISSERTATION

# Design of Wideband Millimeter-Wave Beamformers and Transceivers in Advanced CMOS SOI Technology

by

#### Li Gao

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2020

Professor Gabriel Rebeiz, Chair

With the development of wireless communications, high data rate is becoming essential since it not only augments the current wireless systems but also enables many emerging applications. In order to achieve multi-gigabit-per-second data rates, the fifth generation communication system (5G) is moving forward to the millimeter-wave band, such as 24-29 GHz and 37-42 GHz. Since the frequency is more than 10 times than the current communication protocols, the wavelength is 10 times smaller, which makes the transmission line effects more notable and increases the design complexity. Moreover, the path loss is much larger and therefore a higher output power or antenna EIRP (effective isotropic radiated power) is required to overcome this

loss. Previous millimeter-wave 5G research focused on narrow band, such as 28 GHz and 39 GHz. But if a single system can be wideband and include all of these bands, the simultaneous data rate can be increased and the system cost can be reduced. The research projects in this dissertation, in consequence, focus on different wideband RF ICs, and include power amplifiers (PA), low noise amplifiers (LNA), wideband phased-array receivers with high single-sideband rejection, wideband IQ receivers and wideband front-end circuits including phase-shifters and variable gain amplifiers. All of these circuits were done in advanced CMOS SOI technologies. The thesis concludes with a list of future work to be done in this area.

# **Chapter 1**

# Introduction

# 1.1 Background

Wireless communication system has been driving the connectivity speeds faster and faster. The global mobile data traffic continues to increase with a compound annual growth rate of 46%. In order to fulfill the high data-rate requirements, the fifth-generation (5G) communication has been proposed and is becoming a popular topic in the past several years. With the carrier frequency moving to the millimeter-wave band, the available bandwidth is much larger than 4G communication systems. Based on Shannon theorem, the communication channel capacity is proportional to the bandwidth and inverse proportional to signal to noise ratio (SNR). With a wider bandwidth, a higher date rate can be achieved. Compared with 4G data rate of hundreds of Mbps, the 5G data-rate can goes up to ten of Gbps, which can not only support traditional communication protocols but also allow for emerging applications, such as remote high definition video conferencing, autonomous vehicles and virtual reality.

Despite of the high data-rate advantages, there are also some obstacles. The first one arises from the transistor technology. With the frequency moving to the millimeter-wave band, the maximum available gain from the transistor decreases drastically. Also the parasitic effects

become more and more notable, which makes RFIC design harder. Fortunately, with the continuous scaling of CMOS technology, the  $f_t/f_{\rm max}$  of the CMOS transistors have been driven to higher than 250 GHz, which makes the design of millimeter-wave circuits possible.

The second one is due to the frequency choice. The space path loss factor is proportional to frequency squared. For a 200 meter communication link, the signal attenuation is 86 dB for a 2.4 GHz signal while it is 107 dB for a 28 GHz signal. The exists of atmospheric absorption and mechanical resonance in gaseous molecules further attenuate the signal strength, and limits the wireless communication distance. Therefore, a high density of base stations is required and thus the total system cost is higher than previous 4G communication networks. In order to deal with this issue, large phased-arrays are proposed. With a N×N element phased-array system, the effective isotropic radiated power (EIRP) increases by 20log(N) when compared to a single-channel transmitter. Thus, the communication distance is increased. Also, due to the over-the-air power combining, a single channel does not need to provide a high output power, thus, mitigating thermal concerns and making possible the integration of Si-based power amplifiers (PAs).

The last one comes from the design experience. The wavelength at 30 GHz is 10 mm in the free space and it is even shorter when a substrate exists. Thus, the distributed effect is remarkable, and the designer needs to pay more attention. Moreover, the device model that is provided by the foundry may be inaccurate and results in non-optimal results at mm-wave frequencies. Furthermore, the 3-D electromagnetic simulation tools for passive and active devices must be carefully used to accurately mode the integrated circuit. All of the factors complicate the design and require a higher level of attention and expertise from the designer.

Still the demand for high-data rate communication systems is a strong driving factor of implementing fully integrated mm-wave circuits. Therefore, various research and development activities are in progress both in academia and industry at different frequency ranges in the mm-wave region.

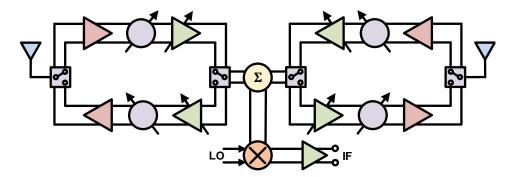

Figure 1.1: Block diagram of a beamformer phased array chip.

# 1.2 Motivation

We have fortunately witnessed the rapid development of wireless communications. And the development of RFIC also evolved into unimaginable complexity and integration. From a technology aspect, CMOS has undoubtedly been one of the most promising technologies due to its performance, low cost and the potential compatibility with baseband circuits, which is the trend for system-on-chip (SOC) solutions. In terms of circuit design, the operating frequency is moving higher and higher, the output power is becoming larger, the noise figure (NF) is becoming lower while the dc power consumption is required to remain approximately the same.

In terms of 5G millimeter-wave IC design, the Federal Communication Commission (FCC) has issued multiple frequency bands for 5G, such as 24-29 GHz and 37-42 GHz. However, most of the previous research focused on 28 GHz design in the past several years. Fig. 1.1 shows a popular phase-array beamformer and transceiver topology, which is widely used in the published literature. Various topology and design techniques are applied to optimize the performance of each block, in the 24-29 GHz band or in the 37-42 GHz band. If one handset needs to be compatible with two mm-wave bands, two sets of phase-array transceivers are needed, which greatly increases the area and cost. Therefore, if one design can include both bands and operate over a very wide bandwidth while maintaining similar performance, then the area and cost can be greatly reduced. The aim of this thesis is to pave the way for the design wideband

beamformers and transceivers for 5G millimeter-wave communication circuits.

# 1.3 Thesis Overview

This thesis presents fully integrated mm-wave circuits for high performance transceiver circuits and systems in advanced CMOS SOI technology.

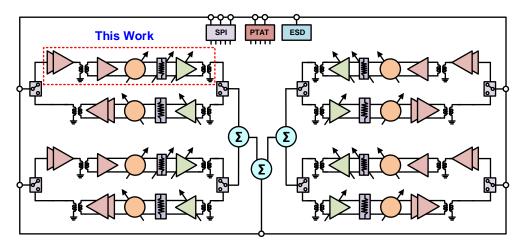

Chapter 2 presents a 22-44 GHz phased-array beamformer in the GlobalFoundries (GF) 45-nm CMOS SOI. The channel includes a wideband single-ended to differential low-noise amplifier (LNA), a 5-bit vector modulator (VM) phase shifter with a measured rms error of < 6°, an attenuator and a variable gain amplifier (VGA) with 16 dB of gain control. The phased-array channel results in a peak gain of 26.3 dB and a 3-dB bandwidth of 20.5-44 GHz. The measured NF is 3-3.6 dB at 22-44 GHz with an IP1dB of -27.5 to -24.5 dBm, and a dc power consumption of 112 mW.

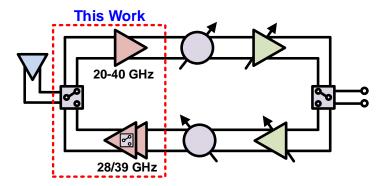

Chapter 3 presents a wideband millimeter-wave front end in 45 nm CMOS SOI for 5G applications. The front-end is composed of a low noise amplifier (LNA), power amplifier (PA) and a single-pole double-throw switch (SPDT). A double-tuned PA is used, and is based a two-stage stacked-amplifier with a reconfigurable load using SOI switches, so as to achieve an optimal load for both 5G frequencies. A wideband series-shunt switch is also developed with high power handling (P1dB > 23 dBm), and < 1 dB insertion loss at 20-40 GHz. In the receive mode, the front-end has a measured peak gain of 19.3 dB with a 3-dB bandwidth of 19.7-40 GHz, a noise figure (NF) < 4 dB at 18-40 GHz and an IP1dB of -19 to -16 dBm. In the transmit mode, and for low-band operation, the peak gain is 17.6 dB with a 3-dB bandwidth of 22.7-30.8 GHz. The Psat is > 18.8 dBm and the peak PAE is 18% at 24-30 GHz, and include the switch loss and compression. For high-band operation, the gain at 36-40 GHz is 13.6±1.5 dB with Psat > 18 dBm. To the author's knowledge, this is the first front-end that covers both the 24-28 GHz and 37-40 GHz 5G bands with high output power and low noise figure. Application areas are in

multi-standard base-stations and small-cells.

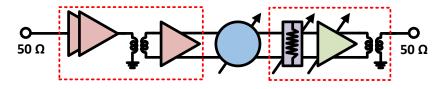

Chapter 4 presents presents a 20-44 GHz image-rejection receiver in 22-nm CMOS FD-SOI. The receiver includes a wideband LNA with a 3-pole high-pass rejection filter coupled to a double-balanced mixer with a wideband LO driver and an IF amplifier. At an intermediate frequency (IF) of 16 GHz, the image band at DC-12 GHz is filtered by the LNA response and is greater than 75 dB over the entire 20-44 GHz range. The receiver results in a gain of 24-28.5 dB and a NF of 3.3-5 dB at 20-44 GHz and achieves a EVM of 3.6-3.7% at the carrier frequency of 28 GHz and 39 GHz with 2 Gbaud symbol rate at 64QAM waveform.

Chapter 5 presents a 20-42 GHz IQ receiver in 22-nm CMOS FD-SOI. The receiver includes a wideband low noise variable gain amplifier (LNVGA), double-balance IQ mixers, a wideband IQ generation network and wideband LO driver, lowpass filters and IF amplifiers. The measured receiver has a peak conversion gain of 22.3 dB with 3-dB bandwidth of 19.8-42 GHz, which covers the whole 5G millimeter-wave band. The measured single sideband NF is 5.2-7 dB and IP1dB is -26 to -23 dBm. The conversion gain can be adjusted by 8 dB and the IP1dB is improved by 5 dB and NF just degrades by 1.2 dB. The gain mismatch between I and Q channel is smaller than 0.6 dB at 20 to 42 GHz. The phase mismatch is smaller than 5°at 28-42 GHz.

Chapter 6 first presents *E*- and *W*-band low noise amplifiers (LNA) in GlobalFoundries 22-nm CMOS FD-SOI (fully depleted silicon-on-insulator). Both amplifiers employ a three-stage cascode design with gain-boosting transformer loads. Design procedures are presented for E-and W-band LNAs for narrowband and wideband applications. The *E*-band LNA focuses on a high-gain, low-power implementation, and results in a gain and noise figure (NF) of 20 dB and 4.6 dB at 77 GHz with a 3-dB bandwidth of 12 GHz, and an input P1dB of -27.4 dBm, for a power consumption of 9 mW. The *W*-band LNA focuses on wideband applications, and results in a peak gain of 18.2 dB with a 3-dB bandwidth of 31 GHz, for a power consumption of 16 mW. The LNAs have a high figure-of-merit (FoM) and show very low power operation in the 70-100 GHz range. After the LNAs in GF 22-nm SOI, another *W*-band LNA with low power

consumption in GF 45-nm CMOS SOI is presented. The LNA has a measured gain is > 10 dB at 80-95 GHz with a peak of 12 dB at 90 GHz. The measured noise figure (NF) is < 4.9 dB at 85-95 GHz with minimum of 4.2 dB at 90 GHz. This is achieved with a total power consumption of 4.7 mW.

Chapter 7 presents a uniform distributed amplifier (DA) based on 45nm CMOS SOI. Four stacked transistors are employed in a single arm to construct a four-stage DA. The wideband distributed amplifier results in a measured maximum gain of 17.1 dB with a 3-dB small-signal bandwidth of 1-17 GHz. The saturated output power is 19 - 21 dBm at 1-17 GHz, with a peak power-added efficiency (PAE) is 12.2-19%. The DA consumes 97 mA from a 4.4 V supply.

Chapter 8 summarizes this dissertation and discusses future works.

# Chapter 2

# A 22-44 GHz Phased-Array Receive Beamformer in 45-nm CMOS SOI for 5G Applications with 3-3.6 dB NF

# 2.1 Introduction

Millimeter-wave 5G phased-arrays is an active area of development and results in communication links with increased date-rate between the base-station and the user. Phased-arrays with high antenna gain and high effective isotropic radiated power (EIRP) are commonly used, both at the base-station and the customer premise equipment (CPE) cites to combat the high path loss at millimeter-waves and increased atmospheric attenuation. The 24-29 GHz and 37-43 GHz bands are now approved worldwide as the standard 5G communication bands, and several 5G systems have been presented in the 28 GHz and 39 GHz bands [1–12].

Phased-array design is now based on the all-RF architecture at the antenna level, where gain and phase control on each channel is done in the RF domain (Fig. 2.1). In order to grow the array to a large number of antenna elements, the beamformer chips have an all-RF design

**Figure 2.1**: Block diagram of a wideband  $2 \times 2$  beamformer chip.

(RF-in/RF-out, 2x2 quad-core, or 8 or 16-elements on the same chip) and a millimeter-wave Wilkinson network is used on the printed-circuit board (PCB) to add the signals from the antennas. A single transceiver and a high-Q filter are then placed at the sum point for up/down-conversion and to filter out the mixer harmonics (TX mode) and interferers (RX mode). In [1–12], various RF beamformers and phased-arrays have been demonstrated, but they are usually narrowband, centered either at 28 GHz or at 39 GHz.

In this chapter, a wideband phased-array beamformer receive channel is proposed and covers the entire 5G millimeter-wave band (22-44 GHz) (Fig. 2.1). There are several challenges to wideband phased-arrays: 1) wideband antenna and array design, 2) wideband and efficient transmit channel with a low-loss Tx/Rx switch, 3) wideband receive channel with low noise and high linearity, and 4) a wideband transceiver with filtering of spurious harmonics. The goal is to eliminate the need of building two phased-arrays, one at 24-29 GHz and one at 37-42 GHz, which results in increased area and cost.

The phased-array receive channel results in a peak gain of 26.3 dB and a 3-dB bandwidth of 20.5-44 GHz. The measured NF is 3-3.6 dB at 22-44 GHz with an IP1dB of -27.5 to -24.5 dBm, and a dc power consumption of 112 mW. This is the first wideband phased-array beamformer which covers the entire millimeter-wave 5G band.

# 2.2 Block Design

Fig. 2.1 presents the block diagram of a wideband 2x2 beamformer chip. This work focuses on the receive beamformer channel, and is well known, the wideband phase shifter and VGA can also be re-used in the transmit channel.

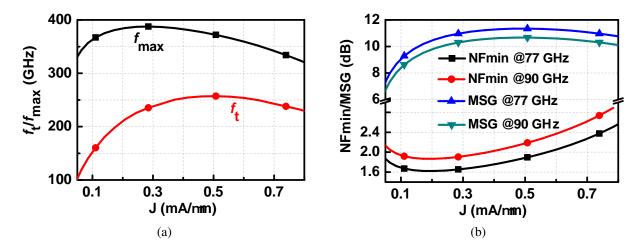

The GlobalFoundries 45-nm RF-SOI process is used and provides 7 layers of copper and one aluminum top-layer [13]. In this technology, the SOI transistors are built in a buried oxide layer that isolates the active device from the  $2.5 \text{ k}\Omega$ -cm resistivity substrate. The high resistivity also results in an inductor Q is at 20-25 at 30 GHz, one of the highest in any process. A floating-body transistor is used with a measured  $f_t/f_{\text{max}}$  of 250/310 GHz, including all connections to the top metal, at a current density of 0.4-0.5 mA/ $\mu$ m [14]. The current density (J) for lowest NF<sub>min</sub> is 0.1-0.2 mA/ $\mu$ m.

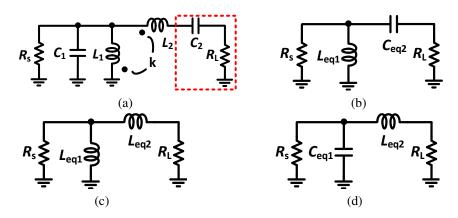

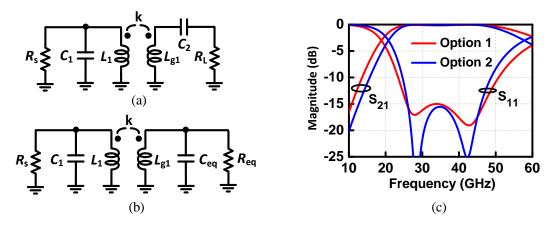

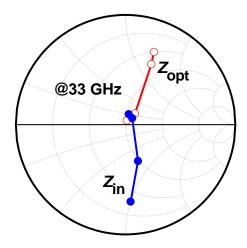

# 2.2.1 Wideband Input and Output Matching Network

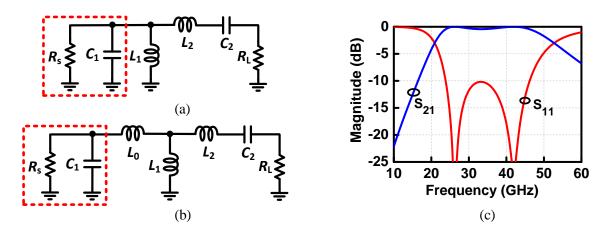

A common-source amplifier is used at the wideband beamformer input for low-noise performance, and in order to realize wideband matching and avoid NF degradation, a two-pole matching is employed. The first solution is shown in Fig. 2.2a, where  $R_L = g_m L_s/C_{gs}$  and  $C_2$  is the series effect of  $L_s$  and  $C_{gs}$ , and results in a shunt-series resonant matching network. For example, a transistor with  $g_m = 40$  ms,  $L_s = 70$  pH and  $C_{gs} = 80$  fF results in  $R_L = 35$   $\Omega$ . Assuming that k = 0 for simplified analysis, and  $L_1/C_1$  and  $L_2/C_2$  having resonant frequencies of  $f_1$  and  $f_2$ , respectively (note that, in general,  $f_2 < f_1$ ). When  $f < f_2$ , the circuit is shown in Fig. 2.2b where  $L_1/C_1$  is now equivalent to  $L_{eq1}$  and  $L_2/C_2$  is equivalent to  $C_{eq2}$ , and this network can transform  $R_L$  (<50  $\Omega$ ) to  $R_s$  (50  $\Omega$ ). When  $f_2 < f < f_1$ , the circuit cannot transform  $R_L$  to  $R_s$  perfectly and results in degraded matching (Fig. 2.2c). When  $f > f_1$ , the circuit can transform  $R_L$  to  $R_s$  again (Fig. 2.2d). Therefore, this circuit realizes a wideband two-pole matching network, and solutions with  $k_0$  can be used to tune the two inductor values.

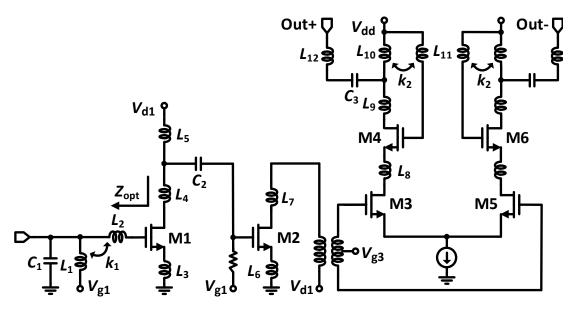

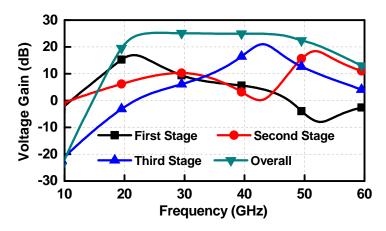

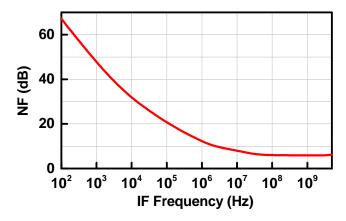

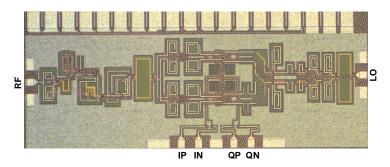

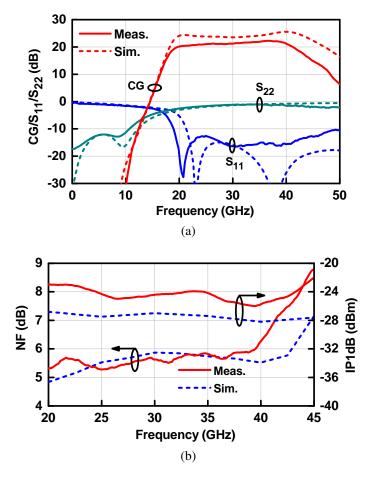

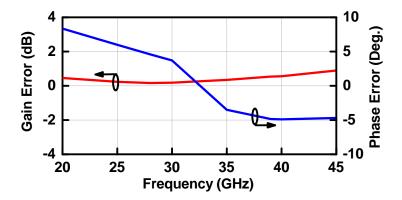

**Figure 2.2**: (a) Option 1 for a two-stage matching network; Equivalent circuit for (b)  $f < f_2$ , (c)  $f_2 < f < f_1$ , (d)  $f > f_1$ .