# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Hardware Development for Non-Hardware Engineers

#### **Permalink**

https://escholarship.org/uc/item/7r89f4gx

#### **Author**

Richmond, Dustin Alexander

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

Hardware Development for Non-Hardware Engineers

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

**Dustin Alexander Richmond**

#### Committee in charge:

Professor Ryan Kastner, Chair Professor Sorin Lerner Professor Trong Nguyen Professor Leonard Porter Professor Steven Swanson

Copyright

Dustin Alexander Richmond, 2018

All rights reserved.

| The Dissertation of Dustin Alexander Richmond is approved and is acceptable in |

|--------------------------------------------------------------------------------|

| quality and form for publication on microfilm and electronically:              |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

| Chair                                                                          |

University of California San Diego 2018

# DEDICATION

This work is dedicated to my parents who have always provided the support I've needed, even when (I thought) I didn't want it.

# **EPIGRAPH**

The ships hung in the sky in much the same way that bricks don't  $Douglas\ Adams$

# TABLE OF CONTENTS

| Signatur                        | e Page                 | ii                         |

|---------------------------------|------------------------|----------------------------|

| Dedicati                        | on                     | į۷                         |

| Epigrapl                        | l                      | ١                          |

| Table of                        | Contents               | V                          |

| List of F                       | igures                 | ix                         |

| List of T                       | ables                  | xi.                        |

| Acknow                          | edgements              | X١                         |

| Vita                            | x                      | V                          |

| Abstract                        | of the Dissertation xv | ii                         |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | 1 Introduction         | 1<br>3<br>4<br>5<br>7<br>8 |

| Chapter                         |                        | 1.                         |

| 2.1                             |                        | 10                         |

| 2.1<br>2.2                      |                        | 10<br>13                   |

| 2.2                             |                        | 15                         |

|                                 |                        | 18<br>18                   |

|                                 |                        | 21                         |

| 2.3                             | <u>C</u>               | 23                         |

| 2.3                             |                        | 2-<br>2-                   |

|                                 |                        | 2<br>32                    |

| 2.4                             |                        | 35                         |

|                                 |                        | 40                         |

|                                 |                        | 41                         |

|                                 |                        | 41                         |

| 2.5                             | e                      | 43                         |

| 2.6                             |                        | 44                         |

| CI.                             |                        | 4.                         |

| Chapter                         |                        | 45<br>45                   |

| 5.1                             | Introduction           | +.                         |

| 3.2     | Building Higher-Order Functions                              | 47 |

|---------|--------------------------------------------------------------|----|

|         | 3.2.1 Templates (Parametric Polymorphism)                    | 48 |

|         | 3.2.2 Arrays                                                 | 54 |

|         | 3.2.3 Recursion and Looping                                  | 55 |

|         | 3.2.4 Higher-Order Functions                                 | 56 |

| 3.3     | Examples                                                     | 57 |

|         | 3.3.1 Interleave                                             | 59 |

|         | 3.3.2 Bit-Reverse                                            | 60 |

|         | 3.3.3 N-Point FFT Stage                                      | 60 |

|         | 3.3.4 Fast Fourier Transform                                 | 6  |

| 3.4     | Results                                                      | 62 |

|         | 3.4.1 Application Kernels                                    | 62 |

|         | 3.4.2 Experimental Setup                                     | 64 |

|         | 3.4.3 Analysis                                               | 65 |

| 3.5     | Related Work                                                 | 67 |

|         | 3.5.1 Hardware Development Languages                         | 67 |

|         | 3.5.2 High-Level Synthesis Languages                         | 68 |

|         | 3.5.3 Domain-Specific Languages                              | 69 |

|         | 3.5.4 Our Work                                               | 69 |

| 3.6     | Conclusion                                                   | 70 |

| 3.7     | Acknolwedgements                                             | 70 |

|         |                                                              |    |

| Chapter |                                                              | 72 |

| 4.1     | Introduction                                                 | 72 |

| 4.2     | Units                                                        | 75 |

|         | 4.2.1 Real-Time IO Unit                                      | 75 |

|         | 4.2.2 Streaming Communication Unit                           | 76 |

|         | 4.2.3 Shared Memory Communication                            | 77 |

| 4.3     | Unit Structure                                               | 77 |

|         | 4.3.1 Demonstration Notebook and Verified Overlay            | 79 |

|         | 4.3.2 Introduction                                           | 79 |

|         | 4.3.3 Creating a Vivado HLS IP Core                          | 80 |

|         | 4.3.4 Building a Bitstream                                   | 80 |

|         | 4.3.5 Overlays and Bitstreams in PYNQ                        | 81 |

|         | 4.3.6 Packaging an Overlay for Distribution                  | 82 |

| 4.4     | Related Work                                                 | 82 |

|         | 4.4.1 Embedded Projects Using FPGA SoCs                      | 83 |

|         | 4.4.2 Related Tools                                          | 83 |

| 4.5     | Conclusion                                                   | 84 |

| 4.6     | Acknolwedgements                                             | 84 |

| Chapter | 5 Everyone's a Critic: A Tool for Evaluating RISC-V Projects | 85 |

| 5.1     | Introduction                                                 | 85 |

| 5.1     | A RISC-V Soft-Processor Evaluation Tool                      | 88 |

|          | 5.2.1   | Hardware Infrastructure               | 89  |

|----------|---------|---------------------------------------|-----|

|          | 5.2.2   | Development Environment               | 90  |

|          | 5.2.3   | Tutorial                              | 92  |

| 5.3      | Results |                                       | 95  |

|          | 5.3.1   | Projects                              | 95  |

|          | 5.3.2   | Compilation Results                   | 98  |

|          | 5.3.3   | ISA Tests                             | 99  |

|          | 5.3.4   | Dhrystone Benchmark                   | 100 |

|          | 5.3.5   | Experience                            | 103 |

| 5.4      | Related | l Work                                | 104 |

| 5.5      | Conclu  | sion                                  | 106 |

| 5.6      | Acknol  | wedgements                            | 106 |

|          |         |                                       |     |

| Chapter  |         | General-Purpose Pipeline Architecture | 107 |

| 6.1      |         | ction                                 | 107 |

| 6.2      | _       | ound                                  | 109 |

|          | 6.2.1   | Inefficiencies in Modern Processor    | 111 |

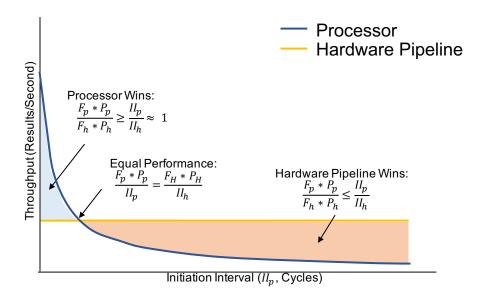

|          | 6.2.2   | The Benefits of Pipelines             | 112 |

|          | 6.2.3   | Processors Versus Pipelines           | 113 |

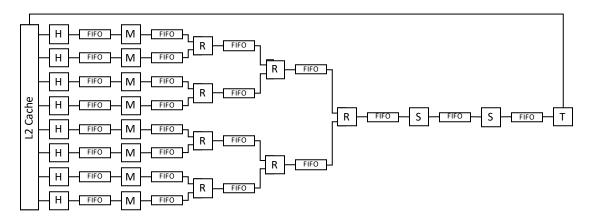

| 6.3      | Propos  | ed Architecture                       | 115 |

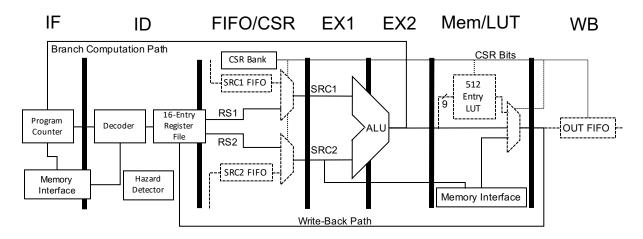

|          | 6.3.1   | RISC-V Implementation                 | 116 |

|          | 6.3.2   | Extensions                            | 117 |

|          | 6.3.3   | Processor Variants                    | 123 |

|          | 6.3.4   | Area Estimate                         | 128 |

| 6.4      | Results |                                       | 130 |

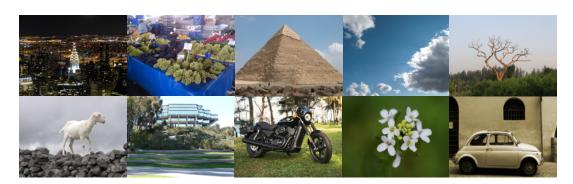

|          | 6.4.1   | Experimental Setup                    | 130 |

|          | 6.4.2   | OpenCV Functions                      | 134 |

|          | 6.4.3   | Results                               | 140 |

|          | 6.4.4   | Analysis                              | 145 |

| 6.5      | Related | l Work                                | 146 |

| 6.6      | Conclu  | sion                                  | 146 |

| 6.7      | Acknol  | wedgements                            | 146 |

| Bibliogr | aphy    |                                       | 148 |

# LIST OF FIGURES

| Figure 2.1.  | RIFFA 2.2 software example in C                                                               | 17 |

|--------------|-----------------------------------------------------------------------------------------------|----|

| Figure 2.2.  | RIFFA 2.2 hardware example in Verilog                                                         | 21 |

| Figure 2.3.  | RIFFA architecture in RIFFA 2.2                                                               | 23 |

| Figure 2.4.  | Classic Engine Layer Architecture RIFFA 2.2                                                   | 26 |

| Figure 2.5.  | Reordering Queue operation for a 128 bit wide bus                                             | 29 |

| Figure 2.6.  | Translation Layer for RIFFA 2.2                                                               | 30 |

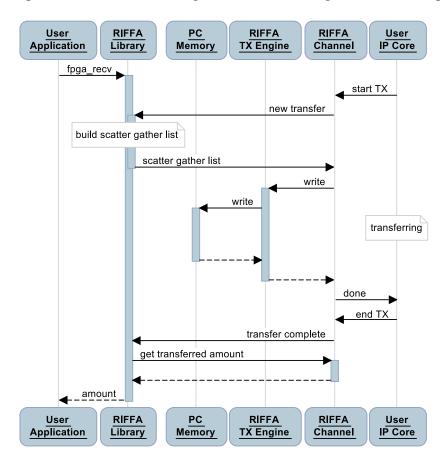

| Figure 2.7.  | Upstream transfer sequence diagram                                                            | 33 |

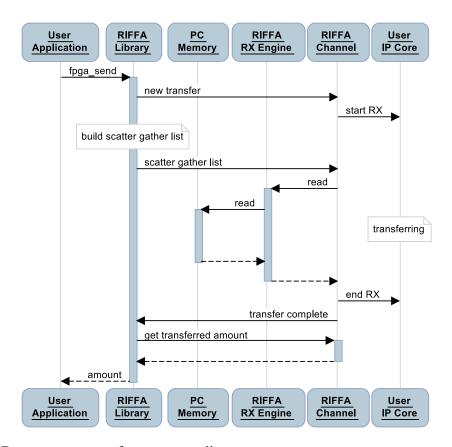

| Figure 2.8.  | Downstream transfer sequence diagram                                                          | 35 |

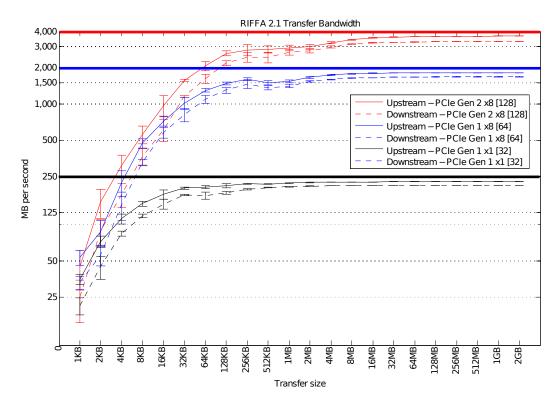

| Figure 2.9.  | Transfer bandwidths as a function of transfer size for several FPGA PCIe link configurations  | 38 |

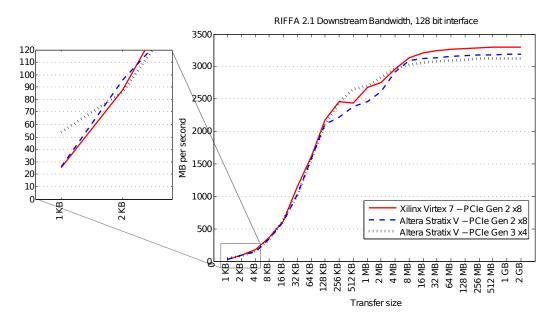

| Figure 2.10. | Downstream bandwidths as a function of transfer size for Altera and Xilinx devices.           | 39 |

| Figure 3.1.  | Higher-order functions in Python and C++                                                      | 46 |

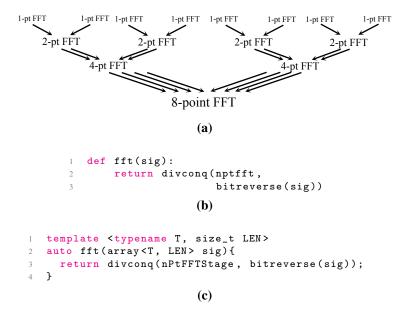

| Figure 3.2.  | A Fast Fourier Transform three ways: Graphically, in Python and in C++ .                      | 47 |

| Figure 3.3.  | (a) Three parameterized instances of the STL array class. (b) Defining a templated class foo. | 49 |

| Figure 3.4.  | Two templated functions: add and arrayfn                                                      | 50 |

| Figure 3.5.  | A C++ function passed as a template parameter                                                 | 51 |

| Figure 3.6.  | Wrapping a function inside of a struct                                                        | 52 |

| Figure 3.7.  | Class-wrapped-functions can be inferred by passing them as instances at the callsites.        | 53 |

| Figure 3.8.  | Applying the new auto keyword to Figure 3.7 allows us to remove the template parameter TO     | 53 |

| Figure 3.9.  | A variety of array constructors and manipulations                                             | 54 |

| Figure 3.10. | Using the recursive array-sum from Figure 3.11                                                | 55 |

| Figure 3.11. | An array-summation implementation using recursive class templates                                             | 55  |

|--------------|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.12. | Implementation of the function reduce using all of the features described in this section.                    | 56  |

| Figure 3.13. | Array summation from Figure 3.10 re-written using reduce defined in Figure 3.12                               | 57  |

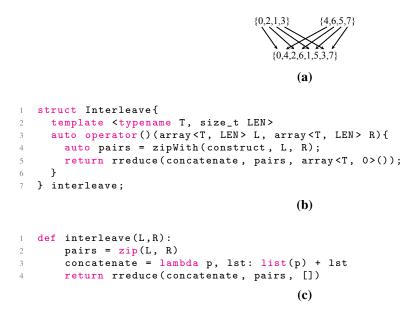

| Figure 3.14. | (a) Interleaving two lists graphically (b) Interleaving two lists in C++ (c) Interleaving two lists in Python | 59  |

| Figure 3.15. | (a) Bit-reverse permutation of a list graphically (b) Bit-reverse in C++ (c) Bit-reverse in Python            | 60  |

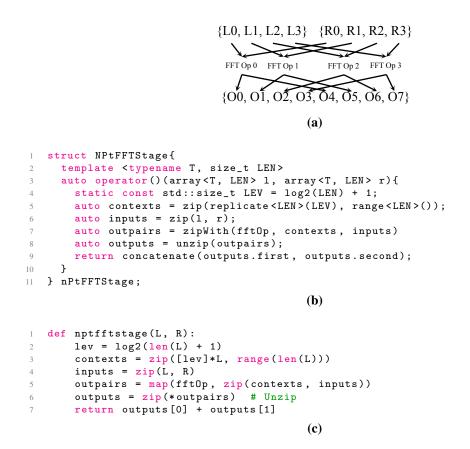

| Figure 3.16. | (b) N-Point FFT Stage using synthesizable higher-order functions (c) N-Point FFT Stage using Python           | 61  |

| Figure 3.17. | FFT Implementation using the functions described in this section                                              | 62  |

| Figure 4.1.  | High-level flow for our PYNQ labs                                                                             | 73  |

| Figure 4.2.  | A cell from the demo notebook showing how the 9-tap 1-dimensional filter can be applied to images.            | 74  |

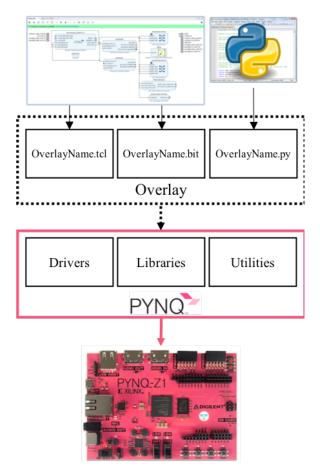

| Figure 4.3.  | The PYNQ flow                                                                                                 | 78  |

| Figure 4.4.  | A Vivado Block Diagram from the Real-Time IO lab showing the AXI Interface connections.                       | 80  |

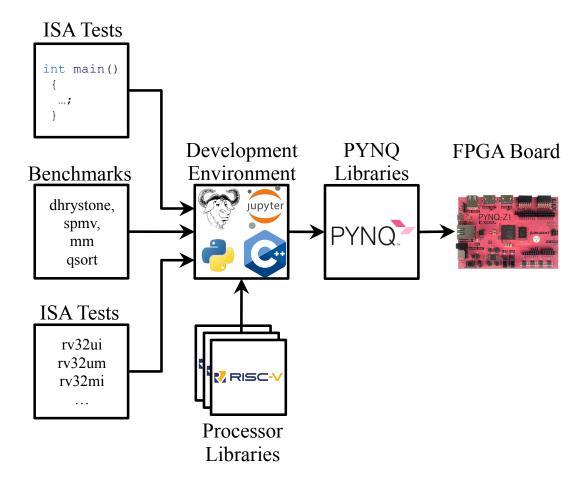

| Figure 5.1.  | Overview of the work presented in this chapter                                                                | 86  |

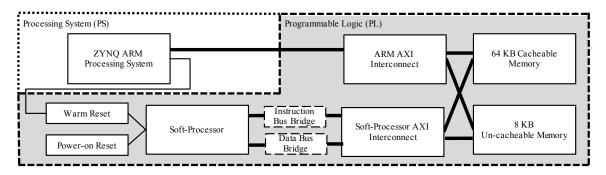

| Figure 5.2.  | A block diagram of the soft processor evauation infrastructure                                                | 88  |

| Figure 5.3.  | Our development environment                                                                                   | 91  |

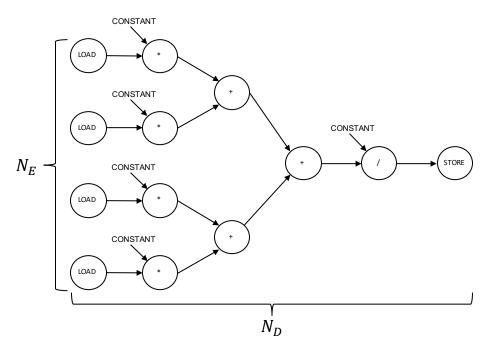

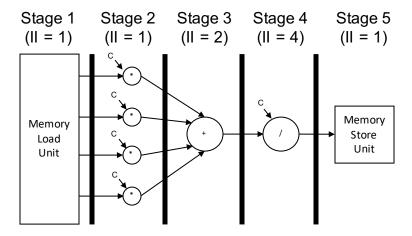

| Figure 6.1.  | A simple Data-Flow Graph                                                                                      | 109 |

| Figure 6.2.  | A compiled instruction sequence                                                                               | 110 |

| Figure 6.3.  | A compiled instruction sequence with Fused-Multiply-Add instructions                                          | 110 |

| Figure 6.4.  | A compiled instruction sequence with vectorized instructions                                                  | 111 |

| Figure 6.5.  | A pipeline implementing the data-flow graph in Figure 6.1                                                     | 113 |

| Figure 6.6.  | Performance curves for Processors and Hardware Pipelines                                                      | 114 |

| Figure 6.7.  | Our proposed multi-processor architecture                                                                                           | 115 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.8.  | Our proposed RISC-V architecture                                                                                                    | 116 |

| Figure 6.9.  | A sequence of Input FIFO Operations                                                                                                 | 120 |

| Figure 6.10. | A sequence of Output FIFO Operations                                                                                                | 121 |

| Figure 6.11. | A sequence of simultaneous Input and Output FIFO Operations                                                                         | 121 |

| Figure 6.12. | A sequence of instructions using min and max                                                                                        | 122 |

| Figure 6.13. | A sequence of instructions demonstrating the Look-Up-Table                                                                          | 123 |

| Figure 6.14. | An example demonstrating 1b instructions and OUT FIFO on the Head processor                                                         | 125 |

| Figure 6.15. | An example demonstrating the SRC1 and OUT FIFO extensions on the Map processor                                                      | 126 |

| Figure 6.16. | An example demonstrating how the Reduce processor can add two values from SRC1 FIFO and SRC2 FIFO, and write the result to OUT FIFO | 127 |

| Figure 6.17. | An example demonstrating the use of SRC2 FIFO on the Tail processor                                                                 | 128 |

| Figure 6.18. | Test images used in our experiments                                                                                                 | 131 |

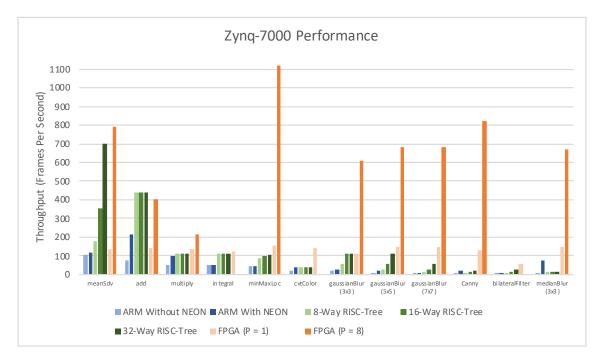

| Figure 6.19. | Throughput results for 12 OpenCV Functions on a Zynq-7000 device. The horizontal axis is sorted by the ARM Without Neon Result      | 141 |

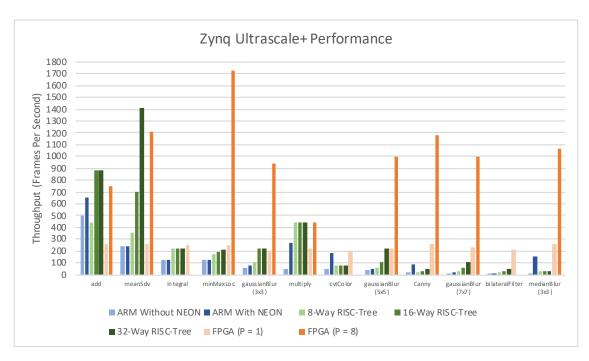

| Figure 6.20. | Throughput results for 12 OpenCV Functions on a Zynq Ultrascale+ Chip.                                                              | 144 |

# LIST OF TABLES

| Table 2.1. | RIFFA 2.2 software API (C/C++)                                                                                                            | 16  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. | RIFFA 2.2 hardware interface                                                                                                              | 19  |

| Table 2.3. | RIFFA 2 maximum achieved bandwidths, link utilization, and normalized link utilization for upstream (Up) and downstream (Down) directions | 36  |

| Table 2.4. | RIFFA latencies.                                                                                                                          | 37  |

| Table 2.5. | RIFFA 2 resource utilization on Xilinx devices                                                                                            | 41  |

| Table 2.6. | RIFFA 2 resource utilization on Altera devices                                                                                            | 41  |

| Table 3.1. | Summary of the list-manipulation and higher-order functions used in this paper. FN is shorthand for a wrapped function from Section 3.2.4 | 58  |

| Table 3.2. | Post-Implementation resource utilization for six algorithms on a PYNQ (XC7Z020) in Vivado 2017.4.                                         | 64  |

| Table 3.3. | Performance results from Vivado HLS 2017.4 for six application kernels on 16-element lists                                                | 65  |

| Table 3.4. | Maximum frequency statistics from 13 implementation runs of Vivado 2017.4                                                                 | 67  |

| Table 3.5. | <i>p</i> -values and H-B rejection thresholds from a permutation test with the null hypothesis of equal means                             | 67  |

| Table 5.1. | Project summary of selected soft-processor projects                                                                                       | 92  |

| Table 5.2. | Architectural feature summary of selected soft-processor projects                                                                         | 92  |

| Table 5.3. | Soft-Processor $F_{Max}$ (MHz) and Resources Consumed                                                                                     | 96  |

| Table 5.4. | RISC-V ISA Test Results for surveyed processors. Results are reported as: (Pass — Fail — Unknown)                                         | 100 |

| Table 5.5. | Implementations of RISC-V Performance Counters                                                                                            | 101 |

| Table 5.6. | Dhrystone Benchmark Results for RISC-V and Microblaze at 50 MHz                                                                           | 102 |

| Table 6.1. | Standard RISC-V Configuration Status Registers (CSR) used in our work                                                                     | 117 |

| Table 6.2. | CSR fifoctrl bit map                                                                                                                      | 118 |

| Table 6.3. | FIFO read instructions added by SRC1 and SRC2 Extensions                                                                                  | 119 |

| Table 6.4.  | Instructions added by the OUT extension                                                                                | 120 |

|-------------|------------------------------------------------------------------------------------------------------------------------|-----|

| Table 6.5.  | min and max instructions added by the Min/Max extension                                                                | 122 |

| Table 6.6.  | Definition of the lutwr instruction                                                                                    | 123 |

| Table 6.7.  | Summary of the features of each processor in Figure 6.7                                                                | 124 |

| Table 6.8.  | Estimated DSP and BRAM consumption for all processor types                                                             | 129 |

| Table 6.9.  | Processor counts for six architecture sizes, from 2 Head processors ( $N_H = 2$ ) to 64 Head processors ( $N_H = 64$ ) | 129 |

| Table 6.10. | Estimated DSP and BRAM resource consumption for 6 architecture sizes .                                                 | 130 |

| Table 6.11. | Device resources and maximum frequencies for Zynq-7000 and Zynq Ultra-scale+                                           | 131 |

| Table 6.12. | Compilation Results for our 12 selected OpenCV Functions on Zynq-7000 and Zynq Ultrascale+ devices.                    | 132 |

| Table 6.13. | Breakdown of images passes to compute the function meanStdDev on different sizes of our architecture                   | 135 |

| Table 6.14. | Breakdown of images passes to compute the function minMaxLoc on different sizes of our architecture                    | 135 |

| Table 6.15. | Breakdown of images passes to compute the function add on different sizes of our architecture                          | 136 |

| Table 6.16. | Breakdown of images passes to compute the function multiply on different sizes of our architecture                     | 136 |

| Table 6.17. | Breakdown of images passes to compute the function integral on different sizes of our architecture                     | 137 |

| Table 6.18. | Breakdown of images passes to compute the function cvtColor on different sizes of our architecture                     | 137 |

| Table 6.19. | Breakdown of images passes to compute the function gaussianBlur on different sizes of our architecture                 | 138 |

| Table 6.20. | Breakdown of images passes to compute the function medianBlur on different sizes of our architecture                   | 139 |

| Table 6.21. | Breakdown of images passes to compute the function Canny on different sizes of our architecture           | 139 |

|-------------|-----------------------------------------------------------------------------------------------------------|-----|

| Table 6.22. | Breakdown of images passes to compute the function bilateralFilter on different sizes of our architecture | 141 |

| Table 6.23. | Throughput results for our 12 selected OpenCV Functions on a Zynq-7000 device                             | 142 |

| Table 6.24. | Throughput results for our 12 selected OpenCV Functions on a Zynq Ultrascale+ device.                     | 144 |

#### **ACKNOWLEDGEMENTS**

I would like to acknowledge Professor Ryan Kastner for his support as the chair of my committee. This thesis would not have happened without his support and guidance.

Chapter 2, is an amended reprint of the material as it appears in the ACM Transactions on Reconfigurable Technology Systems 2015. Jacobsen, Matthew; **Richmond, Dustin**; Hogains, Matthew; and Kastner, Ryan. The dissertation author was the co-investigator and author of this paper.

Chapter 3, in full, is a reprint of the material as it appears in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2018. **Richmond, Dustin**; Althoff, Alric; and Kastner, Ryan. The dissertation author was the primary investigator and author of this paper.

Chapter 5, in full, is a reprint of the material as it was submitted to International Conference on Field-Programmable Custom Computing Machines 2018. A revised version appears at International Conference on Field Programmable Logic and Applications 2018. **Richmond, Dustin**; Barrow, Michael; Kastner, Ryan. The dissertation author was the primary investigator and author of this paper.

Chapter 6, is currently being prepared for submission for publication of the material. **Richmond, Dustin**; Kastner, Ryan. The dissertation author was the primary investigator and author of this material.

#### **VITA**

| 2012      | Bachelor of Science in Computer Engineering, University of Washington, Seattle                           |

|-----------|----------------------------------------------------------------------------------------------------------|

| 2012      | Bachelor of Science in Electrical Engineering, University of Washington, Seattle                         |

| 2012–2018 | Research Assistant, Department of Computer Science and Engineering<br>University of California San Diego |

| 2015      | Masters of Science, University of California San Diego                                                   |

| 2016      | Candidate of Philosophy, University of California San Diego                                              |

| 2018      | Doctor of Philosophy, University of California San Diego                                                 |

#### **PUBLICATIONS**

- "Synthesizable Higher-Order Functions for C++," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems.

- "Everyone's a Critic: A Tool for Exploring RISC-V Projects" in IEEE Conference on Field Programmable Logic and Applications.

- "Generating Custom Memory Architectures for Alteras OpenCL Compiler". In Field Programmable Custom Computing Machines (FCCM), 2016 IEEE 24th Annual International Symposium on, pages 2124. IEEE, 2016.

- "Resolve: Generation of High-Performance Sorting Architectures from High-Level Synthesis" ACM International Symposium on Field Programmable Gate Arrays, 2016.

- "Tunnel Vision: Documenting Excavations in Three Dimensions with Lidar Technology." Advances in Archaeological Practice, 4(2):192204, 2016.

- "RIFFA 2.1: A Reusable Integration Framework for FPGA Accelerators." ACM Transactions on Reconfigurable Technology and Systems, 2015.

- "Enabling FPGAs for The Masses" arXiv preprint arXiv:1408.5870, 2014.

- "A FPGA Design For High-Speed Feature Extraction from a Compressed Measurement Stream." Field Programmable Logic and Applications (FPL), 2013 23rd International Conference on, pages 18, 2013.

- "A Data-Intensive Programming Model for FPGAs: A Genomics Case Study." Symposium on Application Accelerators in High-Performance Computing (SAAHPC12), 2012.

"Diffractive Light Trapping in Crystal-Silicon Films: Experiment and Electromagnetic Modeling." Applied optics, 50(29):57285734, 2011.

"Pressureless Nanoimprinting of Anatase TiO2 Precursor Films." Journal of Vacuum Science & Technology B, 29(2):021603, 2011.

#### ABSTRACT OF THE DISSERTATION

Hardware Development for Non-Hardware Engineers

by

#### **Dustin Alexander Richmond**

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2018

Professor Ryan Kastner, Chair

Recent economics in computer architecture, specifically the end of power-density-performance scaling trends and the inefficiencies in modern processors, has motivated more companies to develop custom hardware. Custom hardware improve important metrics that impact revenue: latency, performance, and power. This has led to the widespread deployment of Field Programmable Gate Arrays (FPGAs) in datacenters, automobiles, communications equipment, and more.

However, hardware development is tedious, time consuming, and costly. There are many challenges: languages are domain specific, few reusable libraries exist, and hardware compilation is slow. In addition, development tools are expensive with a high-degree of vendor lock-in and

domain-specific knowledge. These obstacles have limited hardware development to companies that can afford the associated costs and a few knowledgeable hardware engineers.

Applications for hardware pipelines exist at all scales. Machine learning, computer vision, and text processing are common targets for custom hardware and are pervasive in modern applications. While the details differ between specific applications the computations to well known patterns. These patterns provide a means for abstracting hardware development and increase the accesibility of hardware development for non-hardware engineers.

This thesis presents work on increasing the accessibility of hardware development to non-hardware engineers through the use of common parallel patterns. By abstracting recurring patterns in hardware development we can create languages and architectures with performance comparable to custom hardware circuits, and reduce the cost of hardware development.

# Chapter 1

# Introduction

Improving throughput, reducing latency, and minimizing power consumption are three never-ending, typically conflicting, constraints for computational systems. As Moore's law [1] and Dennard scaling [2] have ended, companies have been forced to find new ways to improve performance and decrease power. Many companies have turned to custom hardware pipelines: bespoke circuits that efficiently perform application tasks previously done on the CPU. These custom hardware pipelines provide throughput, latency, and power benefits by using transistors more efficiently. However, the development of hardware pipelines is difficult and companies have come to face a different kind of constraint: not enough hardware engineers.

Field Programmable Gate Arrays (FPGAs) are a popular choice for implementing custom hardware pipelines. FPGAs are computing architectures with reconfigurable routing and logic gates that allow highly-efficient circuit implementations. FPGAs are more efficient (Performance/Watt) than other computational substrates like Digital Signal Processors (DSPs), CPUs, or GPUs and with lower cost, and faster development cycles than Application Specific Integrated Circuits (ASICs). FPGAs have been used to implement custom hardware pipelines to improve performance [3, 4], increase security [5, 6], and reduce latency [7, 3, 4]. These projects have also been deployed at scale in datacenters [8, 9, 10], in processors [11], in cars [12, 13], and in cell-phone towers [14]. With the widespread deployment and availability of FPGAs, the need for hardware developers is growing.

Unfortunately, developing custom hardware pipelines on FPGAs is notorously difficult. This is because utilizing an FPGA in any system, let alone a data center, is complex, time consuming, and therefore [15]. First, users must identify, design, and optimize a custom hardware architecture for an FPGA. Second, they must choose a communication medium (e.g., PCIe, Ethernet), write and integrate low-level Hardware Development Language (HDL) communication cores. Then users must write kernel drivers to communicate between the CPU and the FPGA. Next, the integration must be compiled, tested, debugged, and verified. These skills are possessed by a small subset of hardware engineers with years of experience — for example — there are 23 (!) named authors on the initial paper describing the FPGA-based Microsoft Catapult project [8].

What is needed are solutions that increase the accessibility of hardware development for non-hardware engineers. This problem has been approached at many abstraction levels: Existing software languages have been extended to create new Hardware Development Languages (HDLs) that reduce verbosity [16, 17, 18]. Communication frameworks have been developed to abstract low-level details of data transfer [19, 20, 21, 22]. High-Level Synthesis (HLS) tools have been developed that emit complete hardware accelerators from algorithm descriptions in software languages [23, 24, 25, 26, 27, 28]. System synthesis tools emit complete systems by integrating HLS tools and communication frameworks [29, 28, 25]. Recent projects have created open-source, high-level libraries to ease FPGA control and communication. Finally, processor instruction sets have been developed that promotes application-specific extensions and customization with support from software toolchains [30]. All these projects have increased the productivity of hardware engineers, but little has been done to increase the general accessibility of hardware development.

Several challenges remain that impede the accessibility of hardware development for non-hardware engineers. First, vendor-specific tools, chip-specific interfaces, and low-level architecture differences inhibit re-use and force designers to re-engineer solutions for every new project. Second, HLS tools lack common abstractions found in software languages, which impedes re-use and familiarity. Three, the increasing number of processor projects, implementation languages, and interface standards hinders evaluation and adoption. Four, hardware targets lack detailed tutorials for non-hardware engineers, preventing uptake. Finally, the FPGA field still suffers from lengthy compile times and that prevent rapid prototyping, experimentation, and development.

This dissertation describes several projects to make hardware architecture development more accessible to non-hardware engineers. We develop RIFFA [20, 21] to address vendor-specific communication barriers in Chapter 2. We create and study a library of synthesizable higher-order functions to provide a common software abstraction in hardware development in Chapter 3. We introduce PYNQ and develop instructional materials, and tools for evaluating soft processor projects in Chapter 4 and Chapter 5. Finally, Chapter 6 demonstrates that an architecture of interconnected soft processors can build a performant general-purpose pipeline accelerator. In short, this thesis will demonstrate that by abstracting recurring patterns in hardware development we can create languages and architectures with performance comparable to custom hardware circuits.

The following sections provide an outline and motivation for each chapter of this thesis:

# 1.1 A (Vendor Agnostic) Reusable Integration Framework for FPGA Accelerators

Hardware pipelines must communicate through external interfaces like Ethernet or PCI Express, or on-chip interfaces like AXI or Avalon. While the underlying protocols are standardized the implementations are subject to vendor-specific wire names, packet formats, and configuration registers. In addition, these interfaces have timing requirements that often necessitate vendor-specific optimizations that can only be performed in low-level Hardware Development Languages (HDLs) inaccessible to non-hardware engineers [15]. For this reason, developing re-usable communication interfaces is inaccessible to even hardware engineers.

The market is filled with expensive solutions from secondary vendors. Companies like Northwest Logic, PLDA, Pico Computing and Xillybus provide PCI Express communication solutions, while Maxeler, Convey and others provide full development environments with languages and simulators. Some companies provide research pricing for academic groups, but the cost can be prohibitive, comes with little support, and no source code. The FPGA community needs solutions that are free and open-source to encourage prototyping and development.

Open-source and research projects have attempted to address this problem: Microsoft Research's Simple Interface for Reconfigurable Computing (SIRC) [31] uses 100 Mb Ethernet on Windows; Open Component Portablity Infrastructure (OpenCPI) [32] provides Ethernet ant PCIe implementations; MPRACE [33] runs only on Linux and exposes a low-level buffer protocol; and DyRACT [34] only supports Xilinx boards. These projects have limited support for operating systems, configurations, vendors, and languages. None of these solutions provide cross-platform support for multiple languages, or vendor hardware restrictions. These problems led to the development of RIFFA 2.0 [20] with broader support for Xilinx PCIe-enabled boards, with four language APIs, and multiple-OS support.

In this chapter, we describe the development of RIFFA 2.1 and RIFFA 2.2 which add pan-vendor support using re-usable hardare cores. We specifically describe our work on RIFFA 2.2, which re-architected the underlying transmit and receive channels for all vendor PCIe Express interfaces.

# 1.2 Higher-Order Functions for Hardware Accelerators

Another obstacle to hardware architecture development are the abstractions provided by languages. Hardware development is traditionally done with Hardware Development Languages (HDLs). HDLs expose wiring, registers, and logic gates which make them verbose with few abstractions [15]. Modern HDLs alleviate this somewhat by adding programming abstractions like interface structures, standard template libraries, and provide higher-order functions to

implement repeatable patterns [16, 17, 18]. Still, optimizing designs requires detailed knowledge about the underlying architecture, like the number of inputs in a FPGA Look-Up-Table, or bit-width of an addition core, or relative speeds of paths on a chip. This highly domain-specific knowledge is a huge barrier to FPGAs which has lead to a push to make hardware design more like software design and enable more software engineers [35] to write hardware cores.

High-Level Synthesis (HLS) tools are being developed to raise designer's level of abstraction from logic gates, registers, wires, and clocks to algorithm development. These tools take a program in a high-level language like C/C++, schedule operations, and emit an HDL circuit that implements the desired behavior [29, 26, 36, 25, 28]. Annotations added by the user direct tools to implement fine-grain pipeline, coarse-grain pipeline, or vector parallelism. More recent work has focused on the development of system synthesis tools, which emit complete systems by integrating the output of HLS tools and communication frameworks [29, 28, 25]. However, state-of-the-art C/C++ synthesis tools still suffer from some of the same issues of tools they were developed to replace: they lack libraries implemeting common patterns.

We have created an open-source library of higher-order functions synthesizable in C/C++ hardware development tools. We implement six common algorithms on a PYNQ board and conclude that our library produces results that are generally statistically indistinguishable traditional techniques. This library increases the commonalities between hardware architecture and software application development.

# 1.3 PYNQ: A Hardware Protoyping Environment

Trends toward higher performance and lower power in mobile computing have pushed FPGA vendors to develop System-on-Chip (SoC) devices. These devices combine ARM processors and FPGA fabrics on a single die to provide high performance and low power for embedded devices. They have been widely used in automobiles [13, 12], in communications [37], robotics [38], and computer vision [39, 27]. The breadth these of applications demonstrate the utility of

SoC devices. However, few development environments for these devices exist.

Many prototyping platforms exist on the embedded prototyping market. These are boards, packaged with Integrated Development Environments (IDEs), for example: Arduino provides a simple bare-bones systems programmed with a C++-like language and IDE with hundreds of libraries; Raspberry Pi is a linux-based, low-cost board with Python libraries and the IDLE IDE; BeagleBone is another linux-based system with a Javascript-like language and Cloud9 IDE to name a few of the most popular. All of these projects provide development boards, extensive libraries, and IDEs which increases the accessibility of the platforms.

One obstacle to FPGA development has been the absence of a standard, development platform. Many boards have been provided, but none match the ease, accessibility, and cost of software projects: Avnet has developed many iterations of the ZedBoard with custom linux distributions, Terasic has developed the DE1 educational board, and Digilent has developed the Arty line. These boards are provided with limited libraries, and rely on long compile times in the vendor tool chains for hardware development. In order to make hardware development more accessible, the community needs standard, low-cost, entry-level development boards for rapid prototyping and development, backed by open-source libraries and accessible in high-level languages.

Recently Xilinx has released project PYNQ - a collection of Python libraries and drivers for ZYNQ SoCs with an Ubuntu Linux image. PYNQ-branded boards have low power ARM processors, a small form-factor, and standard pin headers (Arduino, PMOD, and RasPi). Existing PYNQ applications provide common embedded communcation interfaces like I2C, SPI, and UART. Tutorials and documentation are delivered as web-based Jupyter notebooks served by the PYNQ board. Because of the accessibility of the web-based IDE, PYNQ is being rapidly adopted as a teaching platform across several universities, Tampere University of Technology, BYU [40], the University of Washington, and at UC San Diego. The PYNQ project and boards provide many of the abstractions and libraries that are common in software development boards. However, PYNQ still does not solve two issues: long compile times, and few tutorials for building PYNQ

applications.

Building a PYNQ application comprises a swath of interdependent topics: the Vivado block diagram editor, IP and algorithm development, hardware interfaces, physical memory spaces, drivers, and Python packaging. This has been a conscious (and reasonable) design choice of the PYNQ team to focus on a well-built set of libraries and APIs to aid all-programmable development. Instead, the task of developing tutorials and learning materials has been given to the community.

We have created a set of tutorials demonstrating how to build PYNQ applications using High-Level Synthesis (HLS) tools. Our lab curriculum is split into three units where each unit is a set of independent Jupyter Notebooks teaching a concept. At the end of each tutorial the readers have created a working PYNQ application. These tutorials should help readers overcome the introductory challenges of hardware architecture development.

# 1.4 A Survey of Open-Source RISC-V Processors

The RISC-V project provides a flexible instruction set architecture (ISA) with no licensing fees, a large (and growing) software infrastructure, and broad adoption. The RISC-V ISA is highly flexible with 4 architectural widths, and 13 codified extensions. The flexibility, and openness of the RISC-V specification has lead to a proliferation of open-source RISC-V projects tailored to specific goals. These features have made it a natural choice for imlementing a custom accelerator on an FPGA, since it is easy to tailor to specific application needs.

However the number of open-source RISC-V projects presents a challenge to developers. Cores can use one of many languages, interface standards, architectural features, and worse, different ISA extensions. This makes it difficult to evaluate the relative benefits of open-source RISC-V projects, and presents a challenge to anyone hoping to choose a RISC-V project to use as a hardware accelerator.

To address this problem we have built a tool to evaluate RISC-V projects using PYNQ.

We use our tool to evaluate 5 RISC-V projects and compare against the Xilinx MicroBlaze processor. Our results indicate that while RISC-V projects have a large variance in results, the best RISC-V soft processors are competitive with the Xilinx MicroBlaze on measurements of the maximum clock frequency, area, execution time on standard benchmarks, and executed instructions. Along with tutorials for extending our work to other processors, this work will help engineers overcome the challenges above.

# 1.5 A General-Purpose Pipeline Architecture

Processors are inefficient on modern workloads [41]. Traditional processor architectures have inherent inefficiencies in computations like convolution that are widespread in computer vision, machine learning, and linear algebra. Data movement and re-use in these applications does not map well to modern processor register files and instruction sets. This has pushed many companies to develop custom hardware to improve performance, reduce latency, and save power. [8, 9, 10, 42].

Hardware development is significantly more challenging than software development. Hardware development requires engineers with extensive domain specific knowledge and experience [35]. Hardware development languages are inabstract, with few high-level application libraries [15]. These problems are compounded by the speed of hardware compilation flows; CPU tool flows compile on the order of miliseconds to minutes, while FPGA binaries take tens of minutes to hours and days [43, 44]. These challenges have limited hardware development to companies that can afford the associated costs.

However, these applications are not limited to companies with deep pockets; the same challenges exist at all scales but the cost of hardware development is prohibitive. What is needed is a pipeline architecture that is general enough to capture common parallel patterns [30] and can be re-programmed from high-level interfaces.

In this chapter we propose a general-purpose pipeline architecture using interconnected

RISC-V processors. We perform a study to understand our architecture's performance relative to optimized libraries on an ARM processor and optimized libraries in hardware. We conclude that a heterogeneous collection of processors provides the best performance, and can outperform two generations of ARM processor with performance comparable to static hardware pipelines.

# Chapter 2

# RIFFA 2.2: A (Vendor Agnostic) Reusable Integration Framework for FPGA Accelerators

# 2.1 Introduction

FPGAs are being used by an ever widening audience of designers, engineers, and researchers. These designers are frequently non-hardware engineers as tools such as Xilinx Vivado High Level Synthesis and the Bluespec language are lowering the barriers to entry for FPGA use. Many of these use cases will require high bandwidth input and output between the FPGA and a traditional CPU workstation. When faced with this problem one can either write their own interconnection, license an existing solution from a vendor, or use an open source solution.

Writing an interconnect is a significant amount of work and is a major barrier to FPGA development for non-hardware engineers. FPGAs are flexible enough to connect to virtually any device. However, this flexibility also makes it challenging to connect to virtually any device. The protocol standards that make workstations interoperable must be implemented from the physical layer on up in order for the FPGA to interface with it. This can be a large obstacle to overcome for most designers. In many cases, implementing the interface logic can match or exceed the effort required for implementing the original application or control logic.

Several commercial solutions exist that can be licensed from vendors such as: Northwest Logic, PLDA, and Xillybus. These solutions are PCI Express (PCIe) based. PCIe based interconnects have become the de facto standard for high bandwidth FPGA-PC communication because of PCIe's ubiquitous presence, low latency, and scalable performance. These solutions are high performing and available for most modern FPGA devices. However, the licensing costs can be prohibitively high and often tied to vendor specific hardware. Some offer special pricing for research based licenses, but no source is supplied.

Open source connectivity solutions exist as well, such as: Microsoft Research's Simple Interface for Reconfigurable Computing (SIRC), the Open Component Portablity Infrastructure (OpenCPI), MPRACE, and DyRACT. These solutions offer interconnections over Ethernet or PCIe. SIRC is a full solution with high level APIs and hardware interfaces. It works out of the box with minimal configuration. Unfortunately, it only runs over 100 Mb Ethernet and is only supported on Windows operating systems. This limits the bandwidth and platform. OpenCPI is designed to use either Ethernet or PCIe to connect components such as FPGAs, GPUs, or DSPs. The APIs are general enough to support a number of different components. This flexibility however makes configuring and using OpenCPI difficult and overwhelming. The MPRACE project provides a PCIe based framework that runs on Linux. It provides a low level buffer management API and a DMA IP controller. This low level API is usable but not as well suited for transferring data to and from software applications. Moreover, it only supports Linux platforms. Lastly, the DyRACT project provides a platform for FPGA based accelerators needing PCIe connectivity, DDR3, and partial reconfiguration. It is a nice framework for those needing partial reconfiguration, PCIe connectivity, a clock manager, and memory controller.

There also attempts to integrate FPGAs into traditional software environments. Commercial solutions such as Maxeler, Convey, and National Instruments provide full development environments along with communications frameworks. This class of solutions works only with custom vendor hardware and includes custom programming languages. Similarly, the Altera OpenCL HLS solution includes support for PCIe based FPGA communication as part of their

SDK. The SDK compiles OpenCL kernels to FPGA primitives and produces an OpenCL execution environment that executes on a FPGA instead of a GPU. There are also many framework level attempts to bridge the communications divide between CPUs and FPGA cores. Projects such as: Hthreads [45], HybridOS [46] and BORPH [47] all address this problem. However these solutions utilize custom operating system kernels and often only support CPUs running on the FPGA fabric. All of these frameworks are quite impressive but impose additional programming and runtime constraints, in addition to vendor hardware lock-in.

These problems inhibit FPGA development for all users by increasing non-recoverable engineering costs, and increasing the domain-specific knowledge necessary for FPGA development. What is needed, is a flexible, multi-vendor, multi-language, no-cost solution so that FPGA development can be available for anyone with a desktop computer.

To address these problems, we have developed RIFFA 1.0 [19], and RIFFA 2 [20]. RIFFA is an open source framework that provides a simple data transfer software API and a streaming FIFO hardware interface. It runs over PCIe and hides the details of the protocol so designers can focus on implementing application logic instead of basic connectivity interfaces. It can be integrated with projects built using a variety of tools and method. Both Windows and Linux operating systems are supported and allow communication between multiple FPGAs per host.

In the sections that follow, we present a detailed description of the RIFFA 2.2 design. RIFFA has gone through several iterations. RIFFA 1.0 [19] supported Xilinx devices with limited PCI Express transfer bandwidth and a synchronous API. RIFFA 2.0 removed dependencies on Xilinx IP, replaced the synchronous software API with an asynchronous stream-based API, and maximized PCI Express bandwidth. RIFFA 2.1 added support for PCIe packet reordering and limited Altera support. RIFFA 2.2 rearchitected the transmit and recieve packet formatters to add support for next-generation Xilinx devices. We present a comparison with earlier releases, an analysis of the architecture, and experimental performance results. The chief contributions of this project are:

- RIFFA 2.0: An open source, reusable, integration framework for multi-vendor FPGAs and workstations in PCI Express Gen 2.0.

- RIFFA 2.1: Improved packet reordering, scatter gather DMA,

- RIFFA 2.2: Multi-vendor/multi-generation support and re-usable packet engines in PCI Express Gen 2.

The remainder of this chapter is organized as follows: Section 2.2 describes the high-level abstraction provided by RIFFA. Section 2.3 describes the hardware and software architecture that provides this abstraction and the evolution that occured from RIFFA 1.0 to RIFFA 2.2. Section 2.4 reports performance results. Finally, we conclude in Section 2.5.

# 2.2 Design

RIFFA is based on the concept of communication *channels* between software threads on the CPU and user cores on the FPGA. A channel is similar to a network socket in that it must first be opened, can be read and written, and then closed. However, unlike a network socket, reads and writes can happen simultaneously (if using two threads). Additionally, all writes must declare a length so the receiving side knows how much data to expect. Each channel is independent. RIFFA supports up to 12 channels per FPGA. Up to 12 different user cores can be accessed directly by software threads on the CPU, simultaneously. Designs requiring more than 12 cores per FPGA can share channels. This increases the number of effective channels, but requires users to manually multiplex and demultiplex access on a channel.

Before a channel can be accessed, the FPGA must be opened. RIFFA supports multiple FPGAs per system (up to 5). This limit is software configurable. Each FPGA is assigned an identifier on system start up. Once opened, all channels on that FPGA can be accessed without any further initialization. Data is read and written directly from and to the channel interface. On the FPGA side, this manifests as a first word fall through (FWFT) style FIFO interface for

each direction. On the software side, function calls support sending and receiving data with byte arrays.

Memory read/write requests and software interrupts are used to communicate between the workstation and FPGA. The FPGA exports a configuration space accessible from an operating system device driver. The device driver accesses this address space when prompted by user application function calls or when it receives an interrupt from the FPGA. This model supports low latency communication in both directions. Only status and control values are sent using this model. Data transfer is accomplished with large payload PCIe transactions issued by the FPGA. The FPGA acts as a bus master scatter gather DMA engine for both upstream and downstream transfers. In this way multiple FPGAs can operate simultaneously in the same workstation with minimal CPU system load.

The details of the PCIe protocol, device driver, DMA operation, and all hardware addressing are hidden from both the software and hardware. This means some level of flexibility is lost for users to configure custom behaviors. For example, users cannot setup custom PCIe base address register (BAR) address spaces and map them directly to a user core. Nor can they implement quality of service policies for channels or PCIe transaction types. However, we feel any loss is more than offset by the ease of programming and design.

To facilitate ease of use, RIFFA has software bindings for:

• C/C++

• Python 2.7+

• Java 1.4+

• Matlab 2008a+.

Both Windows 7 and Linux 2.6+ platforms are supported. RIFFA supports the following FPGA families from Xilinx and Altera (annotated with Classic or Ultrascale interface type):

• Xilinx Spartan 6 (Classic Interface)

• Xilinx 7 Series (Classic Interface)

• Xilinx Virtex 6 (Classic Interface)

• Xilinx Ultrascale (Ultrascale Interface)

- Altera Arria II (Classic Interface)

- Altera Stratix IV (Classic Interface)

- Altera Cyclone IV (Classic Interface)

- Altera Stratix V (Classic Interface)

RIFFA designs can make use of PCIe data bus widths: 32, 64, and 128. All PCIe Gen 1 and Gen 2 configurations up to x8 lanes are supported. PCIe Gen 3 up to x4 lanes are supported for all devices.

In the next subsections we describe the software interface, followed by the hardware interface.

#### 2.2.1 Software Interface

The interface for the original RIFFA release [19] was a complicated collection of functions that provided users with an array of data transfer options and threading models. These functions were designed under the assumption that every PC initiated call to the FPGA would result in a transfer of data in both directions. It also required data transfers in either direction to be initiated by the PC. User IP cores would need to be designed with this paradigm in mind to function properly with RIFFA 1.0. RIFFA 2 does not impose such restrictions. The interface on the software side has been distilled down to just a few functions. Moreover, data transfers can be initiated by both sides; PC functions initiate downstream transfers and IP cores initiate upstream transfers. The complete RIFFA 2 software interface is listed in Table 2.1 (for the C/C++ API). We omit the Java, Python, and Matlab interfaces for brevity.

There are four primary functions in the API: open, close, send, and receive. The API supports accessing individual FPGAs and individual channels on each FPGA. There is also a function to list the RIFFA capable FPGAs installed on the system. A reset function is provided that programmatically triggers the FPGA channel reset signal. This function can be useful when developing and debugging the software application. If installed with debug flags turned on, the RIFFA library and device driver provide useful messages about transfer events. The messages will print to the operating system's kernel log. RIFFA includes this functionality

**Table 2.1.** RIFFA 2.2 software API (C/C++).

```

Function Name & Description

int fpga_list(fpga_info_list * list)

Populates the fpga_info_list pointer with info on all FPGAs installed in the system.

fpga_t * fpga_open(int id)

Initializes the FPGA specified by id. Returns a pointer to a fpga_t struct or NULL.

void fpga_close(fpga_t * fpga)

Cleans up memory and resources for the specified FPGA.

int fpga_send(fpga_t * fpga, int chnl, void * data, int len, int offset,

int last, long timeout)

Sends len 4-byte words from data to FPGA channel chn1. The FPGA channel will be

sent len, offset, and last. timeout defines how long to wait for the transfer. Returns

the number of 4-byte words sent.

int fpga_recv(fpga_t * fpga, int chnl, void * data, int len, long timeout)

Receives up to len 4-byte words from the FPGA channel chnl to the data buffer. The

FPGA will specify an offset for where in data to start storing received values. timeout

defines how long to wait for the transfer. Returns the number of 4-byte words received.

void fpga_reset(fpga_t * fpga)

Resets the FPGA and all transfers across all channels.

```

because visibility into hardware bus transfers can be very useful when communicating with custom designed FPGA cores.

The software API has only one function to send data and only one to receive data. This has been intentionally kept as simple as possible. These function calls are synchronous and will block until the transfer has completed. Both take byte arrays as parameters. The byte arrays contain the data to send or serve as the receptacle for receiving data. In the send data function, the offset parameter is used as a hint for the FPGA. It specifies an offset for storing data at the destination. This can be used to support bulk memory copies between the PC and memory on the FPGA. The last parameter is used to group together multiple transfers. If last is 0, the destination should expect more transfers as part of the same group. The final transfer will should have last set to 1. This grouping is entirely user specified and can be useful in situations where memory limitations require sending multiple partial transfers. Lastly, the timeout parameter specifies how many milliseconds to wait between communications during a transfer. Setting this value to an upper bound on computation time will ensure that RIFFA does not return prematurely.

Setting a zero timeout value causes the software thread to wait for completion indefinitely.

```

char buf[BUF_SIZE];

int chnl = 0;

long t = 0; // Timeout

fpga_t * fpga = fpga_open(0);

int r = read_data("filename", buf, BUF_SIZE);

printf("Read %d bytes from file", r);

int s = fpga_send(fpga, chnl, buf, BUF_SIZE/4, 0, 1, t);

printf("Sent %d words to FPGA", s);

r = fpga_recv(fpga, chnl, buf, BUF_SIZE/4, t);

printf("Received %d words from FPGA", r);

// Process results ...

fpga_close(fpga);

```

Figure 2.1. RIFFA 2.2 software example in C.

Figure 2.1 shows an example C application using RIFFA. In this example, the software reads data from a file into a buffer, sends the data to the FPGA, and then waits for a response. The response is stored back into the same buffer and then processed. In this example, the same buffer is used to store the file data and the FPGA result. This is not a requirement. It just makes for a simpler example.

#### In Practice

Our experience with this interface is positive, but not without drawbacks. Removing the expectation of function-call style bi-directional data transfer allows users to design systems with more flexibility. The software interface can be easily understood as there exists a single function for each basic operation (open, close, send, receive). The interface also allows users to develop IP cores that perform either stream processing or traditional von Neumann style computing (bulk memory copies to FPGA memory).

The interface however does not support some common use cases very well. Specifically, many programming models require some type of read/write capability for FPGA based registers. Strictly speaking, this is supported. But it requires users to write an IP core that maps data

transferred with offset parameters to an internal register array (for example). These register accesses require a DMA transfer for every read/write, which is inefficient.

Additionally, the lack of non-blocking function calls makes it cumbersome to perform common stream processing tasks. Consider the example in Figure 2.1. Because the calls fpga\_send and fpga\_recv are blocking, all the data must be transferred to the FPGA via the fpga\_send call before the call to fpga\_recv can be made. The upstream transfer cannot begin until the call to fpga\_recv is made. This arrangement may be a problem if the IP core attached to the channel is designed to start sending a response before it receives all the data. Many streaming oriented designs will produce output in this fashion and attempt to start an upstream transaction while the downstream transaction is still running. To avoid a deadlock, users will need to use two threads; one for the call to fpga\_send and one for the call to fpga\_recv. This allows both calls to execute in an time overlapping manner as the IP core would expect.

RIFFA would benefit from an expanded software API that supports programmed I/O and non-blocking function calls. Future versions may include these features.

#### 2.2.2 Hardware Interface

The interface on the hardware side is composed of two sets of signals; one for receiving data and one for sending data. These signals are listed in Table 2.2. The ports highlighted in blue are used for handshaking. Those not highlighted are the FIFO ports which provide first word fall through semantics. The value of DWIDTH is: 32, 64, or 128, depending on the PCIe link configuration.

Figure 2.2 shows a Verilog example of an IP core that matches the C example code from Figure 2.1. In this example, the IP core receives data from the software thread, counts the number 4-byte words received, and then returns the count.

For upstream transactions, CHNL\_TX must be set high until all the transaction data is consumed. CHNL\_TX\_LEN, CHNL\_TX\_OFF, and CHNL\_TX\_LAST must have valid values until the CHNL\_TX\_ACK is pulsed. The CHNL\_TX\_ACK pulse indicates that channel has read the parameters and

**Table 2.2.** RIFFA 2.2 hardware interface

| Signal Name              | I/O | Description                                                      |  |

|--------------------------|-----|------------------------------------------------------------------|--|

| CHNL_RX_CLK              | О   | Clock to read data from the incoming FIFO.                       |  |

| CHNL_RX                  | I   | High signals incoming data transaction. Stays high until all     |  |

|                          |     | data is in the FIFO.                                             |  |

| CHNL_RX_ACK              | О   | Pulse high to acknowledge the incoming data transaction.         |  |

| CHNL_RX_LAST             | I   | High signals this is the last receive transaction in a sequence. |  |

| CHNL_RX_LEN[31:0]        | I   | Length of receive transaction in 4-byte words.                   |  |

| CHNL_RX_OFF[30:0]        | I   | Offset in 4-byte words of where to start storing received data.  |  |

| CHNL_RX_DATA[DWIDTH-1:0] | I   | FIFO data port.                                                  |  |

| CHNL_RX_DATA_VALID       | I   | High if the data on CHNL_RX_DATA is valid.                       |  |

| CHNL_RX_DATA_REN         | О   | Pulse high to consume value from on CHNL_RX_DATA.                |  |

| CHNL_TX_CLK              | О   | Clock to write data to the outgoing FIFO.                        |  |

| CHNL_TX                  | О   | High signals outgoing data transaction. Keep high until all      |  |

|                          |     | data is consumed.                                                |  |

| CHNL_TX_ACK              | I   | Pulsed high to acknowledge the outgoing data transaction.        |  |

| CHNL_TX_LAST             | О   | High signals this is the last send transaction in a sequence.    |  |

| CHNL_TX_LEN[31:0]        | О   | Length of send transaction in 4-byte words.                      |  |

| CHNL_TX_OFF[30:0]        | О   | Offset in 4-byte words of where to start storing sent data in    |  |

|                          |     | the CPU thread's receive buffer.                                 |  |

| CHNL_TX_DATA[DWIDTH-1:0] | О   | FIFO data port.                                                  |  |

| CHNL_TX_DATA_VALID       | О   | High if the data on CHNL_TX_DATA is valid.                       |  |

| CHNL_TX_DATA_REN         | I   | High when the value on CHNL_TX_DATA is consumed.                 |  |

started the transfer. The CHNL\_TX\_DATA\_OFF value determines where data will start being written to within the PC's receiving byte array (this is the hardware equivalent to the software offset parameter). This is measured in 4-byte words. As described in Section 2.2.1, CHNL\_TX\_LAST must be 1 to signal the end of a set of transfers. This will unblock the thread waiting in fpga\_recv. Data values asserted on CHNL\_TX\_DATA are consumed when both CHNL\_TX\_DATA\_VALID and CHNL\_TX\_DATA\_REN are high.

The handshaking ports are symmetric for both sets of signals. Thus, the behaviors are reversed with downstream transactions. The user core is notified of a new downstream transaction when CHNL\_RX goes high. The user core must acknowledge the transaction by asserting CHNL\_RX\_ACK high for at least one cycle. The CHNL\_RX\_ACK pulse indicates that the user core has read the parameters and that data can now be delivered into the FIFO. This barrier serves to separate FIFO data between downstream transfers. Back to back transfers may otherwise keep the FIFO full and there would be no way to delineate transfer boundaries.

As with upstream transactions, data will be made available on CHNL\_RX\_DATA and is valid when CHNL\_RX\_DATA\_VALID is high. Each cycle CHNL\_RX\_DATA\_VALID and CHNL\_RX\_DATA\_REN are high, data present on CHNL\_RX\_DATA is considered consumed. The channel may present new valid data on that port the following cycle. The values for CHNL\_RX\_LAST, CHNL\_RX\_LEN, and CHNL\_RX\_OFF correspond to those provided via the fpga\_send function call on the host PC and should be used as intended.

Timing diagrams for these signals illustrate the upstream and downstream transfers on a cycle by cycle basis. They are available on the RIFFA website: http://riffa.ucsd.edu.

#### In Practice

The interface requires providing a length value for transfers. This can be problematic in situations where the transfer length is unknown. Consider, for example, a data compression IP core that compresses data received from the host PC. To accommodate this type of situation, the core could buffer the compressed data until it is all generated and then start a upstream transfer. Another solution is to buffer data in chunks and send each in its own transfer. To avoid such workarounds, RIFFA supports early termination on upstream transfers. Designs with unknown upstream transfer size can set CHNL\_TX\_LEN to an upper bound value, start the transaction and send data as it is generated by the core. When the core finishes producing output, it can lower CHNL\_TX, regardless of how much data was actually transferred. The RIFFA channel will interpret this behavior as an early termination and complete the transfer with the data sent thus far. As long as CHNL\_TX is high, the transaction will continue until CHNL\_TX\_LEN words have been consumed.

Despite a minimal set of signals in the hardware interface, we have found that the handshaking protocol can be an obstacle in designs. It requires building a state machine to manage. Many designs simply need a simple FWFT FIFO (or AXI-4 Lite style) interface. In these designs, the handshaking and parameter information are not used but require additional logic and understanding to deal with.

```

parameter INC = DWIDTH/32;

assign CHNL_RX_ACK = (state == 1);

assign CHNL_RX_DATA_REN = (state == 2 || state == 3);

assign CHNL_TX = (state == 4 || state == 5);

assign CHNL_TX_LAST = 1;

assign CHNL_TX_LEN = 1;

assign CHNL_TX_OFF = 0;

assign CHNL_TX_DATA = count;

assign CHNL_TX_DATA_VALID = (state == 5);

wire data_read = (CHNL_RX_DATA_VALID & CHNL_RX_DATA_REN);

always @ (posedge CLK)

case(state)

0: state <= (CHNL_RX ? 1:0);</pre>

1: state <= 2;

2: state <= (!CHNL_RX ? 3:2);

3: state <= (!CHNL_RX_DATA_VALID ? 4:3);</pre>

4: state <= (CHNL_TX_ACK ? 5:4);

5: state <= (CHNL_TX_DATA_REN ? 0:5);</pre>

endcase

always @ (posedge CLK)

if (state == 0)

count <= 0;</pre>

else

count <= (data_read ? count+INC:count);</pre>

```

**Figure 2.2.** RIFFA 2.2 hardware example in Verilog.

# 2.2.3 Changes from RIFFA 1.0

RIFFA 2 is a complete rewrite of the original RIFFA 1.0 release. RIFFA 1.0 only supports the Xilinx Virtex 5 family. RIFFA 2.2 supports all modern FPGA devices from Xilinx and Altera across PCIe Gen 1, Gen 2, and Gen 3<sup>1</sup>.

RIFFA 1.0 requires the use of a Xilinx PCIe Processor Local Bus (PLB) Bridge core. Xilinx has since moved away from PLB technology and deprecated this core. The PLB Bridge core limited the PCIe configuration to a Gen 1 x1 link. Additionally, the bridge core did not support overlapping PLB transactions. This did not have an effect on the upstream direction

<sup>&</sup>lt;sup>1</sup>Up to x4 lanes.

because upstream transactions are one way. Downstream transactions however, must be sent by the core and serviced by the host PC's root complex. Not being able to overlap transactions on the PLB bus results in only one outstanding downstream PCIe transaction at a time. This limits the maximum throughput for upstream and downstream transfers to 181 MB/s and 25 MB/s respectively. The relatively low downstream bandwidth was a chief motivator for improving upon RIFFA 1.0.

RIFFA 1.0 made use of a simple DMA core that uses PLB addressing to transfer data. The hardware interface exposes a set of DMA request signals that must be managed by the user core in order to complete DMA transfers. RIFFA 2 exposes no bus addressing or DMA transfer signals in the interface. Data is read and written directly from and to FWFT FIFO interfaces on the hardware end. On the software end, data is read and written from and to byte arrays. The software and hardware interfaces have been significantly simplified since RIFFA 1.0.

On the host PC, contiguous user space memory is typically scattered across many non-contiguous pages in physical memory. This is an artifact of memory virtualization and makes transfer of user space data difficult. Earlier versions of RIFFA had a single packet DMA engine that required physically scattered user space data be copied between a physically contiguous block of memory when being read or written to. Though simpler to implement, this limits transfer bandwidth because of the time required for the CPU to copy data. RIFFA 2 supports a scatter gather DMA engine. The scatter gather approach allows data to be read or written to directly from/to the physical page locations without the need to copy data.

RIFFA 1.0 supports only a single FPGA per host PC with C/C++ bindings for Linux. Version 2 supports up to 5 FPGAs that can all be addressed simultaneously from different threads. Additionally, RIFFA 2 has bindings for C/C++, Java, Python, and Matlab for both Linux and Windows. Lastly, RIFFA 2 is capable of reaching 97% maximum achievable PCIe link utilization during transfers. RIFFA 1.0 is not able to exceed more than 77% in the upstream direction or more than 11% in the downstream direction.

### 2.3 Architecture

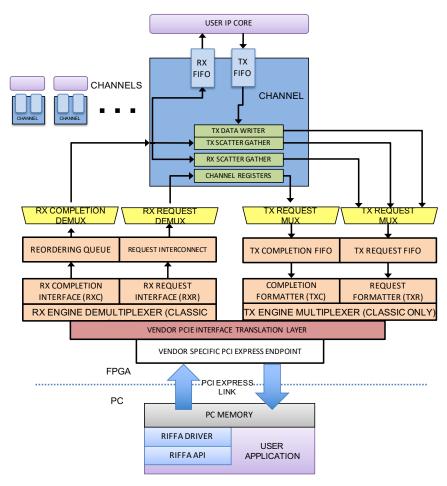

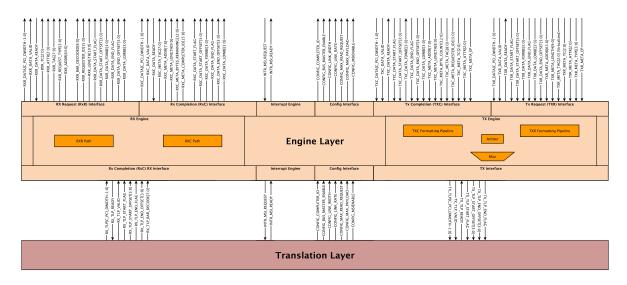

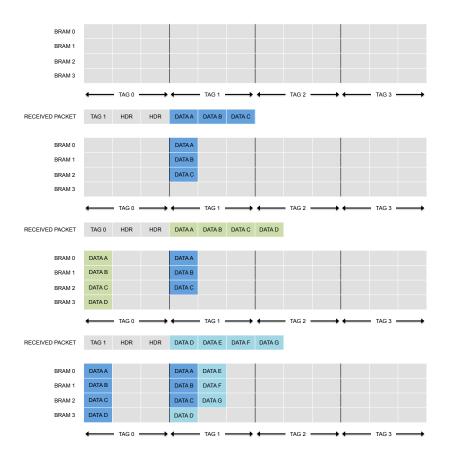

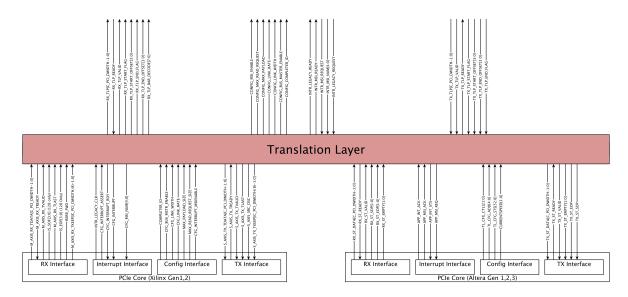

**Figure 2.3.** RIFFA architecture in RIFFA 2.2. The Channel Layer is described in Section 2.3.1, the DMA Layer (Green) in Section 2.3.1, Multiplexer Layer (Yellow) in Section 2.3.1, Engine Layer (Orange) in Section 2.3.1, and the Translation Layer (Red) in Section 2.3.1

A diagram of the RIFFA architecture is illustrated in Figure 2.3. The top of the diagram shows the hardware architecture, as described in Section 2.3.1. The software architecture is described in Section 2.3.2. The underlying goal of RIFFA architectural decisions is to achieve maximum throughput and minimum latency with the fewest resources. As a result, the architecture can run at line rate, never needing to block or pause, in both upstream (FPGA to Host) and downstream (Host to FPGA) directions.

At each level in the architecture, any potential blocking by a channel or component is

averted through the use of FIFOs, multiplexing, and overlapping execution.

#### 2.3.1 Hardware Architecture

RIFFA's hardware architecture is built from layers of abstractions to hide the underlying PCI Express protocol. At the highest layer of abstraction, the user is presented with a series of channel interfaces. At the lowest layer, RIFFA wraps the vendor-specific PCI Express interface. This is shown in Figure 2.3 and described below.

The RIFFA cores are driven by a clock derived from the PCIe reference clock. This clock's frequency is a product of the PCIe link configuration. It runs fast enough to saturate the PCIe link if data were sent every cycle. User cores do not need to use this clock for their CHNL\_TX\_CLK or CHNL\_RX\_CLK.

#### **Channel Layer**

At the top level RIFFA users are presented with the Channel Interface, described in Table 2.2 and shown in blue in Figure 2.3. A set of RIFFA channels provide streaming read and write interfaces, with asynchronous clock-crossings to user cores. These interfaces deal exclusively with payload data.