## **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Memory-Centric Architectures: Bridging the Gap Between Compute and Memory

#### **Permalink**

https://escholarship.org/uc/item/59z905nc

#### **Author**

Li, Shuangchen

## **Publication Date**

2018

Peer reviewed|Thesis/dissertation

## University of California Santa Barbara

# Memory-Centric Architectures: Bridging the Gap Between Compute and Memory

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Shuangchen Li

#### Committee in charge:

Professor Yuan Xie, Chair Professor Margaret Marek-Sadowska Professor Dmitri Strukov Professor William Yang Wang Dr. Hongzhong Zheng

| The Dissertation of Shuangchen Li is approved. |

|------------------------------------------------|

|                                                |

|                                                |

| Professor Margaret Marek-Sadowska              |

|                                                |

| Professor Dmitri Strukov                       |

| Trotessor Dilliur Strukov                      |

|                                                |

| Professor William Yang Wang                    |

|                                                |

| Dr. Hongzhong Zheng                            |

|                                                |

| Professor Yuan Xie, Committee Chair            |

Memory-Centric Architectures: Bridging the Gap Between Compute and Memory

Copyright © 2018

by

Shuangchen Li

#### Acknowledgements

First of all, I sincerely thank my advisor, Prof. Yuan Xie. I have learnt a lot from his board knowledge, wisdom, passionate, skills and I wish I could have learnt them all. His research foresight is what I admire and benefit from the most. This thesis is an example of his great vision. Even more, he almost offers everything and leverages all the resource that he has to make me a better researcher. Words are to pale to express all my gratitude.

Many thanks to Prof. Margaret Marek-Sadowska, Prof. Dmitri Strukov, Prof. William Wang, and Dr. Hongzhong Zheng for serving in my dissertation committee and providing valuable feedback to my qualify exam and this dissertation.

I would like to express my special thank to Prof. Sharon Hu and Prof. Yongpan Liu, who first guided me into the research world during my Master study; Dr. Kaisheng Ma, who taught and helped me a lot for turning into a computer architect when I was in Penn State University. Also, I feel so lucky to have the chance working with Prof. Jishen Zhao and Dr. Cong Xu, who taught me so much knowledge and skills that I will always regard them as my mentors. I would also like to thank Dr. Hang Zhang, who was an alive Google Scholar and offered me lots of help.

I sincerely thank coauthors of my research papers, including but not limited to Dr. Ping Chi, Dr. Kaisheng Ma, Peng Gu, Liu Liu, Yu Ji, Dr. Tao Zhang, and Dr. Krishna Malladi. I also sincerely thank Dr. Dimin Niu, Dr. Hongzhong Zheng, Dr. Niladrish Chatterjee, and Dr. Mike O'Connor for their insightful mentoring during my internships.

I would like to thank all my friends in both PSU and UCSB and all members in the MDL group and the SEAL group, for keeping me accompany in this journey, encouraging and inspiring me, making me all these good memories. Especially Dr. Kaisheng Ma, Ziyang Qi, Xulong Tang, Dr. Cong Xu, Dr. Ping Chi, Dr. Jia Zhan, Hang Zhang, Itir Akgun, Linuo Xue, Liu Liu, Peng Gu, Maohua Zhu, Dylan Stow, Dr. Chao Zhang, and Dr. Xing Hu.

Last but not the least, I would like to thank my parents for their unconditional love and support, and all my friends for making my life vivid.

#### **Curriculum Vitæ**

#### Shuangchen Li

#### **Education**

| 2018 | Ph.D. in Electrical and Computer Engineering (Expected), University of |

|------|------------------------------------------------------------------------|

|      | California, Santa Barbara.                                             |

| 2014 | M.A. in Electrical Engineering, Tsinghua University.                   |

| 2011 | B.S. in Electrical Engineering, Tsinghua University                    |

#### **Publications**

- [1]. Wei-Hao Chen, Wen-Jang Lin, **Shuangchen Li**, Li-Ya Lai, Jian-Wei Su, Huan-Ting Lin, Chien-Hua Hsu, Heng-Yuan Lee, Yuan Xie, Shyh-Shyuan Sheu, and Meng-Fan Chang "A 16Mb Dual-Mode ReRAM Macro with Sub-14ns Computing-In-Memory and Memory Functions Enabled by Self-Write Termination Scheme." Proc. *IEEE International Electron Devices Meeting (IEDM)*, 2017.

- [2]. **Shuangchen Li**, Dimin Niu, Krishna T. Malladi, Hongzhong Zheng, Bob Brennan, and Yuan Xie "DRISA: A DRAM-based Reconfigurable In-Situ Accelerator." Proc. *International Symposium on Microarchitecture (MICRO)*, 2017.

- [3]. Liu Liu, Ping Chi, **Shuangchen Li**, Yuanqing Cheng, and Yuan Xie. "Processing-In-Memory Architecture Design for Accelerating Neuro-Inspired Algorithms." Proc. *Neuro-inspired Computing Using Resistive Synaptic Devices*, 2017.

- [4]. Ping Chi, **Shuangchen Li**, and Yuan Xie. "Building Energy-Efficient Multi-Level Cell STT-RAM Caches with Data Compression." Proc. *Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2017.

- [5]. Chi Ping and **Shuangchen Li** (**Equal Contribution**), Cong Xu, Tao Zhang, Jishen Zhao, Yu Wang, Yongpan Liu, Yuan Xie "PRIME: A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory." Proc. *International Symposium on Computer Architecture (ISCA)*, 2016.

- [6]. Yu Ji, Youhui Zhang, **Shuangchen Li**, Ping Chi, Cihang Jiang, Peng Qu, Yuan Xie, and Wenguang Chen "NEUTRAMS: Neural Network Transformation and Co-design under Neuromorphic Hardware Constraints." Proc. *International Symposium on Microarchitecture* (MICRO), 2016.

- [7]. **Shuangchen Li**, Cong Xu, Jishen Zhao, Lu Yu, Yuan Xie "Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations on Emergying Non-volatile Memories." Proc. *the 53nd Annual Design Automation Conference (DAC)*, 2016.

- [8]. **Shuangchen Li**, Liu Liu, Peng Gu, Cong Xu, and Yuan Xie "NVSim-CAM: A Circuit-Level Simulator for Emerging Nonvolatile Memory based Content-Addressable Memory." Proc. *International Comference on Computer-Aided Design (ICCAD)*, 2016.

- [9]. Peng Gu, **Shuangchen Li**, Dylan Stow, Russell Barnes, Liu Liu, Yuan Xie, and Eren Kursun "Leveraging 3D Technologies for Hardware Security: Opportunities and Challenges." Proc. *Great Lakes Symposium on VLSI (GLVLSI)*, 2016.

- [10]. Ping Chi, **Shuangchen Li**, Yuanqing Cheng, Yu Lu, Seung H. Kang, Yuan Xie. "Architecture Design with STT-RAM: Opportunities and Challenges." Proc. *Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2016. (Invited)

- [11]. Kaisheng Ma, Yang Zheng, **Shuangchen Li**, Karthik Swaminathan, Xueqing Li, Yongpan Liu, John Sampson, Yuan Xie, and Vijaykrishnan Narayanan. "Architecture Exploration for Ambient Energy Harvesting Nonvolatile Processors." Proc. *International Symposium On High Performance Computer Architecture (HPCA)*, 2015. (**Best Paper Award, IEEE Micro Top Picks 2016**)

- [12]. Kaisheng Ma, Xueqing Li, **Shuangchen Li**, Yongpan Liu, John Sampson, Yuan Xie, and Vijaykrishnan Narayanan. "Nonvolatile Processor Architecture Exploration For Energy-Harvesting Applications." *IEEE MICRO magazine*, 2015.

- [13]. **Shuangchen Li**, Ping Chi, Jishen Zhao, K.T. Tim Cheng, and Yuan Xie. "Leveraging Nonvolatility for Architecture Design with Emerging NVM." Proc. *Non-Volatile Memory System and Applications Symposium (NVMSA)*, 2015. (Invited)

- [14]. **Shuangchen Li**, Ang Li, Yuan Zhe, Yongpan Liu, Peng Li, Guanyu Sun, Yu Wang, Huazhong Yang, Yuan Xie. "Leveraging Emerging Nonvolatile Memory in High-Level Synthesis with Loop Transformations." Proc. *International Symposium on Low Power Electronics and Design (ISLPED)*, 2015.

- [15]. Yongpan Liu, Zhewei Li, Hehe Li, Yiqun Wang, Xueqing Li, Kaisheng Ma, **Shuangchen Li**, Mei-Fang Chiang, John Sampson, Yuan Xie, Jiwu Shu, and Huazhong Yang. "Ambient Energy Harvesting Nonvolatile Processors: From Circuit To System." Proc. *the 52nd Annual Design Automation Conference (DAC)*, 2015. (Invited)

- [16]. **Shuangchen Li**, Ang Li, Yongpan Liu, Yuan Xie, and Huazhong Yang. "Nonvolatile Memory Allocation and Hierarchy Optimization for High-Level Synthesis." Proc. *Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2015.

#### **Abstract**

Memory-Centric Architectures: Bridging the Gap Between Compute and Memory

by

#### Shuangchen Li

While the compute part keeping scaling for decades, it becomes more and more difficult for the memory part to catch up. This mismatch raises two grand challenges. One is referred to as the "Memory Wall", in which case the memory latency and bandwidth turn to be the bottleneck, slowing down the system no matter how computing resource improves. The other one is referred to as the "Power Wall", which demands high power efficiency due to a limited power budget, whereas the energy spent on the memory accesses dominates the total energy consumption.

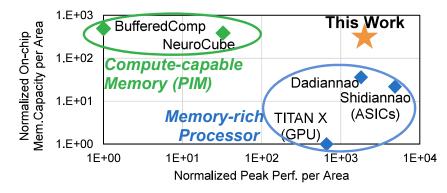

To address those challenges, this dissertation focuses on designing memory-centric architectures to bridge the gap between compute and memory. Two types of memory-centric architecture have been investigated. The first one is the compute-capable memory architecture, which moves computing resources to the memory side. The in-memory computing scheme explores larger bandwidth and reduces data movement overhead. The second one is the memory-rich accelerator architecture, which is designed with tightly coupled high performance computing resource and large-capacity on-die memory. The in-situ computing design provides benefits as a non *Von Neumann* architecture. This dissertation has proposed five architectures, which cover both compute-capable memory and memory-rich accelerator architectures, both the offshore DRAM and emerging non-volatile memory technologies, and a large range of the important applications, such as deep learning, database, graph processing.

# **Contents**

| Cı | ırricu                                                                  | llum Vitae                                                               | vi                 |  |  |  |

|----|-------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|--|--|--|

| Al | ostrac                                                                  | et e e e e e e e e e e e e e e e e e e                                   | viii               |  |  |  |

| 1  | 1.1                                                                     | oduction  Demands for Memory-Centric Architectures                       | 1 2                |  |  |  |

|    | 1.2<br>1.3                                                              | Opportunities and Challenges                                             | 3<br>5             |  |  |  |

| 2  | Bac                                                                     | kgrounds and Related Work                                                | 7                  |  |  |  |

|    | 2.1<br>2.2<br>2.3<br>2.4                                                | System Memory and DRAM Basics                                            | 7<br>8<br>11<br>13 |  |  |  |

| 3  | PINATUBO: A Processing in Emerging Non-volatile Memory Architecture for |                                                                          |                    |  |  |  |

|    |                                                                         | x Bitwise Operations                                                     | 15                 |  |  |  |

|    | 3.1<br>3.2                                                              | Motivation and Overview                                                  | 16<br>18           |  |  |  |

|    | 3.3                                                                     | Architecture and Circuit Design                                          | 23                 |  |  |  |

|    | 3.4                                                                     | Experiment                                                               | 24                 |  |  |  |

|    | 3.5                                                                     | Summary                                                                  | 28                 |  |  |  |

| 4  | PRI                                                                     | ME: Processing In ReRAM-based Main Memory                                | 30                 |  |  |  |

|    | 4.1                                                                     | PRIME Architecture                                                       | 31                 |  |  |  |

|    | 4.2                                                                     | System-Level Design                                                      | 45                 |  |  |  |

|    | 4.3                                                                     | Evaluation                                                               | 52                 |  |  |  |

|    | 4.4                                                                     | Conclusion                                                               | 58                 |  |  |  |

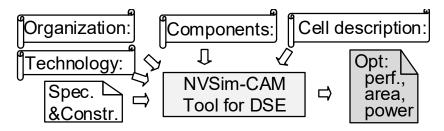

| 5  |                                                                         | SIM-CAM: A Circuit-Level Simulator for Emerging Nonvolatile Memory based |                    |  |  |  |

|    |                                                                         | tent-Addressable Memory                                                  | 59                 |  |  |  |

|    | 5.1                                                                     | Background and Overview                                                  | 61                 |  |  |  |

|   | 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8 | Motivation .  SCOPE Architecture .  H²D Arithmetic .  Discussions .  A Case Study: Deep Learning .  Experiments .  Conclusion . | 12<br>13<br>13<br>13<br>13 |

|---|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 7.3<br>7.4<br>7.5<br>7.6                      | SCOPE Architecture                                                                                                              | 12<br>13<br>13<br>13       |

|   | 7.3<br>7.4<br>7.5                             | SCOPE Architecture                                                                                                              | 12<br>13<br>13<br>13       |

|   | 7.3<br>7.4                                    | SCOPE Architecture                                                                                                              | 12<br>13<br>13             |

|   | 7.3                                           | SCOPE Architecture                                                                                                              | 12                         |

|   |                                               | SCOPE Architecture                                                                                                              | 12                         |

|   | 1.2                                           | Mouvation                                                                                                                       |                            |

|   | 7.0                                           |                                                                                                                                 |                            |

|   | 7.1                                           | Background                                                                                                                      | 12                         |

| 7 | SCC                                           | OPE: A Stochastic Computing Engine for DRAM-based In-situ Accelerator                                                           | 1                          |

|   | 6.6                                           | Conclusion                                                                                                                      | 1                          |

|   | 6.5                                           | Discussion: Which DRISA is Better                                                                                               | 1                          |

|   | 6.4                                           | Experiments                                                                                                                     |                            |

|   | 6.3                                           | Accelerating CNN: A Case Study                                                                                                  |                            |

|   | 6.2                                           | DRISA Architecture                                                                                                              |                            |

| • | 6.1                                           | Overview                                                                                                                        |                            |

| 6 | DRI                                           | SA: A DRAM-based Reconfigurable In-Situ Accelerator                                                                             |                            |

|   | 5.5                                           | Conclusion                                                                                                                      |                            |

|   | 5.4                                           | 3D Vertical ReRAM based TCAM: A case study                                                                                      |                            |

|   |                                               |                                                                                                                                 |                            |

|   | 5.3                                           | Design Space Exploration with NVSIM-CAM                                                                                         |                            |

# Chapter 1

# Introduction

For decades, computing capability has been scaling quite well. For example, the performance of world's top-1 supercomputer has improved 33× in the past decade [1], and the performance of a single GPGPU has even boosted 24× within three years <sup>1</sup>. The successes do not only owe to the technology development (Moore's Law), but also the innovations of computer architecture, such as super-scaler and multi-core. However, while the compute part is developing so fast, it is difficult for the memory part to catch up. For the memory bandwidth, it took JEDEC seven years to develop from DDR3 to DDR4, and after that (year 2014), the peak memory bandwidth of a single CPU [3] has only improved ~15%. For the memory capacity, the DRAM DIMM capacity doubles every three years [4]. It is much slower than the computing scaling (about doubling every two years) [3] and heavily relies on the about-to-end Moore's Law. For the memory latency, it has only improved 26% during 11 years [5]. The unbalanced scaling capability between compute and memory turns into a grand gap.

To further illustrate the gap, Table 1.1 lists two-generation NVIDIA's GPUs' statistics as an example. From Pascal architecture to Volta [2], the computing performance has boosted  $5.5\times$  while the memory bandwidth improvement is only  $1.2\times$ ; the computing resource improved

<sup>&</sup>lt;sup>1</sup>Comparing NVIDIA K40 5Tops/s with V100 120Tops/s for FP16 performance [2].

| 40% but the memory | capacity | stays t | he same. |

|--------------------|----------|---------|----------|

|--------------------|----------|---------|----------|

|             | Comp. peak perf. | Device <b>Mem.</b> | Comp. tran-   | Device <b>Mem.</b> |

|-------------|------------------|--------------------|---------------|--------------------|

|             | (FP16)           | Bandwidth          | sistors count | Capacity           |

| Pascal-2016 | 22Tops/s         | 732GB/s            | 15.3B         | 16GB               |

| Volta-2017  | 120Tops/s        | 900GB/s            | 21.1B         | 16GB               |

|             | 5.5× vs. 1.2×    |                    | 1.4×          | vs. 1×             |

Table 1.1: An example of two generations NVIDIA GPU [2] to show the gap between computing and memory.

# 1.1 Demands for Memory-Centric Architectures

While understanding the gap between the compute and memory, bridging the gap is severely demanded from both the hardware and application points of view, motivating us to focus more on the memory architecture design.

For the hardware, memory revolution is essential to achieve the exascale computing target, i.e., building a supercomputer that deliveries  $10^{18}$  ops/s performance with 20GWatt power budget by 2023 [6]. It requires  $11\times$  improvement on performance and  $8.3\times$  improvement on energy efficiency in the next five years. There are two key challenges and both of them are caused by memory problems. The first one is referred to as the "memory wall", in which case the memory bandwidth turns to the system bottleneck, and the performance cannot be improved no matter how much the computing part improves. The second one is the "power wall", in which case energy efficiency must be improved before putting more compute resources due to a limited power budget. In this aspect, studies have showed accessing the data takes more than 2 orders of magnitude energy then the computing [7], leaving the memory as the bottleneck again.

For the applications, as we are entering the big data era, memory plays a more important role. Especially, some of the killer applications are memory bound. They require very simple

computing but feed on large memory bandwidth. For example, the graph processing applications could speedup  $\sim 5 \times$  given  $\sim 5 \times$  more memory bandwidth [8].

As a conclusion, all these demands inspire us to rethink the whole computer architecture design. After decades of mainly focusing on the computing part, now it is the time to shift our major focus to the memory part. On contrary to the conventional compute-centric architecture, all these demands are driving us towards the memory-centric architecture, which offers us many opportunities to bridge the gap between compute and memory.

# 1.2 Opportunities and Challenges

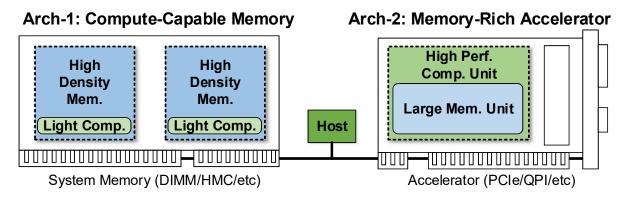

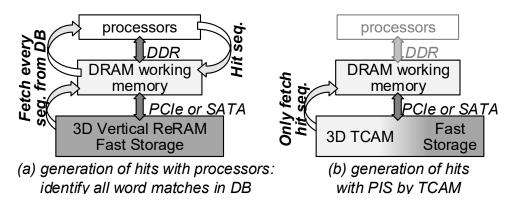

Towards the memory-centric design, there are two promising types of architectures, as shown in Figure 1.1.

Figure 1.1: Two solutions: the compute-capable memory and the memory-rich accelerator.

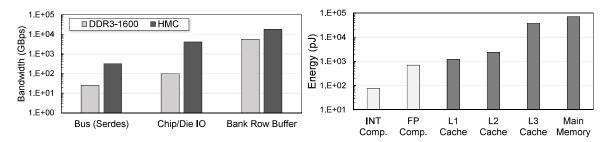

Compute-Capable Memory. The first architecture (Figure 1.1(a)) is referred to as the compute-capable memory. This architecture designs lightweight computing units on the system main memory side. It is also known as Processing-in-memory (PIM) or In-memory computing architecture. The **opportunities** of this architecture is two folded. First, it can embrace the large memory internal bandwidth, which is otherwise wasted. In addition, the closer towards the memory cell, the larger bandwidth is offered. Figure 1.2(left side) shows the internal bandwidth potential of both DDR3 and HMC memory. From the DDR or HMC IO to the row buffer,

there is a  $57\times$  and  $222\times$  bandwidth improvement, respectively. Second, it eliminates the data movement between the host and the memory by performing the computing on the memory side. As shown in the right side of Figure 1.2, the energy spent on the data movement from the system memory (the last bar) is  $\sim 100\times$  larger than that on computing, which highlights the importance of minimizing the data movement. It is reported that the compute-capable memory architecture can archive 80% energy saving on certain applications [8].

However, there are also **challenges**. First, memory industry is very cost-sensitive, so memory is highly optimized for low cost (density). Unfortunately, adding computing elements to inside the memory would incur larger area overhead than that could be accepted by the industry. Second, due to the cost-optimized design rule, it is difficult to design high performance computing units on the memory side. Even if 3D stacking technology is adopted, the empty area on the logic die where the memory-side processors locate are tightly limited [9]. For example, one of the HMC-based compute-capable memory reported 132Gops/s [10], whereas a state-of-the-art GPGPU offers 120Tops/s [2].

Figure 1.2: Left: Memory bus and internal bandwidth at chip/bank hierarchy for both DDR3 and HMC. Right: Data movement dominates the energy consumption (dynamic energy only with 32K-256K-4M-8G memory hierarchy at 45nm [11]).

**Memory-Rich Accelerator.** The second architecture (Figure 1.1(b)) is referred to as the memory-rich accelerator. It tries to merge the compute and memory by packing more on-die memories with the accelerator. The **opportunities** are obvious: accessing on-chip memory embraces larger bandwidth, lower latency, and smaller energy consumption. The benefits encourage many designs to adopt this architecture. For example, the neural network accelera-

tor Dadiannao [12] packs 36MB eDRAM scratchpad memory, Google's TPU packs a 24MB SRAM which consumes the same area as processing units [13], and POWER-9 [14] also packs 128MB eDRAM L3 cache.

However, the **challenges** are also noticeable. The capacity of the memory that can be packed on-die is limited. This is because to be compatible with CMOS technology, the on-die memory are either SRAM or eDRAM. Their memory cell area is large: SRAM cell is  $\sim 146F^2$  [15] and eDRAM cell is  $60F^2 \sim 80F^2$  [16], whereas the commodity DRAM is only  $6F^2$ . An exception is the interposer-based architecture, such as Volta GPU [2], which packs commodity DRAM with processors through links on the interposer. However, its bandwidth, latency, energy consumption are all not compatible with the on-die memory. For example, the on-die eDRAM in Dadiannao [12] offers 1.65TB/s bandwidth, 4.95ns latency, and 0.07pJ/bit [15] energy efficiency, whereas the interposer connected HBM in V100 [2] only has 0.9TB/s bandwidth, but requires  $\sim 200$ ns latency [17] and 3.7pJ/bit [18] energy.

## 1.3 Contributions

The **goal** of this dissertation is to explore both the compute-capable memory and memory-rich accelerator architecture, to bridge the gap between compute and memory. Meanwhile, we have addressed the challenges of both them, i.e., the tight area constraints for the compute-capable memories and the limited memory capacity for the memory-rich accelerator. To this end, the **key idea** of this dissertation is to leverage memory cell themselves for computing. Specifically, we have two compute-capable memory designs.

- PINATUBO, which accelerates the bulk bitwise operations inside the NVM-based main memory with minimal area overhead by leveraging the resistive feature of the memory cells.

- PRIME, a morphable processing-in-memory architecture for ReRAM-based main mem-

ory, which efficiently accelerates neural computation by leveraging ReRAMs unique yet largely overlooked property having both computation and data storage capability in one device.

We also have three memory-rich accelerator designs.

- NVCAM, which designs the accelerator with the content-addressable memory to serve searching tasking with high energy efficiency.

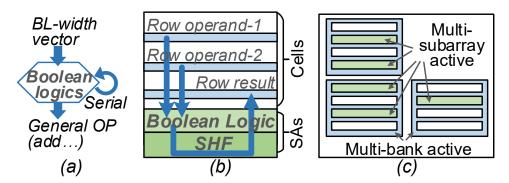

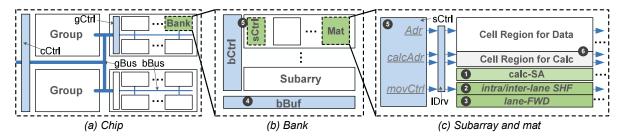

- DRISA, which is an in-situ accelerator built using DRAM technology with the majority of the area consisting of DRAM memory arrays, and computes with logic on every memory bitline, achieving the goal of large memory capacity for the accelerator.

- SCOPE, which combines the stochastic computing arithmetic with the DRISA's in-situ architecture, to further improve its performance.

The architectures that proposed in this dissertation have a board coverage in both terms of technologies and the applications: three of the designs adopts the emerging non-volatile memory technologies, and the other two designs leverage the offshore DRAM technology. In addition, these architectures have covered a large range of applications such as deep learning inference and training, graph processing, database, and bioinformatics.

To conclude, by exploiting the memory cells' special features, we leverage the memory for the computing tasks, and build better memory-centric architectures to further close the gap between compute and memory. The architectures proposed highlight their contributions to tackle the tight area constraints challenge for the compute-capable memory architecture and the limited memory capacity problem for the memory-rich accelerator architecture.

# Chapter 2

# **Backgrounds and Related Work**

In this chapter, we first introduce basic backgrounds about the system memory. Then, we survey the related work for both the compute-cable memory and the memory-rich accelerator architectures, with emphasize on demonstrate the distinguishing of the architecture proposed in this dissertation.

# 2.1 System Memory and DRAM Basics

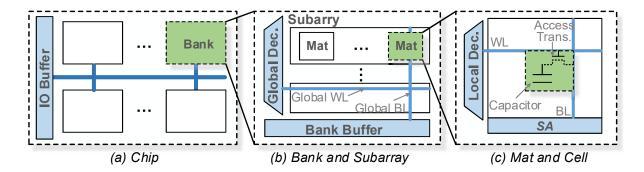

Figure 2.1 shows the basic circuit of commercial DRAMs. A DRAM chip contains multiple banks, which are connected with global buses. Inside a bank, there are subarrays that share global BLs. Global decoders decode parts of the addresses to the global wordlines (WLs) that connected to different subarrays. Cell matrices (Mats) are basic memory arrays that line up and make a subarray. Every Mat has its private local WL decoders, drivers, and sense amplifiers (SAs). A DRAM cell is constructed with a access transistor and a capacitor (1T1C). Within one chip, only a single row in a subarray is activated at one time. The Mats in the subarray work in a lock-step manner.

A DRAM process and a logic process are totally different and incompatible [19]. It is

Figure 2.1: The DRAM basics. Glossary: WL - Wordline; BL - Bitline; SA - Sense Amplifier; Dec - Decoder.

difficult to build logics with a DRAM process, or the other way around. The transistors in a DRAM process are extremely optimized for low leakage, which draws their speed down. For example, substrate bias are added to increase threshold voltage for extra leakage saving. Moreover, a DRAM process usually has three metal layers but logic processes can get more than twelve metal layers, which means logic circuits in a DRAM process will suffer from higher interconnection overhead. As a summary, building complex logic circuits in a DRAM process is problematic with 22% performance degradation and 80% area overhead [19], which is a major reason why earlier PIM researches that put processors and DRAM on the same die haven't turned into a success. On the other hand, building DRAM cells with a logic process turns to be eDRAMs, which is not efficient, either. eDRAM results in 10x area overhead [16, 20], around 4× more power, and 100× shorter retention time [20], compared with DRAMs.

# 2.2 Emerging Nonvolatile Memory Basics

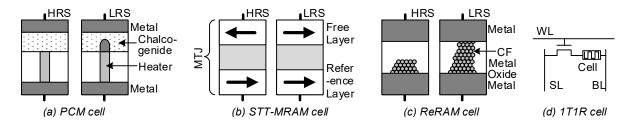

**Device.** Although the working mechanism and the features varies, the three typical types of the NVM have common basics: all of them are based on resistive cell. To represent logic "0" and "1", they rely on the difference of cell resistance ( $R_{\text{high}}$  or  $R_{\text{low}}$ ), which is archived by different state of the device, i.e., high-resistance state (HRS) and low-resistance state (LRS). To

switch between logic "0" and "1", certain polarity, magnitude, and duration voltage is required to be applied on the cell.

Figure 2.2: Device Basics for (a) PCM (b) STT-MRAM (c) ReRAM, and the (d) 1T1R Cell Structure. *PCM* [21] uses phase change material (e.g., chalcogenide glass) to archive two device states. The amorphous state provides HRS and the crystalline state is the LRS. They represent logic "0" and "1" respectively. Switching between those two states requires different heating temperatures and durations, i.e., different write current. Specifically, changing from LRS to HRS is referred as a RESET operation, which requires a high and short current pulse. In contrast, switching from HRS to LRS is denoted as a SET operation, which requires a moderate and long current pulse.

STT-MRAM [22] relies on the magnetic tunnel junction (MTJ) with a fixed ferromagnetic layer (reference layer) and a programmable ferromagnetic layer (free layer). The magnetization direction of the free layer provides two different states. Parallel magnetization direction of the free and reference layer leads to LRS (logic "0"), and in contrast, the anti-parallel magnetization direction leads to HRS (logic "1"). To write logic "1", a negative voltage difference is required. To write logic "0", a positive voltage difference needs to be established.

*ReRAM* [23] sandwiches a metal-oxide layer with two metal layers. The nanoscale conductive filaments (CF) provides two states. A well established CF provides LRS (logic "1") and cut-off CF leads to HRS (logic "0"). When certain polarity voltage is required to switch between HRS and LRS.

**Peripheral Circuitry.** Because of the special feature of the memory cell device, e.g., resistive cell instead of charge-based cell, the peripheral circuitry demands special designs. *Cell*

structure of all the three technologies can implement the memory block with a 1T1R structure [24–26], where it has a wordline (WL) controlling the access transistor, a bitline (BL) for data sensing, and source line (SL) to sense to provide write current (for ReRAM and STT-MRAM in particular). In order to provide high density, 1S1R (1-selector-resistor) structure is proposed for both PCM [27] and ReRAM [28] with only  $4F^2$  cell area. 3D-stacked memorycell is also proposed [29, 30]. To further improve the density, multi-level cell (MLC) is proposed for all of those three NVM [31–33].

Sense amplifier (SA) is the major different between the NVM and conventional SRAM or DRAM. While conventional charge-based memory using a few transistor to amplify the charge difference, the resistance-based NVM has to convert the difference in resistance ( $R_{\rm high}/R_{\rm low}$ ) as voltage or current, which are referred as voltage and current sensing (VSA and CSA), respectively. NVM prefers CSA [34] due to its advantages of fast access and robustness of variation. Besides, NVM requires extra reference cells for sensing  $^1$ . Considering the large area of CSA and the extra reference cell, it is typical to share SA among adjacent columns, which leads to a smaller row buffer size [35].

Other difference besides SA in the peripheral circuitry also exits. The write driver (WD) [24, 30] is design to provide certain polarity, magnitude, and duration voltage or current across the BL and the SL. The support circuit for restore in DRAM is not necessary in NVM, thanks to its non-volatility and non-destructive read. Extra lift time enhancement circuit is probably required for PCM and ReRAM, e.g., flip-N-write [36] and read-before-write [37].

**NVM-based system main memory.** As the NVM technology turns mature, all the three technologies (PCM [37–39], ReRAM [40], and STT-MRAM [41–43]) are proposed as a candidate to be the next generation main memory, due to NVM's high density, better scalability, and ultra-low standby power. In order to tackle the limited lifetime problem of PCM and ReRAM, architecture-level solution such as wear-leveling [39] and comparison-based write [36, 37] are

<sup>&</sup>lt;sup>1</sup>Although self-reference is possible in STT-MRAM, it incurs large latency/energy overhead.

proposed. To migrate the expensive write operation overhead, architecture supports such as write-cancelation [44] and data preset [45] are proposed.

# 2.3 Related Work on Compute-Capable Memories

Early Effort on Processing-in-Memory Architectures The idea of PIM can be traced back to the 1990s. A bulk of works, including IRAM [46], DIVA [47], Active Page [48], FlexRAM [49], proposed the PIM-based architecture by integrating computing logics and DRAM on one chip. We refer to these work as 2D-based PIM. Based on the observation that memory latency is 4x larger than raw DRAM access time, D. Patterson [46] proposed IRAM to merge the processing and DRAM on the same chip. By replacing the original cache hierarchy with DRAM on Alpha 21164 (the fastest processor at that time), they were able to achieve 1x-2x speedup on the applications of database and sparse computing. To further exploit the internal DRAM bandwidth, IRAM also explores the possibility of introducing PIM to vector processor, while the implementation of PIM on traditional 2D DRAM experiences great challenges in cost and manufacture. These work has been criticized for the difficulty of integrating complex logics with DRAM technologies. Even including simple adders in DRAM process technologies induces large overhead and low effective performance. However, recently, this approach has been revisited. Buffered Comparator [50, 51]) puts lightweight comparator with DRAMs. Pro-PRAM [52] leverages 2D NVM for PIM. It uses NVM's lifetime enhancement peripheral circuits (data-comparison write and flip-n-write) for in memory computing. Even thought the area overhead is partially solved by adding much less computing unit, the computing performance of that turns into a new bottleneck.

As a summary, PIM sticks with a main memory position that is optimized for memory density. Building logic elements inside the memory benefit a lot, but the area overhead makes a server limitation.

3D Stacking based Near Data Computing Architectures The emerging technology of 3D die stacking, either through-silicon-via (TSV) based 3D integration or interposer-based 2.5D integration, has alleviated the manufacture concerns of PIM to some extent, which is referred to as 3D-based PIM. The vertical 3D die-stacking with TSVs allows the stacking of multiple memory dies directly on top of the logic die to achieve high memory bandwidth; while the 2.5D silicon interposer allows a high bandwidth connection between the memory stack and the logic die on the same substrate. There are two main streams for the 3D-stacking memory: Hybrid Memory Cube (HMC) and High Bandwidth Memory (HBM) [8, 10, 53–66]. Since the power and area budget is quite limited in the logic die, the processor in HMC prefers to be light-weight, which might not support complex functions, such as branch prediction, dynamic scheduling, and cache hierarchy. IBM [67] proposed Active Memory Cube (AMC), which adds computational elements on the base logic layer to accelerate scientific computing applications. They designed the base logic layer for efficiency and versatility and came up with the following design choices: no caches, hardware scheduling of instructions, a vector instruction set, predicated execution, and gather-scatter accesses directly to memory in the Cube. Several attempts have also been made on HMC-based energy efficient domain specific accelerators. Guo et al. [68] proposes to integrate various accelerators into the base logic layer to obtain an energy efficient accelerated library for memory bounded operations, e.g. matrix operation, data reshaping, and FFT. Gao et al. [69] proposed Tetris, an HMC-based neural network accelerator, which moves the logic of the accumulation operation to the DRAM die, or further into the bank, to reduce the double access of the intermediate results in the neural network applications.

As a summary, the 3D-stacking based PIM architectures are more practical after that researches have taken the lessons from the early 2D-based PIM effort. It revives the PIM research with the help of the severer-than-ever demands of bridging the gap between compute and memory. However, the empty area on the logic die is limited [9], not to mention the fixed power

budget and thermal constraints for the system memory. As a result, the computing performance of the 3D-based PIM is limited. In addition, as shown in Figure 1.2, the closer the computing units are designed to the data, the more benefit we can have from the compute-capable memory architecture. Though on the memory side, the computing units and the memory are still in different dies in the 3D-based PIM. It might not embrace as much as the benefit comparing with the 2D-based PIM.

**Revolutionary DRAM Designs** Recent research has evolved DRAM memory by adding additional functional capability [70]. Rowclone [71] has supported in-DRAM row-to-row copy with minor modification on existing DRAMs. Seshadri *et al.* [72] has explored fast bulk bitwise operations in DRAMs. However, it only support AND/OR operations, which are not logic complete, and hence not for general purpose. DRAF [73] has proposed a DRAM-based FPGA, where DRAM cells are used as look-up tables.

As a summary, the revolutionary DRAM is more like a light version of the 2D-based PIM. To address the cost-sensitive challenge, they come up with smart ideas to minimize the area overhead. However, this come with the drawback of low computing performance, or limited support for the computing operation types.

## 2.4 Related Work on Memory-Rich Accelerators

Memory-Rich Processors Interposer-based 2.5D integration is already embraced by the industry for integrating 3D stacked memories with large-scale designs, due to its feasibility over true 3D integration in terms of cost and better thermal profile. For example, AMD's Fury X GPU integrates 4GB of 3D stacked High-Bandwidth Memory (HBM) [74]; Nvidia's Pascal/Volta GPU increases the capacity of HBM to 16GB [75]; Intel's Knights' Landing CPU also integrates 16GB high bandwidth stacked DRAM [76]. Xilinx recently also announced the Virtex Ultrascale+ FPGA that integrates 8GB HBM [77]. Lots of designs that accelerate NN appli-

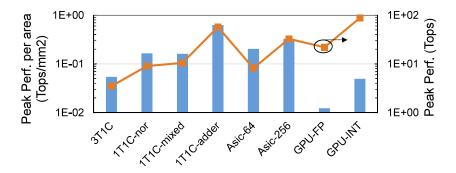

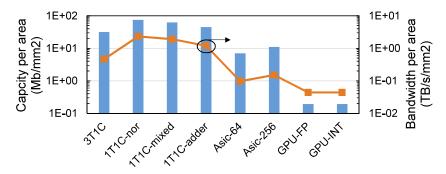

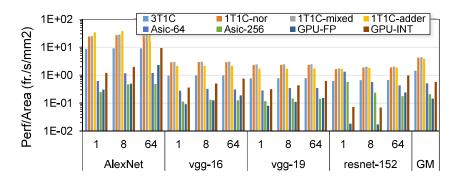

cations with various platforms (ASIC, GPU, FPGA) with large on-chip memory [78–80] have been proposed. TrueNorth [81–84] computes with on-chip SRAM-based crossbars and counters. DaDianNao [78] has 36MB of on-chip memories, but *DRISA* has 512MB. NeuroCube [10] is a PIM architecture for NNs. Though its memory capacity is large, its performance is low.

As a summary, as mentioned in the introduction, the interposer connected memories, although having large memory, the bandwidth, latency, and energy efficiency are not as good as the on-die memories. On the other hand, the on-die memory's density is low and the memory capacity packed is not large enough.

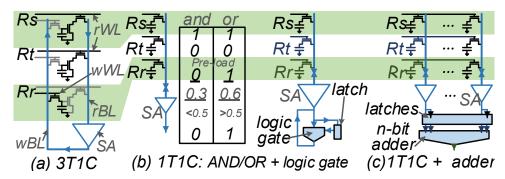

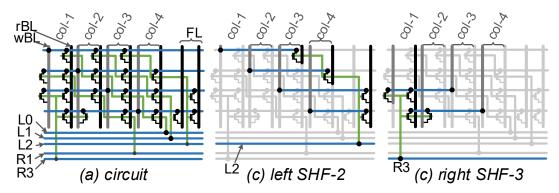

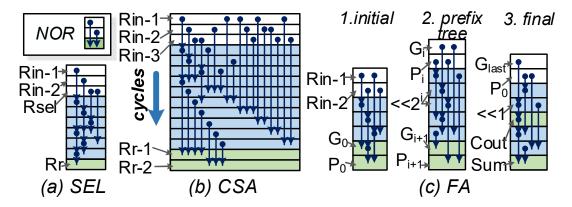

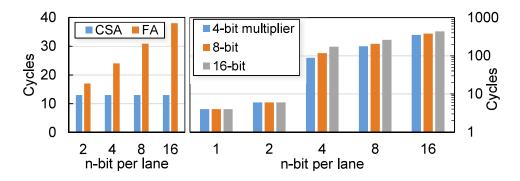

In-situ Computing Accelerators Automata [85] has implemented a reconfigurable processor with a DRAM process. It computes with counters and finite-state machines, by storing programmed states in the DRAM while streaming in the data. Mikamonu [86–88] has proposed to compute with the NOR logic provided by the 3T1C DRAM cell or NVMs, but their proposal does not have data movement mechanisms. Therefore, complex functions (like full adders) are not supported. NVM is very suitable for associate memory implementation [89–93]. Researches have use the NVM-based TCAM in CPU [94], GPGPU [95], and accelerators [96,97]. NVM is also designed as LUT [98] and nonvolatile logic gates [99]. Recent work also take use of ReRAM crossbar's special feature, to implement IMPLY-based logics [100–102]. Also taking use of the crossbar structure, researcher are able to implement dot-product function with high energy efficiency, which is widely used in deep learning acceleration [103, 104].

# Chapter 3

# PINATUBO: A Processing in Emerging Non-volatile Memory Architecture for Bulk Bitwise Operations

The goal of this chapter is to show Non-volatile memory (NVM)'s potential on enabling PIM architecture, while almost all existing efforts focus on DRAM systems and heavily depend on 3D integration. NVM's unique features, such as resistance-based storage (in contrast to charge-based in DRAM) and current-sensing scheme (in contrast to the voltage-sense scheme used in DRAM), are able to provide inherent computing capabilities [101, 105]. Therefore, NVM can enable PIM without the requirement of 3D integration. In addition, it only requires insignificant modifications to the peripheral circuitry, resulting in a cost-efficient solution. Furthermore, NVM-enabled PIM computation is based on in-memory analog signals, which is much more energy efficient than other work that uses digital circuits.

In this chapter, we propose PINATUBO<sup>1</sup>, a <u>Processing In Non-volatile memory ArchiTecture</u>

<sup>&</sup>lt;sup>1</sup>Mount Pinatubo is an active volcano that erupted in 1991. We name our PIM design after Pinatubo, because PIM researches also had a great moment in 1990s, and we believe it is their time to revive. The novel architecture's impact will be like a volcano eruption.

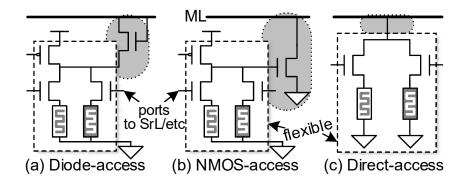

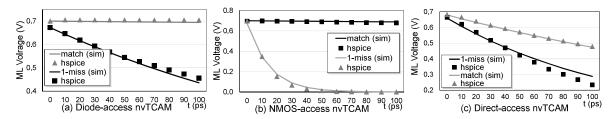

for b<u>U</u>lk <u>B</u>itwise <u>O</u>perations, including OR, AND, XOR, and INV operations. When PINATUBO works, two or more rows are activated simultaneously, the memory will output the bitwise operations result of the open rows. PINATUBO works by activating two (or more) rows simultaneously, and then output of the memory is the bitwise operation result upon the open rows. The results can be sent to the I/O bus or written back to another memory row directly. The major modifications on the NVM-based memory are in the sense amplifier (SA) design. Different from a normal memory read operation, where the SA just differentiates the resistance on the bitline between  $R_{\text{high}}$  and  $R_{\text{low}}$ , PINATUBO adds more reference circuit to the SA, so that it is capable of distinguishing the resistance of { $R_{\text{high}}/2$  (logic "0,0"),  $R_{\text{high}}||R_{\text{low}}$  (logic "0,1"),  $R_{\text{low}}/2$  (logic "1,1")} for 2-row AND/OR operations. It also potentially supports multi-row OR operations when high ON/OFF ratio memory cells are provided. Although we use 1T1R PCM as an example in this paper, PINATUBO does not rely on a certain NVM technology or cell structure, as long as the technology is based on resistive-cell.

Our contributions in this chapter are listed as follows,

- We propose a low-cost processing-in-NVM architecture with insignificant circuit modification and no requirement on 3D integration.

- We design a software/hardware interface which is both visible to the programmer and the hardware.

- We evaluate our proposed architecture on data intensive graph processing and data-base applications, and compare our work with SIMD processor, accelerator-in-memory PIM, and the state-of-the-art in-DRAM computing approach.

# 3.1 Motivation and Overview

Bitwise operations are very important and widely used by database [106], graph processing [107], bio-informatics [108], and image processing [109]. They are applied to replace

expensive arithmetic operations. Actually, modern processors have already been aware of this strong demand, and developed accelerating solutions, such as Intel's SIMD solution SSE/AVX.

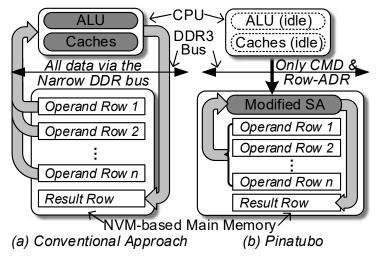

Figure 3.1: Overview: (a) Computing-centric approach, moving tons of data to CPU and write back. (b) The proposed PINATUBO architecture, performs *n*-row bitwise operations inside NVM in one step.

We propose PINATUBO to accelerate the bitwise operations inside the NVM-based main memory. Figure 3.1 shows the overview of our design. Conventional computing-centric architecture in Figure 3.1 (a) fetches every bit-vector from the memory *sequentially*. The data walks through the narrow DDR bus and all the memory hierarchies, and finally is executed by the limited ALUs in the cores. Even worse, it then needs to write the result back to the memory, suffering from the data movements overhead again. PINATUBO in Figure 3.1 (b) performs the bit-vector operations inside the memory. Only commands and addresses are required on the DDR bus, while all the data remains inside the memory. To perform bitwise operations, PINATUBO activates two (or more) memory rows that store bit-vector simultaneously. The modified SA outputs the desired result. Thanks to in-memory calculation, the result does not need the memory bus anymore. It is then written to the destination address thought the WD directly, bypassing all the I/O and bus.

PINATUBO embraces two major benefits from PIM architecture. First, the reduction of data movements. Second, the large internal bandwidth and massive parallelism. PINATUBO

performs a memory-row-length (typical 4Kb for NVM) bit-vector operations. Furthermore, it supports multi-row operations, which calculate multi-operand operations in one step, bringing the equivalent bandwidth  $\sim 1000 \times$  larger than the DDR3 bus.

# 3.2 Architecture and Circuit Design

In this section, we first show the architecture design that enables the NVM main memory for PIM. Then we show the circuit modifications for the SA, LWL driver, WD, and global buffers.

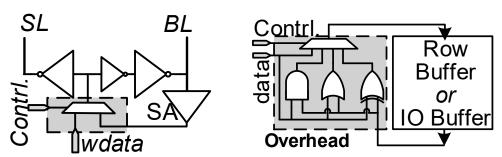

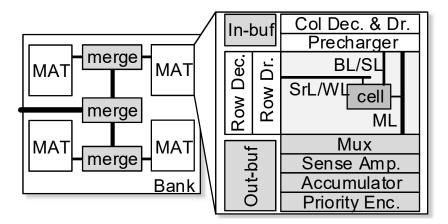

#### **3.2.1** From Main Memory to PINATUBO

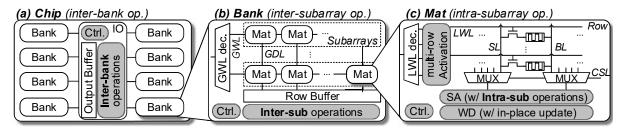

Main memory has several physical/logic hierarchies. *Channels* runs in parallel, and each channel contains several *ranks* that share the address/data bus. Each rank has typical 8 physical *chips*, and each chip has typical 8 *banks* as shown in Figure 3.2 (a). Banks in the same chip share the I/O, and banks in different chips work in a lock-step manner. Each bank has several *subarrays*. As Figure 3.2 (b) shows, Subarrays share the GDLs and the global row buffer. One subarray contains several *MATs* as shown in Figure 3.2 (c), which also work in the lock-step manner. Each Mat has its private SAs and WDs. Since NVM's SA is much larger than DRAM, several (32 in our experiment) adjacent columns share one SA by a MUX.

Figure 3.2: The PINATUBO Architecture. Glossary: Global WordLine (GWL), Global DataLine (GDL), Local WordLine (LWL), SelectLine (SL), BitLine (BL), Column Select-Line (CSL), Sense Amplifier (SA), Write Driver (WD).

According to the physical address of the operand rows, PINATUBO performs three types of bitwise operations: intra-subarray, inter-subarray, and inter-bank operations.

Intra-subarray operations. If the operand rows are all within one subarray, PINATUBO performs intra-subarray operations in each MAT of this subarray. As shown in Figure 3.2 (c), the computation is done by the modified SA. Multiple rows are activated simultaneously, and the output of the modified SA is the operation result. The operation commands (e.g., AND or OR) are sent by the controller, which change the reference circuit of the SA. We also modify the LWL driver is also implemented to support multi-row activation. If the operation result is required to write back to the same subarray, it is directly fed into the WDs locally as an in-place update.

**Inter-subarray operations.** If the operand rows are in different subarrays but in the same bank, PINATUBO performs inter-subarray operations as shown in Figure 3.2 (b). It is based on the digital circuits added on the global row buffer. The first operand row is read to the global row buffer, while the second operand row is read onto the GDL. Then the two operands are calculated by the add-on logic. The final result is latched in the global row buffer.

**Inter-bank operations.** If the operand rows are even in different banks but still in the same chip, PINATUBO performs inter-bank operations as shown in Figure 3.2 (a). They are done by the add-on logic in the I/O buffer, and have a similar mechanism as inter-subarray operations.

Note that PINATUBO does not deal with operations between bit-vectors that are either in the same row or in different chips. Those operations could be avoided by optimized memory mapping, as shown in Section 3.3.

# 3.2.2 Peripheral Circuitry Modification

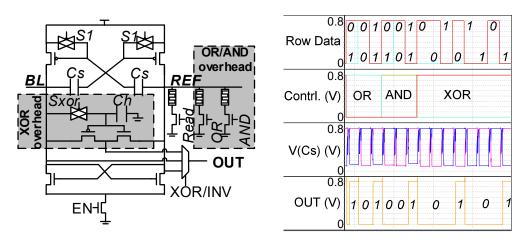

**SA Modification:** The key idea of PINATUBO is to use SA for intra-subarray bitwise operations. The working mechanism of SA is shown in Figure 3.3. Different from the charge-based

DRAM/SRAM, the SA for NVM senses the resistance on the BL. Figure 3.3 shows the BL resistance distribution during read and OR operations, as well as the reference value assignment. Figure 3.3 (a) shows the sensing mechanism for normal reading (Though the SA actually senses currents, the figure presents distribution of resistance for simplicity). The resistance of a single cell (either  $R_{low}$  or  $R_{high}$ ) is compared with the reference value ( $R_{ref-read}$ ), determining the result between "0" and "1". For bitwise operations, an example for a 2-row OR operation is shown in Figure 3.3 (b). Since two rows are activated simultaneously, the resistance on the BL is the parallel connection of two cells. There could be three situations:  $R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{low}||R_{l$

Figure 3.3: Modifying Reference Values in SA to Enable PINATUBO.

Figure 3.4 (a) shows the corresponding circuit modification based on the CSA [110]. As explained above, we add two more reference circuits to support AND/OR operations. For XOR, we need two micro-steps. First, one operand is read to the capacitor  $C_h$ . Second, the other operand is read to the latch. The output of the two add-on transistors is the XOR result. For INV, we simply output the differential value from the latch. The output is selected among

<sup>&</sup>lt;sup>2</sup>"||" denotes production over sum operation.

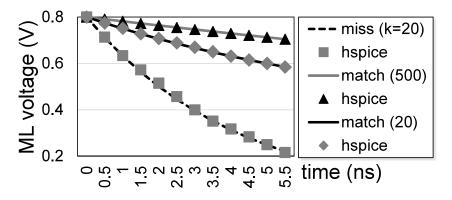

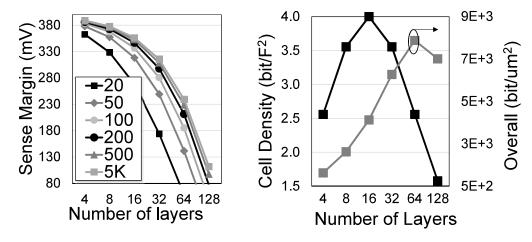

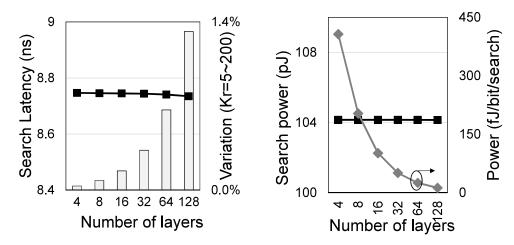

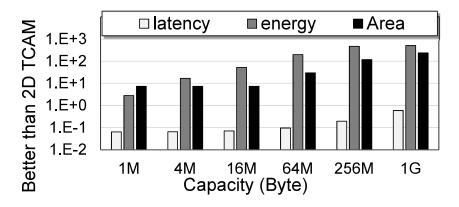

READ, AND, OR, XOR, and INV results by a MUX. Figure 3.4 (b) shows the HSPICE validation of the proposed circuit. The circuit is tested with a large range of cell resistances from the recent PCM, STT-MRAM, and ReRAM prototypes [111].

Figure 3.4: Current Sense Amplifier (CSA) Modification (left) and HSPICE Validation (right).

**Multi-row Operations:** PINATUBO supports multi-row operations that further accelerate the bitwise operations. A multi-row operation is defined as calculating the result of multiple operands at one operation. For PCM and ReRAM which encode  $R_{\text{high}}$  as logic "0", PINATUBO can calculate n-row OR operations<sup>3</sup>. After activating n rows simultaneously, PINATUBO needs to differentiate the bit combination of only one "1" that results in "1", and the bit combination with all "0" that results in "0". This leads to a reference value between  $R_{\text{low}}||R_{\text{high}}/(n-1)$  and  $R_{\text{high}}/n$ . This sensing margin is similar with the TCAM design [112]. State-of-the-art PCM-based TCAM supports 64-bit WL with two cells per bit. Therefore we assume maximal 128-row operations for PCM. For STT-MRAM, since the ON/OFF ratio is already low, we conservatively assume maximal 2-row operation.

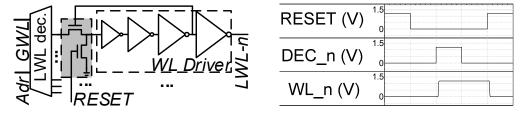

**LWL Driver Modification:** Conventional memory activates one row each time. However, PINATUBO requires multi-row activation, and each activation is a random-access. The modifications of the LWL driver circuit and the HPSICE validation are shown in Figure 3.5. Nor-

<sup>&</sup>lt;sup>3</sup>Multi-row AND in PCM/ReRAM is not supported, since it is unlikely to differentiate  $R_{\text{low}}/(n-1)||R_{\text{high}}|$  and  $R_{\text{low}}/n$ , when n > 2.

mally, the LWL driver amplifies the decoded address signal with a group of inverters. We modify each LWL drive by adding two more transistors. The first transistor is used to feed the signal between inverters back and serves as a latch. The second transistor is used to force the driver's input as ground. During the multi-row activation, it requires to send out the RESET signal first, making sure that no WL has latched anything. Then every time an address is decoded, the selected WL signal is latched and stuck at VDD until the next RESET signal arrives. Therefore, after issuing all the addresses, all the corresponding selected WL are driven to the high voltage value.

Figure 3.5: Local Wordline (LWL) Driver Modification (left) and HSPICE Validation (right).

**WD Modification:** Figure 3.6 (a) shows the modification to a WD of STT-MRAM/ReRAM. We do not show PCM's WD since it is simpler with unidirectional write current. The write current/voltage is set on BL or SL according to the write input data. Normally, the WD's input comes from the data bus. We modify the WD circuit so that the SA result is able to be fed directly to the WD. This circuit bypasses the bus overhead when writing results back to the memory.

Figure 3.6: (a) Modifications to Write Driver (WD). (b) Modifications for Inter-Sub/Bank Operations **Global Buffers Modification:** To support inter-subarray and inter-bank operations, we have to add the digital circuits to the row buffers or IO buffers. The logic circuit's input is the data

from the data bus and the buffer. The output is selected by the control signals and then latched in the buffer, as shown in Figure 3.6 (b).

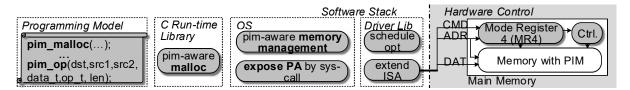

# 3.3 System Support

Figure 3.7 shows an overview of PINATUBO's system design. The software support contains the programming model and run-time supports. The programming model provides two functions for programmers, including the bit-vector allocation and the bitwise operations. The run-time supports include modifications of the C/C++ run-time library and the OS, as well as the development of the dynamic linked driver library. The C/C++ run-time library is modified to provide a PIM-aware data allocation function. It ensures that different bit-vectors are allocated to different memory rows, since PINATUBO is only able to process inter-row operations. The OS provides the PIM-aware memory management that maximizes the opportunity for calling intra-subarray operations. The OS also provides the bit-vector mapping information and physical addresses (PAs) to the PIM's run-time driver library. Based on the PAs, the dynamic linked driver library first optimizes and reschedules the operation requests, and then issues extended instruction for PIM [113]. The hardware control part utilizes the DDR mode register (MR) and command. The extended instructions are translated to DDR commands and issued through the DDR bus to the main memory. The MR in the main memory is set to configure the PIM operations.

Figure 3.7: PINATUBO System Support.

## 3.4 Experiment

In this section, we compare PINATUBO with state-of-the-art solutions and present the performance and energy results.

#### 3.4.1 Experiment Setup

The three counterparts we compare are described below:

**SIMD** is a 4-core 4-issue out-of-order x86 Haswell processor running at 3.3GHz. It also contains a 128-bit SIMD unit with SSE/AVX for bitwise operation acceleration. The cache hierarchy consists of 32KB L1, 256KB L2, and 6MB L3 caches.

**S-DRAM** is the in-DRAM computation solution to accelerate bitwise operations [114]. The operations are executed by charges sharing in DRAM. Due to the read-destructive feature of DRAM, this solution requires copying data before calculation. Only 2-row AND and OR are supported.

**AC-PIM** is an accelerator-in-memory solution, where even the intra-subarray operations are implemented with digital logic gates as shown in Figure 3.6 (b).

The *S-DRAM* works with a 65nm 4-channel DDR3-1600 DRAM. *AC-PIM* and *PINATUBO* work on 1T1R-PCM based main memory whose tRCD-tCL-tWR is 18.3-8.9-151.1ns [115]. *SIMD* works with DRAM when compared with *S-DRAM*, and with PCM when compared with *AC-PIM* and *PINATUBO*. Note that the experiment takes 1T1R PCM for a case study, but PINATUBO is also capable to work with other technologies and cell structures.

The parameters for *S-DRAM* are scaled from existing work [114]. The parameters for *AC-PIM* are collected from synthesis tool with 65nm technology. As to parameters for PINATUBO, the analog/mixsignal part, including SA, WD, and LWL, is extracted from HSPICE simulation; the digital part, including controllers and logics for inter-subarray/bank operations, is extracted from the synthesis tool. Based on those low-level parameters, we heavily modify NVsim [118]

| Vector: pure vector OR operations.                                  |                                                                                            |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| dataset:                                                            | e.g. $19-16-1(s/r)$ means $2^{19}$ -lentgh vector, $2^{16}$ vectors, $2^{1}$ -row $OR$ ops |

|                                                                     | (sequntial/random access)                                                                  |

| Graph:                                                              | bitmap-based BFS for graph processing [107].                                               |

| dataset:                                                            | dblp-2010, eswiki-2013,amazon-2008 [116]                                                   |

| <b>Database:</b> bitmap-based database (Fastbit [106]) application. |                                                                                            |

| dataset: 240/480/720 number of quraying on STAR [117]               |                                                                                            |

Table 3.1: Benchmarks and Data Set

for the NVM circuit modeling, and CACTI-3DD [115] for the main memory modeling, in order to achieve high-level parameters. We also modify the PIN-based simulator Sniper [119] for SIMD processor and the NVM-based memory system. We develop an in-house simulator to evaluate the *AC-PIM*, *S-DRAM*, and PINATUBO. We show the evaluation benchmarks and data sets in Table 3.1, in which *Vector* only has OR operation while *Graph* and *Database* contain all AND, OR, XOR, and INV operations.

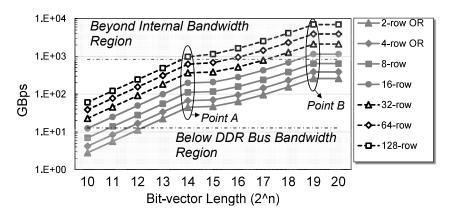

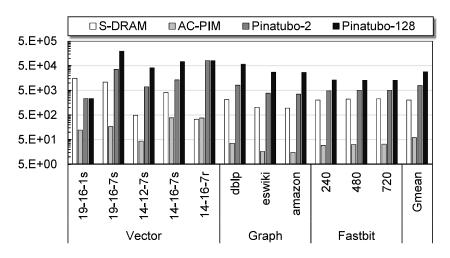

Figure 3.8: PINATUBO's Throughput (GBps) for OR operations.

# 3.4.2 Performance and Energy Evaluation

Figure 3.8 shows PINATUBO's OR operation throughput. We have four observations. First, the throughput increases with longer bit-vectors, because they make better use of the

memory internal bandwidth and parallelism. Second, we observe two turning points, A and B, after which the speedup improvement is showed down. *Turning point* A is caused by the sharing SA in NVM: bit-vectors longer than  $2^{14}$  have to be mapped to columns the SA sharing, and each part has to be processed in serial. *Turning point* B is caused by the limitation of the row length: bit-vectors longer than  $2^{19}$  have to be mapped to multiple ranks that work in serial. Third, PINATUBO has the capability of multi-row operations (as the legends show). For n-row OR operations, larger n provides larger bandwidth. Fourth, the y-axis is divided into three regions: the below DDR bus bandwidth region which only includes short bit-vectors' result; the memory internal bandwidth region which includes the majority of the results; and the beyond internal bandwidth region, thanks to the multi-row operations. DRAM systems can never achieve beyond memory internal bandwidth region.

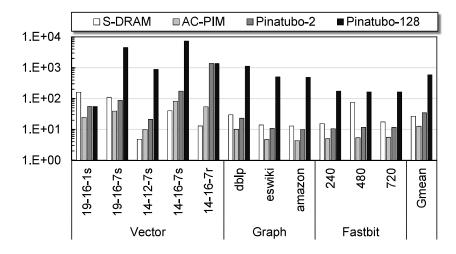

Figure 3.9: Speedup Normalized to SIMD Baseline.

We compare both PINATUBO of 2-row and 128-row operation with two aggressive baselines in Figure 3.9, which shows the speedup on bitwise operations. We have three observations: First, *S-DRAM* has better performance than *PINATUBO-2* in some cases with very long bit-vectors. This is because DRAM-based solutions benefit from larger row buffers, compared with the NVM-based solution. However, the advantage of NVM's multi-row operations still dominates. *PINATUBO-128* is 22× faster than *S-DRAM*. Second, the *AC-PIM* solution

is much slower than *PINATUBO* in every single case. Third, multi-row operations show their superiority, especially when intra-subarray operations are dominating. An opposite example is *14-16-7r*, where all operations are random accesses and it is dominated by inter-subarray/bank operations, so that *PINATUBO-128* is as slow as *PINATUBO-2*.

Figure 3.10: Energy Saving Normalized to SIMD.

Figure 3.10 shows the energy saving result. The observations are similar with those from speedup: *S-DRAM* is better than *PINATUBO-2* in some cases but worse than *PINATUBO-128* on average. *AC-PIM* never has a change to save more energy then any of the other three solutions, since both *S-DRAM* and *PINATUBO* rely on high energy efficient analogy computing. On average, PINATUBO saves 2800× energy for bitwise operations, compared with SIMD processor.

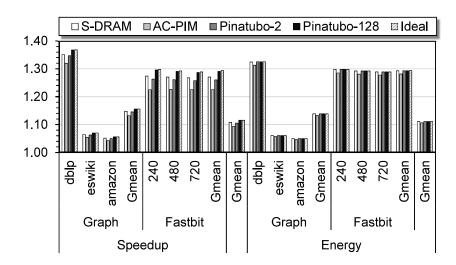

Figure 3.11 shows the overall speedup and energy saving of PINATUBO in the two real-world applications. The *ideal* legend represents the result with zero latency and energy spent on bitwise operations. We have three observations. First, PINATUBO almost achieves the ideal acceleration. Second, limited by the bitwise operations' proportion, PINATUBO can improve graph processing applications by 1.15× with 1.14× energy saving. However, it is data dependent. For the *eswiki* and *amazon* data set, since the connection is "loose", it has to spend most of the time searching for an unvisited bit-vector. For *dblp*, it has 1.37× speedup.

Figure 3.11: Overall Speedup and Energy Saving Normalized to SIMD Baseline.

Third, for the database applications, it achieves  $1.29 \times$  overall speedup and energy saving.

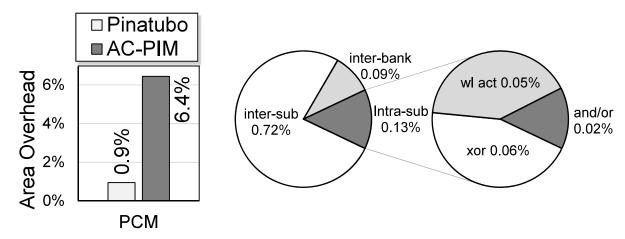

#### 3.4.3 Overhead Evaluation

Figure 3.12 shows the area overhead results. As shown in Figure 3.12 (a), PINATUBO incurs insignificant area overhead only 0.9%. However, *AC-PIM* has 6.4% area overhead, which is critical to the cost-sensitive memory industry. *S-DRAM* reports ~0.5% capacity loss, but it is for DRAM-only result and orthogonal with PINATUBO's overhead evaluation. Figure 3.12 (b) shows the area overhead breakdown. We conclude that the majority area overhead are taken by inter-subarray/bank operations. For intra-subarray operations, XOR operations takes most of the area.

# 3.5 Summary

In this chapter, a processing-in-NVM architecture for bulk bitwise operations is proposed. The computation makes use of NVM's resistive-cell feature and achieves high performance

Figure 3.12: Area Overhead Comparison (left) and Breakdown (right).

and energy efficiency with insignificant area overheads. Experimental results show that the proposed architecture achieves  $\sim 500\times$  speedup and  $\sim 28000\times$  energy saving on bitwise operations, and  $1.12\times$  overall speedup,  $1.11\times$  overall energy saving on data intensive graph processing and database applications with real-world data.

# Chapter 4

# **PRIME: Processing In ReRAM-based**

# **Main Memory**

In this chapter, we propose a novel PIM architecture for efficient NN computation built upon ReRAM crossbar arrays, called PRIME, processing in ReRAM-based main memory. ReRAM has been proposed as an alternative to build the next-generation main memory [120], and is also a good candidate for PIM thanks to its large capacity, fast read speed, and computation capability. In our design, a portion of memory arrays are enabled to serve as NN accelerators besides normal memory. Our circuit, architecture, and software interface designs allow these ReRAM arrays to dynamically reconfigure between memory and accelerators, and also to represent various NNs. The current PRIME design supports large-scale MLPs and CNNs, which can produce the state-of-the-art performance on varieties of NN applications, e.g. top classification accuracy for image recognition tasks. Distinguished from all prior work on NN acceleration, PRIME can benefit from both the efficiency of using ReRAM for NN computation and the efficiency of the PIM architecture to reduce the data movement overhead, and therefore can achieve significant performance gain and energy saving. As no dedicated processor is required, PRIME incurs very small area overhead. It is also manufacture friendly

with low cost, since it remains as the memory design without requirement for complex logic integration or 3D stacking.

The contribution of this paper is summarized as follows:

- We propose a ReRAM main memory architecture, which contains a portion of memory

arrays (full function subarrays) that can be configured as NN accelerators or as normal

memory on demand. It is a novel PIM solution to accelerate NN applications, which

enjoys the advantage of in-memory data movement, and also the efficiency of ReRAM

based computation.

- We design a set of circuits and microarchitecture to enable the NN computation in memory, and achieve the goal of low area overhead by careful design, e.g. reusing the peripheral circuits for both memory and computation functions.

- With practical assumptions of the technologies of using ReRAM crossbar arrays for NN computation, we propose an input and synapse composing scheme to overcome the precision challenge.

- We develop a software/hardware interface that allows software developers to configure

the full function subarrays to implement various NNs. We optimize NN mapping during compile time, and exploit the bank-level parallelism of ReRAM memory for further

acceleration.

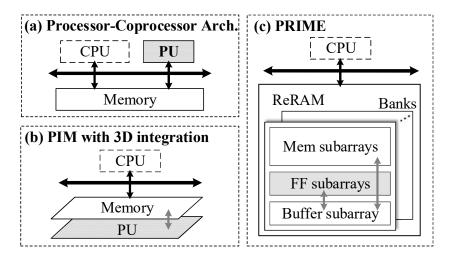

# 4.1 PRIME Architecture

We propose processing in ReRAM-based main memory, PRIME, which efficiently accelerates NN computation by leveraging ReRAM's computation capability and the PIM architecture. Figure 4.1(c) depicts an overview of our design. While most previous NN acceleration approaches require additional processing units (PU) (Figure 4.1(a) and (b)), PRIME directly leverages ReRAM cells to perform computation without the need for extra PUs. To achieve

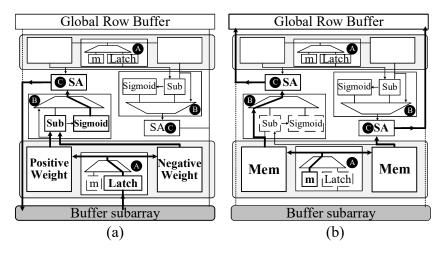

this, as shown in Figure 4.1(c), PRIME partitions a ReRAM bank into three regions: memory (Mem) subarrays, full function (FF) subarrays, and Buffer subarrays.

Figure 4.1: (a) Traditional shared memory based processor-coprocessor architecture, (b) PIM approach using 3D integration technologies, (c) PRIME design.

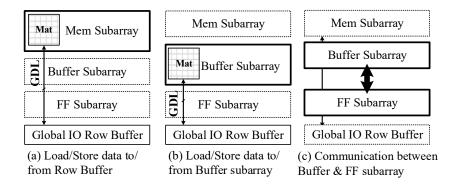

The Mem subarrays only have data storage capability (the same as conventional memory subarrays). Their microarchitecture and circuit designs are similar to a recent design of performance-optimized ReRAM main memory [120]. The FF subarrays have both computation and data storage capabilities, and they can operate in two modes. In memory mode, the FF subarrays serve as conventional memory; in computation mode, they can execute NN computation. There is a PRIME controller to control the operation and the reconfiguration of the FF subarrays. The Buffer subarrays serve as data buffers for the FF subarrays, and we use the memory subarrays that are closest to the FF subarrays as Buffer subarrays. They are connected to the FF subarrays through private data ports, so that buffer accesses do not consume the bandwidth of the Mem subarrays. While not being used as data buffers, the Buffer subarrays can also be used as normal memory. From Figure 4.1(c), we can find that for NN computation the FF subarrays enjoy the high bandwidth of in-memory data movement, and can work in parallel with CPU, with the help of the Buffer subarrays.

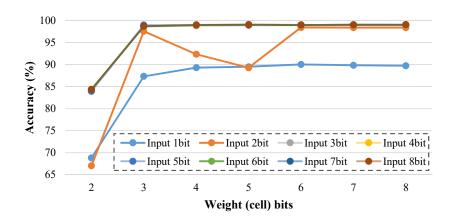

This section describes the details of our microarchitecture and circuit designs of the FF

subarrays, the Buffer subarrays, and the PRIME controller. These designs are independent of the technology assumptions for ReRAM based computation. For generality, we assume that the input data have  $P_{\rm in}$  bits, the synaptic weights have  $P_{\rm w}$  bits, and the output data have  $P_{\rm o}$  bits. With practical assumptions, the precision of ReRAM based NN computation is a critical challenge. We discuss the precision issue and propose a scheme to overcome it in Section 4.1.4. Finally, more details are given about implementing NN algorithms with our hardware design.

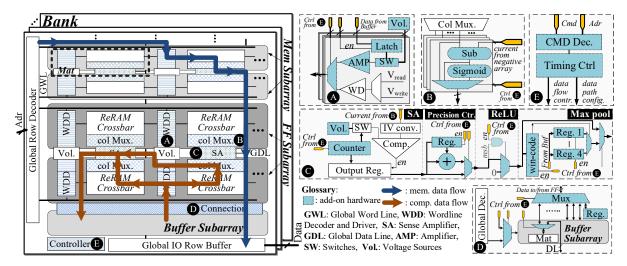

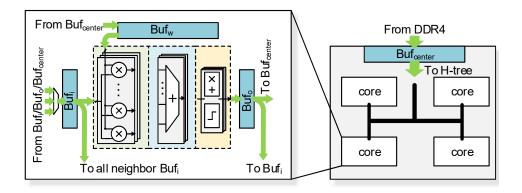

Figure 4.2: The PRIME architecture. Left: bank structure. The blue and red bold lines represent the directions of the data flow for normal memory and for computation, respectively. Right: functional blocks modified/added in PRIME. (A) Wordline driver with multi-level voltage sources; (B) column multiplexer with analog subtraction and sigmoid circuitry; (C) reconfigurable SA with counters for multi-level outputs, and added ReLU and 4-1 max pooling function units; (D) connection between the FF and Buffer subarrays; (E) PRIME controller.

# 4.1.1 FF Subarray Design

The design goal for FF subarray is to support both storage and computation with a minimum area overhead. To achieve this goal, we maximize the reuse of peripheral circuits for both storage and computation.

#### Microarchitecture and Circuit Design

To enable the NN computation function in FF subarrays, we modify decoders and drivers, column multiplexers (MUX), and sense amplifiers (SA) as shown in Figure 4.2.

**Decoder and Driver.** We add several components in decoders and drivers marked as light blue in Figure 4.2 **A**. First, we attach multi-level voltage sources to the wordlines to provide accurate input voltages. NN computation requires that all input data are simultaneously fed into the corresponding wordline. Therefore, we add a latch to control the input voltage. The control signals determine the combination of voltage sources that provide the demanding input voltage. Second, to drive the analog signals transferring on the wordlines, we employ a separate current amplifier on each wordline. Third, rather than two voltage levels used in the memory mode (for read and write, respectively), NN computation requires  $2^{P_{in}}$  levels of input voltages. We employ a multiplexer to switch the voltage driver between memory and computation modes. Finally, we employ two crossbar arrays store positive and negative weights, respectively, and allow them to share the same input port.

Column Multiplexer. In order to support NN computation, we modify the column multiplexers in ReRAM by adding the components marked in light blue in Figure 4.2 **B**. The modified column multiplexer incorporates two analog processing units: an analog subtraction unit and a non-linear threshold (sigmoid) unit [121]. The sigmoid unit can be bypassed in certain scenarios, e.g. when a large NN is mapped to multiple crossbar arrays. In addition, in order to allow FF subarrays to switch bitlines between memory and computation modes, we attach a multiplexer to each bitline to control the switch. Since a pair of crossbar arrays with positive and negative weights require one set of such peripheral circuits, we only need to modify half of the column multiplexers. After analog processing, the output current is sensed by local SAs.

Sense Amplifier. Figure 4.2 **C** shows the SA design with the following modifications as marked in light blue in the figure. First, NN computation requires SAs to offer much higher

precision than memory does. We adopt a  $P_o$ -bit ( $P_o \le 8$ ) precision reconfigurable SA design that has been tested through fabrication [122]. Second, we allow SA's precision to be configured as any value between 1-bit and  $P_o$ -bit, controlled by the counter as shown in Figure 4.2 **C**. The result is stored in the output registers. Third, we allow low-precision ReRAM cells to perform NN computation with a high-precision weight, by developing a precision control circuit that consists of a register and an adder. Fourth, we add a hardware unit to support ReLU function, a function in the convolution layer of CNN. The circuit checks the sign bit of the result. It outputs zero when the sign bit is negative and the result itself otherwise. Finally, a circuit to support 4-1 max pooling is included. More details are discussed in Section 4.1.5.

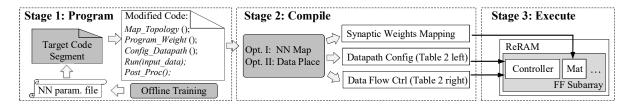

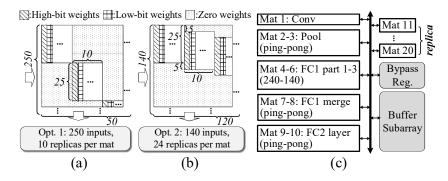

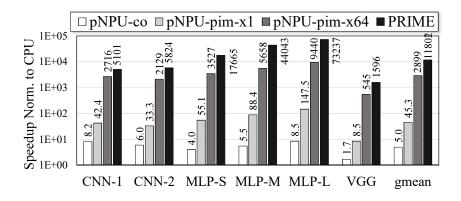

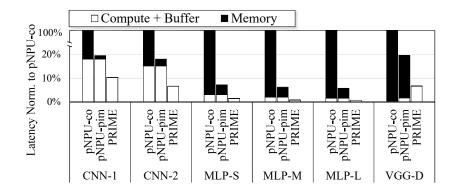

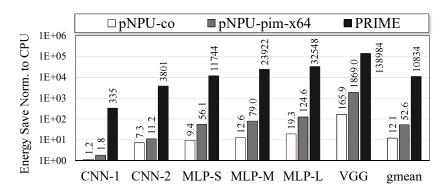

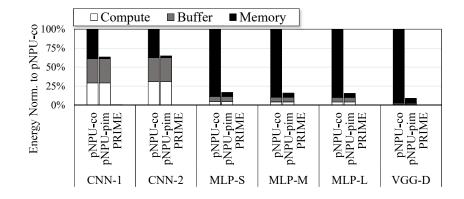

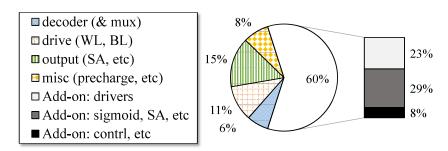

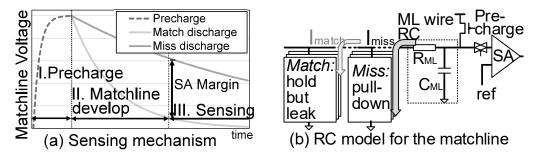

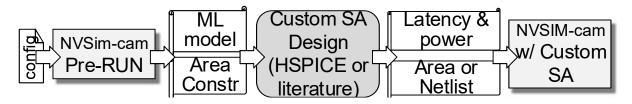

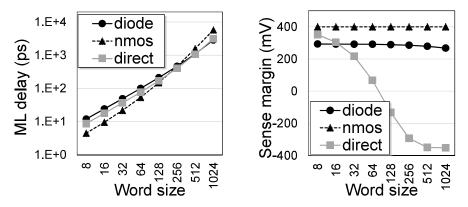

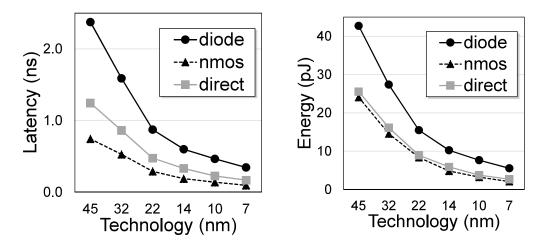

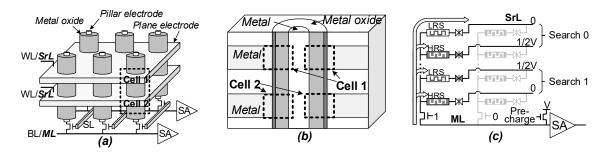

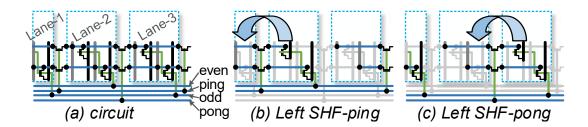

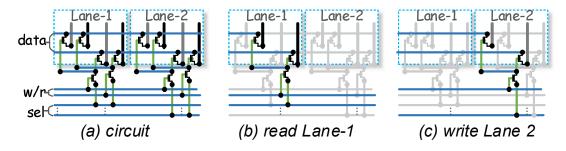

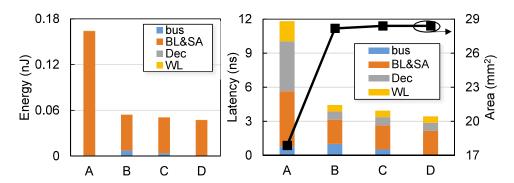

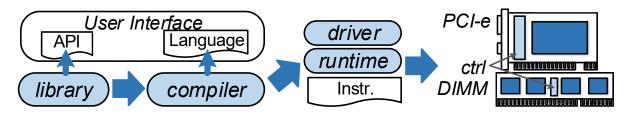

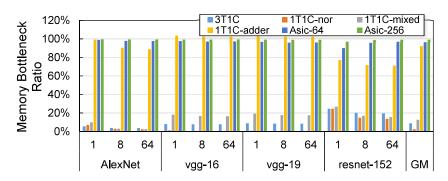

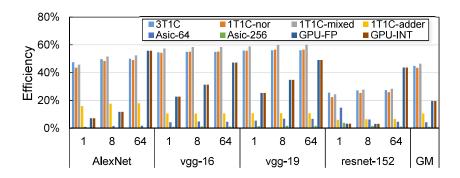

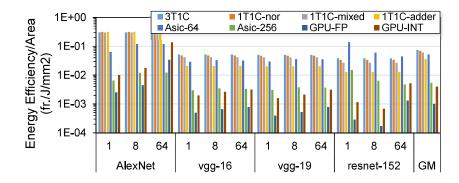

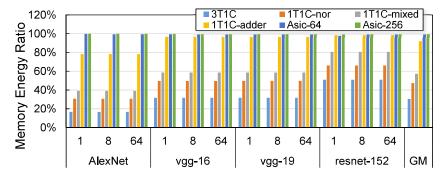

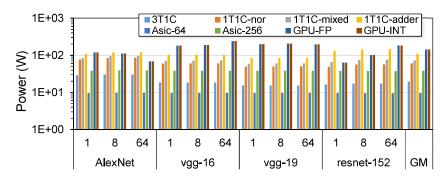

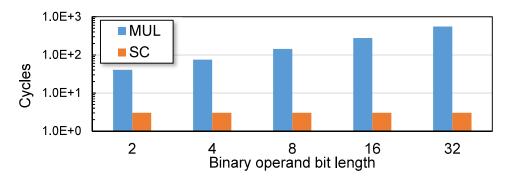

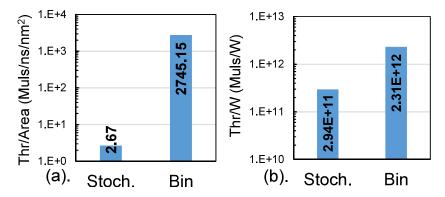

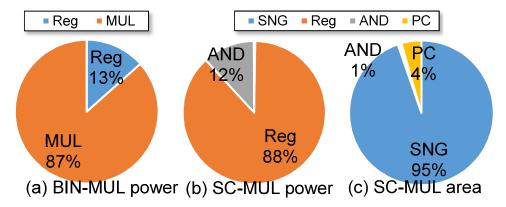

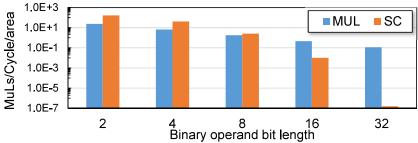

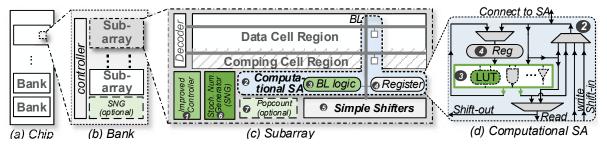

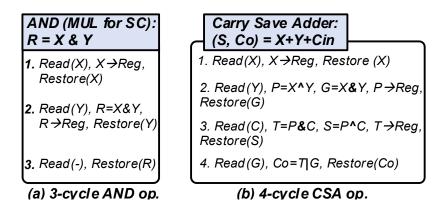

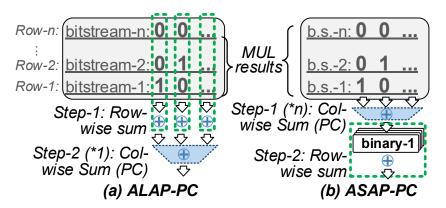

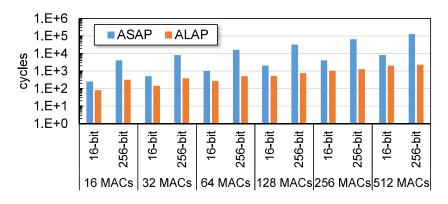

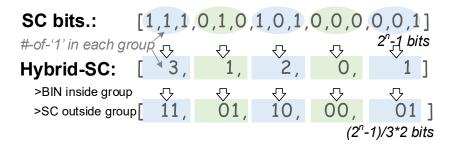

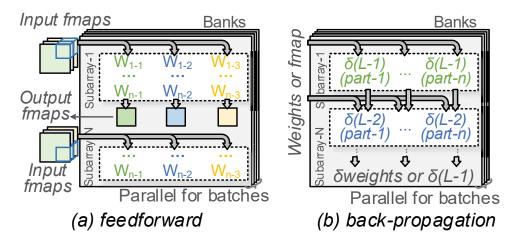

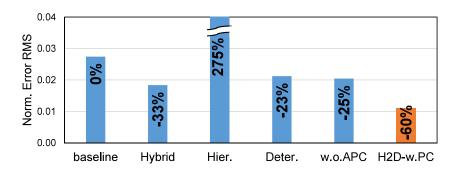

Buffer Connection. Figure 4.2 shows the communication between the FF subarrays and the Buffer subarrays. One adjacent Mem subarray is configured to serve as a buffer for computation, which will be explained in Section 4.1.2. We enable an FF subarray to access any physical location in a Buffer subarray to accommodate the random memory access pattern in NN computation (e.g., in the connection of two convolutional layers). To this end, extra decoders and multiplexers are employed in the buffer connection unit. Additionally, we allow the data transfer to bypass the Buffer subarray in certain scenarios, e.g. when the output of one mat is exactly the input of another. After bypassing the Buffer subarrays, we employ a register as an intermediate data storage.