## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Harsh Environment Silicon Carbide UV Sensor and Junction Field-Effect Transistor

**Permalink** https://escholarship.org/uc/item/4vp770tp

Author Lien, Wei-Cheng

Publication Date 2013

Peer reviewed|Thesis/dissertation

Harsh Environment Silicon Carbide UV Sensor and Junction Field-Effect Transistor

By

Wei-Cheng Lien

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Applied Science & Technology

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Albert P. Pisano, Chair Professor Tsu-Jae King Liu Professor Elad Alon

Fall 2013

Harsh Environment Silicon Carbide UV Sensor and Junction Field-Effect Transistor

Copyright © 2013

by

Wei-Cheng Lien

#### Abstract

#### Harsh Environment Silicon Carbide UV Sensor and Junction Field-Effect Transistor

by

#### Wei-Cheng Lien

#### Doctor of Philosophy in Applied Science & Technology

#### University of California, Berkeley

Professor Albert P. Pisano, Chair

A harsh environment can be defined by one or more of the following: High temperature, high shock, high radiation, erosive flow, and corrosive media. Among all the harsh environment applications, high temperature applications have drawn lots of attention due to the emerging activity in automotive, turbine engine, space exploration and deep-well drilling telemetry. Silicon carbide has become the candidate for these harsh environment applications because of its wide bandgap, excellent chemical and thermal stability, and high breakdown electric field strength. This dissertation details the two building blocks of high-temperature UV sensing chip, namely Ultraviolet sensor and transistors. High temperature performance of silicon carbide metal-semiconductor-metal UV sensor is characterized at high temperatures for the first time. The sensor exhibits high photo-to-dark current ratio and fast rise and fall time even at high temperatures. Complementary SiC junction field-effect transistors of different gate configurations are proposed, fabricated and characterized from room temperature to 600 °C for the first time. High intrinsic gains at high temperatures suggest that complementary junction field-effect transistors are suitable devices for high temperature operational amplifier.

# Contents

| Contents                                                                | i   |

|-------------------------------------------------------------------------|-----|

| List of Figures                                                         | iv  |

| List of Tables                                                          | Х   |

| Acknowledgements                                                        | xii |

| 1. Introduction                                                         | 1   |

| 1.1 Harsh Environment Sensing Application                               | 1   |

| 1.2 Silicon Carbide                                                     | 2   |

| 1.3 SiC Sensors for High Temperature Application                        | 5   |

| 1.3.1 UV Sensor.                                                        | 5   |

| 1.3.2 Pressure Sensor                                                   | 5   |

| 1.4 SiC Electronics Low Voltage High Temperature Application            | 6   |

| 1.5 High Temperature Effects in 4H-SiC                                  | 8   |

| 1.6 Research Objective and Thesis Overview                              | 9   |

| 1.7 References                                                          | 10  |

| 2. Silicon Carbide Metal-Semiconductor-Metal Ultraviolet Photodetectors | 14  |

| 2.1 Introduction                                                        | 14  |

| 2.2 Physics of MSM Photodetectors                                       | 15  |

| 2.3 4H-SiC MSM Photodetectors.                                          | 17  |

| 2.3.1 Fabrication Process and Characterization Methods                  | 17  |

| 2.3.2 Characterization of 4H-SiC Thin Films                             | 18  |

| 2.3.3 Characterization of 4H-SiC MSM Photodetector                          | 19     |

|-----------------------------------------------------------------------------|--------|

| 2.4 Antireflection Layer Using Nanostructure                                | 23     |

| 2.5 Summary                                                                 | 25     |

| 2.6 References                                                              | 26     |

| 3. Silicon Carbide N-Channel Raised Gate Junction Field-Effect Transistors  | 28     |

| 3.1 Introduction                                                            | 28     |

| 3.2 Physics of JFET                                                         | 28     |

| 3.3 Fabrication Process                                                     | 32     |

| 3.4 Metallization of N-Channel Raised Gate JFET                             | 37     |

| 3.5 Electrical Properties of N-Channel Raised Gate JFET                     | 43     |

| 3.5.1 Characterization of N-JFET at Room Temperature                        | 43     |

| 3.5.2 Characterization of N-JFET at High Temperatures                       | 45     |

| 3.5.3 Reliability                                                           | 48     |

| 3.6 TCAD Simulation of N-Channel Raised Gate JFET                           | 50     |

| 3.7 SPICE Parameter Extraction and Device Modeling                          | 53     |

| 3.8 Summary                                                                 | 55     |

| 3.9 Reference                                                               | 55     |

| 4. Silicon Carbide Complementary Buried Gate Junction Field-Effect Transist | ors 59 |

| 4.1 Introduction                                                            | 59     |

| 4.2 Design of Complementary Buried Gate JFET                                | 59     |

| 4.3 Fabrication Process                                                     | 64     |

| 4.4 Metallization of Complementary Buried Gate JFET                         | 68     |

| 4.5 Electrical Properties of N-Channel Buried Gate JFET                     | 71     |

| 4.6 Electrical Properties of P-Channel Buried Gate JFET                     | 73     |

|        |                 | Characterization  |      |           |      |      |    |

|--------|-----------------|-------------------|------|-----------|------|------|----|

|        | Temperature     |                   |      |           | <br> | <br> | /3 |

|        |                 | Characterization  |      |           |      |      | U  |

|        | 4.7 Summary.    |                   |      |           | <br> | <br> | 79 |

|        | 4.8 Reference.  |                   |      |           | <br> | <br> | 79 |

| 5. Con | clusion and Fu  | iture Work        |      |           |      |      | 82 |

|        | 5.1 Contributio | ons of This Work. | •••• |           | <br> | <br> | 82 |

|        | 5.2 Integrated  | SiC Sensor Desig  | n Cl | nallenges | <br> | <br> | 83 |

|        | 5.3 Reference.  |                   |      |           | <br> | <br> |    |

# **List of Figures**

| Figure 1.1: The structure of SiC crystal                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Three most common polytypes of silicon carbide. <i>Copyright: Dr. Christopher</i><br><i>S. Roper</i>                                                                                                        |

| Figure 1.3: Bi-layer stacking for the SiC polytypes 3C, 2H, 4H, and 6H                                                                                                                                                  |

| Figure 1.4: Calculated energy bandgap of Si, 6H-SiC, and 4H-SiC versus temperature8                                                                                                                                     |

| Figure 1.5: Intrinsic carrier concentration in Si, 6H-SiC, and 4H-SiC versus temperature                                                                                                                                |

| Figure 2.1: Schematic of MSM photodetector                                                                                                                                                                              |

| Figure 2.2: (a) The MSM photodetector is considered as two back-to-back Schottky barriers. Energy-band diagrams of MSM PDs at equilibrium (b) with n-type semiconductor layers and (c) with p-type semiconductor layers |

| Figure 2.3: Energy-band diagrams of MSM PDs for p-type semiconductor (a) without light and (b) with light at flat-band voltage                                                                                          |

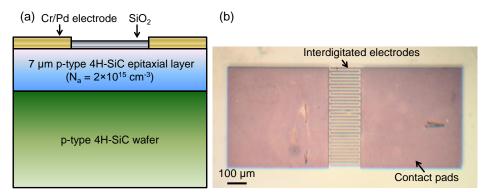

| Figure 2.4: (a) Schematic and (b) optical image of 4H-SiC MSM PDs17                                                                                                                                                     |

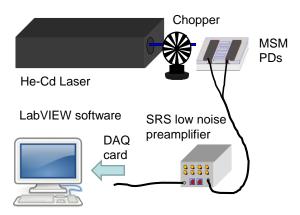

| Figure 2.5: Schematic of time-resolved measurement system                                                                                                                                                               |

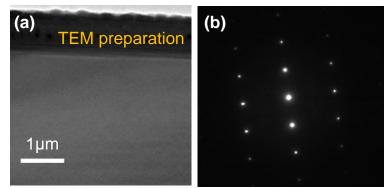

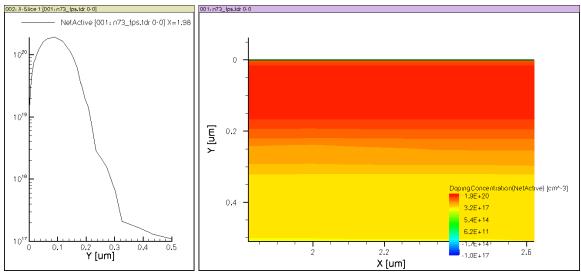

| Figure 2.6: (a) Cross-sectional TEM image and (b) electron diffraction pattern of epitaxial p-type 4H-SiC layer                                                                                                         |

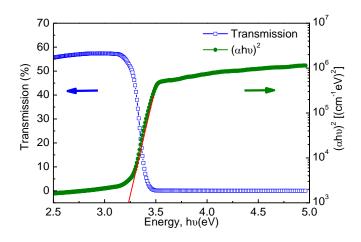

| Figure 2.7: The transmission spectrum (left y axis) and $(\alpha hv)^2$ (right y axis) vs. $hv$ plot of 4H-SiC substrates                                                                                               |

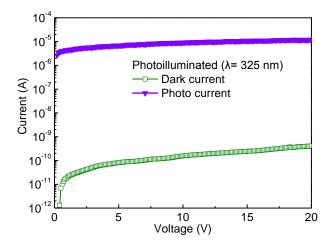

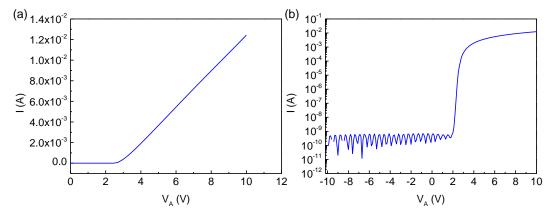

| Figure 2.8: I-V curves of the 4H-SiC MSM PDs measured in the dark and under 325-nm illumination at room temperature                                                                                                     |

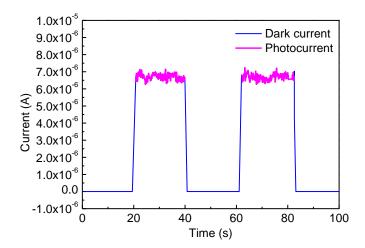

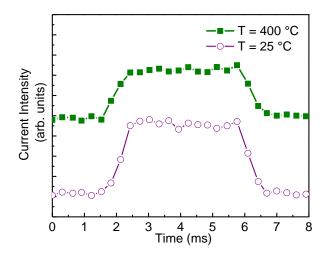

| Figure 2.9: The time dependence of the photocurrent and dark current of SiC MSM PDs at 25 °C under a 5 V bias                                                                                                           |

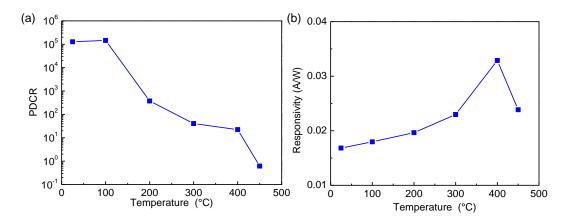

| Figure 2.10: (a) PDCR value and (b) responsivity as function of temperature under a 5 V bias                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

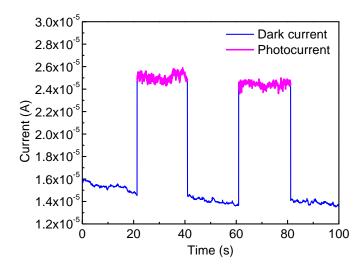

| Figure 2.11: The time dependence of the photocurrent and dark current of SiC MSM PDs at 450 °C under a 5 V bias                                                                                                                                                                                                                                                                                          |

| Figure 2.12: The transient photocurrent of SiC MSM PDs at room temperature and 400 °C under a 5 V bias                                                                                                                                                                                                                                                                                                   |

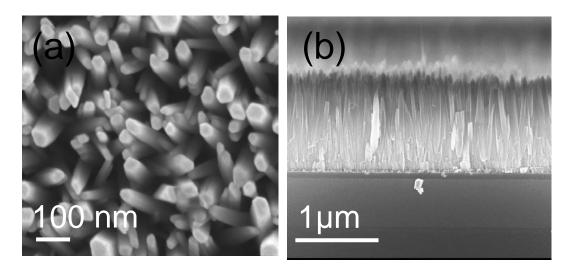

| Figure 2.13: (a) Top view and (b) cross-sectional SEM image of ZnO NRA/SiC layers                                                                                                                                                                                                                                                                                                                        |

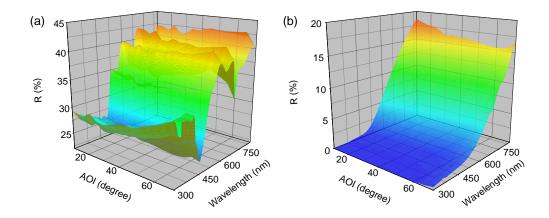

| Figure 2.14: Reflectance spectra of (a) bare SiC MSM PDs and (b) ZnO NRA/ SiC MSM PDs with a wide range of AOIs                                                                                                                                                                                                                                                                                          |

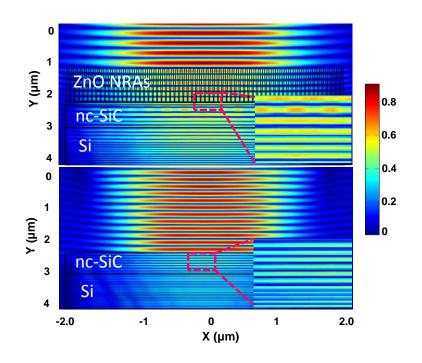

| Figure 2.15: FDTD simulation of time-averaged and normalized TE electric field distribution at 532 nm (a) without and (b) with ZnO NRAs. The insets in (a) and (b) are the enlarged images at the top SiC surface                                                                                                                                                                                        |

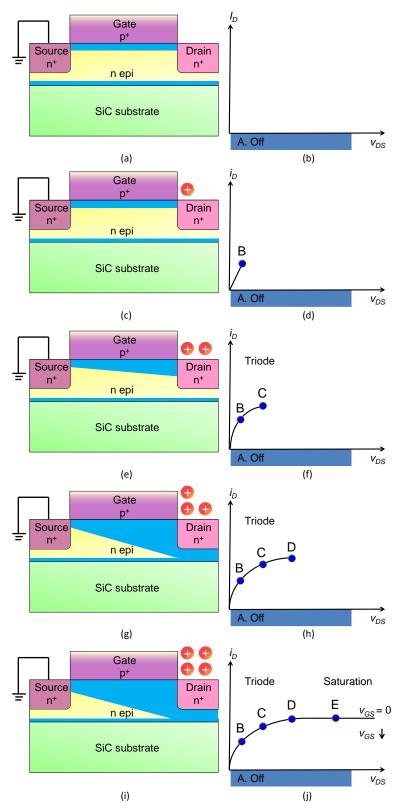

| Figure 3.1: Visualization of various phases of JFET operation and the corresponding $I_D$ - $V_D$ characteristics at $V_{GS} = 0$ V. Note the SiC substrate serves as the body biasing point. The blue color in schematic represents the depletion regions, and the yellow color shows the channel region. The shape of the channel is for the purpose of demonstration and it is not the real situation |

| Figure 3.2: Schematic of a lateral n-channel raised gate 4H-SiC JFET                                                                                                                                                                                                                                                                                                                                     |

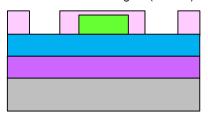

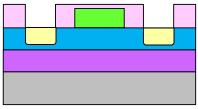

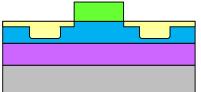

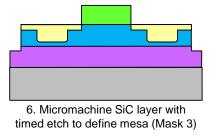

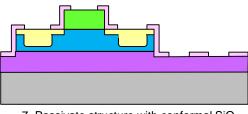

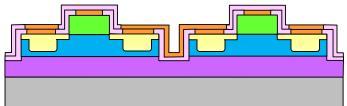

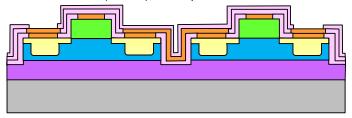

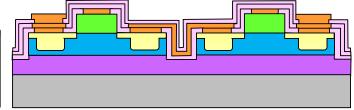

| Figure 3.3: Completed fabrication process flow of 4H-SiC JFET and MSM photodetectors                                                                                                                                                                                                                                                                                                                     |

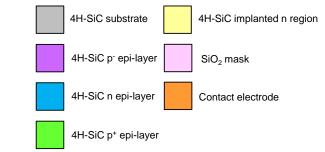

| Figure 3.4: Simulated doping profile of heavily doped drain and source region                                                                                                                                                                                                                                                                                                                            |

| Figure 3.5: (a) Cross-sectional scanning TEM image (b) Electron diffraction of implanted area after annealing at 1450 °C under Argon atmosphere for 30 minutes                                                                                                                                                                                                                                           |

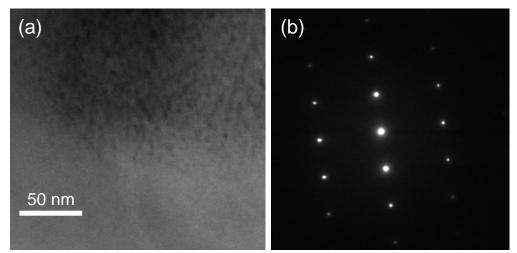

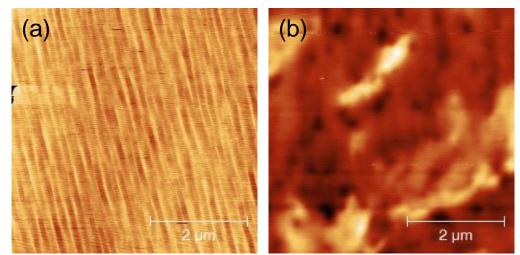

| Figure 3.6: AFM images of SiC samples before annealing and after annealing at 1450 °C under Argon atmosphere for 30 minutes                                                                                                                                                                                                                                                                              |

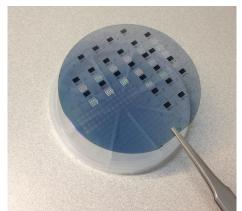

| Figure 3.7: Fabricated 3" 4H-SiC wafer                                                                                                                                                                                                                                                                                                                                                                   |

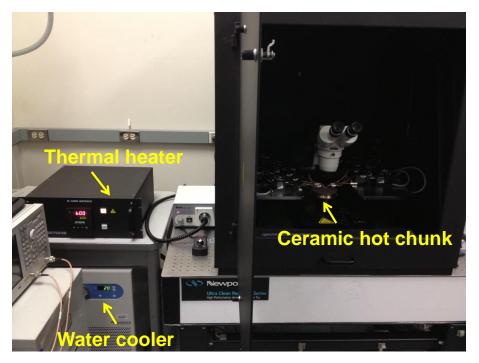

| Figure 3.8: High temperature probe station                                                                                                                                                                                                                                                                                                                                                               |

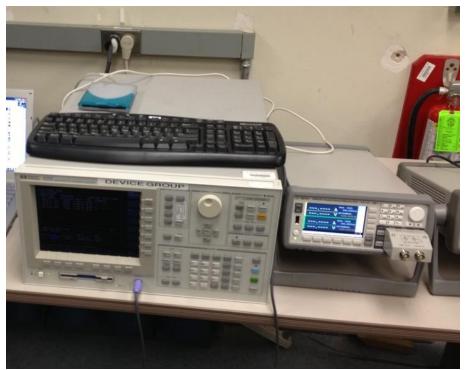

| Figure 3.9: HP 4156B semiconductor parameter analyzer and Agilent B2912A precision source/measurement unit                                                                                                                                                                                                                                                                                               |

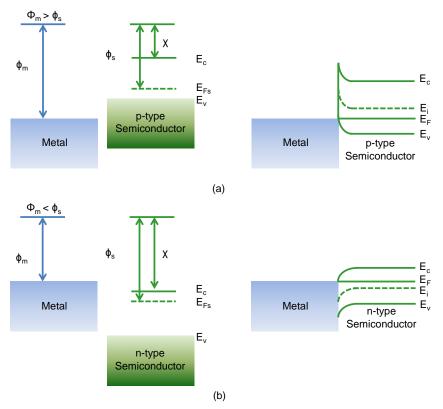

| Figure 3.10: Ideal Ohmic contact of metal with (a) p-type semiconductor and (b) n-type semiconductor                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

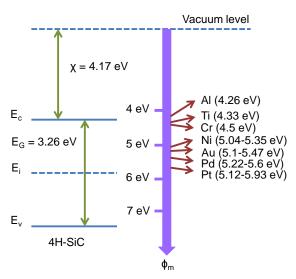

| Figure 3.11: Several metal workfunctions compared with the 4H-SiC band diagram38                                                                                                                                                                                                                                                                                                                   |

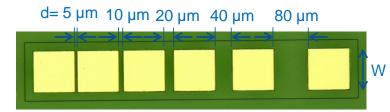

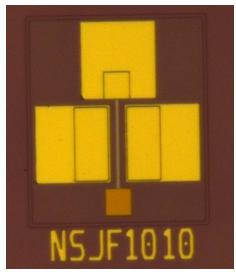

| Figure 3.12: Optical image of TLM structure                                                                                                                                                                                                                                                                                                                                                        |

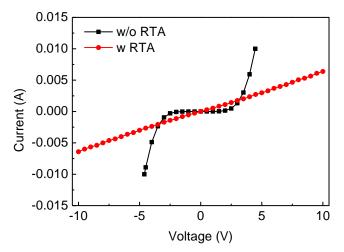

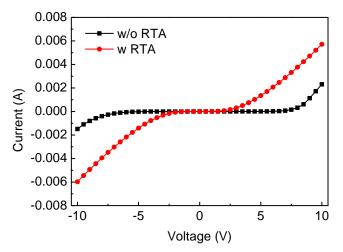

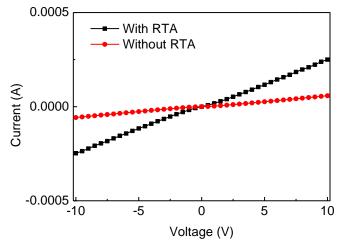

| Figure 3.13: Measure I-V curves of metal and n-type 4H-SiC before and after RTA annealing for TLM structure with $d = 80 \ \mu m$                                                                                                                                                                                                                                                                  |

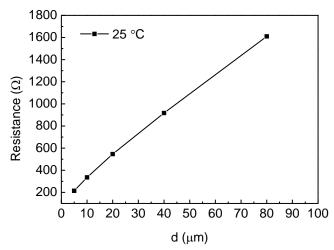

| Figure 3.14: Measured resistance between contacts vs. different distances at room temperature of Ti/Ni/TiW metal stacks and n-type 4H-SiC41                                                                                                                                                                                                                                                        |

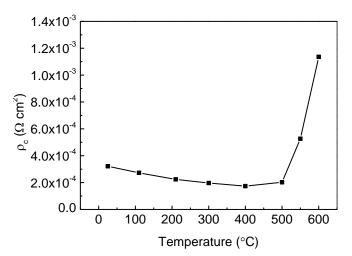

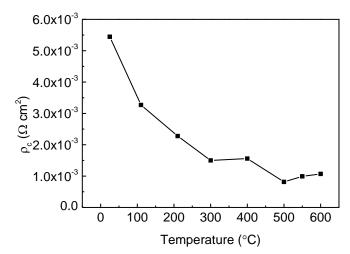

| Figure 3.15: Temperature dependences of specific contact resistance of Ti/Ni/TiW metal stacks to n <sup>+</sup> 4H-SiC                                                                                                                                                                                                                                                                             |

| Figure 3.16: Measure I-V curves of metal and p-type 4H-SiC for TLM structure with $d = 5 \mu m$                                                                                                                                                                                                                                                                                                    |

| Figure 3.17: Optical image of a n-channel raised gate 4H-SiC JFET with $L = 10 \ \mu m$ and $W = 100 \ \mu m$                                                                                                                                                                                                                                                                                      |

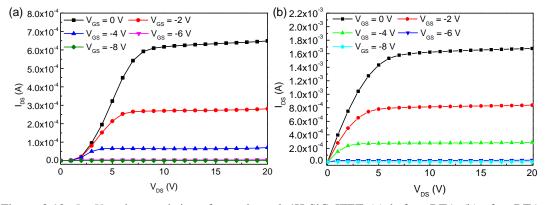

| Figure 3.18: $I_{DS}$ - $V_{DS}$ characteristics of a n-channel 4H-SiC JFET (a) before RTA (b) after RTA under different $V_{GS}$ and with $W/L=100 \ \mu\text{m}/10 \ \mu\text{m}$ at 25 °C44                                                                                                                                                                                                     |

| Figure 3.19: (a) $I_{DS}$ - $V_{GS}$ (b) $\sqrt{I_{DS}}$ - $V_{GS}$ characteristics of a n-channel 4H-SiC JFET with $W/L=100 \ \mu\text{m}/10 \ \mu\text{m}$ and $V_{DS}=20 \text{ V}$ at 25 °C44                                                                                                                                                                                                  |

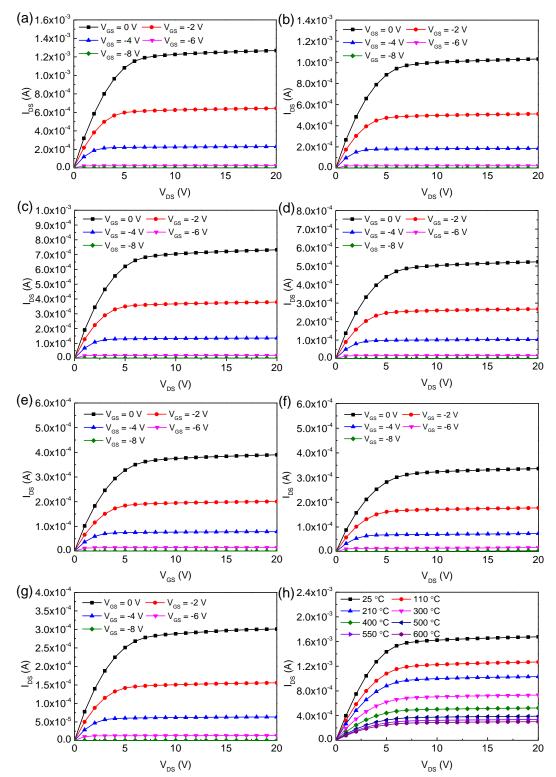

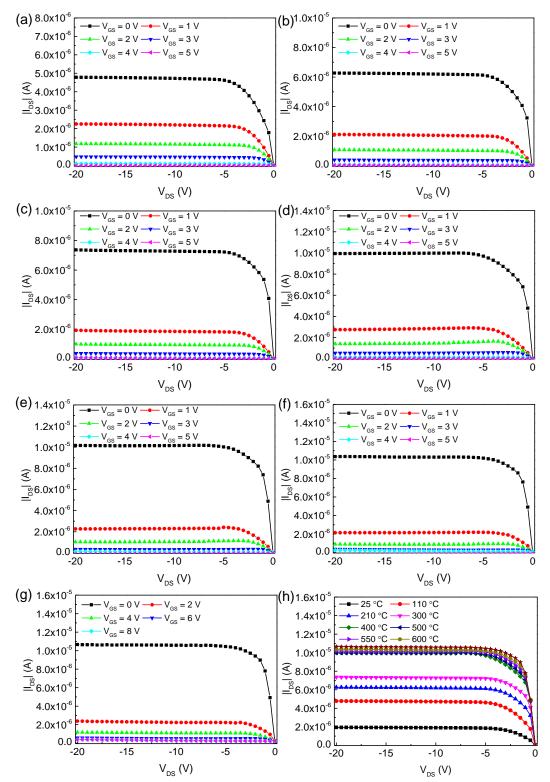

| Figure 3.20: $I_{DS}$ - $V_{DS}$ characteristics of a n-channel 4H-SiC JFET under different $V_{GS}$ and with $W/L=100 \ \mu\text{m}/10 \ \mu\text{m}$ (a) at 110 °C (b) at 210 °C (c) at 300 °C (d) at 400 °C (e) at 500 °C (f) at 550 °C (g) at 600 °C. (h) Temperature dependences of $I_{Dsat}$ of a n-channel 4H-SiC JFET at $V_{GS} = 0$ V and with $W/L=100 \ \mu\text{m}/10 \ \mu\text{m}$ |

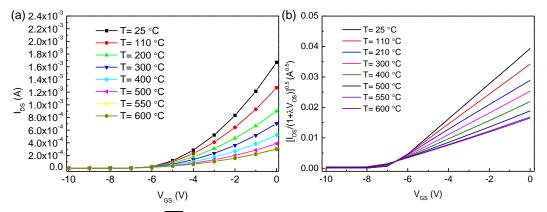

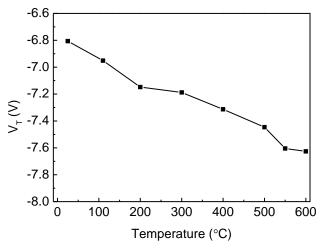

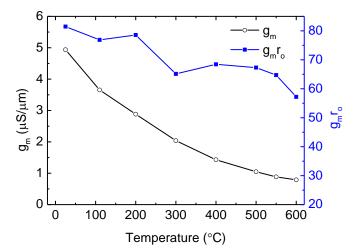

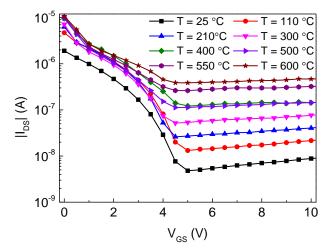

| Figure 3.21: (a) $I_{DS}$ - $V_{GS}$ (b) $\sqrt{I_{DS}}$ - $V_{GS}$ characteristics of a n-channel 4H-SiC JFET under $V_{DS} = 20$ V and with $W/L=100 \ \mu m/10 \ \mu m$ at different temperatures                                                                                                                                                                                               |

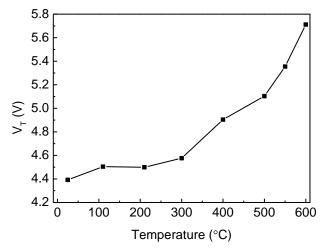

| Figure 3.22: Temperature dependence of threshold voltage of a n-channel 4H-SiC JFET with $W/L=100 \ \mu m/10 \ \mu m$                                                                                                                                                                                                                                                                              |

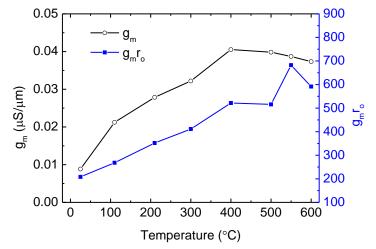

| Figure 3.23: Temperature dependence of transconductance and intrinsic gain of a n-<br>channel 4H-SiC JFET with $W/L=100 \ \mu m/10 \ \mu m$                                                                                                                                                                                                                                                        |

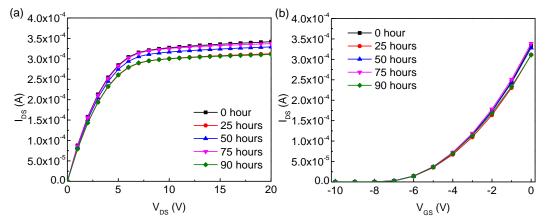

| Figure 3.24: (a) $I_{DS}$ - $V_{DS}$ characteristics at $V_{GS} = 0$ V and (b) $I_{DS}$ - $V_{GS}$ characteristics at $V_{DS} = 20$ V during 0, 25th, 50th, 75th, and 90 hours of electrical operation at 540 °C for a n-channel 4H-SiC JFET with $W/L = 100 \ \mu m/10 \ \mu m$                                                                                                                   |

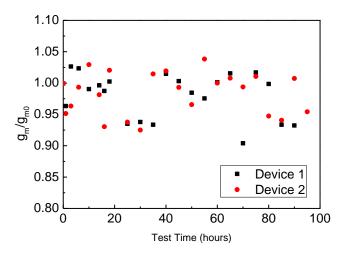

| Figure 3.25: Normalized $g_m$ versus test time at 540 °C through 90 hours for a n-channel 4H-SiC JFET with $W/L = 100 \ \mu m/10 \ \mu m$                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

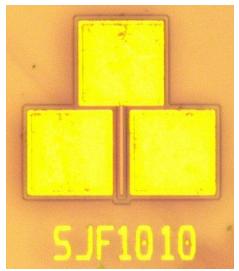

| Figure 3.26: Optical image of a n-channel 4H-SiC JFET with $W/L = 100 \ \mu m/10 \ \mu m$ after thermal reliability test at 540 °C after 90 hours                                                                                                                                                                                                                                                                          |

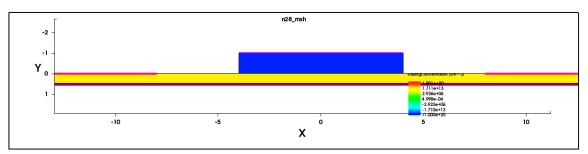

| Figure 3.27: Raised gate JFET structure generated by the Sentaurus structure editor52                                                                                                                                                                                                                                                                                                                                      |

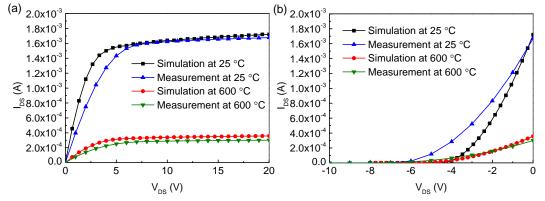

| Figure 3.28: Measured and Simulated (a) $I_{DS}$ - $V_{DS}$ characteristics at $V_{GS} = 0$ V and (b) $I_{DS}$ - $V_{GS}$ characteristics at $V_{DS} = 20$ for n-channel 4H-SiC JFETs with $W/L = 100 \ \mu\text{m}/10 \ \mu\text{m}$ at 25 and 600 °C                                                                                                                                                                     |

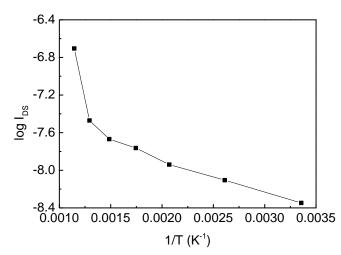

| Figure 3.29: Arrhenius plot of log of drain leakage current versus $1/T$ at $V_{GS} = -10$ V of a n-channel 4H-SiC JFET with $W/L = 100 \ \mu m/10 \ \mu m$                                                                                                                                                                                                                                                                |

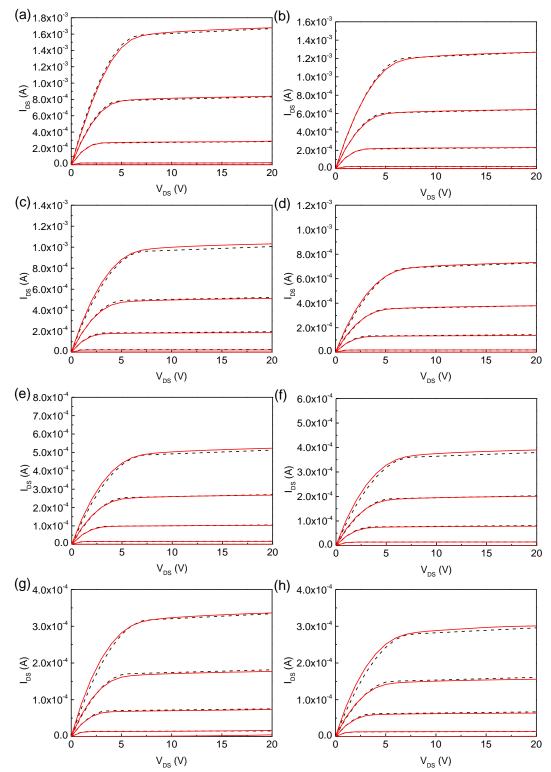

| Figure 3.30: Modeled and measured $I_{DS}$ - $V_{DS}$ characteristics of a n-channel 4H-SiC JFETs under different $V_{GS}$ and with $W/L$ = 100 µm/10 µm (a) at 110 °C (b) at 210 °C (c) at 300 °C (d) at 400 °C (e) at 500 °C (f) at 600 °C. The black dot lines are modeled devices and the red solid lines are measured devices. From the top curve to the bottom curve, $V_{GS}$ are 0, -2, -4, -6, -8 V, respectively |

| Figure 4.1: Buried gate JFET structure generated by the Sentaurus structure editor60                                                                                                                                                                                                                                                                                                                                       |

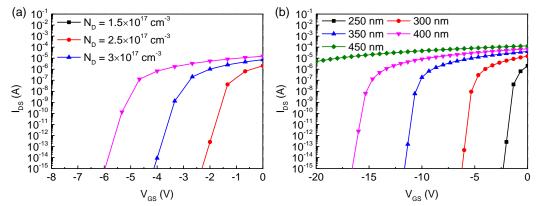

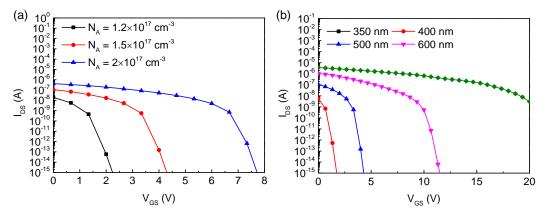

| Figure 4.2: Simulated $I_{DS}$ - $V_{GS}$ of n-channel JFETs with $L = 8 \ \mu m$ and (a) different channel doping with fixed channel depth of 250 nm (b) different channel depth with fixed channel doping of $2.5 \times 10^{17} \text{ cm}^{-3}$ at 25 °C                                                                                                                                                               |

| Figure 4.3: Simulated $I_{DS}$ - $V_{GS}$ of p-channel JFETs with $L = 8 \ \mu m$ and (a) different channel doping with fixed channel depth of 400 nm (b) different channel depth with fixed channel doping of $1.5 \times 10^{17} \text{ cm}^{-3}$ at 25 °C                                                                                                                                                               |

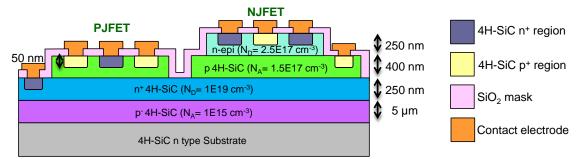

| Figure 4.4: Simulated $I_{DS}$ - $V_{GS}$ of a (a) n-channel (b) p-channel JFET with $L = 8 \mu m61$                                                                                                                                                                                                                                                                                                                       |

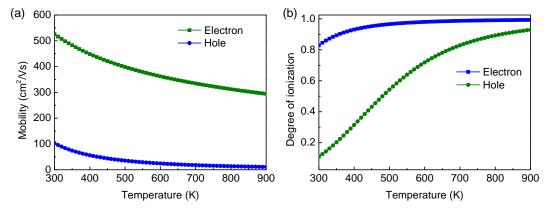

| Figure 4.5: Temperature dependence of (a) carrier mobility and (b) degree of ionization                                                                                                                                                                                                                                                                                                                                    |

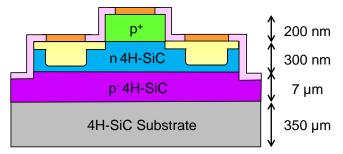

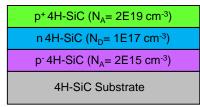

| Figure 4.6: Schematic of 4H-SiC complementary JFETs65                                                                                                                                                                                                                                                                                                                                                                      |

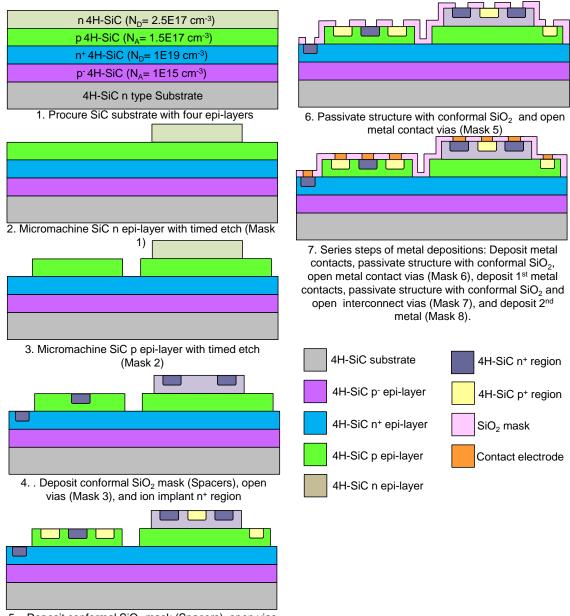

| Figure 4.7: Completed fabrication process flow of 4H-SiC c-JFETs66                                                                                                                                                                                                                                                                                                                                                         |

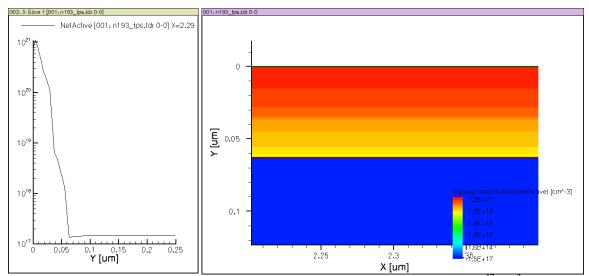

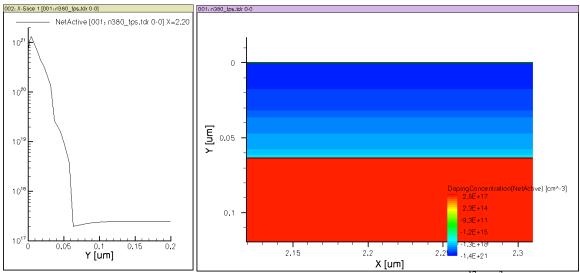

| Figure 4.8: Simulated phosphorous doping profile in the p-channel area with $N_A = 1.5 \times 10^{17} \text{ cm}^{-3}$                                                                                                                                                                                                                                                                                                     |

| Figure 4.9: Simulated aluminum doping profile in the n-channel area with $N_D = 2.5 \times 10^{17}$ cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                       |

| Figure 4.10: SEM image of etching pits after thermal annealing at 1550 °C for 15 minute                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

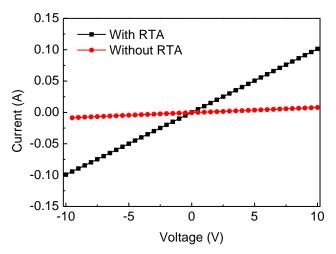

| Figure 4.11: Measure I-V curves of metal and n-type 4H-SiC before and after RTA annealing for TLM structure with $d = 5 \ \mu m$                                                                                                                                                                                                                           |

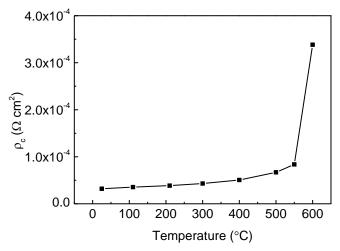

| Figure 4.12: Temperature dependences of specific contact resistance of Ni/Ti/Al/TiW metal stacks to n <sup>+</sup> 4H-SiC                                                                                                                                                                                                                                  |

| Figure 4.13: Measure I-V curves of metal and p-type 4H-SiC before and after RTA annealing for TLM structure with $d = 20 \ \mu m$                                                                                                                                                                                                                          |

| Figure 4.14: Temperature dependences of specific contact resistance of Ni/Ti/Al/TiW metal stacks to p <sup>+</sup> 4H-SiC                                                                                                                                                                                                                                  |

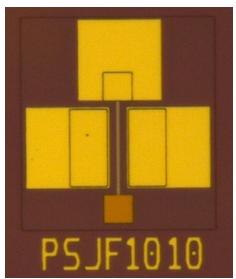

| Figure 4.15: Optical image of a n-channel buried gate 4H-SiC JFET with $L = 10 \ \mu m$ and $W = 100 \ \mu m$                                                                                                                                                                                                                                              |

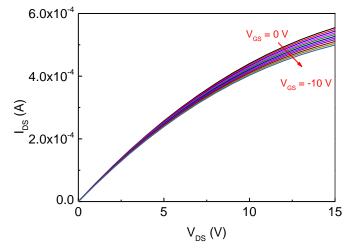

| Figure 4.16: $I_{DS}$ - $V_{DS}$ characteristics of a n-channel buried gate 4H-SiC JFET under different $V_{GS}$ and with $W/L$ = 100 µm/10 µm at 25 °C                                                                                                                                                                                                    |

| Figure 4.17: I-V characteristics of pn junction in the n-channel buried gate 4H-SiC JFET structure                                                                                                                                                                                                                                                         |

| Figure 4.18: Optical image of a p-channel buried gate 4H-SiC JFET with $L = 10 \ \mu m$ and $W = 100 \ \mu m$                                                                                                                                                                                                                                              |

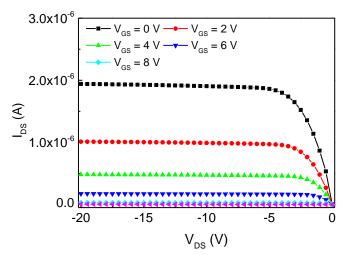

| Figure 4.19: $ I_{DS} $ - $V_{DS}$ characteristics of a p-channel 4H-SiC JFET under different $V_{GS}$ and with $W/L$ = 100 µm/10 µm at 25 °C                                                                                                                                                                                                              |

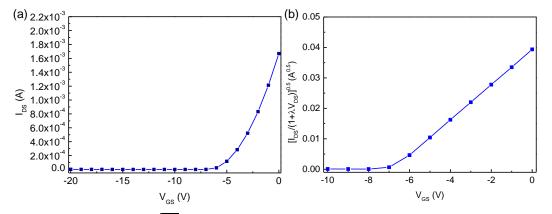

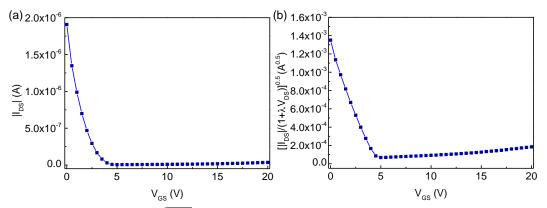

| Figure 4.20: (a) $ I_{DS} -V_{GS}$ (b) $\sqrt{ I_{DS} }-V_{GS}$ characteristics of a p-channel 4H-SiC JFET with $W/L=100 \ \mu\text{m}/10 \ \mu\text{m}$ and $V_{DS}=-20 \ \text{V}$ at 25 °C                                                                                                                                                              |

| Figure 4.21: $I_{DS}$ - $V_{DS}$ characteristics of a p-channel 4H-SiC JFET under different $V_{GS}$ and with $W/L$ = 100 µm/10 µm (a) at 110 °C (b) at 210 °C (c) at 300 °C (d) at 400 °C (e) at 500 °C (f) at 550 °C (g) at 600 °C. (h) Temperature dependences of $I_{Dsat}$ of a p-channel 4H-SiC JFET at $V_{GS}$ = 0 V and with $W/L$ = 100 µm/10 µm |

| Figure 4.22: $ I_{DS}  - V_{GS}$ characteristics of a p-channel 4H-SiC JFET under $V_{DS} = -20$ V and with $W/L= 100 \ \mu m/10 \ \mu m$ at different temperatures                                                                                                                                                                                        |

| Figure 4.23: Temperature dependence of threshold voltage of a p-channel 4H-SiC JFET with $W/L=100 \ \mu m/10 \ \mu m$                                                                                                                                                                                                                                      |

| Figure 4.24: Temperature dependence of transconductance and intrinsic gain of of a p- |

|---------------------------------------------------------------------------------------|

| channel 4H-SiC JFET with $W/L=100 \ \mu m/10 \ \mu m$                                 |

# **List of Tables**

| Table 1.1: High temperature electronics applications.    2                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Mechanical properties of Si and wide bandgap semiconductors. If the thermalexpansion coefficient has two values, the first one is along the a-axis and the second oneis along the c-axis                                                                                         |

| Table 1.3: Electrical properties of Si and wide bandgap semiconductors. If the electron mobility has two values, the first one is perpendicular to the c-axis and the second one is parallel to the c-axis                                                                                  |

| Table 1.4: A sampling of published single transistors for high temperature applications7                                                                                                                                                                                                    |

| Table 2.1: Response time of fabricated 4H-SiC MSM photodetectors                                                                                                                                                                                                                            |

| Table 3.1: Specific contact resistance measurements on 4H-SiC in the literature41                                                                                                                                                                                                           |

| Table 3.2: Sheet resistance and specific contact resistance of Ti/Ni/TiW metal stacks andn-type 4H-SiC at different temperatures                                                                                                                                                            |

| Table 3.3: Extracted parameters of n-channel raised gate 4H-SiC JFET with $W/L=100 \mu m/10 \mu m$ at various temperatures. $g_m$ , $R_{on}$ , $r_o$ , $\lambda$ and $g_m r_o$ is based on $V_{GS} = 0$ V. $I_{Dsat}/I_{off}$ is the ratio of current at $V_{GS} = 0$ V and $V_{GS} = -9$ V |

| Table 3.4: The extracted SPICE parameters of a n-channel 4H-SiC JFET with $W/L=100 \mu m/10 \mu m$ from 25 to 600 °C                                                                                                                                                                        |

| Table 4.1: Optimized parameters of complementary JFETs with L = 10 $\mu$ m. $g_m$ , $r_o$ , and $g_m r_o$ is based on $V_{GS} = 0$ V                                                                                                                                                        |

| Table 4.2: Fitting parameters for low field mobility of 4H-SiC                                                                                                                                                                                                                              |

| Table 4.3: Sheet resistance and specific contact resistance of Ni/Ti/Al/TiW metal stacks and n-type 4H-SiC at different temperatures                                                                                                                                                        |

| Table 4.4: Sheet resistance and specific contact resistance of Ni/Ti/Al/TiW metal stacks and p-type 4H-SiC at different temperatures                                                                                                                                                        |

# Acknowledgments

There are many people who deserve my acknowledgments during the three and half years of my Ph. D. study at the University of California at Berkeley. I would like to express my sincere thanks to my advisor, Professor Albert P. Pisano. He is a caring advisor offering me endless help on my research, course work and even life at Berkeley. He gives me the freedom to explore interesting research topics and encourages me, rather than blaming me, when I am frustrated and make mistakes.

I am also grateful for the support from my dissertation committee members Professor Tsu-Jae King Liu and Professor Elad Alon.

Professors Debbie Senesky, Roya Maboudian, Ali Javey, and Roger Howe have provided me with many inspiring ideas and invaluable advice. The members of the Pisano lab, past and present, have taught me the skills, techniques and valuable discussions for this work. In addition, Dr. Louis Hutin and Nattapol Damrongplasit from Professor Tsu-Jae King Liu's group, and Jun-Chau Chien from Professor Ali Niknejad's group, and Yang Lin and Wei-Chun Li from Professor Clark Nguyen's group shared their knowledge and offered valuable help for me. I would like to thank the staff at Berkeley Marvell Nanolab for providing much assistance related to operating the machines in Nanolab. I also want to thank the staff of the BSAC and ERSO office for helping with purchase orders and grant administration.

My wonderful friends, Fabian Goericke, Matt Chan, Yegan Erdem, Albert Gutes, Ting-Ta Yen, Chih-Ming Lin, Yun-Ju Lai, Ting-Ying Chung, Chih-Wei Chu, Stefano Fissolo, Kuo-Ken Huang and Terry Tsai, deserve my special thanks for their unremitting support and encouragement with everything.

Finally, and most importantly, I want to express my deepest gratitude to my parents and two sisters for their love.

# Chapter 1

## Introduction

#### **1.1 Harsh Environment Sensing Application**

Recently, much research effort has focused on advancing renewable energy resources, such as solar, hydro, wind and geothermal energy. While developing these new technologies, reducing inefficiencies in generation and transmission should be considered. For example, the total energy lost is 61% of energy supply in U.S. in 2012 [1]. One method of addressing the inefficiencies in energy use is through the development of harsh environment sensing technology. Power systems can be advanced by integration of electronics (e.g., communication, signal processing, microactuator control, etc.) to operate at high temperature [2, 3]. Specifically, smart harsh environment electronic sensing systems enable real-time condition based monitoring of temperature and incomplete combustion, and reduce emission of greenhouse gases (NO<sub>x</sub> and CO<sub>2</sub>) in gas turbine systems to guide deep-well oil drilling operation or monitors the subsurface environments found in geothermal power plants.

A harsh environment can be defined by one or more of the following: High temperature (> 350 °C), high shock (> 50,000 g), high radiation (> 100 Mrads), erosive flow, and corrosive media [6]. Silicon is a widely used semiconductor material because of such factors as its high quality, stable oxide, and low cost. However silicon-based microelectronics are not suitable for harsh environments, because the electronic properties of silicon degrade above 300 °C due to the more intrinsic carrier presented than dopant carriers and mechanical properties degrade above 600 °C due to decline in its elastic modulus [3]. As the need increases for electronics and microelectromechanical systems (MEMS) devices suitable for harsh environment applications, including automobile, aerospace, nuclear and military purposes, several technologies such as silicon-on-insulator (SOI) or wide bandgap (WBG) electronics are needed. SOI technology can extend the CMOS operating temperature due to reduce leakage and less parasitic bipolar action [7]. A wide bandgap material has large energy bandgap of 3 eV so the generation of intrinsic carriers will not surpass the dopant carriers at high temperature.

In order to realize integration of the sensing system, the building blocks of the sensor system, such as sensors and transistors, need to be developed. Among all the harsh environment applications, high temperature applications have drawn lots of attention due to the emerging activity in several areas (Table 1.1) [3]. In this work, we focus on

developing the sensor and electronics for high temperature application. Silicon carbide (SiC) has been chosen as the base semiconductor material for this work due to its wide bandgap, high electric field breakdown strength, high thermal conductivity, and high saturated carrier drift velocity [8].

| Application                  | Area                              | Peak<br>ambient<br>(°C) | Chip<br>power<br>(kW) | Target technology |

|------------------------------|-----------------------------------|-------------------------|-----------------------|-------------------|

| Autimotive                   | On-cylinder<br>& Exhaust<br>pipe  | 600                     | < 1                   | WBG               |

| Turbine engine               | Sensors,<br>telemetry,<br>control | 600                     | < 1                   | WBG               |

|                              | Electric actuation                | 600                     | > 10                  | WBG               |

| Spacecraft                   | Power<br>management               | 300                     | > 10                  | WBG               |

|                              | Venus &<br>Mercury<br>exploration | 550                     | 1                     | WBG               |

| Industrial                   | High<br>temperature<br>processing | 600                     | < 1                   | SOI & WBG         |

| Deep-well drilling telemetry | Oil and gas                       | 300                     | < 1                   | SOI & WBG         |

|                              | geothermal                        | 600                     | < 1                   | WBG               |

Table 1.1: High temperature electronics applications.

### **1.2 Silicon Carbide**

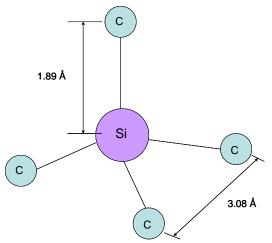

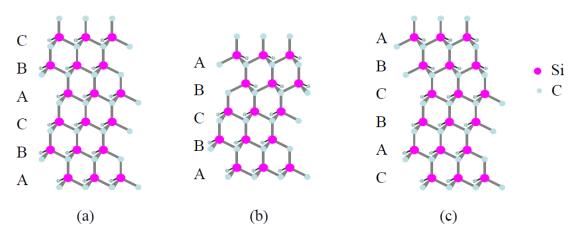

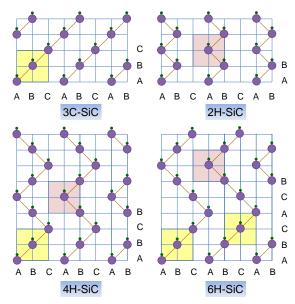

The silicon carbide unit cell is a tetrahedron consisting of four carbon atoms with a silicon atom in the center, as shown in Figure 1.1. There are approximately 200 polytypes of SiC existing in the world [9]. Figure 1.2 shows the three most common polytypes of silicon carbide, consisting of different stacking sequences of SiC bilayer. They are cubic (3C,  $\beta$ -SiC) and hexagonal (H,  $\alpha$ -SiC) with the number denoting the number of SiC bilayer stackings [10]. Because of the possible stacking sequences of SiC bilayer, there are lattice sites in SiC that have a surrounding layer stacking in hexagonal form and others with cubic form, which are denoted hexagonal sites and cubic sites, respectively [11]. Figure 1.3 shows that 3C-SiC has one cubic site and 2H-SiC includes only one hexagonal site. 4H-SiC has one hexagonal and one cubic site, while 6H-SiC exhibits one hexagonal and two cubic sites. 4H-SiC and 6H-SiC polytypes already have commercially available wafers and epitaxy, while 3C-SiC is the only polytype that can be grown heteroepitaxially on a Si wafer. The basic mechanical and electrical properties of the three SiC polytypes, as well as those for Si, GaN, AlN, and diamond are shown in Table 1.2 and 1.3 [11-13].

Figure 1.1: The structure of SiC crystal.

Figure 1.2: Three most common polytypes of silicon carbide [10]. Copyright: Dr. Christopher S. Roper

Figure 1.3: Bi-layer stacking for the SiC polytypes 3C, 2H, 4H, and 6H [11].

|                                                              | Si   | 3C-SiC | 6H-SiC    | 4H-SiC   | 2H-GaN    | 2H-AlN    | Diamond |

|--------------------------------------------------------------|------|--------|-----------|----------|-----------|-----------|---------|

| Lattice a<br>(Å)                                             | 5.43 | 4.36   | 3.08      | 3.08     | 3.189     | 3.112     | 3.567   |

| Lattice c<br>(Å)                                             | NA   | NA     | 15.12     | 10.08    | 5.185     | 4.982     | NA      |

| Thermal<br>expansion<br>coefficient<br>(10 <sup>-6</sup> /K) | 2.6  | 3.28   | 3.35/3.25 | 3.3/3.16 | 5.59/3.17 | 5.27/4.15 | 0.8     |

| Density $(g/cm^3)$                                           | 2.33 | 3.21   | 3.21      | 3.21     | 6.15      | 3.23      | 3.5     |

| Thermal<br>conductivi<br>ty (W/cm<br>K)                      | 1.5  | 3.6    | 4.9       | 4.9      | 1.3       | 2.85      | 20      |

| Melting<br>point (°C)                                        | 1420 | 2830   | 2830      | 2830     | 2500      | 3000      | 4000    |

| Mohs<br>hardness                                             | 7    | 9      | 9         | 9        |           | 7         | 10      |

Table 1.2: Mechanical properties of Si and wide bandgap semiconductors. If the thermal expansion coefficient has two values, the first one is along the a-axis and the second one is along the c-axis.

|                                                              | Si   | 3C-SiC | 6H-SiC  | 4H-SiC   | 2H-GaN | 2H-AIN | Diamond |

|--------------------------------------------------------------|------|--------|---------|----------|--------|--------|---------|

| Energy<br>bandgap<br>(eV)                                    | 1.12 | 2.4    | 3.0     | 3.23     | 3.4    | 6.2    | 5.6     |

| Breakdown<br>field(MV/c<br>m)                                | 0.25 | 2.5    | 2.5     | 2.2      | 3.0    | 2.0    | 20      |

| Electron<br>saturation<br>velocity (10 <sup>7</sup><br>cm/s) | 1.0  | 2.5    | 2.0     | 2.0      | 2.5    | 2.0    | 2.7     |

| Electron<br>mobility<br>(Cm/V s)                             | 1400 | 1000   | 500/100 | 950/1150 | 1245   | 135    | 2200    |

| Hole<br>mobility<br>(cm/V s)                                 | 600  | 50     | 80      | 120      | 370    | 14     | 1600    |

| Dielectric constant                                          | 11.9 | 9.7    | 10.0    | 10.0     | 9.5    | 8.5    | 5.5     |

Table 1.3: Electrical properties of Si and wide bandgap semiconductors. If the electron mobility has two values, the first one is perpendicular to the c-axis and the second one is parallel to the c-axis.

Owing to its superior mechanical properties, SiC is quite suitable for Microelectromechanical systems (MEMS). SiC based MEMS devices have been previously used as temperature and pressure sensors in a high temperature environment [14], high-g accelerometers [15], biomedical sensors [16], and strain sensor [5]. SiC may also be suitable for high frequency MEMS resonators as micromechanical oscillators and

filters due to its high  $E/\rho$  ratio. The resonant frequency of a micromachined device can be expressed as

$$\omega = Cf \sqrt{\frac{E}{\rho}} \tag{1.1}$$

where C is constant, f is a function of Poisson's ratio, E is the material Young's modulus and  $\rho$  is the material density. SiC has been successfully used to fabricate Lamé mode MEMS resonators for signal processing [17].

SiC may be used for high temperature, high power, high frequency and radiation resistance electronics applications. For example, its wide bandgap makes SiC desirable for electronics in high temperature environments. Additionally, the breakdown electric field strength ( $E_{max}$ ) is perhaps the most important factor for high power applications: the  $E_{max}$  of SiC is ten times that of silicon. As high-frequency devices, the saturated electron drift velocity of SiC is twice that of silicon, thereby enabling microwave devices to reach high channel currents [18].

### **1.3 SiC Sensors for High Temperature Application**

SiC sensor technology has been significantly improved in material growth technology and processing over the last few years [19]. Several SiC sensor platforms have been developed for high temperature applications, such as ultraviolet (UV) sensor, gas sensor, pressure sensor. The following sections report some device performance of the SiC sensors.

#### 1.3.1 UV Sensor

A SiC UV sensor is mainly based on the pn diode, and was the first wide bandgap photodetectors to reach the market [13, 20, 21]. The main advantage is the low reverse current, which is ~  $10^{-13}$  A/cm<sup>2</sup> at room temperature,  $10^{-9}$  A/cm<sup>2</sup> at 200 °C and ~  $2 \times 10^{-7}$  A/cm<sup>2</sup> at 350 °C at -10 V for 6H-SiC photodiode [20]. At 25 °C, the peak responsivity typically falls between 0.15-0.175 A/W at 270 nm, corresponding to a quantum efficiency of 70-85%. When the temperature increases, the peak response redshifts and long wavelength responsivity increases. The corresponding quantum efficiency varies between 82 and 96% from -50 to 450 °C [13, 20].

Another type of photodetector (PD), metal-semiconductor-metal (MSM) PD, has also been developed for operating temperatures up to 200 °C using nanocrystalline SiC deposited by ion-beam assisted deposition [22]. MSM offers high speed operation and can be readily integrated with optoelectronic and MEMS for signal detection.

#### 1.3.2 Pressure Sensor

Conventional Si-based pressure sensors are temperature limited and require a cooling system, while a SiC-based pressure sensor can operate at a higher temperature [5, 23]. Both bulk and thin film SiC are employed as a platform for SiC pressure sensors. Bulk micromachining of SiC diaphragms have been employed for the pressure sensor design. A polycrystalline SiC capacitive pressure sensor has been fabricate and packaged in a high-temperature ceramic package [24]. It can detect ~ 5.17 MPa with a sensitivity of 251  $\mu$ V/psi at 300 °C, and ~ 0.7 MPa with a sensitivity of 7.2 fF/psi at 574 °C. A 6H-SiC diaphragm using photoelectrochemically etching and epitaxially grown n-type 6H-SiC was used to create a 6H-SiC piezoresistive pressure sensor [25]. It can detect 6.9 MPa at 600 °C with minimum junction leakage and no plastic deformation.

3C-SiC thin film grown on Si substrate with potential large scale fabrication can also be used for a pressure sensor. A polycrystalline SiC capacitive pressure sensor grown on Si substrate has been proposed [26]. The linear range of capacitance change with applied pressure is between 22.2 and 31.2 per inch absolute pressure (PSIA) at 500  $^{\circ}$ C. The sensitivity is 0.62 pF/PSIA at 400  $^{\circ}$ C and decreases to 0.53 pF/PSIA at 500  $^{\circ}$ C.

### **1.4 SiC Electronics Low Voltage High Temperature** Application

Much progress has been made for the development of high temperature SiC electronic devices for low voltage or low power analog and digital circuit applications. D. M Brown et al. from Generic Electric Company reported a 6H-SiC operational amplifier based on the n-channel enhancement and depletion mode metal-oxide-semiconductor field effect transistors (MOSFETs). It operates up to 300 °C with a low frequency gain of 53 dB and the bandwidth of 269 kHz [27]. A monolithic 6H-SiC CMOS digital integrated circuits has been developed [28]. The threshold voltages of PMOS and NMOS at 300 °C are -6 V and 0.5 V, respectively. The effect channel mobilities of PMOS and NMOS at 300 °C are 7.01 and 20.8 cm<sup>2</sup>/Vs, respectively. Raytheon has been developed the 4H-SiC CMOS integrated circuit with operating temperature of 400 °C [29]. The gate leakage current is less than 1 pA at 350 °C.

A differential amplifier using 6H-SiC metal-semiconductor field effect transistor (MESFETs) and thick film hybrid technology has been reported [30]. It has a voltage gain of 61 dB, common mode rejection ratio (CMRR) of 60 dB, bandwidth of 910 kHz, offset voltage of 151 mV, and power dissipation of 178 mW at 350 °C. NASA Glenn Research Center has demonstrated a 4H-SiC MESFET based hybrid, ultra high frequency band differential oscillator [31]. The oscillator delivers 4.9 dBm at 453 MHz at 475 °C. M. Alexandru et al. designed and characterized 4H-SiC MESFET based inverter, NAND and NOR gates that operate up to 300 °C [32]. 4H-SiC bipolar junction transistor (BJT) with operating temperature up to 500 °C have been reported [33]. The current gain is approximately 42 at 500 °C using Ti/TiW/Al metallization.

Numerous studies exist on SiC junction field effect transistor (JFETs) for high temperature applications, because the JFET structure is based on pn junction which is

free of oxide reliability and Schottky contact stability existing in MOSFET and MESFET in the temperature range of 500 °C. A back gate n-channel 6H-SiC JFET has been developed and modeled up to 400 °C [34]. Daimler Benz Research Laboratories reported the 6H-SiC implanted-gate n-channel JFETs with operating temperature of 400 °C. The transconductance is approximately 0.16 mS/mm and on/off saturation drain current ratio is ~ 106 at 400 °C. NASA Glenn Research Center has demonstrated very stable long term operation of 6H-SiC n-channel JFETs at 500 °C for more than 3007 hours [35]. A 600 °C of NAND and NOR gates have also been developed at this center [36]. An AC coupled differential amplifier using 4H-SiC vertical JFET has been developed, and the voltage gain is 47.8 dB with CMRR of ~ 45 dB at 500 kHz at 450 °C [37]. A. C. Patil et al. has reported a 6H-SiC JFET based two stage differential amplifier with a voltage gain of 69.2 dB and unit gain frequency of 1.4 MHz at 576 °C [38].

Table 1.4 below summarizes the maximum operating temperature of recent works for low voltage high temperature single transistors including SiC, GaN and diamond. SiC shows promising preliminary results in high temperature electronics. However, many challenges still need to be address before the commercialization. First, the process of making SiC based electronics devices is not as mature as that for Si CMOS, because the design and process approaches for Si based electronics can not be directly used for SiC based electronics due to different materials properties. Besides, the reliability and resistivity of Ohmic contact areas need to be further improved for high temperature operations. Perhaps the most important factor however is that large scale, high quality, and low cost epitaxial or single crystal SiC films have not yet been fully developed. A technology capable of providing these would greatly improve the availability of SiC high temperature electronic devices. In summary, there exist many limitations for SiC based electronics and their integrate circuits; however, the superior material properties of SiC makes it desirable for extremely high temperature electronics.

| References                                            | Material  | Device   | Max. Temperature (°C) |

|-------------------------------------------------------|-----------|----------|-----------------------|

| IMB-CNM, Spain<br>(2012) [32]                         | 4H-SiC    | MESFET   | 300                   |

| Raytheon, UK (2011)<br>[29]                           | 4H-SiC    | MOSFET   | 350                   |

| Semisouth Lab, USA<br>(2009) [39]                     | 4H-SiC    | VJFET    | 450                   |

| JPL, USA (2010) [40]                                  | AlGaN/GaN | MOS HEMT | 450                   |

| Tokyo Insitute of<br>Technology, Japan<br>(2013) [41] | Diamond   | JFET     | 450                   |

| KTH, Sweden (2013)<br>[33]                            | 4H-SiC    | BJT      | 500                   |

| NASA, USA [35]                                        | 6H-SiC    | JFET     | 500                   |

| University of Ulm,<br>Germany (2012) [42]             | InAlN/GaN | HEMT     | 1000                  |

|                                | published single transistors | C 1' 1 /           | 1                |

|--------------------------------|------------------------------|--------------------|------------------|

| I able 1 /l. A campling of     | nublished single transistors | tor high temperatu | re annlications  |

| 1 a O O O I T T A samoning O O |                              | IOI men comporate  | ne applications. |

|                                |                              |                    |                  |

#### **1.5 High Temperature Effects in 4H-SiC**

To successfully design the high temperature 4H-SiC sensors and electronics, it is crucial to understand the temperature effect of the fundamental semiconductor physical properties.

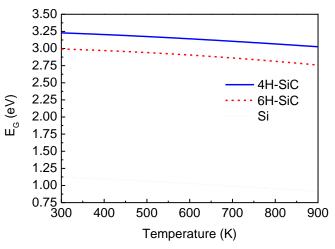

The energy bandgap ( $E_G$ ) in 4H-SiC as a function of temperature is approximated by [43]

$$E_G = 3.265 - 6.5 \times 10^{-4} \left(\frac{T^2}{T + 1300}\right) \tag{1.2}$$

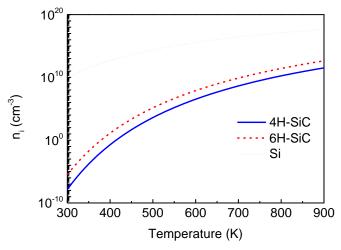

where *T* is temperature. The calculated bandgap of Si, 6H-SiC, and 4H-SiC are plotted in Figure 1.4. 4H-SiC has the highest bandgap through the entire temperature range. As temperature increases, the bandgap is reduced, resulting in larger intrinsic carrier concentrations, larger leakage current in pn junctions and poorer device isolation by reversed-biased junctions [38].

Figure 1.4: Calculated energy bandgap of Si, 6H-SiC, and 4H-SiC versus temperature.

The intrinsic carrier concentration  $(n_i)$  in 4H-SiC is given by [44]

$$n_i = \sqrt{N_c N_v} \exp(-\frac{E_G}{2k_B T}) \tag{1.3}$$

$$N_c = 2M_c \left(\frac{2\pi m_n^* k_B T}{h^2}\right)^{3/2} \tag{1.4}$$

$$N_{\nu} = 2\left(\frac{2\pi m_p^* k_B T}{h^2}\right)^{3/2} \tag{1.5}$$

where  $N_c$  and  $N_v$  are effective density-of-states of electrons in the conduction band and holes in the valence band, respectively.  $k_B$  is Boltzmann constant, h is Planck's constant,  $M_c$  represent the number of equivalent energy minima in the conduction band and is 3 for 4H-SiC,  $m_n^*$  and  $m_p^*$  are the electron effective mass and hole effective mass, respectively. Figure 1.5 compares the intrinsic carrier concentration of Si, 6H-SiC, and 4H-SiC versus temperature. For a given temperature, 4H-SiC has the smallest  $n_i$  due to the largest bandgap energy. The intrinsic carrier concentration of Si at 900 K is  $4.3 \times 10^{17}$  cm<sup>-3</sup> which is comparable with the dopant carrier concentrations. Even at 900 K,  $n_i$  of 6H-SiC and 4H-SiC are only  $4.32 \times 10^{12}$  and  $3.24 \times 10^{11}$  cm<sup>-3</sup>, respectively, suggesting a fundamental advantage of wide bandgap SiC over Si for high temperature application.

Figure 1.5: Intrinsic carrier concentration in Si, 6H-SiC, and 4H-SiC versus temperature.

There are some fundamental properties, such as carrier mobilities and degree of ionization, will be discussed in the following chapter since they are close related to the JFET transistor parameters.

#### **1.6 Research Objective and Thesis Overview**

High-temperature UV sensing chip is beneficial for combustion monitoring and space exploration [45-47]. This dissertation details the two building blocks of high-temperature UV sensing chip, namely UV sensor and transistors.

Chapter 2 investigates the SiC metal-semiconductor-metal (MSM) UV photodetectors (PDs) for high temperature operation. The physics of MSM PDs is first described, then fabrication process. The photo-to-dark current and responsivity of PD are evaluated from room temperature to 450 °C. Finally, the scheme of antireflection layer to boost the PD responsivity is discussed.

In Chapter 3, the study of 4H-SiC n-channel JFET with raised gate configuration is presented. The physics of JFET is discussed and the integration fabrication process of MSM PDs and JFET is described. Metallization scheme for p- and n-type SiC is presented. The basic properties of JFET from 25 to 600 °C is characterized and summarized. TCAD simulation is compared with the measured data, and the possible reasons for different threshold voltage and leakage current are proposed. Finally, a SPICE DC model level 1 is build for the future circuit simulation.

Chapter 4 presents the design of complementary JFET with buried gate configuration. TCAD simulation is used to design the parameters of device structures. One metal stacks forming Ohmic contact with both n- and p- type 4H-SiC at high temperature is described. Current-voltage characteristics and the extracted device parameters are studied in the temperature range of 25-600 °C.

Finally, in Chapter 5 the contributions of this work are summarized and future research directions are suggested.

### **1.7 References**

- [1] L. L. N. Laboratory. *Energy flow*. Available: https://flowcharts.llnl.gov/

- [2] X. Gong, L. An, and C. Xu, "Wireless passive sensor development for harsh environment applications," in *IEEE International Workshop on Antenna Technology (iWAT) 2012*, 2012, pp. 140-143.

- [3] P. G. Neudeck, R. S. Okojie, and L.-Y. Chen, "High-temperature electronics-a role for wide bandgap semiconductors?," *Proceedings of the IEEE*, vol. 90, pp. 1065-1076, 2002.

- [4] N. A. Riza, M. Sheikh, and F. Perez, "Hybrid wireless-wired optical sensor for extreme temperature measurement in next generation energy efficient gas turbines," *Journal of Engineering for Gas Turbines & Power*, vol. 132, p. 051601, 2010.

- [5] D. G. Senesky, B. Jamshidi, K. B. Cheng, and A. P. Pisano, "Harsh environment silicon carbide sensors for health and performance monitoring of aerospace systems: A review," *IEEE Sensors Journal*, vol. 9, pp. 1472-1478, 2009.

- [6] M. Mehregany, "Advances in silicon carbide micro-and nano-electro-mechanical systems fabrication technology and applications," in 2013 Transducers & Eurosensors XXVII: The 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII), 2013, pp. 2397-2402.

- [7] F. Udrea, S. Ali, M. Brezeanu, V. Dumitru, O. Buiu, I. Poenaru, M. Chowdhury, A. De Luca, and J. Gardner, "SOI sensing technologies for harsh environment," in *2012 International Semiconductor Conference (CAS)*, 2012, pp. 3-10.

- [8] J. Casady and R. W. Johnson, "Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review," *Solid-State Electronics*, vol. 39, pp. 1409-1422, 1996.

- [9] M. R. Werner and W. R. Fahrner, "Review on materials, microsensors, systems and devices for high-temperature and harsh-environment applications," *IEEE Transactions on Industrial Electronics*, vol. 48, pp. 249-257, 2001.

- [10] C. S. Roper, "Silicon Carbide Thin Films via Low Pressure Chemical Vapor Deposition for MEMS," Ph. D., Chemical Engineering, University of California at Berkeley, 2007.

- [11] C.-M. Zetterling, *Process technology for silicon carbide devices*: IET, 2002.

- [12] V. Cimalla, J. Pezoldt, and O. Ambacher, "Group III nitride and SiC based MEMS and NEMS: materials properties, technology and applications," *Journal of Physics D: Applied Physics*, vol. 40, p. 6386, 2007.

- [13] E. Monroy, F. Omnes, and F. Calle, "Wide-bandgap semiconductor ultraviolet photodetectors," *Semiconductor Science and Technology*, vol. 18, pp. R33-R51, Apr 2003.

- [14] M. Mehregany, C. Zorman, S. Roy, A. Fleischman, C.-H. Wu, and N. Rajan, "Silicon carbide for microelectromechanical systems," *International materials reviews*, vol. 45, pp. 85-108, 2000.

- [15] A. R. Atwell, R. S. Okojie, K. T. Kornegay, S. L. Roberson, and A. Beliveau, "Simulation, fabrication and testing of bulk micromachined 6H-SiC high-*g* piezoresistive accelerometers," *Sensors and Actuators A: Physical*, vol. 104, pp. 11-18, 2003.

- [16] P. Godignon, "SiC materials and technologies for sensors development," in *Materials Science Forum*, 2005, pp. 1009-1014.

- [17] S. A. Bhave, D. Gao, R. Maboudian, and R. T. Howe, "Fully-differential poly-SiC Lame mode resonator and checkerboard filter," in 18th IEEE International Conference on Micro Electro Mechanical Systems (MEMS 2005), 2005, pp. 223-226.

- [18] W.-C. Lien, "Porous and Epitaxial 3C-SiC Thin Films Technology for Microelectromechanical Systems and Electronics Applications," University of California, Berkeley, 2008.

- [19] N. Wright and A. Horsfall, "SiC sensors: a review," Journal of Physics D: Applied Physics, vol. 40, p. 6345, 2007.

- [20] J. Edmond, H. Kong, A. Suvorov, D. Waltz, and C. Carter Jr, "6H-Silicon Carbide Light Emitting Diodes and UV Photodiodes," *Physica Status Solidi A*, vol. 162, pp. 481-491, 1997.

- [21] D. M. Brown, E. T. Downey, M. Ghezzo, J. W. Kretchmer, R. J. Saia, Y. S. Liu, J. A. Edmond, G. Gati, J. M. Pimbley, and W. E. Schneider, "Silicon carbide UV photodiodes," *IEEE Transactions on Electron Devices*, vol. 40, pp. 325-333, 1993.

- [22] W. C. Lien, D. S. Tsai, S. H. Chiu, D. G. Senesky, R. Maboudian, A. P. Pisano, and J. H. He, "Low-Temperature, Ion Beam-Assisted SiC Thin Films With Antireflective ZnO Nanorod Arrays for High-Temperature Photodetection," *IEEE Electron Device Letters*, vol. 32, pp. 1564-1566, Nov 2011.

- [23] G. Hunter, R. Okojie, P. Neudeck, G. Beheim, G. Ponchak, G. Fralick, J. Wrbanek, and L. Chen, "High temperature electronics, communications, and supporting technologies for Venus missions," in *Proceedings of the Fourth Annual International Planetary Probe Workshop, June*, 2006, pp. 27-30.

- [24] L. Chen and M. Mehregany, "A silicon carbide capacitive pressure sensor for incylinder pressure measurement," *Sensors and Actuators A: Physical*, vol. 145, pp. 2-8, 2008.

- [25] R. S. Okojie, G. M. Beheim, G. J. Saad, and E. Savrun, "Characteristics of Hermetic 6H-SiC Pressure Sensor at 600 C," in AIAA Space 2001 Conference and Exposition, AIAA Paper, 2001, pp. 28-30.

- [26] J. Du and C. A. Zorman, "A polycrystalline SiC-on-Si architecture for capacitive pressure sensing applications beyond 400° C: Process development and device performance," *Journal of Materials Research*, vol. 1, pp. 1-9, 2013.

- [27] D. Brown, E. Downey, M. Ghezzo, J. Kretchmer, V. Krishnamurthy, W. Hennessy, and G. Michon, "Silicon carbide MOSFET integrated circuit technology," *Physica Status Solidi A*, vol. 162, pp. 459-479, 1997.

- [28] S. Ryu, K. Kornegay, J. Cooper Jr, and M. Melloch, "Monolithic CMOS digital integrated circuits in 6H-SiC using an implanted p-well process," *IEEE Electron Device Letters*, vol. 18, pp. 194-196, 1997.

- [29] D. Clark, E. P. Ramsay, A. Murphy, D. A. Smith, R. Thompson, R. Young, J. D. Cormack, C. Zhu, S. Finney, and J. Fletcher, "High temperature silicon carbide CMOS integrated circuits," in *Materials Science Forum*, 2011, pp. 726-729.

- [30] M. Tomana, R. W. Johnson, R. C. Jaeger, and W. C. Dillard, "A hybrid silicon carbide differential amplifier for 350° C operation," *IEEE Transactions on Components, Hybrids, and Manufacturing Technology,* vol. 16, pp. 536-542, 1993.

- [31] Z. D. Schwartz and G. E. Ponchak, "High temperature performance of a SiC MESFET based oscillator," in 2005 IEEE MTT-S International Microwave Symposium Digest, 2005.

- [32] M. Alexandru, V. Banu, M. Vellvehi, P. Godignon, and J. Millán, "Design of Digital Electronics for High Temperature using Basic Logic Gates made of 4H-SiC MESFETs," in *Materials Science Forum*, 2012, pp. 104-108.

- [33] B. G. M. L. Lanni, C.-M. Zetterling, M. Ostling, "A 4H-SiC bipolar technology for high-temperature integrated circuits " in *IMAPS Conference & Exhibition on High Temperature Network (HiTEN 2013)*, 2013.

- [34] S. Zappe, M. Leone, F. Yang, and E. Obermeier, "Characterisation of silicon carbide JFETs with respect to microsystems for high temperature applications," *Microsystem Technologies*, vol. 3, pp. 134-138, 1997.

- [35] P. G. Neudeck, D. J. Spry, L.-Y. Chen, G. M. Beheim, R. S. Okojie, C. W. Chang, R. D. Meredith, T. L. Ferrier, L. J. Evans, and M. J. Krasowski, "Stable Electrical Operation of 6H–SiC JFETs and ICs for Thousands of Hours at 500," *IEEE Electron Device Letters*, vol. 29, pp. 456-459, 2008.

- [36] P. G. Neudeck, G. M. Beheim, and C. S. Salupo, "600 C Logic Gates Using Silicon Carbide JFET's," in 2000 Government Microcircuit Applications Conference, 2000, pp. 20-23.

- [37] J. Fraley, M. Schupbach, J. Yang, B. Western, and A. B. Lostetter, "A 450° C High Voltage Gain AC Coupled Differential Amplifier," in *Materials Science Forum*, 2012, pp. 1253-1256.

- [38] A. C. Patil, "Silicon Carbide JFET Integrated Circuit Technology For High-Temoerature Sensors," Electrical Engineering and Computer Science, Case Western Reserve University, 2009.

- [39] I. Sankin, V. Bondarenko, D. C. Sheridan, M. S. Mazzola, J. B. Casady, J. Fraley, and M. Schupbach, "SiC Lateral Trench JFET for Harsh-Environment Wireless Systems," in *Materials Science Forum*, 2009, pp. 1087-1090.

- [40] K.-A. Son, A. Liao, G. Lung, M. Gallegos, T. Hatake, R. D. Harris, L. Z. Scheick, and W. D. Smythe, "GaN-based high-temperature and radiation-hard electronics

for harsh environments," in SPIE Defense, Security, and Sensing, 2010, pp. 76790U-76790U-8.

- [41] T. Iwasaki, Y. Hoshino, K. Tsuzuki, H. Kato, T. Makino, M. Ogura, D. Takeuchi, H. Okushi, S. Yamasaki, and M. Hatano, "High-Temperature Operation of Diamond Junction Field-Effect Transistors With Lateral pn Junctions," *IEEE Electron Device Letters*, vol. 34, pp. 1175-1177, 2013.

- [42] D. Maier, M. Alomari, N. Grandjean, J.-F. Carlin, M.-A. Diforte-Poisson, C. Dua, S. Delage, and E. Kohn, "InAIN/GaN HEMTs for Operation in the 1000° C Regime: A First Experiment," *IEEE Electron Device Letters*, vol. 33, pp. 985-987, 2012.

- [43] M. E. Levinshtein, S. L. Rumyantsev, and M. S. Shur, *Properties of Advanced Semiconductor Materials: GaN, AIN, InN, BN, SiC, SiGe*: Wiley, 2001.

- [44] T. Ayalew, "SiC Semiconductor Devices Technology, Modeling, and Simulation, "Technical University of Vienna, 2004.

- [45] A. A. Kazemi, "Intersatellite laser communication systems for harsh environment of space," in *SPIE Defense, Security, and Sensing*, 2013, pp. 872010-872010-13.

- [46] E. Kolawa, "Extreme environments technologies for future space science missions," N. A. S. A., 2007.

- [47] D. M. Brown, E. Downey, J. Kretchmer, G. Michon, E. Shu, and D. Schneider, "SiC flame sensors for gas turbine control systems," *Solid-State Electronics*, vol. 42, pp. 755-760, 1998.

# Chapter 2

# Silicon Carbide Metal-Semiconductor-Metal Ultraviolet Photodetectors

### 2.1 Introduction

Photodetectors (PDs), especially for ultraviolet (UV) detection, have drawn interest for use in chemical and biological analysis, combustion flame monitoring, and optical communication devices [1-3]. Over the past few years, different types of PDs have been developed including photoconductor, Schottky barrier photodiodes, p-n and p-i-n photodiodes, avalanche photodiode, phototransistor, metal-insulator-semiconductor structures, and metal-semiconductor-metal (MSM) photodiodes [2, 4].

Most operation environments under UV radiation require the PDs to work at elevated temperatures [2]. However, conventional Si-based PDs, with a narrow bandgap of 1.12 eV, are limited to low operation temperatures (below 125 °C) due to the generation of thermal carriers, significant shifts in the optical properties, and device aging under UV radiation, leading to the severe deterioration in photosensitivity and spectral response [3]. For example, the Si photodiodes exhibit a high dark current density of 0.01 and 10 A/cm<sup>2</sup> at 300 and 500 °C, respectively [5]. Wide-bandgap materials, such as AlN and SiC are potential candidates for the UV photodetection at a high temperature. However, several obstacles need to be overcome before employing wide bandgap semiconductors as UV photodetectors. The first limitation is that the high dopant activation energy is required for these materials making the heavily doped layers with different type of dopants difficult to achieve [6]. The second limitation, which comes with the consequence of the first limitation, is that the lack of reliable Ohmic metal contact to wide bandgap semiconductor at a high temperature [2, 6]. These drawbacks hinder the development of p-n, p-i-n photodiodes and phototransistor by using the wide bandgap materials. On the other hand, MSM PDs based on the two back-to-back Schottky contacts do not require the Ohmic contact, which is beneficial for wide bandgap semiconductors. Furthermore, compared to p-i-n diodes or Schottky barrier photodiodes, MSM PDs offer high operation speed and low capacitance operation, and can be readily integrated with field effect transistors in a single chip without complex fabrication steps [4, 7, 8]. Therefore, MSM PDs using wide bandgap materials is suitable for the development of UV detectors at a high temperature.

Among the variety of wide bandgap materials, 4H-SiC has high thermal conductivity (~4.9 W/cm K, three times larger than Si), strong chemical bond, high electron saturation velocity ( $2 \times 10^{-7}$  cm/s, two times larger than Si) which enables 4H-SiC PDs to operate at high temperature, high power and high radiation environments with high operation speed [6]. In this chapter, we demonstrate a 4H-SiC MSM PD with working temperatures as high as 450 °C. The responsivity under the 325-nm illumination is 0.305 A/W at 20 V bias. 4H-SiC MSM PDs exhibit a fast photoresponse even at 400 °C with rise time and fall time as low as 684 and 786 µs, respectively, demonstrating excellent temperature tolerance and operation speed. This study paves the way for SiC PDs for UV detector applications within extremely harsh conditions.

#### **2.2 Physics of MSM Photodetectors**

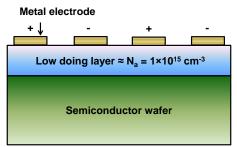

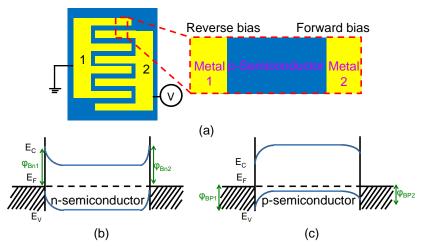

The first metal-semiconductor-metal (MSM) photodetector is demonstrated by T. Sugeta et al. [4]. The structure consists of planar interdigitated metal-semiconductor contacts as shown in Figure 2.1. This structure can be viewed as two back-to-back Schottky barriers of both n- and p- type semiconductor as shown in Figure 2.2. The interdigitated structures allow PDs collecting more photocurrent when they are fully functional. Light is penetrated into semiconductor layers at the gap between of the metal contacts, the layers should have a thickness at least larger than the absorption length  $(1/\alpha)$ , where  $\alpha$  is optical absorption coefficient.

Figure 2.1: Schematic of MSM photodetector.

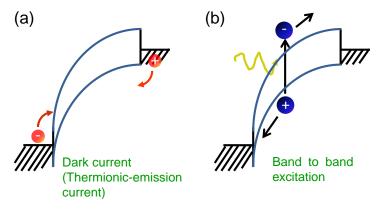

In typical operation, MSM photodetectors consists of two Schottky barriers, bias of any polarity will make one Schottky barrier in the reverse direction and the other in forward bias. When there is no light shinning on the MSM photodetectors, the dark current saturation is mainly due to thermionic-emission current at low bias as shown in Figure 2.3(a) for p-type semiconductor. The saturation current, considering both electron and hole currents, can be expressed as follows

$$I_{dark} = A_1 A_n^* T^2 \exp\left(\frac{-q\phi_{Bn}}{kT}\right) + A_2 A_p^* T^2 \exp(\frac{-q\phi_{Bp}}{kT})$$

(2.1)