## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Multi-level Methodology for PMEM Data Consistency

## Permalink

https://escholarship.org/uc/item/4q1868s6

## Author

Xu, Yi

## Publication Date 2023

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

### Multi-level Methodology for PMEM Data Consistency

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Computer Science**

by

Yi Xu

Committee in charge:

Professor Steven Swanson, Chair Professor Joseph Izraelevitz Professor Paul H. Siegel Professor Geoffrey M. Voelker Professor Jishen Zhao

Copyright

Yi Xu, 2023

All rights reserved.

The Dissertation of Yi Xu is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2023

## DEDICATION

To my family, and to those who have shared this joyful and enriching journey with me.

## EPIGRAPH

Do not go where the path may lead, go instead where there is no path and leave a trail.

Ralph Waldo Emerson

| Disserta              | tion Ap  | proval Page                                                 | iii          |

|-----------------------|----------|-------------------------------------------------------------|--------------|

| Dedicat               | ion      |                                                             | iv           |

| Epigrap               | h        |                                                             | V            |

| Table of              | f Conten | ıts                                                         | vi           |

| List of I             | Figures  |                                                             | ix           |

| List of T             | Tables . |                                                             | xii          |

| Acknow                | ledgem   | ents                                                        | xiii         |

| Vita                  |          |                                                             | xvi          |

| Abstrac               | t of the | Dissertation                                                | xvii         |

| Chapter               | 1 Ir     | ntroduction                                                 | 1            |

| Chapter<br>2.1<br>2.2 | Traditi  | ackgroundional PMEM Machine Modelon-fail PMEM Machine Model | 9<br>9<br>10 |

| Chapter               | -3 L     | og Less, Re-execute More                                    | 13           |

| 3.1                   |          | round                                                       | 13           |

|                       | 3.1.1    | Programming Model                                           | 13           |

|                       | 3.1.2    | Program Analysis Definitions                                | 14           |

| 3.2                   | Clobb    | er Logging Design                                           | 15           |

|                       | 3.2.1    | Undo-Then-Reexecute                                         | 15           |

|                       | 3.2.2    | Improving Performance                                       | 16           |

|                       | 3.2.3    | Clobber Logging                                             | 17           |

| 3.3                   | Clobb    | er-NVM Implementation                                       | 17           |

|                       | 3.3.1    | Using Clobber-NVM                                           | 18           |

|                       | 3.3.2    | Runtime and Callbacks                                       | 20           |

|                       | 3.3.3    | Recovery                                                    | 21           |

|                       | 3.3.4    | Compiler                                                    | 22           |

| 3.4                   | Evalua   | tion                                                        | 26           |

|                       | 3.4.1    | Evaluation Setup                                            | 26           |

|                       | 3.4.2    | Data Structure Benchmarks                                   | 27           |

|                       | 3.4.3    | Performance Breakdown                                       | 31           |

|                       | 3.4.4    | Comparison to iDO                                           | 32           |

|                       | 3.4.5    | Recovery Overhead                                           | 33           |

|                       | 3.4.6    | Memcached                                                   | 34           |

## TABLE OF CONTENTS

|         | 3.4.7   | Vacation                                                             | 36 |

|---------|---------|----------------------------------------------------------------------|----|

|         | 3.4.8   | Yada                                                                 | 37 |

|         | 3.4.9   | Optimization Effectiveness                                           | 38 |

|         | 3.4.10  | Compile Time Overhead                                                | 39 |

| 3.5     |         | 1 Work                                                               | 39 |

| 3.6     | Conclu  | sion                                                                 | 42 |

|         |         |                                                                      |    |

| Chapter | 4 Fa    | nilure is Not an Option, it's an Exception                           | 44 |

| 4.1     | Motiva  | tion                                                                 | 44 |

| 4.2     | Limitat | tions of Prior Art                                                   | 46 |

|         | 4.2.1   | Limitations of Transactions                                          | 46 |

|         | 4.2.2   | Limitations of FASEs                                                 | 47 |

| 4.3     | Proof.  |                                                                      | 51 |

|         | 4.3.1   | Definitions                                                          | 51 |

|         | 4.3.2   | Proof Sketch                                                         | 52 |

| 4.4     | Design  |                                                                      | 53 |

|         | 4.4.1   | Overview                                                             | 54 |

|         | 4.4.2   | Ensuring State Persistence                                           | 55 |

|         | 4.4.3   | Ensuring Correct Restoration                                         | 56 |

| 4.5     | Implen  | nentation                                                            | 57 |

|         | 4.5.1   | Process Life Cycle                                                   | 57 |

|         | 4.5.2   | Kernel-resident State                                                | 61 |

|         | 4.5.3   | Failures in kernel mode                                              | 62 |

|         | 4.5.4   | Limitations                                                          | 62 |

| 4.6     | Evalua  | tion                                                                 | 63 |

|         | 4.6.1   | Evaluation Setup                                                     | 63 |

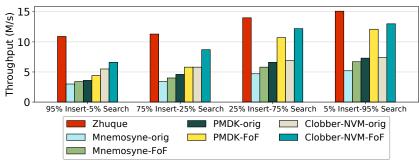

|         | 4.6.2   | Microbenchmarks                                                      | 65 |

|         | 4.6.3   | Python Benchmarks                                                    | 67 |

|         | 4.6.4   | Memcached                                                            | 68 |

|         | 4.6.5   | Vacation and Yada                                                    | 69 |

| 4.7     | Related | l Work                                                               | 70 |

| 4.8     |         | sion                                                                 | 72 |

|         |         |                                                                      |    |

| Chapter | 5 Le    | everaging Persistent Memory in Key-value Stores via a Crash-safe and |    |

|         | D       | urable Cache                                                         | 74 |

| 5.1     | Key-Va  | alue Stores                                                          | 74 |

| 5.2     | PERSIS  | STRON Overview                                                       | 78 |

|         | 5.2.1   | Objectives                                                           | 78 |

|         | 5.2.2   | High-level Design and Challenges                                     | 78 |

|         | 5.2.3   | Comparison to Prior Approaches                                       | 80 |

| 5.3     | PERSIS  | STRON PMEM Cache                                                     | 81 |

|         | 5.3.1   | Cache Internals                                                      | 81 |

|         | 5.3.2   | Transaction Mechanisms                                               | 82 |

|         | 5.3.3   | Crash Recovery                                                       | 84 |

|                 | 5.3.4   | Inferring Transactions                  | 85  |

|-----------------|---------|-----------------------------------------|-----|

|                 | 5.3.5   | Non-Transactions                        | 86  |

| 5.4             | DRAM    | I Caching                               | 86  |

|                 | 5.4.1   | Clean Hot Page Caching                  | 87  |

|                 | 5.4.2   | Warm Page Eviction                      | 87  |

|                 | 5.4.3   | Hybrid Cache Control                    | 88  |

|                 | 5.4.4   | Transactions Involving DRAM Pages       | 88  |

|                 | 5.4.5   | Non-Transactions Involving DRAM Pages   | 89  |

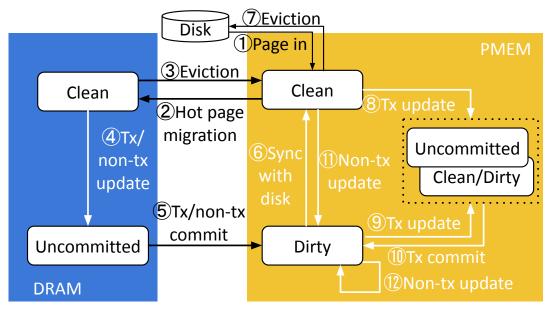

|                 | 5.4.6   | Life Cycle of a Page                    | 90  |

| 5.5             | PERSIS  | STRON Integration with SplinterDB       | 91  |

| 5.6             |         | tion                                    | 92  |

|                 | 5.6.1   | Experimental Setup                      | 92  |

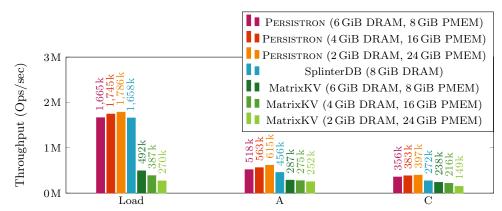

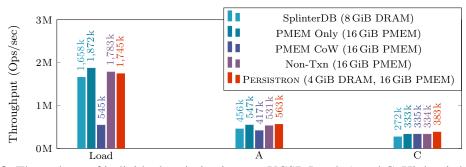

|                 | 5.6.2   | Cost-Equivalent Hardware Configurations | 93  |

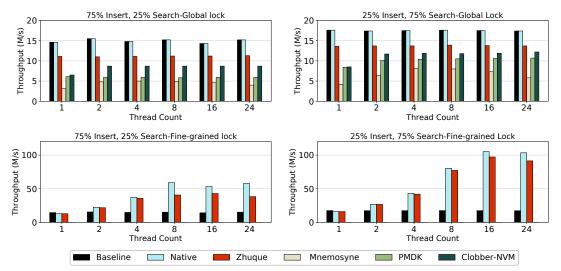

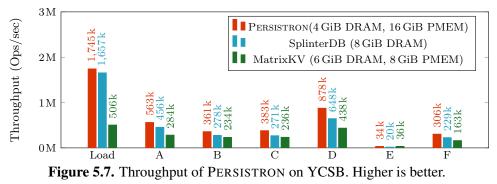

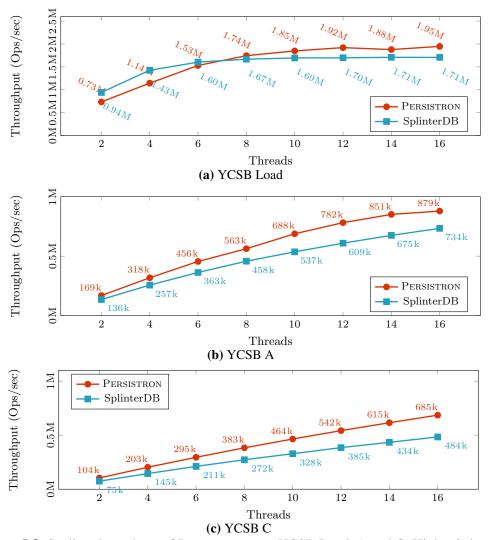

|                 | 5.6.3   | YCSB                                    | 95  |

|                 | 5.6.4   | Scaling                                 | 95  |

|                 | 5.6.5   | Impact of Individual Optimizations      | 97  |

| 5.7             | Related | 1 Work                                  | 98  |

| 5.8             | Conclu  | sion                                    | 100 |

|                 |         |                                         |     |

| Chapter         | 6 C     | onclusion                               | 101 |

| Dibligan        | onhu    |                                         | 105 |

| Bibliography 10 |         |                                         | 103 |

## LIST OF FIGURES

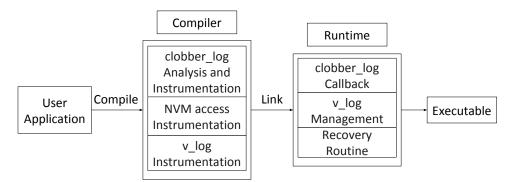

| Figure 3.1.  | Clobber-NVM system overview                                                                                                                                                                                                                                                                          | 17 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2.  | List insert operation using PMDK and Clobber-NVM                                                                                                                                                                                                                                                     | 19 |

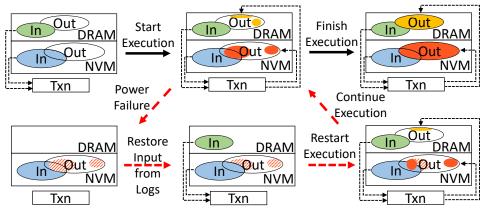

| Figure 3.3.  | Recovery process of one transaction. The <i>In</i> and <i>Out</i> indicates input and output addresses within both DRAM and PMEM                                                                                                                                                                     | 23 |

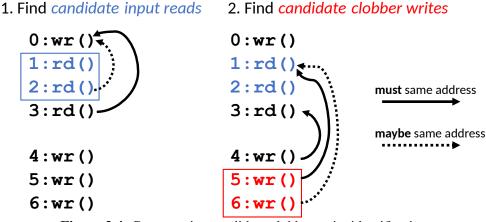

| Figure 3.4.  | Conservative candidate clobber write identification                                                                                                                                                                                                                                                  | 24 |

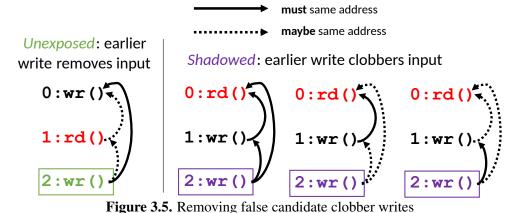

| Figure 3.5.  | Removing false candidate clobber writes                                                                                                                                                                                                                                                              | 25 |

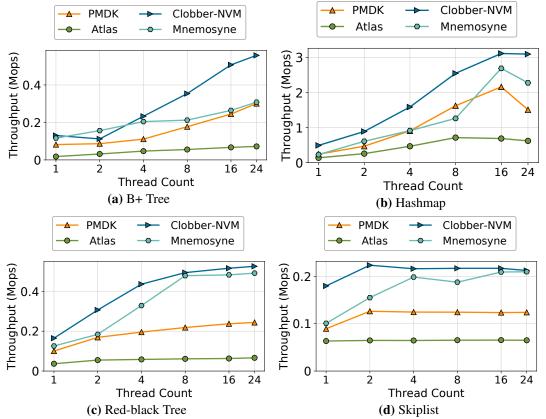

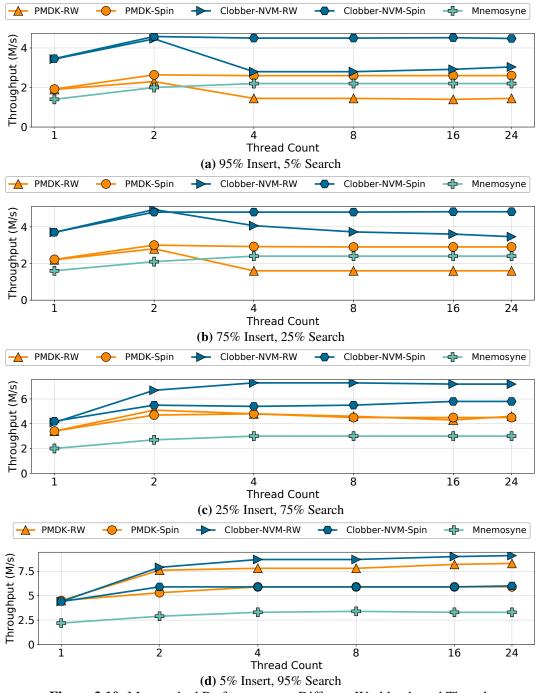

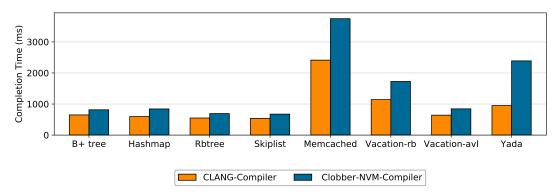

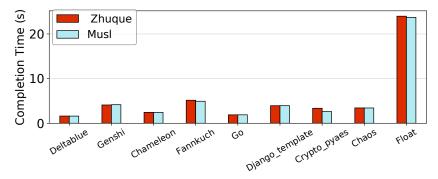

| Figure 3.6.  | Measuring the throughput of different PMEM libraries: each data structure<br>is scaled up to 24 thread. Clobber-NVM shows better performance over<br>other libraries on all data structures                                                                                                          | 28 |

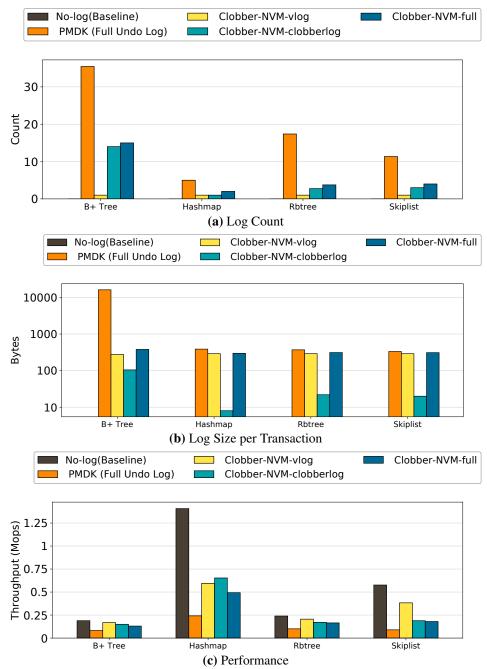

| Figure 3.7.  | Measuring the overhead of different logging strategies: different log count<br>and log size result in different performance. The operated key-value pair<br>has key size 8 bytes (32 bytes for B+ Tree), and value size 256 bytes                                                                    | 30 |

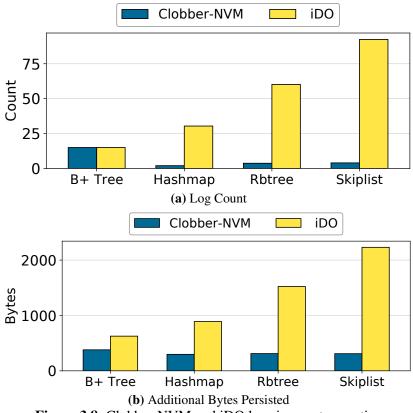

| Figure 3.8.  | Clobber-NVM and iDO log size per transaction                                                                                                                                                                                                                                                         | 33 |

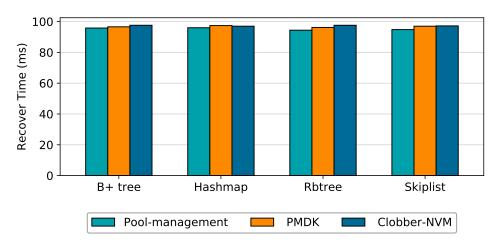

| Figure 3.9.  | Recovery overhead on different data structure                                                                                                                                                                                                                                                        | 34 |

| Figure 3.10. | Memcached Performance on Different Workloads and Threads                                                                                                                                                                                                                                             | 35 |

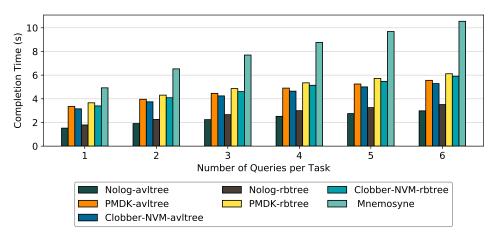

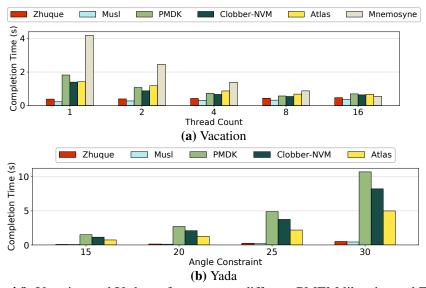

| Figure 3.11. | Vacation performance on different data structure                                                                                                                                                                                                                                                     | 37 |

| Figure 3.12. | Yada Performance on Different Angle Constraining                                                                                                                                                                                                                                                     | 38 |

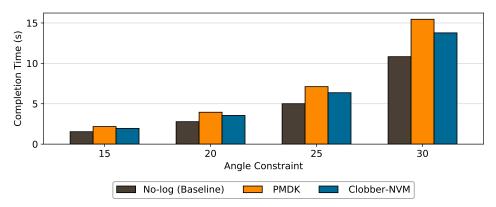

| Figure 3.13. | Optimization effectiveness on data structures and applications                                                                                                                                                                                                                                       | 40 |

| Figure 3.14. | Compile latency on data structures and applications                                                                                                                                                                                                                                                  | 40 |

| Figure 4.1.  | FASE counterexample                                                                                                                                                                                                                                                                                  | 49 |

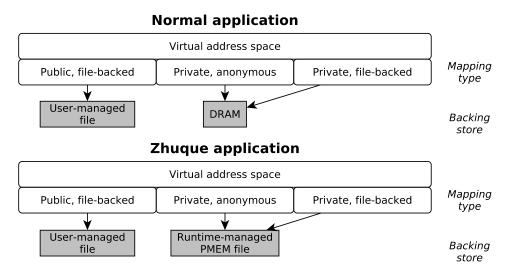

| Figure 4.2.  | Virtual memory in Zhuque. The runtime modifies the backing store based<br>on the mapping type, but the interface presented to the userspace applica-<br>tion does not change                                                                                                                         | 53 |

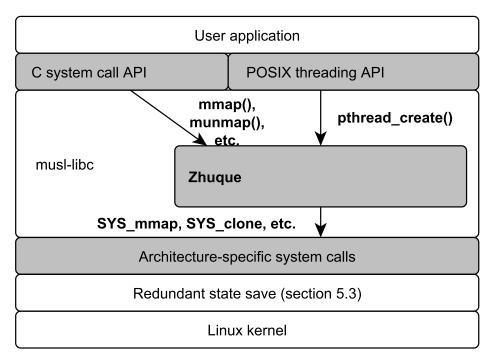

| Figure 4.3.  | Zhuque architecture. User applications link to the C APIs provided by musl<br>libc, and we modify the implementation of the APIs and the arguments<br>passed to the underlying system calls. To protect against failures in kernel<br>mode, we save userspace context to PMEM on entry to the kernel | 58 |

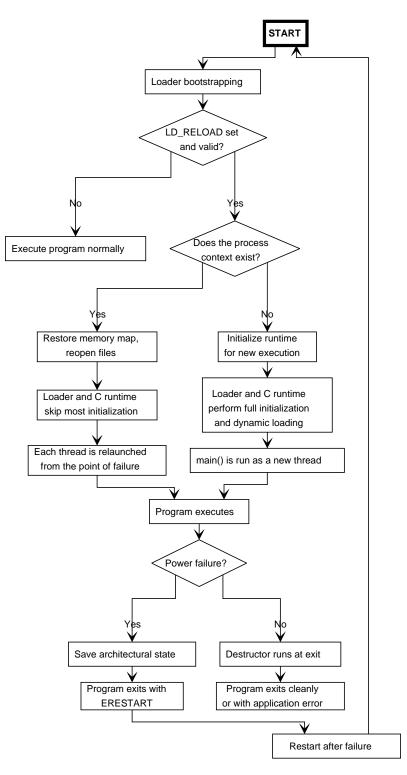

| Figure 4.4. | Zhuque runtime control flow. Zhuque modifies runtime startup and termi-<br>nation; application code is not modified                                                                                                                                                                                                             | 59 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

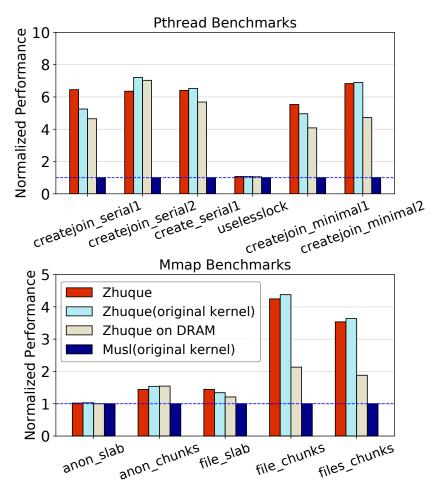

| Figure 4.5. | Measuring the overhead of Zhuque on basic operations. Performance values are normalized to the Musl(original kernel) value                                                                                                                                                                                                      | 66 |

| Figure 4.6. | Measuring the overhead of different Python benchmarks: Zhuque matches native performance on some benchmarks                                                                                                                                                                                                                     | 67 |

| Figure 4.7. | Porting Existing PMEM Libraries to Flush-on-Fail Machines Provides up to 1.76× Improvement                                                                                                                                                                                                                                      | 67 |

| Figure 4.8. | Zhuque Enables Newest Version of Memcached to Run on PMEM, Pro-<br>vides Significantly Better Performance                                                                                                                                                                                                                       | 68 |

| Figure 4.9. | Vacation and Yada performance on different PMEM libraries and Zhuque                                                                                                                                                                                                                                                            | 70 |

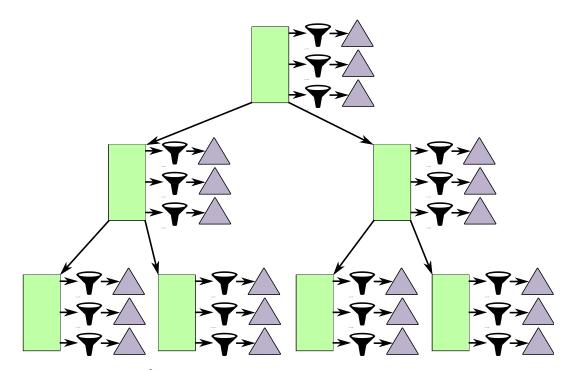

| Figure 5.1. | A size-tiered $B^{\varepsilon}$ -tree, the data structure in SplinterDB. Trunk nodes ( $\square$ ) contain pointers to children and to filters ( $\heartsuit$ ) and branches ( $\triangle$ ). In SplinterDB, branches are B-trees.                                                                                              | 75 |

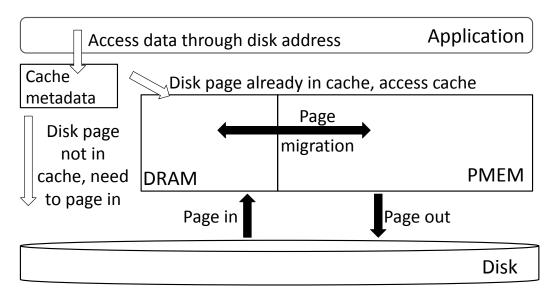

| Figure 5.2. | <b>PERSISTRON architecture.</b> The figure shows the high-level architecture of PERSISTRON. Applications access on-disk data through the caching layer, which is consisted of a DRAM portion and a PMEM portion. Pages dynamically migrate between the two portions.                                                            | 79 |

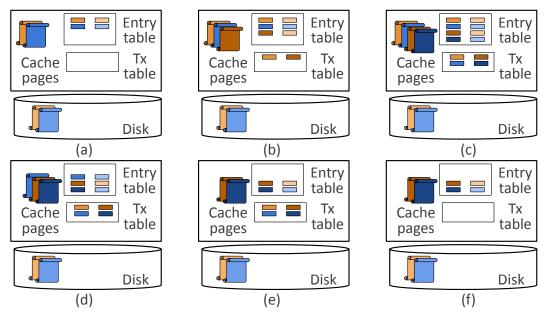

| Figure 5.3. | <b>PERSISTRON Cache Metadata.</b> The figure shows the metadata structures maintained in PERSISTRON's cache. The entry table stores entry metadata for each cache entry. The lookup table stores the mapping from disk address to cache entry number. The transaction table records per-thread transaction management metadata. | 82 |

| Figure 5.4. | <b>PERSISTRON Transactions.</b> The figure shows the sequence of events that happen during normal transaction execution. If failure happens during (a)-(c), PERSISTRON rolls back the transaction. Otherwise, the transaction will be rolled forward.                                                                           | 83 |

| Figure 5.5. | <b>PERSISTRON page life cycle.</b> The figure shows the change of a disk page's in-cache state. The state changes through page read, update, transaction commit, synchronization with the disk, page in, and eviction                                                                                                           | 90 |

| Figure 5.6. | Throughput of cost-equivalent configurations of PERSISTRON on YCSB Load, A and C. Higher is better                                                                                                                                                                                                                              | 93 |

| Figure 5.7. | Throughput of PERSISTRON on YCSB. Higher is better.                                                                                                                                                                                                                                                                             | 95 |

| Figure 5.8. | Scaling throughput of PERSISTRON on YCSB Load, A and C. Higher is better.      | 96 |

|-------------|--------------------------------------------------------------------------------|----|

| U           | Throughput of individual optimizations on YCSB Load, A and C. Higher is better | 97 |

### LIST OF TABLES

Table 5.1.Existing Approaches. The table shows how different approaches exploit persistent<br/>memory in a multi-level hierarchy consisting of DRAM, PMEM, and SSD. None of the<br/>existing approaches utilize PMEM for both immediate persistence and capacity.80

#### ACKNOWLEDGEMENTS

I feel very fortunate and grateful for having the support from many wonderful people. This dissertation would not be possible without them.

First of all, I want to express my gratitude to my advisor, Professor Steven Swanson, for always supporting and believing in me. Throughout this incredible journey, he has been a constant source of inspiration and encouragement. I want to thank him for his support during my moments of doubt, for providing me with the space and freedom to explore my own path, for his patience and being a good listener, and for always being there to guide me when I'm uncertain. I have truly enjoyed and benefited from our discussions on research and life. These conversations have been incredibly inspiring, providing me with invaluable insights and helping me become a better person. Thanks to his mentorship, pursuing a Ph.D. has been an unforgettable and joyful experience. I couldn't have imagined a better Ph.D. journey. I feel truly fortunate to have him as my advisor, and I am deeply grateful for the profound impact he has had on my academic and personal growth.

I want to thank my committee members Professor Geoffrey M. Voelker, Professor Jishen Zhao, Professor Paul H. Siegel, and Professor Joseph Izraelevitz for their valuable comments and feedbacks. I want to express my gratitude to Professor Geoffrey M. Voelker. Every interaction with him, be it during class, committee meetings, or non-academic occasions like the wonderful hiking trips he organized, has been an absolute pleasure. I am truly thankful for the enriching conversations we've shared. I also want to specially thank Professor Joseph Izraelevitz. From the very start of my Ph.D., he has been by my side, providing unwavering support and guidance. As a wonderful mentor and teacher, he has played a crucial role in shaping my journey and growth. I am truly grateful for his presence during the initial phase of my Ph.D. journey.

I want to thanks my collaborator George Hodgkins. I also want to thank my colleagues and friends from NVSL and UCSD. I want to thank Amirsaman Memaripour, Jian Yang, Lu Zhang, Morteza Hoseinzadeh, Juno Kim for their support and guidance. I want to thank Zixuan Wang, Suyash Mahar, Narangerelt Batsoyol, Ziheng Liu, Mingyao Shen, Yun Joon Soh, Chen Chen, Yaxuan Wu, Ke Sun, Renjie Zhao, Yizhou Shan, Haolan Liu, and Zhi Wang. This journey would not be the same without you. I will always miss the time we spend together.

I want to thank my mentors, collaborators and friends from VMware Research and UIUC: Ramnatthan Alagappan, Alex Conway, Aishwarya Ganesan, Rob Johnson, Prashant Pandey, Xundong Sun, Henry Zhu. I appreciate their mentorship and guidance. I truly enjoyed the time spent at VMware Research.

Lastly, I want to express my deepest gratitude to my parents. They have been an unwavering source of support and courage, always encouraging me to pursue my dreams and standing by me in every decision I make. Their love and guidance have shaped me into the person I am today. I cannot adequately put into words how much I love and appreciate them.

Chapter 1, Chapter 2, Chapter 3, and Chapter 6 contain material from "Clobber-NVM: Log Less, Re-execute More", by Yi Xu, Joseph Izraelevitz, and Steven Swanson, which appeared in the Proceedings of International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2021. The dissertation author is the primary investigator and first author of this paper.

Chapter 1, Chapter 2, Chapter 4, and Chapter 6 contain material from "Zhuque: Failure is Not an Option, it's an Exception", by George Hodgkins\*, Yi Xu\* (\*co-first author), Steven Swanson, and Joseph Izraelevitz, which appeared in 2023 USENIX Annual Technical Conference (USENIX ATC 23). The dissertation author is the primary investigator and co-first author of this paper.

Chapter 1, Chapter 2, Chapter 5, and Chapter 6 contain material from "Persistron: Leveraging Persistent Memory in Key-value Stores via a Crash-safe and Durable Cache", by Yi Xu, Ramnatthan Alagappan, Aishwarya Ganesan, Rob Johnson, and Alex Conway, which was submitted for publication at 2024 International Conference on Management of Data. The dissertation author is the primary investigator and first author of this paper.

Permission to make digital or hard copies of part of all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage.

VITA

| 2018      | Bachelor of Science in Computer Science & Technology, Southeast University   |

|-----------|------------------------------------------------------------------------------|

| 2019      | Internship, Oracle                                                           |

| 2021      | Internship, VMware Research Group                                            |

| 2022      | Internship, VMware Research Group                                            |

| 2018-2023 | Graduate Student Researcher, University of California San Diego              |

| 2022      | Candidate of Philosophy, University of California San Diego                  |

| 2023      | Doctor of Philosophy in Computer Science, University of California San Diego |

#### PUBLICATIONS

**Yi Xu**, Ramnatthan Alagappan, Aishwarya Ganesan, Rob Johnson, Alex Conway. "Persistron: Leveraging Persistent Memory in Key-Value Stores via a Crash-safe and Durable Cache", *submitted to ACM SIGMOD International Conference on Management of Data (SIGMOD 2024)*

George Hodgkins\*, **Yi Xu\***, Steven Swanson, Joseph Izraelevitz. "Zhuque: Failure is Not an Option, it's an Exception", *2023 USENIX Annual Technical Conference (USENIX ATC 2023)*, Boston, MA, July 2023 (\* marks equal contribution).

**Yi Xu**, Joseph Izraelevitz, Steven Swanson. "Clobber-NVM: Log Less, Re-execute More", 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2021), Virtual, April 2021.

Joseph Izraelevitz, Jian Yang, Lu Zhang, Juno Kim, Xiao Liu, Amirsaman Memaripour, Yun Joon Soh, Zixuan Wang, **Yi Xu**, Subramanya R. Dulloor, Jishen Zhao, Steven Swanson. "Basic Performance Measurements of the Intel Optane DC Persistent Memory Module", *Arxiv*, March 2019.

#### ABSTRACT OF THE DISSERTATION

#### Multi-level Methodology for PMEM Data Consistency

by

Yi Xu

Doctor of Philosophy in Computer Science

University of California San Diego, 2023

Professor Steven Swanson, Chair

Persistent memory (PMEM) allows direct access to persistent storage via a load/store interface. It promises to realize a vision of high performance, data persistence, a simple programming interface, low cost with minimal storage overhead. Previously, processor caches backed by PMEM were volatile, complicating the design of persistent applications and reducing their performance. The new generation of systems with flush-on-fail semantics provides persistent caches, offering the potential for much simpler, faster PMEM programming and execution models.

PMEM programming systems provide the means to apply sets of writes to persistent states atomically. Unfortunately, most of these systems impose significant overhead and are not

easy to use. Moreover, most existing approaches to incorporating PMEM realize only a subset of the benefits of PMEM.

This dissertation first presents Clobber-NVM, a failure-atomicity library that ensures data consistency by reexecution. Clobber-NVM's novel logging strategy, *clobber logging*, records only those transaction inputs that are overwritten during transaction execution. Then, after a failure, it recovers to a consistent state by restoring overwritten inputs and reexecuting any interrupted transactions. Clobber-NVM utilizes a clobber logging compiler pass for identifying the minimal set of writes that need to be logged. Based on our experiments, Clobber-NVM provides up to  $2.5 \times$  performance improvement over existing solutions.

Second, it introduces Whole Process Persistence (WPP), a new programming model for systems with persistent caches. In the WPP model, all process state is made persistent. On restart after a power failure, this state is reloaded and execution resumes in an applicationdefined interrupt handler. We describe the Zhuque runtime, which transparently provides WPP by interposing on the C bindings for system calls in userspace. It requires little or no programmer effort to run applications on Zhuque. Our measurements show that Zhuque significantly outperforms state-of-the-art PMEM libraries. More important, unlike existing systems, Zhuque places no restrictions on how applications implement concurrency, allowing us to run a newer version of Memcached on Zhuque and gain more than  $7.5 \times$  throughput over the fastest existing persistent implementations.

Finally, it presents PERSISTRON, a key-value store that exploits PMEM effectively with almost no change to the storage layer. Our main observation is that most key-value stores employ a cache to avoid expensive access to storage. By moving the cache layer to PMEM and using regular cache-management functions to manage PMEM, most code is untouched, and the cache is potentially reusable for other applications. We have implemented PERSISTRON by modifying SplinterDB. PERSISTRON can improve query performance by up to 46% over a cost-equivalent all-DRAM configuration of SplinterDB.

xviii

# Chapter 1 Introduction

Persistent memory (PMEM), whether it be based on Intel Optane [56] or flash-backed DRAM over CXL [100], presents new opportunites and challenges for storage systems. PMEM exposes persistent storage as fast, byte-addressable main memory, and allow the processor to access persistent data via load and store instructions directly using the memory bus. PMEM provides instantaneous durability: writes can be persisted almost immediately, allowing inmemory data to live beyond process lifetimes and even across system reboots and unexpected power failures. PMEM is also likely to be approximately an order of magnitude cheaper per gigabyte than DRAM [68].

These unique characteristics present the opportunity to build storage systems which are:

- 1. Fast;

- 2. Simple, because serialization and deserialization can be avoided between CPU and persistent domain;

- 3. Cost-effective, because DRAM can be replaced with cheaper PMEM;

- 4. Capacity-efficient, because applications no longer need to maintain redundant copies of data in both main memory and persistent storage;

- Instantly durable, because writes can be immediately persisted in PMEM without requiring IOs to external storage devices.

Building a system that realizes the promise of persistent programming is not simple.

One of the main challenges to obtaining these potential benefits is the complexity of retrofitting existing code to use PMEM efficiently. PMEM is slower than DRAM, so simply replacing all DRAM with PMEM will result in a slower system overall. Furthermore, PMEM is not likely to be cheap enough to replace flash in large-scale storage systems, and therefore PMEM is likely to be a new component of the memory hiearchy.

Moreover, as caches are volatile, the contents of CPU caches do not survive power loss, and, since caches may delay evicting a modified cache line, writes may not reach PMEM in program execution order. These limitations mean that in the case of an unexpected power loss, a set of logically atomic updates may be torn with only a subset of them reaching PMEM, leaving persistent data in an inconsistent state. This makes reasoning about the state of memory after a crash extremely challenging.

In order to ensure persistent data consistency in the case of power failures, programmers must design applications carefully. Custom solutions use cache line flush instructions to force data from volatile caches to PMEM in a consistent order. However, building applications on the low-level, cache-line-based primitives the ISA provides is difficult.

Over the past decades, many solutions have been proposed to handle data consistency during power failures. These solutions span the spectrum, ranging from custom log-free data structures to user-level "transactional" programming libraries, and to key-value stores. These solutions hide different complexities from programmers and offer various interfaces. However, none of these methods have been proven to fully leverage the potential benefits of PMEM.

In this dissertation, we explore three design points that could potentially expose PMEM in a more efficient and easier-to-use way for upper-level applications in future computer systems.

Programming systems (e.g., libraries, programming models, language support, and

2

compilers) aim to help address the challenges of generic persistent memory programming. They have proliferated over the last decade. Broadly, three families of systems have emerged: each takes a different approach to consistency, and each faces significant challenges which bar widespread adoption.

The first and largest family [123, 112, 97, 127] requires programmers to access persistent state only through well-defined atomic operations (often called transactions). This provides a clean notion of consistency: after recovery from crash, each atomic section has either executed entirely or not at all, meaning that all writes within a specified code region will survive a power loss and become persistent in PMEM, or none will. These transaction-like, "all-or-nothing" semantics make programming on PMEM easier and hide architectural and caching details from programmers.

However, like all transactional memory models, this approach suffers from serious weaknesses: it is fundamentally incompatible with non-transactional synchronization, and has never gained significant traction in real systems.

Moreover, although failure-atomicity libraries give programmers the ability to designate failure-atomic code regions (transactions), this support comes with high performance overhead. Most industrial failure atomicity systems [97, 11] use an undo logging approach. In undo logging systems, where incomplete transactions are undone, the logging of the old value must occur before each write. Undo-based systems have a significant advantage in that reads do not need to be redirected via an interposition layer, but at the cost of many expensive persistence ordering fences [91].

To avoid the high logging cost, JUSTDO logging [61] proposed *recovery-via-resumption*. In contrast to undo logging, JUSTDO logging tracks enough program state (including the program counter) to *resume* a failure-atomic operation at recovery, resuming execution from the interrupted instruction. Subsequent work in iDO logging [85] dramatically increased performance by exploiting regions of code that are idempotent (a segment of code that does not overwrite its inputs). However, the runtime overhead of these systems remains quite high.

3

The second family of PMEM programming systems [12, 54, 61, 85] uses FASEs, regions of code protected by locks, as atomic regions for PMEM updates. Legacy code can run with minimal changes, but these systems suffer from fundamental weaknesses arising from complex locking schemes and external IO. As we will show, addressing these weaknesses either cripples the system or essentially reduces it to a transaction-based system.

The final family of systems takes the more dramatic step of making *everything* in the system persistent via whole-system persistence (WSP) [92]. WSP provides the conceptually simplest programming model: Nothing much changes and, from the program's perspective, crashes never occur. WSP faces two major challenges: First, making all of memory persistent has until recently been infeasible, because regularly flushing volatile caches to PMEM creates enormous performance overheads. Second, making *everything* persistent would require a farreaching redesign of many system components, for an unclear benefit.

The generic PMEM programming systems promises to realize a vision of high performance, data persistence, a simple programming interface, and low storage overhead at the same time. However, they are agnostic of the application characteristics. In addition, their performance and capacity are often constrained by the limitations of PMEM.

As a result, researchers are investigating designs for multi-level hierarchies that incorporate DRAM, PMEM, and SSD in key-value stores. Most current approaches either exploit PMEM's immediate persistence or large capacity, but not both. More concretely, one approach statically decides to move some structures (e.g., the memtable [67], the log [125], or the upper levels of an LSM [125]) in to PMEM. These systems mutate these structures directly on PMEM, thus achieving immediate persistence. However, this approach does not store other (potentially large and frequently accessed) portions of data in the PMEM, forgoing capacity benefits. In contrast, the second approach uses PMEM as an extended read-only cache to augment the existing DRAM block cache, neglecting PMEM's persistence. For example, recent work on RocksDB at Facebook [68] uses PMEM as an extended volatile cache; data in PMEM is discarded after a crash. HYMEM and Spitfire [130, 110] exploit PM capacity and persistency at the same time, but both require substantial code changes.

In this dissertation, we address the failure recovery problem at the transaction level, process level, and caching system level, respectively.

In Chapter 3, we introduce Clobber-NVM, a PMEM library that ensures failure-atomicity by reexecuting interrupted transactions. Clobber-NVM relies on a new logging method *clobber logging*, which merges undo logging with recovery-via-resumption. Clobber logging undo logs any transaction inputs overwritten during transaction execution. If a transaction is interrupted by a failure, clobber logging recovers by first restoring the transaction's overwritten inputs then, subsequently, reexecuting the transaction to completion. This strategy results in our system requiring far less logging than traditional undo-based systems since it only logs a few inputs — in our experiments we reduce the log sizes by  $1.1 \times$  to  $42.6 \times$ , and the log count (ordering fences) by  $2.4 \times$  to  $4.7 \times$ .

In Chapter 4, we propose that WSP-style persistence is due for a renaissance: The advent of PMEM devices and platforms supporting *flush-on-fail* semantics (e.g. eADR for NVDIMMs or GPF for CXL devices) allows developers to treat caches as effectively persistent [60, 27], removing the main performance argument against WSP. Further, we believe that limiting the scope of persistence to a process – yielding *Whole Process Persistence (WPP)* – and providing well-defined, application-level semantics for system failures combine to produce a programming model that is fast, flexible enough to support legacy programs and complex locking schemes, and easy for programmers to use and understand.

WPP provides a simple abstraction to the process: its entire memory is persistent and will survive a power outage. If a power outage occurs, the process receives an OS signal after restart notifying it of the crash. The process can install a normal error handler for this signal which cleans up and exits, or performs more complex application-specific recovery; by default, program execution simply continues at the point of failure.

We describe Zhuque runtime, which provides WPP. Zhuque is faster than existing PMEM programming systems. It is between  $4.7 \times$  and  $10.14 \times$  faster than PMDK [97], Mnemosyne [112],

5

Atlas [12] and Clobber-NVM [123] on STAMP applications. Zhuque is also more flexible than these systems: Since Zhuque is agnostic about the application's locking scheme, it can run the most recent version of memcached, while those systems cannot. As a result, our Zhuque-based persistent memcached is more than  $7.5 \times$  faster than any similar system. We also demonstrate Zhuque's flexibility by running unmodified Python benchmarks with minimal performance loss.

In Chapter 5, we present PERSISTCACHE, a grey-box DRAM/PMEM caching system that requires only small changes to storage layer code in order to achieve the speed, cost, and durability advantages of PMEM-based systems.

PERSISTCACHE combines a straightforward copy-on-write DRAM/PMEM cache and migration policy with hints from the application that enable it to avoid copy-on-write overheads when they are not needed for crash safety. Thus almost all code changes are in the cache, with only a few hints required from the application code.

The core idea behind the design of PERSISTCACHE is that the cache layer is an effective place to introduce PMEM support into an existing storage system. Most storage systems employ a DRAM cache, so this approach should be broadly applicable without major code changes. Implementing PMEM support at the cache layer enables us to use both DRAM and PMEM to create a large cache and to decide which pages live in PMEM versus DRAM, which makes it possible to ensure durability and to avoid PMEM overheads when possible. Furthermore, by ensuring persistence at the cache layer, we can provide instant durability and avoid the overheads of logging.

To ensure that the contents of the PMEM cache always remain consistent, even after a crash, PERSISTCACHE employs a *COW-based transaction mechanism*. No or little keyvalue store code needs modification to use this transaction mechanism: PERSISTCACHE infers transaction boundaries from lock acquisition and release points.

PERSISTCACHE enables high performance via two techniques: *selective transactional updates* and *DRAM caching*. Naively using transactions for all modifications can be prohibitively expensive. PERSISTCACHE allows intermediate storage updates that don't require crash safety (such as building new data structures that aren't yet linked into the main storage data structure) to be performed non-transactionally, which reduces overhead. This is implemented by having the storage system provide hints to the caching layer when transactions are not needed.

Second, while PMEM is faster than SSD, it is still considerably slower than DRAM; thus, it is hard to match the performance of a DRAM-only cache. To solve this problem, PERSISTCACHE uses a (generally smaller) DRAM cache in addition to the PMEM cache. Hot, clean pages are opportunistically moved to the DRAM cache for better read performance. Warm pages are kept around in PMEM, reducing disk accesses.

With this approach, PERSISTCACHE presents a new design point to leverage PMEM effectively. While many prior papers propose radically new ways to manage PMEM, we take a contrarian view: we realize that PMEM can be incorporated into the cache layer, and standard cache-management functions can be used to leverage this new hardware effectively. This view has great practical utility: it delivers high performance while keeping code change to other parts of the application to a minimum.

We have implemented PERSISTCACHE by modifying the cache layer of SplinterDB, a production key-value store that offers high performance. The implementation is mostly self-contained in the caching layer. SplinterDB uses a log-structured merge tree (LSM) as its internal data structure. To integrate with the rest of SplinterDB, we added application-specific hints to mark non-transaction boundaries, such as compactions, and we also reworked one function that needed to be crash safe but could not be easily expressed as a transaction (see Chapter 5.5). We call the resulting key-value store PERSISTRON.

In our experiments, we compare PERSISTRON on a hybrid PMEM/DRAM cache to SplinterDB on a dollar-equivalent all-DRAM cache. PERSISTRON insertion throughput is up to 8% faster than in SplinterDB and query throughput is up to 46% faster, demonstrating that PERSISTRON is able to exploit the increased capacity of PMEM without suffering from its lower performance relative to DRAM. Furthermore, PERSISTRON provides instant durability, whereas SplinterDB does not. We also evaluated against MatrixKV and found that PERSISTRON

insertions were  $3.5 \times$  faster than in MatrixKV and queries were up to 65% faster.

## Acknowledgements

This chapter contains material from "Clobber-NVM: Log Less, Re-execute More", by Yi Xu, Joseph Izraelevitz, and Steven Swanson, which appeared in the Proceedings of International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2021. The dissertation author is the primary investigator and first author of this paper.

This chapter contains material from "Zhuque: Failure is Not an Option, it's an Exception", by George Hodgkins\*, Yi Xu\* (\*co-first author), Steven Swanson, and Joseph Izraelevitz, which appeared in 2023 USENIX Annual Technical Conference (USENIX ATC 23). The dissertation author is the primary investigator and co-first author of this paper.

This chapter contains material from "Persistron: Leveraging Persistent Memory in Key-value Stores via a Crash-safe and Durable Cache", by Yi Xu, Ramnatthan Alagappan, Aishwarya Ganesan, Rob Johnson, and Alex Conway, which was submitted for publication at 2024 International Conference on Management of Data. The dissertation author is the primary investigator and first author of this paper.

## Chapter 2 Background

PMEM has introduced new possibilities for designing storage systems: programs can have byte-addressable access to terabytes of persistent data at near-DRAM latencies. However, utilizing PMEM in a both performant and programmer-friendly manner remains a challenging problem.

This chapter provides necessary background on PMEM and clarifies assumptions about our target systems. We describe the expected machine models.

## 2.1 Traditional PMEM Machine Model

Clobber-NVM is designed for a modern machine equipped with some persistent memory (e.g. Intel Optane DC PMM's [59] or persistent CXL.mem devices [100]). This multicore, cache-coherent machine contains a set of processing cores, with private and shared write-back caches. The caches contain a program's current working set, loaded from the backing memory, which consists of both persistent memory and traditional DRAM. Stores issued by the cores modify cache lines in the caches; subsequent cache line evictions write the modified data back to either volatile (DRAM) or persistent memory, depending on the cache line's physical address. The hardware manages the cache line eviction policy, it may not evict cache lines in the same order they were modified. Moreover, writes are not persistent as long as they reside in the volatile cache. The existence of volatile caches with uncontrolled eviction policies means that the programmer needs to reason about the order in which data updates reach persistent memory. For example, in a stack push() operation, the node must be created *and made persistent* before pointed to by the top pointer. Otherwise the top pointer could be evicted from the cache and become persistent, while its target node, still in the volatile caches, could be lost in a power outage, leaving behind a dangling, persistent, pointer.

To avoid these inconsistencies, programmers must use cache-flush and memory-barrier instructions to enforce the ordering of stores into PMEM. For example, on Intel CPUs, the clflush or clwb instructions explicitly force a dirty cache line into memory, and sfence ensures subsequent writes will not complete until previous flushes that issued before the sfence have reached memory. However, frequent ordering fences limit the overlapping of long-latency flush instructions, result in high runtime overhead [50].

We expect hybrid machines with both PMEM and DRAM in the near term. It is important for the programmer to specify whether the manipulated memory is volatile or not. Programmers can mark regions of the program's address space persistent, and these memory regions are associated each with some named file in a PMEM-aware file system [119, 115, 18]. In the event of a failure, the file system can remap the file into another process's address space for recovery and further use.

## 2.2 flush-on-fail PMEM Machine Model

WPP and PERSISTRON are designed for a multi-core, cache-coherent machine equipped with PMEM (e.g. Intel Optane DC PMM's [59] or persistent CXL.mem devices [100]), and supporting *flush-on-fail* semantics, meaning that they provide a hardware guarantee that all in-flight and cached writes will reach PMEM in the event of an external power failure (as opposed to a fault in the machine or its onboard power supply). Such guarantees are provided by eADR-compliant platforms and NVDIMMs, and CXL platforms and devices supporting Global Persistent Flush (GPF). eADR and GPF are similar solutions targeting different device interfaces: the primary hardware requirement for both is that the platform must store sufficient energy to allow caches and internal device buffers to be drained to persistence after a power failure [1, 100].

On x86 systems, both eADR and GPF require system firmware to initiate and oversee the drain to persistence in response to a System Management Interrupt (SMI) [1, 27, 26]. Upon receiving this interrupt, the processor retires all in-flight instructions, drains all stores to the cache, and saves architectural state (register file etc.) to a designated per-core memory region before beginning execution of the SMI handler [29]. In both GPF and eADR, this handler first flushes the processor caches (and, for CXL, the caches of any CXL.cache device), and then proceeds to flush the buffers on the PMEM devices (NVDIMMs for eADR, CXL.mem devices for GPF) [1, 27].

Applications still need to ensure updates are crash-consistent, but do not necessarily need to evict cachelines to enforce update persistency.

## Acknowledgements

This chapter contains material from "Clobber-NVM: Log Less, Re-execute More", by Yi Xu, Joseph Izraelevitz, and Steven Swanson, which appeared in the Proceedings of International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2021. The dissertation author is the primary investigator and first author of this paper.

This chapter contains material from "Zhuque: Failure is Not an Option, it's an Exception", by George Hodgkins\*, Yi Xu\* (\*co-first author), Steven Swanson, and Joseph Izraelevitz, which appeared in 2023 USENIX Annual Technical Conference (USENIX ATC 23). The dissertation author is the primary investigator and co-first author of this paper.

This chapter contains material from "Persistron: Leveraging Persistent Memory in

Key-value Stores via a Crash-safe and Durable Cache", by Yi Xu, Ramnatthan Alagappan, Aishwarya Ganesan, Rob Johnson, and Alex Conway, which was submitted for publication at 2024 International Conference on Management of Data. The dissertation author is the primary investigator and first author of this paper.

## Chapter 3 Log Less, Re-execute More

## 3.1 Background

This chapter provides necessary background and clarifies assumptions about our target systems. Clobber-NVM is designed for a modern machine equipped with both PMEM and DRAM, with volatile CPU cache. We begin by describing the expected programming model, then provide necessary concepts for our program analysis.

#### **3.1.1 Programming Model**

Clobber-NVM is one of many *failure-atomicity libraries* that provide a simpler programming model for PMEM: we describe this model here. With these libraries, a programmer can designate a region of code to be *failure-atomic*, that is, all of the code region's effects will survive a failure (e.g. power loss), or none will. Once the effects of the code region are guaranteed to survive a crash, the operation is *committed*. In general, in order to ensure failure-atomicity, it is necessary to log extra information during normal execution to support *recovery* after a failure. Recovery code can then use this extra, *logged* information to clean up interrupted failure-atomic operations and return back to a consistent state.

In the literature, these failure-atomic code regions (or *operations*) are often termed *failure-atomic sections (FASEs)*, or *transactions*. Generally speaking, the boundaries of the transaction are programmer defined using some interface of the underlying failure atomicity

runtime. Note that these transactions are not traditional ACID (Atomicity, Consistency, Isolation, Durability) transactions [49, 46] — depending on the system, they may or may not provide isolation. That said, many failure-atomicity libraries link failure atomicity to concurrency control, either by building full ACID semantics or marking lock-protected critical sections as failure-atomic regions.

Clobber-NVM is a recovery-via-resumption failure-atomicity system. In these systems, interrupted transactions are resumed; this strategy stands in contrast to more traditional undo [97, 11] and redo [113, 54, 83] logging based systems, where interrupted failure-atomic updates roll back. Recovery-via-resumption requires saving sufficient program state such that resumption is possible.

Clobber-NVM uses an interface of transactions conceptually compatible with Intel's PMDK [97] library. Following this interface, we expect the programmer to explicitly mark failure atomic transactions. Furthermore, following PMDK's concurrency model, we expect transactions to acquire and release locks in a conservative, strong strict two-phase locking pattern [98, 114]: that is, locks protect memory locations from data races; transactions acquire the associated lock at transaction begin and in a fixed order (to prevent deadlock); transactions hold the locks until transaction commit. Assuming the programmer follows these constraints, both PMDK and Clobber-NVM transactions provide true ACID semantics.

#### **3.1.2 Program Analysis Definitions**

Clobber-NVM's design relies on compiler dependency analysis to minimize the amount of logging needed for proper reexecution and recovery of interrupted transactions. We describe key concepts required for this analysis here.

A Clobber-NVM *transaction* is a programmer-delineated code region with a single entry and (possibly) multiple exits. Following standard terminology [32], a code region (resp. transaction) *output* is a variable value which is assigned within the region and is *live-out* from its exit. That is, a region output is a value written in the region and read after it. Similarly, we define a code region (resp. transaction) *input* to be a variable value that is *live-in* to the region and used within the region. That is, a region input is a value assigned before the region's execution and read within it. Note that both inputs and outputs refer to values, not variables (a natural consequence of LLVM's SSA-based [41, 39] program represention).

A code region is *deterministic* if, for a given set of inputs, it always produces the same set of outputs. Clobber-NVM expects its transactions to be deterministic, and to not cause runtime errors or program exits (e.g., segmentation faults). This assumption is universal for recovery-via-resumption systems [61, 85, 3].

## **3.2** Clobber Logging Design

Clobber logging is a recovery strategy that minimizes logging calls and log size by recording overwritten inputs to a transaction. If the transaction is interrupted, recovery proceeds by restoring the overwritten inputs then recevcuting the transaction. Clobber logging's key insight is that logging only overwritten inputs is sufficient to reexecute a transaction with the exact same results, and, as a consequence, values at other addresses never need to be logged, since they will be overwritten upon reexecution.

Following the concepts introduced in Chapter 3.1.2, we deem a transaction input a *clobbered input* if it may be overwritten within this transaction, and term this write a *clobber write*. Clobbered inputs are a problem for reexecution. If an input is clobbered during transaction execution, reexecuting the code will use a new value for the input.

#### **3.2.1 Undo-Then-Reexecute**

To understand how clobber logging can ensure failure atomicity, we first describe a naive version of clobber logging that ignores dependency analysis. We term this explanatory failure-atomicity strategy *undo-then-reexecute*.

At every store, undo-then-reexecute records an undo log entry containing the old, overwritten value. On recovery, it replays the undo log backwards, leaving erasing all effects of the transaction. Instead of stopping at this point (as conventional undo logging would), undo-thenreexecute then reexecutes the transaction from start to finish.

Undo-then-reexecute differs from classical undo logging in a few notable ways. First, it recovers the program state to a point after the interrupted transaction, as opposed to before. Second, once started, a transaction never rolls back, so a transaction can be marked as committed soon as it begins. Finally, undo-then-reexecute assumes that inputs unmodified by the transaction will be available for reexecution during recovery. In our machine model, this assumption does not hold for data in DRAM or shared with other threads. Inputs in volatile memory will disappear during a power failure, and shared inputs might change prior to reexecution.

A correct version of undo-then-reexecute must address these challenges: First, it must make a persistent copy of volatile inputs so they are available after restart. Second, it must adapt a concurrency model that prevents transaction inputs from being changed after being read and transaction outputs from being read before commit (e.g. through its locking scheme).

### **3.2.2 Improving Performance**

Undo-then-reexecute and undo logging are both slow since they log the same information at every store. For a PMEM library to optimize undo-then-reexecute, it should attempt to remove extraneous logging. First, it should understand what logging is truly necessary in order to ensure that reexecution gives the same result. Second, it should understand what logging operations are unnecessary because it will reexecute the transaction.

To ensure reexecution of a transaction gives the same result, the transaction needs to be deterministic and have the same inputs (arguments and memory state) as the previous interrupted execution. This is why the undo-then-reexecute strategy needs the "undo" step: it needs to revert the transaction's clobbered inputs to their unmodified state.

However, undo logging records more than the clobbered transaction inputs: it also records the old values before writes to the transaction output addresses (e.g. modified memory locations). Traditional undo logging relies on these records to roll back the transaction's changes. But

Figure 3.1. Clobber-NVM system overview

undo-then-reexecute does not need to undo its changes. Because it will reexecute the transaction, and the transaction will write the same values to the same memory locations, any written data from the previous execution will be regenerated and overwritten.

## 3.2.3 Clobber Logging

The clobber logging strategy is simply this: undo-then-reexecute, but *only* undo log before clobber writes. Like any correct undo-then-reexecute strategy on a persistent memory system, clobber logging needs to preserve volatile inputs and adapt an appropriate concurrency scheme. Clobber logging optimizes undo-then-reexecute by logging the clobbered inputs and ensuring all non-clobber inputs are available during recovery. Then, it reexecutes the transactions to produce the correct results. As we will show, clobber logging require less logging and incurs lower runtime overheads than conventional undo logging.

## **3.3** Clobber-NVM Implementation

The Clobber-NVM failure-atomicity system is a joint compiler/runtime library. Key system components are shown in Figure 3.1.

Our compiler extension, built on top of LLVM [76, 41], is principally used to identify clobber writes within transactions using dependency analysis. Due to aliasing, this identification requires significant reasoning about dependency chains. After this analysis, the compiler adds callbacks to both clobber writes and to memory accesses within transactions to automate logging

and recovery.

Our runtime library manages the program during execution and recovery. It catches callbacks inserted by the compiler and programmer and directs the accesses to the appropriate logs. The runtime manages two logs: the clobber\_log, which logs clobbered inputs, and the  $v_log$ , which logs volatile transaction inputs (inputs that reside either on the stack or in the volatile heap and would not be available during recovery. Usually these are function arguments).

The runtime will also initiate recovery of interrupted transactions after a crash. Recovery, for each transaction, proceeds by first restoring volatile state from the  $v_log$  and restoring clobbered state from the clobber\_log, then reexecuting the interrupted transaction using the restored inputs.

To create a Clobber-NVM program, a developer needs to write transactions in a manner that meets our programming model, compile using our compiler with its extensions, and link to our runtime library. Recovering a Clobber-NVM program is done by restarting the program.

## 3.3.1 Using Clobber-NVM

Clobber-NVM's C programming model is designed to be easily used — most of its annotations and requirements have equivalents in Intel's PMDK library.

Figure 3.2(a) shows an example transaction written for Clobber-NVM, which executes a persistent list insertion (the equivalent PMDK C and C++ code are also shown). First, note the Clobber-NVM transaction is isolated within a function (line 1), termed the txfunc. Clobber-NVM's compiler instruments the call-site to collect the function name and its arguments within the v\_log, and the function provides a convenient handle to initiate reexecution.

Upon entering the function, the appropriate locks are acquired on both persistent data (the list) and the volatile data (the new value). As with PMDK, transactions must be synchronized using conservative, strong strict two-phase locking for proper recovery [102]. We use the txbegin macro to start the actual transaction (line 4). As we intend to use a volatile non-local pointer within the transaction, we must record it using the vlog\_preserve macro (line 5). With

```

void plist_ins(plist* lst, char* v,

2 size_t vsz, lock* v_lk){

lock(lst->lk); lock(v_lk);

3

txbegin();

4

vlog_preserve(v,vsz);

5

pnode* n = pmalloc(sizeof(pnode));

6

n->val = pmalloc(strlen(v));

7

strcpy(n->val, v);

8

n \rightarrow nxt = lst \rightarrow hd;

9

// lst->hd is a clobbered input

10

// and will be clobber logged

11

lst->hd = n;

12

txend();

13

unlock(lst->lk); unlock(v_lk);

14

15 }

```

(a) Clobber-NVM

```

16 void plist_ins(TOID(plist) lst,

17 char* v, lock* v_lk){

lock(lst->lk); lock(v_lk);

18

TX_BEGIN(pop){

19

TOID(struct pnode) n =

20

21

TX_NEW(struct pnode);

D_RW(n) \rightarrow val =

22

TX_NEW(strlen(v));

23

TX_ADD_FIELD(n, val);

24

strcpy(D_RW(n)->val, v);

25

TX_ADD_FIELD(n, nxt);

26

27

D_RW(n) \rightarrow nxt = D_RO(lst) \rightarrow hd;

TX_ADD_FIELD(lst, hd);

28

29

D_RW(lst) \rightarrow hd = D_RO(n);

}TX_END {}

30

unlock(lst->lk); unlock(v_lk);

31

32 }

```

(b) PMDK C

```

33 void plist::ins(char* v,

34 lock* v_lk){

auto p = pool_by_vptr(this);

35

transaction::run(p,[this,v]{

36

37

auto n =

make_persistent<pnode>(v);

38

strcpy(n->val, v);

39

n->nxt = this->hd;

40

this->hd = n;

41

},this->lk,v_lk);

42

43 }

```

(c) PMDK C++

#### Figure 3.2. List insert operation using PMDK and Clobber-NVM

locks acquired and volatile inputs recorded, we can execute the transaction.

At the transaction's beginning, we allocate memory from PMEM using the pmalloc interface (lines 6 and 7). Note that on line 12, we will change the list head to the new node, thereby clobbering a transaction input — this clobbered input will be identified automatically by the compiler, and then recorded by the runtime. Also note that Clobber-NVM does not require special macros when accessing persistent memory — the appropriate callbacks are added by the compiler. Assuming no power loss, the transaction will terminate and commit with the txend macro (line 13), and release its locks (line 14).

#### **3.3.2 Runtime and Callbacks**

Clobber-NVM's runtime manages the program's persistent state during execution and recovery. This task requires it to manage a few internal structures and to catch all necessary callbacks, added by both the user and the compiler.

The user is responsible for invoking four callbacks. The txbegin and txend macros inform the runtime of a starting or committing transaction, triggering a persistent update of the transaction's status. The pmalloc macros informs the runtime to allocate memory from PMEM, instead of DRAM. As the application's semantics decide which sets of writes should happen failure-atomically and which memory allocation should allocate from PMEM, the compiler is unable to assist with these callbacks. The vlog\_preserve macro informs the runtime that some volatile non-local pointer input will be used during transaction execution — this input must be preserved persistently in the v\_log. As compiler analysis is necessarily incomplete with respect to the transaction's read set, and as the appropriate v\_log callbacks must occur at transaction begin, the developer must provide this information.

The compiler inserts other callbacks handled by the runtime. The first type of callback occurs at possible clobber write sites. This callback triggers a logging action in the runtime to record the clobbered inputs in its clobber\_log. The second callback occurs at every memory access, and allows the runtime to appropriately swizzle pointers to support relocatable backing

PMEM storage. The final callback occurs on the top of txfuncs — this callback is used to record soon-to-begin transaction, collects the function name and its arguments.

Our runtime is implemented over Intel's PMDK v1.6 libpmemobj — it replaces the transaction, logging, allocation, and recovery management but preserves the user-facing interface for PMEM region management and crash detection. In particular, Clobber-NVM's runtime manages two key logging systems: the clobber\_log, which holds clobbered inputs, and the  $v_log$ , which holds both volatile inputs and tracks ongoing transaction state. Every ongoing transaction maintains one log  $v_log$  entry.

Our clobber\_log is built over PMDK's undo log API. This design choice leaves Clobber-NVM's clobber\_log very simple, and provides an additional benefit — as PMDK's performance improves, so does Clobber-NVM.

In contrast, the v\_log is directly managed by the runtime. We manage the per-thread v\_log using a global linked list resident in persistent memory, and allocate it on thread creation. The thread will use this log to manage its (at most one) active transaction. Using both the vlog\_preserve macro and the compiler instrumented callback on entry into the txfunc, the log records the function arguments, function name and additional needed volatile data in the log at transaction begin. We use a single bit in each v\_log to decide if re-execution is necessary on its corresponding thread. When the transaction begins, it is marked as ongoing, and the bit is cleared at commit.

### 3.3.3 Recovery

Clobber-NVM recovers PMEM data to a consistent state via re-execution. We here describe the Clobber-NVM's recovery process.

Figure 3.3(top row) shows a transaction progressing through normal execution. At transaction begin (top left), its inputs are already initialized and its outputs have not yet been touched. As the transaction executes (Figure 3.3, top center), it reads inputs, from both PMEM and DRAM, and writes to output addresses to both PMEM and DRAM. Note that some writes to

21

output addresses may be clobber writes and will overwrite some inputs. During normal execution, the transaction will progress to completion and commit (Figure 3.3, top right), completely writing all outputs.

A transaction interrupted by a crash follows a different path. As with normal execution, the transaction starts with initialized inputs and untouched outputs (Figure 3.3, top left), then progresses through execution by writing to some output addresses (Figure 3.3, top center), including clobber writes. However, a power failure during execution drops the transaction to the recovery path.

After the power loss, the transaction loses all volatile memory and some PMEM values that still resided in the machine's (volatile) caches (Figure 3.3, bottom left). At restart, Clobber-NVM first detects if there are any uncommitted, ongoing transactions using the per-thread  $v_{-}$ logs. Using the transaction's logs, Clobber-NVM restores both the volatile and clobbered inputs, though the values at output addresses may still be inconsistent (Figure 3.3, bottom center).

With its inputs restored, the transaction is ready to restart (Figure 3.3, bottom right). Clobber-NVM recovers each thread independently — a valid strategy since our locking scheme ensures all ongoing transaction lock sets are disjoint. To recover a transaction, the corresponding txfunc is called, reexecuting the transaction from the beginning. Once the transaction executes past the point when the failure happened, the transaction has overwritten any incomplete values, erasing any inconsistencies caused by the power loss (Figure 3.3, top center). The transaction will continue to progress to completion and commit (Figure 3.3, top right).

# 3.3.4 Compiler

Clobber-NVM compiler identifies clobber writes and insert other utility callbacks.

The first compiler pass identifies writes within a transaction that may clobber an input, then instruments the clobber\_log callback before the writes happen. This pass relies on classic alias analysis to identify clobber writes. However, this basic alias analysis is not necessarily precise and may over identify clobber writes, though this is a performance, not a safety issue.

22

Figure 3.3. Recovery process of one transaction. The *In* and *Out* indicates input and output addresses within both DRAM and PMEM.

The pass subsequently refines the result through novel analysis propagation.

Then the second pass adds callbacks to all memory accesses: these callbacks allow the system to intercept accesses to PMEM and, as necessary, swizzle the pointers to redirect the accesses to the relocatable backing region. Finally, the third pass instruments the code for recovery: it adds v\_log callbacks to the txfunc to record their names and arguments.

Clobber-NVM's compiler is built on top of LLVM [76, 41]. We use clang [37] as the frontend compiler to translates C/C++ code to LLVM IR, and introduce the three passes [40] described above to the LLVM compiler toolchain. All passes operate on LLVM IR [39].

In the remainder of this subsection, we describe our clobber write identifying pass in detail, starting with the conservative implementation, then describing our iterative refinement.

**Conservative Clobber Writes Identification** Clobber-NVM's conservative clobber write identification follows two steps. The first step identifies *candidate input reads*, that is, reads that could conceivably be the first operation on a value. The second step uses these reads to find *candidate clobber writes*, that is, writes that could conceivably overwrite an input. Note that both steps are conservative — all possible input reads and all possible clobber writes will be candidates.

The identification pass relies on LLVM alias analysis [38] to identify candidate input reads and clobber writes. Alias analysis produces pair-wise results that indicate two memory accesses (1) cannot, (2) may or (3) must point to the same location.

Figure 3.4. Conservative candidate clobber write identification

Using alias analysis, the first step traverses all reads in the transaction, searching for candidate input reads. Reads that are *dominated* by an earlier write (all paths to the read first execute the write), and whose dominating write must modify the same address, cannot be candidate input reads. All other reads are labeled as a candidate input read. Figure 3.4(left) shows this process.

In the second step, the compiler identifies candidate clobber writes for each candidate input read. Candidate clobber writes include all *successor* writes (writes that may be executed after the input read) that may write to the same address as the input read. Figure 3.4(right) shows this identification.

At this point, the compiler has conservatively identified all clobber writes, but some candidates may never overwrite an input. Figure 3.4(right) shows an example of such a candidate clobber write on line 6: the input will already be clobbered on line 5.

**Dependency Analysis Propagation** To reduce Clobber-NVM's logging cost, we perform additional dependency analysis propogation to remove candidate clobber writes that, upon further analysis, can never be true clobber writes. We target two general types of *false clobber candidates*.

The first type of false clobber candidate we term *unexposed*. This false candidate may indeed be the first write to overwrite a candidate input, but, if it does — it is provable the input candidate is a false input. The scenario is shown in Figure 3.5(left). In this scenario, the

candidate input read is dominated by some earlier write. Since the earlier write and the read may not access the same location, the read is considered a candidate input. The subsequent write may also access the read's location, and so it is considered to be a clobber candidate. However, both writes are guaranteed to access the same location through alias analysis — as a consequence, if the later write overwrites the read, the read cannot be an input (it will be dominated by the earlier write).

The second type of false clobber write candidate is a candidate which is *shadowed* by some earlier clobber write. A shadowed candidate may indeed overwrite an input, but if it does, it is guaranteed that some earlier write already clobbered it. This relationship requires two conditions. First, it requires some earlier write to dominates the shadowed write. Secondly, the alias relationship between the input read, earlier write, and shadowed write must ensure that if the shadowed write does overwrite the input, the earlier write will have first. There are three alias combinations between the three accesses that meet these criteria: they are shown in Figure 3.5(right). In practice, this kind of false candidate occurs often in loops: the first iteration clobbers the input, but subsequent iterations do not need to log.

Our analysis searches for both types of false clobber candidates by iterating over every pair of a candidate clobber write and its corresponding input read, and then looking for an additional write that would then form one of these four cases.

# 3.4 Evaluation

In this section, we evaluate Clobber-NVM's performance to provide answers to the following questions:

- How much improvement does Clobber-NVM provide for persistent data structures compared to other libraries?

- What is the reason for Clobber-NVM's high performance?

- What is Clobber-NVM's recovery overhead compared to PMDK?