# UC San Diego

**UC San Diego Electronic Theses and Dissertations**

# Title

Coding for flash memories

**Permalink** https://escholarship.org/uc/item/2sh083mw

**Author** Yaakobi, Eitan

Publication Date 2011

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

# **Coding for Flash Memories**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Communication Theory and Systems)

by

Eitan Yaakobi

Committee in charge:

Professor Paul H. Siegel, Co-Chair Professor Alexander Vardy, Co-Chair Professor Ilya Dumer Professor Alon Orlitsky Professor Steven Swanson

2011

Copyright Eitan Yaakobi, 2011 All rights reserved. The dissertation of Eitan Yaakobi is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Co-Chair

University of California, San Diego

2011

DEDICATION

Dedicated to my parents and to the memory of Prof. Jack K. Wolf.

| TABLE OF CONTENTS |

|-------------------|

| Signature Page        |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dedication            |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Table of Contents   v |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| List of Figures       |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| List of Tables        |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Acknowledgements      |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Vita                  | xiii                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Abstract of the       | e Dissertation                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Chapter 1             | Introduction11.1Background11.2Flash Memory Basics21.3Codes for Flash Memories31.4Dissertation Overview4                                                                                                                                                                                                                                                                                  |  |  |  |

|                       | Bibliography 5                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Chapter 2             | Rewriting Codes for Flash Memories82.1Introduction82.2Preliminaries and Flash Codes Definition92.3Two Bits Flash Codes92.4Index-less Indexed Flash Codes132.5Nearly Optimal Construction162.6Flash Codes of Constant Rate222.7Buffer Codes232.7.1Buffer Codes Definition232.7.2Single-Cell Buffer Codes232.7.3Multiple-Cells Buffer Codes252.8Conclusion and Open Problems29Bibliography |  |  |  |

| Chapter 3             | Codes for Write-Once Memories       32         3.1       Introduction       32         3.2       Preliminaries       33         3.3       Previous Work       35         3.4       Two-Write WOM-Codes       38         3.4.1       Two-Write WOM-Codes Construction       39                                                                                                            |  |  |  |

|           | 3.4.2 Random Coding                                                              |

|-----------|----------------------------------------------------------------------------------|

|           | 3.4.3 Application to the Blackwell Channel                                       |

|           | 3.5 Multiple-Write WOM-Codes                                                     |

|           | 3.5.1 Non-binary Two-Write WOM-Codes                                             |

|           | 3.5.2 Three-Write WOM-Codes                                                      |

|           | 3.5.3 Four-Write WOM-Codes                                                       |

|           | 3.5.4 Multiple-Write WOM-Codes                                                   |

|           | 3.6 Concatenated WOM-Codes                                                       |

|           | 3.7 Fixed-rate WOM-codes                                                         |

|           | 3.8 Summary and Comparison                                                       |

|           |                                                                                  |

|           | Bibliography 63                                                                  |

| Chapter 4 | Multiple Error-Correcting WOM-Codes    66                                        |

|           | 4.1 Introduction                                                                 |

|           | 4.2 Preliminaries and Previous Work                                              |

|           | 4.3 Single-Error-Detecting WOM-Codes                                             |

|           | 4.4 Single-Error-Correcting WOM-Codes                                            |

|           | 4.5 Double-Error-Correcting WOM-Codes                                            |

|           | 4.6 Triple-Error Correcting WOM-Codes                                            |

|           | 4.7 Multiple Error-Correcting WOM-Codes                                          |

|           | 4.8 Summary and Conclusions                                                      |

|           | Bibliography                                                                     |

| Chapter 5 | On Codes that Correct Asymmetric Errors with Graded Magnitude Distri-            |

| _         | bution                                                                           |

|           | 5.1 introduction                                                                 |

|           | 5.2 Preliminaries                                                                |

|           | 5.3 Constructions of <i>t</i> -Asymmetric $\ell$ -Limited-Magnitude              |

|           | Error-Correcting Codes                                                           |

|           | 5.4 A Construction of $(t_1, t_2)$ -Asymmetric                                   |

|           | $(\ell_1, \ell_2)$ -Limited-Magnitude Error-Correcting Codes                     |

|           | 5.5 A Construction of $(1, 1)$ -Asymmetric $(1, \ell)$ -Limited-Magnitude Error- |

|           | Correcting Codes                                                                 |

|           | 5.6 Conclusion                                                                   |

|           | Bibliography 103                                                                 |

| Chapter 6 | On The Parallel Programming of Flash Memory Cells                                |

|           | 6.1 Introduction                                                                 |

|           | 6.2 Terms and Concepts                                                           |

|           | 6.3 Optimal Programming without Feedback                                         |

|           | 6.4 Programming with Inter-Cell Interference                                     |

|           | 6.5 Feedback Information on Cell Levels                                          |

|           | 6.6 Programming with Feedback Information on Cell Levels 127                     |

|           | 6.7 Conclusion                                                                   |

|           |                                                                                  |

|           | Bibliography                                                 | 131 |

|-----------|--------------------------------------------------------------|-----|

| Chapter 7 | Storage Coding for Wear Leveling in Flash Memories           | 133 |

| •         | 7.1 Introduction                                             | 133 |

|           | 7.2 Terms and Concepts                                       | 134 |

|           | 7.3 Coding for Minimizing Auxiliary Blocks                   | 137 |

|           | 7.3.1 Data Movement without Coding                           | 137 |

|           | 7.3.2 Storage Coding with One Auxiliary Block                | 139 |

|           | 7.4 Efficient Storage Coding over $GF(2)$                    | 140 |

|           | 7.5 Storage Coding with Minimized Number of Erasures         | 144 |

|           | 7.5.1 Optimal Solution with Canonical Labelling              | 144 |

|           | 7.6 Conclusion and Future Research                           | 149 |

|           | Bibliography                                                 | 149 |

| Chapter 8 | Error Characterization and Coding Schemes for Flash Memories | 151 |

| -         | 8.1 Introduction                                             | 151 |

|           | 8.2 Flash Memory Structure                                   | 152 |

|           | 8.3 Error Characterization of Flash Memories                 | 154 |

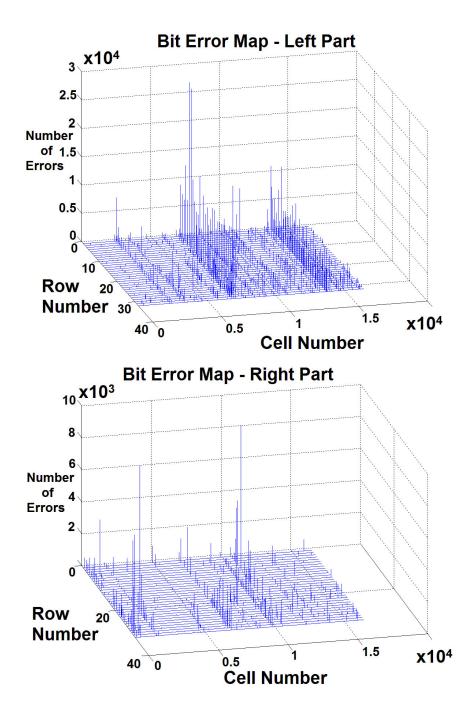

|           | 8.3.1 Page-level BER                                         | 154 |

|           | 8.3.2 Bit-level BER                                          | 156 |

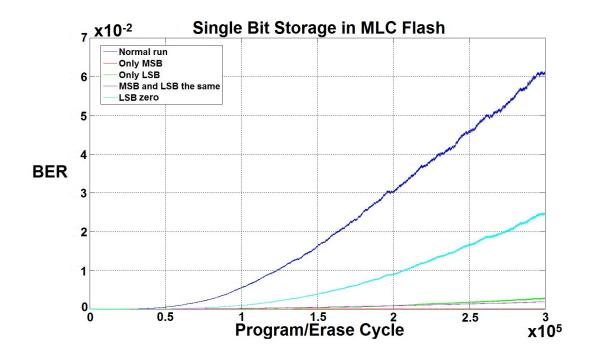

|           | 8.4 Partial Cell State Usage in MLC                          | 157 |

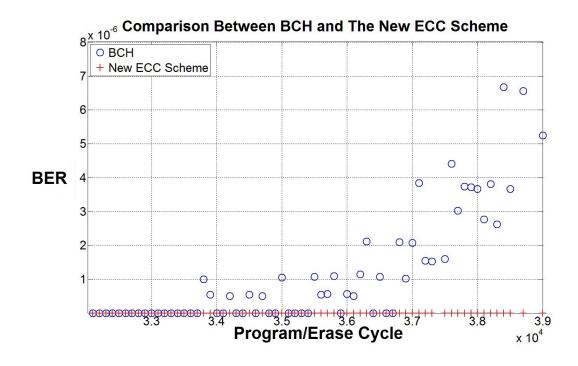

|           | 8.5 ECC for MLC Flash                                        | 159 |

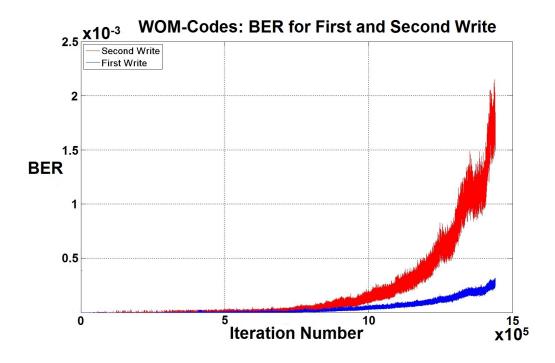

|           | 8.6 WOM-Codes for Flash Memories                             | 162 |

|           | 8.7 Summary and Conclusions                                  | 164 |

|           | Bibliography                                                 | 164 |

## LIST OF FIGURES

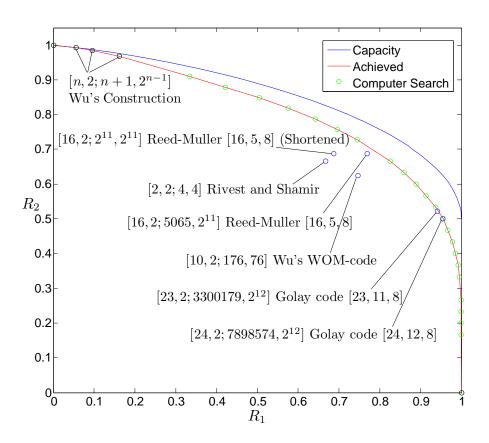

| Figure 3.1:                                                             | The capacity region and achieved rates of two-write WOM-codes                                                                                                                                               |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

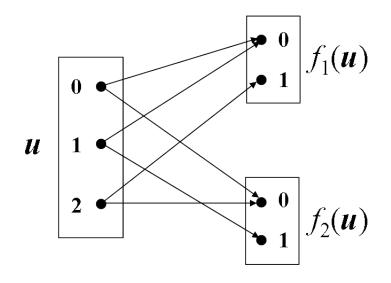

| Figure 3.2:                                                             | The Blackwell Channel.         46                                                                                                                                                                           |

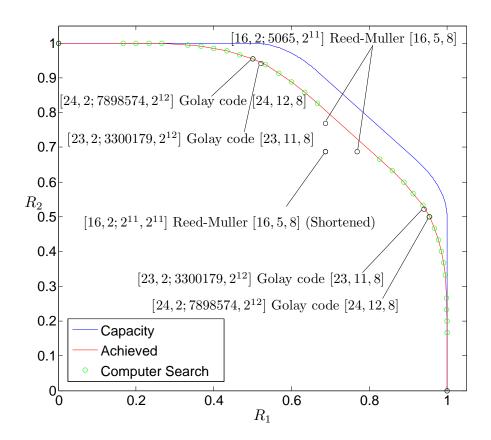

| Figure 3.3:                                                             | The capacity region and the achieved rates of the Blackwell channel 48                                                                                                                                      |

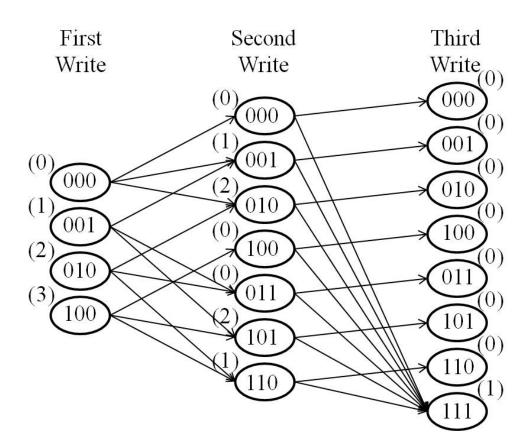

| Figure 3.4:                                                             | A [3,3;4,3,2] three-write WOM-code                                                                                                                                                                          |

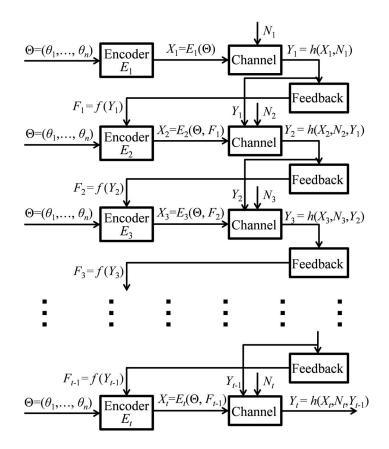

| Figure 6.1:                                                             | The information theoretic framework of the cell programming model 107                                                                                                                                       |

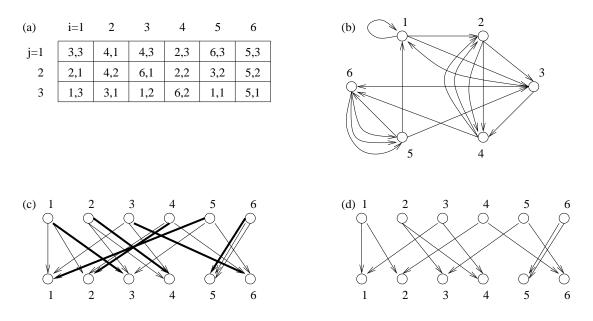

| Figure 7.1:                                                             | Data movement with $n = 6, m = 3. \dots 135$                                                                                                                                                                |

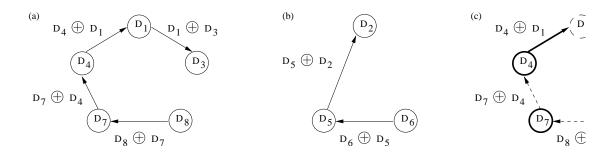

| Figure 7.2:                                                             | Example of Algorithm 7.4.1. $\delta_i$ denotes the data in page $p_i$ , for $i = 0, 1, \dots, 8.142$                                                                                                        |

| Figure 7.3:                                                             | The directed path $S$ of a semi-cycle, whose vertices and edges represent data. 143                                                                                                                         |

|                                                                         |                                                                                                                                                                                                             |

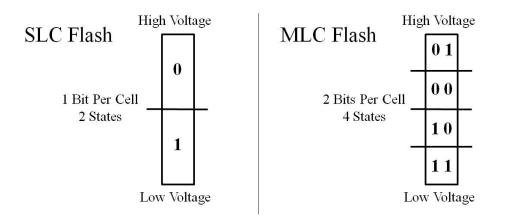

| Figure 8.1:                                                             | Mappings of cell levels to binary representations in SLC and MLC flash 153                                                                                                                                  |

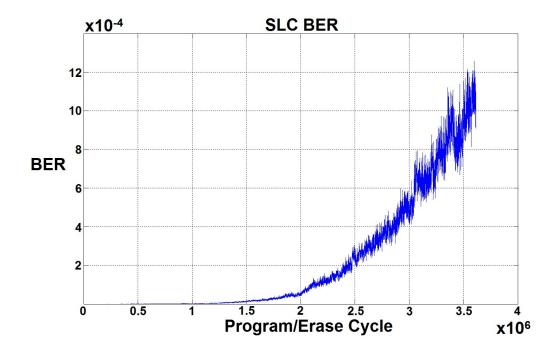

| Figure 8.1:<br>Figure 8.2:                                              | Mappings of cell levels to binary representations in SLC and MLC flash.153Raw BER for SLC flash.155                                                                                                         |

| e                                                                       |                                                                                                                                                                                                             |

| Figure 8.2:                                                             | Raw BER for SLC flash                                                                                                                                                                                       |

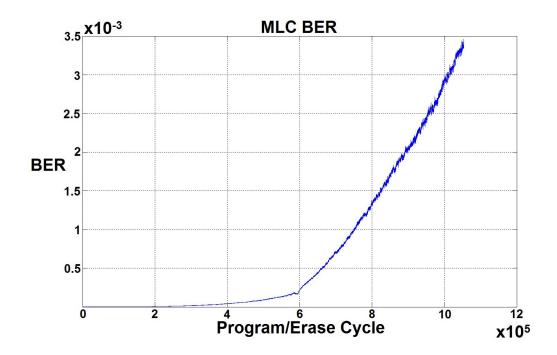

| Figure 8.2:<br>Figure 8.3:                                              | Raw BER for SLC flash.155Raw BER for MLC flash.155                                                                                                                                                          |

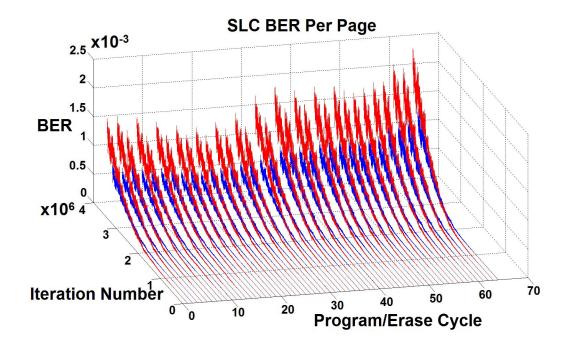

| Figure 8.2:<br>Figure 8.3:<br>Figure 8.4:                               | Raw BER for SLC flash.155Raw BER for MLC flash.155BER per Page for SLC Block.156                                                                                                                            |

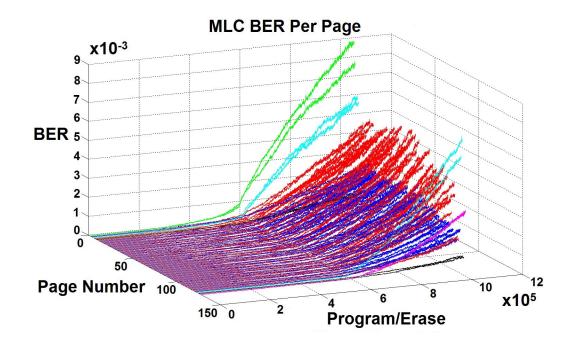

| Figure 8.2:<br>Figure 8.3:<br>Figure 8.4:<br>Figure 8.5:                | Raw BER for SLC flash.155Raw BER for MLC flash.155BER per Page for SLC Block.156BER per Page for MLC Block.157Bit Error Map for SLC Block.158Different Schemes for Storing a Single Bit in an MLC Block.159 |

| Figure 8.2:<br>Figure 8.3:<br>Figure 8.4:<br>Figure 8.5:<br>Figure 8.6: | Raw BER for SLC flash.155Raw BER for MLC flash.155BER per Page for SLC Block.156BER per Page for MLC Block.157Bit Error Map for SLC Block.158                                                               |

### LIST OF TABLES

| Table 3.1: | A WOM-code Example                                                         | 32  |

|------------|----------------------------------------------------------------------------|-----|

| Table 3.2: | Upper bounds on the sum-rate of fixed-rate WOM-codes                       | 36  |

| Table 3.3: | Prior best-known sum-rates for unrestricted-rate and fixed-rate WOM-codes. | 38  |

| Table 3.4: | Sum-rates of concatenated WOM-codes                                        | 57  |

| Table 3.5: | Sum-rates of fixed-rate WOM-codes                                          | 61  |

| Table 3.6: | Comparison with known unrestricted-rate WOM-codes                          | 62  |

| Table 3.7: | Comparison with known fixed-rate WOM-codes                                 | 63  |

| Table 8.1: | Typical layout of an SLC block                                             | 153 |

| Table 8.2: | Typical layout of an MLC block                                             | 153 |

#### ACKNOWLEDGEMENTS

Many people have contributed for my work in the past five years. Words are not enough in order to express my gratitude and thank each one of them.

First of all, I would like to express my deepest gratitude for my three advisors, Prof. Paul H. Siegel, Prof. Alexander Vardy, and Prof. Jack K. Wolf. Interacting with three of the best researchers in the world and enjoying their guidance as mentors was a tremendous benefit throughout my time at UCSD. I gained from their experience, enjoyed their patience, care, and encouragement along the way. Especially, I want to thank them for their belief in me right from the beginning. They helped me to push and reach the best out of myself.

I was very fortunate to interact with more researchers during the PhD program. This collaboration paved the way for a fruitful and very enjoyable research. I would like to thank Prof. Steven Swanson for the opportunity to collaborate with him and his lab and expanding my research into new and fascinating directions. I thank him also for serving in my committee and I thank Prof. Alon Orlitsky and Prof. Ilya Dumer for their time and effort in serving in my committee as well. I would like to thank my former M.Sc. advisor, Prof. Tuvi Etzion. His guidance in my research work and all other aspects of my life is extremely valuable and helped me a lot. I would like to thank Prof. Shuki Bruck and Prof. Andrew Jiang. Collaborating with them and their colleagues was a great honor for me. I want to thank them for establishing this new research area of coding for flash memories, which opened the path for my Phd research. I would like to thank all my other colleagues: Adrian Caulfield, Amy Chen, Joel Coburn, Lara Dolecek, Ryan Gabrys, Laura Grupp, Scott Kayser, Jing Ma, Hessam Mahdavifar, and Robert Mateescu. This collaboration had a tremendous contribution for my research and I am very grateful for that.

I would like to thank the staff of the CMRR and the ECE department staff: Arline Allen, Ray Descoteaux, Betty Manoulian, Gennie Miranda, Jan Neumann, Robert Rome, Shana Slebioda, and Iris Villanueva. You provided me with the perfect workplace and support for any administrative help I needed and much more than that.

I thank the current and previous STAR members: Sharon Aviran, Aman Bhatia, Brian Butler, Amir Hadi Djahanshahi, Federica Garin, Lynn Greiner, Junsheng Han, Toshio Ito, Aravind Iyengar, Seyhan Karakulak, Scott Kayser, Zsigmond Nagy, Minghai Qin, Marco Papaleo, Ori Shental, Mohammad Hossein Taghavi, Ido Tal, Saeed Sharifi Tehrani, Han Wang, Hao Wang, Zheng Wu, and Xiaojie Zhang, the non-volatile systems laboratory members: Adrian Caulfield, Joel Coburn, Laura Grupp, Hung-Wei Tseng, and Michael Wei, as well as current and past ECE students: Craig Armstrong, Steve Cho, Lorenzo Coviello, Shay Har-Noy, Hessam Mahdavifar, Mehmet Parlak, Mattew Pugh, Nevena Rakuljic, Rohit Ramanujam, and Sheu-Sheu Tan. I have benefited from the interaction I had with each one of them whether for research, organizing seminars, and any other activity on campus.

A special thank for all my friends in San Diego, Israel, and other parts of the world. Their love, belief in me, and serving as my extended family made me feel home and gave me the strength along this trip. It is impossible to go through all their names but I want to thank each one of them individually for this tremendous help and support.

I want to thank my loving and caring family: my brother Arik and his wife Revital, their great kids Opal and Orian, my sister Hadar and her Fiance Roey, my sister Maayan and her husband Benny, and my wonderful parents Baruch and Carmela. I am grateful for their love, endless support and help in any aspect of my life which made this trip so much easier for me.

Last and most importantly, I would like to cherish the memory of Jack Wolf and dedicate him this work. His contribution for my work cannot be described in just words. The guidance I was fortunate to receive from Jack for my research and more importantly for life will be remembered with me for ever.

This thesis was supported in part by the University of California Lab Fees Research Program, Award No. 09-LR-06-118620-SIEP, the Intel Ph.d. Fellowship program, the ISEF Foundation, and the Center for Magnetic Recording Research at the University of California, San Diego.

Chapter 2 is in part a reprint of the material in the papers: E. Yaakobi, P.H. Siegel, and J.K. Wolf, "Buffer Codes for Multi-Level Flash Memory," *IEEE International Symposium on Information Theory*, Poster session, Toronto, Canada, July 2008, and H. Mahdavifar, P.H. Siegel, A. Vardy, J.K. Wolf, and E.Yaakobi, "A Nearly Optimal Construction of Flash Codes," *Proc. IEEE International Symposium on Information Theory*, pp. 1239–1243, Seoul, Korea, June 2009. Chapter 3 is in part a reprint of the material in the papers: E. Yaakobi, S. Kayser, P.H. Siegel, A. Vardy, and J.K. Wolf, "Efficient Two-Write WOM-Codes," *Proc. IEEE Information Theory Workshop*, Dublin, Ireland, August-September 2010, and S. Kayser, E. Yaakobi, P.H. Siegel, A. Vardy, and J.K. Wolf, "Multiple-Write WOM-Codes," *48-th Annual Allerton Conference on Communication, Control and Computing*, Monticello, IL, September 2010. Chapter 4 is in part a reprint of the material in the paper: E. Yaakobi, P.H. Siegel, A. Vardy, and J.K. Wolf, "Multiple Error-Correcting WOM-Codes," *Proc. IEEE International Symposium on Information Theory*, pp. 1933–1937, Austin, Texas, June 2010. Chapter 5 is in part a reprint of the material

in the paper: E. Yaakobi, P.H. Siegel, A. Vardy, and J.K. Wolf, "On Codes that Correct Asymmetric Errors with Graded Multiple Distribution," to appear *IEEE International Symposium on Information Theory*, Saint Petersburg, Russia, July 2011. Chapter 6 is in part a reprint of the material in the paper: E. Yaakobi, A. Jiang, P.H. Siegel, A. Vardy, and J.K. Wolf, "On The Parallel Programming of Flash Memory Cells," *Proc. IEEE Information Theory Workshop*, Dublin, Ireland, August-September 2010. Chapter 7 is in part a reprint of the material in the paper: A. Jiang, R. Mateescu, E. Yaakobi, J. Bruck, P.H. Siegel, A. Vardy, and J.K. Wolf, "Storage Coding for Wear Leveling in Flash Memories," *IEEE Transactions on Information Theory*, vol. 56, no. 10, pp. 5290–5299, October 2010. Chapter 8 is in part a reprint of the material in the paper: E. Yaakobi, J. Ma, L. Grupp, P.H. Siegel, S.Swanson, and J.K. Wolf, "Error Characterization and Coding Schemes for Flash Memories," *Proc. Workshop on the Application of Communication Theory to Emerging Memory Technologies*, Miami, Florida, December 2010.

#### VITA

| 2005 | B.A. in Computer Science, Technion - Israel Institute of Technology                  |

|------|--------------------------------------------------------------------------------------|

| 2005 | B.A. in Mathematics, Technion - Israel Institute of Technology                       |

| 2007 | M.Sc. in Computer Science, Technion - Israel Institute of Technology                 |

| 2011 | Ph.D. in Electrical and Computer Engineering, University of California,<br>San Diego |

#### PUBLICATIONS

Eitan Yaakobi, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Multiple Error-Correcting WOM-Codes," submitted to *IEEE Transactions on Information Theory*, May 2011.

Minghai Qin, Eitan Yaakobi, and Paul H. Siegel "Time-Space Constrained Codes for Pahse-Change Memories," submitted to *Globecom Communications Conference*, Houston, Texas, December 2011.

Eitan Yaakobi, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "On Codes that Correct Asymmetric Errors with Graded Multiple Distribution," to appear *IEEE International Symposium on Information Theory*, Saint Petersburg, Russia, July 2011.

Eitan Yaakobi, Jing Ma, Laura Grupp, Paul H. Siegel, Steven Swanson, and Jack K. Wolf, "Error Characterization and Coding Schemes for Flash Memories," *Proc. Workshop on the Application of Communication Theory to Emerging Memory Technologies*, Miami, Florida, December 2010.

Anxiao (Andrew) Jiang, Robert Mateescu, Eitan Yaakobi, Jehoshua Bruck, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Storage Coding for Wear Leveling in Flash Memories," *IEEE Transactions on Information Theory*, vol. 56, no. 10, pp. 5290–5299, October 2010.

Scott Kayser, Eitan Yaakobi, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Multiple-Write WOM-Codes," *48-th Annual Allerton Conference on Communication, Control and Computing*, Monticello, IL, September 2010.

Tuvi Etzion, Alexander Vardy, and Eitan Yaakobi, "Dense Error-Correcting Codes in the Lee Metric," *Proc. IEEE Information Theory Workshop*, Dublin, Ireland, August-September 2010.

Eitan Yaakobi, Anxiao (Andrew) Jiang, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "On The Parallel Programming of Flash Memory Cells," *Proc. IEEE Information Theory Workshop*, Dublin, Ireland, August-September 2010.

Eitan Yaakobi, Scott Kayser, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Efficient Two-Write WOM-Codes," *Proc. IEEE Information Theory Workshop*, Dublin, Ireland, August-September 2010.

Eitan Yaakobi and Tuvi Etzion, "High Dimensional Error-Correcting Codes," *Proc. IEEE International Symposium on Information Theory*, pp. 1178–1182, Austin, Texas, June 2010. Eitan Yaakobi, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Multiple Error-Correcting WOM-Codes," *Proc. IEEE International Symposium on Information Theory*, pp. 1933–1937, Austin, Texas, June 2010.

Laura Grupp, Adrian Caulfield, Joel Coburn, Steven Swanson, Eitan Yaakobi, Paul Siegel, Jack Wolf, "Characterizing Flash Memory: Anomalies, Observations, and Applications," *MICRO 42*, New-York, New-York, December 2009.

Anxiao (Andrew) Jiang, Robert Mateescu, Eitan Yaakobi, Jehoshua Bruck, Paul H. Siegel, Alexander Vardy, and Jack K. Wolf, "Storage Coding for Wear Leveling in Flash Memories," *Proc. IEEE International Symposium on Information Theory*, pp. 1234–1238, Seoul, Korea, June 2009.

Hessam Mahdavifar, Paul H. Siegel, Alexander Vardy, Jack K. Wolf, and Eitan Yaakobi, "A Nearly Optimal Construction of Flash Codes," *Proc. IEEE International Symposium on Information Theory*, pp. 1239–1243, Seoul, Korea, June 2009.

Tuvi Etzion and Eitan Yaakobi, "Error-Correction of Multidimensional Bursts", *IEEE Transactions on Information Theory*, vol. 55, no. 3, pp. 961–976, March 2009.

Eitan Yaakobi, Alexander Vardy, Paul H. Siegel, and Jack K. Wolf, "Multidimensional Flash Codes," *Proc. 46-th Annual Allerton Conference on Communication, Control and Computing*, Monticello, IL, September 2008.

Eitan Yaakobi, Paul H. Siegel, and Jack K. Wolf, "Buffer Codes for Multi-Level Flash Memory," *IEEE International Symposium on Information Theory*, Poster session, Toronto, Canada, July 2008.

Eitan Yaakobi and Tuvi Etzion, "Error Correction of Multidimensional Bursts," *Proc. IEEE International Symposium on Information Theory*, pp. 1178–1182, Nice, France, June 2007.

#### ABSTRACT OF THE DISSERTATION

#### **Coding for Flash Memories**

by

Eitan Yaakobi

## Doctor of Philosophy in Electrical Engineering (Communication Theory and Systems)

University of California, San Diego, 2011

Professor Paul H. Siegel, Co-Chair Professor Alexander Vardy, Co-Chair

Flash memories are, by far, the most important type of non-volatile memory in use today. They are employed widely in mobile, embedded, and mass-storage applications, and the growth in this sector continues at a staggering pace. Moreover, since flash memories do not suffer from the mechanical limitations of magnetic disk drives, solid-state drives have the potential to upstage the magnetic recording industry in the foreseeable future. The research goal of this dissertation is the discovery of new coding theory methods that supports efficient design of flash memories.

Flash memory is comprised of blocks of cells, wherein each cell can take on  $q \ge 2$  levels. While increasing the cell level is easy, reducing its level can be accomplished only by erasing an entire block. Such block erasures are not only time-consuming, but also degrade the

memory lifetime.

Our main contribution in this research is the design of rewriting codes that maximize the number of times that information can be written prior to incurring a block erasure. Examples of such coding schemes are *flash/floating codes* and *buffer codes*, introduced by Jiang and Bruck et al. in 2007, and *WOM-codes* that were presented by Rivest and Shamir almost three decades ago. The overall goal in these codes is to maximize the amount of information written to a fixed number of cells in a fixed number of writes.

Furthermore, the design of error-correcting codes in flash memories is extensively studied. It is shown how to modify WOM-codes to support an error-correction capability. Motivated by the asymmetry of the error behavior of flash memories and the work by Cassuto et al., a coding scheme to correct asymmetric errors is presented. An extensive empirical database of errors was used to develop a comprehensive understanding of the error behavior as well as to design specific error-correcting codes for flash memories.

This research on flash memories is expanded to other directions. *Wear leveling* techniques are widely used in flash memories in order to reduce and balance block erasures. It is shown that coding schemes to be used in these techniques can significantly reduce the number block erasures incurred during data movement. Also, the design of parallel cell programming algorithms is studied for the specific constraints and behavior of flash cells.

# Chapter 1

# Introduction

# 1.1 Background

Coding theory was effectively born in 1948, with the publication of Shannon's celebrated classic paper [3]. It was recognized early on that error-correction coding is a powerful system design technique that can fundamentally change the trade-offs in a communication system. Indeed, in order to improve performance, error-control coding has been widely used by the communications and data storage industries. In particular, the research in this dissertation focuses on the relevant problems arising from flash memory systems.

Any communication channel can be considered as a transmission of information either from one place to another — space domain, or from one time to another — time domain. In both types of communication channels, the information cannot be perfectly transmitted and a noisy version of it is received. The noise can be caused by various reasons. If the information is transmitted in the space domain then any natural source such as weather conditions, radiation, thermal effects, etc. can cause noise in the channel. In the time domain, the information is stored on a memory device and any physical defect or degradation of the memory reliability can damage the stored data. For example, a scratch on a CD will corrupt the bits that are stored in that area on the CD. Both channels use the same types of signal processing systems and error-control codes in order to transmit the information reliably.

Data storage devices rely upon error detection and correction (EDAC) codes to ensure highly reliable information retrieval. Optical storage devices, such as CD- and DVD-based recorders, allocate significant overhead for the redundancy introduced by the encoding of data into codewords. High-performance hard disk drives also devote overhead for high-rate EDAC codes that can correct multiple erroneous symbols within a codeword. The powerful codes used in these storage devices are the culmination of decades of research and development, and efforts to design more powerful and efficient EDAC coding algorithms are ongoing.

Non-volatile data storage devices, particularly those based upon flash memory technologies, are revolutionizing the way we access and manipulate information. They have many attractive features compared to magnetic hard disk drives, including their compactness, shock resistance, lack of moving parts, and lower data-access time. Flash memory is now the storage medium of choice in portable consumer electronic applications, and high performance solidstate drives (SSDs) are also being introduced into mobile computing, enterprise storage, data warehousing, and data-intensive computing systems. Accordingly, there is a surge in interest in the refinement, development, and expanded commercial use of these non-volatile memory technologies. On the other hand, these technologies present major challenges in the areas of device reliability, endurance, and energy efficiency. These challenges can be overcome, in part, through innovative coding and data handling techniques.

Flash memory chips may use single-level cell (SLC) technology, where each cell can store one binary digit, or multi-level cell (MLC) technology, where each cell can store multiple binary digits. First generation flash storage devices have used only low-redundancy EDAC codes that offer minimal error correction and detection capabilities, such as single-bit error-correcting Hamming codes and error-detecting cyclic redundancy check (CRC) codes. The demand for increased storage capacity, coupled with the introduction of MLC flash technology, has created the need for more powerful ECC methods, such as BCH codes and Low-Density Parity-Check (LDPC) codes.

### **1.2 Flash Memory Basics**

A flash memory consists of an array of floating-gate cells, organized into blocks (a typical block comprises roughly  $2^{20}$  cells). Hot-electron injection is used to inject electrons into a cell, where they become trapped. The Fowler-Nordheim tunneling mechanism (field emission) can be used to remove electrons from an entire block of cells, thereby discharging them. The level of a cell is a function of the amount of charge (electrons) trapped within it. Historically, flash cells have been designed to store only two values (one bit); however, multilevel flash cells are actively being developed and are already in use in many devices [3]. In multilevel flash cells, voltage is quantized to q discrete threshold values. The parameter q can range from q = 2 (the conventional two-state case) up to q = 16.

The most conspicuous property of flash storage is its inherent asymmetry between cell programming (charge placement) and cell erasing (charge removal). While adding charge to a single cell is a fast and simple operation, removing charge from a cell is very difficult. In fact, flash memories do not allow a single cell to be erased; rather, only entire blocks (comprising up to  $2^{20}$  or more cells) can be erased. Thus, a single cell erase operation requires the cumbersome process of copying an entire block to a temporary location, erasing it, and then re-programming all the cells except one. Moreover, since over-programming (raising the charge of a cell above its intended level) can only be corrected by a block erasure, in practice, a conservative procedure is used for programming a cell. Charge is injected into the cell over numerous rounds; after every round, the charge level is measured and the next-round injection is configured, so that the charge gradually approaches its desired level. All this is extremely costly in time and energy. Such block can tolerate about  $10^4 - 10^5$  or fewer erasures.

# **1.3** Codes for Flash Memories

As flash memory has become ubiquitous in recent years, finding solutions for its limited lifetime and asymmetric programming behavior has become an important challenge. Examples of such coding solutions were given in [4,8,9,11,12,17,31]. The goal in these codes is to rewrite the information into flash memories while preserving the constraint that on each write cells can only increase their value. In fact, the model and behavior of a flash memory is very similar to the well-studied write-once memory (WOM) model. Inspired by memories such as punch cards and optical disks, Rivest and Shamir first introduced WOM-codes in 1982. Similarly to flash, in these memories, the media can be represented as a collection of write-once bit locations, each of which initially represents a bit value 0 that be irreversibly overwritten with a bit value 1. Constructions of WOM-codes were given for example in [2, 5, 5, 13, 17, 18] and were recently improved in [11, 19]. Error correcting WOM-codes were also studied in [20, 21] and more recent constructions appeared in [29].

Slightly different and yet very related are the rank modulation codes [12, 13]. In rank modulation, the information is not stored according to the exact cell levels but rather by the cell permutation which is derived from these levels. Other works explore efficient data movement in flash memories that minimize the number of block erasures as well as extra space [13, 17] and fast cell programming algorithms of flash memories [7, 8, 27].

## **1.4 Dissertation Overview**

After understanding the model and constraints in flash memory we can overview the problems which this dissertation solves using coding theory tools.

In Chapter 2, we present rewriting codes for flash memories. The first part of this chapter focuses on the *flash codes* problem and a nearly optimal construction of such codes is presented. In the second part, *buffer codes* are studied. An upper bound and a construction of such codes are presented which improve upon the related previous work.

WOM-codes are studied in Chapter 3. We first show how to construct two-write WOMcodes that improve upon the best previously known. These codes are also used to construct codes for the Blackwell channel. Then, we show how to extend these codes to an arbitrary number of writes, giving the best known WOM-codes for  $3 \le t \le 10$  writes.

The study of WOM-codes is continued in Chapter 4. Here, error-correcting WOM-codes are constructed which improve upon the previously known single-error-correcting WOM-codes. Extensions for double- and triple-error-correcting WOM-codes are given as well. For triple-error-correction, we introduce the notion of strong cyclic error-correcting codes. Finally, we show how to design WOM-codes for the correction of any arbitrary number of errors.

Chapter 5 describes a new error model for multi-level flash memories based upon a graded distribution of asymmetric errors of limited magnitudes. We show how to use a previous construction by Cassuto et al. [5] of asymmetric limited-magnitude error-correcting codes in order to develop a family of codes that correct asymmetric errors in the new model.

Chapter 6 presents algorithms for programming flash memory cells. First, a model which describes the programming of flash memory cells is given. According to this model, algorithms to program the cells in parallel are given. Modifications to programming with noise and inter-cell interference are given as well. Then, we show an algorithm that is used to get information about the characteristics of the cells and using this information we show how to program a cell with feedback.

Chapter 7 studies how to efficiently move data in flash memories. We show how to utilize coding schemes in order to construct codes that reduce the number of auxiliary blocks used in the algorithm as well as the number of block erasures.

Finally, Chapter 8 uses empirical data to characterize the flash error behavior. This information will be useful in the design of new error-correcting codes for flash memories. Furthermore, we explore in this chapter the implementation of WOM-codes in flash memories.

# **Bibliography**

- [1] P. Cappelletti, C. Golla, P. Olivo and E. Zanoni (*Ed.*), *Flash memories*, Kluwer Academic Publishers, 1st Edition, 1999.

- [2] Y. Cassuto, M. Schwartz, V. Bohossian, and J. Bruck, "Codes for asymmetric limitedmagnitude errors with application to multi-level flash memories," *IEEE Trans. Inform. Theory*, vol. 56, no. 4, pp. 1582–1595, April 2010.

- [3] C.E. Shannon, "A mathematical theory of communication," *Bell Systems Tech. J.*, vol. 27, pp. 379–423 and pp. 623–656, 1948.

- [4] F. Chierichetti, H. Finucane, Z. Liu, and M. Mitzenmacher, "Designing floating codes for expected performance," to appear in *IEEE Trans. Inform. Theory*.

- [5] G.D. Cohen, P. Godlewski, and F. Merkx, "Linear binary code for write-once memories," *IEEE Trans. Inform. Theory*, vol. 32, no. 5, pp. 697–700, October 1986.

- [6] T. Etzion, A. Vardy, and E. Yaakobi, "Dense error-correcting codes in the Lee metric," Proc. IEEE Inform. Theory Workshop, Dublin, Ireland, August-September 2010.

- [7] T. Etzion and E. Yaakobi, "Error-correction of multidimensional bursts", *IEEE Trans. In-form. Theory*, vol. 55, no. 3, pp. 961–976, March 2009.

- [8] P. Godlewski, "WOM-codes construits à partir des codes de Hamming," Discrete Math., no. 65, no. 3, pp. 237–243, July 1987.

- [9] L. Grupp, A. Caulfield, J. Coburn, S. Swanson, E. Yaakobi, P.H. Siegel, and J.K. Wolf, "Characterizing flash memory: anomalies, observations, and applications," *MICRO-42*, pp. 24–33, December 2009.

- [10] A. Jiang, V. Bohossian, and J. Bruck, "Floating codes for joint information storage in write asymmetric memories," *Proc. IEEE Int. Symp. Inform. Theory* pp. 1166–1170, Nice, France, June 2007.

- [11] A. Jiang and J. Bruck, "Joint coding for flash memory storage," Proc. IEEE Int. Symp. Inform. Theory, pp. 1741–1745, Toronto, Canada, July 2008.

- [12] A. Jiang and J. Bruck, "On the capacity of flash memories," *Proc. Int. Symp. on Inform. Theory and Its Applications*, pp. 94–99, Auckland, New Zealand, 2008.

- [13] A. Jiang, M. Langberg, R. Mateescu, and J. Bruck, "Data movement and aggregation in flash memories," *Proc. IEEE Int. Symp. Inform. Theory*, pp. 1918–1922, Austin, Texas, June 2010.

- [14] A. Jiang, M. Landberg, M. Schwartz, and J. Bruck, "Universal rewriting in constrained memories," *Proc. IEEE Int. Symp. Inform. Theory*, pp. 1219–1223, Seoul, Korea, July 2009.

- [15] A. Jiang and H. Li, "Optimized cell programming for flash memories," Proc. IEEE Pacific Rim Conference on Communications, Computers and Signal Processing (PACRIM), pp. 914–919, Victoria, BC, August 2009.

- [16] A. Jiang, R. Mateescu, M. Schwartz, and J. Bruck, "Rank modulation for flash memories," *IEEE Trans. Inform. Theory*, vol. 55, no. 6, pp. 2659–2673, October 2010.

- [17] A. Jiang, R. Mateescu, E. Yaakobi, J. Bruck, P.H. Siegel, A. Vardy, and J.K. Wolf, "Storage coding for wear leveling in flash memories," *IEEE Transactions on Information Theory*, vol. 56, no. 10, pp. 5290–5299, October 2010.

- [18] A. Jiang, M. Schwartz, and J. Bruck, "Correcting charge-constrained errors in the rank modulation scheme," *IEEE Trans. Inform. Theory*, vol. 56, no. 5, pp. 2112–2120, May 2010.

- [19] S. Kayser, E. Yaakobi, P.H. Siegel, A. Vardy, and J.K. Wolf, "Multiple-write WOM-codes," *Proc. 48-th Annual Allerton Conference on Communication, Control and Computing*, Monticello, IL, September 2010.

- [20] H. Mahdavifar, P.H. Siegel, A. Vardy, J.K. Wolf, and E. Yaakobi, "A nearly optimal construction of flash codes," *Proc. IEEE Int. Symp. Inform. Theory*, pp. 1239–1243, Seoul, Korea, July 2009.

- [21] F. Merkx, "Womcodes constructed with projective geometries," *Traitement du signal*, vol. 1, no. 2-2, pp. 227–231, 1984.

- [22] R.L. Rivest and A. Shamir, "How to reuse a write-once memory," *Inform. and Contr.*, vol. 55, no. 1–3, pp. 1–19, December 1982.

- [23] Y. Wu, "Low complexity codes for writing write-once memory twice," Proc. IEEE Int. Symp. Inform. Theory, pp. 1928–1932, Austin, Texas, June 2010.

- [24] Y. Wu and A. Jiang, "Position modulation code for rewriting write-once memories," acceptted by *IEEE Trans. Inform. Theory*, October 2010.

- [25] E. Yaakobi and T. Etzion, "Error correction of multidimensional bursts," Proc. IEEE Int. Symp. Inform. Theory, pp. 1381–1385, Nice, France, June 2007.

- [26] E. Yaakobi and T. Etzion, "High dimensional error-correcting codes," Proc. IEEE Int. Symp. Inform. Theory, pp. 1178–1182, Austin, Texas, June 2010.

- [27] E. Yaakobi, A. Jiang, P.H. Siegel, A. Vardy, and J.K. Wolf, "On the parallel programming of flash memory cells," *Proc. IEEE Inform. Theory Workshop*, Dublin, Ireland, August-September 2010.

- [28] E. Yaakobi, S. Kayser, P.H. Siegel, A. Vardy, and J.K. Wolf, "Efficient two-write WOMcodes," Proc. IEEE Inform. Theory Workshop, Dublin, Ireland, August-September 2010.

- [29] E. Yaakobi, J. Ma, L. Grupp, P.H. Siegel, S. Swanson, and J.K. Wolf, "Error characterization and coding schemes for flash memories," *Proc. Workshop on the Application of Communication Theory to Emerging Memory Technologies*, Miami, Florida, December 2010.

- [30] E. Yaakobi, P.H. Siegel, A. Vardy, and J.K. Wolf, "Multiple error-correcting WOM-codes," *Proc. IEEE Int. Symp. Inform. Theory*, pp. 1933–1937, Austin, Texas, June 2010.

- [31] E. Yaakobi, P.H. Siegel, and J.K. Wolf, "Buffer codes for multi-level flash memory," *Proc. IEEE Int. Symp. Inform. Theory*, Poster session, Toronto, Canada, July 2008.

- [32] E. Yaakobi, A. Vardy, P.H. Siegel, and J.K. Wolf, "Multidimensional flash codes," *Proc.* 46-th Allerton Conference on Communication, Control and Computing, Monticello, IL, September 2008.

- [33] G. Zémor, "Problèmes combinatoires liés à l'écriture sur des mémoires," Ph.D. Dissertation, ENST, Paris, France, November 1989.

- [34] G. Zémor and G.D. Cohen, "Error-correcting WOM-codes," *IEEE Trans. Inform. Theory*, vol. 37, no. 3, pp. 730–734, May 1991.

# Chapter 2

# **Rewriting Codes for Flash Memories**

# 2.1 Introduction

In Chapter 1, we described how flash memories work and in particular the constraints of such memories. The most conspicuous property of flash-storage technology is its inherent asymmetry between cell programming (charge placement) and cell erasing (charge removal). In fact, flash technology does not allow a single cell to be erased — rather, only entire blocks can be erased. This constraint makes it important to design coding schemes that maximize the number of times information stored in a flash memory can be written (and re-written) prior to incurring a block erasure.

Such coding schemes — known as *floating codes* or *flash codes* and *buffer codes* — were first introduced in [1,7,8] a few years ago. Since then, several more papers on this subject have appeared in the literature [5,9,9,11,12,17]. It should be pointed out that flash codes and buffer codes can be regarded as examples of memories with constrained source, which were described in [11]. Yet another example of such codes are the write-once memory (WOM) codes [2,3,5], that have been studied since the early 1980s. In fact, flash codes may be regarded as a generalization of WOM-codes. Slightly different and yet very related are the rank modulation codes [12, 13]. In rank modulation, the information is not stored according to the exact cell levels but rather by the cell permutation which is derived from these levels.

### 2.2 Preliminaries and Flash Codes Definition

Let us first give a precise definition of flash codes that were introduced less formally in the previous section. We use  $\{0,1\}^k$  to denote the set of binary vectors of length k, and refer to the elements of this set as *information vectors*. The set of possible levels for each cell is denoted by  $\mathcal{A}_q = \{0, 1, \ldots, q-1\}$  and thought of as a subset of the integers. The  $q^n$ vectors of length n over  $\mathcal{A}_q$  are called *cell-state vectors*. With this notation, any flash code  $\mathbb{C}$ can be specified in terms of two functions: an encoding map  $\mathcal{E}$  and a decoding map  $\mathcal{D}$ . The *decoding map*  $\mathcal{D} : \mathcal{A}_q^n \to \{0,1\}^k$  indicates for each cell-state vector  $\mathbf{x} \in \mathcal{A}_q^n$  the corresponding information vector. In turn, the *encoding map*  $\mathcal{E} : \{0,1,\ldots,k-1\} \times \mathcal{A}_q^n \to \mathcal{A}_q^n \cup \{E\}$  assigns to every index i and cell-state vector  $\mathbf{x} \in \mathcal{A}_q^n$ , another cell-state vector  $\mathbf{y} = \mathcal{E}(i, \mathbf{x})$  such that  $y_j \ge x_j$  for all j and  $\mathcal{D}(\mathbf{y})$  differs from  $\mathcal{D}(\mathbf{x})$  only in the i-th position. If no such  $\mathbf{y} \in \mathcal{A}_q^n$  exists, then  $\mathcal{E}(i, \mathbf{x}) = E$  indicating that block erasure is required. To bootstrap the encoding process, we assume that the initial state of the n memory cells is  $(0, 0, \ldots, 0)$ . Henceforth, iteratively applying the encoding map, we can determine how *any sequence* of transitions  $0 \to 1$  or  $1 \to 0$ in the k information bits maps into a sequence of cell-state vectors, eventually terminated by the block erasure. This leads to the following definition.

**Definition 2.2.1.** An  $(n, k)_q$  flash code  $\mathbb{C}(\mathcal{D}, \mathcal{E})$  guarantees t writes if for all sequences of up to t transitions  $0 \to 1$  or  $1 \to 0$  in the k information bits, the encoding map  $\mathcal{E}$  does not produce the block erasure symbol E. If so, we say that  $\mathbb{C}$  is an  $(n, k, t)_q$  code, and define the *deficiency* of  $\mathbb{C}$  as  $\delta(\mathbb{C}) = n(q-1) - t$ .

In addition to this definition, we will also use the following terminology. Given a vector  $x = (x_1, x_2, ..., x_m)$  over  $\mathcal{A}_q$ , we define its *weight* as  $wt(x) = x_1 + x_1 + \cdots + x_m$  (where the addition is over the integers), and its *parity* as  $wt(x) \mod 2$ .

# 2.3 Two Bits Flash Codes

In this section, we present our first construction of flash codes. In [8], a construction for storing two bits is presented and is shown to be optimal. The construction given here will be proved to be optimal as well and we believe that it is more intuitive.

In this construction, the leftmost and rightmost cells correspond to the first and second bit, respectively. When rewriting, if the first or second bit changes its value then the leftmost or rightmost cell of level less than q - 1 is increased by one level, respectively. In general, the cell-state vector has the following form:

$$(q-1,\ldots,q-1,x_i,0,\ldots,0,x_j,q-1,\ldots,q-1)$$

where  $0 < x_i, x_j \le q - 1$ . This principle repeats itself until only one cell is left with level less than q - 1. Then, this cell is used to store two bits according to its residue modulo 4. If this residue is 0, 1, 2, 3 then the value of the bits is  $(v_1, v_2) = (0, 0), (1, 0), (0, 1), (1, 1),$ respectively. The construction is presented for odd values of q and we will discuss later how to modify it for even values as well. In what follows, these maps are described algorithmically, using (C-like) pseudo-code notation.

**Decoding map**  $\mathcal{D}_2$ : The input to this map is a cell-state vector  $\mathbf{x} = (x_1, x_2, \dots, x_n)$ . The output is the corresponding two-bit information vector  $(v_1, v_2)$ .

```

i_{1} = \texttt{find\_left\_cell}(y_{1}, y_{2}, \dots, y_{n});

i_{2} = \texttt{find\_right\_cell}(y_{1}, y_{2}, \dots, y_{n});

\texttt{if}(i_{2} == 0) \quad // \text{ all cells are full}

\{v_{1} = q - 1 \pmod{2}; v_{2} = \lfloor ((q - 1) \pmod{4}) / 2 \rfloor; \}

\texttt{if}(i_{1} == i_{2}) \quad // \text{ there is only one non-full cell}

\{v_{1} = y_{i_{1}} \pmod{2}; v_{2} = \lfloor (y_{i_{1}} \pmod{4}) / 2 \rfloor; \}

\texttt{if}(i_{1} != i_{2}) \quad // \text{ there are at least two non-full cells}

\{v_{1} = y_{i_{1}} \pmod{2}; v_{2} = y_{i_{2}} \pmod{2}; \}

```

**Encoding map**  $\mathcal{E}_2$ : The input to this map is a cell-state vector  $\mathbf{x} = (x_1, x_2, \dots, x_n)$ , and an index  $j \in \{1, 2\}$  of the bit that has changed. Its output is either a new cell-state vector  $\mathbf{y} = (y_1, y_2, \dots, y_n)$  or the erasure symbol E.

```

(y_1, y_2, \dots, y_n) = (x_1, x_2, \dots, x_n); \\ i_1 = find\_left\_cell(y_1, y_2, \dots, y_n); \\ i_2 = find\_right\_cell(y_1, y_2, \dots, y_n); \\ if(i_2 == 0) return E; \\ if(i_1 == i_2) // there is only one non-full cell \\ \{ if(j == 2) a = 2; \\ else a = j + 2 \cdot (y_{i_1} (mod 2)); \\ if(y_{i_1} + a > q - 1) return E; \\ else \{ y_{i_1} = y_{i_1} + a; return; \} \} \\ y_{i_j} = y_{i_j} + 1; \\ if((i_2 - i_1 == 1) \land (y_{i_j} == q - 1)) \\ \{ v_{i_j} = 0; v_{i_{3-j}} = y_{i_{3-j}} (mod 2); \\ a = 2 \cdot v_2 + v_1 - (y_{i_{3-j}} (mod 4)); \\ if(a < 0) y_{i_{3-j}} = y_{i_{3-j}} + a; \}

```

The function **find\_left\_cell**  $(y_1, y_2, ..., y_n)$  finds the leftmost cell of level less than q - 1 and if there is not such a cell then it returns n + 1. Similarly, the function **find\_right\_cell**  $(y_1, y_2, ..., y_n)$  finds the rightmost cell of level less than q - 1 and if there is not such a cell then it returns 0. The notation  $y_{i_j}$  stands for the variable  $y_{i_1}$  in case j = 1, and  $y_{i_2}$  if j = 2. The same rule applies for  $y_{i_{3-j}}$ . The symbol  $\wedge$  stands for the logical operator "and". The next theorem proves the number of writes this construction guarantees.

**Theorem 2.3.1.** If there are *n q*-level cells and *q* is odd, then the code  $\mathbb{C}(\mathcal{D}_2, \mathcal{E}_2)$  guarantees at least  $t = (n-1)(q-1) + \left|\frac{q-1}{2}\right|$  writes before erasing.

**Proof.** As long as there is more than one cell of level less than q - 1, the weight of the cell-state vector increases by one on each write. This may change only after at least (n-1)(q-1) writes. Assume that there is only one cell of level less than q - 1 after s = (n-1)(q-1) + k writes, where  $k \ge 0$ , and call it the *i*-th cell. Starting this write, the different residues modulo 4 of the *i*-th cell correspond to the four possible two-bit information vector  $(v_1, v_2)$ . Therefore, on the *s*-th write, we also need to increase the level of the *i*-th cell so it will correspond to the correct information vector on this write. For all succeeding writes, if the second bit changes then the *i*-th cell increases by two levels. If the first bit changes from 0 to 1 then the *i*-th cell increases by one level and otherwise by three levels. Therefore, if there are *m* more writes and  $v_1 = 0$  then the *i*-th cell increases by at most 2m levels, and if there are *m* more writes and  $v_1 = 1$  then the *i*-th cell increases by at most 2m + 1 levels.

Let us consider all possible values of k and the information vector  $(v_1, v_2)$  on the s-th write in order to calculate the number of guaranteed writes before erasing. Note that on the s-th write  $(v_1 + v_2) \equiv s \pmod{2}$ . Furthermore, since q is odd, the value of the bit that is written changes from one to zero because it reaches level q - 1, and thus the other bit has value  $k \pmod{2}$ .

Assume k(mod 4) = 0, then (v<sub>1</sub>, v<sub>2</sub>) = (0,0) and the level of the *i*-th cell does not increase on the *s*-th write. Since v<sub>1</sub> = 0, after *m* writes the cell increases by at most 2*m* levels. Hence, there are at least <sup>q-1-k</sup>/<sub>2</sub> more writes and the total number of writes is at least

$$(n-1)(q-1) + k + \frac{q-1-k}{2} \ge (n-1)(q-1) + \frac{q-1}{2}$$

2. Assume  $k \pmod{4} = 1$ , then  $(v_1, v_2) = (1, 0)$  or  $(v_1, v_2) = (0, 1)$ . If  $(v_1, v_2) = (1, 0)$ then on the *s*-th write the *i*-th cell does not increase its level and after *m* writes its level increases by at most 2m + 1 levels. If  $(v_1, v_2) = (0, 1)$  then the *i*-th cell increases by one level and after *m* writes its level increases by at most 2m more levels. Hence, in both cases there are at least  $\frac{q-2-k}{2}$  more writes. Together we get that the total number of writes is at least

$$(n-1)(q-1) + k + \frac{q-2-k}{2} \ge (n-1)(q-1) + \frac{q-1}{2}.$$

3. Assume  $k \pmod{4} = 2$ , then  $(v_1, v_2) = (0, 0)$  and the *i*-th cell increases by two levels on *s*-th write. Since  $v_1 = 0$  after *m* more writes the cell increases by at most 2m levels and hence there are at least  $\lfloor (q - 1 - (k + 2))/2 \rfloor$  more writes, where  $k \ge 2$ . There total number of write is at least

$$(n-1)(q-1) + k + \frac{q-3-k}{2} \ge (n-1)(q-1) + \frac{q-1}{2}.$$

4. Assume k(mod 4) = 3, then (v<sub>1</sub>, v<sub>2</sub>) = (1,0) or (v<sub>1</sub>, v<sub>2</sub>) = (0,1). If (v<sub>1</sub>, v<sub>2</sub>) = (1,0) then on the s-th write the i-th cell increases by two levels and after m more writes it increases by at most 2m + 1 levels. If (v<sub>1</sub>, v<sub>2</sub>) = (0,1) then the i-th cell increases by three levels and after m more writes it increases by at most 2m more levels. Hence there are at least <sup>q-4-k</sup>/<sub>2</sub> more writes, where k ≥ 3. Thus, the total number of writes is at least

$$(n-1)(q-1) + k + \frac{q-4-k}{2} \ge (n-1)(q-1) + \frac{q-1}{2}.$$

In any case, the guaranteed number of writes is  $(n-1)(q-1) + \lfloor \frac{q-1}{2} \rfloor$ .

For even values of q, the construction is very similar. As long as there is more than one cell of level less q - 1 we follow the same rules for the encoding. For the decoding, since q - 1 is no longer even, the value of  $v_1$  is the parity of the cells  $1, \ldots, i_1$ , where  $i_1$  is the leftmost cell of value less q - 1. The value of  $v_2$  is the parity of the cells  $i_2, i_2 + 1, \ldots, n$ , where  $i_2$  is the rightmost cell of value less q - 1. If there is only one left cell, then it represents a value of two bits as before according to its residue modulo 4. If the the index of the last available cell is i then

$$v_1 = (i - 1 + y_i) \pmod{2},$$

$v_2 = ((n - i) + \lfloor (y_i \pmod{4}) / 2 \rfloor) \pmod{2}.$

Also, the last cell does not reach level q - 1 so is always possible to distinguish what the last cell is. We omit the tedious details as the proof is similar to the case where q is odd.

### 2.4 Index-less Indexed Flash Codes

What is the smallest possible write deficiency  $\delta_q(n,k)$  for an  $(n,k,t)_q$  flash code, and how does it behave asymptotically as the code parameters k and n get large? The best-known lower bound, due to Jiang, Bohossian, and Bruck [8], asserts that

$$\delta_q(n,k) \ge \frac{1}{2}(q-1)\min\{n,k-1\}.$$

(2.1)

How closely can this bound be approached by code constructions? It appears that the answer to this question depends on the relationship between *k* and *n*. In this section, we are concerned mainly with the case where both *k* and *n* are large, and *n* is much larger than *k* (in particular,  $n \ge k^2$ ). In Section 2.6, we will consider the case k/n = const. At the other end of the spectrum, the case k > n has been studied in [11].

The first construction of flash codes for large k are the so-called *indexed flash codes*, due to Jiang and Bruck [9, 9]. In this construction, the k information bits are partitioned into  $m_1 = k/k'$  subsets of k' bits each (with  $k' \leq 6$ ) while the memory cells are subdivided into  $m_2 \geq m_1$  groups of n' cells each. Additional memory cells (called *index cells*) are set aside to indicate for each subset of k' bits which group of n' memory cells is used to store them. The deficiency of the resulting flash codes is  $O(\sqrt{qn})$ . Note that for  $n \geq k$ , the lower bound on write deficiency in (2.1) behaves as  $\Omega(qk)$ , and thus does not depend on n. Consequently, the gap between the Jiang-Bruck construction [9] and the lower bound could be arbitrarily large, especially when n is much larger than k.

In [17], a different construction of flash codes was proposed. These codes are based upon representing the *n* memory cells as a high-dimensional array, and achieve a write deficiency of  $O(qk^2)$ . Crucially, the deficiency of these codes does *not* depend on *n*. Nevertheless, there was still a significant gap between  $O(qk^2)$  — which was the best currently known result — and the lower bound of  $\Omega(qk)$ .

Our point of departure are the indexed flash codes by Jiang and Bruck [9,9], that were briefly described above. In this section, we eliminate the need for index cells — and, thus, the overhead associated with these cells — in the Jiang-Bruck construction [9]. This is achieved by "encoding" the indices into the order in which the cell levels are increased.

As in [9], we partition the *n* memory cells into *m* groups of n' cells each. However, while in [9] the value of n' is more or less arbitrary, in our construction n' = k. We henceforth refer to such groups of n' = k cells as **blocks** (though they are not related to the *physical blocks* of floating-gate cells which comprise the flash memory). We will furthermore use, throughout

this chapter, the following terminology. We say that:

- ▶ a block is *full* if all its cells are at level q-1;

- ▶ a block is *empty* if all its cells are at level zero;

- ▶ a block is *active* if it is neither full nor empty.

In our construction, each block represents *exactly one bit*. This implies that the total number of blocks, given by  $m = \lfloor n/k \rfloor$ , must be at least k, which in turn implies  $n \ge k^2$ . If n is not divisible by k, the remaining cells are simply left unused. Finally, we also assume that either k is even or q is odd. If this is not the case, we can invoke the same construction with k replaced by k + 1 (and the last bit permanently set to zero).

The key idea is that each block is used to encode not only the current value of the bit that it represents, but also *which* of the k bits it represents. The value of the bit is simply the parity of the block. The index of the bit is encoded in the *order* in which the levels of the k cells are increased. For example, if the block stores the *i*-th bit, first the level of the *i*-th cell in the block is increased from 0 to q-1 in response to the transitions  $0 \rightarrow 1$  and  $1 \rightarrow 0$  in the bit value. Then, the same procedure is applied to the (i+1)-st cell, the (i+2)-nd cell, and so on, with the indices i + 1, i + 2, ... interpreted cyclically (modulo k). This process is illustrated in the following example.

**Example 2.4.1.** Suppose that k = 4 and q = 3. If a block represents the first bit, then its cell levels will transition from (0, 0, 0, 0) to (2, 2, 2, 2) in the following order:

$$(0000) \rightarrow (1000) \rightarrow (2000) \rightarrow (2100) \rightarrow (2200)$$

$$\rightarrow (2210) \rightarrow (2220) \rightarrow (2221) \rightarrow (2222)$$

On the other hand, for a block that represents the second bit, the corresponding cell-writing order is given by:

$$(0000) \to (0100) \to (0200) \to (0210) \to (0220)$$

$\to (0221) \to (0222) \to (1222) \to (2222)$

The cell-writing orders for blocks that represent the third and fourth bits are given, respectively, by

$$(0000) \rightarrow (0010) \rightarrow (0020) \rightarrow (0021) \rightarrow (0022)$$

$\rightarrow (1022) \rightarrow (2022) \rightarrow (2122) \rightarrow (2222)$

and

$$(0000) \rightarrow (0001) \rightarrow (0002) \rightarrow (1002) \rightarrow (2002)$$

$$\rightarrow (2102) \rightarrow (2202) \rightarrow (2212) \rightarrow (2222)$$

Note that, unless a block is full, it is always possible to determine which cell was written first and, consequently, which of the k = 4 bits this block represents.

We now provide a precise specification of an  $(n, k)_q$  flash code  $\mathbb{C}$  based upon this idea, in terms of a decoding map  $\mathcal{D}_A$  and an encoding map  $\mathcal{E}_A$ .

**Decoding map**  $\mathcal{D}_A$ : The input to this map is a cell-state vector  $\mathbf{x} = (\mathbf{x}_1 | \mathbf{x}_2 | \cdots | \mathbf{x}_m)$ , partitioned into *m* blocks. The output is the corresponding information vector  $(v_0, v_1, \dots, v_{k-1})$ .

$(v_0, v_1, \dots, v_{k-1}) = (0, 0, \dots, 0);$ for  $(j = 1; j \le m; j = j + 1)$ if  $(active(x_j))$  $\{ i = read_index(x_j); v_i = parity(x_j); \}$

**Encoding map**  $\mathcal{E}_A$ : The input to this map is a cell-state vector  $\mathbf{x} = (\mathbf{x}_1 | \mathbf{x}_2 | \cdots | \mathbf{x}_m)$ , partitioned into *m* blocks of *k* cells, and an index *i* of the bit that has changed. Its output is either a cell-state vector  $\mathbf{y} = (\mathbf{y}_1 | \mathbf{y}_2 | \cdots | \mathbf{y}_m)$  or the erasure symbol E.

```

\begin{array}{l} (y_1|y_2|\cdots|y_m)=(x_1|x_2|\cdots|x_m);\\ \text{for }(j=1;\;j\leqslant m;\;j=j+1)\\ \text{if }(\text{active }(x_j) \land (\texttt{read\_index }(x_j)==i))\\ \{\texttt{write }(y_j);\;\texttt{break}; \}\\ \text{if }(j==m+1) \; //\; active \; block \; not \; found\\ \text{for }(j=1;\;j\leqslant m;\;j=j+1)\\ \text{if }(\texttt{empty }(x_j))\;\{\texttt{write\_new }(i,y_j);\;\texttt{break}; \}\\ \text{if }(j==m+1) \; //\; no\; empty\; blocks\; remain\\ \texttt{return E}; \end{array}

```

To complete the specification of the flash code  $\mathbb{C}(\mathcal{D}_A, \mathcal{E}_A)$ , let us elaborate upon all the functions used in the pseudo-code above. The functions **active** (x), respectively **empty** (x), simply determine if the given block is active, respectively empty. The function **parity** (x) computes the parity of x, defined in Section 5.2. Note that the parity of a full block is always zero (since k(q-1) is even, by assumption). The function **read\_index** (x) computes the bit-index encoded in an active block  $x = (x_0, x_1, \dots, x_{k-1})$ . This can be done as follows. Find all the zero cells in x. Note that these cells always form one cyclically contiguous run, say  $x_j, x_{j+1}, \dots, x_{j+r}$  (where the indices are modulo k). Then the index of the corresponding bit is

$i = j + r + 1 \mod k$ . If there are no zeros in x, there must be exactly one cell, say  $x_j$ , whose level is strictly less than q-1. In this case, the bit-index is  $i = j + 1 \mod k$ . The function **write(y)** proceeds along similar lines. Find the single cyclically contiguous run of zeros in  $(y_0, y_1, \ldots, y_{k-1})$ , say  $y_j, y_{j+1}, \ldots, y_{j+r}$ . If  $y_{j-1} < q-1$ , increase  $y_{j-1}$  by one; otherwise set  $y_j = 1$ . If there are no zeros in y, find the unique cell  $y_j$  such that  $y_j < q-1$  and increase its level by one. Fin- ally, the function **write\_new(i, y)** simply sets  $y_i = 1$ .

**Theorem 2.4.1.** The write deficiency of the flash code  $\mathbb{C}(\mathcal{D}_A, \mathcal{E}_A)$  described above is at most

$$(k-1)\Big((k+1)(q-1) - 1\Big) = O(qk^2)$$

(2.2)

**Proof.** Note that at each instance, at most k of the m blocks are active. The encoding map  $\mathcal{E}_A(i, \mathbf{x})$  produces the erasure symbol E when there are no more empty blocks, and the block representing the *i*-th bit is full. In the worst case, this may occur when there are k - 1 active blocks, each using just one cell level. This contributes (k - 1)(k(q-1) - 1) unused cell levels. In addition, there are at most k - 1 cells that are unused due to the partition into  $m = \lfloor n/k \rfloor$  blocks of exactly k cells. These contribute at most (k - 1)(q-1) unused cell levels.

### 2.5 Nearly Optimal Construction

It is apparent from the proof of Theorem 2.4.1 that the deficiency of the flash code  $\mathbb{C}(\mathcal{D}_0, \mathcal{E}_0)$ , constructed in Section 2.4, is due primarily to the following: when writing stops, there are still potentially numerous unused cell levels. The key idea developed in this section is to *continue writing* after the encoding map  $\mathcal{E}_0$  produces the erasure symbol E, utilizing those cell levels that are left unused by  $\mathcal{E}_0$ . Obviously, it is *not* possible to continue writing using the same encoding and decoding maps. However, it may be possible to do so if, at the point when  $\mathcal{E}_0$  produces the erasure symbol E, we switch to a *different encoding procedure*, say  $\mathcal{E}_1$ . In fact, this idea can be applied iteratively: once  $\mathcal{E}_1$  reaches its limit, we will transition to another encoding map  $\mathcal{E}_2$ , then yet another map  $\mathcal{E}_3$ , and so on.

Assuming that  $k \equiv 0 \pmod{4}$ , here is one way to continue writing after the encoding map  $\mathcal{E}_0$  has been exhausted. When  $\mathcal{E}_0$  produces the erasure symbol E, we say that the *first stage* of encoding is over and transition to the *second stage*, as follows. First, we re-examine the cellstate vector  $\mathbf{x} = (\mathbf{x}_1 | \mathbf{x}_2 | \cdots | \mathbf{x}_m)$  and re-partition it into  $2m = 2 \lfloor n/k \rfloor$  blocks of k/2 cells each. Most of these smaller blocks will be already full, but we may find some  $m_1$  of them that are either empty or active (live). Observe that  $m_1 \leq 2(k-1)$  since at the end of the first stage, there are at most k-1 active blocks of k cells, and each of them produces at most two live (non-full) blocks of k/2 cells.

If  $m_1 \ge k$ , we can continue writing as follows. Once again, each of the  $m_1$  blocks will represent exactly one bit; as before, the value of this bit is determined by the parity of the block. As part of the transition from the first stage to the second stage, we record the current information vector  $(v_0, v_1, \ldots, v_{k-1})$  in the first k of the  $m_1$  live blocks, say  $x_1, x_2, \ldots, x_k$ . To this end, whenever **parity**  $(x_i) \ne v_{i-1}$ , we increase the level of one of the cells in  $x_i$  by one; otherwise, we leave  $x_i$  as is.

Since the blocks now have k/2 cells rather than k cells, it is no longer possible to encode in each block which of the k information bits it represents. Therefore, we set aside for this purpose  $2(k-1) \left[ \log_a(k+2) \right]$  index cells (that are not used during the first stage). These cells are partitioned into 2(k-1) blocks of  $\mu = \lceil \log_a(k+2) \rceil$  cells each, which we call *index blocks*. Henceforth, it will be convenient to refer to the blocks of k/2 cells as *parity blocks*, in order to distinguish them from the index blocks. Initially, the first k index blocks  $u_1, u_2, \ldots, u_k$ are set so that  $u_i = i$  (in the base-q number system), which reflects the fact that the information bits  $v_0, v_1, \ldots, v_{k-1}$  are stored (in that order) in the first k live parity blocks. The next  $m_1 - k$  index blocks are set to  $(0, 0, \dots, 0)$ , thereby indicating that the corresponding (live) parity blocks are available to store information bits. The last  $2(k-1) - m_1$  index blocks are set to  $(q-1, q-1, \dots, q-1)$  to indicate that the corresponding parity blocks are full (in fact, nonexistent). Finally, it is possible that in the process of enforcing **parity**  $(x_i) = v_{i-1}$  for the first k live parity blocks, some of these blocks become full (this happens iff  $wt(x_i) = (k/2)(q-1) - 1$ and  $v_i = 0$  at the end of the first stage, since k/2 is even by assumption). To account for this fact, we set the corresponding index blocks to  $(q-1, q-1, \ldots, q-1)$ . This completes the transition from the first stage to the second stage, which is invoked when the encoding map  $\mathcal{E}_0$  produces the erasure symbol E.

Let us now summarize the foregoing discussion by giving a concise algorithmic description of the transition procedure.

**Transition procedure**  $\mathcal{T}_1$ : Partition the memory into  $2\lfloor n/k \rfloor$  parity blocks of k/2 cells, and identify the  $m_1 \leq 2(k-1)$  parity blocks  $x_1, x_2, \ldots, x_{m_1}$  that are not full. If  $m_1 < k$ , output the erasure symbol E and terminate. Otherwise, set the 2(k-1) index blocks  $u_1, u_2, \ldots, u_{2k-2}$  as

follows:

$$\boldsymbol{u}_{i} = \begin{cases} i & \text{for } i = 1, 2, \dots, k \\ 0 & \text{for } i = k + 1, k + 2, \dots, m_{1} \\ q^{\mu} - 1 & \text{for } i = m_{1} + 1, m_{1} + 2, \dots, 2k - 2 \end{cases}$$

(2.3)

where  $\mu = \lceil \log_q(k+2) \rceil$  is the number of cells in each index block, then record the information vector  $(v_0, v_1, \dots, v_{k-1})$  in the first *k* live parity blocks  $x_1, x_2, \dots, x_k$ , as follows:

```

for (i = 1; i \le k; i = i + 1)

if (parity (x_i) \ne v_{i-1})

{ increment (x_i); if (full (x_i)) u_i = q^{\mu} - 1; }

```

The function **full**(x) determines whether the given block x (which could be a parity block or an index block) is full. The function **increment**(x) increases by one the level of a cell (does not matter which) in the given live block.

During second-stage encoding and decoding, we will need to figure out for each active parity block x which of the k information bits it represents. To this end, we will have to find and read the index block u that *corresponds* to x. How exactly is the correspondence between parity blocks and index blocks established? Note that, upon the completion of the transition procedure  $T_1$ , there is the same number of live parity blocks and live index blocks; moreover, the *j*-th *live* index block corresponds to the *j*-th *live* parity block, for all *j*. The encoding procedure will make sure that this correspondence is preserved throughout the second stage: whenever a parity block becomes full, it will make the corresponding index block full as well.

We are now ready to present the encoding and decoding maps which are, again, specified in C-like pseudo-code notation.

**Decoding map**  $\mathcal{D}_1$ : The input is a cell-state vector  $\mathbf{x} = (\mathbf{x}_1 | \mathbf{x}_2 | \cdots | \mathbf{x}_{2m} \| \mathbf{u}_1 | \mathbf{u}_2 | \cdots | \mathbf{u}_{2k-2})$ , partitioned into 2m parity blocks, of k/2 cells each, and 2(k-1) index blocks. The output is the information vector  $(v_0, v_1, \dots, v_{k-1})$ .

$$\begin{array}{l} (v_0, v_1, \dots, v_{k-1}) = (0, 0, \dots, 0); \\ \texttt{for } (\ell = j = 1; \ j \leqslant 2m; \ j = j + 1) \\ \{ & \texttt{if (full}(x_j)) \texttt{ continue}; \ // \textit{skip full blocks} \\ \texttt{while (full}(u_\ell)) \ \ell = \ell + 1; \ // \textit{skip full blocks} \\ i = u_\ell; \ \ell = \ell + 1; \\ \texttt{if } (i \neq 0) \ v_{i-1} = \texttt{parity}(x_j); \\ \end{array}$$

Given an index *i* of the bit that has changed, the encoding map  $\mathcal{E}_1$  first tries to find an active parity block *x* that represents the *i*-th information bit. If such a block is found, it is incremented

and checked for getting full (in which case the corresponding index block is set to  $q^{\mu} - 1$ ). If not, another live parity block is allocated to represent the *i*-th information bit. If no more live parity blocks are available, the erasure symbol E is returned.

**Encoding map**  $\mathcal{E}_1$ : The input is a cell-state vector  $\mathbf{x} = (\mathbf{x}_1 | \mathbf{x}_2 | \cdots | \mathbf{x}_{2m} \| \mathbf{u}_1 | \mathbf{u}_2 | \cdots | \mathbf{u}_{2k-2})$ , partitioned into 2m parity blocks and 2(k-1) index blocks, and an index *i* of the information bit that changed. Its output is either a cell-state vector  $\mathbf{y} = (\mathbf{y}_1 | \mathbf{y}_2 | \cdots | \mathbf{y}_{2m} \| \mathbf{u}_1' | \mathbf{u}_2' | \cdots | \mathbf{u}_{2k-2}')$  or the symbol E.