## UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Design Techniques for Ultra-High-Speed Time-Interleaved Analog-to-Digital Converters

**Permalink** https://escholarship.org/uc/item/2ft3480b

**Author** Duan, Yida

Publication Date 2015

Peer reviewed|Thesis/dissertation

Design Techniques for Ultra-High-Speed Time-Interleaved Analog-to-Digital Converters

(ADCs)

By

Yida Duan

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Ali M. Niknejad Professor Paul K. Wright

Spring 2015

# Design Techniques for Ultra-High-Speed Time-Interleaved Analog-to-Digital Converters (ADCs)

Copyright 2015 by Yida Duan

#### Abstract

Design Techniques for Ultra High Speed Analog-to-Digital Converters

by

#### Yida Duan

#### Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

### University of California, Berkeley

### Professor Elad Alon, Chair

Analog-to-Digital Converters (ADCs) serve as the interfaces between the analog natural world and the binary world of computer data. Due to this essential role, ADC circuits have been well studied over 40 years, and many problems associated with them have already been solved. However in recent years, a new species of ADCs has appeared, and since then attracted lots of attention. These are ultra-high-speed (often greater than 40GS/s) time-interleaved ADCs of low or medium resolution (around 6 to 8 bit) built in CMOS processes. Although such ADCs can be used in highspeed electronic measurement equipment and radar systems, the recent driving force behind them is next generation 100Gbps/400Gbps fiber optical transceivers. These transceivers take advantage of ultra-high-speed ADCs and digital-signal-processors (DSPs) to enable ultra-high data-rate communications in long-haul networks (city-to-city, transcontinental, and transoceanic fiber links), metro networks (fibers that connect enterprises in metropolitan areas), and data centers (fiber links within data center infrastructures). At such high sampling rate, massively time-interleaved successive-approximation ADC (SAR ADC) architecture has emerged as the dominant solution due to its excellent power efficiency. Several recent works has demonstrated success in achieving high sampling rate. However, the sampling network has become the bottleneck that limits the input bandwidth in these ADCs. It is apparent that conventional switch-based track-and-hold (T&H) circuit cannot satisfy the >20GHz bandwidth requirement. In addition, it is unclear what the optimal interleaving configuration is. Each state-of-the-art design adopts a different interleaving configuration – from straightforward conventional 1-rank interleaving to 2-rank hierarchical sampling or even 3 ranks. How to partition interleaving factors among different ranks has not yet been investigated. Furthermore, asynchronous SAR sub-ADCs are often used in these designs to push the sampling rate even further. The well-known sparkle-code issues caused by comparator meta-stability in asynchronous SARs can significantly increase the Bit-Error-Rate (BER) of the transceivers unless power hungry error correction coding are implemented in the system. Although many works in the literature attempted to deal with the meta-stability in asynchronous SARs, the effectiveness of these approaches have not been fully demonstrated. In this thesis, I will first propose a new cascode-based T&H circuits to improve the ADC bandwidth beyond the limit of conventional switch-based T&H circuits. Then, a system design and optimization methodology of hierarchical time-interleaved sampling network is presented in the context of cascode T&H. To deal with sparkle-code issue in asynchronous SAR sub-ADCs, a new back-end meta-stability correction technique is employed. An extensive statistical analysis is provided to verify the correction algorithm can greatly reduce sparkle-code error-rates. To further demonstrate the effectiveness of the proposed circuits and techniques, two prototype ADCs have

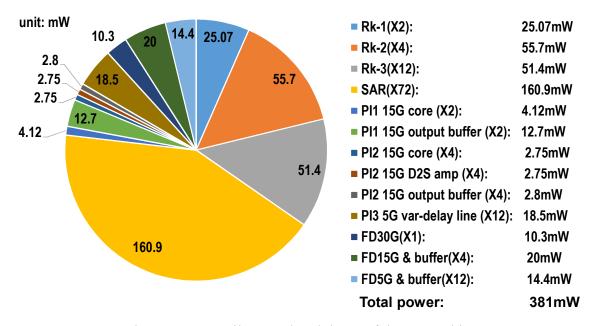

been implemented. The first 7b 12.5GS/s hierarchically time-interleaved ADC in 65nm CMOS process demonstrates 29.4dB SNDR and >25GHz bandwidth. The later 6b 46GS/s ADC in 28nm CMOS employs asynchronous SAR sub-ADC design with back-end meta-stability correction. The measurement results show it achieves sparkle-code error free operation over 1e10 samples in addition to achieving >23GHz bandwidth and 25.2dB SNDR. The power consumption is 381mW from 1.05V/1.6V supplies, and the FOM is 0.56pJ/conversion-step.

To my mother

To Wen

## Contents

| Co              | ontents                               |                                                        | ii |  |

|-----------------|---------------------------------------|--------------------------------------------------------|----|--|

| List of Figures |                                       |                                                        |    |  |

| List of Tables  |                                       |                                                        |    |  |

| 1.              | Introduction                          |                                                        | 1  |  |

|                 | 1.1 Thesis or                         | ganization                                             | 3  |  |

| 2.              | High-speed sam                        | pling                                                  | 4  |  |

|                 | 2.1 Track-and                         | d-hold circuits                                        | 4  |  |

|                 | 2.1.1                                 | Switch-based T&H circuits                              | 5  |  |

|                 | 2.1.2                                 | Cascode-based T&H circuits                             | 7  |  |

|                 | 2.1.3                                 | Mitigation of non-idealities in T&H circuits           | 9  |  |

|                 | 2.2 Hierarchi                         | cal time-interleaving                                  | 16 |  |

|                 | 2.2.1                                 | Optimization of hierarchical sampling network          | 19 |  |

|                 | 2.3 Implement                         | ntation and measurement results of the 7b 12.8GS/s ADC | 22 |  |

| 3.              | . High-speed power-efficient sub-ADC  |                                                        |    |  |

|                 | 3.1 SAR sub-                          | ADC                                                    | 26 |  |

|                 | 3.1.1                                 | Synchronous and asynchronous SAR                       | 27 |  |

|                 | 3.1.2                                 | Comparator meta-stability and sparkle-codes            | 31 |  |

|                 | 3.2 Back-end                          | meta-stability correction                              | 34 |  |

|                 | 3.2.1                                 | Meta-stability correction by detect-then-stop method   | 35 |  |

|                 | 3.2.2                                 | Back-end meta-stability correction                     | 37 |  |

|                 | 3.2.3                                 | Statistical analysis of sparkle-code error-rate        | 40 |  |

| 4.              | 6b 40GS/s hiera                       | rchically time-interleaved asynchronous SAR ADC        | 46 |  |

|                 | 4.1 System ov                         | verview                                                | 46 |  |

|                 | 4.2 Sampling circuits                 |                                                        | 48 |  |

|                 | 4.3 Clock generation and distribution |                                                        | 49 |  |

|                 | 4.3.1                                 | Frequency dividers                                     | 49 |  |

|                 |                                       | Phase interpolator and duty-cycle correction circuits  | 51 |  |

|                 | 4.3.3                                 | Variable delay-line                                    | 52 |  |

|                 |                                       | implementation                                         | 53 |  |

|                 | 4.5 Measurem                          | ent results and discussion                             | 57 |  |

| 5.              | Conclusion                            |                                                        | 64 |  |

|                 | 5.1 Summary                           |                                                        | 64 |  |

|                 | 5.2 Future wo                         | rk                                                     | 65 |  |

### Bibliography

iii

# **List of Figures**

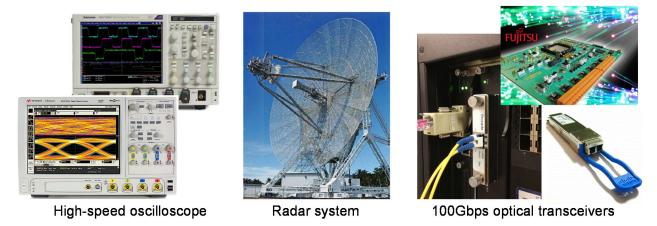

| 1.1                                 | Applications for ultra-high-speed ADCs                                                                                                                                        | 1            |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

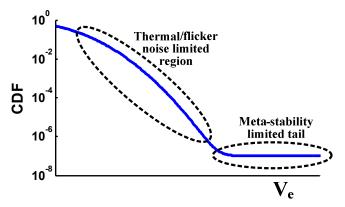

| 1.2                                 | Cumulative distribution function (CDF) of conversion error of a common ADC                                                                                                    | 2            |

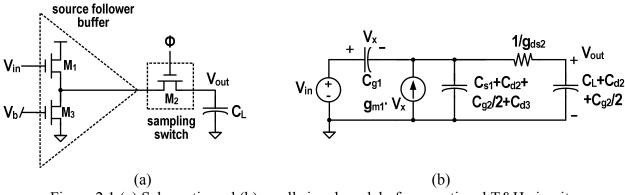

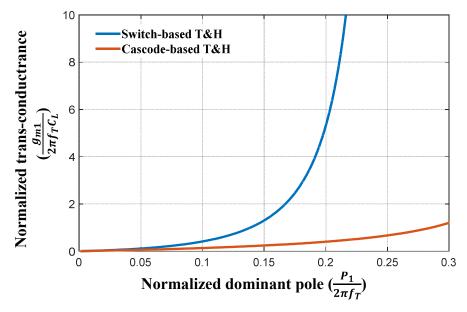

| 2.1<br>2.2                          | (a) Schematic and (b) small signal model of conventional T&H circuit<br>The speed-power trade-off curves for (a) switch-based T&H circuit and (b) cascode-base<br>T&H circuit | 5<br>ed<br>6 |

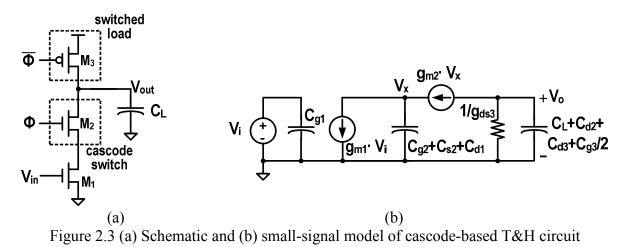

| 2.3                                 | (a) Schematic and (b) small-signal model of cascode-based T&H circuit                                                                                                         | 7            |

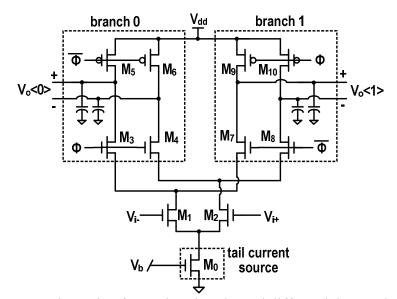

| 2.4                                 | Schematic of a 2x time-interleaved differential cascode T&H                                                                                                                   | 8            |

| 2.5                                 | Schematic and functional block diagram of cascode samplers with (a) triode PMOS load                                                                                          | ,            |

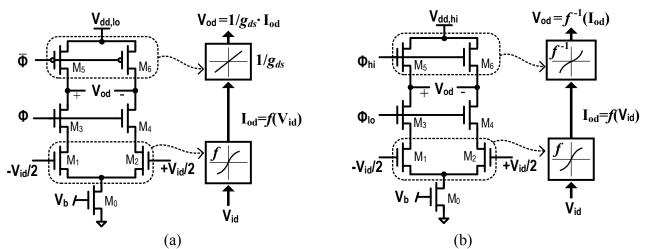

|                                     | and (b) saturation NMOS load                                                                                                                                                  | 10           |

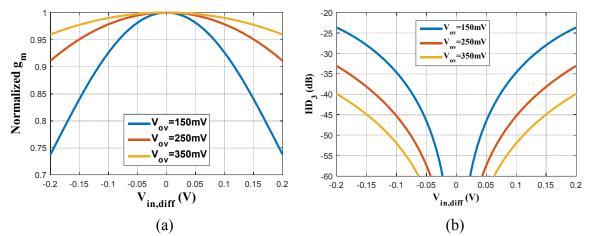

| 2.6                                 | Input of a differential pair vs. (a) normalized trans-conductance and (b) HD <sub>3</sub> for different over-drive voltages                                                   | t<br>10      |

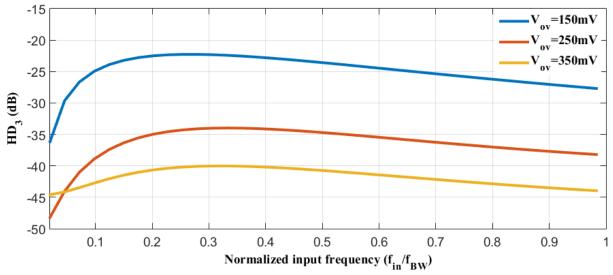

| 2.7                                 | normalized input frequency vs. HD <sub>3</sub> for a 400mV peak-to-peak input sinewave and different overdrive voltages (V <sub>ov</sub> )                                    | 12           |

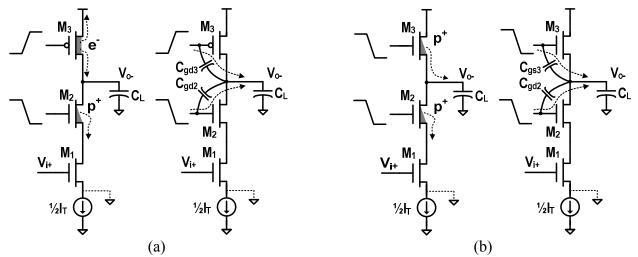

| 2.8                                 | Illustration of charge injection and clock-feedthrough in cascode-based T&H with (a) triode PMOS load and (b) saturation NMOS load                                            | 13           |

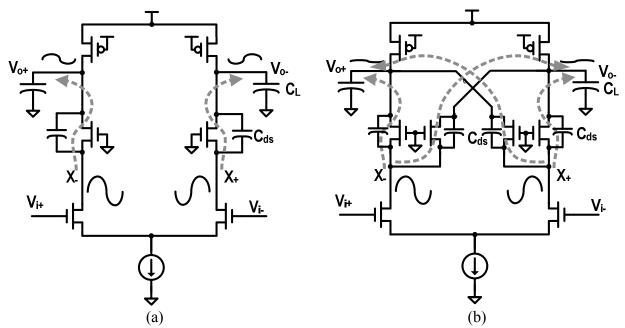

| 2.9                                 | illustration of signal-feedthrough issue in (a) cascode T&H and (b) cascode T&H with feedthrough cancellation                                                                 | 14           |

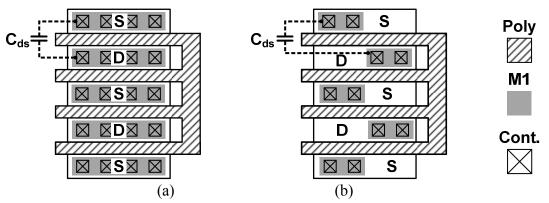

| 2.10                                | Layout of cascode NMOS (a) with large $C_{ds}$ and (b) with minimum $C_{ds}$                                                                                                  | 14           |

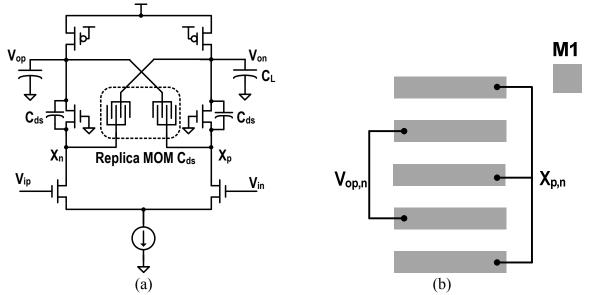

| 2.11                                | (a) Schematic of cascode T&H with replica MOM $C_{ds}$ feedthrough cancellation (b) layor                                                                                     |              |

|                                     | of replica MOM $C_{ds}$                                                                                                                                                       | 15           |

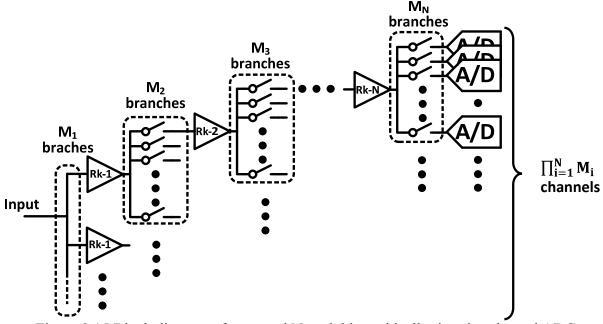

|                                     | Conventional time-interleaved ADC                                                                                                                                             | 16           |

|                                     | Block diagram of a 3 rank hierarchically time-interleaved ADC                                                                                                                 | 17           |

| <ul><li>2.14</li><li>2.15</li></ul> | Timing diagram of a 3 rank hierarchically time-interleaved ADC<br>Block diagram of a general N-rank hierarchically time-interleaved ADC                                       | 18<br>19     |

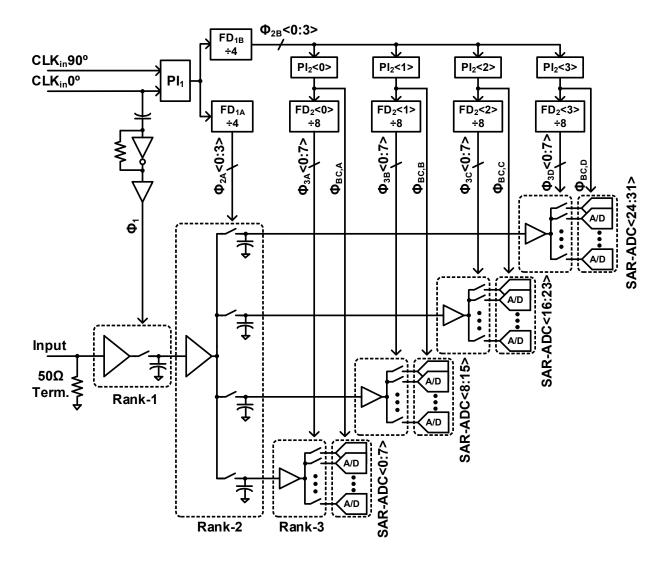

|                                     | Block diagram of the 7b 12.8GS/s ADC in 65nm CMOS                                                                                                                             | 23           |

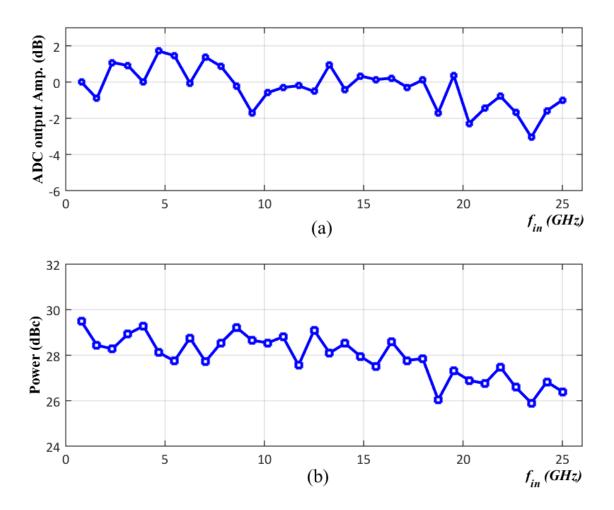

| 2.17                                | the input frequency vs. (a) normalized output amplitude, and (b) SNDR of the 7b 12.8GS                                                                                        |              |

| 2.17                                | ADC                                                                                                                                                                           | 24           |

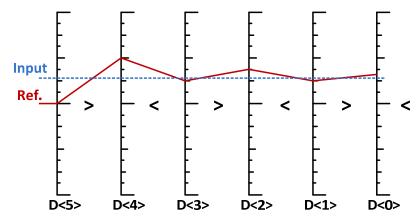

| 3.1                                 | Illustration of the conversion algorithm of 6-bit SAR ADC                                                                                                                     | 26           |

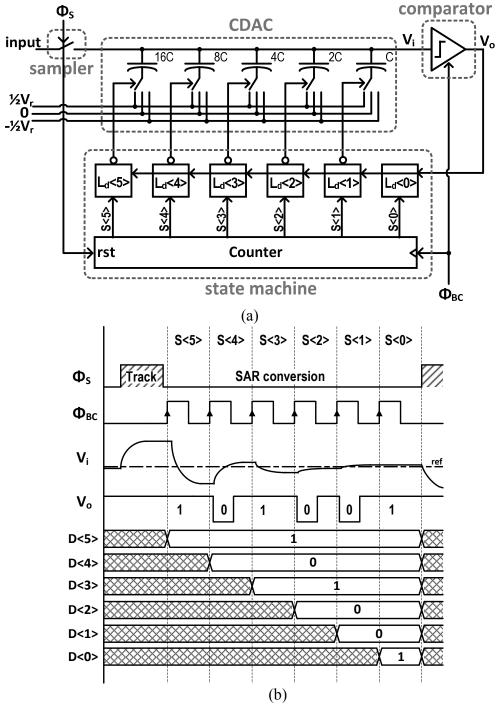

| 3.2                                 | (a) schematic and (b) timing diagram of a 6-bit synchronous SAR ADC                                                                                                           | 27           |

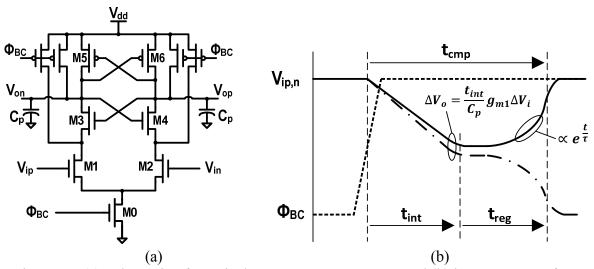

| 3.3                                 | (a) Schematic of a typical Strongarm comparator, and (b) its output waveforms                                                                                                 | 28           |

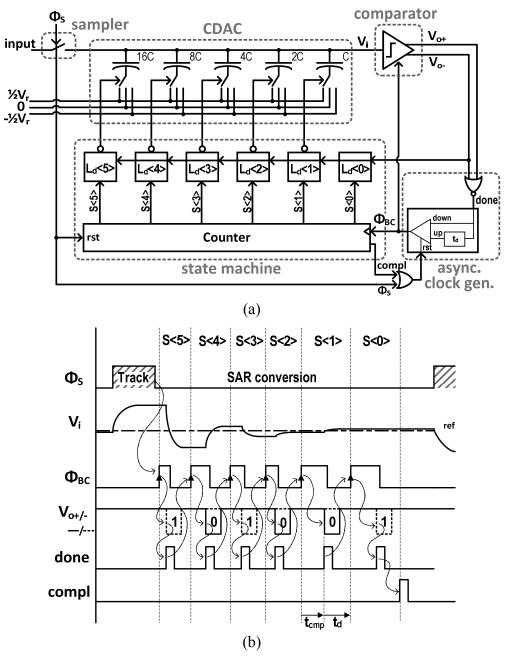

| 3.4                                 | (a) Schematic and (b) timing diagram of classic asynchronous SAR ADC                                                                                                          | 30           |

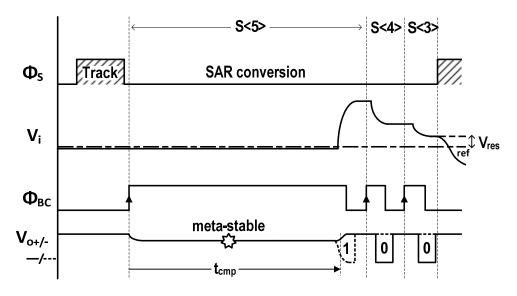

| 3.5                                 | SAR ADC waveforms for a scenario that results in a sparkle-code                                                                                                               | 32           |

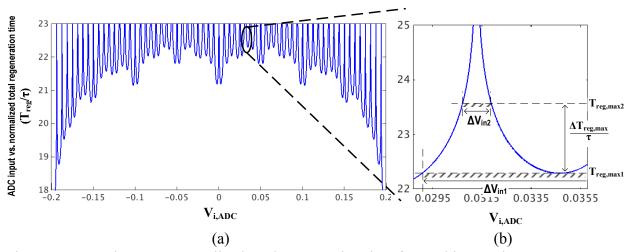

| 3.6                                 | ADC input vs. normalized total regeneration time for a 6-bit asynchronous SAR ADC w 400mV input swing and 1.05V supply                                                        | ith<br>34    |

| 3.7                                 | Estimated sparkle-code error-rate vs. normalized additional conversion time for a 6-bit asynchronous SAR ADC with 400mV input swing and 1.05V supply                          | 34           |

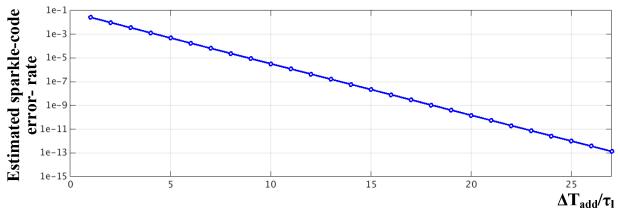

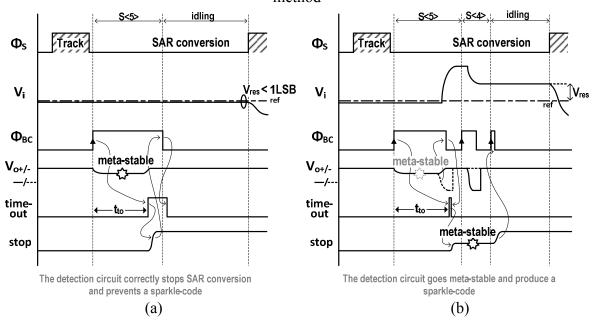

| 3.8                                 | Waveform of a classic asynchronous SAR ADC in the scenario that (a) a meta-stability                                                                                          |              |

| 3.9                                 | event does not cause a sparkle-code and (b) a meta-stability event caused a sparkle-code Schematic of asynchronous SAR ADC with detect-then-stop sparkle-code correction      | 35           |

|                                     | method                                                                                                                                                                        | 36           |

| 3.10 | Waveform of detect-then-stop meta-stability correction circuit in the scenario of (a) the           |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | meta-stability is correctly detected, and (b) the detection circuit goes meta-stable                | 36 |

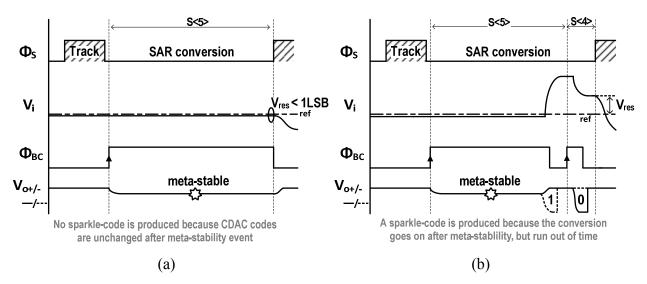

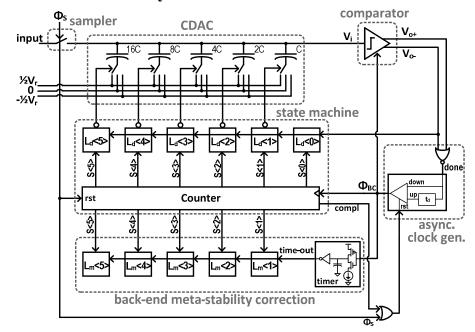

| 3.11 | Schematic asynchronous SAR ADC with back-end meta-stability correction circuit                      | 37 |

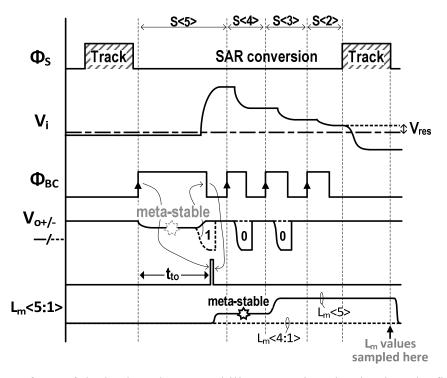

| 3.12 | Waveform of the back-end meta-stability correction circuit when the first correction bit            |    |

|      | $(L_m < 5>)$ goes meta-stable                                                                       | 38 |

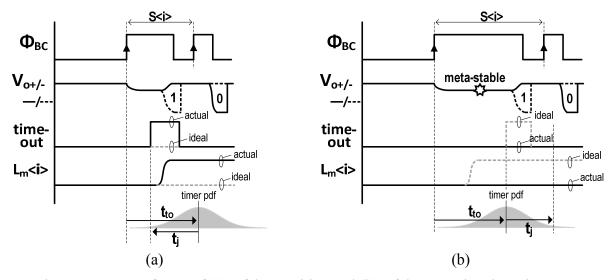

| 3.13 | Waveform of (a) a false-positive and (b) false-negative detection error                             | 40 |

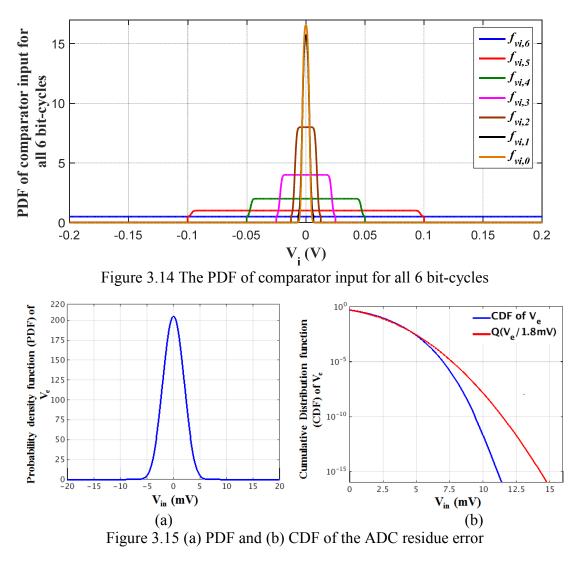

| 3.14 | The PDF of comparator input for all 6 bit-cycles                                                    | 44 |

| 3.15 | (a) PDF and (b) CDF of the ADC residue error                                                        | 44 |

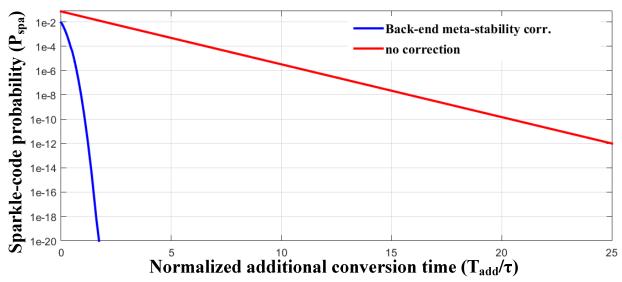

| 3.16 | Additional conversion time vs. the sparkle-code error-rate for asynchronous SAR ADC                 |    |

|      | with and without back-end correction                                                                | 45 |

| 4.1  | (a) block diagram and (b) timing diagram of the ADC chip                                            | 46 |

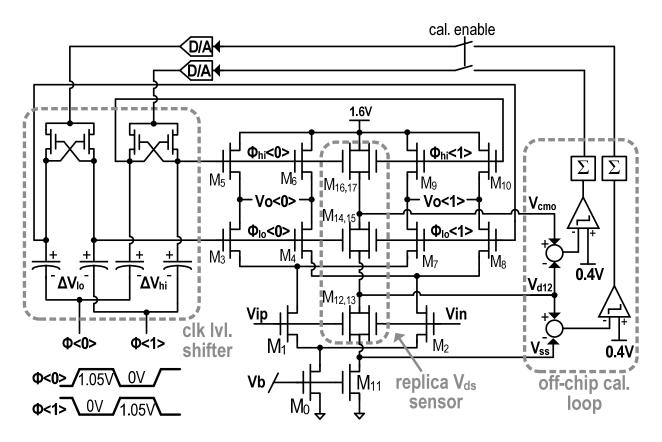

| 4.2  | The implementation of Rk-1 cascode T&H circuit                                                      | 48 |

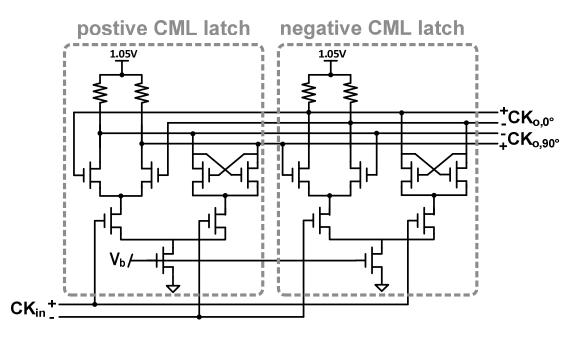

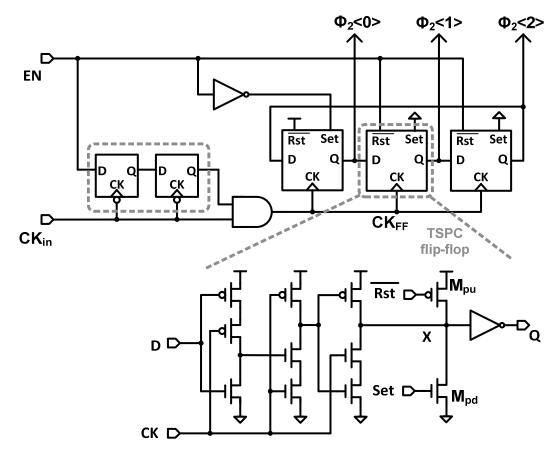

| 4.3  | Schematic of front-end frequency divider (FD <sub>1</sub> )                                         | 49 |

| 4.4  | Schematic of the first CMOS frequency divider (FD <sub>2</sub> )                                    | 50 |

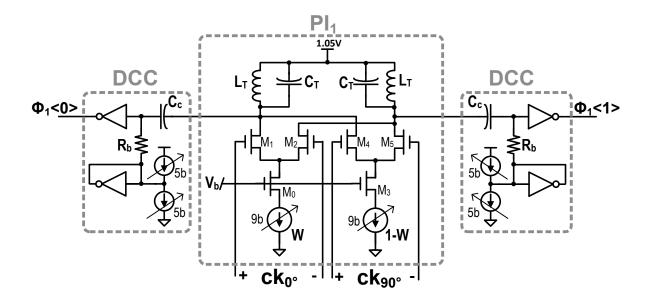

| 4.5  | Schematic of the front-end phase interpolator (PI <sub>1</sub> ) and duty-cycle correction circuits |    |

|      | (DCC)                                                                                               | 51 |

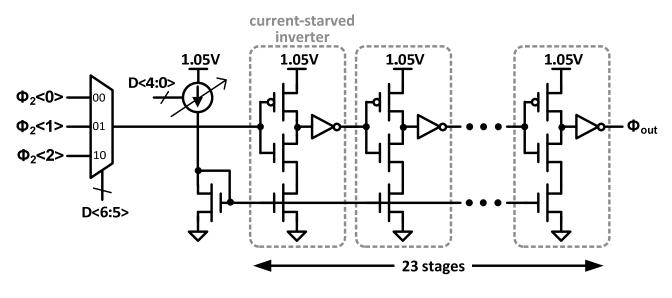

| 4.6  | Schematic of variable-delay-line                                                                    | 52 |

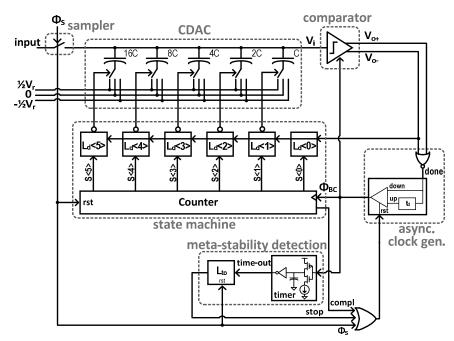

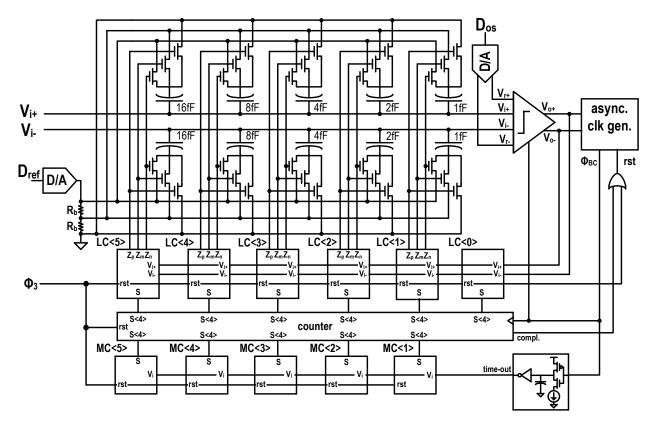

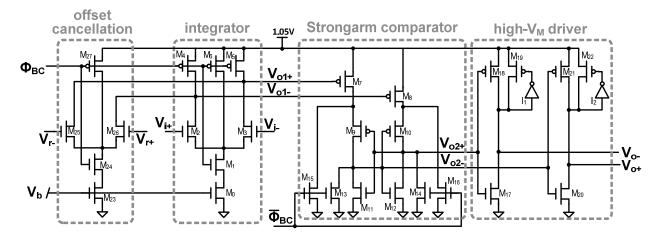

| 4.7  | Complete schematic of 6-bit asynchronous SAR sub-ADC                                                | 53 |

| 4.8  | Comparator schematic                                                                                | 54 |

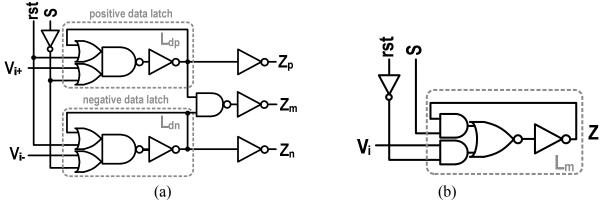

| 4.9  | Schematic of (a) SAR logic cell (LC) and (b) meta-stability cell (MC) used in the SAR               |    |

|      | ADC                                                                                                 | 55 |

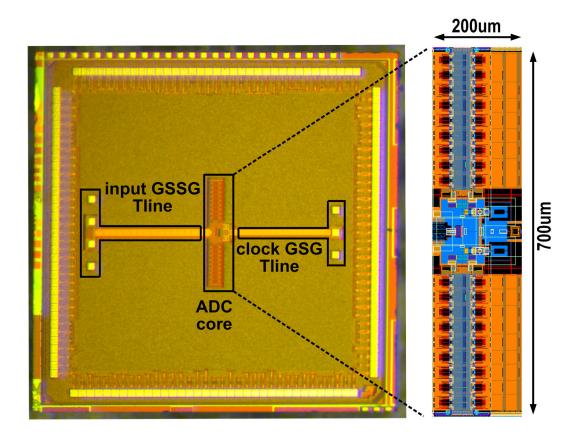

| 4.10 | die photo                                                                                           | 57 |

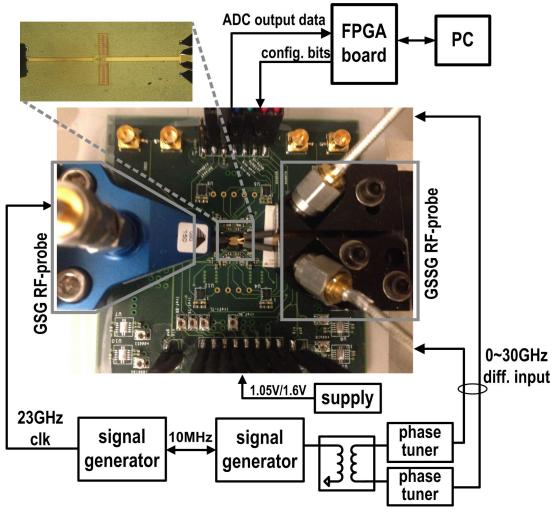

| 4.11 | Test setup                                                                                          | 58 |

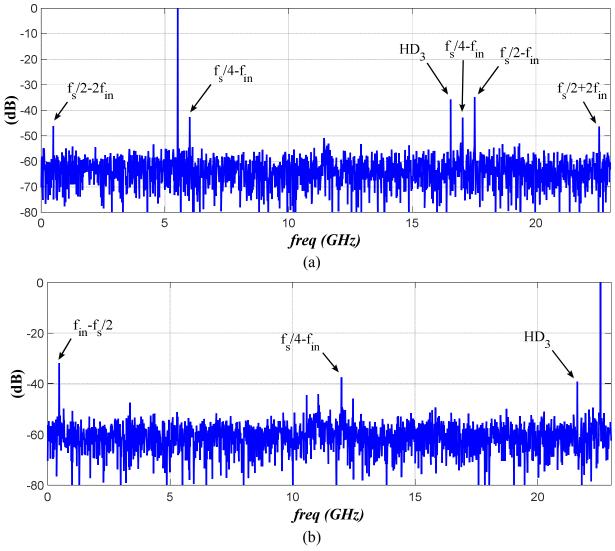

| 4.12 | ADC output spectrum using 3600-pt FFT for (a) a 5.5GHz input tone, and (b) a 23.5GHz                | Z  |

|      | input tone                                                                                          | 59 |

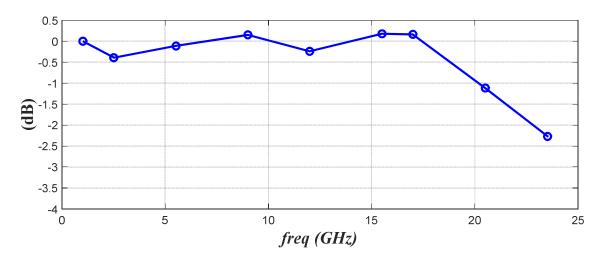

|      | Input frequency vs. normalized ADC output amplitude                                                 | 60 |

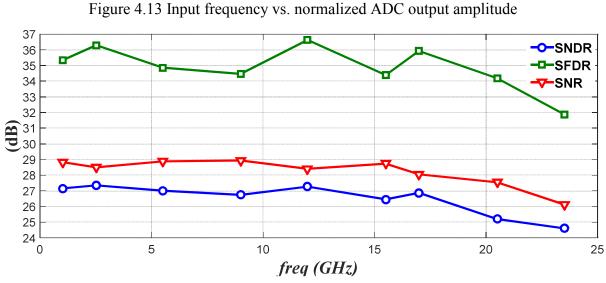

| 4.14 | ADC input frequency vs. SNDR, SFDR and SNR                                                          | 60 |

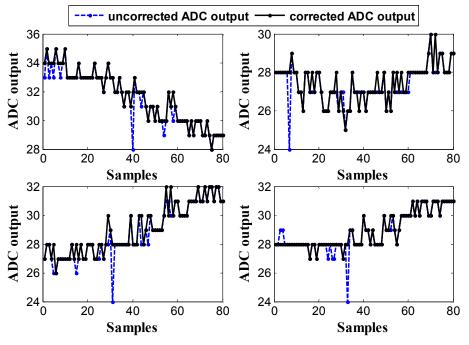

|      | Examples of captured sparkle-codes                                                                  | 61 |

| 4.16 | Detailed power breakdown of the ADC chip                                                            | 62 |

# **List of Tables**

### I. Comparison table

63

## Acknowledgements

Spending a decade at UC Berkeley is a long time, even for people like me who refuse to graduate. It is exactly a third of my life now. Many things happened in this decade: besides gaining fifty pounds then losing fifty pounds then gaining back fifty pounds and the numerous sleepless nights stressed out for tape-outs, I generally had an enjoyable decade. I enjoyed my Berkeley decade not because of the tasty local food or the interesting local people or the magnificent protests, but because of the great colleagues, awesome friends, and the tremendously knowledgeable and kind mentors without whom I will not be who I am right now. Here are the people to whom I owe my sincere gratitude.

Needlessly to say, I would first and foremost thank my advisor and friend, Prof. Elad Alon. He is not only vastly knowledge, but also extremely kind and considerate. Regardless how busy he was, he always found time for in-depth technical discussions with me and my fellow students. He has supported me throughout my ph.D. career, despite many of my progress-less years. Under his guidance, I have become an analog/mixed-signal circuit designer. I owe my career to him.

Second, I would sincerely thank my long time mentor and friend, Prof. Ali M. Niknejad. I have learned so much through his lectures and office hours. I enjoyed so much having technical discussions with him. He has given me great guidance in my ph.D. career. He is not just a vastly knowledgeable professor, a great educator, and a kindly humble person, but also a tremendous soccer player. I still remember his powerful headers vividly. I would also like to thank him for organizing the amazing "Soccer and Circuits" retreat, during which I had so much fun.

In addition, I would like to thank Prof. Vladimir Stejanovic for his guidance and support during my last year at UC Berkeley. He is such a nice and easy going person with so many crazy and interesting ideas. I wish I could have more time to work with him. I would also like to thank Prof. Bernhard E. Boser, who first brought me into the world of the data converters and taught me so much about them.

Then, I would also like to thank Prof. Paul K. Wright for being so kind to be a member of my dissertation committee. I would like to thank Prof. Seth Sanders and Prof. Liwei Lin, for being members of my qualification exam committee and suffered 2 hours of my exhausting presentation.

Furthermore, I would also like to thank my friends and colleagues, to whom I wasn't always nice to: Jiashu Chen, Lingkai Kong, Yue Lu, Paul Liu, Jaeduk Han, Dusan Stepanovic, Jun-Chau Chien, Nai-Chung Kuo, Chintan Thakkar, Kwangmo Jung, John Crossley, Hanh-Phuc Le, Steven Callendar, Ping-Chen Huang, Wenting Zhou, Shinwon Kang, Jaehwa Kwak, Lu Ye, Jung-Dong Park, Siva Thyagarajan, Chen Sun, Krishna Settaluri, Sen Lin, Eric Chang, Nathan Narevsky, Brian Zimmer, Kosta Trotskovsky, Wei-hung Chen, Debopriyo Chowdhury, Amin Arbabian, Ehsan Adabi, Zhiming Deng, Chinwuba Ezekwe ... I would also like to thank BWRC staffs, especially Fred Burghdart, Tom Boot, Sarah Jordan, and Olivia Nolan for their support in the office and lab.

At last, I would like to thank many great mentors from industrial and academia whom I was fortunate to get to know. I would like to thank Dr. Qiong Wu, and Kevin Mahooti of NXP

semiconductor, Dr. Xiaoye (Sean) Wang, Gene Lin, and Dr. Li Lin of Marvell semiconductor, Dr. Ken Chang of Xilinx inc., Prof. Boris Murmann of Stanford University, Prof. Un-Ku Moon of Oregon State University, Dr. Robert Neff and Dr. Ken Nishmura of Keysight, Dr. Stephane Le Tual, and Dr. Andreia Cathelin of ST Microeletronics, Dr. James Gorecki and Lawrence Tsai of Inphi Corporation.

## **Chapter 1**

## Introduction

An Analog-to-Digital Converter (ADC) is a basic circuit block that typically converts a continuous-time analog input signal into samples of quantized binary data that can be processed by digital processors. Throughout history, ADCs played important roles in a wide range of electronic systems. Recently, there are particularly high demands for ADCs of extremely high sampling rate, usually >40GS/s. This is driven by applications such as high-speed electronic measurement systems, radars, and most recently, the next-generation of optical transceivers. Electronic measurement systems such as real-time oscilloscopes use high-speed ADCs to acquire input analog waveform and accurately present it to the user with high fidelity. Modern radar systems employ ADC/DSP for reliable detection. In order to satisfy exponentially growing demands for data consumption, 100Gbps/400Gbps fiber optics transceivers employ high-order modulation schemes to push the data-rate beyond the bandwidth of existing fibers and optical components [1], [2], [3]. For example, DP-QPSK (Dual-Polarization Quadrature-Phase-Shift-Keying) has been deployed recently in most existing long-haul/metro fiber links, with 16-QAM expected to follow in a few years, fiber links within mega data-centers are currently moving toward 4-PAM solutions – pulse amplitude modulation with 4 levels. These modulation schemes rely on ADC/DSP for demodulation, channel equalization, and clock-data recovery. In all these application, using CMOS technologies is very beneficial not only due to their advantage in cost and power, but also because many DSP functions can be readily integrated along with the ADC to process its raw data before sending the useful information off-chip. Medium resolution between 6b and 8b is usually sufficient for these applications.

Figure 1.1 Applications for ultra-high-speed ADCs

Previous works [1], [2], [3], [4], have demonstrated that massively time-interleaved Successive-Approximation-Registers (SAR) ADCs are able to achieve >40GS/s in CMOS with reasonable Figure-Of-Merit (FOM). > 40GS/s sampling rate has been achieved with 16 or more SAR sub-ADC channels. However, their bandwidths are below 20GHz – much lower than the Nyquist-rate. This bandwidth limitation is due to several issues associated with sampling. First, the input of a traditional time-interleaved ADC is directly connected to a large number of parallel switches [1] [5] [6]. The ADC input capacitance caused by the parasitic capacitors of all these switches can be quite large, and the low-pass filter formed by this ADC input capacitance with the  $25\Omega$  equivalent input resistance – the  $50\Omega$  termination resistor in parallel with the  $50\Omega$ cable/transmission line characteristic impedance – may have a low cut-off frequency. To make things worse, since all the sampling switches track a continuous changing analog input, the sampling clocks that drive these switches must satisfy stringent jitter requirement to avoid SNDR attenuation at high frequencies. Unless extra power is spent to distribute these many sampling clocks with low jitter, the Effective-Resolution-Bandwidth (ERBW) of the ADC can be even lower.

In addition, the input signal must pass through the sampling switch before charging the sampling capacitor in conventional track-and-hold circuits. The sampling capacitor sees the on resistance of the switch in series with the output impedance of the circuits in front, which may be the output impedances of the ADC driver [1] [6], or in some cases, another sampling switch [4]. The series resistance penalty of these switches can significantly lower the track-and-hold bandwidth. Once the sampling is performed, the discrete-time interleaved samples must be quantized by sub-ADCs, which introduce more errors to the system. Other than quantization noise, thermal/fliker noise, large amplitude error may occur as a result of meta-stability of the decision circuit inside the sub-ADCs. These rarely occurring meta-stability-induced errors – sparkle codes – have a non-Gaussian distribution profile, and may have much higher error-rate than the Gaussian distributed thermal/flicker noise at large amplitude (Figure 1.2). Electronic measurement results or detection [7]. As a result, excessive power may be spent to just to keep the sparkle-code error rate below the acceptable levels.

Figure 1.2 Cumulative distribution function (CDF) of conversion error of a common ADC

This thesis investigates the BW limitation and sparkle-code error-rate issue in ultra-highspeed time-interleaved ADCs. Novel sampling architectures such as hierarchical time-interleaving that enables high sampling rate with good power efficiency is also studied. Circuit techniques such as cascode T&H circuits are proposed to alleviate the BW limitation. An optimization method for hierarchical sampling network with cascode T&H circuit is presented. A new back-end metastability correction circuit is developed to reduce sparkle-code error rate for asynchronous SAR sub-ADCs. A 6b 46GS/s prototype ADC is fabricated in 28nm Fully-Depleted Silicon-on-Insulator (FDSOI) process to demonstrate the results.

### **1.1 Thesis Organization**

Despite the numerous architecture and implementations, all ADCs perform 2 basic functions: sampling and quantization. Thus, the discussion in this thesis is divided into 2 parts: Chapter 2 starts the discussion from sampling, especially focusing on high speed sampling. After a brief review of sampling errors, track-and-hold bandwidth, and time-interleaving, the limitations of conventional switch-based samplers are introduced. Then, a new cascode-based sampling circuit is proposed. The concept of time-interleaving is also reviewed, and the technique of hierarchical time-interleaved sampling is studied. Later in the chapter, a general optimization method for hierarchically time-interleaved sampler networks using cascode sampler is presented. At the end of the chapter, the implementation and measurement results of the 7b 12.8GS/s ADC test-chip is presented to demonstrate the effectiveness of these techniques. Chapter 3 focuses on the other aspect of ADCs: quantization. After a brief discussion of different quantizer (sub-ADC) architectures, the 2 popular types of SAR architecture (synchronous and asynchronous) are introduced. Meta-stability caused sparkle-code is extensively analyzed in the context of SAR ADC, and a new back-end meta-stability correction circuit to reduce sparkle-code error rate is propose. A statistical analysis and associated measurements are provided to demonstrate the effectiveness of the proposed correction technique. After the theoretical discussions and analysis, chapter 4 presents the detailed implementation and measurement results of the prototype 6b 46GS/s hierarchically time-interleaved ADC. Finally, chapter 4 concludes this thesis and provides a brief discussion of future works.

## **Chapter 2**

## **High Speed Sampling**

Sampling is the process that converts a continuous-time signal into discrete-time samples. The output samples of an ideal sampler exactly equals its input at the respective sampling instances. In reality however, a practical sampler usually suffers from finite bandwidth – i.e., the signal is low-pass filtered before the samples are taken. This can significantly attenuate signal amplitude at high frequencies. Random jitter in the sampling clock can move sampling instances away from its ideal position, which corrupts the samples for fast changing inputs. The sampler can also give rise to nonlinear distortion depending on its implementation.

In ultra-high-speed ADCs, sampler design is extremely challenging. As the sampling time  $(T_s)$  is reduce to approach the rise/fall time of digital gates, all practical sampler implementations fail. This can only be resolved by time-interleaving, which takes advantage of parallelism: many lower speed samplers take turns to sample the input, and together achieve high aggregate throughput. Even if the sampling rate of the samplers can be brought down significantly by time-interleaving, broad bandwidth must be maintained in each individual sampler. The following section starts the sampler study from the designs of ultra-high bandwidth sampling circuits.

### 2.1 Track-and-hold circuit

Electronic samplers are implemented by track-and-hold circuits. In CMOS processes, the most common way to build track-and-hold circuit is the single transistor switch, as shown in Figure 2.1a. Like digital latch circuits, track-and-hold circuits have two phases defined by high and low state of the sampling clock: a transparent phase (track time) and an opaque phase (hold time). A unity gain buffer usually precedes the track-and-hold switch. Although it requires static power consumption, this buffer is necessary in most ADC systems because it serves several important purposes: first, it reduces the kick-back effect to ADC input from the sampling clock. The rising or falling edge of the sampling causes a glitch at the input side of the sampling switch due to capacitive coupling by the parasitic gate to source/drain capacitance of the transistor. In fiber optic transceivers, this glitch may be reflected back-and-forth between the trans-impedance amplifier (TIA, usually reside in another chip in front of the ADC chip) and the ADC resulting in long-term post-cursor inter-symbol-interference (ISI). The workload of DSP must be increased to cancel this post-cursor, thus power consumption must be increased. Even without direct capacitive feedthrough from the sampling clock, the time-variant input capacitance of the sampling switch itself causes time-variant reflection coefficient at the ADC input. In addition to kick-back reduction, the buffer isolates the sampling capacitor from the ADC input, and reduces the input capacitances

of the ADC. Unlike low-speed counter parts, the input capacitances of ultra-high-speed ADCs must be very small in order not to limit the bandwidth. As mentioned earlier, the  $25\Omega$  equivalent input impedance and the ADC input capacitance form a low pass filter, and the cut-off frequency of the filter must be higher than the bandwidth to avoid high frequency attenuation. Furthermore, embedded ADCs are often proceeded by other circuits such as continuous-time linear equalizer (CTLE), variable-gain amplifier (VGA), etc. A large ADC input capacitance imposes stringent requirement on the driving capabilities of its preceding circuits, and causes significant increase in power consumption. In section 2.1.1, we start the discussion from analyzing issues of conventional switch-based track-and-hold circuit.

### 2.1.1 Switch-based track-and-hold

Figure 2.1 (a) Schematic and (b) small signal model of conventional T&H circuit

A conventional track-and-hold circuit (Figure 2.1) consists of a source follower buffer combined with a series sampling switch. As mention earlier, the front-end buffer is necessary to reduce kick-back and input capacitance. The final load capacitance  $C_L$  is thus driven by the sum of the output resistance of the source follower and the switch resistance. Even if bootstrapped [8] [9], the on-resistance of the sampling switch can be still a significant fraction of the total impedance seen by  $C_L$  for broadband designs. This series configuration of resistors makes the conventional sampling circuit very power-inefficient in high speed designs. In order to rigorously highlight this issue, we can use a small signal model (Figure 2.1b) to analyze the power-speed trade off.

To provide some quantitative insights, we will assume all NMOS's has the same  $f_T^1$  and the  $f_T$  of all the PMOS transistors is half that of the NMOS transistors, and that the ratio between  $C_{d,s}$  and  $C_g$  is 1 for all transistors. We will further assume (as is the case in most CMOS technologies nodes from 65nm down to 20nm) that the maximum triode  $g_{ds}$  of a transistor is roughly twice the maximum saturation  $g_m$ . With all of these assumptions combined, if  $f_T$  is the unity current-gain frequency of all the NMOS transistors, then  $g_{ds3}/C_{g3} = 2 \cdot 2\pi f_T$ . Finally,  $g_{ds3}$ is equal to  $g_{m1}$  for unity DC gain. Using first-order moment matching, the dominant pole of the conventional T&H circuit can be estimated as:

<sup>&</sup>lt;sup>1</sup> Although it is not strictly optimal for the current sources device  $(M_3)$  as  $f_T$  can be scaled larger with smaller size, the headroom limitation in low supply modern process usually limits the degree of its downsizing.

$$P_{1} \cong \frac{1}{\frac{C_{g1} + C_{s1} + C_{d3} + C_{d2} + C_{s2} + C_{g2} + C_{L}}{g_{m1}} + \frac{C_{L} + C_{d2} + C_{g2}/2}{g_{ds2}}}$$

(2.1)

Utilizing the assumptions as stated earlier, (2.1) becomes:

$$P_{1} = \frac{2\pi f_{T}}{\frac{15}{4} + 3\beta + \left(\frac{1}{2\beta} + 1\right)\frac{2\pi f_{T}C_{L}}{g_{m1}}}$$

(2.2)

Where  $\beta = W_2/W_1$  is the ratio of the widths of M<sub>2</sub> and M<sub>1</sub>. The dominant pole achieves its maximum value when  $\beta = 1/\sqrt{3g_{m1}/\pi f_T C_L}$ , and this optimal P<sub>1</sub> is:

$$\frac{P_1}{2\pi f_T} = \frac{1}{\frac{15}{4} + \frac{2\pi f_T C_L}{g_{m1}} + 2\sqrt{\frac{3}{2} \cdot \frac{2\pi f_T C_L}{g_{m1}}}}$$

(2.3)

Equation (2.3) relates the normalized bandwidth of the T&H,  $P_1/2\pi f_T$ , to the normalized trans-conductance of the source follower buffer,  $g_{m1}/2\pi f_T C_L$ . Since the trans-conductance is directly proportional to the static current consumption, equation (2.3) represents the speed-power trade-off of the T&H circuit. This trade-off curve is plotted in Figure 2.2. For low frequency designs ( $P_1 \ll 2\pi f_T$ ), the T&H power consumption scales linearly with bandwidth. As the design bandwidth approaches a significant fraction of  $f_T$  ( $P_1 \sim \frac{1}{10} f_T$ ), the trade-off quickly bends upwards, as increasingly more power is required for every small increment in bandwidth. This is due to capacitive self-loading of the source follower buffer and sampling switch, and the switch resistance penalty makes this trade-off extremely power inefficient. As the ADC bandwidth requirement approaches >20GHz, the switch-based sampler quickly becomes unviable.

Figure 2.2 The speed-power trade-off curves for (a) switch-based T&H circuit and (b) cascodebased T&H circuit

Although power inefficient, switch-based T&H circuit is widely used in medium/low speed applications. This is due to its excellent linearity performance. The source follower buffer can easily achieve >50dB spurious-free-dynamic-range (SFDR) over the entire bandwidth due to its inherent internal feed-back. Although charge injection, non-zero fall time, and voltage-dependent switch resistances, can cause sampling errors, the error voltages these effects create are for the most part linearly dependent on input voltage. Thus, they only cause a gain error to the first order, which can be easily fixed by gain calibration in the DSP. The slight higher-order dependence of these effects on input voltage is usually not significant enough to degrade SNDR for low to medium resolution ADCs.

### 2.1.2 Cascode-based track-and-hold

In order to mitigate the penalty caused by the series resistance of the sampling switch and hence improve the tradeoff between sampling speed and power consumption, we propose a cascode T&H circuit that merges the sampling operation into the buffer itself [10] [11]. A single-ended version of the proposed cascode T&H schematic and its equivalent small-signal model are shown in Figure 2.3. During the track phase when  $\Phi$  is high, M<sub>1,2,3</sub> form a cascode common-source amplifier, with in this case, the PMOS M<sub>3</sub> acting as a triode load resistor. It worth mentioning that the load device does not necessarily have to be PMOS, and as discussed later, a NMOS load device might be preferred depending on the design requirements. M<sub>1</sub> and M<sub>3</sub> are sized to provide a DC gain of ~1. During the hold phase when  $\Phi$  is low, both M<sub>2</sub> and M<sub>3</sub> are cut-off and the output voltage is held on  $C_L$ . The key advantage of this design is that as long as the cascode device (M<sub>2</sub>) operates in saturation and has sufficiently high  $f_T$  relative to the operating rate, the dominant pole of the circuit is set only by the output node resistance and capacitance. In other words, in contrast to the traditional sampling circuit, the addition of the sampling switch does not directly affect the settling time.

Similar to the analysis of switch-based T&H, we can use small signal models (Figure 2.3b) to estimate the dominant pole for the cascode T&H circuit:

$$P_1 = -\frac{g_{ds3}}{C_L + C_{d2} + C_{d3} + C_{g3}/2}$$

(2.4)

Using the earlier assumptions for switch-based T&H, (2.4) can be rewritten as:

$$\frac{P_1}{2\pi f_T} = \frac{1}{\frac{2\pi f_T C_L}{g_{m1}} + \frac{5}{2}}$$

(2.5)

With equation (2.5) in hand, we can plot the trade-off between  $g_m$  and the bandwidth for cascode-based T&H along with conventional T&H on the Figure 2.2. Notice that the advantage of the cascode sampler is most apparent when the circuit bandwidth approaches a significant fraction of  $f_T$  (but remains well below  $f_T$  so that the source node of the cascode is still relatively fast). Specifically, for  $P_1 = \frac{1}{8}f_T$  – which is ~30GHz in a typical 28nm process – the conventional sampler requires more than four times higher  $g_m$  (and hence power) than the proposed cascode sampler<sup>2</sup>.

Figure 2.4 Schematic of a 2x time-interleaved differential cascode T&H

As shown in Figure 2.4, a differential cascode-based T&H circuit also includes a tail current source device (M<sub>0</sub>) to reject input common mode variation. The example has 2 differential current branches (branch 0 and branch 1) to track the input signal in both high and low clock phases. For example, when  $\Phi$  is low,  $V_o(0)$  is held on the sampling capacitors, and branch 0 is disabled. During this inactive period of branch 0, the current of the differential pair is steered to branch 2 to enable it to track the input at  $V_o(0)$ . This way, 1-to-2 way de-multiplexing function can be implemented, and hence 2X higher sampling speed can be achieved without increasing static power consumption. In addition, utilizing the complementary clock phases can also keep the input capacitance of the T&H constant for both high and low clock phases. In general, 1-to-N demultiplexor (or N-way time-interleaved sampler) requires N cascode branches and N phases of non-overlapping clocks with 1/N duty-cycle. As the interleaving factor N grows large to achieve higher aggregate sampling rate, the metal routing to reach each sub-ADC also linearly increases

<sup>&</sup>lt;sup>2</sup> This analysis is based on schematic simulation. The parasitic in post-layout usually makes the advantages of cascode-based T&H circuit even greater.

as the pitch of each sub-ADC is fixed by the technology and its load capacitance. Even if top metal layer is used for routing, it may still cause significant parasitic capacitance – in some cases it can be even larger than the sampling capacitors. The buffer of the conventional switch-based T&H circuit must drive this parasitic capacitor as well as the sampling capacitor, thus making it even more power inefficient. In contrast, this parasitic capacitor is naturally mitigated in the cascode-based T&H circuit, because the metal routing is connected to the low impedance source nodes of the cascode devices (M<sub>3,4,7,8</sub>) and results in the 2<sup>nd</sup> pole at:

$$P_2 = \frac{g_m}{N \cdot C_d + C_g + C_p} \tag{2.6}$$

Where  $g_m$ ,  $C_g$ , and  $C_d$  are the trans-conductance, drain junction, and gate capacitances of the cascode devices;  $C_p$  is the parasitic capacitances of the wire routing. Using the assumption stated as the beginning of this section, equation (2.6) becomes:

$$P_2 = \frac{f_T}{N + \frac{C_w}{g_m}} \tag{2.7}$$

To guarantee sufficient settling time or tracking bandwidth, the second pole must be larger than the first pole,  $P_1 \gg P_2$ . Given a technology, this would require  $g_m$  to be sufficiently high, and Nto be not too large. When designing a cascode-based T&H circuit, we suggest start from equation 2.5 to calculate  $g_m$  for a given load capacitor. Assuming the casocde device has the same size of the differential pair, equation 2.7 can be used to obtain maximum interleaving factor (or demultiplexing factor) per T&H circuit.

### 2.1.3 Mitigation of non-idealities in T&H circuits

Other than tracking bandwidth and settling time, practical switch-based T&H circuits are also affected by many non-ideal buffer and switch behaviors, such as nonlinear distortion, charge injection, clock and hold-time signal feedthrough. Similarly, the cascode-based T&H circuit also faces their issues. In some cases, the device non-idealities can cause more severe problems in cascode T&H than the switch T&H. In this section, we will analyze these non-ideal behaviors in the context of cascode-based T&H circuit and discuss methods to mitigate these issues.

Figure 2.5 Schematic and functional block diagram of cascode samplers with (a) triode PMOS load, and (b) saturation NMOS load

Figure 2.6 Input of a differential pair vs. (a) normalized trans-conductance and (b) HD<sub>3</sub> for different over-drive voltages

First, the speed advantage of the cascode sampling structure does not come without expense. In particular, while in the conventional switch-based design linearity is significantly improved by the internal feedback of the source follower circuit, the cascode T&H with PMOS load illustrated in Figure 2.5a is an open loop structure, and thus suffers from distortion due to inherent nonlinearity of MOSFET devices. Since  $g_{ds}$  of the triode PMOS loads  $M_{3,4}$  is as a fairly constant conductance, the dominant source of non-linearity is  $g_m$  of the differential pair  $M_{1,2}$ . Thus, one can simply examine the transfer characteristics of a differential pair to predict the distortion of the cascode T&H circuit. As shown in Figure 2.6a, the variation in large-signal  $G_m$  with large differential input amplitude gives rise to third-order distortion (HD<sub>3</sub>). Assuming only HD<sub>3</sub> is present – which is a good approximation for differential circuit with moderate signal swing – the large-signal  $G_m$  can be modeled as a function of input voltage:

$$G_m = G_{m0} - \frac{\Delta G_m}{V_{sw}^2} \cdot V_{in}^2$$

(2.8)

Where  $V_{sw}$  is the peak differential input swing,  $G_{m0}$  is the trans-conductance at  $V_{in} = 0$  – the same as small-signal  $g_m$ , and  $\Delta G_m$  is the change in trans-conductance as the input increases from 0 to the peak swing. For a sinewave input with amplitude  $V_{in,diff}$ ,  $V_{in} = V_{in,diff} \sin(\omega t)$ , the large signal output current is:

$$I_{od} = G_{m0} \cdot V_{in,diff} \sin(\omega t) - \Delta G_m \cdot V_{in,diff}^2 \sin^3(\omega t)$$

(2.9)

Thus, the differential output voltage is:

$$V_{od} \approx \frac{1}{g_{ds}} \left[ G_{m0} \cdot V_{in,diff} \sin(\omega t) - \Delta G_m \cdot V_{in,diff}^2 \sin^3(\omega t) \right]$$

(2.10)

Using Equation 2.10, the HD<sub>3</sub> caused by input-dependent large-signal  $G_m$  can be approximated as:

$$HD_3 \approx 20 \cdot \log_{10} \left( \frac{\Delta G_m}{4G_{m0}} \right)$$

(2.11)

According to Equation 11, the HD<sub>3</sub> of the cascode T&H is directly related to the percentage deviation of the large-signal trans-conductance at the amplitude from the small-signal  $g_m$ . The normalized trans-conductance of a differential pair  $(G_m(V_{in,diff})/G_{m0})$  vs. differential input amplitude  $(V_{in,diff})$  curves for different overdrive voltages for a 28nm technology are shown in Figure 2.6a. As the input swing becomes smaller, the deviation of its full-swing  $G_m$  from its peak value  $G_{m0}$  is reduced. Thus, a straightforward way to improve HD<sub>3</sub> is to reduce input swing at the expense of reduced signal-to-noise ratio (SNR). With a given input amplitude, one also has the option to reduce the HD<sub>3</sub> by increasing the overdrive voltage,  $V_{ov}$ . However, increasing  $V_{ov}$  has the side effects of reducing power efficiency and output headroom. To design a cascode sampler, one has to carefully choose  $V_{in,diff}$  and  $V_{ov}$  to satisfy the HD<sub>3</sub> requirement. In a typical 28nm process, with a  $V_{ov}$  of 350mV for the input transistors and a moderate  $V_{in,diff}$  of ~200mV (peak-to-peak voltage swing of 400mV), the HD<sub>3</sub> is well below -40dBc, which is sufficient for a 6-bit design. An attractive feature of using triode PMOS load is that the voltage drop across the load can be quite small. Therefore, to keep a stack of only three transistors (M<sub>0,1,3</sub>/M<sub>0,2,4</sub>) in saturation, core supply voltage (~1V) can be used to reduce power.

In addition to using brute force to reduce HD<sub>3</sub>, a more sophisticated way is to replace the switched triode PMOS load in the cascode T&H with switched saturation NMOS load, as shown in Figure 2.5b. As long as  $M_{5,6}$  is matched to  $M_{1,2}$ , the nonlinear output current produced by the large-signal  $G_m$  of  $M_{1,2}$  is inverted by the same large-signal  $G_m$  of  $M_{5,6}$ . In reality, although  $g_{ds}$ -modulation, device mismatch, and body-effect limits the achievable HD<sub>3</sub> in this circuit, simulation has shown it has at least 8dB better linearity than triode PMOS laod. Additional benefit of using cascode T&H with saturation NMOS loads are better supply rejection ratio and less clocking power consumption due to single-phase clock. To keep all transistors in saturation and reduce the effect of  $g_{ds}$ -modulation over the entire output swing, a high supply voltage of 1.6V is required. In addition, the gate voltage  $V_g$  of the NMOS load and the cascode switch must be level shifted above 1V to keep the cascode devices in saturation; chapter 3 will discuss details on how to level-shift  $V_g$ 's to appropriate levels. When the cascode T&H with NMOS load is used as the front-end T&H circuit, one must pay special attention to frequency-dependent effects of HD<sub>3</sub>. As shown in

Figure 2.7, although nonlinearity inversion by the NMOS loads greatly improve HD<sub>3</sub> at very low frequency, the HD<sub>3</sub> may quickly degrades as frequency increases. This dependence causes a bowlshaped HD<sub>3</sub> curve, and the worst-case HD<sub>3</sub> is slightly lower than  $1/3 \cdot BW$ . This can be intuitively understood as frequency increases, the impedance of the load capacitor becomes smaller, and more output current is shunted into the load capacitor. The part of output current shunted into the load capacitor does not get inverted by the matched NMOS load, and thus raising HD<sub>3</sub>. As the frequency increases beyond  $1/3 \cdot BW$ , the HD<sub>3</sub> is higher than the T&H BW and gets filtered out by the inherent low-pass filter. Since this distortion term has memory effect, analyzing it mathematically requires to invoke Volterra series expansion, therefore can be cumbersome. To study the effect of frequency dependent linearity reduction for the cascode T&H with NMOS load, large signal transient simulations are used. As shown in Figure 2.7, with 200mV peak amplitude and 350mV overdrive voltage, the cascode T&H with NMOS load achieves >-40dB HD<sub>3</sub> over the entire bandwidth. At this point, it worth pointing out that the rank-2 and rank-3 sample-and-hold circuits in a hierarchically time-interleaved sampling network track the output of front-end (rank-1) T&H – a constant voltage during the entire tracking phase, which will be discussed in the next section. As long as the output voltage of these circuits settles, the HD<sub>3</sub> does not degrade from this . Therefore, cascode T&H circuit with NMOS load can be used to achieve its full linearity potential as analog de-multiplexors after the signal is sampled.

Figure 2.7 Normalized input frequency vs. HD<sub>3</sub> for a 400mV peak-to-peak input sinewave and different overdrive voltages (V<sub>ov</sub>)

Figure 2.8 Illustration of charge injection and clock-feedthrough in cascode-based T&H with (a) triode PMOS load and (b) saturation NMOS load

In addition to linearity issues, just like conventional switch-based T&H, the "top plate sampling" used by the cascode T&H is prone to signal-dependent noise, and we need to analyze issues such as charge injection and clock/signal feed-through and make sure their effects do not degrade the SNDR. In the case of conventional sampling circuit, inversion charge in the sampling switch can flow to the sampling node when the switch is opened, causing signal-dependent voltage error [12]. Fortunately, such problem does not exist in cascode T&H with triode PMOS load to the first order. Since the cascode devices  $M_{3,4}$  are in saturation during track time (Figure 2.8a), their channels are "pinched off" at the drain nodes (output nodes). Most of inversion charges will inject into the source node because they are distributed close to the source node [13]. Therefore, the inversion charges in M<sub>3,4</sub> do not affect the sampled output voltage when the they are turned off. The only remaining potential source of charge injection error in the cascode sampler circuit is from the triode PMOS loads. Although some of the signal-dependent inversion charge in these devices will transfer to the output when they are turned off, this effect does not necessarily degrade SNDR. Specifically, the linearly dependent inversion charge merely causes a gain error; it is only the nonlinearly dependent inversion charge that gives rise to distortion. Fortunately, as verified by SPICE simulations, this nonlinearly dependent portion of the inversion charge in the PMOS loads is not significant enough to be a concern for medium resolution designs.

On the other hand, the problem of clock feed-through in cascode T&H with PMOS load is similar to conventional T&H. The single-end output voltage change caused by clock feed-through is:  $\Delta V_o = (-V_{t,n}C_{gd,n} + V_{t,p}C_{gd,p})/C_L$ . This is merely a common-mode shift and do not cause SNDR degradation if the threshold and C<sub>gd</sub> of transistors are constant. To make things better, the PMOS load and NMOS cascode devices are drive by opposite clock phases, and the feedthrough effects from these devices partially cancel each other. The resulting common-mode shift is usually too small to cause any problem for the circuits it drives. In reality, the slight signal-dependence in threshold voltage and C<sub>gd</sub> can slightly degrade SFDR, but this dependence is so small that it does not cause any linearity problem for medium resolution ADCs. This is verified with SPICE simulation. Similarly, the cascode devices M<sub>3,4</sub> in cascode T&H with saturation NMOS load do not inject charges to the output (Figure 2.8b). However, nearly all channel charges in the NMOS load flows to the output at the falling edge of the clock. Although this charge injection might not cause significant distortion, the resulting T&H gain attenuation is more severe than the triode PMOS load. The differential voltage error caused charge injection of the NMOS loads is approximately  $\Delta V_o = -C_{gs}/C_L \cdot V_{in}$ . For very high speed designs,  $C_L$  can be as small as  $C_{gs}$  of the load devices, so charge injection may cause quite a lot signal attenuation. One way to alleviate this issue is to add dummy switches at the output to suck out the injected charges, but doing so adds more capacitance at the output load and reduce the bandwidth. A simple but effective approach is to increase the gain during track time by slightly reducing the width of load NMOS to compensate the attenuation caused by charge injection. To design the cascode T&H with NMOS load, its T&H gain must be verified by transient simulation.

Figure 2.9 Illustration of signal-feedthrough issue in cascode T&H (a) without and (b) with feedthrough cancellation

Figure 2.10 Layout of cascode NMOS (a) with large  $C_{ds}$  and (b) with minimum  $C_{ds}$

Figure 2.11 (a) Schematic of cascode T&H with replica MOM  $C_{ds}$  feedthrough cancellation (b) the layout of the replica MOM  $C_{ds}$

Another problem in T&H circuit is the hold-time signal feed-through caused by capacitive coupling from the source nodes of  $M_{3,4}$  (X<sub>+,-</sub>)and the output nodes (V<sub>0+,0-</sub>) through C<sub>ds</sub> when the sampler is in hold mode (Figure 2.9a). The magnitude of this error is proportional to  $\frac{c_{ds}}{c_L}$ . This is a well-known issue of the time-interleaved ADCs with top-plate sampling structure. A common solution is to cancel the feed-through by adding dummy transistors that cross couple  $X_{+,-}$  and  $V_{0+,-}$ , as shown in Figure 2.9b [14]. However, the drain/source junction capacitance added by the dummy transistors in this approach can reduce the speed of the sampler. To mitigate the effect of signal feed-through without sacrificing speed, we introduce 2 feed-though reduction methods that take advantage of advanced layout. First, we can directly reduce C<sub>ds</sub> by appropriately laying out the devices [11], [15]. In particular, instead of the typical layout shown in Figure 10a, one can minimize the overlap between the source/drain contacting regions as shown in Figure 10b. The only downside of this layout strategy is increased contact resistance to the source/drain, but in many designs/processes, the resulting effect on the bandwidth of the buffer is negligible. Postlayout simulations indicate that this layout technique achieves a more than 10X reduction of Cds. If increasing contact resistance is not tolerable or the design rule does not allow Metal-1 drain/source stripes to have unequal length, one can also use fringe capacitor made by replica Metal-1 stripes instead a dummy transistor to cancel feed-though (Figure 2.11b). This replica Cds mimics the actual transistor C<sub>ds</sub> without adding parasitic drain/source to bulk/gate capacitance. Although the replica Metal-1 capacitor may not exactly match C<sub>ds</sub> of the transistor due to the fringing field from Metal-1 to polysilicon gate, the amount of reduction by this approximate  $C_{ds}$  is usually more than enough for the 6-bit design.

To demonstrate effectives of cascode samplers, a 7b 12.8GS/s ADC with PMOS loadtest chip is fabri

## 2.2 Hierarchical time-interleaving

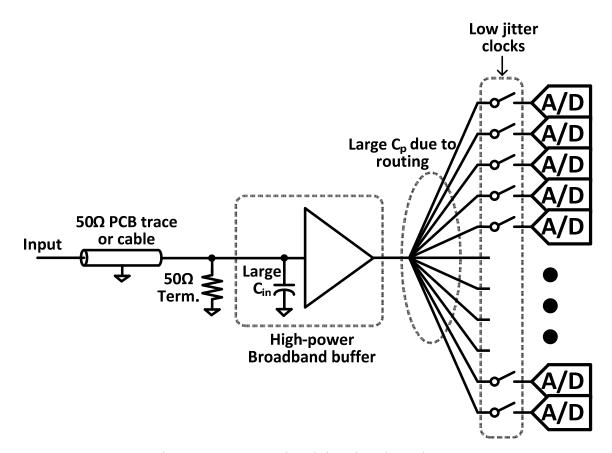

Figure 2.12 Conventional time-interleaved ADC

As mentioned earlier and highlighted in Figure 2.12, the conventional time-interleaved ADC consists of a broadband input buffer that drives many parallel sampling switches followed by sub-ADCs. 3 issues make this structure infeasible for ultra-high-speed designs. First, since all the sampling switches directly sample the continuous changing analog output of the buffer, jitter in all the sampling clocks may translate into sampled voltage error, therefore degrading SNR at high frequencies. For example, to limit jitter induced noise below the quantization noise level for a 6bit 50GS/s ADC at Nyquist, the sampling clock jitter must be below 81fs. To meet such stringent jitter requirement, many stages of large CMOS gates (often >10um in width) must be used to distribute the sampling clocks in order to reduce added jitter and to keep sharp sampling edges for better supply noise rejection. As a result, excessive amount of power is spent just to distribute these many sampling clocks across a long distance to reach the sub-ADCs. Second, the cluster of routing at the output node of the buffer adds a large parasitic capacitor in addition to the parasitic capacitors of the large number sampling switches. In many cases, the total parasitic capacitance at the output of the buffer can be orders of magnitude larger than the input capacitor of the sub-ADCs. Therefore, in order to maintain the ADC bandwidth, lots of power in the buffer is wasted to drive these "useless" parasitic capacitors. At last, the large-size broadband input buffer may have a large input capacitor, and the low-pass filter formed by the input capacitor of the buffer and the equivalent input resistance adds a 2<sup>nd</sup> pole in addition to the pole caused by the track-and-hold

circuits, which further reduces the ADC bandwidth. In a standalone ADC module, the input resistance is limited by the termination resistance and characteristic impedance of the transmission line of the PCB trace or the cable, which is usually 250hm (500hm in parallel with 500hm). For a Nyquist rate 50GS/s ADC, if the T&H circuit (buffer with the sampling switches) is designed to have a pole at 30GHz, the total ADC input capacitor including the input capacitor of the buffer and ESD capacitor (if any) must be < 83fF to maintain the overall ADC bandwidth above 25GHz. This is an extremely stringent requirement. In the case of embedded ADCs, the ADC is proceeded by driver circuits such as TIA and CTLE. In this case, the input pole is formed by the input capacitor of the buffer input capacitance imposes extremely stringent requirement on the driver circuits, and can make the overall system solution infeasible.

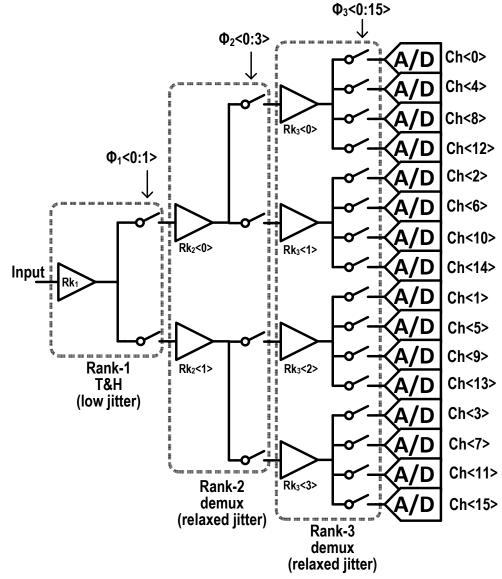

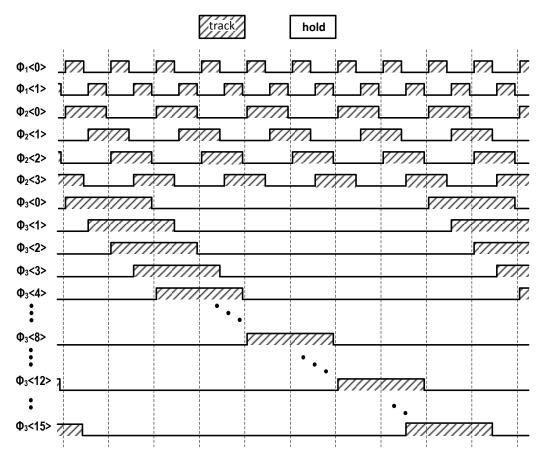

Figure 2.13 Block diagram of a 3 rank hierarchically time-interleaved ADC

Figure 2.14 Timing diagram of a 3 rank hierarchically time-interleaved ADC

An elegant way to alleviate all these issues is hierarchical time-interleaving [4], [14], [11], [15], [10], [16], [17], [18], [19]. An example design adopting a hierarchical time-interleaving approach is shown in Figure 2.13. Figure 2.14 illustrates its timing diagram. The example has 3ranks of samplers and a total of 16 sub-ADC channels. The rank-1 T&H circuit (Rk-1) is 2-way time-interleaved in order to reduce the number of required low-jitter clocks that needs be generated and distributed. Once the continuously changing input voltage is sampled and held by rank-1 T&H, the output of this circuit is a constant voltage during the entire hold time. Thus, any perturbation of sampling clock edges at the Rank-2 sampler ( $\Phi_2(0:3)$ ) do not directly translate into voltage errors as long as it is within this hold window, allowing the jitter requirements for the Rank-2 and subsequent ranks of samplers to be greatly relaxed. As a result, the only jitter-critical clock in the entire sampler system is the 2 sampling clocks of the font-end sampler,  $\Phi_1$ . An additional benefit of hierarchical sampling is the greatly reduced signal routing at the output of the front-end buffer; since it can limit the input bandwidth of the entire ADC, the bandwidth of this buffer is critical. As opposed to conventional time-interleaved ADCs where the input buffer must fan-out to all sub-ADCs (in this example, 16 sub-ADCs), the front-end sampler drives only the next rank (Rk-2) of samplers/de-multiplexors (in this case, a single Rank-2 demux.), thus substantially reducing the parasitic capacitance at the output of the frond-end sampler. Furthermore, by utilizing a small interleaving factor at the front-end, the errors caused by sampling time mismatch between subsequent sub-channels are almost entirely removed (as long as the intermediate stages settle), eliminating the amount of sampling clocks that require precise timing calibration [18]. As shown

in Figure 2.14, the duty-cycle of sampling clocks for rank-2 and rank-3 ( $\Phi_2\langle 0:3 \rangle$  and  $\Phi_3\langle 0:15 \rangle$ ) are set such that only 1 interleaved switch following the inter-rank buffer is closed at any given time. For example, the sampling clocks associated with sampler Rk<sub>3</sub>(0) –  $\Phi_3\langle 0 \rangle$ ,  $\Phi_3\langle 4 \rangle$ ,  $\Phi_3\langle 8 \rangle$ , and  $\Phi_3\langle 12 \rangle$  – are non-overlapping clocks with 25% duty-cycle. This 25% duty-cycle clocking scheme for  $\Phi_3$  is the most efficient because each Rk-3 buffer "sees" only 1 sub-ADC at a time instead of 2 sub-ADCs if 50% duty-cycle clock is used. Thus, the driving capability (g<sub>m</sub>) of Rk-3 buffer in the case of 25% duty-cycle clock can be made 2X smaller than the case of 50% duty-cycle clock. Note the duration of track time becomes longer as the analog signal propagates from Rk<sub>1</sub> to subsequent ranks. Therefore, the settling requirement for later ranks can be greatly relaxed to save power. The next section will provide a detailed analysis on how to size the T&H at each rank according to the settling time requirement for minimum power.

### 2.2.1 Optimization of hierarchical sampling network

Figure 2.15 Block diagram of a general N-rank hierarchically time-interleaved ADC

In this section, we develop a general method to optimize the sizes of the T&H circuits and the sampling capacitors for a cascode sampler network with a fixed sampling hierarchy (i.e. fixed number of ranks and branching factors at each rank). Assuming the sampling network has N ranks and each sampler at Rk-i fans out to  $m_i$  branches (Figure 2.15) and the non-overlapping clock scheme, the available settling time at each rank,  $T_i$ , can be calculated as a function of sampling rate of the overall ADC,  $f_s$ , and  $m_i$ 's:

$$T_{i} = \begin{cases} \frac{1}{m_{1}m_{2}f_{s}} & (i \leq 2) \\ \left(\prod_{2}^{i-1}m_{k} - \prod_{1}^{i-2}m_{k}\right)\frac{1}{2f_{s}} & (i > 2) \end{cases}$$

(2.12)

As shown in Section II, the dominant pole of the cascode sampler is its output pole, so if the DC gain is one and the settling error is set to be  $\varepsilon$ , the settling constraint at Rank-i is:

$$\frac{T_i}{\ln(\varepsilon)} = \frac{C_{total,i}}{g_{m,i}}$$

(2.13)

where  $g_{m,i}$  and  $C_{total,i}$  are the trans-conductance and total load capacitance of Rank-i, respectively. In addition to the settling time constraint, the front-end sampler also has to meet the overall ADC bandwidth requirement:

$$\frac{1}{2\pi f_B} = \frac{C_{total,1}}{g_{m,1}}$$

(2.14)

Where  $f_B$  is the ADC bandwidth. Combining (1), (2), and (3) results in:

$$\frac{\mathcal{C}_{total,i}}{g_{m,i}} = \tau_i' \qquad (2.15)$$

where:

$$\tau_{i}' = \begin{cases} \min\left(\frac{1}{\ln(\varepsilon)} \cdot \frac{1}{2m_{1}m_{2}f_{s}}, \frac{1}{2\pi f_{B}}\right) & (i=1) \\ \frac{1}{\ln(\varepsilon)} \cdot \frac{1}{2m_{1}m_{2}f_{s}} & (i=2) \\ \left(\prod_{2}^{i-1}m_{k} - \prod_{1}^{i-2}m_{k}\right) \cdot \frac{1}{\ln(\varepsilon)} \cdot \frac{1}{2f_{s}} & (i>2) \end{cases}$$

(2.16)

The total input referred noise must be less than the ADC noise budget to avoid SNDR degradation. The sampled noise power at the output of Rank-i is:

$$\overline{V_{n,i}}^2 = \frac{NF \cdot kT}{C_{total,i}}$$

(2.17)

Substituting (4) in to (6),

$$\overline{V_{n,i}}^2 = \frac{NF \cdot kT}{\tau_i'} \cdot \frac{1}{g_{m,i}}$$

(1.18)

where *NF* is the effective noise factor of the cascode sampler. The total input referred noise of the sampler network can be written as a dot product, and the sampler noise constraint becomes:

$$\overline{V_{n,in}}^2 = NF \cdot kT \begin{bmatrix} \frac{1}{\tau_1'} & \dots & \frac{1}{\tau_N'} \end{bmatrix} \cdot \begin{bmatrix} \frac{1}{g_{m,1}} \\ \vdots \\ \frac{1}{g_{m,N}} \end{bmatrix} \le N_B$$

(1.19)

where  $N_B$  is the budget for thermal and flicker noise. Since sampling capacitors are added to reduce the thermal noise, an additional constraint must be imposed on these capacitors.  $C_{total,i}$  is

the sum of the output capacitance of Rank-i, the added sampling capacitance  $(C_{L,i})$ , and the input capacitance of Rank-i+1:

$$C_{total,i} = \frac{\gamma \cdot g_{m,i}}{f_T} + C_{L,i} + \frac{g_{m,i+1}}{f_T}$$

(1.20)

Where  $\gamma$  is the ratio between the output capacitance and the input capacitance<sup>3</sup>. Substituting (9) into (4) results in:

$$C_{L,i} = \left(\tau_{i}' - \frac{\gamma}{f_{T}}\right) g_{m,i} - \frac{1}{f_{T}} g_{m,i+1}$$

(1.21)

With the help of matrix formulation, the dependence of  $C_{L,i}$  on  $g_{m,i}$  for all the ranks in the sampler network described in (10) can be written in one equation:

$$\begin{bmatrix} C_{L,1} \\ C_{L,2} \\ \vdots \\ C_{L,N-1} \\ C_{L,N} \end{bmatrix} = \begin{bmatrix} \tau_1'' & -1/f_T & \cdots & 0 \\ 0 & \tau_2'' & \cdots & 0 \\ \vdots & \ddots & \vdots \\ 0 & \cdots & \tau_{N-1}'' & -1/f_T \\ 0 & \cdots & 0 & \tau_N'' \end{bmatrix} \cdot \begin{bmatrix} g_{m,1} \\ g_{m,2} \\ \vdots \\ g_{m,N-1} \\ g_{m,N} \end{bmatrix} \ge \begin{bmatrix} 0 \\ 0 \\ \vdots \\ 0 \\ C_{SAR} \end{bmatrix}$$

(1.22)

where  $\tau_i'' = \tau_i' - \frac{\gamma}{f_T}$ . The inequality in (10) describes the fact that the additional sampling capacitances must be greater than zero, except for the sampling capacitor of the last rank which needs to be larger than the input capacitance of the SAR ADC. Finally, the total power of the sampler network is proportional to the sum of the  $g_m$ 's of all the samplers in the network:

$$Power \propto \begin{bmatrix} m_1 & \cdots & \prod_{1}^{N-2} m_k & \prod_{1}^{N-1} m_k \end{bmatrix} \cdot \begin{bmatrix} g_{m,1} \\ \vdots \\ g_{m,N-1} \\ g_{m,N} \end{bmatrix}$$

(1.23)

With equations (8), (11), and (12), the overall optimization can now be formulated as:

$<sup>^{3}</sup>$  The C<sub>g</sub> of a transistor can have a slight dependence on overdrive voltage, C<sub>g</sub> is usually not directly related V<sub>ov</sub>. Therefore,  $\gamma$  also have some dependence on V<sub>ov</sub>. In this analysis, a constant V<sub>ov</sub> is assumed.

<sup>&</sup>lt;sup>4</sup> inv\_pos(x) is defines as 1/x, where x>0.

where  $\overline{g_m} = \begin{bmatrix} g_{m,1} \\ \vdots \\ g_{m,N} \end{bmatrix} > 0$  are the variables to be optimized. Since the cost function and the constraints are convex functions of  $\overline{g_m}$ , a convex optimization algorithm can be used [20].

When designing high speed hierarchically time-interleaved ADC with a power constraint, I recommend to start from sub-ADC design. The speed of SAR sub-ADC determines the minimum overall interleaving factor of the sampler. Once the input capacitances and maximum sampling rate of sub-ADC are obtained, different sampling hierarchies can be explored with the power optimization method developed in this section to find the configuration(s) that yields the lowest sampler network power consumption. Note that the power consumption of clock generation and distribution network is not taken into account in this optimization method. Therefore, the designer must make intelligent decision to pick the most feasible sampling network configuration with consideration of clocking power in mind. I recommend to go through the designs of clock distribution network for several feasible sampler hierarchies and find the solution with lowest overall power consumption.

## 2.3 Implementation and measurement results of the 7b 12.8GS/s ADC

To demonstrate the effectiveness of cascode T&H circuits and hierarchical time-interleaving, a 7b 12.8GS/s ADC is implemented in a 65nm CMOS process [10], [11] (Figure 2.16). The ADC consists of 3 ranks of sampler with a single front-end (Rk-1) T&H circuits to reduce ADC input capacitance and jitter-critical sampling clocks. A single Rk-2 samplers/demultiplexers demultiplexes the fall-rate samples into 4 time-interleaved samples at 3.2GS/s. 4 Rk-3 samplers/demultiplexers further bring down the sample rate to 400MS/s - the rate of sub-ADCs. Finally, the 32 SAR sub-ADCs converts the analog samples into digital codes. Note that only 1 out of the 37 clocks ( $\Phi_1$ ) is jitter critical and requires power hungry drivers. Thus, small size CMOS gates are used to distribute the rest of the clocks. The phase-interpolators (PI) and frequency dividers (FD) are used to generate all the required sampling clocks. The details of their implementation will be discussed in chapter 4. The cascode T&H circuits with PMOS loads are used to implement the T&H circuits. Figure 2.17a shows ADC output amplitude versus the input frequency, and Figure 2.17b shows the measured SNDR. Despite the relatively low  $f_T$  of the process, the ADC achieved 25GHz effective resolution bandwidth (ERBW) thanks to the casode sampling circuits. To the best of the author's knowledge, it achieves the highest ERBW among published CMOS ADCs. Thanks to hierarchically time-interleaved architecture, the power optimized ADC achieves the effective number of bits (ENOB) of 4.2 at 25GHz while consuming only 168mW. The figure-of-merit (FOM) is 0.79pJ/conversion-step.

Figure 2.16 Block diagram of the 7b 12.8GS/s ADC in 65nm CMOS

Figure 2.17 the input frequency vs. (a) normalized output amplitude, and (b) SNDR of the 7b 12.8GS/s ADC

# **Chapter 3**

# **High-speed power-efficient sub-ADC**

As mentioned earlier, the sub-ADC design is extremely important because it determines the overall interleaving factor of the sampler and have a large impact on overall ADC power. In ADC designs with a high degree of interleaving, the power consumption, the area, and the input capacitance of sub-ADCs must be carefully considered. The importance of sub-ADC power is perhaps self-evident, but sub-ADC area can be equally important since a large sub-ADC implies longer wiring to route the inputs and clocks. These long wires can lead to significant parasitic loading and hence substantially increased sampler/clock distribution power. Similarly, the input capacitance of sub-ADCs are the loads for last rank de-multiplexors. Thus, large sub-ADC input capacitance can raise the power consumption of the entire sampling network.

The common sub-ADC candidates are flash, pipeline, single/dual slope, and SAR ADCs. Although flash architecture has the potential to achieve high speed [21] [22] [5] [23], it requires at large number of comparators for medium resolution ADCs - 63 comparators for a 6-bit sub-ADC - resulting in large area and input capacitance. Conventional pipeline ADCs can have a much smaller input capacitance, but due to the numerous analog residue amplifiers needed in the design, both their area and power efficiency are poor [6]. Although novel techniques such as ringamplifier based pipeline architectures [24] [25] [26] can achieve extremely high figure-of-merit (FOM) and small area, they suffer from limitations of large dead-zone induced noise and low sampling speed. As a result, pipeline architectures are not suited for sub-ADC designs in ultrahigh-speed ADCs with medium resolution. Another architecture that has gained lots of attention in recent years is the single/dual slope ADC. Based on the linear search algorithm, it converts the signal voltage into a time delay using a voltage to time converter, and then counts the number of pulses from a reference clock cycles that passed within the delay. Although single/dual slope ADCs [27] can achieve very good power and area efficiency at low sampling rate, it quickly run out of steam for medium to high speed designs. For example, a 6-bit 1GS/s single/dual slope ADC requires a 64GHz reference clock, which is infeasible to implement with even 28nm CMOS logic gates. Unlike single/dual slope ADCs, SAR ADC is based on binary search algorithm, and thus is able to run much faster [28]. Although SAR ADC is usually slower than pipeline or flash, it does not have any analog components. Therefore, SAR can achieve high power efficiency. In addition, the input capacitance and area of a SAR are limited by the size of capacitive digital-to-analog converter (CDAC), and can be made extremely small thanks to modern CMOS process with fine pitch and tall metal stack [29]. Due to these reasons, SAR ADC is an ideal candidate for sub-ADC designs in a massively time-interleaved ADC system.

## 3.1 SAR sub-ADC

Figure 3.1 Illustration of the conversion algorithm for a 6-bit SAR ADC

As mentioned earlier, SAR ADCs use the binary search procedure. Take a 6-bit SAR ADC for example (Figure 3.1), the most-significant-bit (MSB) – D<5> in this case – is first obtained by comparing the input voltage to the half-scale voltage,  $\frac{1}{2}V_{fs}$ . Depending on the result of MSB, the reference level is moved up or down by a quarter of full-scale,  $\pm \frac{1}{4}V_{fs}$ . Then, the next bit, D<4>, is decided by comparing the input voltage to the new reference voltage. Based on the decision of D<4>, the reference level is moved by  $\pm \frac{1}{8}V_{fs}$ . This process is repeated for 4 more times with a smaller change in the reference level each time to complete conversion. Note that 6 comparison cycles – also known as bit-cycles – are needed for 6-bit SAR ADC, and after the initial setting to half-scale, the reference level is moved 5 times. The difference between input level and reference level is reduced by a factor of 2 after each cycle, and the residue difference at the end of SAR conversion represents the quantization error.

#### 3.1.1 Synchronous and asynchronous SAR

Figure 3.2 (a) schematic and (b) time diagram of a 6-bit synchronous SAR ADC

The implementation of a 6-bit synchronous SAR ADC (Figure 3.2a) consists of 4 basic building blocks, a sampler, a capacitive digital-to-analog converter (CDAC), a comparator, and a state machine. Since the sampler in this case is the cascode T&H circuit of the last rank which has been thoroughly studied in Chapter 2, it will not be discussed here. As mentioned earlier, metal-to-

metal fringe capacitors in advanced CMOS processes have high capacitance density and extremely well-controlled matching – usually lower than 2% variation for 1fF unit size capacitors. Thus, small size capacitor digital-to-analog converter (CDAC) is almost always used to save power. The SAR ADC in Figure 3.2a uses a 5-bit binary weighted CDAC to move reference levels across  $V_{fs}$ . Since the MSB decision is the sign bit, it can be decided without changing the state of the CDAC. Thus, 5-bit CDAC – instead of 6-bit CDAC – is sufficient for this 6-bit SAR ADC design. As shown in Figure 3.2b, The conversion time is evenly divided into 6 bit-cycles by a digital counter triggered by rising edge of a high frequency "bit-cycling" clock  $\Phi_{BC}$ . The 6 bit-cycles are represented by the 6 states of the counter, S(5: 0). Only 1 out of 6 S(5: 0) can be high at a time. From the start of the SAR conversion, S(5: 0) are pulsed sequentially from S(5) to S(0). The asserted counter output, S(i), represents the active bit-cycle at the time.

Figure 3.3 (a) Schematic of a typical Strongarm comparator, and (b) its output waveforms