# Lawrence Berkeley National Laboratory

LBL Publications

Title

Production and testing of the powerboard for ATLAS ITk Strip barrel modules

Permalink

https://escholarship.org/uc/item/29z5k272

Journal

Journal of Instrumentation, 18(01)

**ISSN**

1748-0221

Authors

Haber, C

Heim, T

Kelly, S

<u>et al.</u>

Publication Date

2023

DOI

10.1088/1748-0221/18/01/c01043

Copyright Information

This work is made available under the terms of a Creative Commons Attribution-NonCommercial License, available at  $\frac{https://creativecommons.org/licenses/by-nc/4.0/}{https://creativecommons.org/licenses/by-nc/4.0/}$

Peer reviewed

TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS - TWEPP2022 19 - 23 SEPTEMBER, 2022 BERGEN, NORWAY

# Production and Testing of the Powerboard for ATLAS ITk Strip Barrel Modules

C. Haber, T. Heim, S. Kelly, K. Krizka and Z. Zhang A.1

<sup>a</sup>Lawrence Berkeley National Laboratory, Berkeley, CA 94720, USA

E-mail: zhicai.zhang@cern.ch

ABSTRACT: The upgrade of the ATLAS ITk strips detector for HL-LHC will employ a custom PCB (powerboard) for on-module DC-DC conversion, HV switching, and monitoring. Production of about 14,100 of such PCBs with high reliability is a big challenge. This paper will present the production procedure and quality control (QC) testing system for the powerboards to be installed on ITk Strip barrel modules. During production, about 150 powerboards will be produced every week. Each powerboard will need to pass QC tests before they are assembled to module. The QC tests include thermal cycling between -35 °C and 40 °C, burn-in (continuous running of DC-DC converter at high load), and basic functionality and characterization electrical tests of the low voltage (LV), high voltage (HV), and monitoring functions of the powerboard. A custom QC test system will be presented, which is based on a reusable PCB (active board) with all testing circuits, a one-time powerboard carrier card, and a Z-turn SoC board which hosts and runs the testing program. The production procedure and QC test system has been tested with 400 powerboards during pre-production, and the system has been proven ready for production with the desired testing program, speed, safety, and cost. Performance and typical failures of powerboards observed during the QC test of pre-production powerboards will also be presented.

KEYWORDS: particle tracking detectors, solid state detectors, detector design and construction technologies and materials, manufacturing, voltage distributions

<sup>&</sup>lt;sup>1</sup>Corresponding author.

| C | ontents                                                                 |   |

|---|-------------------------------------------------------------------------|---|

| 1 | Introduction                                                            | 1 |

| 2 | Powerboard production and testing procedure                             | 3 |

| 3 | Powerboard QC system                                                    | 3 |

| 4 | Performance and typical failures observed on pre-production powerboards | 5 |

| 5 | Summary                                                                 | 6 |

|   |                                                                         |   |

#### 1 Introduction

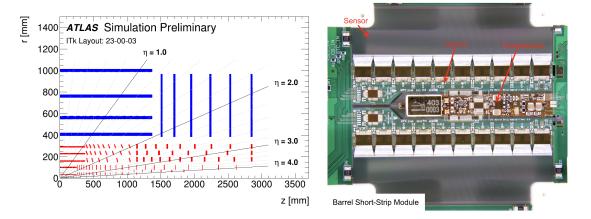

For the High Luminosity upgrade of the LHC (HL-LHC), the ATLAS experiment [1] will replace the present SCT with the ITk Strip detector [2]. The ITk Strip detector is composed of about 18,000 modules in total of 60 M strip channels distributed in four layers in the barrel and six layers in each endcap, as shown in the left plot of Figure 1.

**Figure 1**. Left: Layout of ATLAS ITk detector for HL-LHC upgrade. The ITk Strip layers are shown in blue. Right: Picture of a short-strip module used in ITk Strip barrel. Two hybrids and one powerboard are glued on top of the strip sensor.

Two types of local support structures are used for the ITk Strip, with rectangular staves in the barrel and wedge-shaped petals in the endcap. For the barrel region, each stave supports 14 modules on each side. The two innermost barrel layers use short-strip modules and the two outermost barrel layers use long-strip modules. The right plot of Figure 1 shows a picture of a short-strip module, which consists of a strip sensor, two hybrids, and a powerboard. The sensor has a size of 98 mm × 98 mm, and it has four rows (or two rows for long-strip sensor) of 1,280 strips. The hybrids are flexible PCBs which contain the front-end chips to read the signals from the strips. The powerboard,

which is glued on the sensor next to or in between the hybrids, is responsible for providing and monitoring the HV (up to 500 V with a few mA current) for the sensor bias, as well as the LV (1.5 V with up to 4 A current) for the front-end chips on the hybrids.

The baseline powering scheme of the ITk Strip uses parallel powering with DC-DC converters. Each side of the stave contains one 11 V LV line and four HV lines, which are shared by 14 modules in total. The 11 V is converted into 1.5 V with a DC-DC converter on each module. Each HV line on the stave is shared by groups of modules, and the ON/OFF control of HV on an individual module is done by the powerboard on the module.

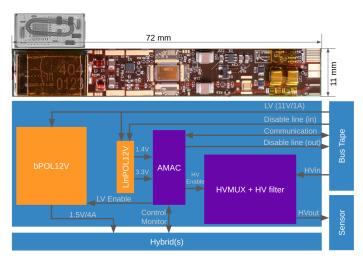

Figure 2 shows a picture of a powerboard together with a simplified schematic diagram of its design. The heart of the powerboard is the custom buck converter, bPOL12V [3]. A 500 nH air-core solenoid inductor is used (the actual inductance is reduced by the shield box to around 250 nH), providing a switching frequency for the DC-DC converter at around 2 MHz. A 1 mil thick aluminum shield box is used together with the copper layers in the PCB to shield from the strong ATLAS magnetic field, as well as to mitigate the electromagnetic induced noise transmitted to the sensor under the powerboard. The bPOL12V is controlled and monitored by a custom automatic monitor and control chip (AMAC) on the powerboard. The AMAC is powered by an always on linear regulator (linPOL12V). The HV control and current measurement is done by the AMAC together with an HVMUX circuit based on a GaN FET device [4]. The AMAC is also responsible for the control and monitoring of the hybrids, including interlock and temperature monitoring.

**Figure 2.** Top: A powerboard, with an X-ray image of the area under the shield box. Bottom: A simplified schematic diagram of the powerboard design.

In total, 14,100 barrel powerboards will be produced for the ITk Strip (for about 12,000 barrel modules allowing a system yield of around 85%). Section 2 will discuss the procedure to produce and test such number of powerboards, including the required quality control (QC) tests to ensure reliability of the produced powerboards. In section 3, we will discuss the system we developed to perform powerboard QC. A total of about 1,100 powerboards have been produced during the preproduction period (pre-production powerboards are not used for the detector), with 400 produced at the full production rate and tested with the full QC system. In section 4, we will present some performance results of those 400 powerboards, along with some typical failures of the powerboards

we observed during pre-production QC tests.

### 2 Powerboard production and testing procedure

The powerboards are produced and tested in panels, with each panel (flex array) containing 10 powerboards. The powerboard PCB is made with four-layer flexible polyamide material. After SMD loading, powerboards are singulated from the flex array and loaded onto a powerboard carrier card for wirebonding and electrical tests. The powerboard carrier card is a temporary PCB used to host 10 powerboards during powerboard QC. After wirebonding, the powerboards go through QC tests, which include visual inspection, thermal cycling, burn-in, and electrical tests in between steps:

- Visual inspection: Take a high resolution picture of each powerboard and examine the

powerboard to check for missing/tombstoned components, missing/broken wirebonds, solder

splash on bond pads, and incomplete seams on the shield box.

- **Thermal cycling**: Cycle the temperature of powerboards between -35 °C and 40 °C (as measured by the temperature sensors on powerboard) three times.

- Burn-in: Load the DC-DC converter at 2 A for 24 hours without interruption.

- Electrical tests: Basic tests of the powerboard functionalities, such as bPOL12V and lin-POL12V ON/OFF measurements, HV ON/OFF measurements, AMAC function tests, as well as characterization of LV, HV and AMAC settings, such as scan of the DC-DC converter efficiency/temperatures/currents at different loads. Electrical tests are performed at both room temperature (20 °C) and cold temperature (-35 °C) in between visual inspection, thermal cycling, and burn-in.

After passing all the QC steps, powerboards will be shipped to module assembly sites, where reception tests will be performed on the received powerboards before they are loaded onto modules, which include visual inspection and electrical tests.

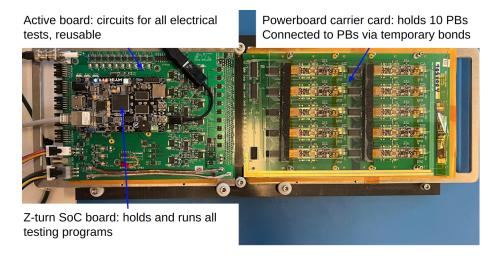

#### 3 Powerboard QC system

Groups of 10 powerboards are tested on carrier cards during QC. The carrier card will be discarded once the powerboards are loaded onto modules after QC. In order to reduce the cost, only necessary multiplexers are placed on the carrier card, from which the output signals from the powerboards are sent to a reusable PCB called the active board where all the testing circuits are hosted. The active board includes variable load circuits for the DC-DC converter, HV current measurement circuits, monitoring ADCs for output signals from the powerboard (DC voltage, temperature sensor output, etc.), and multiplexers for AMAC communication commands. The active board is connected to a Z-turn SoC board, which hosts and runs all the testing program on the active board. The carrier card is connected to the active board via a 200 pin card edge connector for quick change of carrier card. Figure 3 shows the testing system with carrier card, active board, and Z-turn SoC board. This testing system is used both for large scale powerboard testing during QC at Berkeley Lab and for

powerboard reception tests at module assembly sites. When used for powerboard reception tests, the system is placed on a table top; when used for powerboard QC, a group of such systems is placed inside a temperature controlled crate.

**Figure 3**. Powerboard electrical testing system: active board and the Z-turn board (left) and carrier card (right).

Figure 4 shows the rack used for the powerboard QC. The QC system contains the following main components:

- Test crates: Each rack contains two aluminum test crates (only one shown in Figure 4) as mechanical support and cooling supply for the active boards and carrier cards. The crate is divided into two sides: one side for the powerboard carrier cards and the other side for the active boards. One crate hosts 10 active boards and 10 carrier cards, which in total can test 100 powerboards at the same time. A group of five active boards are daisy chained together and share one Z-turn SoC board.

- Cooling system: The active board side and the carrier card side use seperate cooling systems. The carrier cards, where the powerboards are located, need to be cooled down to -35 °C, and cooling fluid from an SPS Scientific chiller is therefore circulated inside the carrier card side of the crate. The carrier card side and the active board side of the crate are not well thermally insulated, and when the carrier card side is at -35 °C, the temperature of the active side can also go below 0 °C without active cooling/heating, which is out of the working range of the Z-turn SoC board. Therefore, a separate cooling system with water- and fan-based radiators is running on the active board side of the crate to provide heating when the carrier card goes below 0 °C and cooling during powerboard burn-in.

- Monitoring, control, and safety system: The temperature and humidity of the crate are constantly monitored via climate sensors placed in different locations of the crate; the output of the climate sensors is read out by an environmental monitoring board which sends data to Grafana for monitoring. To protect the powerboards and testing boards inside the crate, an interlock board is used. The interlock board takes the temperature, humidity, dry-air flow

speed, etc. as input monitoring signals, and sends interlock signals to the chiller and power supply to turn them OFF if any of the monitored signals is out of specified range. The interlock board is purely hardware based with analog signals as input, and uses comparators and logic gates to take simple OR of all monitored signals as the interlock output signal.

• **Software**: All the QC steps are automated and integrated into an all-in-one custom web-based GUI. The GUI contains communication with Z-turn SoC board for executing electrical tests, communication with the chiller for thermal cycling, communication with the ITk production database for uploading test data, and monitoring tables and graphs for the testing results and crate status.

Figure 4. The powerboard QC test system: back (left) and front (right) view.

#### 4 Performance and typical failures observed on pre-production powerboards

During pre-production, a total of 400 powerboards have gone through the complete QC procedure with the massive test system we have developed, of which 394 powerboards have passed all the QC steps and six have been flagged as bad powerboards, resulting in a yield rate of 98.5%. Besides those six bad powerboards, we also observed about 5% of powerboards with broken wirebonds, and they were identified during visual inspection or initial electrical tests and were then fixed afterwards. We also noticed that the broken bonds all appear in one shipping batch, which indicates that the wirebonds were broken due to improper handling during shipping. Among the six bad powerboards, one powerboard could not establish communication with the AMAC, and the other five powerboards had low DC-DC efficiencies (lower than 60% at around 1 A load), with two of them having low efficiencies at all temperatures and three of them having low efficiencies only at low temperatures. No new failures were observed after the burn-in step. An extended burn-in at

higher temperatures and longer burn-in duration is being planned as part of the quality assurance (QA) of the powerboards.

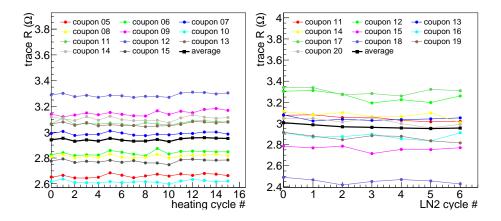

In order to test the quality of the PCB material, two test coupons are produced on each flex array. The test coupon uses the same material and layers as the powerboards, and contains a long trace, long via chains, and layers of copper pads. The trace and via chains represent the minimum trace and via sizes on the powerboard. We tested the properties and reliability of the PCB material from each batch by measuring the resistance of the trace and via chain and the capacitance between copper pads under different environments (e.g. thermal shock, irradiation). Figure 5 shows the long trace resistance measurement after cycles of thermal shock. No major change of resistance was observed after thermal shocks.

**Figure 5**. Trace resistance of test coupon after cycles of thermal shock: heating in oven (left) and dipping in liquid nitrogen (right).

Reliability tests of other components on the powerboard, such as linPOL12V reliability tests at high loads with periodic power cycles and bPOL12V reliability tests on powerboards as part of a long extended burn-in procedure, are also being carried out or planned to be carried out.

#### 5 Summary

The powerboard is a critical component for the power, monitor, and control of the ITk Strip Module. Production of 14,100 such PCBs for barrel modules with high reliability is a big challenge, as full industrialization proved to be difficult due to custom components and testing requirements. We have presented a custom production QC system to be run at Berkeley Lab, which is capable of performing thermal cycling, burn-in, and electrical tests for 200 powerboards simultaneously. The QC system has been proven to work efficiently during pre-production of the powerboards. Performance of the powerboards during pre-production has also been presented. The powerboard yield is higher than 98% and no major issues were observed during pre-production.

## Acknowledgments

This work was supported by the U.S. Department of Energy, Office of Science, High Energy Physics, under Contract No. DE-AC02-05CH11231.

#### References

- [1] ATLAS Collaboration, *The ATLAS Experiment at the CERN Large Hadron Collider, JINST* **3** (2008) S08003.

- [2] ATLAS Collaboration, *Technical Design Report for the ATLAS Inner Tracker Strip Detector*, CERN-LHCC-2017-005. ATLAS-TDR-025 (CERN, Geneva, Switzerland, 2017).

- [3] F. Faccio, et al, *The bPOL12V DCDC converter for HL-LHC trackers: towards production readiness*, PoS (2020): 070.

- [4] E. Giulio Villani, et al, *HVMUX*, high voltage multiplexing for the ATLAS strip tracker upgrade, *JINST* **15** (2020) C05003.