# UCLA UCLA Electronic Theses and Dissertations

### Title

Coprocessor Acceleration for Domain-Specific Computing

## Permalink

https://escholarship.org/uc/item/1bp8611m

### **Author** Zou, Yi

**Publication Date** 2012

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Coprocessor Acceleration for Domain-Specific Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

## Yi Zou

© Copyright by Yi Zou 2012

### Abstract of the Dissertation

# Coprocessor Acceleration for Domain-Specific Computing

by

### Yi Zou

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2012 Professor Jason Cong, Chair

There is a growing trend to use coprocessors to offload and accelerate domain-specific applications in order to obtain significant performance improvement and energy/power reductions. Two important coprocessor components in the heterogeneous system are the GPU and F-PGA. GPU (graphics processing unit) is increasingly used as a data-parallel coprocessor for general computations. The newest GPU has a much larger number of cores (compared to CPU) and very high peak FLOPS. FPGA (field programmable gate array), on the other hand, allows users to customize, at fine-grain level, the computational data path and memory hierarchy according to the exact need of the applications. FPGA excels in integer operations and bit-level operations.

The thesis starts with several coprocessor acceleration examples for our focus application domains: the first domain is on VLSICAD algorithms and the second is on computational medical imaging. We detail application acceleration examples in the domains including lithography simulation for IC manufacturing, medical image reconstruction using compressive sensing, and medical image registration using fluid models. Both GPU-accelerated versions and FPGA-accelerated versions have been implemented. Based on these implementations, we then analyze the performance and energy trade-offs, the interaction between the diverse application requirements and a spectrum of hardware systems, and how those domain-specific coprocessor acceleration case studies further bring us insights for domainspecific architecture innovations. In the end, we showcase an example for collaborative execution on the heterogeneous platform. Different scheduling policies are needed to optimize performance or energy. The thesis concludes as we present reusable architecture templates and realizations for futuristic accelerator-rich CMPs. The dissertation of Yi Zou is approved.

Alex Bui

Milos Ercegovac

Glenn Reinman

Jason Cong, Committee Chair

University of California, Los Angeles 2012

To my parents ... who raised me To all the people who love me and support me

# TABLE OF CONTENTS

| 1        | Intr | $\operatorname{troduction}$                                              |    |

|----------|------|--------------------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                               | 1  |

|          | 1.2  | FPGA/GPU Coprocessor Implementation: Lithography Simulation, Fluid       |    |

|          |      | Registration and CT Image Reconstruction                                 | 3  |

|          | 1.3  | Managed Task-level Parallelism for heterogeneous Computing               | 5  |

| <b>2</b> | Cop  | processor Acceleration                                                   | 6  |

|          | 2.1  | General-Purpose Computing on GPUs (GPGPU)                                | 6  |

|          |      | 2.1.1 Graphics Processing Units (GPU)                                    | 6  |

|          |      | 2.1.2 GPU Programming Environment                                        | 8  |

|          | 2.2  | Reconfigurable Computing                                                 | 9  |

|          |      | 2.2.1 FPGA-Centric Accelerator Systems                                   | 10 |

|          |      | 2.2.2 High-Level Synthesis Tools                                         | 13 |

|          | 2.3  | A Heterogeneous Node with CPU, GPU and FPGAs                             | 15 |

|          | 2.4  | Run-Time Support                                                         | 16 |

| 3        | FPO  | GA/GPU Accelerated Lithography Simulation                                | 18 |

|          | 3.1  | Introduction                                                             | 18 |

|          | 3.2  | Basics for Aerial Image Simulation                                       | 20 |

|          |      | 3.2.1 The Imaging Equation                                               | 20 |

|          |      | 3.2.2 Image-Based Simulation versus Polygon-Based Simulation             | 22 |

|          |      | 3.2.3 Detailed Settings for the Imaging Equation Using the Polygon-Based |    |

|          |      | Approach                                                                 | 23 |

|          | 3.3  | FPGA-based Accelerator for the Imaging Simulation                        | 24 |

|   |     | 3.3.1  | Image Padding for the Polygon-based Approach                          | 24 |

|---|-----|--------|-----------------------------------------------------------------------|----|

|   |     | 3.3.2  | Rearranging the Nested Loop                                           | 27 |

|   |     | 3.3.3  | Communication Analysis and HW/SW Partitioning $\hdots$                | 29 |

|   |     | 3.3.4  | Exploring Parallelism                                                 | 29 |

|   |     | 3.3.5  | Memory Partitioning using Modulo Addressing                           | 32 |

|   |     | 3.3.6  | Address Generation Logic for Partitioned Memory                       | 35 |

|   |     | 3.3.7  | Output Data Multiplexing                                              | 38 |

|   |     | 3.3.8  | Loop Pipelining and Function Block Pipelining                         | 40 |

|   |     | 3.3.9  | Using Wider Memory Access to Balance the Usage of Memory Ports .      | 42 |

|   | 3.4 | Levera | aging C to HDL Compiler for Hardware Generation                       | 42 |

|   |     | 3.4.1  | C-Based Hardware Generation and Optimization without Code Re-         |    |

|   |     |        | finement                                                              | 43 |

|   |     | 3.4.2  | Code Rewriting/Refinements for the Core Nested Loop $\ . \ . \ . \ .$ | 44 |

|   | 3.5 | Exper  | imental Results                                                       | 45 |

|   |     | 3.5.1  | Speedup Measurement                                                   | 46 |

|   |     | 3.5.2  | Accuracy of the Fixed-point Computation                               | 49 |

|   |     | 3.5.3  | Comparison with the FFT-Based Approach and Other Acceleration         |    |

|   |     |        | Techniques                                                            | 50 |

|   | 3.6 | Relate | ed Work                                                               | 53 |

|   | 3.7 | Concl  | usions                                                                | 54 |

| 4 | FPO | GA/GI  | PU Accelerated Fluid Registration                                     | 55 |

|   | 4.1 | ·      | luction                                                               | 55 |

|   |     |        |                                                                       |    |

|   | 4.2 | Fluid  | Registration Algorithm Review                                         | 57 |

|   | 4.3 | Modu   | le-Level Implementation                                               | 58 |

|   |     | 4.3.1  | Gaussian Smoothing                                                    | 59 |

|   |     | 4.3.2          | Displacement Update                                        | 61       |

|---|-----|----------------|------------------------------------------------------------|----------|

|   |     | 4.3.3          | Interpolation                                              | 62       |

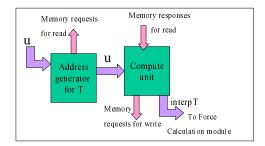

|   |     | 4.3.4          | Force Calculation                                          | 63       |

|   |     | 4.3.5          | Initial Implementation                                     | 63       |

|   | 4.4 | Optim          | izations                                                   | 64       |

|   |     | 4.4.1          | Algorithm Adaption                                         | 64       |

|   |     | 4.4.2          | Prefetching                                                | 65       |

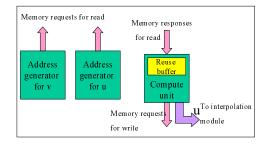

|   |     | 4.4.3          | Data Reuse                                                 | 66       |

|   |     | 4.4.4          | Streaming Across Modules                                   | 67       |

|   |     | 4.4.5          | Time Tiling Using a Ghost-Zone Approach                    | 67       |

|   |     | 4.4.6          | Towards Automated Code Generation                          | 69       |

|   | 4.5 | Exper          | imental Results                                            | 69       |

|   |     | 4.5.1          | Accuracy Comparison                                        | 70       |

|   |     | 4.5.2          | Performance of Our Implementation                          | 70       |

|   |     | 4.5.3          | Power Consumption                                          | 72       |

|   | 4.6 | Conclu         | usions                                                     | 72       |

| 5 | FPO | GA/G           | PU Accelerated CT Reconstruction using Compressive Sensing | 74       |

|   | 5.1 | Introd         | uction                                                     | 74       |

|   | 5.2 | EM+7           | ΓV Algorithm                                               | 76       |

|   |     | F 0 1          |                                                            |          |

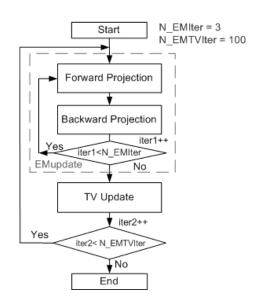

|   |     | 5.2.1          | Algorithm Overview                                         | 76       |

|   |     | 5.2.1<br>5.2.2 | Algorithm Overview       Tracer Engine                     | 76<br>78 |

|   |     |                |                                                            |          |

|   | 5.3 | 5.2.2<br>5.2.3 | Tracer Engine                                              | 78       |

|   |     | 5.3.2   | No Cache Interleaved Access                                      | 82  |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     | 5.3.3   | Resolving Access Conflicts in Parallel Backward Tracing          | 83  |

|   | 5.4 | Impler  | nentation & Optimization                                         | 85  |

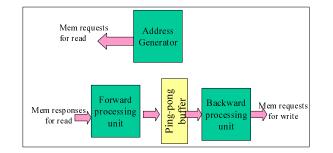

|   |     | 5.4.1   | Streaming Architecture                                           | 85  |

|   |     | 5.4.2   | Prefetching                                                      | 87  |

|   |     | 5.4.3   | Fixed-Point Conversion                                           | 88  |

|   |     | 5.4.4   | Arithmetic Specialization & Area Optimization                    | 89  |

|   |     | 5.4.5   | Reducing the Data Accesses via Sparsity                          | 90  |

|   |     | 5.4.6   | Simultaneous Reconstruction of Two Images                        | 90  |

|   | 5.5 | Experi  | mental Results                                                   | 91  |

|   |     | 5.5.1   | Kernel Performance and Energy Consumption                        | 93  |

|   |     | 5.5.2   | Application Performance and Energy Consumption                   | 95  |

|   | 5.6 | Conclu  | sions and Future Work                                            | 96  |

| 6 | Arc | hitectu | re Templates for Coprocessor Acceleration                        | 97  |

|   | 6.1 | Collab  | orative Execution on the Heterogeneous Platform                  | 97  |

|   |     | 6.1.1   | Benefit of Heterogeneous Computing                               | 98  |

|   |     | 6.1.2   | Image Pipeline Example                                           | 98  |

|   |     | 6.1.3   | Benefit of Dynamic Work Stealing Across Heterogeneous Components | 101 |

|   | 6.2 | Schedu  | ıling Dynamic Loops                                              | 106 |

|   | 6.3 | Archit  | ecture Templates and Implementations for Dynamic                 |     |

|   |     | Loops   |                                                                  | 108 |

|   |     | 6.3.1   | Parallelizing Inner Loops                                        | 108 |

|   |     | 6.3.2   | Multi-PE Realization with Static Allocation                      | 109 |

|   |     | 6.3.3   | Multi-PE Realization with Dynamic Allocation                     | 110 |

|    | 6.4   | Result | s with Different Templates                           |

|----|-------|--------|------------------------------------------------------|

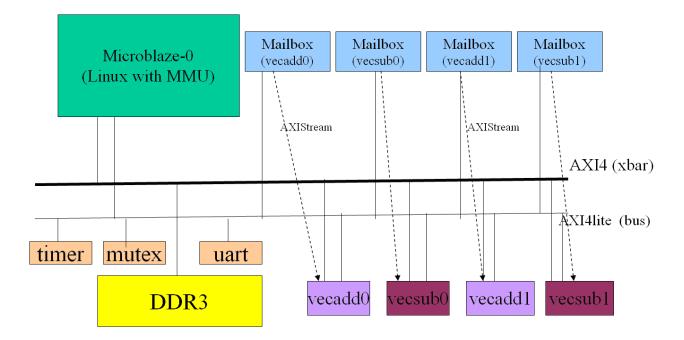

|    | 6.5   | Archit | ecture Template for Accelerator Management           |

|    |       | 6.5.1  | System-level Diagram                                 |

|    |       | 6.5.2  | Application Code                                     |

|    |       | 6.5.3  | Device Driver                                        |

|    |       | 6.5.4  | Global Accelerator Manager                           |

|    |       | 6.5.5  | Accelerator Implementation                           |

|    | 6.6   | Puttin | g the Template in Action                             |

|    |       | 6.6.1  | Single Process Execution                             |

|    |       | 6.6.2  | Multiple Processes with Accelerator Sharing          |

|    |       | 6.6.3  | Multiple Processes that Invoke Multiple Accelerators |

|    |       | 6.6.4  | Benefits over Conventional Invocation Scheme         |

|    | 6.7   | Resolv | ring Potential Deadlocks in the Template             |

|    | 6.8   | Conclu | usions and Future work                               |

| 7  | Con   | cludin | g Remarks                                            |

| Re | efere | nces . |                                                      |

# LIST OF FIGURES

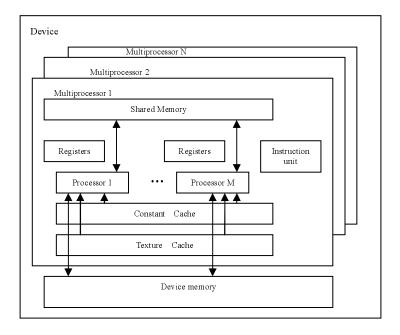

| 2.1  | Hardware model of GT200 series GPU                                            | 7  |

|------|-------------------------------------------------------------------------------|----|

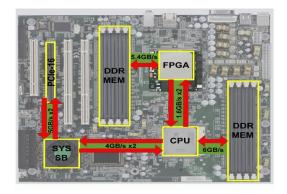

| 2.2  | XD1000 system diagram                                                         | 10 |

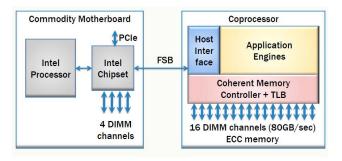

| 2.3  | Overall system diagram of Convey HC-1 hybrid computer                         | 11 |

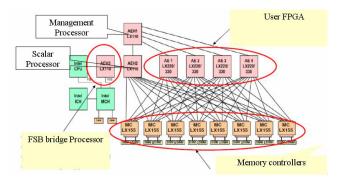

| 2.4  | Coprocessor-side diagram of Convey HC-1 hybrid computer                       | 11 |

| 2.5  | Binary interleave                                                             | 13 |

| 2.6  | Design flow using AutoPilot HLS tools                                         | 14 |

| 3.1  | Rectilinear polygons can be processed similar to rectangles                   | 21 |

| 3.2  | Pseudo-code for the nested loop                                               | 25 |

| 3.3  | Pseudo-code for the rearranged nested loop                                    | 26 |

| 3.4  | Computation of the inner nested loop                                          | 28 |

| 3.5  | Naive partitioning based on geometric locations                               | 30 |

| 3.6  | Block scheduling for naive partitioning                                       | 31 |

| 3.7  | Pseudo-code for the partially unrolled nested loop                            | 31 |

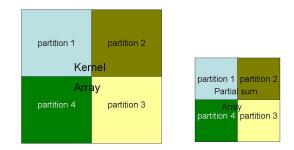

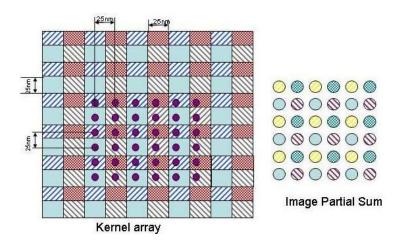

| 3.8  | 4-way (2 by 2) memory partition scheme for load balancing                     | 34 |

| 3.9  | Address generation and output data multiplexing                               | 35 |

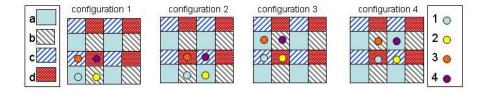

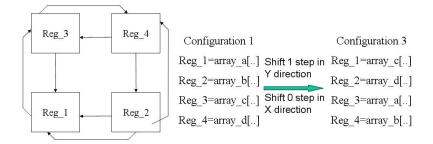

| 3.10 | 2D ring for 2 by 2 partitioning                                               | 37 |

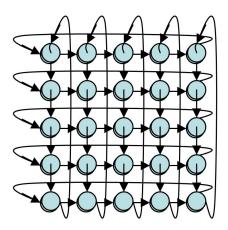

| 3.11 | Ring based data multiplexing for 5 by 5 partitioning                          | 38 |

| 3.12 | Pseudo code for 2D ring multiplexing for 5 by 5 partitioning                  | 39 |

| 3.13 | Loop flattening for deep loop pipelining                                      | 40 |

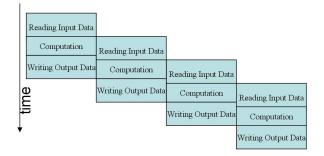

| 3.14 | Block pipelining/overlaping communication and computation                     | 40 |

| 3.15 | Explicit control flow on overlapping communication and computation $\ldots$ . | 41 |

| 3.16 | Using wider data to balance the use of the memory ports                       | 42 |

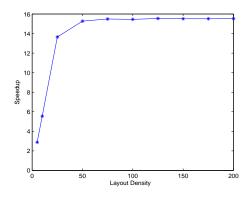

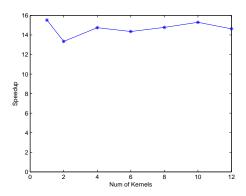

| 3.17 | Speedup plot with accelerator, single kernel                                  | 45 |

| 3.18 | Speedup plot with accelerator, multiple kernels, $N=200$                                 | 6 |

|------|------------------------------------------------------------------------------------------|---|

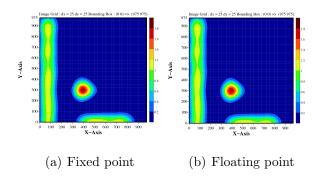

| 3.19 | Contour graph using fixed-point or floating-point computation                            | 7 |

| 3.20 | Error distribution for the contour graph                                                 | 7 |

| 3.21 | Pseudo-code for the core computation using CUDA                                          | 1 |

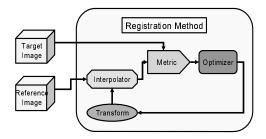

| 4.1  | Block diagram of image registration algorithms                                           | 6 |

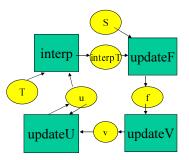

| 4.2  | Dataflow between procedures                                                              | 8 |

| 4.3  | 1D IIR PE                                                                                | 0 |

| 4.4  | 1D Gaussian IIR                                                                          | 0 |

| 4.5  | Displacement update                                                                      | 2 |

| 4.6  | Interpolation module                                                                     | 3 |

| 4.7  | Ghost-zone in 2D                                                                         | 6 |

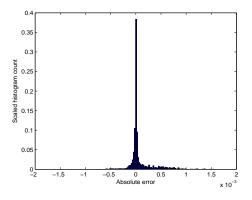

| 4.8  | Accuracy comparison                                                                      | 0 |

| 4.9  | One test image set with size $256^3$                                                     | 3 |

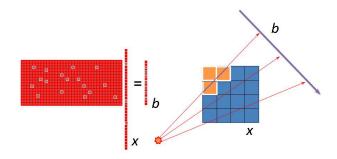

| 5.1  | Ray tracing in forward projection                                                        | 6 |

| 5.2  | EM+TV block diagram                                                                      | 7 |

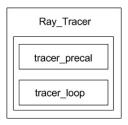

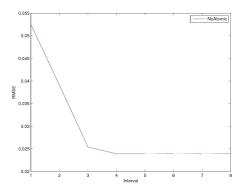

| 5.3  | Ray tracer block diagram                                                                 | 9 |

| 5.4  | Ray Tracing Core Engine    80                                                            | 0 |

| 5.5  | Ray-based parallel mapping                                                               | 3 |

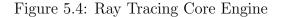

| 5.6  | RMSE vs. Intervals                                                                       | 4 |

| 5.7  | Overall streaming architecture inside one FPGA AE                                        | 6 |

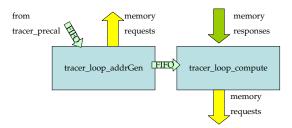

| 5.8  | Streaming architecture inside one $Tracer loop$ kernel $\ldots \ldots \ldots \ldots $ 88 | 8 |

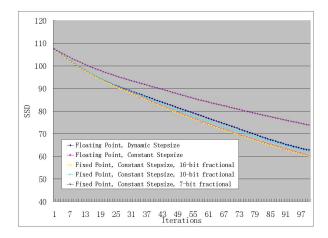

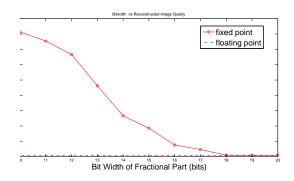

| 5.9  | Fractional bit width and reconstruction quality                                          | 9 |

| 5.10 | Masking for backward projection                                                          | 0 |

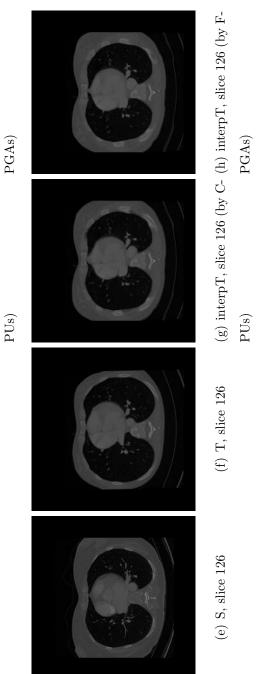

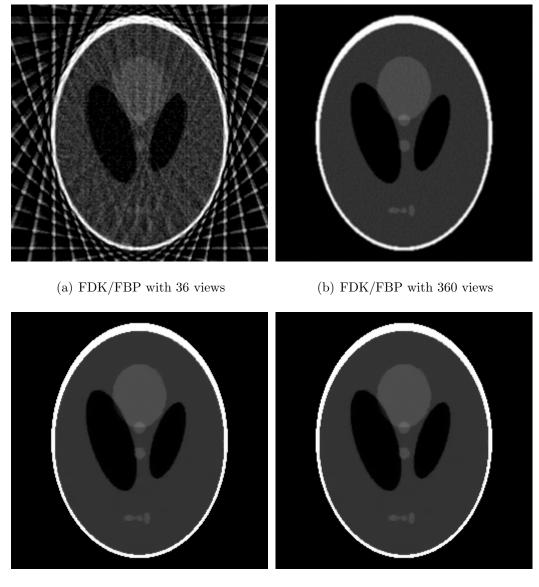

| 5.11 | Slices of test phantom images                                                            | 2 |

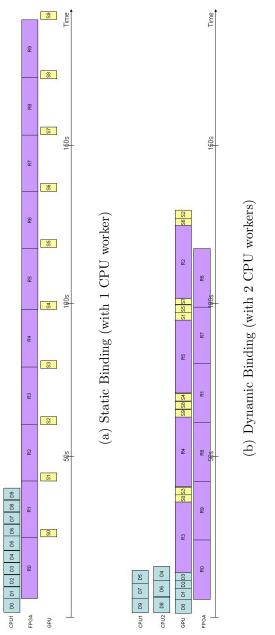

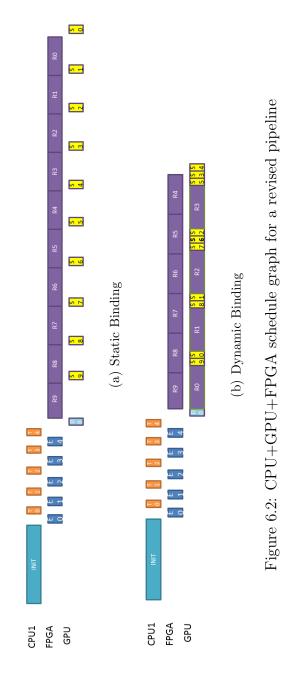

| 6.1 | CPU+GPU+FPGA schedule graph                             | 102 |

|-----|---------------------------------------------------------|-----|

| 6.2 | CPU+GPU+FPGA schedule graph for a revised pipeline      | 105 |

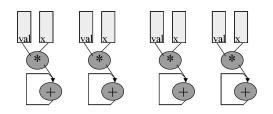

| 6.3 | Sparse matrix vector multiplication                     | 107 |

| 6.4 | Tree adder with banked storage                          | 109 |

| 6.5 | Multiple PEs with local storage                         | 110 |

| 6.6 | System-level prototyping diagram on Xilinx ML605 board  | 117 |

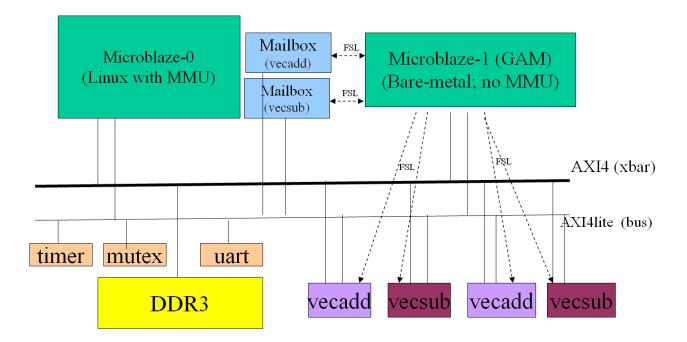

| 6.7 | Conventional scheme (without GAM) on Xilinx ML605 board | 126 |

## LIST OF TABLES

| 3.1 | Device information of EP2S180                                                                                                   | 45  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Device utilization of the design with 5 by 5 partitioning $\ldots \ldots \ldots \ldots$                                         | 45  |

| 3.3 | Running time comparison with or without accelerator, single kernel $\ldots$ .                                                   | 47  |

| 3.4 | Running time comparison with or without accelerator, multiple kernels, $N=200$                                                  | 48  |

| 3.5 | Performance rate (Mpixel/s)<br>comparison of various algorithm and platforms $% \left( {{{\rm{A}}} \right)_{\rm{A}}} \right)$ . | 48  |

| 4.1 | Performance comparison of 3D Gaussian IIR                                                                                       | 68  |

| 4.2 | Performance comparison of the remaining modules                                                                                 | 68  |

| 4.3 | Overall performance comparison                                                                                                  | 68  |

| 4.4 | Area results of our design                                                                                                      | 71  |

| 5.1 | Area optimization for the <i>tracer_precal</i>                                                                                  | 90  |

| 5.2 | Performance and energy numbers for computing kernels for $128^3$ data. Laten-                                                   |     |

|     | cy of FPGA (former number) is roughly 2X of the throughput (latter number)                                                      |     |

|     | when we construct two images simultaneously.                                                                                    | 94  |

| 5.3 | Area results                                                                                                                    | 95  |

| 5.4 | Application performance and energy consumption                                                                                  | 95  |

| 6.1 | Performance of the applications on CPUs, GPUs and FPGAs                                                                         | 98  |

| 6.2 | Dynamic work stealing                                                                                                           | 103 |

| 6.3 | Cycle counts for test matrices                                                                                                  | 112 |

| 6.4 | Timing breakdown for <i>vecadd</i> example                                                                                      | 123 |

| 6.5 | Timing for multiple processes of vecadd (using Synthetic case 2) $\ldots \ldots$                                                | 124 |

| 6.6 | Timing for multiple processes and multiple accelerators of vecadd and vec-                                                      |     |

|     | sub(using Synthetic case 2)                                                                                                     | 125 |

| 6.7 | Timing for multiple processes and multiple accelerators of vecadd and vec- |     |

|-----|----------------------------------------------------------------------------|-----|

|     | sub(using Synthetic case 2) in conventional template                       | 127 |

#### ACKNOWLEDGMENTS

I would like to thank my adviser Prof Jason Cong for the insightful guidance and continuous help during the PhD study. It is not possible to have the thesis without our weekly group meetings and countless Email exchanges (with him) which inspire the research ideas and pinpoint the focus. The thesis is further strengthened through numerous iterations of paper/thesis revisions. I would also like to thank my committee members Prof Alex Bui, Prof Milos Ercegovac and Prof Glenn Reinman for their constructive and critical feedback for my thesis. I am very grateful for Janice Martin-Wheeler who helped the language editing of my papers and the thesis. The thesis also benefits from various discussions from current and former lab members: Jianwen Chen, Mohammadali Ghodrat, Karthik Gururaj, Hui Huang, Muhuan Huang, Wei Jiang, Bin Liu, Chunyue Liu, Bingjun Xiao, Ming Yan, Bo Yuan and Peng Zhang.

The research conducted in this thesis is generously supported by funds from UC MICRO program, UC Discovery program (with industry support from Altera Corp, Magma Design Automation, Nvidia Corp and Mentor Graphics Corp), and NSF Grant CCF-0926127 NSF Center for Domain-Specific Computing (CDSC). Some chapters are based on materials of my published works. Chapter 3 is based on the adaption of paper P4. Alfred Wong from Magma Design Automation gave us sample kernels data and engaged in valuable discussions. The XD1000 development system is obtained through Xtremedata university program. Chapter 4 is based on the adaption of paper P8. Igor Yanovsky and Prof Luminita Vese at UCLA department of mathematics provide us the reference source code for the fluid registration implementation. Chapter 5 is based on an extended version of paper P10. Ming Yan and Prof Luminita Vese at UCLA department of mathematics provide us the reference source code for the EMTV reconstruction implementation. Chapter 6 is based on the rewrite of materials in papers P6 and P11. The CnC-HC tool and the Habanero runtime are provided by Rice Habanero project as part of the CDSC effort. Xilinx Inc and AutoESL (now part of Xilinx Inc) donate us various FPGA devices/boards and licenses for the design tools (including high-level synthesis tools) through the Xilinx university program.

### Vita

| 2000-2004 | B.S., Department of Computer Science and Technology |

|-----------|-----------------------------------------------------|

|           | Tsinghua University, Beijing, P.R.China             |

| 2004-2006 | M.S., Department of Computer Science and Technology |

|           | Tsinghua University, Beijing, P.R.China             |

### PUBLICATIONS

P1. J. Cong and Y. Zou, "Lithographic Aerial Image Simulation with FPGA-Based Hardware Acceleration", Proc. 16th ACM/SIGDA International Symposium on Field Programmable Gate Arrays (FPGA 2008), pages 67-76, Monterey, CA, Feb 2008.

P2. J. Cong, K. Gururaj, B. Liu, C. Liu, Z. Zhang, S. Zhou and Y. Zou, "Evaluation of Static Analysis Techniques for Fixed-Point Precision Optimization", Proc. 17th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2009), pages 231-234, Napa, CA, Apr 2009.

P3. J. Cong, W. Jiang, B. Liu, and Y. Zou, Automatic Memory Partitioning and Scheduling for Throughput and Power Optimization, in Proc. International Conference on Computer-Aided Design (ICCAD 2009), pages. 697-704, San Jose, CA, Nov 2009.

P4. J. Cong and Y. Zou, "FPGA-Based Hardware Acceleration of Lithographic Aerial Image Simulation", ACM Transactions on Reconfigurable Technology and Systems, Vol.2, No.3, Article 17, Sep 2009. P5. J. Cong and Y. Zou, "Parallel Multi-level Analytical Global Placement on Graphics Processing Units", Proc. International Conference on Computer-Aided Design (ICCAD 2009), pages 681-688, San Jose, CA, Nov 2009.

P6. J. Cong and Y. Zou, "A Comparative Study on the Architecture Templates for Dynamic Nested Loops", Proc. 18th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2010), pages 251-254, Charlotte, NC, May 2010.

P7. J. Cong, M. Huang and Y. Zou, "3D Recursive Gaussian IIR on GPU and FPGAs", Proc. IEEE Symposium on Application Specific Processors (ASAP 2011), San Diego, CA, Jun 2011.

P8. J.Cong, M. Huang and Y. Zou, "Accelerating Fluid Registration Algorithm on Multi-FPGA Platforms", Proc. International Conference on Field Programmable Logic and Applications (FPL 2011), Chania, Crete, Greece, Sep 2011.

P9. A. Bui, K.Cheng, J. Cong, L. Vese, Y. Wang, B. Yuan and Y. Zou, "Platform Characterization for Domain-Specific Computing (invited paper)", Proc. Conference on Asia South Pacific Design Automation (ASPDAC 2012), Sydney, Australia, Jan 2012.

P10. J. Chen, J. Cong, M.Yan and Y. Zou, "FPGA-Accelerated 3D Reconstruction using Compressive Sensing", Proc. International Symposium on Field-Programmable Gate Arrays (FPGA 2012), Monterey CA, Feb 2012.

P11. A. Sbirlea, Y. Zou, Z. Budimlic, J. Cong and V. Sarkar, Mapping a Data-Flow Programming Model onto Heterogeneous Platforms, Proc. ACM SIGPLAN/SIGBED Conference on. Languages, Compilers, Tools and Theory for Embedded Systems (LCTES 2012), Beijing, China, Jun 2012.

# CHAPTER 1

## Introduction

#### 1.1 Motivation

Recently, the frequency scaling of microprocessors has slowed down, and the trend is that more and more cores are being put in a single chip. Programs need to actively leverage parallel computing to make the best use of available computing resources.

On the other hand, the conventional multi-core system may not be the best architecture realization for a particular application specification. These multi-core systems are generalpurpose in nature and are typically less power-efficient. As the number of cores continue to increase, the power density of the system creates the utilization wall [1] where not all the components can be active all the time. The term "dark silicon" [2] is used to refer to the transistor underutilization on the future many-core chips. This motivates us to take the domain-specific approach to customize the hardware platform in order to improve the power/performance of the computing system. Off-the-shelf coprocessors such as FPGAs and GPUs can offload certain computation-intensive parts of the application, and can significantly accelerate overall system performance. GPU is a device that is traditionally used for rendering images for computer display and gaming purposes, but it is also used as a data-parallel coprocessor for general computations. The newest GPUs have a much larger number of cores (compared to CPUs) and very high peak FLOPS. The FPGA, on the other hand, allows users to customize, at fine-grain level, the computational data path and memory hierarchy according to the exact need of the applications. FPGA excels in integer operations and bit-level operations. While the specialization using the coprocessors does bring in further under-utilization, the superior energy-efficiency of the coprocessors creates an effective means to battle the utilization wall.

The research is partially funded by the CDSC (Center for Domain-Specific Computing) [3] project. The vision of the CDSC project is to look beyond parallelization, adapt the hardware architecture to application domains, and focus on domain-specific customization as the next disruptive technology to bring orders-of-magnitude power-performance efficiency improvement to important application domains. Using this technology, we can potentially build a "supercomputer in a box" to illustrate the energy-efficient computing. As part of the effort of the CDSC project, we have built a heterogeneous testbed that contains both FPGA and GPU in a tightly integrated fashion. Still, the challenges for using the coprocessors are two-fold.

First, we need to obtain the component-specific implementation efficiently. Because the hardware architecture of the coprocessor may be completely different from the traditional multi-core, different implementation schemes for each coprocessor component are likely needed. For the GPU, we use the Nvidia CUDA toolkit, which is a C/C++ language augmented to support the single program multiple data (SPMD) paradigm. For the FPGA, we use the AutoESL high-level synthesis (HLS) tools to describe the bare-metal hardware accelerator in hardware-oriented C-language. The CUDA toolkit (or the more general cross-vendor API OpenCL) has been widely accepted in the GPGPU community. We have implemented several interesting applications using the GPU: mixed-size circuit global placement [4], and MRI image reconstruction using compressive sensing. But for the FPGA, the C-based highlevel synthesis has not yet reached very broad adoption. The frustration can be seen in the FCCM'11 top 10 predictions: "No. 1 prediction: a high-level, object-oriented solution for FPGA design will be popular, it won't be C to gates; and the No. 5 prediction: VHDL and Verilog will remain ubiquitous for circuit expression." Yet we will allocate a major portion of this thesis to present several FPGA-based coprocessor accelerator cases to advocate the HLS development flow for the FPGA. I will detail the optimization scheme used (at C-level) to obtain a design implementation with the best performance, and the potential performance/energy benefit. The limitations and work-arounds of the current flow also motivate us to pursue further automations.

The second challenge is to manage those coprocessor accelerators efficiently, assuming the component-specific implementation is ready. For example, we map a medical imaging pipeline that includes image denoising, image registration and segmentation onto the heterogeneous platform. Efficient implementations on either FPGA or GPU can speed up each individual application by 10X to 20X respectively, and with a 2X to 4X improvement on energy-efficiency.

When we have a batch of images to process, the task-level parallelism in the macro dataflow permits concurrent execution on multiple processors as well as coprocessors (including GPU and FPGA). Moreover, some application kernels are more suitable for FPGA coprocessors, some are more suitable for GPUs, and some portion of the codes shall still be left to CPUs to execute. We need to consider these preferences of kernel binding as well as resource availability in the mapping.

By using the task-level data flow description called Concurrent Collections (CnC) [5], and the underlying Habanero run-time, we can achieve the load-balancing (through workstealing) across different heterogeneous components. A dynamic task to coprocessor binding (with cross-device stealing) can boost the overall accelerated performance compared to a static binding. However, the Habanero runtime works in user-space and will not perform any coprocessor/accelerator management at the whole system-level. We then present a practical architecture template implementation that mimics the features of accelerator-rich CMPs. We realize a global accelerator manager (GAM) using an embedded processor. The embedded processor performs the actual accelerator invocation and is the gateway/abstraction-layer for the application code and device drivers.

# 1.2 FPGA/GPU Coprocessor Implementation: Lithography Simulation, Fluid Registration and CT Image Reconstruction

In this section we briefly highlight our achievements of the three applications that are described in this thesis. Lithography simulation, as an essential step in design for manufacturability (DFM), is still far from computationally efficient. Most leading companies use large clusters of server computers to achieve acceptable turn-around time. Thus coprocessor acceleration is very attractive for obtaining increased computational performance with reduced power consumption. We designed a customized accelerator on an FPGA using a polygon-based simulation model. An application-specific memory partitioning scheme is designed to meet the bandwidth requirements for a large number of processing elements. Deep loop pipelining and ping-pong buffer based function block pipelining are also implemented in our design. A 15X speedup is obtained using the FPGA-device in the Xtremedata XD1000 system versus the software implementation running on a microprocessor of the same system. The performance is 2X that of a CUDA implementation GPU 8800GT, yet the FPGA only consumes about a fraction (1/20) of the power of the GPU. The implementation also leverages stateof-art C-to-RTL synthesis tools. At the same time, we also identified the need for manual architecture-level exploration for parallel implementations—with the most important one being memory partitioning.

In the clinical applications, medical image registrations on the images taken from different times and/or through different modalities are needed in order to have an objective clinical assessment of the patient. Viscous fluid registration is a powerful PDE-based method that can register large deformations in the imaging process. We present our implementation of the fluid registration algorithm on the multi-FPGA platform Convey HC-1. We obtain a 35X speedup versus single-threaded software on a CPU, and comparable performance with GPU (Telsa C1060). The implementation is achieved using a high-level synthesis (HLS) tool, with additional source-code level optimizations including fixed-point conversion, tiling, prefetching, data-reuse, and streaming across modules using a ghost zone (time-tiling) approach. These manual steps need to be further automated by existing HLS software.

The radiation dose associated with computerized tomography (CT) is significant. Compressive sensing methods provide mathematic approaches to reduce the radiation exposure, without sacrificing image quality. However, the computational requirement of the algorithm is prohibitive, and much higher than conventional image reconstruction algorithms like the Feldkamp-Davis-Kress (FDK) algorithm. We present an FPGA implementation of one compressive sensing algorithm with applications on CT image reconstruction. The ray tracing forward and backward projection procedures have abundant random off-chip accesses, as well as load-balancing issues, and are good fit for the multi-FPGA platform that excels in interleaved memory access. Our FPGA EM kernel is 50% faster than the GPU implementation on Telsa C1060. Moreover, our FPGA kernel can process two independent images at the same time, and thus the kernel throughput is 3X that of Tesla C1060 and slightly better than the Fermi GTX480 GPU. Moreover, our EM kernel is deployed in a hybrid (CPU+GPU+FPGA) computer, and we show that the hybrid approach delivers better performance and energy than GPU-only solutions.

### **1.3** Managed Task-level Parallelism for heterogeneous Computing

We need a diverse and customizable architecture to meet the needs of diverse applications. To address the needs, we built a heterogeneous testbed that contains both the FPGA and GPU in a tightly integrated fashion. From the perspective of application-side, we need to consider two issues: first, the coprocessors introduce additional computational elements and thus we can further explore task-level parallelism where tasks on the CPU, GPU and FPGA can potentially run in parallel; second, some kernels are more suitable for FPGA coprocessors, some are more suitable for GPUs, and some portion of the codes shall still be left to CPU to execute.

We use the modeling language chosen by the Center for Domain Specific Computing (CDSC): Concurrent Collection [5], which develops a software flow that is capable of converting high-level task-level dataflow into a lower-level *async-finish* style parallel code. We demonstrate a working example that maps a medical image processing pipeline onto one heterogeneous platform with CPU, GPU and FPGAs. The limitation is that the management scheme works within a single process. We then discuss the architecture template and support that works at the system-level, which can move some scheduling logic from software into hardware.

# CHAPTER 2

## **Coprocessor Acceleration**

The goal of the Center for Domain-Specific Computing (CDSC) [3] is to develop domainspecific hardware architectures, and the software systems to greatly improve the performance and the energy efficiency of domain-specific applications. In this thesis we focus on two application domains. The first one is VLSICAD, because many of the algorithms in the domain are quite computational intensive and requires heavyweight clusters to compute. The second one is medical imaging, given its significant impact on the healthcare industry. To achieve our goal, it is essential to benchmark how well current commodity platforms perform, and identify opportunities for architectural innovations.

### 2.1 General-Purpose Computing on GPUs (GPGPU)

The first type of accelerator component is the graphics processing unit or GPU. The GPU is the processing unit specifically designed for handling the computation for computer graphics. It is increasingly used as massive-parallel many-core processor that can aid general purpose computation.

#### 2.1.1 Graphics Processing Units (GPU)

Conventional GPU contains a number of processors for vertex processing, texture processing and fragment pipeline. Texture processing is normally vector-based as textures will contain RGB components for visualization.

The Nvidia GT200 series GPU uses a unified shader architecture, so that tasks for vertex processing, fragment pipelining and texture processing are all performed by the unified shad-

Figure 2.1: Hardware model of GT200 series GPU

er.<sup>1</sup> Also, it uses scalar processors rather than vector processors; thus it is much friendlier for general computing tasks. Figure 2.1 shows the hardware model for the GT200 series GPU. Each device is composed of N stream multiprocessors (SM), and each multiprocessor is composed of M stream processors (SP). Each processor has its dedicated registers. The M stream processors in each multiprocessor share a fast-access scratchpad memory called "Shared Memory" (as shown in Figure 2.1), and share the instruction unit. These M processors run exactly the same threaded program in the SPMD (single program multiple data) model. The constant cache and texture cache are also shared by the M processors in the same multiprocessor. Compared to the previous generation G80 series, GT200 also adds the double precision support. Each multiprocessor has one double precision unit.

Another major vendor of the graphics compute card is AMD. The overall architecture of the AMD GPU compute card is very similar to those from Nvidia. Yet they may have different ratio of arithmetic units, special function units and texture shading units. One major difference is that the AMD card uses 4-way or 5-way VLIW at the finest level, where the Nvidia card uses the scalar processor. AMD's recent Graphics Core Next (GCN) ar-

<sup>&</sup>lt;sup>1</sup>GT200 is the codename for the latest version of Nvidia GPU. GTX280 and Tesla C1060 are specific names of the video cards that use the GT200 series of GPU.

chitecture also adopted the scalar architecture. A detailed comparison between the Nvidia GPU architecture and the AMD GPU architecture can be seen in [6].

Modern GPU compute cards sit on the PCI-express slots and talk to the host CPU using PCI-express protocols. The 2.0 version of the PCI-express will have 500MB/s peak bandwidth per lane and 8GB/s bandwidth for a 16-lane connection. A 16-lane connection is what we use in most modern GPU compute cards. Note the PCI-e bandwidth is still significant lower than the peak bandwidth of the on-board off-chip memory bandwidth of the GPU card, which can be around 100GB/s.

#### 2.1.2 GPU Programming Environment

Writing general programs for GPUs requires an in-depth understanding of the graphics concepts and a conversion from the general computing task to a graphics processing pipeline. This, often, is not an intuitive and easy task.

CUDA is the C environment for programming the G80, G92 and GT200 series GPUs. It uses massive threading to overlap the computing with the memory access latency, and it also provides the scratchpad-like shared memory for fast access (note the size of the shared memory is very limited). Thread creation and switching are very lightweight on the GPU compared to a multi-core CPU. In the CUDA environment, users can write SPMD code to map onto the hardware architecture. Inside the code, users can define the parallelism among different multiprocessors by specifying the number of parallel blocks to use:  $N\_block$ . Also the parallelism inside each multiprocessor is specified by the number of threads inside each block:  $N\_thread$ . A total of  $N\_block * N\_thread$  threads shall be created for that code. The block ID and thread ID are used to identify different threads, and they can access different data based on their IDs. Each thread can access per-thread registers, per-thread-block shared memory, per-thread-block cache and per-device global memory.

The hardware architecture of the Nvidia GPUs also has certain limitations. Because of the SIMD fashion used in the stream multiprocessor, there is significant overhead in handling divergent control flows. No synchronization between thread-blocks is provided except through global memory on the board. Memory access needs to follow a special access pattern (called coalesced access) where a half-warp (16 in the GT200 architecture) of threads shall access continuous memory locations for optimal memory bandwidth. These architecture restrictions impose considerable challenges for implementation, and require significant tuning efforts for better performance.

Another general-purpose programming framework for GPU computing is OpenCL [7]. OpenCL is an open, industry-standard framework, which has gained support from almost all CPU/GPU manufacturers including AMD, Intel, and NVIDIA; CUDA is only supported on Nvidia GPUs. The GPU implementations in this thesis are done using CUDA rather than OpenCL, because at that time the CUDA toolkit is more mature than the Nvidia OpenCL toolkit. While the two share a similar programming paradigm, the OpenCL program is slightly lower-level (in order to achieve platform neutral) and is more lengthy to write.

### 2.2 Reconfigurable Computing

Reconfigurable computing leverages the specialized hardware platforms to adapt the computational need through hardware customization. In the 1960s, pioneering work by Prof Gerald Estrin at UCLA proposed the architecture that features the fixed plus reconfigure hardware [8, 9]. Similarly, the Stanford GARP project [10] combines a RISC processor with a reconfigurable hardware. Most modern reconfigurable systems use the field programmable gate array (FPGA) as the major component to realize the customizable hardware kernel. A typical FPGA architecture consists of an array of logic blocks (called configurable logic block, CLB), I/O pads, and routing channels. The logic block uses a lookup-table (LUT) to realize arbitrary bit-level logical expressions. The routing channel is also programmable at bit-level. Modern FPGAs also incorporated several hardware blocks such as block RAM, DSP units, and carry chains. High-end FPGAs now feature thousands of block RAMs, where multiple block RAMs can provide parallel data accesses simultaneously. Because of the nature of FPGA, it is well suited to accelerate bit-level, fixed-point parallel computation; though floating point arithmetic is also supported via efficient utilization of DSP units in

Figure 2.2: XD1000 system diagram

modern FPGAs.

The principle of customizable computing is not limited to FPGA-based computing; also applies to other reconfigurable systems that use coarse-grain reconfigurable logics. Several more recent reconfigurable architectures are further surveyed in [11]. The book by [12] presents comprehensive examples on reconfigurable computing.

This year, we celebrated the 20th anniversary of FCCM, which is a conference that is specifically dedicated to reconfigurable computing. We have seen many successful examples for reconfigurable computing, such as networking and communications [13], image processing [14], finance [15], data-warehousing [16], bioinformatics [17], radar and remote sensing [18] etc.

The case studies we present in the following chapters also showcase successful examples of reconfigurable computing where we target VLSICAD and medical imaging.

#### 2.2.1 FPGA-Centric Accelerator Systems

FPGA accelerators still have no standard packaging or interconnect protocols, and thus a number of choices are available. Several cards (e.g., Xilinx ML605, Altera DE4, Nallatech PCIe-280) also provide PCI-express edges. These may be the easiest integration options, but typically only one or two SODIMMs are attached to these cards and the bandwidth from the SODIMMs is relatively poor compared to the bandwidth of GPUs. Axel [19] and QP [20] all use this type of FPGA accelerator.

Figure 2.3: Overall system diagram of Convey HC-1 hybrid computer

Figure 2.4: Coprocessor-side diagram of Convey HC-1 hybrid computer

In the lithographic simulation acceleration, we used the XD1000 system from XtremeData. Figure 2.2 is the system diagram of XtremeData's XD1000 development system, which is the hardware platform we use. This development system uses a dual Opteron motherboard and one Opteron is replaced by an XD1000 coprocessor module. The XD1000 coprocessor communicates with the host Opteron CPU via Hypertransport links, and it is built based on Altera's largest FPGA in the Stratix II family: EP2S180.

The applications in the medical imaging domain are very memory-intensive. Because the size of the 3D images is too big to fit in the on-chip RAM or on-board SRAM chip, we need to use off-chip DRAM extensively. Some cards (e.g., SRC Map station) use memory DIMM slots with proprietary protocol. The more compelling choices are the FPGA accelerators that use processor interconnects. AMD opened its HyperTransport bus through its Torrenza initiative, and Intel later opened its Front Side Bus to third party FPGA board vendors as well. Representative systems include Xtremedata's XD1000F and XD2000F (using HyperTransport), Nallatech's FSB development system, and Convey HC-1 (using FSB).

Among these systems, we further selected Convey HC-1(ex) as our baseline platform for implementing medical imaging applications. Figure 2.3 shows the system diagram for the Convey HC-1. The form-factor of the platform is a 2-U rack-mountable server box. Figure 2.4 shows the structures of the coprocessor hardware of the Convey HC-1. The HC-1 platform has four user FPGAs (Virtex5 LX330). The CPU and different FPGAs access the off-chip memory using a shared memory model. The system employs an on-board crossbar to realize the interconnection. Cache coherence is also handled through the FSB protocols. Convey realizes a cache-coherent NUMA (ccNUMA) system on top of a FSB protocol stack. Each FPGA is presented with 16 external memory access channels. (Eight physical memory ports are connected to eight memory controllers that run at 300MHZ. Core design runs at 150MHZ. Thus, effectively the design on each FPGA is presented with 16 "logical" memory access channels through time multiplexing.) Convey HC-1 provides a very large bandwidth (claims to have 80GB/s peak bandwidth) for coprocessor side memory. Note, a claimed 80GB/s coprocessor side memory bandwidth in Convey HC-1 is only slightly lower than the bandwidth of one Tesla C1060 card (around 100GB/s). In practice, we observe that 30% to 50% of the peak bandwidth can be achieved. As a comparison, the Xilinx ML605 board has only one SODIMM and the off-chip sustained memory bandwidth from SODIMM measured less than 1GB/s. In the Nallatech FSB development system, the FPGA coprocessor does not have a large coprocessor-side memory but accesses the system memory through the front-side bus and the bandwidth is limited to the bandwidth of FSB (around 8GB/s).

The multi-FPGA platform Convey HC-1(ex) uses an interleaved memory scheme. Different FPGAs access the off-chip memory using a shared memory model. The system employs an on-board crossbar to realize the interconnection. In HC-1ex, the user FPGAs are upgraded from Virtex5 LX330 to Virtex6 LX760. The system supports two modes of an interleave scheme. The prime number interleave is where the system uses a prime number of banks to better support power-of-two strides. The other interleave scheme is called the binary interleave.

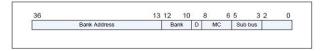

The binary interleave scheme takes out the 12th to 3rd bits (counted from the LSB) of the virtual address to determine the bank the address falls in. The system features 1024

Figure 2.5: Binary interleave

banks. In particular, the 9th to 6th bits of the address determine which memory DIMM the address falls in. The system has 16 DIMMs in total. Figure 2.5 illustrates the binary interleave scheme. We can see from Figure 2.4 that each memory controller is connected to two DIMMs. The D bit in Figure 2.5 determines which DIMM to select from the two DIMMs. Each DIMM has 64 banks.

#### 2.2.2 High-Level Synthesis Tools

One of our unique approaches on reconfigurable computing is through the use of high-level synthesis tools. As the complexity of FPGA designs goes up, it is more and more challenging to implement the design manually using RTL-level descriptions such as Verilog or VHDL. Electronic system-level (ESL) is a cutting-edge technology which allows users to describe their designs at high level, such as C/C++, and ESL tools further perform high-level synthesis (HLS) to generate platform-specific RTL automatically. The adoption of these tools leads to a significant savings in design effort and reduced turn-around time.

Currently there are many ESL products in the market, such as Impulse C [21] from Impulse Accelerated Technologies, Catapult C [22] from Calypto Design Systems, DK Suite and Handel-C [23] from Agility (now part of Mentor Graphics), Cynthesizer [24] from Forte Design Systems, AutoPilot [25] from AutoESL Design Technologies (now part of Xilinx), PICO Extreme FPGA [26] from Synfora (now part of Synopsys), C-to-Silicon Compiler [27] from Cadence, just to name a few.

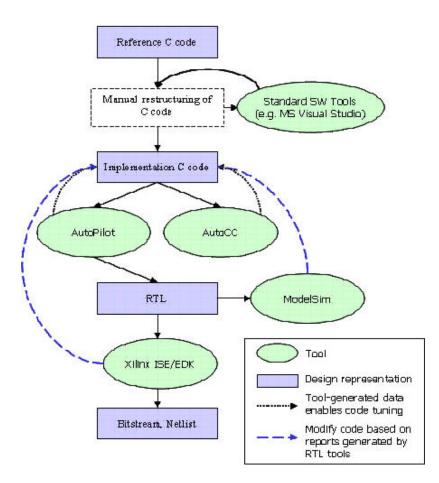

AutoPilot [25] is the ESL tool that we use in this thesis, because it uses the latest technology and leverages a robust open compiler framework; it features a rich set of optimization passes and compiler transforms for hardware synthesis; it also has a very wide C/C++ lan-

Figure 2.6: Design flow using AutoPilot HLS tools

guage support. (Also it is the tool that we have access to.) It accepts synthesizable C, C++, or SystemC as input and generates RTLs in Verilog or VHDL, while we primarily use C as input. AutoPilot is based on the xPilot system [28] licensed from UCLA, but has been commercialized by AutoESL Design Technologies for further development. Figure 2.6 (from BDTI certification report [29]) shows the design flow using AutoPilot tools. Starting from the C code, we perform hardware-oriented code refinement at C-level to obtain a bit-accurate synthesizable code. Simulation can be done by pre-synthesis *autocc* tool, or at RTL-level using third-party simulators. The RTL is further synthesized to obtain the bitstream through vendor tools (e.g., Xilinx ISE).

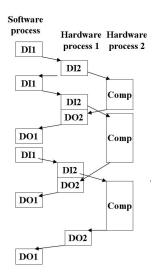

The AutoPilot tool will only generate the RTL for one IP. Designers need to connect the IP with other IPs or system interfaces. Platform-specific interface wrappers in RTL are needed to provide a fast integration path. For example, in the case of the Convey system, the interface for one external memory access port is separated into one request FIFO and one response FIFO.

Note that from Figure 2.6 we can see that an important step in the flow is manual code refinement. In this thesis we describe many details on how those refinements are done. These also motivate further automations that need to be addressed by the high-level synthesis tools.

### 2.3 A Heterogeneous Node with CPU, GPU and FPGAs

As part of the CDSC project, we further combine the GPU accelerator and FPGA accelerator into a single server node.

The form-factor of the Convey HC-1 platform is a 2-U rack-mountable server box. The motherboard has two PCI-e X16 slots, but there is no physical space to host a Tesla compute card due to form-factor issues. Currently, we use a PCI-express expansion box, Magma ExpressBox 2, to host a Tesla compute card C1060.

In the HPC space, a distributed memory paradigm is typically used across the cluster nodes, and shared memory is used within each node. However, coprocessors bring in additional complexity, because coprocessors have access to coprocessor-side memory, and the coprocessor-side memory may not be directly addressable from the host. FPGAs also have a large amount of coprocessor-side memory, which can be placed in a shared virtual memory space along with the host-side memory space. This needs some OS support as well as hardware support. Convey Computer realizes a cache-coherent NUMA (ccNUMA) system on top of a FSB protocol stack. With the release of CUDA 4.0 that supports unified virtual addressing, our heterogeneous server node should be able to support a shared virtual memory space across CPU, GPU and FPGAs. Currently, the GPU card in our system still has its own address space.

Our system runs Convey Linux, which is essentially a Linux distribution with modifications to better support the shared virtual memory system. Convey also provides the compiler and debugger toolchains for the system as well. The compiler can recognize certain Conveyspecific pragmas. It also has the ability to generate vectorized code that runs on a vector ISA which can be implemented on FPGAs. NVIDIA CUDA drivers and CUDA toolkit are installed on the system as well.

### 2.4 Run-Time Support

Despite over four decades of research, few high-level parallel programming models and runtimes are available to domain experts who are not, at the same time, experts in parallelism. Fortunately, this situation is starting to change. Frameworks such as Map-Reduce [30] successfully exploit implicit parallelism on distributed systems and have also been extended to heterogeneous platforms such as GPU [31] and FPGA [32], but unfortunately have a restricted programming model. The StarSs model builds a task-level model using a pragma-based approach (similar to OpenMP) to ease the burden of task-level programming for different architectures; its instantiations include Cell Superscalar [33] for the Cell broadband engine and GPUSs [34] for a system with multiple accelerators. Dryad [35] is a research project at Microsoft Research for a general-purpose runtime data-parallel applications. An application written for Dryad is modeled as a directed acyclic graph (DAG). However, its focus is on the multi-core cluster platform and does not provide sufficient heterogeneity support.

We have installed the CnC-HC and Habanero-C runtime on the platform to provide the runtime and the high-level implementation flow for heterogeneous computing. The Habanero-C (HC) language [36] is a parallel programming model developed at Rice University in the Habanero Research project. Habanero-C has two basic primitives for the task parallel programming model borrowed from X10 [37]: async and finish.

The async statement ( async  $\langle \text{ stmt } \rangle$  or async { stmt1 .. stmtN } ) causes the current executing thread to fork a new child task that will execute one or more statements. The parent task continues executing the statements that follow the async statement and does not wait for the child task to finish its execution. The finish statement ( finish  $\langle \text{ stmt } \rangle$  or finish { stmt1 .. stmtN } ) performs a join operation. Consider a thread that executes the statements inside a finish scope. These may spawn one or more children, but no instructions which follow the finish scope are allowed to start executing until all such children, grandchildren, etc., have finished executing. The language permits any level of nesting of the async and finish scopes, and supports terminally-strict computation and multiple scheduling policies (work-first or help-first) [38], which is more general than Cilk [39] that realizes spawn-sync computations which must be fully-strict and work-first.

For locality, Habanero-C uses Hierarchical Place Trees (HPTs) [40]. HPTs define hierarchical trees of execution location, which are an abstraction for underlying hardware. These places could be cores, groups of cores sharing different levels of cache, or devices such as GPUs or FPGAs. The HC language allows the programmer to spawn a task explicitly at such a place, and the work-stealing runtime is designed to take advantage of this information and preserve locality. The Habanero-C runtime uses a work-stealing scheduler that supports cross-device stealing. An FPGA can steal from a task queue for GPU and vise-versa.

Concurrent Collections (CnC) is a macro dataflow model developed by Intel [5] for execution of C++ programs on homogeneous multicore processors. CnC is a general programming model, while the CnC-HC is a specific instantiation of the model. CnC-HC was developed on top of the Habanero C (HC) programming language, and it uses the async and finish constructs available in HC. However, not all dependency graphs can be expressed using only async and finish, so we need a CnC runtime. CnC-HC took a new and different approach from those in previous instantiations of the CnC model—that of spawning a step only when all data is available in order to eliminate the overhead of repeated task creation when necessary. To better aid the user in specifying the preference of task binding, we added the affinity field in the CnC description. For each task in the CnC dataflow, users can specify a numerical value for each processor/coprocessor (a larger value denotes a greater preference). More details on CnC-HC are in [41].

# CHAPTER 3

# FPGA/GPU Accelerated Lithography Simulation

#### 3.1 Introduction

Optical lithography is the technology used for printing circuit patterns onto wafers. As the technology scales down, and the feature size is even smaller than the wavelength of the light employed (e.g., 193nm lithography), significant light interference and diffraction may occur during the imaging process. Lithography simulation, which tries to simulate the imaging process or the whole lithography process— from illumination to mask to imaging to resist—is considered an essential technique for the emerging field of DFM.

Lithography simulation can be done through various methods with different accuracy. Model- or rule-based optical proximity correction (OPC) uses empirical rules and models from experimental data to perform the simulation and discover the defects caused by lithography [42]. It is fast but not accurate enough. On the other hand, using finite difference or finite element methods to solve the corresponding electromagnetic equations directly [43] is a very accurate approach, but is so expensive that it can only simulate small regions and designs.

The coherent decomposition method [44] can better balance the accuracy and running time, and is the main method used in computational lithography for large designs. It first decomposes the whole optical imaging system into many coherent systems with decreasing importance. The image corresponding to each coherent system can be obtained via numerical image convolution, and the final image is the weighted sum of the image of each coherent system. However, the method still needs a large amount of CPU time to perform the simulation because the number of layers and the size of images are large. As the technology scales down and the accuracy requirement goes up, it will be more challenging to meet the tight requirement of design turn-round time.

Leading commercial computational lithography products have already started to use special coprocessor acceleration to further accelerate computation. Brion Technologies (now part of ASML) reports that each leaf node composed of two CPUs and four FPGAs in their Tachyon System can achieve 20X speedup over one single CPU node [45]. Mentor Graphics uses the Cell Broadband Engine to accelerate the computation in their nmOPC product [46]. Clear Shape Technologies has filed patents for using GPUs to accelerate the computation [47].

We present a new hardware implementation for accelerating lithography imaging simulation on FPGA platforms. Unlike the image-based approach Brion takes, which ultimately relies on the accelerated performance of 2D-FFT, we use the polygon-based approach [48, 49] instead. The polygon-based approach makes use of the fact that the actual layouts are solely composed of rectilinear shapes, and it has comparable or even better performance than an image-based approach in software implementation. Recent advances in OPC algorithms, e.g., IB-OPC [50], also employ a polygon-based approach for lithography intensity simulation. Moreover, the polygon-based approach pre-computes the convolution and stores that into a look-up table, and the subsequent computation mainly just involves some additions and subtractions on the look-up value. Thus the polygon-based approach could be better approximated via fixed-point computations without sacrificing much accuracy. The algorithm can be better parallelized and accelerated by utilizing the high bandwidth of on-chip memory in FPGA.

Another unique aspect of our work is that we leverage state-of-art C to HDL compilation tools and write all our design in C, whereas the FPGA accelerator design by Brion [45] was based on completely manual RTL coding. A design described in higher-level languages such as C/C++ is more portable to various platforms and easier to maintain. Also these tools could evaluate multiple design choices faster and perform various kinds of optimizations for improved performance against the RTL-based design, but those tools also have limitations on the supported language features. The challenge we experienced for this design is that of manually developing an efficient memory partitioning scheme, based on the observation of the memory access pattern, to provide a large data bandwidth for a larger number of processing elements. Deep loop pipelining and the overlapping of the communication and computation via ping-pong buffers are also implemented to take advantage of both instruction-level parallelism and task-level parallelism. All the design techniques are represented at algorithmic level in the code refinement/rewriting of ANSI C, and the resulting C code is further synthesized into RTL though the automatic C-to-RTL synthesis tools.

## 3.2 Basics for Aerial Image Simulation

#### 3.2.1 The Imaging Equation

The coherent decomposition method first decomposes the whole optical system, into a series of coherent optical systems (using eigenvalue decomposition). The series is truncated to a finite one based on the ranking of the eigenvalues. If we only keep K significant eigenvalues and eigenvectors, the image can be computed as:

$$I(x,y) \approx \sum_{k=1}^{K} \lambda_k |(O \otimes \phi_k)(x,y)|^2$$

(3.1)

Here the I(x, y) is the image intensity,  $\lambda_k$  is the  $k^{th}$  eigenvalue, O(x, y) is the object function (field) and  $\phi_k(x, y)$  is the  $k^{th}$  eigenvector. The symbol  $\otimes$  denotes convolution (2D image convolution). For more details on the derivation of the coherent decomposition method, please refer to [51].

One way to perform the 2D image convolution is through 2D FFT. We can first transform the padded object pattern (see Section 3.2.3) and the eigenvector into the frequency domain via 2D FFT. (Note the FFT of the eigenvector  $\phi_k$  only needs to be computed once and can be reused.) Then we multiply the eigenvector and object pattern in the frequency domain. Finally we can obtain the convolution result via an inverse FFT of the multiplied result. This is the image-based simulation that is also used by [45].

As the actual layout of VLSI circuits is only composed of polygons (or rectangles if we perform polygon decomposition on the layout), the convolution of different sizes of polygon-

Figure 3.1: Rectilinear polygons can be processed similar to rectangles

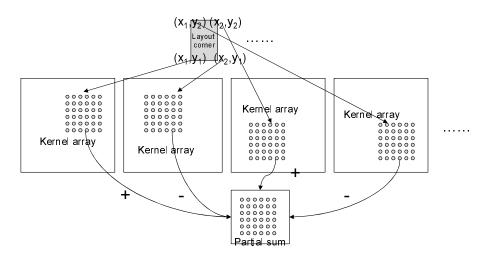

s/rectangles can be pre-computed and stored. We first consider purely rectangle cases. The convolution for an object pattern solely composed of N rectangles with vertices at  $(x_1^{(n)}, y_1^{(n)})$ ,  $(x_2^{(n)}, y_1^{(n)})$ ,  $(x_1^{(n)}, y_2^{(n)})$ ,  $(x_2^{(n)}, y_2^{(n)})$ ,  $(x_2^{(n)}, y_2^{(n)})$ ,  $(x_2^{(n)}, y_2^{(n)})$ , can be simplified via quadrant functions.

The object pattern in one padded area can be written as:

$$O(x,y) = \sum_{n=1}^{N} [Q(x - x_1^{(n)}, y - y_1^{(n)}) - Q(x - x_2^{(n)}, y - y_1^{(n)}) + Q(x - x_2^{(n)}, y - y_2^{(n)}) - Q(x - x_1^{(n)}, y - y_2^{(n)})]$$

(3.2)

where quadrant function

$$Q(x,y) = \begin{cases} 1 & if \ x \ge 0 \ and \ y \ge 0 \\ 0 & otherwise \end{cases}$$

The convolution equation thus can be rewritten as:

$$I(x,y) \approx \sum_{k=1}^{K} \lambda_{k} |(O \otimes \phi_{k})(x,y)|^{2}$$

=

$$\sum_{k=1}^{K} \lambda_{k} |\sum_{n=1}^{N} [\psi_{k}(x - x_{1}^{(n)}, y - y_{1}^{(n)}) - \psi_{k}(x - x_{2}^{(n)}, y - y_{1}^{(n)}) + \psi_{k}(x - x_{2}^{(n)}, y - y_{2}^{(n)}) - \psi_{k}(x - x_{1}^{(n)}, y - y_{2}^{(n)})]|^{2}$$

(3.3)

where

$$\psi_k(x,y) = Q(x,y) \otimes \phi_k(x,y)$$

is the convolution of the quadrant function with the  $k^{th}$  eigenvector. This is the polygon/rectanglebased algorithm we use, and it is described in more detail in [49].

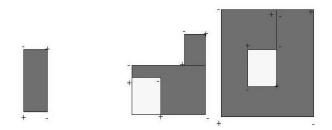

For rectilinear polygons, an equation similar to Equation 3.2 can be written using quadrant functions on each vertex of the polygons. In Figure 3.1, we label the + and - on the vertexes of rectilinear polygons (the rectangle is simply a special type of rectilinear polygon, and + and - are just the signs for the look-up value for the vertexes; see Equation 3.2 and Equation 3.3 for the rectangle case). We go from a vertex which is at bottom-left, and label that with + and go around the border of the polygon and label that with - and +respectively.

Using rectangles or polygons will not alter the overall algorithm and design presented in the following. For simplicity and benchmarking purposes, we assume we are given N rectangles with 4N vertexes for one region of the image in the subsequent illustration, while our litho simulation tool, which goes from GDSII to simulated image, is also capable of processing polygons from the GDSII directly without the need for rectangle decomposition.

#### 3.2.2 Image-Based Simulation versus Polygon-Based Simulation

It is worthwhile to briefly discuss the trade-offs between image-based simulation and polygonbased simulation. Image-based simulation first converts the layout, which in most cases is stored in GDSII, into an object image, and then gets the image convolution via FFT and IFFT. Note that only image-based simulation needs to take this additional conversion step from the GDSII to the object image, which might also be expensive. The 2D-FFT algorithm, although well studied, still needs a large number of floating-point operations. On the other hand, the polygon-based algorithm can use fixed-point computation without losing much accuracy, and thus can be implemented without using any floating-point operations. Suppose the rounding error for the elements in  $\psi_k$  in Equation 3.3 is  $2^{-p}$ , the absolute error for computing  $\sum_{n=1}^{N} [\psi_k(x - x_1^{(n)}, y - y_1^{(n)}) - \psi_k(x - x_2^{(n)}, y - y_1^{(n)}) + \psi_k(x - x_2^{(n)}, y - y_2^{(n)}) - \psi_k(x - x_2^{(n)}, y - \psi_k(x - x_2^{(n)}) - \psi_k(x - x_2^{(n)}$  $\psi_k(x-x_1^{(n)},y-y_2^{(n)})$  is bounded by  $4N * 2^{-p}$ . If we assume the error distribution for the elements in  $\psi_k$  is a uniform distribution between  $-2^{-p}$  and  $2^{-p}$ , the error distribution of the sum  $\sum_{n=1}^{N} [\psi_k(x - x_1^{(n)}, y - y_1^{(n)}) - \psi_k(x - x_2^{(n)}, y - y_1^{(n)}) + \psi_k(x - x_2^{(n)}, y - y_2^{(n)}) - \psi_k(x - x_1^{(n)}, y - y_2^{(n)}) - \psi_k(x - x_1^{(n)}, y - y_1^{(n)}) - \psi_k(x - x_1^{(n)}, y - \psi_k(x - x_1^{(n)}) - \psi_k(x - x_1^{(n)}) - \psi_k(x - x_1^{(n)})$  $y_2^{(n)}$ ] follows uniform sum distribution. Its variance is proportional to N and the standard deviation is proportional to  $\sqrt{N}$ ; thus the actual error is much smaller, statistically, than the conservative error bound which is linear with N.

Both algorithms scale linearly with the number of pixels to compute. The issue of the polygon-based approach is that the running time will also depend on the layout density, which determines the number of polygons or rectangles in a unit area within the interaction range (N in Equation 3.3), while the image-based approach only depends on the chip area. We implemented the 2D-FFT based 2D-convolution using the FFTW package [52], and tested that on kernels with size 400 by 400. We found that the running time is comparable to a polygon-based method with a moderate density (see Section 3.5.3). The polygon-based approach requires less computation and runs faster for layers that are not very dense, and the image-based approach runs faster for very dense layers. Note that the polygon-based approach also saves the step on conversion from polygons to images, as polygons are naturally stored in GDSII.

In terms of the FPGA-based acceleration, FFT is still tightly constrained by the available DSP units or logic slices, and the peak FLOPs of FPGA are at the same magnitude with the peak FLOPs of modern CPU; thus, typically only a 2 to 8X speedup is seen on accelerating FFT on FPGA platforms via parallel implementation [53]. Fixed-point FFT core for FPGA is also available and gives potentially larger speedup, but it will have worse accuracy because multiplication can enlarge the absolute error. For the polygon-based approach, the convolution on the quadrant function can be pre-computed using highly accurate floating-point computations (on CPU) and reused multiple times. The time to pre-compute the convolution can be ignored as it is a one-step process. The remaining computations only involve table look-up and simple addition/subtraction operations, and are much more suitable for a decent speedup. Therefore, in this work we use the polygon/rectangle-based approach rather than the image-based approach for accelerator design.

# 3.2.3 Detailed Settings for the Imaging Equation Using the Polygon-Based Approach

We assume that the convolutions of eigenvectors and the quadrant functions are already precomputed, and sampled into a 2D array called *kernel*. The region/range of the kernel we use is 2000nm by 2000nm; it is sampled on a 5nm grid, and thus contains 400 by 400 numbers. The image we need to compute is on a 25nm grid. Without loss of generality, we assume the layout corners (vertexes of the polygons) are also on the 5nm grid. (If the layout corner is on a much finer grid, interpolation will be used to get the kernel value.) These settings used in our algorithm and implementation were recommended by our industry collaborators from Magma Design Automation [54], but our architecture certainly is not confined to these settings and can be extended to other settings. Some setting changes require a recompile/resynthesis while some do not. This depends on whether the change of underlying hardware is needed. For example, the design synthesized with a large N (layout density metric) can be used for a smaller N without the need of changing hardware. On the other hand, enlarging array sizes or changing the memory partitioning schemes will affect the underlying hardware and a recompile/re-synthesis will be needed to generate the new hardware bitstreams.

## 3.3 FPGA-based Accelerator for the Imaging Simulation

#### 3.3.1 Image Padding for the Polygon-based Approach

Both the object pattern and the simulated image are large; however, when we compute one region of the image, only one padded region of the object needs to be considered due to the locality of the litho effects. For example, for a kernel ranges within a 2000nm by 2000nm area, if we want to compute a 1000nm by 1000nm image region, an object pattern within a range of 3000nm by 3000nm needs to be taken into computation. The reason for this is that some objects are far away from the current pixel and out of the interaction range, and therefore need not be considered.

The computation complexity is proportional to the number of rectangles N taken into computation, and the intensity of each pixel is determined by the rectangles within the interaction range (2000nm by 2000nm in our case) around this pixel.

```

for (x=0;x<pixel_max;x++)

for (y=0;y<pixel_max;y++)</pre>

{

//Initialize pixel intensity

I[x][y]=0;

for (k=0;k<K;k++)

{

//Initialize partial sum

I_{k}[x][y]=0;

//Core computation

for (n=0;n<4*N;n++)

{

addr_x = 5 * x - rect_x[n] + c;

addr_y = 5*y - rect_y[n] + c;

\mathbf{I}_{-}\mathbf{k} \;[\; \mathbf{x} \;] \;[\; \mathbf{y}] {+} {=} (-1)^n * \mathbf{k} \operatorname{ernel} \left[\; \mathbf{k} \;\right] \left[\; addr_x \;\right] \left[\; addr_y \;\right];

}

I [x] [y] += I_k [x] [y] * I_k [x] [y];

}

}

```

Figure 3.2: Pseudo-code for the nested loop

```

//Initialize pixel intensity

for (x=0;x<pixel_max;x++)</pre>

for (y=0;y<pixel_max;y++)</pre>

I[x][y]=0;

for (k=0;k<K;k++)

{ //Initialize partial sum

for (x=0;x<pixel_max;x++)

for (y=0;y<pixel_max;y++)</pre>

I_{k}[x][y]=0;

//The core computation

for (n=0;n<4N;n++)

for (x=0;x<pixel_max;x++)</pre>

for (y=0;y<pixel_max;y++)</pre>

{

addr_x = 5 \times -rect_x[n] + c;

addr_y = 5*y - rect_y[n] + c;

I_k[x][y] += (-1)^n * kernel[k][addr_x][addr_y];

}

//Square operation

for (x=0;x<pixel_max;x++)</pre>

for (y=0;y<pixel_max;y++)</pre>

I[x][y] += I_k[x][y] * I_k[x][y];

}

```

Figure 3.3: Pseudo-code for the rearranged nested loop

#### 3.3.2 Rearranging the Nested Loop