## **UC Irvine**

#### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Three-Dimensional NoC Reliability Evaluation Automated Tool (TREAT)

#### **Permalink**

https://escholarship.org/uc/item/0s0855fv

#### **Author**

Eghbal, Ashkan

#### **Publication Date**

2016

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Three-Dimensional NoC Reliability Evaluation Automated Tool (TREAT)

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Ashkan Eghbal

Dissertation Committee: Professor Nader Bagherzadeh, Chair Professor Jean-Luc Gaudiot Professor Pai H. Chou

Portion of Chapter 3 © 2015 Elsevier-The VLSI Journal on Integration Chapter 4 © 2015 IEEE-Transactions on Computers

Portion of Chapter 6 © 2015 ACM-Symposium on Networks-on-Chip

Portion of Chapter 7 © 2015 IEEE-Transactions on Computers

Portion of Chapter 7 © 2015 IEEE-VLSI Test Symposium

Portion of Chapter 7 © 2014 IEEE-Defect and Fault Tolerance in VLSI and Nanotechnology Systems

# **DEDICATION**

I dedicate my dissertation work to my parents and many friends. A special feeling of gratitude to my loving parents, for their endless love, support, and encouragement. I also dedicate this dissertation to my many friends who have supported me throughout the process.

# TABLE OF CONTENTS

|              |       |                                                            | Page |

|--------------|-------|------------------------------------------------------------|------|

| $\mathbf{L}$ | IST ( | OF FIGURES                                                 | vi   |

| $\mathbf{L}$ | IST ( | OF TABLES                                                  | viii |

| $\mathbf{A}$ | CKN   | IOWLEDGMENTS                                               | ix   |

| $\mathbf{C}$ | URR   | CICULUM VITAE                                              | X    |

| $\mathbf{A}$ | BST   | RACT OF THE DISSERTATION                                   | xiii |

| 1            | Inti  | roduction                                                  | 1    |

|              | 1.1   | The Future Design Trends                                   | 2    |

|              |       | 1.1.1 Moving from Single Core to Many-core                 | 3    |

|              |       | 1.1.2 Moving from 2D to 3D Integration                     | 4    |

|              |       | 1.1.3 Moving from Bus-based to Network-based Interconnects | 5    |

|              |       | 1.1.4 3D NoC                                               | 6    |

|              | 1.2   | Reliability of 3D NoC                                      | 8    |

|              | 1.3   | Contribution of this Thesis                                | 10   |

|              | 1.4   | Similar Tools                                              | 12   |

|              | 1.5   | Dissertation Outline                                       | 16   |

| 2            | Dep   | pendability Threats and Means                              | 17   |

|              | 2.1   | Dependability Threats                                      | 18   |

|              |       | 2.1.1 Fault                                                | 18   |

|              |       | 2.1.2 Error                                                | 19   |

|              |       | 2.1.3 Failure                                              | 20   |

|              | 2.2   | Dependability Means                                        | 22   |

|              |       | 2.2.1 Fault Prevention                                     | 22   |

|              |       | 2.2.2 Fault Tolerance                                      | 23   |

|              |       | 2.2.3 Fault Removal                                        | 25   |

|              |       | 2.2.4 Fault Forecasting                                    | 25   |

|              | 2.3   | Fault Injection                                            | 26   |

| 3 | $Th\epsilon$      | 3D N                                        | IoC Architecture 30                                                                                                                                                                                                                       |

|---|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1               | Basic                                       | Definitions                                                                                                                                                                                                                               |

|   |                   | 3.1.1                                       | Flit and Physical Unit (phit)                                                                                                                                                                                                             |

|   |                   | 3.1.2                                       | Flow Control                                                                                                                                                                                                                              |

|   |                   | 3.1.3                                       | Routing Algorithm                                                                                                                                                                                                                         |

|   |                   | 3.1.4                                       | Topology                                                                                                                                                                                                                                  |

|   | 3.2               | The 3                                       | D NoC Router Architecture                                                                                                                                                                                                                 |

|   |                   | 3.2.1                                       | Links                                                                                                                                                                                                                                     |

|   |                   | 3.2.2                                       | NI                                                                                                                                                                                                                                        |

|   |                   | 3.2.3                                       | Buffer                                                                                                                                                                                                                                    |

|   |                   | 3.2.4                                       | Routing Management Unit                                                                                                                                                                                                                   |

|   |                   | 3.2.5                                       | Crossbar Switch                                                                                                                                                                                                                           |

|   | 3.3               | Propo                                       | sed TagNoC Routing Method                                                                                                                                                                                                                 |

|   |                   | 3.3.1                                       | Scalability                                                                                                                                                                                                                               |

|   |                   | 3.3.2                                       | Performance                                                                                                                                                                                                                               |

|   |                   | 3.3.3                                       | Power Consumption                                                                                                                                                                                                                         |

|   |                   | 3.3.4                                       | Frequency Results                                                                                                                                                                                                                         |

|   |                   | 3.3.5                                       | Area Analysis                                                                                                                                                                                                                             |

| 4 | 4.1<br>4.2<br>4.3 | Physic<br>4.1.1<br>4.1.2<br>4.1.3<br>Logic- | Challenges in 3D NoC  Cal-level Potential Faults in 3D NoC  TSV Issues  Thermal Concerns  Single Event Effect (SEE) Impacts level Fault Models  Effects on 3D NoC  59  60  60  67  67  68  67  68  69  69  69  69  60  60  60  60  60  60 |

| 5 | TR                | елт б                                       | ramework 73                                                                                                                                                                                                                               |

| J | 5.1               |                                             | AT Components                                                                                                                                                                                                                             |

|   | 5.2               |                                             | Fault Models in TREAT                                                                                                                                                                                                                     |

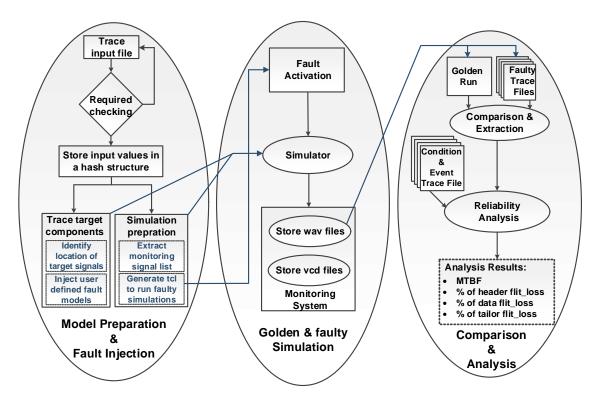

|   | 0.2               | 5.2.1                                       | Model Preparation and Fault Injection                                                                                                                                                                                                     |

|   |                   | •                                           | Golden and Faulty Simulation                                                                                                                                                                                                              |

|   |                   | 5.2.3                                       | Comparison and Analysis                                                                                                                                                                                                                   |

|   | 5.3               |                                             | mic Fault Models in TREAT                                                                                                                                                                                                                 |

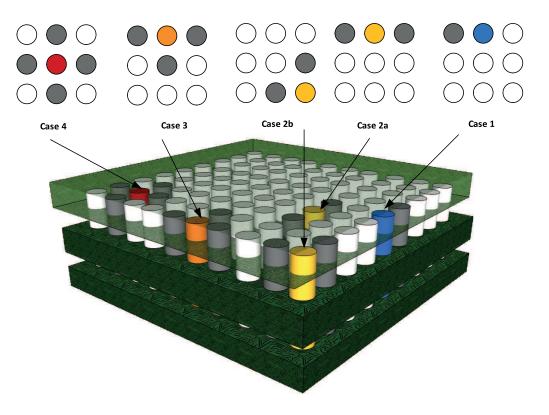

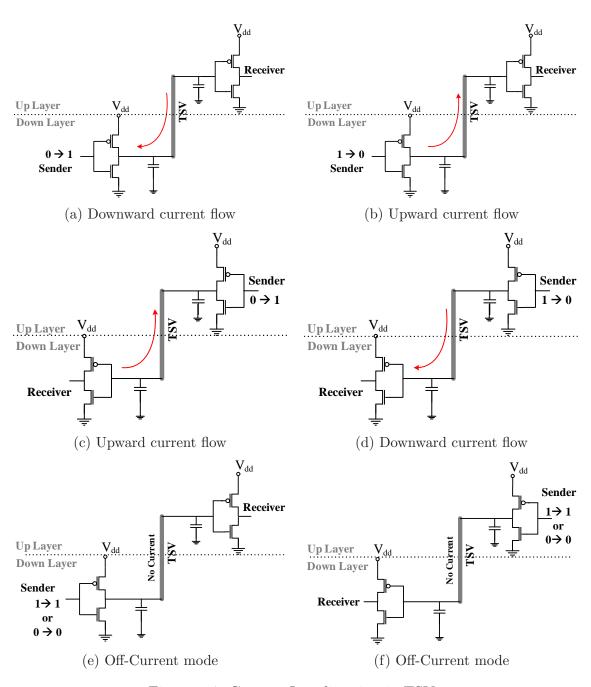

|   | 0.0               | 5.3.1                                       | Current Direction in TSV                                                                                                                                                                                                                  |

|   |                   | 5.3.2                                       | CTTC Circuit-level Modeling                                                                                                                                                                                                               |

|   |                   | 5.3.3                                       | CTTC Effect on TV                                                                                                                                                                                                                         |

|   |                   | 5.3.4                                       | CTTC Classification                                                                                                                                                                                                                       |

|   |                   | 5.3.5                                       | CTTC Fault Model                                                                                                                                                                                                                          |

|   |                   | 0.0.0                                       | 011010001                                                                                                                                                                                                                                 |

| 6 | TR                |                                             | Evaluation 97                                                                                                                                                                                                                             |

|   | 6.1               |                                             | Fault Injection Parameters and Experimental Results 98                                                                                                                                                                                    |

|   |                   | 6.1.1                                       | Static Fault Injection Characteristics                                                                                                                                                                                                    |

|   |                   | 6.1.2                                       | Experimental Results                                                                                                                                                                                                                      |

|   | 6.2               | Dynar                                       | nic Fault Injection Parameters and Experimental Results 101                                                                                                                                                                               |

|    |       | 6.2.1   | Fault model accuracy                             | 103 |

|----|-------|---------|--------------------------------------------------|-----|

|    |       | 6.2.2   | CTTC Fault Characterization                      | 104 |

| 7  | Fau   | lt Miti | igation Codings for TSV-based 3D ICs             | 107 |

|    | 7.1   | Propo   | sed TCMA Technique                               | 107 |

|    |       | 7.1.1   | Baseline TCMA                                    | 108 |

|    |       | 7.1.2   | Enhanced TCMA                                    | 109 |

|    |       | 7.1.3   | TCMA Elaboration and Evaluation                  | 114 |

|    | 7.2   | Induct  | tive TSV-to-TSV Coupling Analysis and Mitigation | 119 |

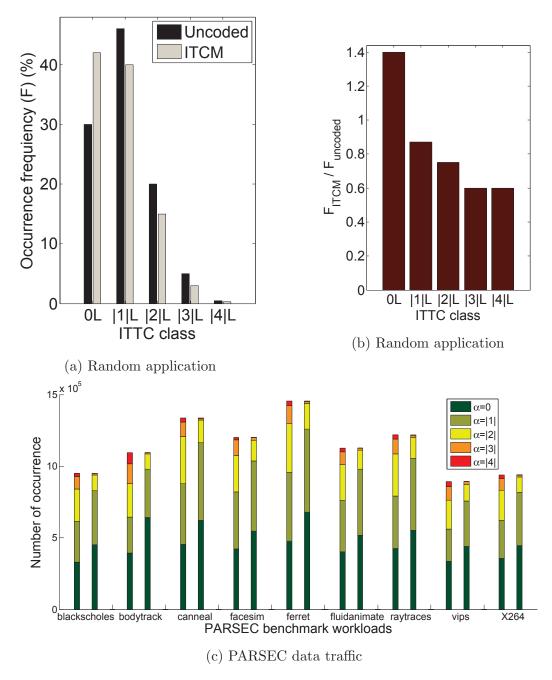

|    |       | 7.2.1   | ITTC Characteristics                             | 120 |

|    |       | 7.2.2   | Proposed ITCM Technique                          | 124 |

|    |       | 7.2.3   | ITCM Method Evaluation                           |     |

| 8  | Con   | clusio  | n                                                | 130 |

| Bi | bliog | graphy  |                                                  | 133 |

# LIST OF FIGURES

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                   |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1<br>1.2<br>1.3                                                   | SoC consumer portable design complexity trends [44]                                                                                                                                                                                                                                                                                                                                                                                             | 5                                      |

| 2.1<br>2.2<br>2.3                                                   | Fault, error, and failure                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                     |

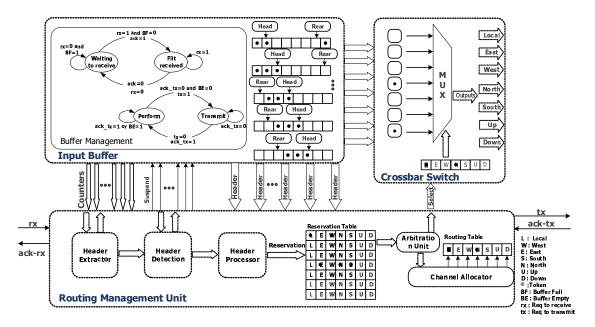

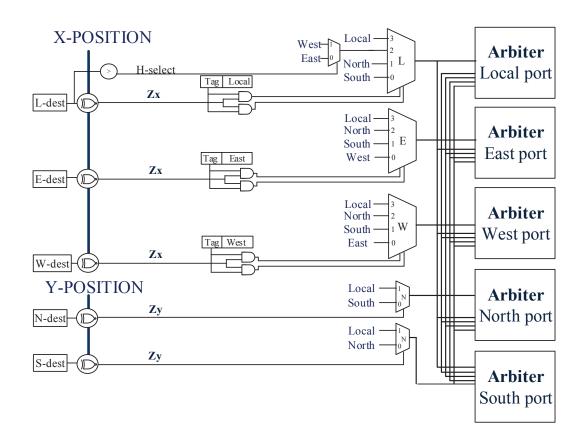

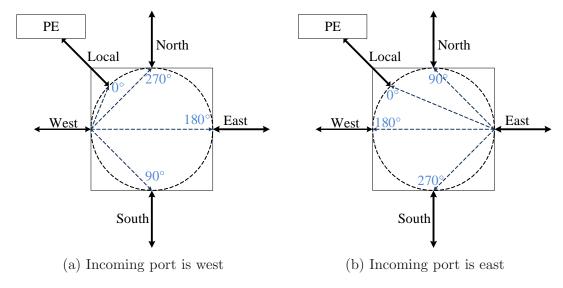

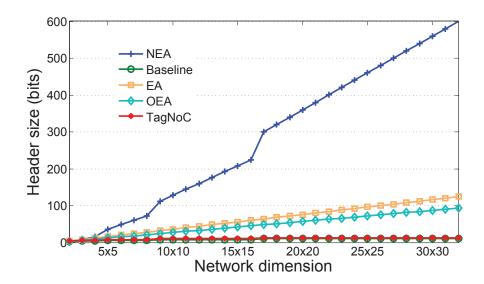

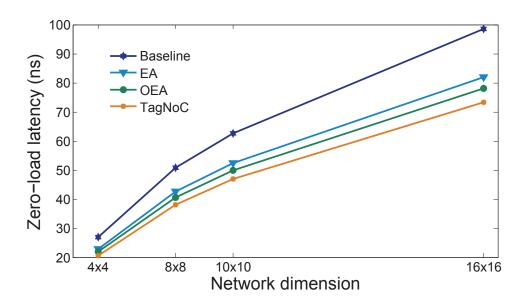

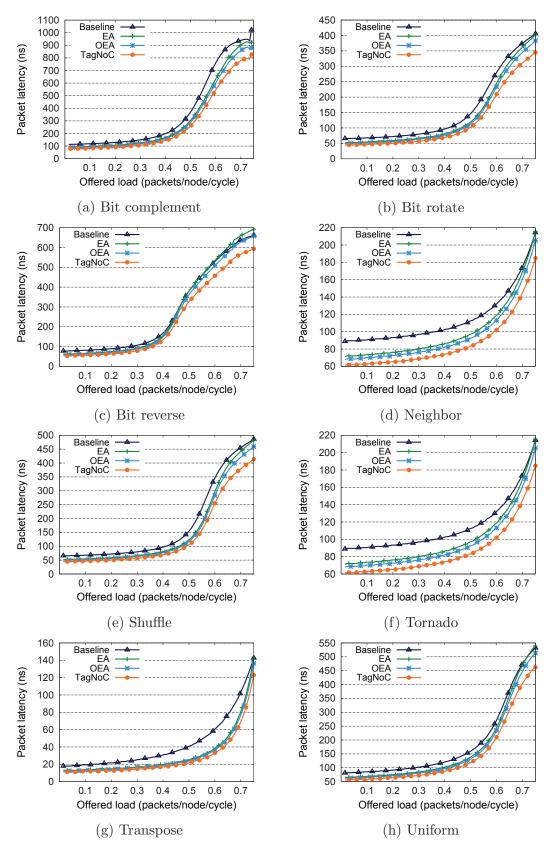

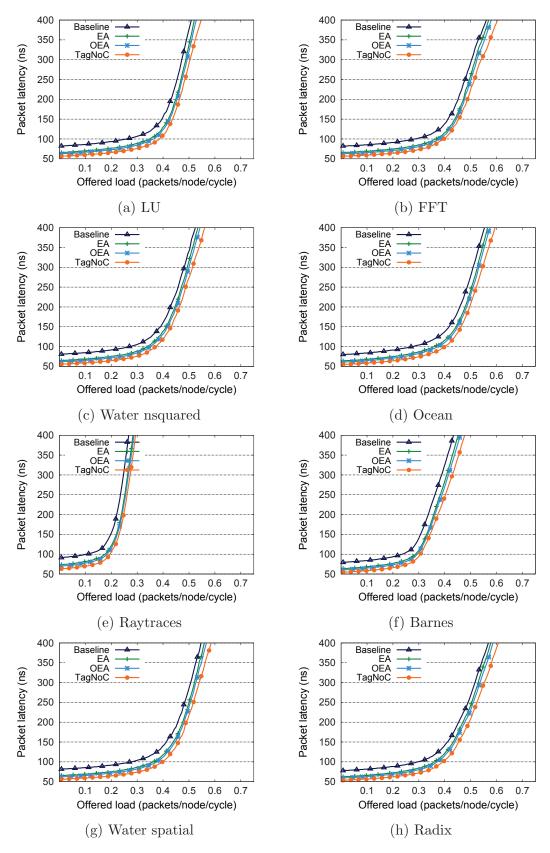

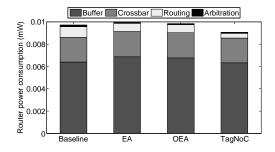

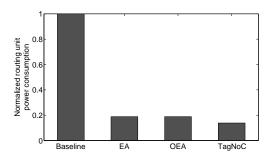

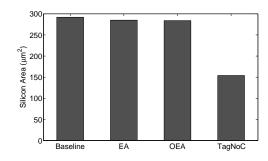

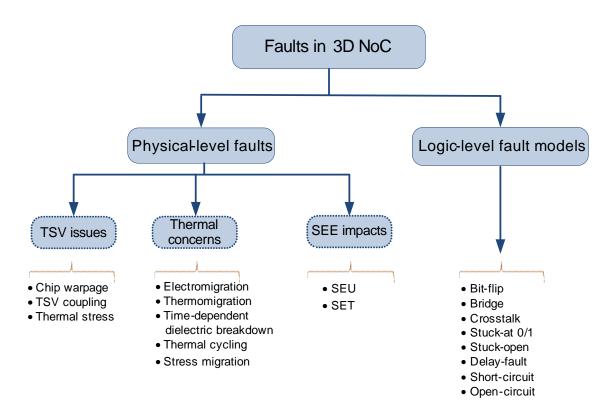

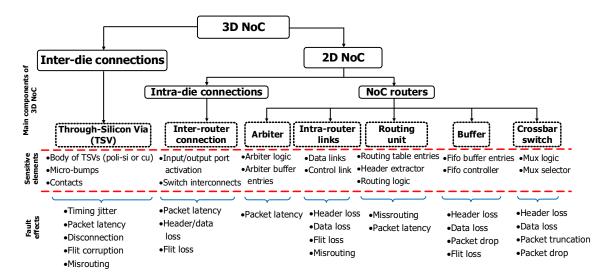

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | TSV-based 3D NoC and TSV top view  Example of NI functionality  3D NoC router architecture  TagNoC architecture for a 5-port NoC router  Port forwarding directions  Routing overhead bits in the header flit vs. number of nodes  Zero-load latency versus different network size  Average packet latency under synthetic traffic  Average packet latency under SPLASH-2 application traffic  Power consumption and area occupation comparison | 40<br>41<br>46<br>47<br>49<br>51<br>52 |

| 4.1<br>4.2                                                          | Potential physical-level and logic-level faults in 3D NoC Classification of faults and their effects in 3D NoC components                                                                                                                                                                                                                                                                                                                       |                                        |

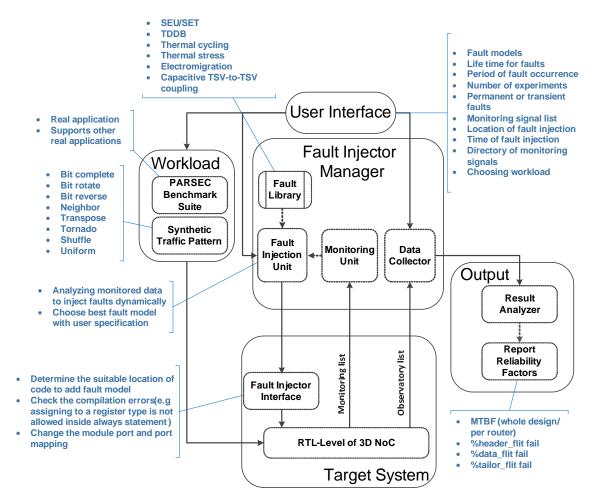

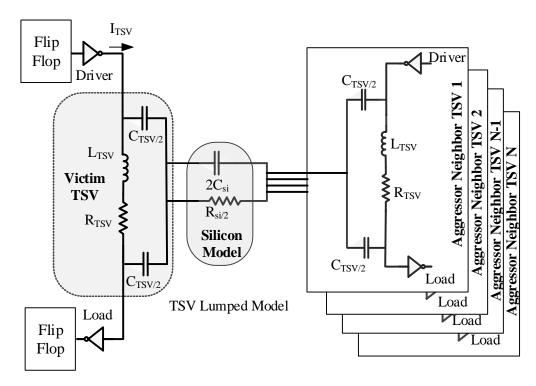

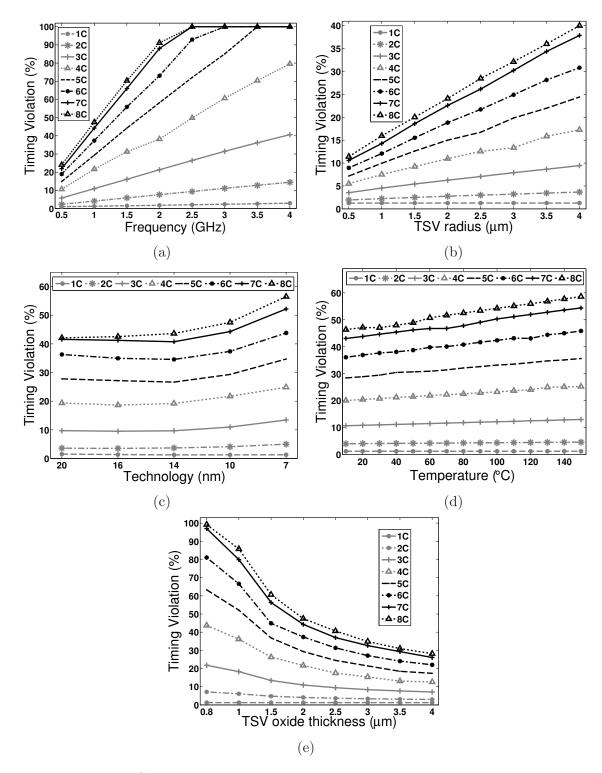

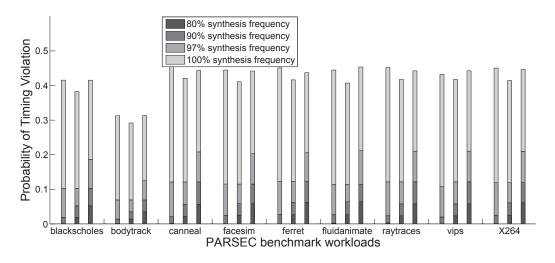

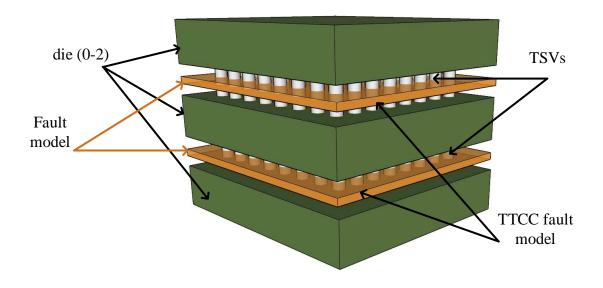

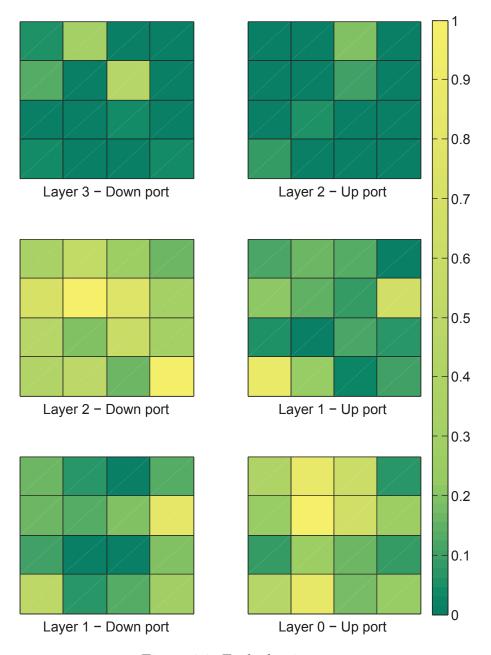

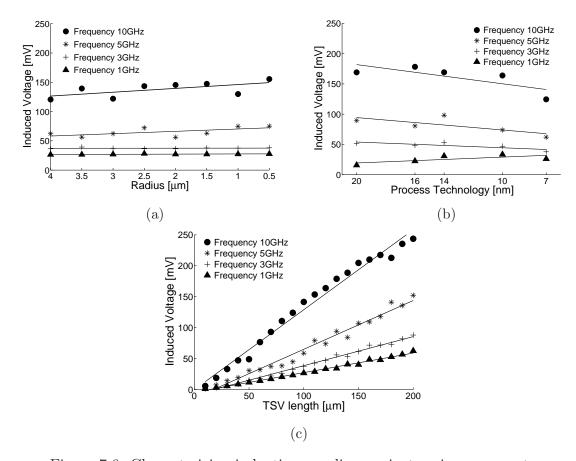

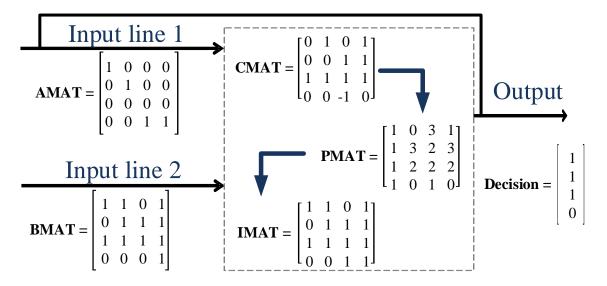

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9         | TREAT components  TREAT phases  Different TSV patterns leading to various TSV coupling classes  Current flow direction in TSV.  Circuit-level of victim TSV and its neighbors  Characterizing capacitive coupling against various parameters  Probability of TV for PARSEC benchmark workloads  Current and CTTC matrices in a 3 × 3 mesh of TSVs  Fault model usage demonstration in 3D-NoC                                                    | 77<br>83<br>84<br>86<br>88<br>90       |

| 6.1<br>6.2<br>6.3<br>6.4                                            | Header, data, tailor flit failure rate                                                                                                                                                                                                                                                                                                                                                                                                          | 101<br>102                             |

| 6.5 | Fault model usage demonstration in 3D-NoC                            | 105 |

|-----|----------------------------------------------------------------------|-----|

| 6.6 | Fault density map                                                    | 106 |

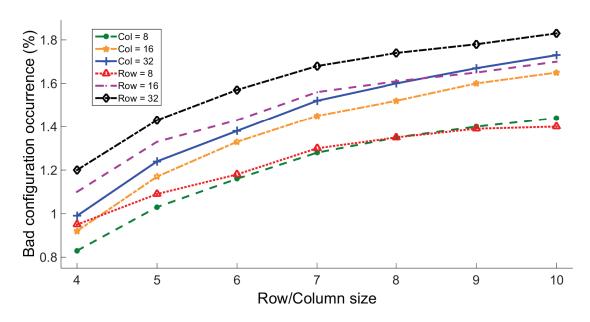

| 7.1 | Probability of bad configuration occurrence                          | 109 |

| 7.2 | Potential configurations to generate 7C and 8C capacitive coupling . | 111 |

| 7.3 | An example that shows baseline algorithm issues                      | 115 |

| 7.4 | Number of 7C/8C for random data bit patterns in small mesh of TSVs   | 116 |

| 7.5 | 7C and 8C capacitive coupling for random and PARSEC applications     | 117 |

| 7.6 | Characterizing inductive coupling against various parameters         | 121 |

| 7.7 | 4x4 mesh of TSV example of ITCM                                      | 127 |

| 7.8 | Evaluating the efficiency of ITCM for an $8 \times 8$ TSV bus        | 129 |

# LIST OF TABLES

|     |                                                                  | Page |

|-----|------------------------------------------------------------------|------|

| 3.1 | Horizontal direction                                             | 45   |

| 3.2 | Vertical direction                                               | 45   |

| 3.3 | Header size comparison of proposed methods                       | 47   |

| 3.4 | System configuration parameters                                  | 53   |

| 3.5 | NI power overhead for extra routing information computation      | 56   |

| 3.6 | Router clock periods                                             | 57   |

| 4.1 | Physical faults and their corresponding logic-level fault models | 69   |

| 5.1 | CTTC categorization with occurrence probability of each type     | 92   |

| 5.2 | Different configuration of TSV arrays                            | 93   |

| 6.1 | System configuration parameters                                  | 98   |

| 6.2 | Fault injection distribution                                     | 99   |

| 7.1 | Current flow of tsvs before and after encoding                   | 110  |

| 7.2 | Hardware synthesize results                                      |      |

| 7.3 | ITTC categorization with occurrence probability of each type     | 122  |

| 7.4 | Hardware synthesis results of ITCM                               | 129  |

# **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to my adviser, Prof. Nader Bagherzadeh for offering the opportunity for a PhD in addition to his guiding and supporting me over the years. He has set an example of excellence as a researcher, mentor, and role model.

I would like to thank my thesis committee members, Prof. Jean-Luc Gaudiot and Prof. Pai H. Chou, for their insightful comments; their discussions, ideas, and feedbacks have been absolutely invaluable.

I would like to thank my labmate, Pooria M. Yaghini and my collaborator Siavash S. Yazdi, who contributed to this research. I am very grateful to both of you.

I would like to thank IEEE, Elsevier, and ACM publishers who have given me the permission to incorporate my previous published work with them into my dissertation.

# CURRICULUM VITAE

## Ashkan Eghbal

#### EDUCATION:

| • Doctor of Philosophy in Computer Engineering | 2016               |

|------------------------------------------------|--------------------|

| University of California, Irvine               | Irvine, California |

| • Master of Science in Computer Engineering    | <b>2010</b>        |

| Amirkabir University of Technology of Tehran   | Tehran, Iran       |

| • Bachelor of Science in Computer Engineering  | 2007               |

| Azad University of Iran, Central Branch        | Tehran, Iran       |

#### RESEARCH EXPERIENCE:

| • Graduate Research Assistant<br>University of California, Irvine | <b>2010–2016</b><br>Irvine, California |

|-------------------------------------------------------------------|----------------------------------------|

| • Graduate Research Assistant                                     | 2008-2010                              |

| Amirkabir University of Technology of Tehran                      | Tehran, Iran                           |

#### TEACHING EXPERIENCE:

| • Lecturer                                            | Long Beach, California |

|-------------------------------------------------------|------------------------|

| Microprocessors and Controllers III                   | Spring 2016            |

| Data Structure and Algorithms                         |                        |

| Digital Circuit Design I                              | Fall 2015              |

| Computer Organization and Assembly Programming        |                        |

| Dept. of CECS, California State University of Long Be | ach                    |

| • Teaching Associate                            | Irvine, California |

|-------------------------------------------------|--------------------|

| Introduction to Digital Design Laboratory       | Summer 2015        |

| Dept. of EECS, University of California, Irvine |                    |

• Teacher Assistant Irvine, California

Introduction to Digital Design Laboratory

Computer system and C programming

Irvine, California

Fall 2013, Summer 2014

Spring 2012/2015, Summer 2013

Computer Organization Winter 2012/2013/2014, Fall 2014/2015 Dept. of EECS, University of California, Irvine

• Peer Mentor Irvine, California

International Students of University of California, Irvine Fall 2011/2012/2013

#### SELECTED HONORS AND AWARDS:

| • Author of featured paper<br>IEEE Transaction on Computers (ToC)                                                                              | December 2015 |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| • Awarded NSF travel grant International Symposium on Computer Architecture (ISCA)                                                             | May 2015      |

| • DAC Young Student Support Program Award 52 <sup>nd</sup> Design Automation Conference (DAC), 2015                                            | May 2015      |

| • AGS Travel grant Award (UCI) To present my accepted paper in VTS 2015 33 <sup>th</sup> VLSI Test Symposium (VTS), 2015 IEEE                  | March 2015    |

| • Second place of IEEE Orange County and<br>Western Digital Student Design Contest<br>11 <sup>th</sup> International System-on-Chip Conference | Oct 2013      |

| • First place of IEEE Orange County and<br>Western Digital Student Design Contest<br>$10^{th}$ International System-on-Chip Conference         | Oct 2012      |

| • First place of IEEE Orange County and<br>Western Digital Student Design Contest<br>9 <sup>th</sup> International System-on-Chip Conference   | Nov 2011      |

| • Graduate Research Student Fellowship EECS Dept. of University of California Irvine                                                           | 2010-2011     |

#### PROFESSIONAL MEMBERSHIPS:

Institute of Electrical and Electronics Engineers (IEEE) Since 2013

#### PUBLICATIONS:

#### Journal papers:

- [J5] P.M. Yaghini, A.Eghbal, S.S.Yazdi, and N. Bagherzadeh, M.M. Green, "Capacitive and Inductive TSV-to-TSV Resilient Approaches for 3D ICs," IEEE Transactions on Computers, vol.65, no.3, pp.693-705, 2016.

- [J4] **A.Eghbal**, P.M. Yaghini, M. Khayambashi, and N. Bagherzadeh, "Analytical Fault Tolerance Assessment and Metrics for TSV-based 3D Network-on-Chip," IEEE Transactions on Computers, vol.64, no.12, pp.3591-3604, Dec 2015.

- [J3] P.M. Yaghini, A.Eghbal, M. Khayambashi, and N. Bagherzadeh, "Coupling Mitigation in 3D Multiple-Stacked Devices," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.23, no.12, pp.2931-2944, 2015.

- [J2] P.M. Yaghini, A.Eghbal, and N. Bagherzadeh, "On the Design of Hybrid Routing Mechanism for Mesh-based Network-on-Chip," Integration, the VLSI Journal Elsevier, Vol50, pp. 183-192, 2015.

- [J1] M. Khayambashi, P.M. Yaghini, A.Eghbal, and N. Bagherzadeh, "Analytical Reliability Analysis of 3D NoC Under TSV Failure," ACM Journal on Emerging Technologies in Computing Systems (JETC), vol. 11, no.4, pp. 43:1-43:16, 2015.

#### **Conferences:**

- [C5] F. Verbeek, P.M. Yaghini, A.Eghbal, N. Bagherzadeh, "Deadlock Verification of Cache Coherence Protocols and Communication Fabrics," accepted in DATE 2016.

- [C4] P.M. Yaghini, **A.Eghbal**, S.S.Yazdi, and N. Bagherzadeh, "Accurate System-level TSV-to-TSV Capacitive Coupling Fault Model for 3D-NoC," Proceedings of the 9th International Symposium on Networks-on-Chip, pp. 3:1–3:8, 2015.

- [C3] A.Eghbal, P.M. Yaghini, and N. Bagherzadeh, "Capacitive Coupling Mitigation for TSV-based 3D ICs, "The 33th International IEEE VLSI Test Symposium (VTS), pp.1-6, April 2015.

- [C2] A.Eghbal, P.M. Yaghini, S.S.Yazdi, and N. Bagherzadeh, "TSV-to-TSV Inductive Coupling-Aware Coding, "IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, pp. 92-97, 2014.

- [C1] P.M. Yaghini, A. Eghbal, and N. Bagherzadeh, "A GALS Router for Asynchronous Network-on-Chip," The 2nd ACM International Workshop on Manycore Embedded systems, pp. 52-56, 2014.

## ABSTRACT OF THE DISSERTATION

Three-Dimensional NoC Reliability Evaluation Automated Tool (TREAT)

By

#### Ashkan Eghbal

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2016

Professor Nader Bagherzadeh, Chair

Technology scaling and higher operational frequencies are no longer sustainable at the same pace as before. The processor industry is rapidly moving from a single core with high-frequency designs to many-core with lower frequency chips; Network-on-Chip (NoC) has been proposed as a scalable and efficient on-chip interconnection among cores. In addition, employing Three-Dimensional (3D) integration instead of Two-Dimensional (2D) integration is the other trend to keep the traditional expected performance improvements. The combination of 3D integration and NoC technologies provides a new horizon for on-chip interconnect design. In more detail, the reduction of the length and number of global interconnects; by applying Through-Silicon Via (TSV) is the major advantage of 3D NoCs.

However, shrinking transistor sizes, smaller interconnect features, and 3D packaging issues, lead to higher error rates and unexpected timing variations. Although many researches have focused on reliability issues for 3D NoC architectures, To develop a general technique to advance both the intuitive understanding and the quantitative measurement of how potential physical faults influence the behavior of 3D NoC is lacking. The goal of my dissertation is to develop a Three-Dimensional NoC Reliabil-

ity Evaluation Automated Tool (TREAT), for the first time, as an automated analysis tool to analyze effects of static and dynamic faults in 3D NoC architectures. It is capable of evaluating the vulnerability of different architectural components in the presence of faults by using the fault injection method. This approach allows injecting faults into the 3D NoC platform dynamically by monitoring the status of links and components to decide where and when inject faults accurately. TREAT provides the strength of different components in terms of reliability-based metrics such as Mean Time Between Failure (MTBF) and header/data/trailer flit failure rate for different level of granularity. The output reports of TREAT are critical in devising fault-tolerant techniques with low overhead cost. TREAT can be used at the early stage of the design process in order to prevent costly redesigns after assessing dependability for the target architecture.

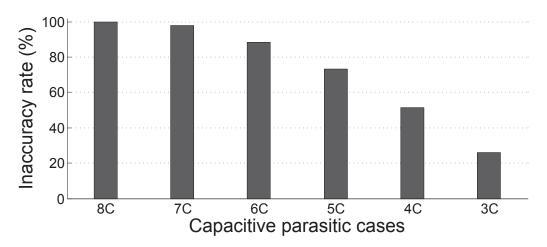

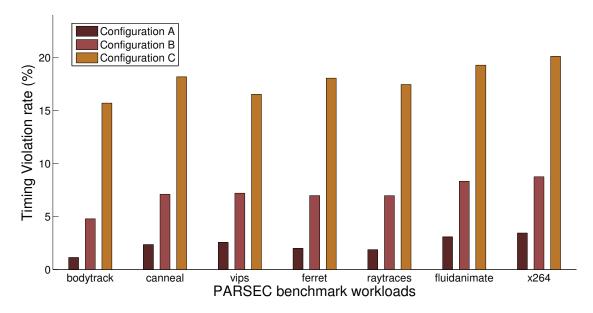

Comparing to existing fault injector tools, TREAT is specifically developed for 3D NoC platforms and it is not a general fault injector tool. Such a tool is needed since the characteristics and behavior of a 3D NoC component is different from other computational platforms; 3D NoCs are susceptible to different fault sources that are not fully addressed by existing tools. Furthermore, one of the most important advantages of TREAT is supporting dynamic fault injection by monitoring the status of the NoC platform. This is critical since based on the reported experiments in this dissertation, random TSV coupling fault injection may result in 26%-99% inaccuracy of reliability evaluation process. The fault injector interface is responsible for injecting fault accurately where and when they should in order to enhance the reliability evaluation. None of the existing tools offer these capabilities as a single package.

# Chapter 1

# Introduction

Since the technology scaling does not treat wire delay and gate delay equally, many-cores' interconnection design became challenging. Consequently, a novel communication method is required to take the benefits of many-core designs as they are highly demanded for both embedded systems and super-computers. Additionally, the reliability characteristic is of crucial importance in today's High Performance and Energy Efficient Computing (HPEEC) applications since the malfunctioning of a component results in lower performance and waste of energy, [112]. Therefore, similar to any new technology the reliability of the proposed communication methodologies is a crucial issue.

With this in mind, a reliability analysis tool is needed to uncover the sensitive components and to evaluate the efficiency of the proposed robust designs. Although many general analysis tools have been presented especially for investigating the reliability properties of the processors, these tools are not accurate enough to reveal fault tolerance characteristics of the next generation on-chip communication links.

The purpose for this research is to develop a specific reliability analysis tool, to

address the unexpected effects of physical faults in on-chip interconnections statically and dynamically. In the rest of this chapter, the necessity and the basic concepts of on-chip links with their reliability issues are briefly discussed. Additionally, the available reliability analysis tools are also introduced and compared with the one which is proposed in this dissertation. Then the contributions of this research are listed and discussed and finally, the outline of the dissertation is provided.

## 1.1 The Future Design Trends

The three well known factors in traditional high performance Processing Element (PE) designs are: Instruction Level Parallelism (ILP), gates per clock, and process technology. However, the first two factors have already reached their limits [40, 67]. The problem of process technology scaling is more related to wire issues and energy consumption concerns rather than the device design challenges. Applying higher frequencies results in more energy consumption, clocking synchronization concerns, and signal/power integrity issues. Moreover, the unexpected heat generation in PEs is already known as a major concern though they have never been super-fast yet. In addition, technology and supply voltage scaling slows down due to physical limitation in nano fabrication feature size. The leakage energy consumption, lithography complexity, and process variation issues are some critical examples of these physical constraints. On the other side, there are plentiful of computational applications in the market that demand more complex processing calculations such as smart phones, gaming consoles, or weather forecast applications. With these limitations there are significant concerns in moving forward to follow the *Moore's* law for next generation of IC designs. Therefore, different solutions have been suggested by researchers to exploit the technology capacity and keep the traditional performance improvements such as: proposing many-core designs, Three-Dimensional (3D) integration, and new generation of interconnections [67, 33, 89]. Each of these solutions is discussed separately in the following subsections.

## 1.1.1 Moving from Single Core to Many-core

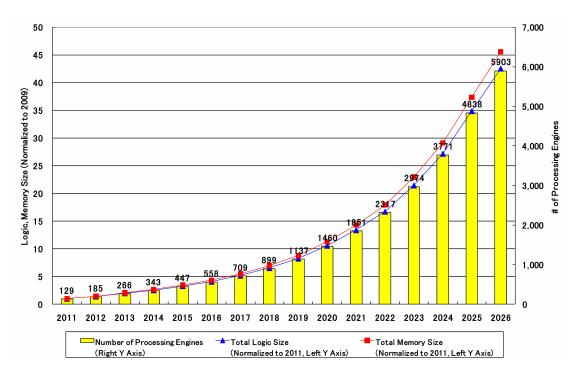

With each passing year, the number of problems where experiments are impossible, dangerous, or inordinately costly is growing. To provide vastly more accurate predictive models and the analysis of massive quantities of data are some examples of these problems [2]. In order to meet performance demands, parallel computing is ample motivation for proposing many-core architectures as predicted by ITS reports which is shown in Figure 1.1. Based on the represented trend in Figure 1.1 the number of cores will be increased by a factor of 10 by the next decade.

However, many-core popularity is not only limited to super-computer applications. Modern embedded systems also require massive processing power due to computationally intensive embedded applications, such as self-driving automobiles' control unit, real-time speech recognition, video conferencing, software-defined radio, and cryptography. With these considerations it is concluded that, many-core design is the only de facto solution for HPEEC applications [42], which has been already found its way into mass production. Two major benefits of replacing a high frequency single core chip by the many-core designs with a reasonable frequency are providing better level of resource sharing and occupying less Printed Circuit Board (PCB) space. The other advantage of many-core design is increasing the raw performance by enhancing the clock per instruction factor rather than frequency, which consequently results in slower growth in energy consumption. Therefore, many-core architecture manifests a good tradeoff between technology scaling and limited energy budget requirement.

Figure 1.1: SoC consumer portable design complexity trends [44]

#### 1.1.2 Moving from 2D to 3D Integration

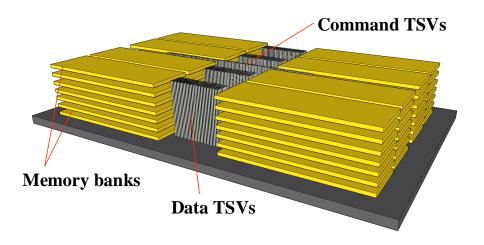

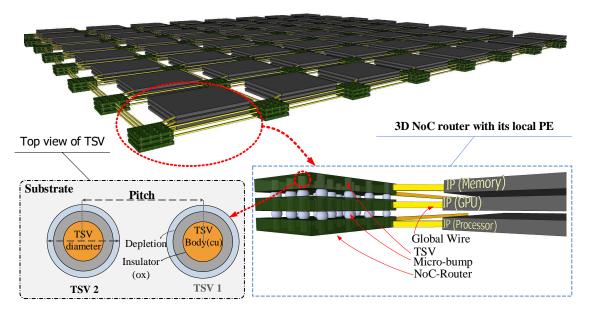

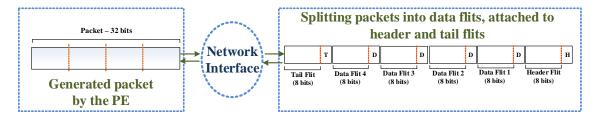

The other solution which has been recently become popular is to add one more dimension to the 2D state of the art architectures (resulting in 3D designs). This method provides numerous opportunities to connect PEs and memory cells on one package with larger bandwidth. The 3D memory, known as Hyper Memory Cube (HMC), is an industrial example of applying this technique [47, 105]. Figure 1.2 shows the graphical structure of 3D memory in which memory banks are stacked on top of each other and connected through vertical interconnection known as Through Silicon-Via (TSVs). One of the promises of HMC is that it eliminates the so-called "memory wall," the problem of the disparity between CPU clock speed/bandwidth and the memory systems [24]. The 32-layer V-NAND flash memory is the other example of this approach which has been started for mass production by Samsung Company. In addition to industrial examples, the 3D cache architecture has become a popular topic of study among researchers [128, 37, 124].

Figure 1.2: TSV-based 3D multiple-stacked memory

In general, 3D ICs are proposed as a viable solution for integrating more PEs on a chip, without the need for extra footprint area [126]. According to the characteristics of the 3D architectures, data transmission is done both horizontally and vertically at the same time. Moreover, 3D designs provide shorter interconnect links in which cores are usually located centimeters apart on a chip are now could be placed millimeters apart from each other vertically. Therefore, as 3D ICs compared to the 2D ones are expected to support higher performance, lower latency, smaller form factor, and less energy consumption.

# 1.1.3 Moving from Bus-based to Network-based Interconnects

The chip data transmission needs more attention as the complexity of systems increases, in a way that devising a new communication infrastructure is necessary. In other words, the traditional, bus-based core communication infrastructures, are considered as one of the performance bottleneck in many-core systems. The reason is that the wire delays have become more critical in smaller feature size, as technology

scaling results in larger capacitance for global wires. It has been reported that under 45nm technology size, Metal-1 and intermediate-level metal wires (local wires) are expected to have the same line-widths and thicknesses, demonstrating similar process variation effects. The effect of process variations on local metal layers are expected to have smaller effect on overall circuit delay because of their relatively shorter lengths as compared to global wires [125]. Therefore, global wires are not scalable in terms of delay, energy consumption, and bandwidth. In addition, global clocking is another challenge in traditional bus-based interconnections. The clock tree method has been suggested to resolve this issue, but it consumes large portion of energy and area budget. In addition, due to clock skew effect even larger portion of the total cycle time [67] is needed. It should be also added that a bus-based system has a limited capability of concurrent communication. The intrinsic resistance and capacitance of the bus also increase by connecting more number of cores. Moreover, buses broadcast the data to transfer them among the cores in which the entire bus wires should be switching from on to off state periodically; resulting in large waste of energy. Because of these important considerations, the Network-on-chip (NoC) architecture has been proposed as a practical alternative for the traditional system-on-chip (SoC) approach, supporting better modularity, scalability and higher bandwidth [29, 92, 67]. In fact, an NoC consists of multiple point-to-point data links interconnected by routers to implement the connectivity of on-chip Intellectual Properties (IPs).

#### 1.1.4 3D NoC

NoCs have become significant over the past 10 years in order to fully utilize the integration capacity with billion-transistor on a chip. However, because of the aforementioned benefits of 3D IC designs, as discussed in subsection 1.1.2, the 2D NoC designs must be expanded to support 3D schemes [89]. The combination of 3D inte-

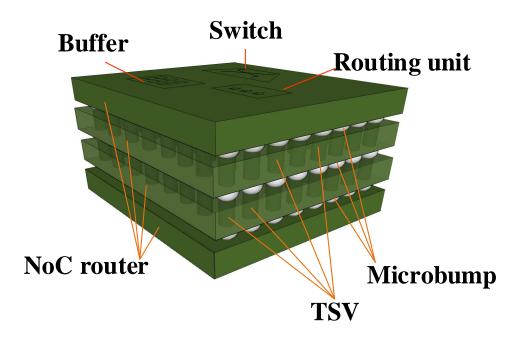

Figure 1.3: Side view of 3D NoC

gration and NoC technologies provides a new horizon for on-chip interconnects design, which combines the benefits of short vertical interconnects of 3D ICs and the scalability of NoCs. Compared with 2D NoCs, 3D NoCs greatly reduce the network diameter and overall communication distance; they improve communication performance and reduce energy consumption [89].

The TSV is currently the most popular technology to connect 2D NoC routers vertically. They are actually large vertical wires which are surrounded by an insulation and depletion layers. Additionally, TSVs are very short and fine-pitched links, which provide high-bandwidth communication channels. They are also highly compatible with the standard CMOS process which makes them capable of integrating into existing circuits without extra design cost.

In more details, 2D NoC routers are connected by TSVs (inter-die interconnects) through connectors with small diameters called Microbumps [19]. Microbumps are actually the metal connectors on both topside and backside of the chip which are

integrated into the copper filled TSV process for electrical connection between chips. Figure 1.3 shows 3D structure of stacked 2D NoC routers vertically connected by Microbumps and TSVs. The buffer, crossbar switch, and routing unit are the fundamental components of a 2D NoC router, which are individually explained in Section 3.2. In fact, TSVs implement a serial data transmission method in which each TSV is capable of single bit data transmission at a time, sequentially. This is why each NoC router is connected to several TSVs and Microbumps as shown in Figure 1.3. It should be noted that, due to large sizes of TSVs, all the routers cannot be connected to the routers of the other layers. Therefore, vertically partially connected 3D NoCs are more practical and have been the focus of majority of researchers instead of vertically fully connected 3D NoCs.

On the other side, 3D NoC architectures demand many trade-offs in order to meet some specific performance requirements, which results in various design issues. One of these major design concerns is the reliability of 3D NoC which is the goal of this research. The reliability issue in 3D NoC is briefly described in subsection 1.2 and further discussed in Chapter 4.

# 1.2 Reliability of 3D NoC

To design a robust computing circuit has been considered for many years ago. Recently it has received a great deal of attention as the CMOS technology approaches the nanoscale level. Shrinking transistor sizes, smaller interconnect features, 3D packaging issues, and higher frequencies of CMOS circuits lead to higher error rates and more thermal and timing violations [70]. Many approaches have been proposed to enhance the robustness of NoCs, mostly in the areas of routing algorithms [88, 82], communication infrastructure [12, 76, 77, 98], or micro-architecture designs [57, 74, 29].

Many fault-tolerant routing algorithms have been proposed for both 2D [23] and 3D NoC [79] designs. The idea of bypassing faulty data paths within failed routers has been suggested as a lightweight fault-tolerant method [58]. A fault-aware IP-core mapping to NoC routers is proposed in [69]. They address the problem of transient link failures by means of temporally and spatially redundant transmission of messages. A stochastic communication paradigm is proposed in [12] to provide a fault-tolerant communication. This approach is based on probabilistic broadcast where packets are forwarded randomly to the neighboring nodes. However, none of them protect faulty datapath inside routers. In [9], the authors deploy some error correcting schemes to achieve combined energy minimization and reliability optimization design goals. A fault-tolerant router architecture is proposed in [29] to guarantee the functionality of NoC in the presence of faults. They detect the most tenuous components of router against different sources of faults first and then tolerate them to save power and area overhead of employing fault-tolerant techniques. An adaptive fault-tolerant NoC router with the power consumption consideration is proposed in [74]. They improve error correction capability of their design based on the frequency of fault occurrence. A novel bidirectional fault-tolerant NoC architecture capable of mitigating both static and dynamic channel failures is also proposed [108].

However, in all of these approaches the dependability of NoC design is improved, regardless of imposing redundancies (hardware, information, and time) or based on reliability analysis reports with general tools. Also, there is no measurement capability to compare the effectiveness of the proposed reliable 3D NoC architectures. In fact, experimental and analytical techniques are two popular methods to explore the dependability of systems. Categorizing the effects of potential faults on the performance of a system is a necessity for both techniques. An analytical model for reliability evaluation of 2D NoC has been presented in [21], but it is not reusable for 3D die-stacking designs in which new sources of faults are presented.

Many major reliability issues are presented by the emergence of 3D structures such as thermal concerns and TSV issues as a result of 3D structures. The unwanted heat generation by PEs in 3D NoC should be removed effectively otherwise it may result in other problems. Three major effects of heat generation are increasing the device temperature, generating thermal stress, more thermomigration as a result of cooling down methods. In addition, TSVs may also cause unwanted noise sources as a result of inductive and capacitive coupling effects. These effects are different from the traditional crosstalk issues due to differences between the physical characteristics of TSVs and 2D wires. They are still active areas of research. Additionally, the generated noise signals by TSVs, may also have undesirable effect on the performance of 2D components such as transistors or 2D wires. A minimum distance between TSVs and these components is required to prevent undesirable effects of TSVs impacting the functionality of the 3D NoC architectures. Furthermore, there are still additional issues for developing 3D architecture EDA tools [14]. Accuracy of simulated environment is a concern for experimental methods in order to analyze dependability of a system. On the other hand, measurements are expensive and time consuming while time-to-market cycle is of great importance.

Consequently, developing general analytical techniques to advance both the intuitive understanding and the quantitative measurement of how potential physical faults influence the behavior of 3D NoC are still lacking although many researches have focused on reliability issues for 3D NoC architectures.

## 1.3 Contribution of this Thesis

The goal of this dissertation is to present an accurate reliability analysis tool for 3D NoC platform. The presented reliability analysis tool in this dissertation is called

Three-Dimensional NoC Reliability Evaluation Automated Tool (TREAT). TREAT is able to analyze effects of static and dynamic faults in 3D NoC architectures. This tool can be applied investigating the capability of proposed fault-tolerant 3D NoC approaches at the early stage of the design, which saves both time and cost of design. The major stages of my dissertation are:

- Discovering the source of physical faults in 3D NoC and categorizing them based on their possible effect on the functionality and performance of the 3D NoC. In more details, all possible potential sources of physical faults in 3D NoC environment have been studied. The impacts of all potential physical faults on 3D NoC components are also addressed to be used for reliability metrics in TREAT. All main components of a 3D NoC router architecture and sensitive entities with their possible responses to physical faults are categorized in this dissertation [26].

- Designing and developing an HDL environment of 3D NoC router as a platform of running the experiments, called Three-Dimensional HDL Emulator NoC (THENoC). As a side project an optimized on-chip routing algorithm is also proposed which takes advantages of both source routing and distributed routing algorithms for 2D NoC and scalable to 3D NoC designs. This method eliminates the heavy routing process of intermediate routers for each packet from source toward its destination by imposing a light overhead independent from the network size [119].

- Modeling the logic-level of all possible physical faults in 3D NoC router and defining the property of injected faults dynamically by profiling the status of different components. These logic-level faults are modeled and applied as fault libraries in TREAT. By comparing the value of selected signals and their assertion time in 3D NoC components after running both faulty and faultless experiments the vulnerability of each component is reported. The effect of psychical fault models which are discussed in Chapter 4 are used as evaluation metrics in TREAT.

• Automating the fault injection and reliability evaluation processes and verifying its functionality with THENoC. It is capable of implementing static fault injection based on the provided information by the user or to accomplish dynamic fault injection process based on the analyzed feedback from the simulator. For static fault injection process this experiment is repeated as many times as the user defines for various fault activation time and periods, while a single experiment is needed for dynamic fault modelings.

## 1.4 Similar Tools

Fault injection is one of the popular method of reliability analysis which is addressed in Chapter 2. The impacts of faults have been evaluated by several research groups for various design objectives. Different methods are proposed with the goal of fault injection based on the analysis such as software fault injection, simulation fault injection and physical level fault injection.

Physical-based fault injection involves augmenting the system under analysis with specially designed test hardware to allow for the injection of faults into the system and examine their effects. Although the experimental process in this method is fast, but the experimental set up is time consuming. In addition, this method needs the actual hardware in order to run the fault injection process, resulting in a costly method. Software-based fault injection includes the modification of the running software on the system under analysis in order to modify the system state according to the programmers modeling view of the system. This is popular for cases that have communicative or cooperative functions so that there is enough interaction to make fault injection useful. Comparing to physical-based fault models they do not need the actual model of the system, but they have some limitation in terms of fault injection coverage and

observability. Finally, simulation-based fault injection method requires an accurate model of the system under analysis. The accuracy of the model and simulation time, are major concerns for these approaches, but they have full control of fault injection and fault modeling. This approach is not expensive either, since it does not need the actual hardware of the design. Because TREAT is a simulation-based fault injector tool, various simulation-based fault injector tools are introduced to show they are not appropriate for 3D NoC reliability analysis objective.

- MEFISTO-C: is a VHDL-based fault injection tool developed at Chalmers University of Technology, Sweden that conducts fault injection experiments using VHDL simulation models. The tool is an improved version of the MEFISTO which was developed jointly by LAAS-CNRS and Chalmers. Also a similar tool called MEFISTO-L has been developed at LAAS-CNRS. MEFISTO-C uses the vantage optimum VHDL simulator and injects faults via simulator commands in variables and signals defined in the VHDL model. It offers the user a variety of predefined fault models as well as other features to set-up and automatically conducts fault injection campaigns on a network of UNIX workstations. This tool generates modified components descriptions called mutants. The mutants generation is based on a static information and the model has to be recompiled for each experiment [34].

- VHDL-based Evaluation of Reliability by Injection Faults Efficiently (VERIFY): is developed at University of Erlangen-Nurnberg, Germany. VERIFY uses an extension of VHDL for describing faults correlated to a component, enabling hardware manufacturers, which provide the design libraries, to express their knowledge of the fault behavior of their components. Multi-threaded fault injection which utilizes checkpoints and comparison with a golden run is used for faster simulation of faulty runs. The proposed extension to the VHDL language requires modification of the VHDL language itself. VERIFY uses an integrated fault model, the

dependability evaluation is very close to that of the actual hardware [101].

- HEARTLESS: is a hierarchical register-transfer-level fault-simulator for permanent and transient faults that was developed, by CE Group-BTU Cottbus in Germany, to simulate the fault behavior of complex sequential designs such as processor cores. Furthermore, it serves for the validation of online test units of embedded processors. It can support permanent stuck-at faults, transient bit flip and delay faults. HEARTLESS was developed in ANSI C++. The whole design or parts (macros) can be selected for fault simulation based on fault list generation. Fault list is reduced according to special rules derived from logic level structures and signal traces. HEARTLESS can be enhanced by utilizing macros described in a C-function [93].

- GSTF: is another VHDL-based fault injection tool developed by Fault Tolerance Systems Group at the Polytechnic University of Valencia, Spain. This tool is presented as an automatic and modeling dependent fault injection tool for use on an IBM-PC or compatible system to inject faults into VHDL models (at gate, register and chip level). The tool has been incorporated into a commercial VHDL simulator (V-System by Model Technology) and can implement the main injection techniques: Simulator commands, saboteurs and mutants. Both transient and permanent faults, of a wide range of types, can be injected into medium-complexity models. The tool can inject a wide range of fault models, surpassing the classical models of stuck-at and bit-flip and it is able to analyze the results obtained from the injection campaigns, in order to study the error syndrome of the system model and/or validate its fault-tolerance mechanisms [6].

- Fault Tolerance Injection (FTI): is developed at Universidad Carlos III de Madrid in Spain, for fault-tolerant digital ICs in the RT abstraction level. The main objective of FTI is to generate a fault-tolerant VHDL design description. Designer provides an original VHDL description and some guidelines about the type

of fault-tolerant techniques to be used and their location in the design. FTI tool processes original VHDL descriptions by automatic insertion of hardware and information redundancy. Therefore, a unified format to deal with descriptions is needed. There are several intermediate formats that represent, by means of a database, the VHDL description in a formal way that could be accessed and processed with some procedural interface. Fault-tolerant components to be included into VHDL original descriptions have already been described and stored in a special library called FT library. These components come from previous researches about FT and designer just use them. FTI use an intermediate format for VHDL descriptions (FTL/TAURI) and it will work only with synthesizable descriptions IEEE 1076 [32].

Many other fault injector tools have been presented for various design objectives by research groups in addition to the famous ones which are listed in this section. However, none of the existing tools are efficiently reusable for 3D NoC platforms, since 3D NoCs are susceptible to different fault sources that are not fully addressed by existing tools like 3D design issues. Furthermore, components and behavior of a 3D NoC is different from other computational platforms as discussed in [26]. ARROW [11] is the only fault injector tool for NoC platform, which only supports 2D NoC design and it does not provide any reliability analysis. TREAT is specifically developed for 3D NoC platforms and it is not a general fault injector tool. Additionally, one of the most advantages of TREAT is its capability of intelligent fault injection by monitoring the status of the NoC platform (dynamic faults), while most of existing fault injector tools inject faults randomly. This is critical since based on our experiments; random fault injection may result in 26%-99% inaccuracy of reliability evaluation process. The presented tool is capable of evaluating the Verilog model of 3D NoC architecture or fault-tolerant techniques. TREAT includes the following features which none of the mentioned tools offer them all in one package:

- Automatic fault-injection

- Rich set of fault models

- Designed specifically for NoC

- Single and multi-bit fault activation

- Dynamic and static fault models

- 3D IC-specific fault models

- NoC specific reliability analysis and reporting

#### 1.5 Dissertation Outline

The rest of the thesis is organized as follows: Chapter 2 discovers the basic terminologies in fault-tolerant and fault evaluation communities which are used in other chapters. The basic components for a general fault injector tool are also discussed in this chapter. The 3D NoC architecture is explained in detail in Chapter 3, which is needed to recognize the major causes of fault occurrence and their effects on a 3D NoC design. The presented 3D NoC architecture in Chapter 3 is also applied in this dissertation to as a platform to run the experiments. The reliability challenges in 3D NoC interconnection are uncovered in Chapter 4, with their logic-level fault models. The effects of each of presented physical fault on the functionality of 3D NoC design are also discussed in this chapter. The framework of TREAT is introduced in Chapter 5. The experimental results of both static and dynamic fault injection processes are also presented in Chapter 6 to verify the capability of TREAT. Finally, Chapter 8 concludes the dissertation and discusses the potential directions for future work of this research.

# Chapter 2

# Dependability Threats and Means

To guarantee the correctness of computing and communication services of many-core systems, has always been a major challenge for both designers and end users. Designers need to develop more complex architectures which are capable of providing the expected services even in a faulty environment with limited energy consumption and area overhead. On the user's side, adding the dependability and fault tolerance features to electronic devices convey higher market prices. As an example, the price of the DDR memory slots with ECC (Error Correction Code) functionality is almost double the price of elemental components. In general, dependability is defined as the ability to deliver service that can justifiably be trusted.

A systematic exposition of the concepts of dependability consists of three parts: the threats to, the attributes of, and the means by which dependability is attained. There are many well-known attributes for dependability such as: reliability, availability, safety, security, survivability, maintainability, and other well known attributes. As discussed in Chapter 1, the goal of this dissertation is to provide a reliability analysis tool for 3D NoC environments which is considered one of the major attributes of the

system dependability. The dependability threats and means terminologies in addition to the concept of fault injection which are all needed for discussions of the following chapters are addressed in this chapter.

# 2.1 Dependability Threats

A system may not always perform as it is expected to, because of environmental conditions or internal faults. Higher temperature or voltage, neutrons and alpha particles, interconnect noises, electromagnetic interferences, and electrostatic discharge are some examples of undesirable environmental conditions for on-chip circuits. Each of these environmental conditions may result in an internal fault and consequently causes other unexpected behavior in the system. In general, causes and consequences of deviations from the promised functionality of a system are known as dependability threats including: fault, error, and failure. Each of these terminologies is individually discussed in the following subsections [8, 3]:

#### 2.1.1 Fault

Fault is a physical defect, imperfection, or flaw that occurs within some hardware or software component. A delay in an electronic circuit or missing the priority of operators in a math equation in a software program are some examples of faults.

A fault is classified into two major categories which are called active and dormant ones. A fault is active when it ends in an error, otherwise it is dormant. An active fault is either an internal or external fault. An internal fault was actually a dormant fault which has been triggered by the computation process or environmental conditions. An active fault may again become dormant, awaiting a new trigger. Most of internal faults switch repeatedly between their dormant and active states. As an example assume there is a memory cell with a predefined operational temperature. If the environmental temperature has changed for an unexpected reason the memory cell will be infected by the thermal fault. This is an example of external fault in which a dormant fault is converted to an active one. Also as an example of internal fault assume a single bit is infected by a fault before it is accessed. In this case the infected single data bit represents as a dormant fault until it is approached. Once this data bit is read, it becomes an active fault [38]. In case of write access, the infected fault bit is called to be overwritten before causing an error.

In other words, faults can also be categorized based on their temporal persistence known as: transient, permanent, or intermittent. A transient fault has an active status for a limited time and never gets activated again till the end of system's simulation. However, a permanent fault exists in the system till the end of system's life time. In addition, many of the faults switch between their dormant and active states which are called intermittent faults. But their activation time and intervals' length are not necessarily the same.

#### 2.1.2 Error

An error is defined as a deviation from accuracy or correctness which is the manifestation of a fault. To miss capturing the serial data bits by a memory cell because of delay fault or to generate an unexpected value as a result of missing the priority of operators are both error examples.

Similar to faults, an error can be categorized into two types which are: detected or latent errors. With applying error detection techniques; an error is called a latent

one, as long as it has not been recognized, otherwise it remains as latent error in the system [86]. As an example an error in a single memory bit of the cache entry caused by positive charge and kinetic energy of alpha particles, known as Single Event Upset (SEU) fault, can be either latent or detected. If the ECC decoder unit of the cache entry has recognized the result of SEU fault, it is detected; otherwise it keeps its latent status. In addition, a latent error may disappear or be overwritten before it is detected. But, most often many of the errors are propagated and consequently generate more errors or pass through the system which result in single or more failures.

#### 2.1.3 Failure

A failure is the non-performance of some action that is due or expected. Such as packet loss in data transmission because of missing correct data capturing or missing a software event as a result of regenerating unexpected values are examples of failures. A component failure causes a fault for the system which it belongs to or the other components which are interacting with.

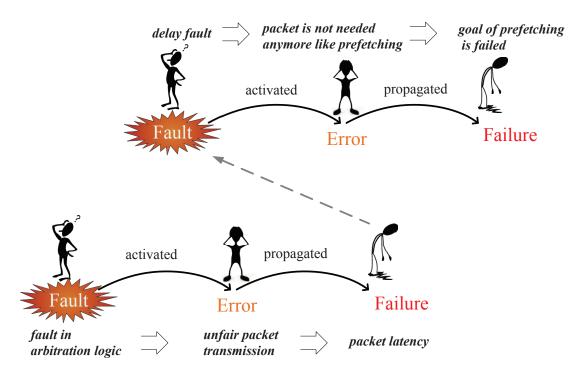

Figure 2.1 summarizes the relation between faults, errors, and failures. This figure also includes an example for each transition from a component's fault to failure which results in another component's fault and consequently a system failure. To illustrate this example assume there is a many-core system in which instructions are supposed to be prefetched from the memory, while the memory and cores are connected to each other through a network. If a fault in arbitration component of routing unit is activated; it will generate an unfair packet transmission through the system which consequently results in a packet latency failure. In a normal condition the maximum delay for each packet including instructions is predictable if the arbitration component works correctly, otherwise the packet will be captured with an unknown latency.

Figure 2.1: Fault, error, and failure

This failure can be considered as a kind of delay latency in the receiver side which is supposed to perform the prefetching operation. The activation of the delay fault results in an error in which the packet is not needed anymore. This error results in a system failure in the prefetching process. This example is a typical case especially in modern GPUs that are composed of many-core and memory units in which the prefetching technique has been proposed in order to increase the performance.

In addition to dependability threats, the means of dependability are also discussed in the next subsection to classify the types of methods discussed with the goal of resolving the unexpected behavior of faulty electronic circuits.

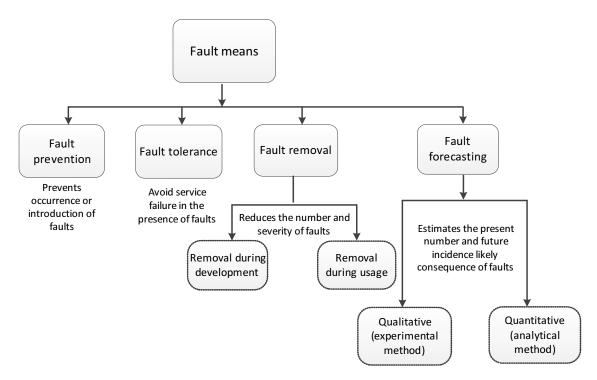

Figure 2.2: Fault means

# 2.2 Dependability Means

Dependability means can be grouped into four major classes to attain the expected level of dependability attributes. These categories are: fault prevention, fault tolerance, fault removal, and fault forecasting. Figure 2.2 summarizes these approaches which are discussed individually in the following subsections; through they are not independent from each other.

### 2.2.1 Fault Prevention

It includes all the methods which prevent the occurrence or introduction of faults. In more details, any hardware (such as hardware shielding and radiation hardening) or software activities (such as information hiding and modularized programming) at design time with the goal of protecting the system from different sorts of fault occurrence is known as fault prevention. However, if the applied method is not resilient enough to prevent the fault occurrence, they cannot resolve the issue.

#### 2.2.2 Fault Tolerance

These methods are proposed to protect the system in the presence of active faults to deliver its correct service. In higher level of abstraction fault-tolerant approaches intend to remove the errors from the system (known as error processing techniques) or to prevent the transition of dormant faults to be active ones (by applying fault handling methods). These two methods are discussed separately in the following paragraphs:

### **Error Processing**

The error processing technique can be implemented by either of applying error recovery or error compensation approaches. For the error recovery approach, the erroneous state is replaced by an error-free state, while for the error compensation technique the integrated redundancies guarantee the delivery of error-free service. The error detection method is a critical step in error recovery approaches, for recognizing the erroneous state, resulting in the notion of self-checking component. The error recovery process is implemented in two different formats which are: backward recovery or forward recovery. For the backward recovery there is a transition from the current state to the state prior to error occurrence. As expected this method cannot resolve the permanent faults. On the other hand, for the forward recovery there is a transition from the current erroneous state to a new state from which the system can operate correctly.

In error compensation approach, the self-checking component is still needed. In this

method the execution of non-failed component is delivered to present the correct service, if the error is detected by the self-checking component. In more details, when error compensation is performed in a system, composed of self-checking components partitioned into classes executing the same tasks, there is simple switching within a class from a failed component to non-failed one. Additionally, error recovery approach imposes larger time overhead but less hardware or information redundancy as compared to the error compensation method.

### Fault Handling

Fault handling is the other well-known technique proposed for a fault-tolerant design by preventing the located faults to be activated again. Fault handling is accomplished in four stages:

- [C1] to locate and recognize the cause(s) of errors.

- [C2] to prevent faults to be activated again which can be done by isolating the faulty identified components from the system.

- [C3] to reconfigurable the system if it is not able to deliver the system without the faulty isolated component.

- [C4] to reinitialize the system by checking and updating the new configuration of the system.

To select either of error processing and fault handling techniques and their implementation depends on the system requirement, overhead budget, and underlying fault assumption. It is critical that the fault-tolerant mechanisms are resilient enough against the faults that can affect them [86, 3]. Additionally, for any given fault-tolerant method, the fault hypothesis and the fault coverage are two major properties which should be considered by the designer. The fault hypothesis represents the types of faults which the proposed technique should tolerate and the fault coverage shows the

probability that the fault hypothesis is respected when a fault actually occurs in the system.

### 2.2.3 Fault Removal

This method can be applied both during the development phase or operational system's lifetime. During the development phase fault removal is done in three stages including: verification, diagnosis, and correction. In the verification stage it is checked to investigate if the system fulfills the given properties, which are described as verification conditions. If it does not, the other two steps follow: diagnosing the fault(s) that prevented the verification conditions, and then performing the required alteration. An important aspect of this technique during development stage is the verification of fault tolerance mechanisms. Verifying the capability of the proposed fault-tolerant methods is critical. Fault removal during the operational phase of a system's life is either corrective or preventive maintenance. The corrective methods remove the reported faults ended in error(s), while protective approaches recognize and remove faults before they cause an error [3].

## 2.2.4 Fault Forecasting

Fault forecasting is a method to evaluate the system behavior against the fault occurrence or activation. It can be accomplished in two different techniques: quantitative (formal) evaluation and qualitative (experimental) one. For quantitative method, the whole system is modeled by probabilistic equations. In this approach the malfunctioning probability of the modeled components are reported as measures of dependability. This method is fast but complex especially as the size of system grows, but the system is simulated and its behavior is evaluated in the presence of faults by running

large number of experiments. This method is not as fast as formal methods, but it has more controllability over more parts of the system. Fault injection technique is a typical example of this method. Fault injection can also take place in the verification stage of the fault removal method.

All of the four dependability means are somehow related to each other and in some cases they have some overlaps. However, a typical question is that which of them guarantees to deliver a dependable system. In most cases, the expected dependability is not achieved by using any of them, separately. Different fault-tolerant techniques have been introduced by researchers, but it would be more cost effective to employ them if the resiliency of the target device against different sources of fault is available. This knowledge can be achieved by applying fault forecasting methods in order to address the vulnerable components of the system. With this strategy the expected dependability is met while redundancies cost is kept low. In practice, fault removal and fault forecasting methods are followed by each other. In other words, after rejecting a system by the fault forecasting, several fault removal tests are applied. These new tests provide actions that can help the designer to improve the system. This loop is repeated until reaching the desirable design. The main goal of this dissertation is to present a fault forecasting technique for 3D NoC environment. To reach this goal fault injection technique is used which is briefly in the following Section.

# 2.3 Fault Injection

Fault injection is a process in which responses of the system are analyzed to verify the behavior of the designed system in the presence of predefined faults. This is a popular approach in reliability evaluation of computing and communication systems such as processors, micro-controllers, and interconnections [31, 27, 116]. In this method faults

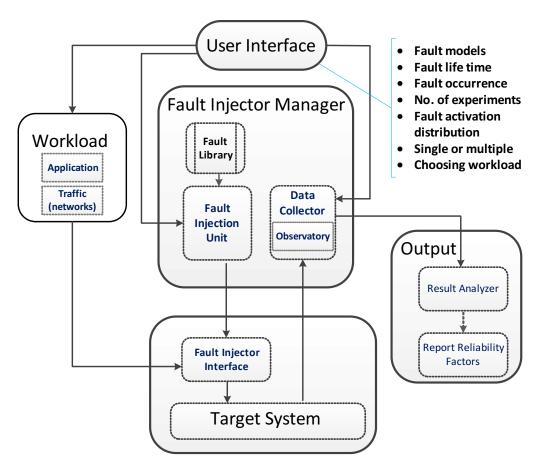

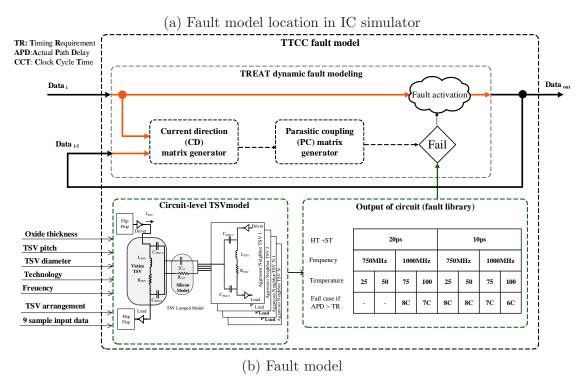

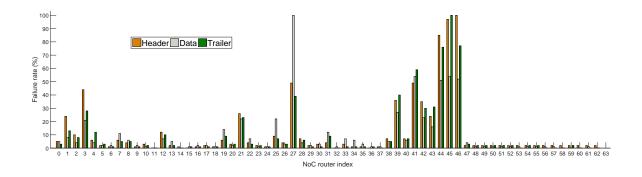

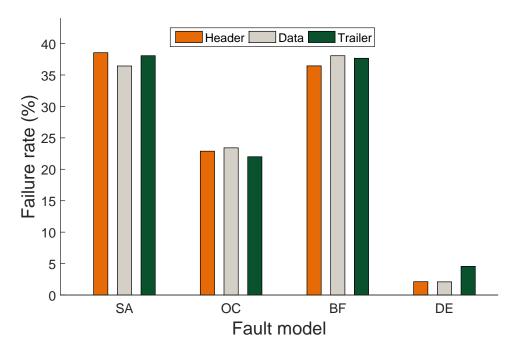

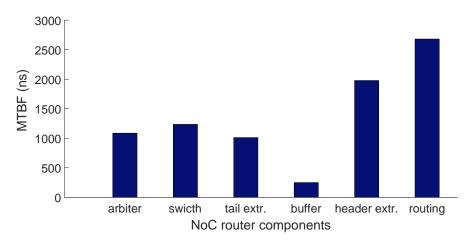

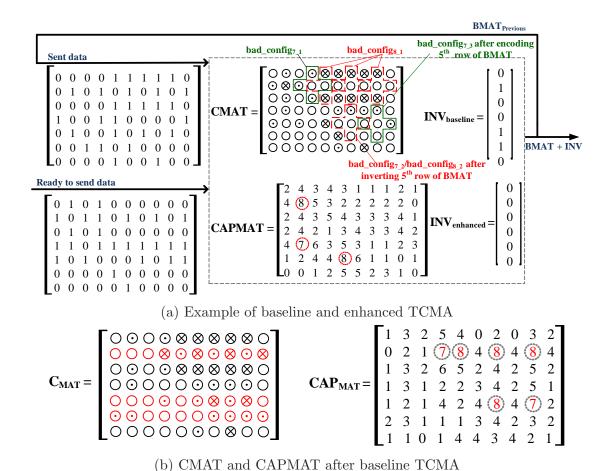

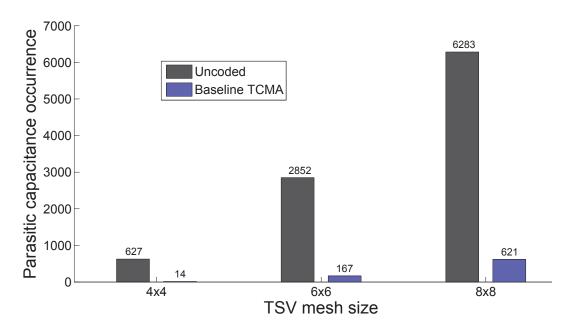

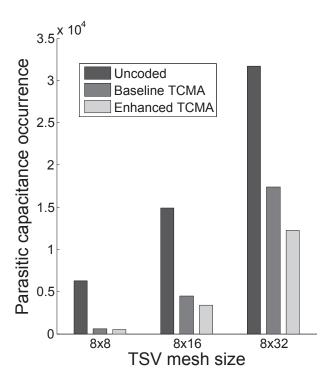

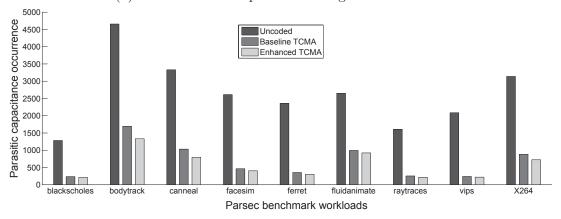

Figure 2.3: A typical fault injector components