# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Floorplan Representation, Global Placement, and Routability Analysis for VLSI Layout Design Automation

**Permalink** https://escholarship.org/uc/item/0gd0z8d0

Author Kang, Ilgweon

Publication Date 2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Floorplan Representation, Global Placement, and Routability Analysis for VLSI Layout Design Automation

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Ilgweon Kang

Committee in charge:

Professor Chung-Kuan Cheng, Chair Professor Ronald Graham Professor Andrew B. Kahng Professor Farinaz Koushanfar Professor Bill Lin

2018

Copyright Ilgweon Kang, 2018 All rights reserved. The dissertation of Ilgweon Kang is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2018

# DEDICATION

I dedicate this thesis to my family. Without their support this thesis would not have been finished.

# TABLE OF CONTENTS

| Signature Page  | e                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dedication      | iv                                                                                                                                                                                                                                                                                                                                                          |  |

| Table of Conte  | ents                                                                                                                                                                                                                                                                                                                                                        |  |

| List of Figures | s viii                                                                                                                                                                                                                                                                                                                                                      |  |

| List of Tables  | xii                                                                                                                                                                                                                                                                                                                                                         |  |

| Acknowledgm     | ents                                                                                                                                                                                                                                                                                                                                                        |  |

| Vita            | xv                                                                                                                                                                                                                                                                                                                                                          |  |

| Abstract of the | Dissertation                                                                                                                                                                                                                                                                                                                                                |  |

| Chapter 1       | Introduction       1         1.1       Researches on Physical Layout       3         1.1.1       Back-Board Ordering       4         1.1.2       Two-Dimensional Physical Layout Design       4         1.1.2       Two-Dimensional Physical Layout Design       4                                                                                          |  |

|                 | 1.1.3Multi-Dimensional Physical Layout Design: 3-D, Potentially 4-D and Beyond71.1.4Benchmarks71.2New Opportunities On Physical Design91.2.1Physical Design and ITRS10                                                                                                                                                                                      |  |

|                 | 1.2.2         New Techniques         11           1.2.3         New Markets for IC Design         12                                                                                                                                                                                                                                                        |  |

|                 | 1.3 Conclusion                                                                                                                                                                                                                                                                                                                                              |  |

|                 | 1.4 Acknowledgments                                                                                                                                                                                                                                                                                                                                         |  |

| Chapter 2       | 3-D Floorplan Representations by Using Corner Links and Partial<br>Order152.1 Introduction162.2 Floorplan Overview202.2.1 Basis of Floorplanning202.2.2 Classification of Floorplanning212.2.3 Fundamental Floorplan Representations232.2.4 Mosaic Floorplan252.3 New 3-D Floorplan Representations: Corner Link and Partial<br>Order292.3.1 Corner Links29 |  |

|                 | 2.3.2 Partial Order                                                                                                                                                                                                                                                                                                                                         |  |

|           | 2.4  | 3-D Floorplan Representation Properties                                                                                     | 37 |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------|----|

|           | 2.7  | 2.4.1 Corner Links and Partial Order Representations                                                                        | 38 |

|           |      | 2.4.2 Corner Links and Four Trees Representation                                                                            | 42 |

|           |      | 1                                                                                                                           |    |

|           |      | 2.4.3 Partial Order Representation to Valid Floorplan                                                                       | 43 |

|           |      | 2.4.4 Partial Order Representation to Blocks' Absolute Co-                                                                  | 10 |

|           | 2.5  | ordinates                                                                                                                   | 46 |

|           | 2.5  | 3-D Floorplan Representation Algorithms                                                                                     | 48 |

|           |      | 2.5.1 Corner Links to Partial Order Representation                                                                          | 48 |

|           |      | 2.5.2 Partial Order to Absolute Coordinate Representation .                                                                 | 49 |

|           | 2.6  | Conclusion                                                                                                                  | 51 |

|           | 2.7  | Acknowledgments                                                                                                             | 52 |

| Chapter 3 | Adva | ncing Solution Quality and Routability Validation in Global                                                                 |    |

| <b>I</b>  |      | ment                                                                                                                        | 53 |

|           | 3.1  | Introduction                                                                                                                | 54 |

|           |      | 3.1.1 Density function and density penalty factor                                                                           | 55 |

|           |      | 3.1.2 Routability-driven placement                                                                                          | 55 |

|           | 3.2  | Placement Overview                                                                                                          | 58 |

|           | 3.3  | Constraint-Oriented Local-Density Function                                                                                  | 58 |

|           | 5.5  | 3.3.1 Necessity of Local Density Function                                                                                   | 58 |

|           |      | 3.3.2 Constraint-Oriented Local-Density Penalty for Each                                                                    | 50 |

|           |      | $Bin b_i \dots \dots$ | 59 |

|           |      | 3.3.3 Local-Density Cost Coefficient $\Delta_i$ per Each Cell $i$                                                           | 61 |

|           |      | 3.3.4 Formulation: Local Density Function and Gradient                                                                      | 62 |

|           |      | 3.3.5 Additional Details and Illustration                                                                                   | 65 |

|           | 3.4  | Improved Dynamic Step Size Adaptation                                                                                       | 68 |

|           |      | 3.4.1 Improved Dynamic Step Size Adaptation                                                                                 | 69 |

|           |      | 3.4.2 Trial Global Placement                                                                                                | 73 |

|           | 3.5  | Routability-Driven Placement                                                                                                | 75 |

|           |      | 3.5.1 Capacity and Blockage Calculation                                                                                     | 75 |

|           |      | 3.5.2 Demand Calculation                                                                                                    | 76 |

|           |      | 3.5.3 Cell Inflation                                                                                                        | 77 |

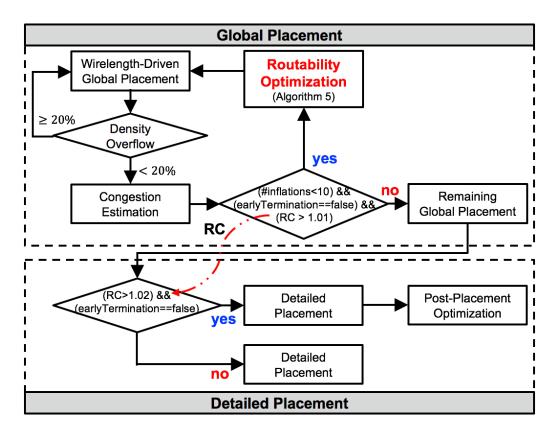

|           |      | 3.5.4 Overall Flow                                                                                                          | 78 |

|           | 3.6  | Experiments                                                                                                                 | 82 |

|           |      | 3.6.1 Standard Cell Placement                                                                                               | 82 |

|           |      | 3.6.2 Mixed-Size Placement                                                                                                  | 85 |

|           |      | 3.6.3 Routability-Driven Placement                                                                                          | 86 |

|           |      | 3.6.4 State of Academic vs. Industry Placement                                                                              | 92 |

|           | 3.7  | Conclusion                                                                                                                  | 92 |

|           | 3.8  | Acknowledgments                                                                                                             | 93 |

| Chapter 4    | Fast and Precise Routability Analysis with Conditional Design Rules 94 |

|--------------|------------------------------------------------------------------------|

|              | 4.1 Introduction                                                       |

|              | 4.2 Related Works and Our Approach                                     |

|              | 4.3 SAT-Friendly ILP Formulation                                       |

|              | 4.3.1 ILP-Based Detailed Routing Optimization 99                       |

|              | 4.3.2 ILP-Based Design Rule Formulation 104                            |

|              | 4.4 ILP-to-SAT Conversion                                              |

|              | 4.4.1 Advantage of Our SAT-Friendly ILP 107                            |

|              | 4.4.2 Logic Simplification                                             |

|              | 4.4.3 Reduced SAT Formulation                                          |

|              | 4.5 Experiments                                                        |

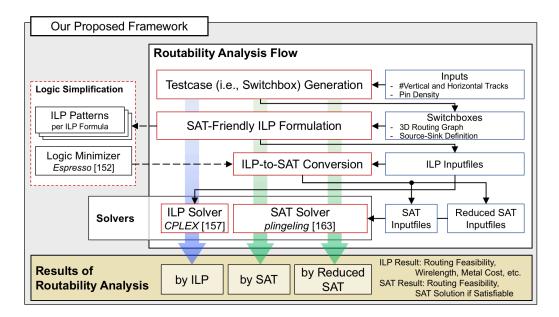

|              | 4.5.1 Overall Flow of the Proposed Framework 111                       |

|              | 4.5.2 Experimental Results                                             |

|              | 4.6 Conclusion                                                         |

|              | 4.7 Acknowledgements                                                   |

| Character 5  |                                                                        |

| Chapter 5    | Conclusion                                                             |

| Bibliography |                                                                        |

### LIST OF FIGURES

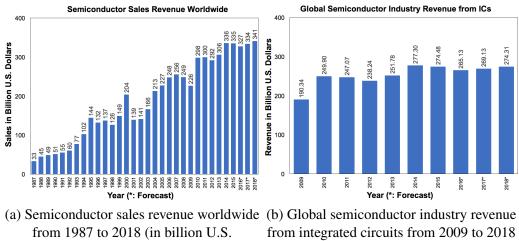

| Figure 1.1:                | Illustrations of semiconductor industry market size for the past decades.<br>The asterisk marks at year indices indicate the value by forecasting.                                                                                                                               | 2       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

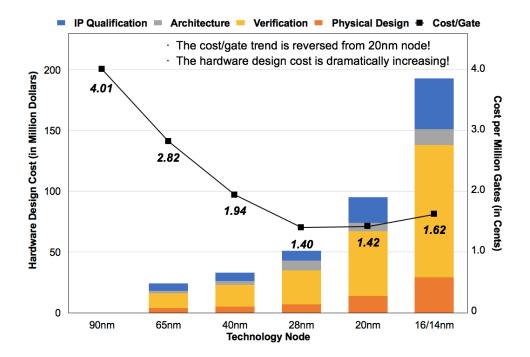

| Figure 1.2:                | Distribution of hardware design cost per technology node (bar chart) and the cost per gate trend (line) [155]. Hardware design cost at 90nm                                                                                                                                      |         |

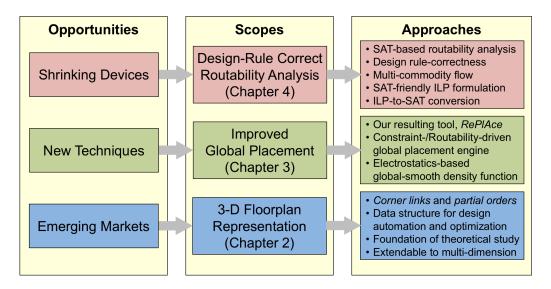

| Figure 1.3:                | technology node is not available from the reference [155] The organization of this dissertation. New 3-D floorplan representa-<br>tions, improved global placement engine, and SAT-based design-rule<br>correct routability analysis                                             | 2       |

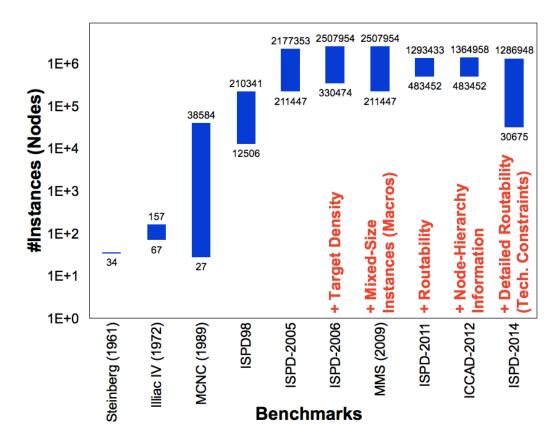

| Figure 1.4:                | The benchmarks plotted with ranges of instances (displayed in log scale). Benchmarks are selectively chosen from Table 1.1. The minimum and maximum instances are displayed at the bottom and the top                                                                            |         |

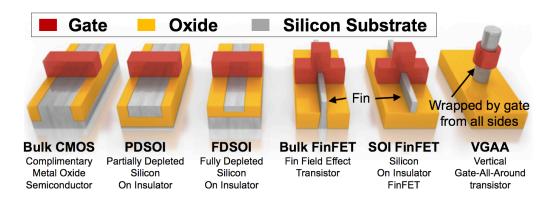

| Figure 1.5:                | of each bar, respectively                                                                                                                                                                                                                                                        | 9<br>10 |

| Figure 1.6:<br>Figure 1.7: | Transistor structure roadmap [159]                                                                                                                                                                                                                                               | 11      |

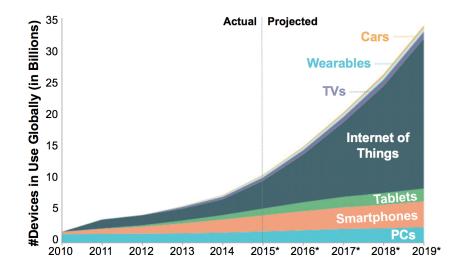

| 8                          | market [119]                                                                                                                                                                                                                                                                     | 13      |

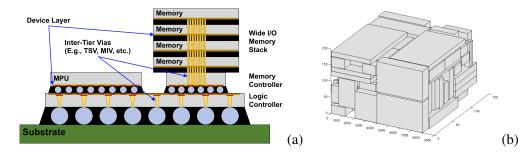

| Figure 2.1:                | An example of 3-D IC. (a) A 3-D IC package, re-illustrated based on the original figure in [165]. (b) A general 3-D floorplan to map a design into physical space of hardware [129]                                                                                              | 17      |

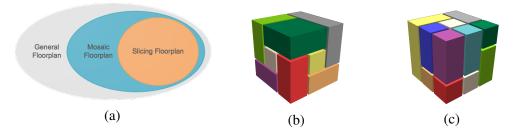

| Figure 2.2:                | Classification of floorplans. (a) Set relation chart of floorplan classi-<br>fications. (b) An example of the mosaic floorplan. (c) An example of<br>the slicing floorplan where we can partition the floorplan into single                                                      | 22      |

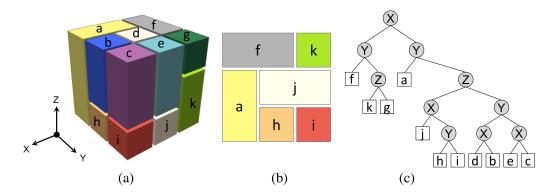

| Figure 2.3:                | An example of 3-D slicing floorplan with 11 blocks, i.e., blocks <i>a-k</i> . (a) The 3-D slicing floorplan from Figure 2.2(c) and its coordinate system. (b) The bottom layer layout of the 3-D slicing floorplan. (c)                                                          |         |

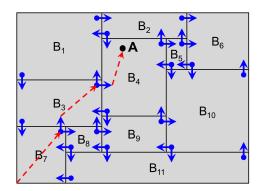

| Figure 2.4:                | The slicing tree representation of the 3-D slicing floorplan An example of corner-stitching-based 2-D floorplan representation. Each blue arrow depicts stitch, which is pointer. Red dotted arrows show the searching path for the block containing point <i>A</i> by following | 23      |

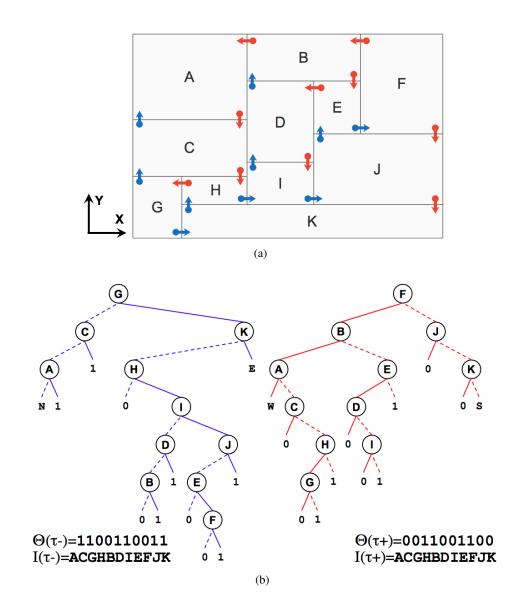

| Figure 2.5:                | the pre-defined pointers                                                                                                                                                                                                                                                         | 24      |

| Eiguro 2.6.                | twin binary trees for the floorplan of Figure 2.5(a). The pair of trees represents the up-right and down-left corner relations.                                                                                                                                                  | 26      |

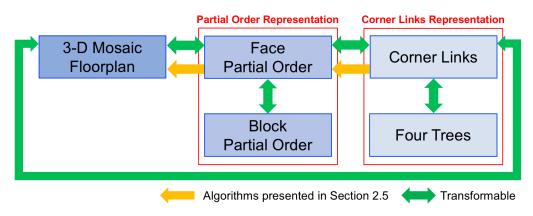

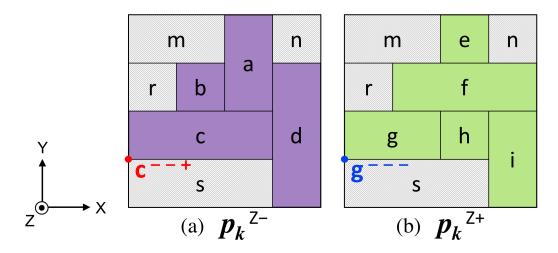

| Figure 2.6:                | Relations of the 3-D mosaic floorplan, corner links and four trees representations, and face and block partial orders                                                                                                                                                            | 29      |

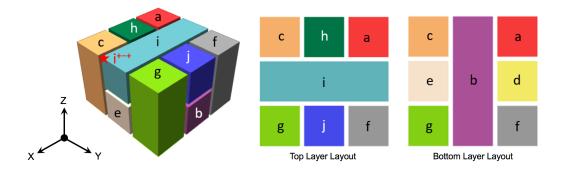

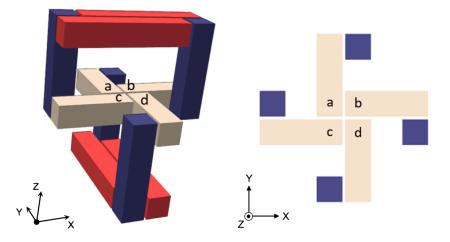

| Figure 2.7:  | A 3-D mosaic floorplan and layouts of the top and bottom layers.<br>There are ten blocks, <i>a</i> - <i>j</i> . A vertex of block <i>i</i> depicted by the red star indicates $i^{+-+}$ corner ( $i^{X+Y-Z+}$ ), meaning that the corner is located                                      |                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

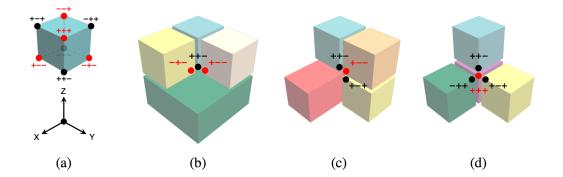

| Figure 2.8:  | at maximum X, minimum Y, and maximum Z coordinates of block $i$ .<br>Illustrations of neighboring corners. (a) Each red dot is one of four<br>opposite corners in 3-D floorplan, forming the root for each of four<br>trees representation (as shown in Figure 2.9). (b)-(d) Examples of | 30                              |

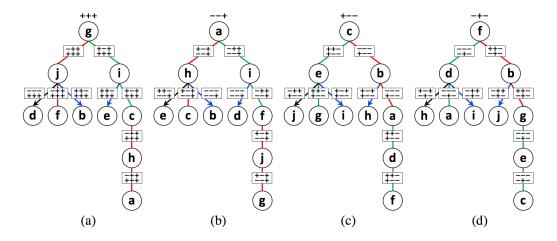

| Figure 2.9:  | corner links                                                                                                                                                                                                                                                                             | <ul><li>31</li><li>32</li></ul> |

| Figure 2.10: | Examples of constructing trees in Figures 2.9(a) and (b). Figures (a) and (b) correspondingly illustrate traversing procedures from each root, i.e., (a) corner $g^{+++}$ and (b) corner $a^{+}$ . Blocks <i>j</i> and <i>h</i> have                                                     |                                 |

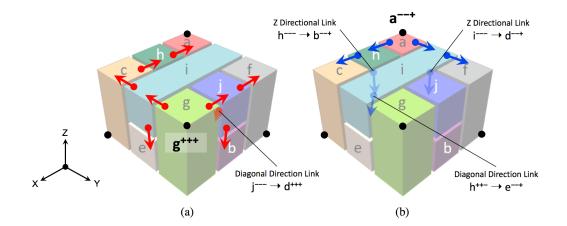

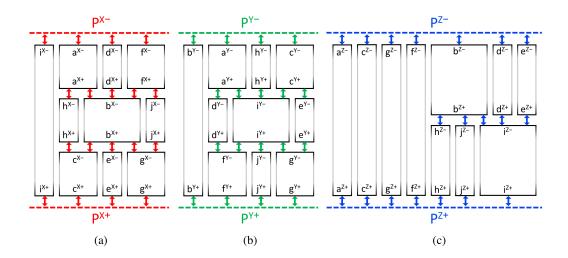

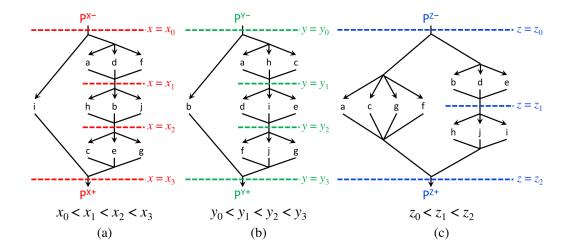

| Figure 2.11: | three neighboring corners to diagonal, $X$ , and $Z$ directions The face partial order representation for the 3-D mosaic floorplan in Figure 2.7. Figures (a), (b), and (c) present the face partial orders in $X$ (and) $X$ (graph) and $Z$ (blue) directions approximately             | 33                              |

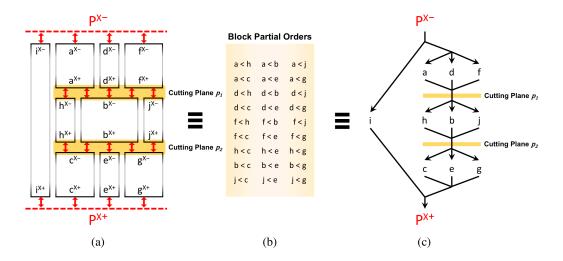

| Figure 2.12: | (from Figure 2.11(a)), (b) the $X$ -directional block partial orders, and                                                                                                                                                                                                                | 35                              |

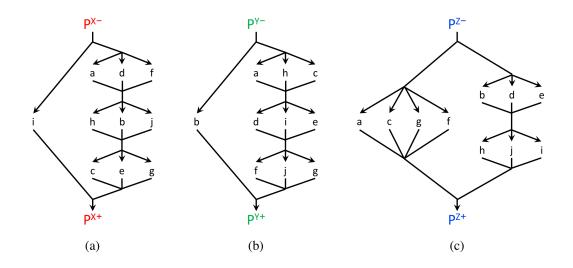

| Figure 2.13: |                                                                                                                                                                                                                                                                                          | 36                              |

| Figure 2.14: | mosaic floorplan in Figure 2.7                                                                                                                                                                                                                                                           | 37                              |

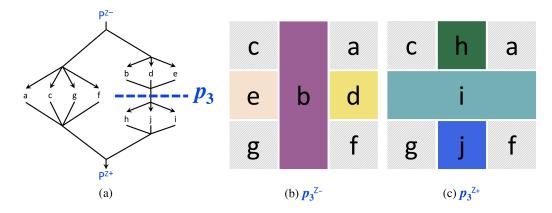

| Figure 2.15: | (i.e., $p_3^{Z^+}$ ) directions, respectively                                                                                                                                                                                                                                            | 40                              |

| Figure 2.16: | $S-$ and $S+$ are sets of blocks in $p_k^{Z-}$ and $p_k^{Z+}$ , respectively A special example for the non-degenerate 3-D floorplan, which has                                                                                                                                           | 40                              |

| Figure 2.17: | corners having more than one neighboring corner                                                                                                                                                                                                                                          | 42                              |

|              | the 3-D floorplan based on the partial order representation in Fig-<br>ure 2.13.                                                                                                                                                                                                         | 46                              |

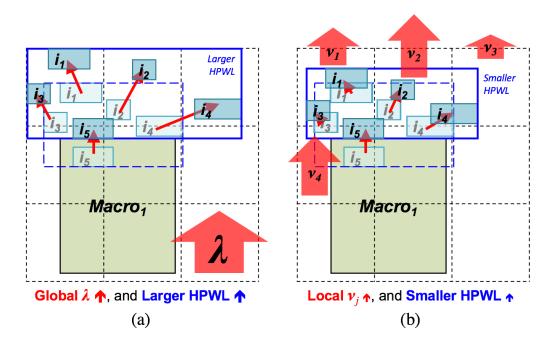

| Figure 3.1:  | Density forces with (a) global density-penalty factor $\lambda$ , and (b) constraint-<br>oriented local-density penalty factor $v_j$ per each bin. (Bin boundaries<br>are indicated by black dotted lines. Standard-cell instances are la-                                               |                                 |

|              | beled $i_1, \dots, i_5$ .)                                                                                                                                                                                                                                                               | 61                              |

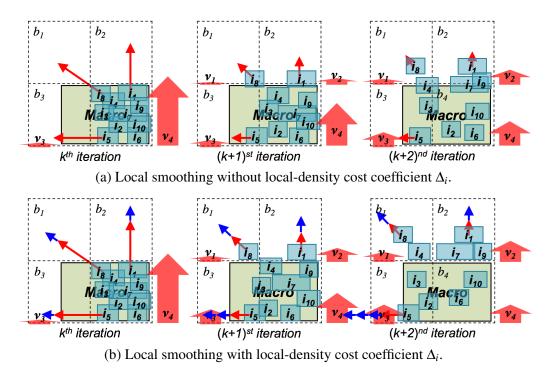

| Figure 3.2:                  | Local smoothing methods (a) without and (b) with local-density cost coefficient $\Delta_i$ . Figures are ordered from left to right by iteration in-                                                                                                                     |          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                              | dices. Figure (b) shows the effect of a larger force to spread cells from the overflowed bin $b_4$ .                                                                                                                                                                     | 63       |

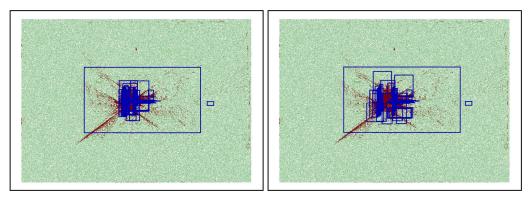

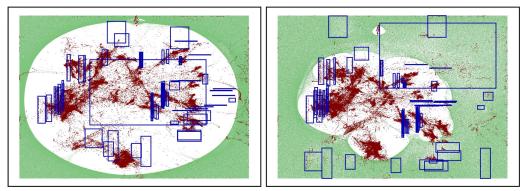

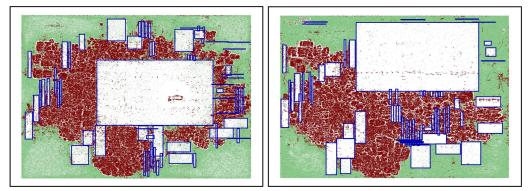

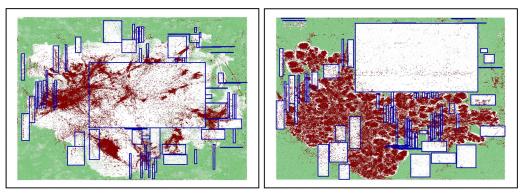

| Figure 3.3:                  | Placement of <i>NEWBLUE1</i> [138]: left hand side (LHS) images are from ePlace-MS [81], and right hand side (RHS) images are from                                                                                                                                       |          |

| Figure 3.4:                  | RePlAce-ld. The target density is set to 100%                                                                                                                                                                                                                            | 66       |

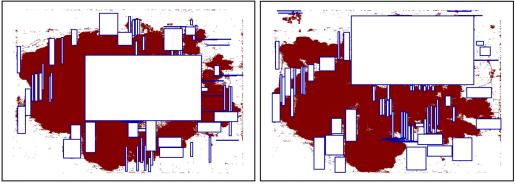

| Figure 3.5:                  | RePlAce-ld. The target density is set to 100%. Continued An illustration conceptually showing the benefit of dynamic step size adaptation. Cost is composite of wirelength and density. (a) Constant large step size; (b) Constant small step size; and (c) Our improved | 67       |

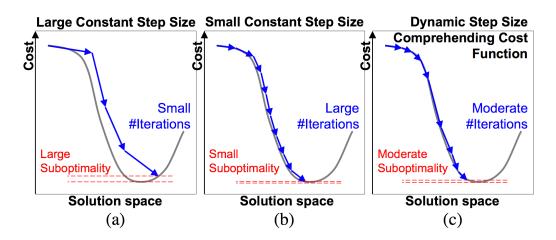

| Figure 3.6:                  | dynamic step size adaptation                                                                                                                                                                                                                                             | 69       |

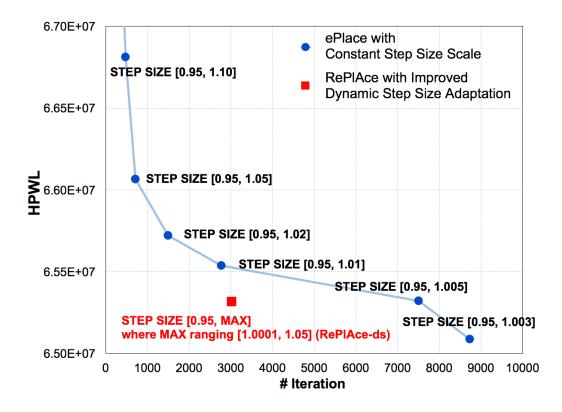

| Figure 3.7:                  | squares)                                                                                                                                                                                                                                                                 | 71       |

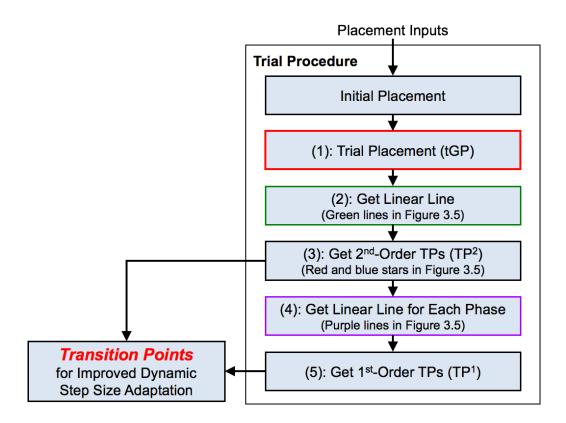

| Figure 3.8:                  | strategy, on the <i>ADAPTEC1</i> [138] testcase. RePlAce-ds achieves a dominating runtime and solution quality (red square) Flowchart of our trial placement procedure. The red rectangle in-                                                                            | 72       |

| Figure 3.9:                  | dicates nonlinear optimization using Nesterov's method. The actual placement procedure follows this trial placement procedure Illustration of blockage calculation. For the vertical edge on the right,                                                                  | 74       |

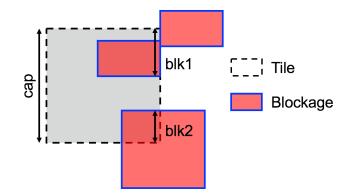

| Figure 3.10:                 | blk = blk1 + blk2. Note the union of blocked capacity for the upper<br>two blockages                                                                                                                                                                                     | 76       |

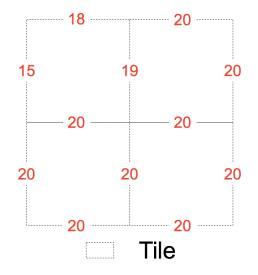

|                              | horizontal routing demand of $max(15, 19) = 19$ , and a vertical routing demand of $max(18, 20) = 20$ .                                                                                                                                                                  | 77       |

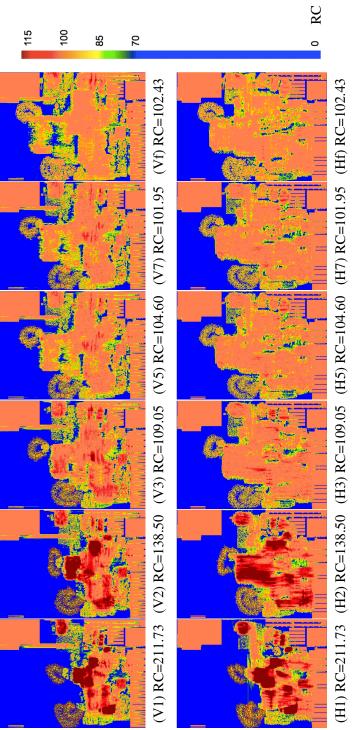

| Figure 3.11:<br>Figure 3.12: | -                                                                                                                                                                                                                                                                        | 79       |

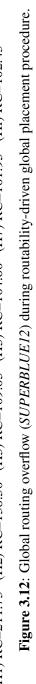

| Figure 3.13:                 | global placement procedure.<br>Runtime breakdown (#iterations) aggregated over all reported test-<br>cases in the ISPD-2005 and ISPD-2006 benchmark suites for (a)<br>RePlAce-ds, and in the MMS benchmark suite for (b) RePlAce-ds<br>and (c) RePlAce-ldds.             | 81<br>86 |

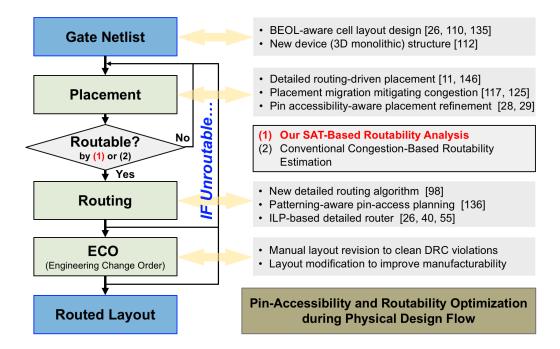

| Figure 4.1:                  | Efforts to secure the pin-accessibility during the PD procedure. Fail-<br>ure to produce routable (or routed) design in each step indicates loop-<br>back of PD procedure, causing additional design cost. Our SAT-based                                                 |          |

|                              | routability analysis (in red font) enables a fast and precise assessment.                                                                                                                                                                                                | 97       |

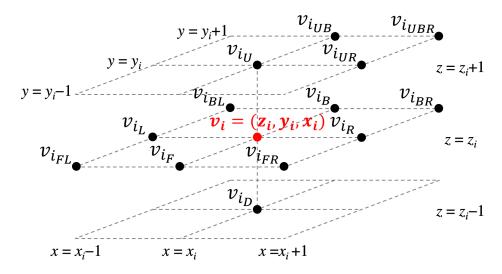

| Figure 4.2:  | Adjacent vertices (for our ILP formulation) of $v_i$ in the routing graph $G. \ldots \ldots$ |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

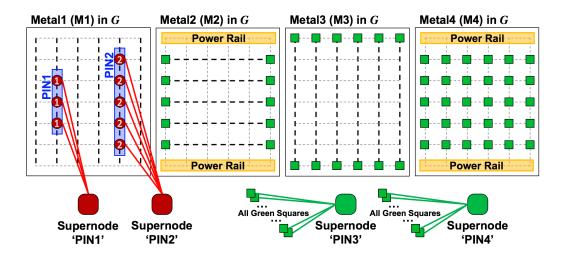

| Figure 4.3:  | An example of supernodes. <i>PIN</i> 1 and <i>PIN</i> 2 respectively cover three and five vertices on <i>M</i> 1 layer. Outer pins ( <i>PIN</i> 3 and <i>PIN</i> 4) are con-                                        |

|              | nected to boundary vertices of $G$                                                                                                                                                                                  |

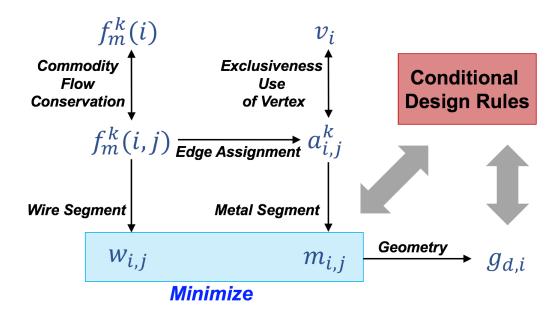

| Figure 4.4:  | Relations of our ILP-based routing optimization formulas and variables.104                                                                                                                                          |

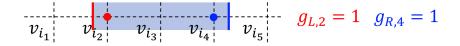

| Figure 4.5:  | An example to determine $g_{d,i}$                                                                                                                                                                                   |

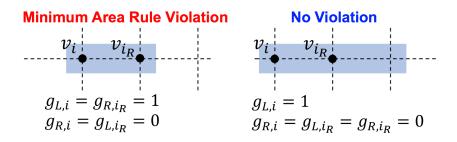

| Figure 4.6:  | An example of the minimum area rule                                                                                                                                                                                 |

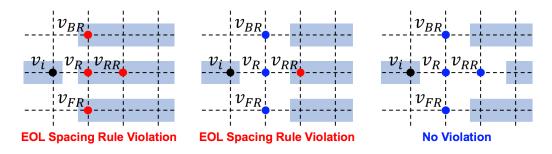

| Figure 4.7:  | An example of the end-of-line (EOL) spacing rule 106                                                                                                                                                                |

| Figure 4.8:  | Overall flow of our routability analysis                                                                                                                                                                            |

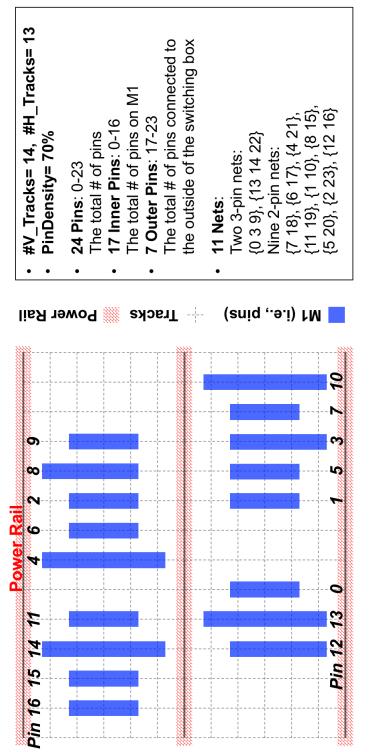

| Figure 4.9:  | An example layout with $14 \times 13$ vertial and horizontal tracks. 70%                                                                                                                                            |

|              | pin density. The total $\#pins=24$ . 17 pins are on $M1$ and seven                                                                                                                                                  |

|              | pins are outside of the layout (#outer pins are determined by Rent's                                                                                                                                                |

|              | rule [147]). We have 11 nets (i.e., two 3-pin nets and nine 2-pin nets). 112                                                                                                                                        |

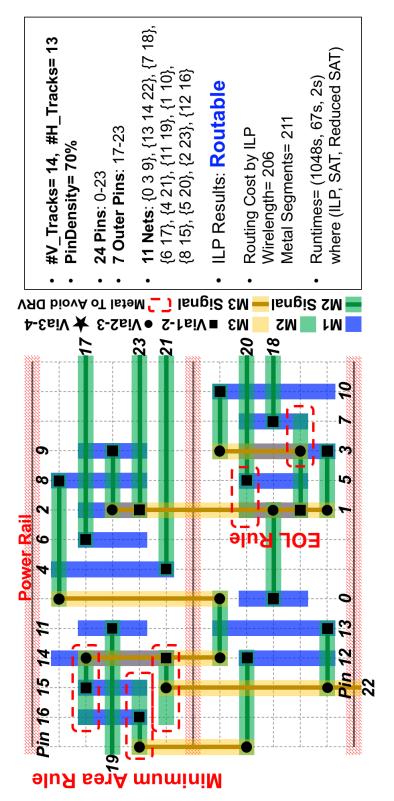

| Figure 4.10: | The ILP-based optimal routing solution for the layout in Figure 4.9.                                                                                                                                                |

|              | Cost = 417. Five more metal segments are assigned to avoid design                                                                                                                                                   |

|              | rule check (DRC) violations (red dotted circles)                                                                                                                                                                    |

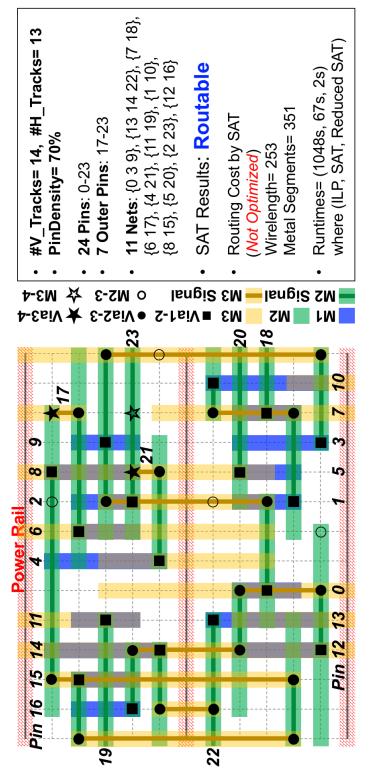

| Figure 4.11: | The reduced SAT-based routing solution for the layout in Figure 4.9.                                                                                                                                                |

|              | Cost = 604. The solution is not optimal, but takes only $0.19\%$ of                                                                                                                                                 |

|              | ILP's runtime, thus we can analyze the routability quickly 114                                                                                                                                                      |

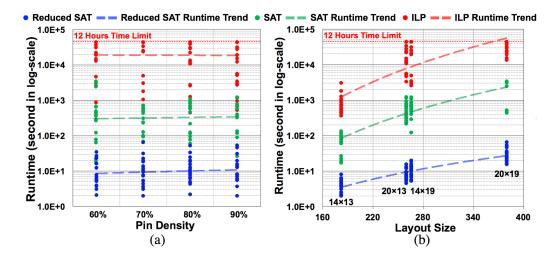

| Figure 4.12: | The runtime trends (in log-scale) across the (a) pin density and (b)                                                                                                                                                |

| -            | layout size (#vertical $\times$ #horizontal tracks)                                                                                                                                                                 |

|              |                                                                                                                                                                                                                     |

### LIST OF TABLES

| Table 1.1:               | Placement benchmark suites, from classic to modern benchmarks                                                                                                                                                                                                                                              | 8        |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 2.1:               | <i>X</i> -, <i>Y</i> -, and <i>Z</i> -directional absolute coordinates of all blocks of the 3-D floorplan in Figure 2.7, based on the relative orders of cutting planes in Figure 2.17. With the given physical dimensions of blocks, we can obtain the entire coordinates as described in Equations (2.2) | 47       |

| Table 3.1:               | Notations for local-density function.                                                                                                                                                                                                                                                                      | 64       |

| Table 3.2:               | Notations for routability-driven placement. We use the default length unit in the DAC-2012 and ICCAD-2012 benchmark suites.                                                                                                                                                                                | 75       |

| Table 3.3:               | RePlAce functionalities and the corresponding suffixes (command-<br>line options) that produce the results reported below.                                                                                                                                                                                 | 80       |

| Table 3.4:               | Statistics for ISPD-2005 [93], ISPD-2006 [92], and MMS [138] bench-                                                                                                                                                                                                                                        | 02       |

| Table 3.5:               | mark suites                                                                                                                                                                                                                                                                                                | 83       |

| Table 3.6:               | benchmarks                                                                                                                                                                                                                                                                                                 | 84<br>89 |

| Table 3.7:               | Scaled HPWL (sHPWL) ( $\times 10^7$ ), routing congestion (RC) and CPU runtime (minutes) comparison of RePlAce to leading published results for DAC-2012 [121] global routability-driven placement.                                                                                                        | 90       |

| Table 3.8:               | Scaled HPWL (sHPWL) ( $\times 10^7$ ), routing congestion (RC) and CPU runtime (minutes) comparison of RePlAce to leading published results for ICCAD-2012 [122] global routability-driven placement.                                                                                                      | 91       |

| Table 4.1:<br>Table 4.2: | Notations for ILP and SAT formulation                                                                                                                                                                                                                                                                      | 100      |

|                          | resents results of five distinct testcases, and shows numbers on average.                                                                                                                                                                                                                                  | 116      |

#### ACKNOWLEDGMENTS

Foremost, I would like to thank my advisor Professor Chung-Kuan Cheng for his encouragement and support. Without his generous advice my Ph.D. study would not have been finished. Indeed, I have learned a lot from him not only his brilliant academic knowledge, also his attitude toward research and life.

I would like to thank to my father Kyungchan Kang and my mother Woesoon Kim for their devotion and support. I would like to thank to my father-in-law Jongkyun Noh and my mother-in-law Kyoungock Jin for their encouragement. And I would like to thank to my wife Heemin Noh for her selfless support and my son Ryan Hyunwoo Kang for his assistance. My research would not have been possible without their sacrifice.

I would like to thank Professor Andrew B. Kahng for his academical support and encouragement. I have been truly influenced by his passionate and responsible attitude toward research.

I would like to thank my labmates (Xinyuan Wang, Po-Ya Hsu, Dongwon Park), former labmates (Dr. Hao Zhuang, Dr. Jingwei Lu, Professor Seokhyeong Kang, Dr. Tuck-Boon Chan, Dr. Siddhartha Nath, Dr. Jiajia Li, Dr. Wei-Ting (Jonas) Chan, Hyein Lee, Kwangsoo Han, Jeng-Hau Lin, Xinan Wang) and schoolmates (Lutong Wang, Mulong Luo, Bangqi Xu, Yeseong Kim, Xun Jiao, Dr. Seungjin Na) for their support and encouragement.

I would like to thank my industrial collaborators (Nancy MacDonald, Changho Han) for their insightful feedback and comments in my researches. I would like to thank my colleagues (Yufeng Luo, Dr. Chin-Chih Chang, Dr. Min Ouyang) for their thoughtful support and invaluable guidance.

I sincerely appreciate my thesis committee members Professor Ronald Graham, Professor Farinaz Koushanfar and Professor Bill Lin for their time and insightful feedback and comments.

The material in this thesis is based on the following publications.

Chapter 1 contains a reprint of Ilgweon Kang and Chung-Kuan Cheng, "Physical Layout after Half a Century: From Back-Board Ordering to Multi-Dimensional Placement and Beyond", *Proc. ACM/IEEE International Symposium on Physical Design*, 2017. The dissertation author is the primary author of the paper.

Chapter 2 contains a reprint of Fang Qiao, Ilgweon Kang, Daniel Kane, Evangeline Fung Yu Young, Chung-Kuan Cheng and Ronald Graham, "3D Floorplan Representations: Corner Links and Partial Order", *Proc. IEEE International Conference of 3D System Integration*, 2016. Chapter 2 also contains the draft submitted to *ACM Transactions on Design Automation of Electronic Systems*, Ilgweon Kang, Fang Qiao, Dongwon Park, Daniel Kane, Evangeline Fung Yu Young, Chung-Kuan Cheng and Ronald Graham, "3-D Floorplan Representations by Using Corner Links and Partial Order". The dissertation author is a main contributor of the paper and the primary author of the submitted draft.

Chapter 3 contains the draft submitted to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Chung-Kuan Cheng, Andrew B. Kahng, Ilgweon Kang and Lutong Wang, "Advancing Solution Quality and Routability Validation in Global Placement", 2017. The dissertation author is the primary author of the submitted draft.

Chapter 4 contains a reprint of Ilgweon Kang, Dongwon Park, Changho Han and Chung-Kuan Cheng, "Fast and Precise Routability Analysis with Conditional Design Rules", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2018. The dissertation author is the primary author of the paper.

My coauthors (Professor Chung-Kuan Cheng, Professor Ronald Graham, Changho Han, Professor Andrew B. Kahng, Professor Daniel Kane, Dongwon Park, Fang Qiao, Lutong Wang, and Professor Evangeline F. Y. Young, listed in alphabetical order) have all kindly approved the inclusion of the aforementioned publications in my thesis. VITA

| 2006         | B.Sc., Electrical and Electronics Engineering,<br>Yonsei University, Seoul, Republic of Korea |

|--------------|-----------------------------------------------------------------------------------------------|

| 2008         | M.Sc., Electrical and Electronics Engineering,<br>Yonsei University, Seoul, Republic of Korea |

| 2008-2010    | Engineer, DRAM Development Division,<br>SK Hynix, Icheon, Republic of Korea                   |

| 2010-2012    | Engineer, R&D Division,<br>SK Hynix, Icheon, Republic of Korea                                |

| 2016         | C.Phil., Computer Science (Computer Engineering),<br>University of California, San Diego      |

| 2017-Present | Lead Software Engineer, Digital Signoff Group,<br>Cadence Design Systems Inc., San Jose       |

| 2018         | Ph.D., Computer Science (Computer Engineering),<br>University of California, San Diego        |

All papers co-authored with Professor Andrew B. Kahng and the paper published at International Symposium on Physical Design (2018) have authors listed in alphabetical order. The first two drafts in the list are submitted for publication. The last three papers are published when the dissertation author was pursuing his Master's degree in Yonsei university, Seoul, Republic of Korea.

- Ilgweon Kang, Fang Qiao, Dongwon Park, Daniel Kane, Evangeline Fung Yu Young, Chung-Kuan Cheng and Ronald Graham, "3-D Floorplan Representations by Using Corner Links and Partial Order", *ACM Transactions on Design Automation of Electronic Systems*, under review.

- Chung-Kuan Cheng, Andrew B. Kahng, **Ilgweon Kang** and Lutong Wang, "Advancing Solution Quality and Routability Validation in Global Placement", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, under review.

- Ilgweon Kang, Dongwon Park, Changho Han and Chung-Kuan Cheng, "Fast and Precise Routability Analysis with Conditional Design Rules", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2018, to appear.

- Chung-Kuan Cheng, Ronald Graham, Ilgweon Kang, Dongwon Park, Xinyuan Wang, "Tree Structures and Algorithms for Physical Design", *Proc. ACM/IEEE International Symposium on Physical Design*, 2018, pp. 120-125.

- Ilgweon Kang and Chung-Kuan Cheng, "Physical Layout after Half a Century: From Back-Board Ordering to Multi-Dimensional Placement and Beyond", *Proc. ACM/IEEE International Symposium on Physical Design*, 2017, pp. 123-128.

- Fang Qiao, Ilgweon Kang, Daniel Kane, Chung-Kuan Cheng and Ronald Graham, "3D Floorplan Representations: Corner Links and Partial Order", *Proc. IEEE International Conference of 3D System Integration*, 2016, pp. 1-5.

- Hao Zhuang, Wenjian Yu, Shih-Hung Weng, Ilgweon Kang, Jeng-Hau Lin, Xiang Zhang, Ryan Coutts and Chung-Kuan Cheng, "Simulation Algorithms with Exponential Integration for Time-Domain Analysis of Large-Scale Power Delivery Networks", *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems 35(10) (2016), pp. 1681-1694.

- Jingwei Lu, Hao Zhuang, Ilgweon Kang, Pengwen Chen and Chung-Kuan Cheng, "ePlace-3D: Electrostatics based Placement for 3D-ICs", *Proc. ACM/IEEE International Symposium on Physical Design*, 2016, pp. 11-18.

- Jeng-Hau Lin, Hao Liu, Chia-Hung Liu, Phillip Lam, Gung-Yu Pan, Hao Zhuang, Ilgweon Kang, Patrick P. Mercier and Chung-Kuan Cheng, "An Interdigitated Non-Contact ECG Electrode for Impedance Compensation and Signal Restoration", *Proc. IEEE Biomedical Circuits and Systems Conference*, 2015, pp. 543-546.

- Hao Zhuang, Wenjian Yu, **Ilgweon Kang**, Xinan Wang and Chung-Kuan Cheng, "An Algorithmic Framework of Large-Scale Circuit Simulation Using Exponential Integrators", *Proc. ACM/IEEE Design Automation Conference*, 2015, pp. 163:1-163:6.

- Hao Zhuang, Xinan Wang, **Ilgweon Kang**, Jeng-Hau Lin and Chung-Kuan Cheng, "Dynamic Analysis of Power Delivery Network with Nonlinear Components Using Matrix Exponential Method", *Proc. IEEE Symposium on Electromagnetic Compatibility and Signal Integrity*, 2015, pp. 248-252.

- Ilgweon Kang, Xinan Wang, Jeng-Hau Lin, Ryan Coutts and Chung-Kuan Cheng, "Impulse Response Generation from S-Parameters for Power Delivery Network Simulation", *Proc. IEEE Symposium on Electromagnetic Compatibility and Signal Integrity*, 2015, pp. 277-282.

- Tuck-Boon Chan, Andrew B. Kahng, Ilgweon Kang, Hyein Lee and Jiajia Li, "Toward Assessment of True 3D Design Benefits over 2D Implementation", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2014, poster presentation.

- Andrew B. Kahng and Ilgweon Kang, "Co-Optimization of Memory BIST Grouping, Test Scheduling, and Logic Placement", *Proc. ACM/IEEE Design, Automation and Test in Europe*, 2014, pp. 196:1-196:6.

- Andrew B. Kahng, Ilgweon Kang and Siddhartha Nath, "Incremental Multiple-Scan Chain Ordering for ECO Flip-Flop Insertion", *Proc. ACM/IEEE International Conference on Computer-Aided Design*, 2013, pp. 705-712.

- Woosik Jeong, Ilgweon Kang, Kyowon Jin and Sungho Kang, "A Fast Bulit-in Redundancy Analysis for Memories with Optimal Repair Rate Using a Line-based Search Tree", *IEEE Transactions on Very Large Scale Integration Systems* 17(12) (2009), pp. 1665-1678.

- Ilgweon Kang, Woosik Jeong and Sungho Kang, "High-Efficiency Memory BISR with Two Serial RA Stages Using Spare Memories", *IET Electronics Letters* 44(8) (2008), pp. 515-517.

- Ilgweon Kang and Sungho Kang, "The Efficient Memory BISR Architecture Using Sign Bits", *Journal of the Institute of Electronics Engineers of Korea SD* 44(12) (2007), pp. 85-92.

#### ABSTRACT OF THE DISSERTATION

### Floorplan Representation, Global Placement, and Routability Analysis for VLSI Layout Design Automation

by

#### Ilgweon Kang

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2018

Professor Chung-Kuan Cheng, Chair

In the past decades, semiconductor technologies have significantly contributed to the modern society and human welfare, and led entire industries toward more automated systems with advancement of integrated circuits (ICs). Innovations and achievements on physical design (PD) have guided progresses of modern VLSI designs and automation. With the advanced performance of ICs, the overall industry has been profitable, and the global semiconductor market size has shown an upward-climbing trend for the past decades. Consequently, high-performance ICs enable the recent advent of the fourth industrial revolution that evolves almost every industry, e.g., artificial intelligence (AI), the Internet of things (IoT), bio- and nano-technology, autonomous vehicles, robotics, etc. While "Moore's Law" and "Dennard Scaling" have shown the correction of the slowing down, designing IC has become much more sophisticated and complicated. IC layout design directly impacts on timing closure, die utilization, routability, and design turnaround time (TAT); these in turn affect the classic design metrics of operating frequency, yield, power consumption and cost. As a result, physical design engineers face many nontrivial challenges, and the overall design cost increases rapidly. The industries look for higher efficiency in design optimization, automation, and innovation for high-performance ICs and design-cost reduction.

This dissertation describes new design methodologies for the advanced IC layout development and design automation. Chapter 2 introduces new three-dimensional (3-D) floorplan representations, *corner links, four trees*, and *partial order*, which enhance 3-D IC physical design automation. Our floorplan representations are potentially extendable toward multiple dimensions by adding factors such as time, energy, temperature, security, etc. Chapter 3 describes our constraint-driven and routability-driven global placement engine, *RePlAce*. RePlAce is a flat, nonlinear analytical global placement engine with electrostatics-based global-smooth density cost function. RePlAce addresses routing congestion as well as classical design goals (such as wirelength, area, etc.) with analogy of charge and electrical potential distribution. Chapter 4 presents a new framework that quickly identifies the design rule-correct routability smethod is developed on top of the multi-commodity flow theory and SAT-friendly ILP-based (integer linear programming-based) detailed routing formulation.

# Chapter 1

# Introduction

In the past decades, semiconductor technologies have significantly contributed to the modern society and human welfare, and led entire industries toward more automated systems with advancement of integrated circuits (ICs). Innovations and advancements on physical design (PD) guide progresses of modern VLSI designs and the automation and deserve considerable credits on the reduction of design gaps of VLSI layout designs. By virtue of the PD community and their efforts, the performance of ICs has been extremely advanced, the overall industry has been profitable, and the global semiconductor market size has shown an upward climbing for the past decades (as shown in Figures 1.1(a)-(b)).

While "Moore's Law" and "Dennard Scaling" have shown the correction of the slowing down, the hardware design cost increases rapidly and the cost per gate trend reverses from downward decreasing toward upward increasing after 20*nm* technology node. Figure 1.2 shows the hardware design cost per technology node in bar chart and the cost per gate trend in a curved line. In other words, the cost reduction by scaling becomes harder and harder or no longer available. In the meantime, the growth rate of IC industry revenue has stagnated. Thus, the industrial environment looks for higher efficiency on design optimization, automation, and innovation for cost reduction and performance improvement.

On the time scale of half a century, the challenges and opportunities we face today are actually the extension of, and in the same context as what we encountered before in the perspective of semiconductor history. Although we have faced many nontrivial chal-

(in billion U.S. dollars) [154].

**Figure 1.1**: Illustrations of semiconductor industry market size for the past decades. The asterisk marks at year indices indicate the value by forecasting.

dollars) [164].

**Figure 1.2**: Distribution of hardware design cost per technology node (bar chart) and the cost per gate trend (line) [155]. Hardware design cost at 90nm technology node is not available from the reference [155].

**Figure 1.3**: The organization of this dissertation. New 3-D floorplan representations, improved global placement engine, and SAT-based design-rule correct routability analysis.

lenges in the past, the integrated circuit industry has overcome and grown by our research and development. With this in mind, in the remaining Chapter 1, we present the current challenges on physical design and present opportunities that enable us to drive new growth engine. Then this dissertation describes new methodologies for improved physical design and its automation in three topics; (i) three-dimensional floorplan representation in Chapter 2, (ii) constraint-driven and routability-driven global placement in Chapter 3, and (iii) design rule-correct routability analysis based on Boolean satisfiability (SAT) formulation in Chapter 4.

The remainder of this chapter is organized as follows. Section 1.1 reviews researches and progresses on VLSI physical layout design. Section 1.2 introduces new opportunities on physical design with reference to the International Technology Roadmap for Semiconductors (ITRS). Section 1.3 concludes this chapter.

# 1.1 Researches on Physical Layout

Physical layout formulation is based on the VLSI technologies. On the other hand, physical layout enables the technologies, reduces design gaps, and extends the reach of the design capability. The academic activities have blossomed following the original

mission started by the SHARE committee half a century ago. The SHARE committee was formed in 1955 with the purpose of "Share to Help Avoid Redundant Effort". In 1964, the committee organized the first design automation conference (DAC) to provide a medium whereby people can interchange ideas, techniques, experience, and even specific programs on a regular basis.<sup>1</sup> In this section, we summarize researches and progresses on physical layout designs.

#### 1.1.1 Back-Board Ordering

The placement paper published at the first Design Automation Conference (DAC 1964) [130] is about back board ordering. At the very early days of physical layout design, most design complexity occurs at board and system levels. Placement of back boards was formulated as a one-dimensional ordering problem. We arrange circuit boards on a backplane in a linear order to minimize the wiring requirement of the backplane. Clearly, the quality of the placement causes a direct impact on the cost and performance of the system. Thus, the importance of physical layout optimization/automation is recognized in the early time of circuit designs. In [35], the author devised graphs to represent the placement process and thus used graph theory and Dijkstra algorithm to search for the optimal solutions. This work is one of the early attempts to use graph theory and mathematical algorithms for physical layout design automation.

#### 1.1.2 Two-Dimensional Physical Layout Design

For IC chip designs, we treat the placement as a two-dimensional (2-D) problem. In the transition between 1970s and 1980s, as the on-die circuit complexity increased, the need of placement tools became evident: layout designers could no longer handle hundreds of objects to produce high quality results in short turnaround. Early works in 1970s [36] [37] [38] [39] took advantage of previous works on one-dimensional ordering to improve the two-dimensional placement by rows or by columns iteratively, then the authors performed a two-dimensional placement with a tree search approach. After the

<sup>&</sup>lt;sup>1</sup>The first three DACs (i.e., DAC'64-DAC'66) were called as the SHARE design automation workshop. Later, International Conference on Computer-Aided Design was started in 1981 and then ISPD in 1997 after several years of workshop as a predecessor.

investigation, an in-house place-and-route (P&R) system (namely *LAMBDA*) [39] was announced as an industrial physical layout design tool.

As the circuit complexity kept growing, we observed several breakthroughs in placement algorithms to tackle the design gaps. With interconnect dominance, placement solution plays a significant role on system performance. IC designers allocate heavy efforts to improve the placement quality. We have seen the innovations via netlist/graph partitioning methods, combinatorial algorithms, and hierarchical approaches. In the 1980s when the placement sizes are less than a hundred thousand components, annealing-based methods produced excellent results [109]. However, as the problem sizes grew, the scalability of the iterative methods became a bottleneck. Partitioning-based placement methods could reduce the complexity using hierarchical methodologies at the expenses of quality loss due to suboptimal partitioning results.

As the placement problem size approached million components, major placement tools started with analytical algorithms using quadratic or nonlinear optimization. The analytical methods were proposed in the late 1970s [6] [51] [104] [133]. Throughout the years, many innovations made the method efficient and effective.

- The sparsity of the circuit was exploited with a quadratic formulation [22].

- The linear wire length metric was approximated with nonlinear equations.

- The cell density was enforced by partitioning, pulling anchors or local repulsive forces [15] [19] [22] [62] [69] [72] [123].

- Recently in ePlace [80] [81], the density was treated as electronic charges. The balance of the electrostatic system was modelled as classic Poisson equations. The global repulsive force could then be derived using fast Fourier transform with O(nlogn) complexity where *n* is the size of the problem.

- At the architecture level, floorplanning is a useful tool for physical layout design automation [44] [91] [95] [102] [118] [134].

With the highly competitive environments discussed above, the semiconductor IC market demand us more efforts and innovations to develop new design methodologies and to improve IC's performance. The role of physical design (PD) is to execute the physical

implementation flow, which carries the system design process. Physical design is one corner stone of a reliable, predictable implementation fabric [58] that enables system-level signoff. For a "modern" IC design, PD engineers must consider all design aspects together with various nontrivial design goals.

Due to the important role in the IC implementation steps, placement is one crucial research subject and we have many topics to further improve the solution quality. Thus, we should push the edge to further improve the solution quality and reduce the design gaps. In [5] [88], the authors summarize researches and progresses on placement and suggest directions that require intensive studies. As the authors of [5] [88] commonly mentioned, new approaches for performance-driven placement are intensively studied and should be studied in addition to the traditional placement metrics. We have seen in placement articles, the key words such as timing driven [87], routability driven [41], clock aware, datapath aware, signal integrity aware, power aware, etc. Recently, low-power design became one target objective for IC designs [5] [159]. The effort is to reduce packaging cost, increase battery life, and achieve high performance without thermal stress. Still, to produce low power design with tight constraints is nontrivial. In addition, mixed-size placement needs further improvement [88] [138]. In mixed-size designs, large modules can block routing space and enforce detours on critical interconnect. Thus, manual intervention is still wanted to place, refine, and align large modules. Additionally, tighter vertical integration in the design flow is important for the system performance. For example, interactions and convergences among physical design procedures frequently occur to reduce cost and improve solution quality: interactions between placement and gate sizing, buffer insertion, design for manufacturing; interface with logic synthesis, clock tree synthesis (CTS) and engineering change order (ECO). Thus, PD designers must consider more design aspects than before. Separately, a recent publication [61] gives a couple of interesting data points/correlations with respect to design automation research and design automation research outputs (papers, patents, and EDA companies).

# 1.1.3 Multi-Dimensional Physical Layout Design: 3-D, Potentially 4-D and Beyond

The extension to three-dimensional placement was initiated for the mapping of the dynamic FPGA (field-programmable gate array). Physical layout becomes a compiler tool for the high performance reconfigurable computing. Since the same space can be time shared by various functions, time domain becomes the third dimension for the placement. In this case, the turnaround time for the placement became even more critical since compilation is part of user experiences.

Recently, as three-dimensional IC technologies emerged as a promising option for the "more-than-Moore" strategy, three-dimensional layout became one key piece of the puzzle to enable the technology. We have found that with the addition of the third dimension, the floorplan topologies are much more complicated and the problem appears intriguing [103]. On top of three-dimensional physical space, we can add time as an extra dimension to make layout four-dimensional. Potentially, the number of dimensions can increase with extra factors such as energy, thermal, security and etc.

For three-dimensional placement, physical design engineers must address the challenging issues such as 3-D IC thermal distribution, floorplanning, clock tree synthesis, power distribution network, stacking methods by using through-silicon via (TSV) or monolithic inter-tier via (MIV), etc.

#### 1.1.4 Benchmarks

The release of the benchmarks enables the researchers to measure the algorithms on a common platform, and makes the research relevant to practice. Therefore, many innovations can be incorporated into EDA tools for applications in a faster pace. Table 1.1 lists classic and modern placement benchmark suites while Figure 1.4 depicts the trend. As shown in Figure 1.4, the number of instances saturates after 2005, but additional design features, e.g., density and routability, contribute to design complexity. In the meanwhile, the saturated circuit size calls a necessity of benchmarks with even larger number of instances since the size of circuits does matter on the choice of methods and quality of results, e.g., using distributed computation and memory management.

| Benchmark        | Description                                                    |

|------------------|----------------------------------------------------------------|

| Steinberg [115]  | Steinberg back-board placement                                 |

| Illiac IV [116]  | Board-level design for supercomputer                           |

| MCNC [13]        | General purpose benchmarks for design automation               |

| ISPD98 [3]       | Physical design applications, e.g., partitioning and placement |

| ISPD-2005 [93]   | Placement (also applicable to floorplanning and routing)       |

| ISPD-2006 [92]   | Placement with target density per benchmark                    |

| MMS [138]        | Large-scale modern mixed-size (MMS) placement                  |

| ISPD-2011 [120]  | (Global) Routability-driven placement                          |

| DAC-2012 [121]   | (Global) Routability-driven placement                          |

| ICCAD-2012 [122] | Design hierarchy aware (global) routability-driven placement   |

| ICCAD-2013 [71]  | Placement finishing – detailed placement and legalization      |

| ISPD-2014 [146]  | Detailed routing-driven placement                              |

| ICCAD-2014 [68]  | Incremental timing-driven placement                            |

| ISPD-2015 [11]   | Blockage-aware detailed routing-driven placement               |

| ICCAD-2015 [67]  | Incremental timing-driven placement                            |

| ISPD-2016 [139]  | Routability-driven FPGA placement                              |

| ISPD-2017 [158]  | Clock-aware FPGA placement                                     |

Table 1.1: Placement benchmark suites, from classic to modern benchmarks.

**Figure 1.4**: The benchmarks plotted with ranges of instances (displayed in log scale). Benchmarks are selectively chosen from Table 1.1. The minimum and maximum instances are displayed at the bottom and the top of each bar, respectively.

# 1.2 New Opportunities On Physical Design

In this section, we introduce new opportunities on physical design in three aspects: (i) the international technology roadmap for semiconductors (ITRS) shows that technology is going through divergence and evolution, which calls for new physical layout researches; (ii) paradigm-shifting design methodologies and innovative algorithmic techniques can improve design automation tools, and (iii) the semiconductor market and economy forecast show potential returns for further investments from the government and the industry.

#### **1.2.1** Physical Design and ITRS

The latest ITRS [159] report suggests numerous challenging research topics. Figure 1.5 illustrates the transistor structures for logic devices. For 10nm technology, the transistor structure use finFET and the technology node will advance to 7nm for mass production soon. As shown in Figure 1.6, the extensions to the existing FDSOI and fin-FET will sustain for two or three technology nodes until 2020 [159]. Beyond 2020 a transition to gate-all-around and potentially to vertical nanowires devices will be needed, providing new research topics.

Design of the routable and manufacturable layout for integrated circuits (ICs) has been more and more challenging as technology nodes are continuously advanced to sub-10*nm* [159]. One of the major difficulties is caused by the resolution limitations of optical lithography, using 193*i* wavelength [40] [110]. Multi-patterning techniques such as LELE (litho-etch-litho-etch), SADP and SAQP (self-aligned double and quadruple patterning) enable successful development of 10*nm* and sub-10*nm* technology nodes for foundries. However, they also induce complex conditional design rules for manufacturability which introduce new huddles for IC design.

Securing pin accessibility of IC components has become a critical bottleneck during detailed routing, due to less number of routing tracks and increasing pin density [110] [136]. FinFET device with smaller pin geometry makes the pin accessibility problem even harder [1]. The number of routing tracks in a single placement row has been

**Figure 1.5**: Shrink scenarios for logic devices [160]. In the current market (January 2017), the state-of-the-art transistor structure is finFET with 10nm technology.

| Year of Production              | 2015  | 2017  | 2019 | 2021 | 2024 | 2027  | 2030  |

|---------------------------------|-------|-------|------|------|------|-------|-------|

| Technology Node (nm)            | 16/14 | 11/10 | 8/7  | 6/5  | 4/3  | 3/2.5 | 2/1.5 |

| Transistor Structure            |       |       |      |      |      |       |       |

| Fully Depleted SOI (FDSOI)      |       |       |      |      |      |       |       |

| FinFET                          |       |       |      |      |      |       |       |

| Lateral Gate-All-Around (LGAA)  |       |       |      |      |      |       |       |

| Vertical Gate-All-Around (VGAA) |       |       |      |      |      |       |       |

| Monolithic 3D                   |       |       |      |      |      |       |       |

Figure 1.6: Transistor structure roadmap [159].

reduced from 12 tracks to nine/eight/seven tracks [64], and even five-track cell library with one fin is recently announced [8]. In the meanwhile, scaling metal pitch is lagged behind scaling device pitch, causing severe complications of interconnection induced by decrease of the valid access points for pins [151]. Consequently, the detailed routing step easily takes days of turnaround time (TAT), but a "successful" routing nonetheless is not guaranteed. Thus, we need a new design tool with fast TAT in analyzing the feasibility of the given layout architecture, e.g., design rules and patterns of pin assignment.

In Chapter 4, we propose a novel framework that efficiently identifies the conditional design rule-correct routability through well-organized ILP (integer linear programming) and SAT (Boolean satisfiability) formulation. Due to less number of pin-access points and dense pins for sub-10*nm* IC designs, the growing mismatch between globalroute congestion map and detailed-route design rule check (DRC) violations may endanger the on-time tapeout by demanding too many manual layout revisions [17]. The absence of fast and precise routability analysis tool at the early physical design stage (e.g., before routing) exposes the entire IC design project to high-risk unpredictability. Our resulting framework offers an early "go/no-go" decision opportunity for the remaining PD procedure, based on the precise routability assessment.

#### **1.2.2** New Techniques

Since designing ICs has been much more sophisticated and complicated, we need new techniques to solve many nontrivial challenges. IC layout design quality directly impacts overall design quality of results with respect to timing closure, die utilization, routability, and design turnaround time; these in turn affect the classic metrics of operating frequency, yield, power consumption and cost. Thus, the industrial environment looks for higher efficiency on design optimization, automation, and innovation for better performance and cost reduction.

Emerging algorithmic techniques from outside fields also provide potential methods to solve some physical design bottlenecks. Attempts to apply artificial intelligence and deep learning techniques present progresses to predict potential congestion during placement and to detect data paths from netlist or design-hierarchy information. Massively parallel computing gives new chances to try distributed algorithms which can drastically improve our computation and memory capacity. We remain the adaptation of the paradigm-shifting new techniques into the physical design as the future works, but we firmly believe that these new techniques will introduce new breakthroughs to us, opening tremendous opportunities.

In Chapter 3, we describe our constraint- and routability-driven global placement engine, *RePlAce*. Placement solution quality directly impacts overall IC design quality as placement is a fundamental, critical step in the physical design (PD) of integrated circuits (ICs) [60]. Despite significant improvement in placement algorithms over the past decades [89], efficient and effective placement remains a challenging issue [5], e.g., routable placement solution. The placement process must provide a routable solution to the router. RePlAce is a flat, nonlinear analytical global placement engine with electrostatics-based global-smooth density cost function, addressing routing congestion as well as classical design goals with analogy of charge and electrical potential distribution. RePlAce is the first work to achieve superior solution quality across all the ISPD-2005, ISPD-2006, MMS, DAC-2012 and ICCAD-2012 benchmark suites with a single placement engine.

#### **1.2.3** New Markets for IC Design

By virtue of physical designers' efforts, the performance of ICs has been extremely advanced, the overall industry has been profitable, and the global semiconductor market size has shown an upward climbing for the past decades. Consequently, the highly advanced ICs enable the recent advent of the fourth industrial revolution, evolving al-

Figure 1.7: Internet of Things (IoT): The explosively growing Internet device market [119].

most every industry, e.g., artificial intelligence (AI), the Internet of things robotics (IoT), biotechnology, autonomous vehicles, etc.

Historically, the EDA industry grew from solving new design problems and the industry grew by expanding the market demand. From the mid-90s, the Internet revolution has led the skyrocketing growth of the information technology. The advancement of semiconductor enabled portable and powerful devices with more functionality. Eventually, billions of electronic devices will be connected through the Internet (so called the Internet of Things (IoT), Figure 1.7). The trend inevitably results in "small quantity batch production" of ICs ensuring low power application, by very cost-effective design and manufacturing. The new market will enable a new growth engine to our industry with new opportunities.

In Chapter 2, we propose new 3-D IC floorplan representations, *corner links, four trees*, and *partial order*, enhancing 3-D IC physical design automation. As the market demand smaller footprint/wirelength and less power consumption, but better performance and more functionalities, we need a new IC design methodology to deliver the high-performance ICs. While "Moore's Law" and "Dennard Scaling" have shown the correction of the slowing down, three-dimensional (3-D) ICs offer a potential breakthrough to enable a paradigm-shift strategy, called "more than Moore", with novel features and

advantages over the conventional 2-D process technology by the nature of 3-D IC fabrication. With the three-dimensional (3-D) interconnections, 3-D IC provides substantial wirelength reduction and massive amount of bandwidth, leading performance improvement to overcome many of the nontrivial challenges of the semiconductor industry. Moreover, 3-D IC integration enables to stack disparate technologies with various functionalities into a single system-in-package (SiP), introducing "true 3-D IC" design.

# 1.3 Conclusion

In this chapter, we briefly review the previous paths and challenges in physical layout design field. Then, we introduce and summarize new opportunities of physical design related researches. These new opportunities strongly motivate the researches in this dissertation.

# **1.4** Acknowledgments

Chapter 1 contains a reprint of Ilgweon Kang and Chung-Kuan Cheng, "Physical Layout after Half a Century: From Back-Board Ordering to Multi-Dimensional Placement and Beyond", *Proc. ACM/IEEE International Symposium on Physical Design*, 2017. The dissertation author is the primary author of the paper.

I would like to thank my coauthor Chung-Kuan Cheng.

# Chapter 2

# **3-D Floorplan Representations by Using Corner Links and Partial Order**

Three-dimensional integrated circuit (3-D IC) technology offers a potential breakthrough to enable a paradigm-shift strategy, called "more than Moore", with novel features and advantages over the conventional 2-D process technology. With the three-dimensional interconnections, 3-D IC provides substantial wirelength reduction and a massive amount of bandwidth, which gives significant performance improvement to overcome many of the nontrivial challenges of semiconductor industry. Moreover, 3-D integration technology enables stacking disparate technologies with various functionalities into a single systemin-package (SiP), introducing "true 3-D IC" design.

As the first physical design (PD) step, floorplanning takes a crucial role to determine IC's overall design qualities such as footprint area, timing closure, power distribution, thermal management, etc. However, lack of efficient 3-D floorplanning algorithms that implement advantages of 3-D integration is a critical bottleneck for PD automation of 3-D IC design and implementation. 3-D floorplanning is a well-known NP-hard problem, and most of 3-D floorplan algorithms rely on heuristics and iterative improvements. Thus, developing efficient 3-D IC floorplan representations is important since floorplan representation provides the foundation of data structure to search the solution space for 3-D IC floorplanning. A well-defined floorplan representation provides an organized and cost-effective methodology to design high-performance 3-D IC.